JP6091582B2 - ゲートドライバ - Google Patents

ゲートドライバ Download PDFInfo

- Publication number

- JP6091582B2 JP6091582B2 JP2015216202A JP2015216202A JP6091582B2 JP 6091582 B2 JP6091582 B2 JP 6091582B2 JP 2015216202 A JP2015216202 A JP 2015216202A JP 2015216202 A JP2015216202 A JP 2015216202A JP 6091582 B2 JP6091582 B2 JP 6091582B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- source

- signal

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1335—Structural association of cells with optical devices, e.g. polarisers or reflectors

- G02F1/133528—Polarisers

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/481—Insulated gate field-effect transistors [IGFETs] characterised by the gate conductors

- H10K10/482—Insulated gate field-effect transistors [IGFETs] characterised by the gate conductors the IGFET comprising multiple separately-addressable gate electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1335—Structural association of cells with optical devices, e.g. polarisers or reflectors

- G02F1/13363—Birefringent elements, e.g. for optical compensation

- G02F1/133638—Waveplates, i.e. plates with a retardation value of lambda/n

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0847—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory without any storage capacitor, i.e. with use of parasitic capacitances as storage elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0254—Control of polarity reversal in general, other than for liquid crystal displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0267—Details of drivers for scan electrodes, other than drivers for liquid crystal, plasma or OLED displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0286—Details of a shift registers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0291—Details of output amplifiers or buffers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/20—Organic diodes

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Nonlinear Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Shift Register Type Memory (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of El Displays (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Semiconductor Memories (AREA)

- Logic Circuits (AREA)

Description

関する。また、半導体装置を適用した表示装置及び当該表示装置を具備する電子機器に関

する。

に、絶縁体上に非単結晶半導体により形成されたトランジスタを用いて、画素回路やシフ

トレジスタ回路等を含む駆動回路(以下、内部回路という)を一体形成する技術は、低消

費電力化、低コスト化、信頼性の向上、狭額縁化等に大きく貢献するため、活発に開発が

進められている。絶縁体上に形成された内部回路は、FPC(Flexible pri

nted circuit)等を介して絶縁体の外に配置されたコントローラIC等(以

下、外部回路という)に接続され、その動作が制御されている。

て構成されるシフトレジスタ回路が考案されている(特許文献1参照)。

め、ノイズが出力端子に発生しやすく、出力端子に発生したノイズによりシフトレジスタ

回路が誤動作するという問題を抱えていた。

回路が考案されている。例えば、特許文献2では、いわゆるスタティック駆動によって、

シフトレジスタ回路を動作することが提案されている。この場合、シフトレジスタ回路は

、出力端子がフローティング状態にならないため、出力端子に発生するノイズを減らすこ

とができる。

号を出力する選択期間と、非選択信号を出力する非選択期間とに分かれる。この動作期間

のうちほとんどの期間が非選択期間になる。選択信号が高電位(ハイレベル信号)である

場合には、非選択期間において、出力端子にトランジスタを介して非選択信号(低電位(

ロウレベル信号))を供給している。つまり、出力端子に低電位を供給するためのトラン

ジスタは、回路の動作期間のうちほとんどの期間においてオン状態となっている。

したがって劣化することが知られている。トランジスタが劣化すると、例えば、しきい値

電圧がプラス側へシフトするしきい値電圧シフトが起こり、回路の動作不良が生じる問題

がある。

例えば、トランスファーゲート)等と違って電流が流れる向きが固定されている場合が多

い。つまり、トランジスタのソースとドレインが固定化されているため、ドレイン側に電

界が集中し、トランジスタが劣化しやすくなっている。

トランジスタの劣化に伴う回路の動作不良を抑制することを目的の一とする。又は、トラ

ンジスタを有する回路の信頼性を向上させることを目的の一とする。

、Lレベル信号(ロウレベル信号))を出力し続けるトランジスタにおいて、当該トラン

ジスタを流れる電流の方向を入れ替える(反転させる)構成とする。つまり、トランジス

タの第1の端子と第2の端子(ソース又はドレインとなる端子)に加わる電圧の大小関係

を任意の期間毎に入れ替えることにより、ソースとドレインを任意の期間毎に切り替える

構成とする。

ル信号)を出力し続ける部分では、当該特定レベルの信号として、互いに異なる複数の電

位を有するLレベル信号(任意の期間毎に電位が変化するLレベル信号)を用いる。例え

ば、あるトランジスタを介してLレベル信号を出力し続ける場合、Lレベル信号として、

電位がVLHからなる第1の電位と、電位がVLLからなる第2の電位(VLH>VLL

)が任意の期間毎に切り替わる信号を用いることができる。つまり、電位が変化する信号

をLレベル信号として用い、トランジスタを流れる電流の方向を入れ替える(ソースとド

レインを入れ替える)ことによって、ソース側又はドレイン側への電界の集中を抑制し、

トランジスタの劣化を低減させる。

て機能すればどのような電位としてもよい。例えば、Lレベル信号が回路において非選択

信号となる場合には、第1の電位と第2の電位が非選択信号として機能するように電位を

設定すればよい。また、複数の電位として、3つ以上の電位を設定してもよい。

Hレベル信号として、電位がVHHからなる第1の電位と、電位がVHLからなる第2の

電位(VHH>VHL)が任意の期間に切り替わる信号を用いる。なお、第1の電位(V

HH)と第2の電位(VHL)は、回路においてHレベル信号として機能すればどのよう

な電位としてもよい。例えば、Hレベル信号が回路において選択信号となる場合には、第

1の電位と第2の電位が選択信号として機能するように電位を設定すればよい。

れ、他方が第3の配線と電気的に接続された第1のトランジスタと、ソース又はドレイン

の一方が第2の配線と電気的に接続され、他方が第3の配線と電気的に接続された第2の

トランジスタと、ゲートが第3の配線に電気的に接続され、第3の配線に供給される選択

信号によりオンとなり且つ非選択信号によりオフとなる第3のトランジスタとを有し、選

択信号が第1のトランジスタがオンしている期間に第1の配線から第3の配線へ供給され

、非選択信号が第2のトランジスタがオンしている期間に第2の配線から第3の配線へ供

給され、選択信号又は非選択信号の少なくとも一方が所定の期間毎に電位が変化する信号

であることを特徴としている。

れ、他方が第3の配線と電気的に接続された第1のトランジスタと、ソース又はドレイン

の一方が第2の配線と電気的に接続され、他方が第3の配線と電気的に接続され、且つ互

いに並列に設けられた複数の第2のトランジスタと、ゲートが第3の配線に電気的に接続

され、第3の配線に供給される選択信号によりオンとなり且つ非選択信号によりオフとな

る第3のトランジスタとを有し、選択信号が第1のトランジスタがオンしている期間に第

1の配線から第3の配線へ供給され、非選択信号が所定の期間毎に電位が変化する信号で

あって、複数の第2のトランジスタのいずれかがオンしている期間に第2の配線から第3

の配線へ供給されることを特徴としている。

れ、他方が第3の配線と電気的に接続された第1のトランジスタと、ソース又はドレイン

の一方が第2の配線と電気的に接続され、他方が第3の配線と電気的に接続された第2の

トランジスタと、ソース又はドレインの一方が第4の配線と電気的に接続され、他方が第

3の配線と電気的に接続された第4のトランジスタと、ゲートが第3の配線に電気的に接

続され、第3の配線に供給される選択信号によりオンとなり且つ非選択信号によりオフと

なる第3のトランジスタとを有し、選択信号が第1のトランジスタがオンしている期間に

第1の配線から第3の配線へ供給され、非選択信号が第2のトランジスタがオンしている

期間又は第4のトランジスタがオンしている期間に第2の配線又は第4の配線から第3の

配線へ供給され、第2の配線及び第4の配線には互いに異なる電位が印加され、且つ第2

の配線に印加される電位と第4の配線に印加される電位が入れ替わることを特徴としてい

る。

なるスイッチとして動作するため、トランジスタの極性(導電型)は特に限定されない。

ただし、オフ電流を抑えたい場合、オフ電流が少ない方の極性のトランジスタを用いるこ

とが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を有するトランジス

タやマルチゲート構造を有するトランジスタ等がある。または、スイッチとして動作させ

るトランジスタのソース端子の電位が、低電位側電源(Vss、GND、0Vなど)の電

位に近い値で動作する場合はNチャネル型トランジスタを用いることが望ましい。反対に

、ソース端子の電位が、高電位側電源(Vddなど)の電位に近い値で動作する場合はP

チャネル型トランジスタを用いることが望ましい。なぜなら、Nチャネル型トランジスタ

ではソース端子が低電位側電源の電位に近い値で動作するとき、Pチャネル型トランジス

タではソース端子が高電位側電源の電位に近い値で動作するとき、ゲートとソースの間の

電圧の絶対値を大きくできるため、スイッチとして、より正確な動作を行うことができる

からである。さらに、トランジスタがソースフォロワ動作をしてしまうことが少ないため

、出力電圧の大きさが小さくなってしまうことが少ないからである。

型のスイッチをスイッチとして用いてもよい。CMOS型のスイッチにすると、Pチャネ

ル型トランジスタまたはNチャネル型トランジスタのどちらか一方のトランジスタが導通

すれば電流が流れるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力

信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。さら

に、スイッチをオンまたはオフさせるための信号の電圧振幅値を小さくすることが出来る

ので、消費電力を小さくすることも出来る。

たはドレイン端子の一方)と、出力端子(ソース端子またはドレイン端子の他方)と、導

通を制御する端子(ゲート端子)とを有している。一方、スイッチとしてダイオードを用

いる場合、スイッチは、導通を制御する端子を有していない場合がある。そのため、トラ

ンジスタよりもダイオードをスイッチとして用いた方が、端子を制御するための配線を少

なくすることが出来る。

続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続さ

れている場合とを含むものとする。ここで、A、Bは、対象物(例えば、装置、素子、回

路、配線、電極、端子、導電膜、層、など)であるとする。したがって、所定の接続関係

、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続

関係以外のものも含むものとする。

とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイ

オードなど)が、AとBとの間に1個以上接続されていてもよい。あるいは、AとBとが

機能的に接続されている場合として、AとBとの機能的な接続を可能とする回路(例えば

、論理回路(インバータ、NAND回路、NOR回路など)、信号変換回路(DA変換回

路、AD変換回路、ガンマ補正回路など)、電位レベル変換回路(電源回路(昇圧回路、

降圧回路など)、信号の電位レベルを変えるレベルシフタ回路など)、電圧源、電流源、

切り替え回路、増幅回路(信号振幅または電流量などを大きく出来る回路、オペアンプ、

差動増幅回路、ソースフォロワ回路、バッファ回路など)、信号生成回路、記憶回路、制

御回路など)が、AとBとの間に1個以上接続されていてもよい。例えば、AとBとの間

に別の回路を挟んでいても、Aから出力された信号がBへ伝達される場合は、AとBとは

機能的に接続されているものとする。

気的に接続されている場合(つまり、AとBとの間に別の素子や別の回路を挟んで接続さ

れている場合)と、AとBとが機能的に接続されている場合(つまり、AとBとの間に別

の回路を挟んで機能的に接続されている場合)と、AとBとが直接接続されている場合(

つまり、AとBとの間に別の素子や別の回路を挟まずに接続されている場合)とを含むも

のとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続さ

れている、とのみ明示的に記載されている場合と同じであるとする。

置である発光装置は、様々な形態を用いることが出来る。例えば、表示素子、表示装置、

発光素子または発光装置としては、EL(エレクトロルミネッセンス)素子(有機物及び

無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LE

D、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ

)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ

(GLV)、プラズマディスプレイパネル(PDP)、デジタルマイクロミラーデバイス

(DMD)、圧電セラミックディスプレイ、カーボンナノチューブ、などを用いることが

できる。これらは、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが

変化する表示媒体を有することができる。なお、EL素子を用いた表示装置としてはEL

ディスプレイなどがある。電子放出素子を用いた表示装置としてはフィールドエミッショ

ンディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Surface−

conduction Electron−emitter Disply)などがある

。液晶素子を用いた表示装置としては液晶ディスプレイ(透過型液晶ディスプレイ、半透

過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶

ディスプレイ)などがある。電子インクや電気泳動素子を用いた表示装置としては電子ペ

ーパーなどがある。

子である。なお、EL層としては、1重項励起子からの発光(蛍光)を利用するもの、3

重項励起子からの発光(燐光)を利用するもの、1重項励起子からの発光(蛍光)を利用

するものと3重項励起子からの発光(燐光)を利用するものとを含むもの、有機物によっ

て形成されたもの、無機物によって形成されたもの、有機物によって形成されたものと無

機物によって形成されたものとを含むもの、高分子の材料、低分子の材料、高分子の材料

と低分子の材料とを含むものなどを有することができる。ただし、これに限定されず、E

L素子として様々なものを有することができる。

電子放出素子として、スピント型、カーボンナノチューブ(CNT)型、金属―絶縁体―

金属を積層したMIM(Metal−Insulator−Metal)型、金属―絶縁

体―半導体を積層したMIS(Metal−Insulator−Semiconduc

tor)型、MOS型、シリコン型、薄膜ダイオード型、ダイヤモンド型、金属―絶縁体

―半導体−金属型等の薄膜型、HEED型、EL型、ポーラスシリコン型、表面伝導(S

CE)型などを有することができる。ただし、これに限定されず、電子放出素子として様

々なものを有することができる。

子であり、一対の電極、及び液晶により構成される。なお、液晶の光学的変調作用は、液

晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御

される。なお、液晶素子としては、ネマチック液晶、コレステリック液晶、スメクチック

液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、

高分子液晶、高分子分散型液晶(PDLC)、強誘電液晶、反強誘電液晶、主鎖型液晶、

側鎖型高分子液晶、プラズマアドレス液晶(PALC)、バナナ型液晶などを挙げること

ができる。また、液晶の駆動方式としては、TN(Twisted Nematic)モ

ード、STN(Super Twisted Nematic)モード、IPS(In−

Plane−Switching)モード、FFS(Fringe Field Swi

tching)モード、MVA(Multi−domain Vertical Ali

gnment)モード、PVA(Patterned Vertical Alignm

ent)モード、ASV(Advanced Super View)モード、ASM(

Axially Symmetric aligned Micro−cell)モード

、OCB(Optically Compensated Birefringence

)モード、ECB(Electrically Controlled Birefri

ngence)モード、FLC(Ferroelectric Liquid Crys

tal)モード、AFLC(AntiFerroelectric Liquid Cr

ystal)モード、PDLC(Polymer Dispersed Liquid

Crystal)モード、ゲストホストモード、ブルー相(Blue Phase)モー

ドなどを用いることができる。ただし、これに限定されず、液晶素子及びその駆動方式と

して様々なものを用いることができる。

ど)、粒子により表示されるもの(電気泳動、粒子移動、粒子回転、相変化など)、フィ

ルムの一端が移動することにより表示されるもの、分子の発色/相変化により表示される

もの、分子の光吸収により表示されるもの、電子とホールが結合して自発光により表示さ

れるものなどのことをいう。例えば、電子ペーパーの表示方法として、マイクロカプセル

型電気泳動、水平移動型電気泳動、垂直移動型電気泳動、球状ツイストボール、磁気ツイ

ストボール、円柱ツイストボール方式、帯電トナー、電子粉流体、磁気泳動型、磁気感熱

式、エレクトロウェッテイング、光散乱(透明/白濁変化)、コレステリック液晶/光導

電層、コレステリック液晶、双安定性ネマチック液晶、強誘電性液晶、2色性色素・液晶

分散型、可動フィルム、ロイコ染料による発消色、フォトクロミック、エレクトロクロミ

ック、エレクトロデポジション、フレキシブル有機ELなどを用いることができる。ただ

し、これに限定されず、電子ペーパー及びその表示方法として様々なものを用いることが

できる。ここで、マイクロカプセル型電気泳動を用いることによって、電気泳動方式の欠

点である泳動粒子の凝集、沈殿を解決することができる。電子粉流体は、高速応答性、高

反射率、広視野角、低消費電力、メモリー性などのメリットを有する。

を表面に形成し且つ溝内に蛍光体層を形成した基板とを狭い間隔で対向させて、希ガスを

封入した構造を有する。あるいは、プラズマチューブを上下からフィルム状の電極で挟み

込んだ構造とすることも可能である。プラズマチューブとは、ガラスチューブ内に、放電

ガス、RGBそれぞれの蛍光体などを封止したものである。プラズマディスプレイパネル

は、電極間に電圧をかけることによって紫外線を発生させ、蛍光体を光らせることで、表

示を行うことができる。なお、放電方式としては、DC型とAC型があり、どちらを用い

てもよい。ここで、プラズマディスプレイパネルの駆動方式としては、AWS(Addr

ess While Sustain)駆動、サブフレームをリセット期間、アドレス期

間、維持期間に分割するADS(Address Display Separated

)駆動、CLEAR(HI‐CONTRAST&LOW ENERGY ADDRESS

&REDUCTION OF FALSE CONTOUR SEQUENCE)駆動、

ALIS(Alternate Lighting of Surfaces)方式、T

ERES(Technology of Reciprocal Sustainer)

駆動などを用いることができる。ただし、これに限定されず、プラズマディスプレイパネ

ルの駆動方式として様々なものを用いることができる。

、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射

型液晶ディスプレイ)、グレーティングライトバルブ(GLV)を用いた表示装置、デジ

タルマイクロミラーデバイス(DMD)を用いた表示装置などの光源としては、エレクト

ロルミネッセンス、冷陰極管、熱陰極管、LED、レーザー光源、水銀ランプなどを用い

ることができる。ただし、これに限定されず、光源として様々なものを用いることができ

る。

用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微

結晶(マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う)シリコンなど

に代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを用いることが

出来る。TFTを用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よ

りも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることが

できる。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多く

の個数の表示装置を製造できるため、低コストで製造できる。さらに、製造温度が低いた

め、耐熱性の弱い基板を用いることができる。そのため、透光性を有する基板上にトラン

ジスタを製造できる。そして、透光性を有する基板上のトランジスタを用いて表示素子で

の光の透過を制御することが出来る。あるいは、トランジスタの膜厚が薄いため、トラン

ジスタを構成する膜の一部は、光を透過させることが出来る。そのため、開口率が向上さ

せることができる。

晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その

結果、ゲートドライバ回路(走査線駆動回路)やソースドライバ回路(信号線駆動回路)

、信号処理回路(信号生成回路、ガンマ補正回路、DA変換回路など)を基板上に一体形

成することが出来る。

晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。この

とき、レーザー照射を行うことなく、熱処理を加えるだけで、結晶性を向上させることも

可能である。その結果、ソースドライバ回路の一部(アナログスイッチなど)およびゲー

トドライバ回路(走査線駆動回路)を基板上に一体形成することが出来る。さらに、結晶

化のためにレーザー照射を行わない場合は、シリコンの結晶性のムラを抑えることができ

る。そのため、画質の向上した画像を表示することが出来る。

ことは可能である。

で行うことが望ましいが、それに限定されない。パネルの一部の領域のみにおいて、シリ

コンの結晶性を向上させてもよい。選択的に結晶性を向上させることは、レーザー光を選

択的に照射することなどにより可能である。例えば、画素以外の領域である周辺回路領域

にのみ、レーザー光を照射してもよい。または、ゲートドライバ回路、ソースドライバ回

路等の領域にのみ、レーザー光を照射してもよい。あるいは、ソースドライバ回路の一部

(例えば、アナログスイッチ)の領域にのみ、レーザー光を照射してもよい。その結果、

回路を高速に動作させる必要がある領域にのみ、シリコンの結晶化を向上させることがで

きる。画素領域は、高速に動作させる必要性が低いため、結晶性が向上されなくても、問

題なく画素回路を動作させることが出来る。結晶性を向上させる領域が少なくて済むため

、製造工程も短くすることが出来、スループットが向上し、製造コストを低減させること

が出来る。必要とされる製造装置の数も少ない数で製造できるため、製造コストを低減さ

せることが出来る。

れらにより、特性やサイズや形状などのバラツキが少なく、電流供給能力が高く、サイズ

の小さいトランジスタを製造することができる。これらのトランジスタを用いると、回路

の低消費電力化、又は回路の高集積化を図ることができる。

O)、シリコンゲルマニウム(SiGe)、砒化ガリウム(GaAs)、酸化インジウム

酸化亜鉛(IZO)、インジウム錫酸化物(ITO)、酸化錫(SnO)などの化合物半

導体または酸化物半導体を有するトランジスタや、さらに、これらの化合物半導体または

酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、

製造温度を低くでき、例えば、室温でトランジスタを製造することが可能となる。その結

果、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形

成することが出来る。なお、これらの化合物半導体または酸化物半導体を、トランジスタ

のチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、こ

れらの化合物半導体または酸化物半導体を抵抗素子、画素電極、透光性を有する電極とし

て用いることができる。さらに、それらをトランジスタと同時に成膜又は形成できるため

、コストを低減できる。

る。これらにより、室温で製造、低真空度で製造、又は大型基板上に製造することができ

る。マスク(レチクル)を用いなくても製造することが可能となるため、トランジスタの

レイアウトを容易に変更することが出来る。さらに、レジストを用いる必要がないので、

材料費が安くなり、工程数を削減できる。さらに、必要な部分にのみ膜を付けるため、全

面に成膜した後でエッチングする、という製法よりも、材料が無駄にならず、低コストに

できる。

る。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。

このような基板を用いた半導体装置は、衝撃に対して強くすることができる。

タ、接合型トランジスタ、バイポーラトランジスタなどをトランジスタとして用いること

が出来る。MOS型トランジスタを用いることにより、トランジスタのサイズを小さくす

ることが出来る。よって、複数のトランジスタを搭載することができる。バイポーラトラ

ンジスタを用いることにより、大きな電流を流すことが出来る。よって、高速に回路を動

作させることができる。

成してもよい。これにより、低消費電力、小型化、高速動作などを実現することが出来る

。

。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。マルチゲ

ート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に

接続された構成となる。マルチゲート構造により、オフ電流の低減、トランジスタの耐圧

向上(信頼性の向上)を図ることができる。あるいは、マルチゲート構造により、飽和領

域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があ

まり変化せず、電圧・電流特性の傾きをフラットにすることができる。電圧・電流特性の

傾きがフラットである特性を利用すると、理想的な電流源回路や、非常に高い抵抗値をも

つ能動負荷を実現することが出来る。その結果、特性のよい差動回路やカレントミラー回

路を実現することが出来る。

る。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域

が増えるため、電流値の増加を図ることができる。または、チャネルの上下にゲート電極

が配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図

ることができる。なお、チャネルの上下にゲート電極が配置される構成にすることにより

、複数のトランジスタが並列に接続されたような構成となる。

配置されている構造、正スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた

構造、チャネル領域を並列に接続した構造、またはチャネル領域が直列に接続する構成も

適用できる。さらに、チャネル領域(もしくはその一部)にソース電極やドレイン電極が

重なっている構造も適用できる。チャネル領域(もしくはその一部)にソース電極やドレ

イン電極が重なる構造にすることによって、チャネル領域の一部に電荷が溜まることによ

り動作が不安定になることを防ぐことができる。あるいは、LDD領域を設けた構造を適

用できる。LDD領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向

上(信頼性の向上)を図ることができる。あるいは、LDD領域を設けることにより、飽

和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流

があまり変化せず、電圧・電流特性の傾きをフラットにすることができる。

ることができる。したがって、所定の機能を実現させるために必要な回路の全てを、同一

の基板に形成することも可能である。例えば、所定の機能を実現させるために必要な回路

の全てを、ガラス基板、プラスチック基板、単結晶基板、またはSOI基板などの様々な

基板を用いて形成することも可能である。所定の機能を実現させるために必要な回路の全

てが同じ基板を用いて形成されていることにより、部品点数の削減によるコストの低減、

又は回路部品との接続点数の低減による信頼性の向上を図ることができる。あるいは、所

定の機能を実現させるために必要な回路の一部が、ある基板に形成され、所定の機能を実

現させるために必要な回路の別の一部が、別の基板に形成されていることも可能である。

つまり、所定の機能を実現させるために必要な回路の全てが同じ基板を用いて形成されて

いなくてもよい。例えば、所定の機能を実現させるために必要な回路の一部は、ガラス基

板上にトランジスタにより形成され、所定の機能を実現させるために必要な回路の別の一

部は、単結晶基板に形成され、単結晶基板を用いて形成されたトランジスタで構成された

ICチップをCOG(Chip On Glass)でガラス基板に接続して、ガラス基

板上にそのICチップを配置することも可能である。あるいは、そのICチップをTAB

(Tape Automated Bonding)やプリント基板を用いてガラス基板

と接続することも可能である。このように、回路の一部が同じ基板に形成されていること

により、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信

頼性の向上を図ることができる。あるいは、駆動電圧が高い部分及び駆動周波数が高い部

分の回路は、消費電力が大きくなってしまうので、そのような部分の回路は同じ基板に形

成せず、そのかわりに、例えば、単結晶基板にその部分の回路を形成して、その回路で構

成されたICチップを用いるようにすれば、消費電力の増加を防ぐことができる。

ては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。

従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合

には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるもの

とする。なお、色要素は、三色に限定されず、三色以上を用いても良いし、RGB以外の

色を用いても良い。例えば、白色を加えて、RGBW(Wは白)としても可能である。あ

るいは、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色な

どを一色以上追加することも可能である。あるいは、例えば、RGBの中の少なくとも一

色に類似した色を、RGBに追加することも可能である。例えば、R、G、B1、B2と

してもよい。B1とB2とは、どちらも青色であるが、波長が異なっている。同様に、R

1、R2、G、Bとすることも可能である。このような色要素を用いることにより、より

実物に近い表示を行うことができる。このような色要素を用いることにより、消費電力を

低減することが出来る。別の例としては、一つの色要素について、複数の領域を用いて明

るさを制御する場合は、その領域一つ分を一画素とすることも可能である。よって、一例

として、面積階調を行う場合または副画素(サブ画素)を有している場合、一つの色要素

につき、明るさを制御する領域が複数あり、その全体で階調を表現するが、明るさを制御

する領域の一つ分を一画素とすることも可能である。よって、その場合は、一つの色要素

は、複数の画素で構成されることとなる。あるいは、明るさを制御する領域が一つの色要

素の中に複数あっても、それらをまとめて、一つの色要素を1画素としてもよい。よって

、その場合は、一つの色要素は、一つの画素で構成されることとなる。あるいは、一つの

色要素について、複数の領域を用いて明るさを制御する場合、画素によって、表示に寄与

する領域の大きさが異なっている場合がある。あるいは、一つの色要素につき複数ある、

明るさを制御する領域において、各々に供給する信号を僅かに異ならせるようにして、視

野角を広げるようにしてもよい。つまり、一つの色要素について、複数個ある領域が各々

有する画素電極の電位が、各々異なっていることも可能である。その結果、液晶分子に加

わる電圧が各画素電極によって各々異なる。よって、視野角を広くすることが出来る。

える場合であるとする。一画素(一色分)と明示的に記載する場合は、一つの色要素につ

き、複数の領域がある場合、それらをまとめて一画素と考える場合であるとする。

リクスに配置(配列)されているとは、縦方向もしくは横方向において、画素が直線上に

並んで配置されている、又はギザギザな線上に配置されている場合を含む。よって、例え

ば三色の色要素(例えばRGB)でフルカラー表示を行う場合に、ストライプ配置されて

いる場合、又は三つの色要素のドットがデルタ配置されている場合も含む。さらに、ベイ

ヤー配置されている場合も含む。なお、色要素のドット毎にその表示領域の大きさが異な

っていてもよい。これにより、低消費電力化、又は表示素子の長寿命化を図ることができ

る。

しないパッシブマトリクス方式を用いることが出来る。

ンジスタだけでなく、さまざまな能動素子(アクティブ素子、非線形素子)を用いること

が出来る。例えば、MIM(Metal Insulator Metal)やTFD(

Thin Film Diode)などを用いることも可能である。これらの素子は、製

造工程が少ないため、製造コストの低減、又は歩留まりの向上を図ることができる。さら

に、素子のサイズが小さいため、開口率を向上させることができ、低消費電力化や高輝度

化をはかることが出来る。

素子)を用いないパッシブマトリクス型を用いることも可能である。能動素子(アクティ

ブ素子、非線形素子)を用いないため、製造工程が少なく、製造コストの低減、又は歩留

まりの向上を図ることができる。能動素子(アクティブ素子、非線形素子)を用いないた

め、開口率を向上させることができ、低消費電力化や高輝度化をはかることが出来る。

を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレ

イン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソー

スとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソー

スまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインと

して機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例と

しては、それぞれを第1端子、第2端子と表記する場合がある。あるいは、それぞれを第

1電極、第2電極と表記する場合がある。あるいは、第1領域、第2領域と表記する場合

がある。

する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2

端子などと表記する場合がある。

号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極と

は、チャネル領域を形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部

分の導電膜のことを言う。なお、ゲート電極の一部は、LDD(Lightly Dop

ed Drain)領域またはソース領域(またはドレイン領域)と、ゲート絶縁膜を介

してオーバーラップしている場合もある。ゲート配線とは、各トランジスタのゲート電極

の間を接続するための配線、各画素の有するゲート電極の間を接続するための配線、又は

ゲート電極と別の配線とを接続するための配線のことを言う。

ータ線、データ信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言

う。ソース領域とは、P型不純物(ボロンやガリウムなど)やN型不純物(リンやヒ素な

ど)が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物

が含まれる領域、いわゆる、LDD(Lightly Doped Drain)領域は

、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソ

ース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソー

ス電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各トラン

ジスタのソース電極の間を接続するための配線、各画素の有するソース電極の間を接続す

るための配線、又はソース電極と別の配線とを接続するための配線のことを言う。

回路を有する装置のことをいう。さらに、半導体特性を利用することで機能しうる装置全

般を半導体装置と呼んでもよい。または、半導体材料を有する装置のことを半導体装置と

言う。

を含む複数の画素を含んでいても良い。なお、表示装置は、複数の画素を駆動させる周辺

駆動回路を含んでいても良い。なお、複数の画素を駆動させる周辺駆動回路は、複数の画

素と同一基板上に形成されてもよい。なお、表示装置は、ワイヤボンディングやバンプな

どによって基板上に配置された周辺駆動回路、いわゆる、チップオングラス(COG)で

接続されたICチップ、または、TABなどで接続されたICチップを含んでいても良い

。なお、表示装置は、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなど

が取り付けられたフレキシブルプリントサーキット(FPC)を含んでもよい。なお、表

示装置は、フレキシブルプリントサーキット(FPC)などを介して接続され、ICチッ

プ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたプリント配線

基板(PWB)を含んでいても良い。なお、表示装置は、偏光板または位相差板などの光

学シートを含んでいても良い。なお、表示装置は、照明装置、筐体、音声入出力装置、光

センサなどを含んでいても良い。

シート、光源(LED、冷陰極管など)、冷却装置(水冷式、空冷式)などを有していて

も良い。

素子を有している場合は、発光装置は、表示装置の具体例の一つである。

をいう。

視型、投写型、透過型、反射型、半透過型などがある。

ば、ソース信号線から画素内への信号の入力を制御するトランジスタ(選択用トランジス

タ、スイッチング用トランジスタなどと呼ぶことがある)、画素電極に電圧または電流を

供給するトランジスタ、発光素子に電圧または電流を供給するトランジスタなどは、駆動

装置の一例である。さらに、ゲート信号線に信号を供給する回路(ゲートドライバ、ゲー

ト線駆動回路などと呼ぶことがある)、ソース信号線に信号を供給する回路(ソースドラ

イバ、ソース線駆動回路などと呼ぶことがある)などは、駆動装置の一例である。

は、互いに重複して有している場合がある。例えば、表示装置が、半導体装置および発光

装置を有している場合がある。あるいは、半導体装置が、表示装置および駆動装置を有し

ている場合がある。

良を抑制することができる。

上させることができる。

る態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及

び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って実施の形態の

記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一

部分又は同様な機能を有する部分は異なる図面間で共通の符号を用いて示し、同一部分又

は同様な機能を有する部分の詳細な説明は省略する。

態で述べる別の内容(一部の内容でもよい)、及び/又は、一つ若しくは複数の別の実施

の形態で述べる内容(一部の内容でもよい)に対して、適用、組み合わせ、又は置き換え

などを行うことが出来る。

述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

その実施の形態において述べる別の図(一部でもよい)、及び/又は、一つ若しくは複数

の別の実施の形態において述べる図(一部でもよい)に対して、組み合わせることにより

、さらに多くの図を構成させることが出来る。

して、発明の一態様を構成することは可能である。したがって、ある部分を述べる図また

は文章が記載されている場合、その一部分の図または文章を取り出した内容も、発明の一

態様として開示されているものであり、発明の一態様を構成することが可能であるものと

する。そのため、例えば、能動素子(トランジスタ、ダイオードなど)、配線、受動素子

(容量素子、抵抗素子など)、導電層、絶縁層、半導体層、有機材料、無機材料、部品、

基板、モジュール、装置、固体、液体、気体、動作方法、製造方法などが単数又は複数記

載された図面(断面図、平面図、回路図、ブロック図、フローチャート、工程図、斜視図

、立面図、配置図、タイミングチャート、構造図、模式図、グラフ、表、光路図、ベクト

ル図、状態図、波形図、写真、化学式など)または文章において、その一部分を取り出し

て、発明の一態様を構成することが可能であるものとする。一例としては、N個(Nは整

数)の回路素子(トランジスタ、容量素子等)を有して構成される回路図から、M個(M

は整数で、M<N)の回路素子(トランジスタ、容量素子等)を抜き出して、発明の一態

様を構成することは可能である。別の一例としては、N個(Nは整数)の層を有して構成

される断面図から、M個(Mは整数で、M<N)の層を抜き出して、発明の一態様を構成

することは可能である。別の一例としては、N個(Nは整数)の要素を有して構成される

フローチャートから、M個(Mは整数で、M<N)の要素を抜き出して、発明の一態様を

構成することは可能である。

体例が記載される場合、その具体例の上位概念を導き出すことは、当業者であれば容易に

理解される。したがって、ある一つの実施の形態において述べる図または文章において、

少なくとも一つの具体例が記載される場合、その具体例の上位概念も、発明の一態様とし

て開示されているものであり、発明の一態様を構成することが可能である。

示されているものであり、発明の一態様を構成することが可能である。したがって、ある

内容について、図に記載されていれば、文章を用いて述べていなくても、その内容は、発

明の一態様として開示されているものであり、発明の一態様を構成することが可能である

。同様に、図の一部を取り出した図についても、発明の一態様として開示されているもの

であり、発明の一態様を構成することが可能である。

)などが有するすべての端子について、その接続先を特定しなくても、当業者であれば、

発明の一態様を構成することは可能な場合がある。特に、端子の接続先が複数の場合には

、その端子の接続先を特定の箇所に限定する必要はない。したがって、能動素子(トラン

ジスタ、ダイオードなど)、受動素子(容量素子、抵抗素子など)などが有する一部の端

子についてのみ、その接続先を特定することによって、発明の一態様を構成することが可

能な場合がある。

することが可能な場合がある。または、ある回路について、少なくとも機能を特定すれば

、当業者であれば、発明を特定することが可能な場合がある。したがって、ある回路につ

いて、機能を特定しなくても、接続先を特定すれば、発明の一態様として開示されている

ものであり、発明の一態様を構成することが可能である。または、ある回路について、接

続先を特定しなくても、機能を特定すれば、発明の一態様として開示されているものであ

り、発明の一態様を構成することが可能である。

本実施の形態では、トランジスタを具備する半導体装置の一例に関して説明する。

が導通(On(オン))している期間に当該トランジスタを流れる電流の方向を入れ替え

る(反転させる)構成となっている。つまり、トランジスタが導通している期間に当該ト

ランジスタの第1の端子と第2の端子(ソース又はドレインとなる端子)に加わる電圧の

大小関係を任意の期間毎に入れ替えることにより、ソースとドレインを任意の期間毎に切

り替える構成とする。以下に、具体的な回路構成及び動作について図面を参照して説明す

る。

タ111と、配線102と配線103の間に設けられたトランジスタ112とを少なくと

も有している(図1(A)参照)。

方が配線103に電気的に接続されている。トランジスタ111がオンすることにより、

配線101に入力される信号(IN1)が配線103に供給される。トランジスタ112

は、ソース又はドレインの一方が配線102に電気的に接続され、他方が配線103に電

気的に接続されている。トランジスタ112がオンすることにより、配線102に入力さ

れる信号(IN2)が配線103に供給される。

、又は配線102に入力される信号(IN2)に対応する第2の信号が供給される。

ロウ(L)レベル信号)を用い、トランジスタ111及びトランジスタ112のオン又は

オフを制御することにより、配線103にHレベル信号又はLレベル信号を選択的に出力

できる。また、図2(A)に示すように、配線103にトランジスタのゲートを接続し、

配線103からHレベル信号又はLレベル信号を出力することにより、当該トランジスタ

のオン又はオフを制御することができる。

場合を示しているが、Pチャネル型で設けてもよい。又は、トランジスタ111とトラン

ジスタ112の極性が異なっていてもよいし、各トランジスタをCMOSで設けてもよい

。また、トランジスタ111は配線101と配線103との間のスイッチとして機能し、

トランジスタ112は配線102と配線103との間のスイッチとして機能し得る(図1

(B)参照)。

2の少なくとも一方について、当該トランジスタを流れる電流の方向を入れ替える構成と

する。つまり、トランジスタ111とトランジスタ112の少なくとも一方について、ト

ランジスタのソース又はドレインとなる端子である第1の端子と第2の端子に加わる電圧

の大小関係を任意の期間毎に入れ替える(ソースとドレインを入れ替える)構成とする。

トランジスタを流れる電流の方向を入れ替える構成とすることが好ましい。例えば、図1

(A)において、トランジスタ112が長い期間オン状態を維持する場合には、少なくと

も当該トランジスタ112を流れる電流の方向(A方向又はB方向)を入れ替える構成と

する。つまり、トランジスタ112の第1の端子と第2の端子に加わる電圧の大小関係を

期間毎に入れ替える(ソースとドレインを入れ替える)構成とする。

的に接続されている構成(例えば、配線103がゲート線として機能する場合)について

説明する(図2(A)参照)。また、配線102に入力する信号として、電位が所定の期

間毎に変化する信号を用いることによって、トランジスタ112がオンしている期間に当

該トランジスタ112を流れる電流の方向を入れ替える場合について説明する。

入力される信号(IN1)、配線102に入力される信号(IN2)、トランジスタ11

1のゲートに入力される信号(IN3)、トランジスタ112のゲートに入力される信号

(IN4)を示している。もちろん、これらの信号(IN1〜IN4)は一例であり、図

2に示した信号に限られない。

させる信号(IN3)が入力される。その結果、トランジスタ111がオン状態となり、

配線101に入力された信号(IN1)に対応する第1の信号(ここでは、Hレベル信号

(トランジスタ121をオンさせる選択信号))がトランジスタ111を介して配線10

3に供給される。そして、配線103に接続されているトランジスタ121のゲートに選

択信号が入力され、トランジスタ121がオンする(図3(A)参照)。

Hの場合、トランジスタ111のしきい値をVthとすると、配線103に出力される信

号の電位はVH−Vthとなる。配線103に出力される信号の電位をVHとするために

は、期間T1においてトランジスタ111のゲートを浮遊状態とし、ブートストラップ動

作を行うことによって、トランジスタ111のゲートに入力する信号(IN3)の電位を

VH+Vthより大きくすればよい。もちろん、配線103に出力される信号の電位をV

Hとするために、トランジスタ111のゲートに入力する信号(IN3)の電位をあらか

じめVH+Vthより大きくなるように設定(例えば、VH+Vth+α)してもよい。

し、これに限定されず、配線103に選択信号が出力されるのであれば、トランジスタ1

12がオンとなっていてもよい。この場合、配線102に入力される信号(IN2)の電

位がVHとなっていることが好ましい。

の場合には、配線101に入力される信号は、Lレベル信号になっていることが望ましい

。

させる信号(IN4)が入力される。このとき、トランジスタ112において、配線10

2に接続されている端子の電位(この場合、VLL)は配線103に接続されている端子

の電位(この場合、VH)より低くなるため、配線102に接続されている端子がソース

となり、配線103に接続されている端子がドレインとなる。その結果、トランジスタ1

12において、ゲートとソース間の電位VgsB=VH−VLLがトランジスタ112の

しきい値より大きくなるため、トランジスタ112がオン状態となり、配線102に入力

された信号(IN2)に対応する第2の信号(ここでは、トランジスタ121をオフさせ

る非選択信号、電位VLL)がトランジスタ112を介して配線103に供給される。

れ、トランジスタ121がオフする。なお、トランジスタ111は、期間T2において、

オフ状態となっている。ただし、これに限定されず、IN1がVLLになるならトランジ

スタ111がオン状態となっていてもよい。

端子の電位が配線103に接続されている端子の電位より低くなることにより、配線10

2に接続されている端子がソースとなり、配線103に接続されている端子がドレインと

なり、電流はドレインからソース(図2(A)中B方向)に流れる(図3(B)参照)。

れる信号(IN2)の電位がVLLからVLH(VLL<VLH)に変化する。このとき

、トランジスタ112において、配線102に接続されている端子の電位(この場合、V

LH)が配線103に接続されている端子の電位(この場合、VLL)より高くなるため

、配線102に接続されている端子がドレインとなり、配線103に接続されている端子

がソースとなる。トランジスタ112において、ゲートとソース間の電位VgsA=VH

−VLHがトランジスタ112のしきい値より大きい状態を維持するため、トランジスタ

112がオン状態を維持し、配線102に入力された信号(IN2)に対応する第2の信

号(ここでは、トランジスタ121をオフさせる非選択信号、電位VLH)がトランジス

タ112を介して配線103に供給される。

されるため、トランジスタ121がオフ状態を維持する。ここで、電位VLHと電位VL

Lは互いに異なり、且つトランジスタ121のゲートに印加されても当該トランジスタ1

21をオンさせない電位である。例えば、トランジスタ121のソース又はドレインにお

いて最も低い電位をVmin、最も高い電圧をVmax、トランジスタ121のしきい値

電圧をVthとしたとき、VLH−Vmin<Vth、VH−Vmax>Vthを満たす

関係とすればよい。

端子の電位が配線103に接続されている端子の電位より高くなることにより、配線10

2に接続されている端子がドレインとなり、配線103に接続されている端子がソースと

なり、電流はドレインからソース(図2(A)中A方向)に流れる(図3(C)参照)。

、配線103には所定の期間毎に電位VLLと電位VLHが切り替わる第2の信号が供給

され(ここでは、電位がVLHである信号、偶数の期間に電位がVLLである信号が供給

される)、トランジスタ121はオフ状態を維持する。また、トランジスタ112は、オ

ン状態を維持するが、電流の方向が入れ替わる構成となる(図3(D)(E)参照)。

期間毎に電位が変化するLレベル信号(非選択信号)を入力することによって、トランジ

スタ112においてソース又はドレインとなる2つの端子の電圧の大小関係を入れ替え、

トランジスタ112を流れる電流の方向を入れ替えている。

入れ替える)構成とすることにより、トランジスタ121を安定してオフさせるためにト

ランジスタ112を長い期間オン状態とする場合であっても、トランジスタ112のチャ

ネル部(ドレイン端)での電界の集中を緩和し、トランジスタ112の劣化を低減するこ

とができる。その結果、トランジスタの劣化に伴う回路の動作不良を抑制し、信頼性を向

上することができる。

、ナノクリスタル)をチャネル形成領域とする場合には、回路の動作期間において長い期

間オン状態を維持するトランジスタを図2、図3で示したように動作させることはトラン

ジスタの劣化の低減に有効となる。なお、アモルファスシリコンや微結晶シリコン以外で

あっても、例えば、ポリシリコン、酸化物半導体(ZnO、IGZO(InGaZnO)

等)、有機半導体、カーボンナノチューブ等をチャネル形成領域とする場合であってもト

ランジスタの劣化の低減に有効となる。

Lからなる第2の電位(VLH>VLL)が任意の期間毎に切り替わる信号を用いた場合

を示したが、配線102に入力する信号は、互いに電位が異なる2種類の信号に限られな

い。トランジスタ121をオンさせない電位であれば、互いに異なる3種類以上の電位を

組み合わせてトランジスタ112に入力してもよい。

らなる第2の電位を同じ期間交互に繰り返し入力する場合を示したが、第1の電位と第2

の電位を入力する期間は任意に設定することができる。また、配線102に電位がVLH

からなる第1の電位と、電位がVLLからなる第2の電位を同じ期間交互に繰り返し入力

する場合であっても、その周期は任意に設定することができる。

、上記図2では配線101に一定電位の信号を入力する場合(例えば、配線101を電源

線に接続する場合)を示したが、配線101に他の信号(例えば、クロック信号)を入力

してもよい。また、上記図2では期間T2〜期間Tnにおいて、トランジスタ111がオ

フ状態となる場合を示したが、配線101からLレベル信号が供給される場合には、トラ

ンジスタ111をオン状態とする期間を設けてもよい。

をVLLとした場合を示したが、トランジスタ112がオフとなるのであればこれに限ら

れない。例えば、トランジスタ112のゲートに入力する信号(IN4)の電位としてV

LLより低い電位としてもよい。この場合、トランジスタ112がオフの際に、Vgsを

0Vより小さくすることができるため、当該トランジスタ112の劣化を効果的に抑制す

ることができる。

持する場合を示したが、これに限られない。例えば、期間T2〜期間Tnのある期間にお

いてトランジスタ112をオフとする構成としてもよい。つまり、トランジスタ112が

オンしている期間とオフしている期間を組み合わせ、さらに、オンしている期間では当該

トランジスタ112を流れる電流の向きを入れ替える構成とする。この場合、トランジス

タ112の劣化をより効果的に抑制することができる。なお、トランジスタ112をオフ

する期間において配線102と配線103の電位は等しくてもよいし、異なっていてもよ

い。また、トランジスタ112をオフとする期間は特に限定されないが、制御のしやすさ

からトランジスタ112をオンする期間とオフする期間をほぼ等しくすることが好ましい

。

を一時的に浮遊状態とすることによって、トランジスタ111のゲートとソース間の容量

結合を利用するブートストラップ動作を適用した回路構成とすることができる。この場合

、図1(C)に示すように、トランジスタ111のゲートと、ソース又はドレインの一方

の間に容量素子115を設けた構成としてもよい。容量素子115を設けることにより、

安定してブートストラップ動作を行うことができる。なお、トランジスタ111のゲート

と、ソース又はドレインとの間に十分な寄生容量が生じる場合には、容量素子115を設

けずにブートストラップ動作を行うことも可能である。

の方向を入れ替える構成を例に挙げたが、トランジスタ111がLレベル信号を出力し続

ける場合には、トランジスタ111を流れる電流の方向を入れ替える構成とすればよい。

この場合、配線101に入力する信号(IN1)として、電位がVLHからなる第1の電

位と、電位がVLLからなる第2の電位(VLH>VLL)が任意の期間毎に切り替わる

信号を用いることができる。

合には、当該トランジスタ112(又はトランジスタ111)を流れる電流の方向を入れ

替える構成とすればよい。この場合、配線102(又は配線101)に入力する信号とし

て、電位がVHHからなる第1の電位と、電位がVHLからなる第2の電位(VHH>V

HL)が任意の期間に切り替わる信号を用いることができる。

替わる構成としてもよい。例えば、トランジスタ111を介して配線101から配線10

3にHレベル信号が供給され、トランジスタ112を介して配線102から配線103に

Lレベル信号が供給される場合、配線101に入力する信号(IN1)として電位がVH

Hからなる第1の電位と、電位がVHLからなる第2の電位が任意の期間毎に切り替わる

信号を用い、配線102に入力する信号(IN2)として電位がVLHからなる第1の電

位と、電位がVLLからなる第2の電位が任意の期間毎に切り替わる信号を用いることが

できる。

21をNチャネル型のトランジスタで設けた場合を示したが、Pチャネル型のトランジス

タで設けてもよい(図4(A)〜(F)参照)。Pチャネル型のトランジスタで設けた場

合には、配線102に入力する信号として、電位がVHHからなる第1の電位と、電位が

VHLからなる第2の電位(VHH>VHL)が任意の期間に切り替わる信号を用いるこ

とによって、トランジスタ112を流れる電流の方向が入れ替わるように動作させること

ができる。その結果、トランジスタ112の劣化を低減し回路の動作不良を抑制すること

ができる。なお、図4では、トランジスタ111、トランジスタ112及びトランジスタ

121をPチャネル型のトランジスタで設けた場合を示したが、トランジスタ121をN

チャネル型のトランジスタで設けてもよい。

た構成を含む)と適宜組み合わせて実施することができる。

本実施の形態では、上記実施の形態と異なる構成を有する半導体装置の一例に関し図面を

参照して説明する。

タ111と、配線102と配線103の間に互いに並列して設けられた複数のトランジス

タ112a、112bとを少なくとも具備している(図5(A)参照)。つまり、図5(

A)に示す構成は、図1で示した構成にトランジスタ112bを追加した構成となってい

る(図5のトランジスタ112aが図1のトランジスタ112に対応している)。なお、

図5(A)では、2個のトランジスタ(トランジスタ112a、112b)を並列して設

けた場合を示したが、トランジスタの数は3個以上設けてもよい。

接続され、他方が配線103に接続されており、互いに並列に設けられている。そのため

、トランジスタ112a、112bの少なくとも一方がオンすることにより、配線102

に入力される信号(IN2)が配線103に供給される。

線102に入力される信号(IN2)に対応する第2の信号が供給される。

型で設けた場合を示しているが、Pチャネル型で設けてもよいし、CMOSで設けてもよ

い。また、トランジスタ111は、配線101と配線103との間のスイッチとして機能

し、トランジスタ112a、112bは配線102と配線103との間のスイッチとして

機能する(図5(B)参照)。

2a、112b)のオンとオフを交互に行う。そして、複数のトランジスタを流れる電流

の方向を入れ替える構成(トランジスタのソース又はドレインとなる端子に加わる電圧の

大小関係を期間毎に入れ替える(ソースとドレインを入れ替える)構成)とする。つまり

、並列に設けられた複数のトランジスタのオンとオフとを制御する。そして、複数のトラ

ンジスタを流れる電流の方向を制御することにより、トランジスタのチャネル部(ドレイ

ン端)での電界の集中を緩和し劣化を低減する。

図6(A)〜(F)はそれぞれ、配線103から出力される信号(Out)、配線101

に入力される信号(IN1)、配線102に入力される信号(IN2)、トランジスタ1

11のゲートに入力される信号(IN3)、トランジスタ112aのゲートに入力される

信号(IN4)、トランジスタ112bのゲートに入力される信号(IN5)を示してい

る。図6では、配線102に入力される信号(IN2)の周期がトランジスタ112a、

112bのゲートに入力される信号(IN4、IN5)の1/2である場合を示している

。もちろん、入力される信号(IN1〜IN5)は一例であり、これらに限定されるもの

でない。

を示しており、A1、A2、B1、B2はそれぞれ図5に示した方向に対応している。ま

た、トランジスタがオフして電流が流れない期間は×で示している。

させる信号(IN3)が入力される。その結果、トランジスタ111がオン状態となり、

配線101に入力された信号(IN1)に対応する第1の信号(ここでは、Hレベル信号

(選択信号))がトランジスタ111を介して配線103に供給される。配線103にト

ランジスタ121のゲートが接続されている場合(図5(C)参照)には、当該配線10

3に接続されているトランジスタ121のゲートに選択信号が入力され、トランジスタ1

21がオンする。

Hの場合、トランジスタ111のしきい値をVthとすると、配線103に出力される信

号の電位はVH−Vthとなる。この場合、配線103に出力される信号の電位をVHと

するためには、期間T1においてトランジスタ111のゲートを浮遊状態とし、ブートス

トラップ動作を行う構成とすればよい。もちろん、配線103に出力される信号の電位を

VHとするために、トランジスタ111のゲートに入力する信号(IN3)の電位をあら

かじめVH+Vth以上に設定してもよい。

但し、これに限定されず、配線103に選択信号が出力されるのであれば、トランジスタ

112a、112bがオンとなっていてもよい。この場合、配線102に入力される信号

(IN2)の電位がVHとなっていることが好ましい。

オンさせる信号(IN4)が入力される。このとき、トランジスタ112aにおいて、配

線102に接続されている端子の電位(この場合、VLL)が配線103に接続されてい

る端子の電位(この場合、VH)より低くなるため、配線102に接続されている端子が

ソースとなり、配線103に接続されている端子がドレインとなる。その結果、トランジ

スタ112aにおいて、ゲートとソース間の電位VgsB=VH−VLLがトランジスタ

112aのしきい値より大きくなるため、トランジスタ112aがオン状態となり、配線

102に入力された信号(IN2)に対応する電位がVLLの第2の信号(非選択信号)

がトランジスタ112aを介して配線103に供給される。

接続されているトランジスタ121のゲートに非選択信号が入力され、トランジスタ12

1がオフする。

(ここでは、VLLからVLHに変化)する。このとき、トランジスタ112aにおいて

、配線102に接続されている端子の電位(この場合、VLH)が配線103に接続され

ている端子の電位(この場合、VLL)より高くなるため、配線102に接続されている

端子がドレインとなり、配線103に接続されている端子がソースとなる。その結果、ト

ランジスタ112aにおいて、ゲートとソース間の電位VgsA=VH−VLLがトラン

ジスタ112aのしきい値より大きくなるため、トランジスタ112aがオン状態を維持

し、配線102に入力された信号(IN2)に対応する電位がVLHの第2の信号(非選

択信号)がトランジスタ112aを介して配線103に供給される。

接続されているトランジスタ121のゲートに非選択信号が入力されるため、トランジス

タ121はオフを維持する。

れている端子の電位が配線103に接続されている端子の電位より低くなることにより、

配線102に接続されている端子がソースとなり、配線103に接続されている端子がド

レインとなり、電流はドレインからソース(図5中B1方向)に流れる。一方、期間T2

の後半では、トランジスタ112aにおいて、配線102に接続されている端子の電位が

配線103に接続されている端子の電位より高くなることにより、配線102に接続され

ている端子がドレインとなり、配線103に接続されている端子がソースとなり、電流は

ドレインからソース(図5中A1方向)に流れる。

トに当該トランジスタ112bをオンさせる信号(IN5)が入力される。このとき、ト

ランジスタ112bにおいて、配線102に接続されている端子の電位(この場合、VL

L)が配線103に接続されている端子の電位(この場合、VLH)より低くなるため、

配線102に接続されている端子がソースとなり、配線103に接続されている端子がド

レインとなる。その結果、トランジスタ112bにおいて、ゲートとソース間の電位Vg

sB=VH−VLLがトランジスタ112bのしきい値より大きくなるため、トランジス

タ112bがオン状態となり、配線102に入力された信号(IN2)に対応する電位V

LLの第2の信号(非選択信号)がトランジスタ112bを介して配線103に供給され

る。

接続されているトランジスタ121のゲートに非選択信号が入力されるため、トランジス

タ121はオフを維持する。

(ここでは、VLLからVLHに変化)する。このとき、トランジスタ112bにおいて

、配線102に接続されている端子の電位(この場合、VLH)が配線103に接続され

ている端子の電位(この場合、VLL)より高くなるため、配線102に接続されている

端子がドレインとなり、配線103に接続されている端子がソースとなる。その結果、ト

ランジスタ112bにおいて、ゲートとソース間の電位VgsA=VH−VLLがトラン

ジスタ112bのしきい値より大きくなるため、トランジスタ112bがオン状態を維持

し、配線102に入力された信号(IN2)に対応する電位VLHの第2の信号(非選択

信号)がトランジスタ112bを介して配線103に供給される。

接続されているトランジスタ121のゲートに非選択信号が入力されるため、トランジス

タ121はオフを維持する。

れている端子の電位が配線103に接続されている端子の電位より低くなることにより、

配線102に接続されている端子がソースとなり、配線103に接続されている端子がド

レインとなり、電流はドレインからソース(図5中B2方向)に流れる。一方、期間T3

の後半では、トランジスタ112bにおいて、配線102に接続されている端子の電位が

配線103に接続されている端子の電位より高くなることにより、配線102に接続され

ている端子がドレインとなり、配線103に接続されている端子がソースとなり、電流は

ドレインからソース(図5中A2方向)に流れる。

うち前半の期間に配線102から電位がVLLである第2の信号が配線103に供給され

、オンしている期間のうち後半の期間に配線102から電位がVLHである第2の信号が

配線103に供給される。そのため、トランジスタ112aがオンしている期間のうち前

半の期間は、配線102に接続されている端子がソースとなり、配線103に接続されて

いる端子がドレインとなり、電流はドレインからソース(図5中B1方向)に流れる。ま

た、トランジスタ112aがオンしている期間のうち後半の期間は、配線102に接続さ

れている端子がドレインとなり、配線103に接続されている端子がソースとなり、電流

はドレインからソース(図5中A1方向)に流れる。

期間)のうち後半の期間は、配線102の電位がVLHとなるため、トランジスタ112

bにおいてゲートとソース間電圧(Vgs)が負(Vgs<0V)となる。このように、

トランジスタ112bにおいて、ゲートとソース間電圧(Vgs)が負(Vgs<0V)

となる期間を設けることにより、トランジスタの劣化を効果的に抑制することができる。

うち前半の期間に配線102から電位がVLLである第2の信号が配線103に供給され

、オンしている期間のうち後半の期間に配線102から電位がVLHである第2の信号が

配線103に供給される。そのため、トランジスタ112bがオンしている期間のうち前

半の期間は、配線102に接続されている端子がソースとなり、配線103に接続されて

いる端子がドレインとなり、電流はドレインからソース(図5中B2方向)に流れる。ま

た、トランジスタ112bがオンしている期間のうち後半の期間は、配線102に接続さ

れている端子がドレインとなり、配線103に接続されている端子がソースとなり、電流

はドレインからソース(図5中A2方向)に流れる。

期間)のうち後半の期間は、配線102の電位がVLHとなるため、トランジスタ112

aにおいてゲートとソース間電圧(Vgs)が負(Vgs<0V)となる。このように、

トランジスタ112aにおいて、ゲートとソース間電圧(Vgs)が負(Vgs<0V)

となる期間を設けることにより、トランジスタの劣化を効果的に抑制することができる。

スタがオンしている期間に当該トランジスタを流れる電流の方向を入れ替える(トランジ

スタの第1の端子と第2の端子(ソース又はドレインとなる端子)に加わる電圧の大小関

係を期間毎に入れ替える(ソースとドレインを入れ替える))構成とすることにより、ト

ランジスタのチャネル部(ドレイン端)での電界の集中を緩和し劣化を低減することがで

きる。その結果、トランジスタの劣化に伴う回路の動作不良を抑制し、信頼性を向上する

ことができる。

る期間とオフする期間をほぼ等しくすることが制御のしやすさの点から好ましい。この場

合、トランジスタ112a、トランジスタ112bがオンしている期間のうち半分の期間

毎にトランジスタを流れる電流の向きを変えることができる。

ジスタ112b)が交互にオンとオフする場合を示したが、トランジスタ112aとトラ

ンジスタ112bのオンとオフの期間が一部重なるように動作させてもよい。つまり、ト

ランジスタ112aとトランジスタ112bの双方がオンしている期間や双方がオフして

いる期間を設けてもよい。

、112bのゲートに入力される信号(IN4、IN5)の1/2である場合を示したが

これに限られず、1/2より小さくてもよいし大きくてもよい。また、図6において、配

線102に入力される信号(IN2)の位相をずらしてもよく、例えば、配線102に入

力される信号(IN2)を1/2又は1/4周期だけ位相をずらしてもよい。

はトランジスタ112a、112bのゲートに入力される信号(IN4、IN5)の周期

より小さい場合に限られない。以下に、配線102に入力される信号(IN2)の周期が

トランジスタ112a、112bのゲートに入力される信号(IN4、IN5)の周期と

同じ場合、大きい場合について図面を参照して説明する。

以下の説明において、図7、図8の(A)〜(F)はそれぞれ、配線103から出力され

る信号(Out)、配線101に入力される信号(IN1)、配線102に入力される信

号(IN2)、トランジスタ111のゲートに入力される信号(IN3)、トランジスタ

112aのゲートに入力される信号(IN4)、トランジスタ112bのゲートに入力さ

れる信号(IN5)を示している。図7、図8では、配線102に入力される信号(IN

2)の周期がトランジスタ112a、112bのゲートに入力される信号(IN4、IN

5)より大きい場合(IN2の周期がIN4、IN5の周期の2倍の場合)を示している

。もちろん、入力される信号(IN1〜IN5)は一例であり、これらに限定されるもの

でない。

れる向きを示しており、A1、A2、B1、B2はそれぞれ図5に示した方向に対応して

いる。また、トランジスタがオフして電流が流れない期間は×で示している。また、トラ

ンジスタがオンしているが電流が流れない期間は−で示している。

る信号(IN3)が入力される。ここでは、上記図6の期間T1と同様に動作する。

オンさせる信号(IN4)が入力される。このとき、トランジスタ112aにおいて配線

102に接続されている端子の電位(この場合、VLL)は配線103に接続されている

端子の電位(この場合、VH)より低くなるため、配線102に接続されている端子がソ

ースとなり、配線103に接続されている端子がドレインとなる。その結果、トランジス

タ112aにおいて、ゲートとソース間の電位VgsB=VH−VLLがトランジスタ1

12aのしきい値より大きくなるため、トランジスタ112aがオン状態となり、配線1

02に入力された信号(IN2)に対応する電位がVLLの第2の信号(非選択信号)が

トランジスタ112aを介して配線103に供給される。

、当該配線103に接続されているトランジスタ121のゲートに非選択信号が入力され

、トランジスタ121がオフする。

る端子の電位が配線103に接続されている端子の電位より低くなることにより、配線1

02に接続されている端子がソースとなり、配線103に接続されている端子がドレイン

となり、電流はドレインからソース(図5中B1方向)に流れる。

オフさせる信号(IN4)が入力され、トランジスタ112bのゲートに当該トランジス

タ112bをオンさせる信号(IN5)が入力され、トランジスタ112aとトランジス

タ112bのオンとオフが入れ替わる。このとき、トランジスタ112bにおいて、配線

102に接続されている端子の電位(この場合、VLH)が配線103に接続されている

端子の電位(この場合、VLL)より高くなるため、配線102に接続されている端子が

ドレインとなり、配線103に接続されている端子がソースとなる。その結果、トランジ

スタ112bにおいて、ゲートとソース間の電位VgsA=VH−VLLがトランジスタ

112bのしきい値より大きくなるため、トランジスタ112bがオン状態となり、配線

102に入力された信号(IN2)に対応する電位がVLHの第2の信号(非選択信号)

がトランジスタ112bを介して配線103に供給される。

る端子の電位が配線102に接続されている端子の電位より低くなることにより、配線1

03に接続されている端子がソースとなり、配線102に接続されている端子がドレイン

となり、電流はドレインからソース(図5中A2方向)に流れる。

が負(Vgs<0V)となる。このように、トランジスタ112aにおいて、ゲートとソ

ース間電圧(Vgs)が負(Vgs<0V)となる期間を設けることにより、Vgs=0

Vとなる場合と比較してトランジスタの劣化を効果的に抑制することができる。

オンさせる信号(IN4)が入力され、トランジスタ112bのゲートに当該トランジス

タ112bをオフさせる信号(IN5)が入力され、トランジスタ112aとトランジス

タ112bのオンとオフが入れ替わる。また、配線102の電位がVLHを保持するため

、配線103の電位もVLHを維持する。従って、トランジスタ112aにおいては、配

線102に接続されている端子の電位と配線103に接続されている端子の電位とが等し

くなるため、トランジスタ112aには電流は流れない。

オフさせる信号(IN4)が入力され、トランジスタ112bのゲートに当該トランジス

タ112bをオンさせる信号(IN5)が入力され、トランジスタ112aとトランジス

タ112bのオンとオフが入れ替わる。このとき、トランジスタ112bにおいて、配線

102に接続されている端子の電位(この場合、VLL)が配線103に接続されている

端子の電位(この場合、VLH)より低くなるため、配線102に接続されている端子が

ソースとなり、配線103に接続されている端子がドレインとなる。その結果、トランジ

スタ112bにおいて、ゲートとソース間の電位VgsB=VH−VLLがトランジスタ

112bのしきい値より大きくなるため、トランジスタ112bがオン状態となり、配線

102に入力された信号(IN2)に対応する電位がVLLの第2の信号(非選択信号)

がトランジスタ112bを介して配線103に供給される。

る端子の電位が配線103に接続されている端子の電位より低くなることにより、配線1

02に接続されている端子がソースとなり、配線103に接続されている端子がドレイン

となり、電流はドレインからソース(図5中B2方向)に流れる。

ジスタ111はオフ状態を維持し、トランジスタ112a、112bは交互にオンとなり

、配線103には電位VLHと、電位VLLが任意の期間毎に切り替わる信号が入力され

る。そのため、配線103にトランジスタ121のゲートが接続されている場合には、当

該トランジスタ121が安定してオフ状態を維持する。

る(ソースとドレインを入れ替える)ことができない。従って、ある期間毎に、配線10

2に入力される信号(IN2)の周期をずらし、トランジスタ112aを流れる電流の方

向を入れ替える構成とすることが好ましい。

2aを流れる電流の方向を入れ替える構成とした場合を示している。図8に示した動作で

は、トランジスタ112bを流れる電流の方向を入れ替える(ソースとドレインを入れ替

える)ことができない。従って、回路の動作時において、図7に示した動作と図8に示し

た動作を期間毎に切り替えることによって、配線102に入力される信号(IN2)の周

期をトランジスタ112a、112bのゲートに入力される信号(IN4、IN5)より

大きくした場合であってもトランジスタ112a及びトランジスタ112bの劣化を低減

することができる。

ジスタ112b)が交互にオンとオフする場合を示したが、トランジスタ112aとトラ

ンジスタ112bのオンとオフの期間が一部重なるように動作させてもよい。つまり、ト

ランジスタ112aとトランジスタ112bの双方がオンしている期間や双方がオフして

いる期間を設けてもよい。

12a、112bのゲートに入力される信号(IN4、IN5)の2倍である場合を示し

たがこれに限られず、2倍より小さくてもよいし大きくてもよい。

以下の説明において、図9、図10の(A)〜(F)はそれぞれ、配線103から出力さ

れる信号(Out)、配線101に入力される信号(IN1)、配線102に入力される

信号(IN2)、トランジスタ111のゲートに入力される信号(IN3)、トランジス

タ112aのゲートに入力される信号(IN4)、トランジスタ112bのゲートに入力

される信号(IN5)を示している。図9、図10では、配線102に入力される信号(

IN2)の周期がトランジスタ112a、112bのゲートに入力される信号(IN4、

IN5)の周期と等しい場合を示している。もちろん、入力される信号(IN1〜IN5

)は一例であり、これらに限定されるものでない。

流れる向きを示しており、A1、A2、B1、B2はそれぞれ図5に示した方向に対応し

ている。また、トランジスタがオフして電流が流れない期間は×で示している。また、ト

ランジスタがオンしているが電流が流れない期間は−で示している。

により、トランジスタを動作させる。

ら電位がVLLである第2の信号が配線103に供給され、トランジスタ112bがオン

のときに配線102から電位がVLHである第2の信号が配線103に供給される(図9

参照)。

スタ112aにおいて配線102に接続されている端子がソースとなり、配線103に接

続されている端子がドレインとなり、電流はドレインからソース(図5中B1方向)に流

れる。また、トランジスタ112bがオンのとき、トランジスタ112bにおいて配線1

03に接続されている端子がソースとなり、配線102に接続されている端子がドレイン

となり、電流はドレインからソース(図5中A2方向)に流れる。また、トランジスタ1

12aがオフの場合に、当該トランジスタ112aにおいてゲートとソース間電圧(Vg

s)を負(Vgs<0V)とすることができるため、Vgs=0Vとなる場合と比較して

トランジスタの劣化を効果的に抑制することができる。

、配線102に接続されている端子の電位と配線103に接続されている端子の電位が等

しくなった場合には、ソースとドレインの区別がなくなる。

電位がVLHである第2の信号が配線103に供給され、トランジスタ112bがオンの

ときに配線102から電位がVLLである第2の信号が配線103に供給される(図10

参照)。

スタ112aにおいて配線102に接続されている端子がドレインとなり、配線103に

接続されている端子がソースとなり、電流はドレインからソース(図5中A1方向)に流

れる。また、トランジスタ112bがオンのとき、トランジスタ112bにおいて配線1

03に接続されている端子がドレインとなり、配線102に接続されている端子がソース

となり、電流はドレインからソース(図5中B2方向)に流れる。また、トランジスタ1

12bがオフの場合に、当該トランジスタ112bにおいてゲートとソース間電圧(Vg

s)を負(Vgs<0V)とすることができるため、Vgs=0Vとなる場合と比較して

トランジスタの劣化を効果的に抑制することができる。

ば、反転させ)、図9の動作と図10の動作を組み合わせて行うことにより(例えば、図

11参照)、トランジスタ112a、トランジスタ112bをそれぞれ流れる電流の方向

を入れ替える(トランジスタのソース又はドレインとなる端子に加わる電圧の大小関係を

期間毎に入れ替える(ソースとドレインを入れ替える))構成とすることができる。その

結果、トランジスタ112a及びトランジスタ112bのチャネル部(ドレイン端)での

電界の集中を緩和し劣化を低減することができる。さらに、並列に設けられた複数のトラ

ンジスタ(トランジスタ112a、トランジスタ112b)のオンとオフを交互に行うこ

とによって、トランジスタの劣化を抑制することができる。

イバとして適用する場合、1フレーム期間毎に図9に示す動作と図10に示す動作を切り

替えて行うことができる。

a、112bのゲートに入力される信号(IN4、IN5)の立ち上がり及び立ち下がり

を同じタイミングで行う場合を示しているが、これに限られず、例えば、配線102に入

力される信号(IN2)の周期を1/4周期だけ位相をずらして動作させてもよい。

に行うと共に、当該複数のトランジスタを流れる電流の方向を入れ替える(トランジスタ

のソース又はドレインとなる端子に加わる電圧の大小関係を期間毎に入れ替える(ソース

とドレインを入れ替える))構成とすることによって、トランジスタのチャネル部(ドレ

イン端)での電界の集中を緩和し、トランジスタの劣化を効果的に抑制することが可能と

なる。

12b及びトランジスタ121をNチャネル型のトランジスタで設けた場合を示したが、

Pチャネル型のトランジスタで設けてもよい。この場合も、トランジスタ112a、11

2bを流れる電流の方向が入れ替わるように動作させることにより、トランジスタの劣化

を低減し回路の動作不良を抑制することができる。

が、Hレベル信号を出力し続ける場合には、配線101と配線103の間に互いに並列し

て設けられた複数のトランジスタを設け、配線101に入力する信号として、電位がVL

Hからなる第1の電位と、電位がVLLからなる第2の電位が任意の期間毎に切り替わる

信号を用いる構成とすることができる。

た構成を含む)と適宜組み合わせて実施することができる。

本実施の形態では、上記実施の形態と異なる構成を有する半導体装置の一例に関し図面を

参照して説明する。

タ111と、配線102と配線103の間に設けられたトランジスタ112と、配線10

4と配線103の間に設けられたトランジスタ114とを少なくとも具備している(図1

2(A)参照)。

方が配線103に接続されている。つまり、図12に示す構成は、図5で示した構成に配

線104を追加し、更に図5のトランジスタ112bのソース又はドレインの一方を配線

102ではなく配線104に電気的に接続した構成となっている。そのため、トランジス

タ114がオンすることにより、配線104に入力される信号(IN6)が配線103に

供給される。

号、配線102に入力される信号(IN2)に対応する第2の信号、又は配線104に入

力される信号(IN6)に対応する第3の信号が供給される。

とトランジスタ114に同時に異なる信号を供給することができる。その結果、信号の周

波数を低減させ、消費電力を下げることが可能となる。

Nチャネル型で設けた場合を示しているが、Pチャネル型で設けてもよいし、CMOSで

設けてもよい。また、トランジスタ111は、配線101と配線103との間のスイッチ

として機能し、トランジスタ112は配線102と配線103との間のスイッチとして機

能し、トランジスタ114は配線104と配線103との間のスイッチとして機能する(

図12(B)参照)。

において、ソース又はドレインの一方がそれぞれ配線103に接続され、他方がそれぞれ

異なる配線に接続された複数のトランジスタ(図12では、トランジスタ112、114

)のオンとオフを交互に行うと共に、当該複数のトランジスタを流れる電流の方向を入れ

替える(トランジスタのソース又はドレインとなる端子に加わる電圧の大小関係を期間毎

に入れ替える(ソースとドレインを入れ替える))構成とする。つまり、複数のトランジ

スタのオンとオフとを制御し、且つ流れる電流の方向を制御することにより、トランジス

タのチャネル部(ドレイン端)での電界の集中を緩和し劣化を低減する。

される信号(Out)、配線101に入力される信号(IN1)、配線102に入力され

る信号(IN2)、配線104に入力される信号(IN6)、トランジスタ111のゲー

トに入力される信号(IN3)、トランジスタ112のゲートに入力される信号(IN4

)、トランジスタ114のゲートに入力される信号(IN5)を示している。もちろん、

入力される信号(IN1〜IN6)は一例であり、これらに限定されるものでない。

れる向きを示しており、A1、A2、B1、B2はそれぞれ図12に示した方向に対応し

ている。また、トランジスタがオフして電流が流れない期間は×で示している。また、ト

ランジスタがオンしているが電流が流れない期間は−で示している。

の期間毎に切り替えて印加する。以下の説明では、配線102に電位VLLを印加し、配

線104に電位VLHを印加する期間Tx1〜期間Txnと、配線102にVLHを印加

し、配線104にVLLを印加する期間Ty1〜期間Tynを任意の期間毎に切り替えて

動作させる場合について示す。

101に入力された信号(IN1)に対応する第1の信号(ここでは、Hレベル信号(選

択信号))が配線103に供給される。配線103にトランジスタ121のゲートが接続

されている場合(図12(C)参照)には、当該配線103に接続されているトランジス

タ121のゲートに選択信号が入力され、当該トランジスタ121がオンする。

Tx2、Tx4、Tx6、Tx8、Txn)に配線102から電位がVLLである第2の

信号が配線103に供給され、トランジスタ114がオンのとき(ここでは、期間Tx3

、Tx5、Tx7)に配線104から電位がVLHである第3の信号が配線103に供給

される(図13参照)。配線103にトランジスタ121のゲートが接続されている場合

(図12(C)参照)には、当該トランジスタ121がオフする。

タ112において配線102に接続されている端子がソースとなり、配線103に接続さ

れている端子がドレインとなり、電流はドレインからソース(図12中B1方向)に流れ

る。また、トランジスタ114がオンのとき、トランジスタ114において配線103に

接続されている端子がソースとなり、配線102に接続されている端子がドレインとなり

、電流はドレインからソース(図12中A2方向)に流れる。

期間Ty4、Ty6、Ty8、Tyn)に配線102から電位がVLHである第2の信号

が配線103に供給され、トランジスタ114がオンのとき(ここでは、期間Ty3、T

y5、Ty7)に配線104から電位がVLLである第3の信号が配線103に供給され

る(図14参照)。

タ112において配線102に接続されている端子がドレインとなり、配線103に接続

されている端子がソースとなり、電流はドレインからソース(図12中A1方向)に流れ

る。また、トランジスタ114がオンのとき、トランジスタ114において配線103に

接続されている端子がドレインとなり、配線104に接続されている端子がソースとなり

、電流はドレインからソース(図12中B2方向)に流れる。

)を任意の期間毎に反転させ、図13の動作と図14の動作を組み合わせて行うことによ

り(例えば、図15参照)、トランジスタ112、トランジスタ114をそれぞれ流れる

電流の方向を入れ替える(トランジスタのソース又はドレインとなる端子に加わる電圧の

大小関係を期間毎に入れ替える(ソースとドレインを入れ替える))構成とすることがで

きる。その結果、トランジスタ112及びトランジスタ114のチャネル部(ドレイン端

)での電界の集中を緩和し劣化を低減することができる。さらに、複数のトランジスタ(

トランジスタ112、トランジスタ114)のオンとオフを交互に行うことによって、ト

ランジスタの劣化を抑制することができる。

イバとして適用する場合、1フレーム期間毎に図13に示す動作と図14に示す動作を切

り替えて行うことができる。

えば、非選択信号)を配線103に供給し続ける場合であっても、配線102、配線10

4を定電位とすることができるため、低消費電力化を図ることができる。

た構成を含む)と適宜組み合わせて実施することができる。

本実施の形態では、上記実施の形態で示した構成の使用形態に関し図面を参照して説明す

る。

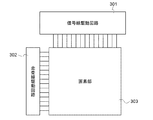

ソースドライバ)及び画素部を有する表示装置において、走査線駆動回路及び/又は信号

線駆動回路に適用することができる(図16参照)。

示す。図17では、複数の画素が設けられた液晶表示装置のゲートドライバに上記実施の

形態1で示した構成を適用する場合を示している。

る配線103a〜103cのいずれかに電気的に接続され、ソース又はドレインの一方が

ソース線として機能する配線141a〜141cのいずれかに電気的に接続され、他方が

画素電極125に電気的に接続されている。また、画素電極125と対向電極126の間

に液晶材料が設けられた構成となっている。なお、図17では、配線101a〜101c

をそれぞれ電気的に独立して設けた構成を示したが、共通化して設けてもよい。

〜101cから選択信号となるHレベル信号を供給し、トランジスタ121をオフさせる

には、トランジスタ112を介して配線102から非選択信号となるLレベル信号を供給

すればよい。

けられたトランジスタ121をオンさせた後、当該トランジスタ121をオフさせる非選

択信号をトランジスタ121のゲートに供給する必要がある。特に、トランジスタ121

を安定してオフ状態とするには、トランジスタ112を介して配線103a〜103cに

非選択信号を所定の期間供給し続けることが有効となる。

ベル信号を入力し、トランジスタ112がオンしている期間において当該トランジスタ1

12を流れる電流の方向を入れ替える構成とすることにより、トランジスタ112の劣化

を低減することができる。その結果、各画素に設けられたトランジスタ121を安定して

オフさせると共に、トランジスタ112の劣化に伴う回路の動作不良を抑制することがで

きる。

する場合には、回路の動作期間において長い期間オン状態を維持するトランジスタの劣化

を低減することは回路の動作不良の抑制に有効となる。

2、画素に設けられたトランジスタ121を全てNチャネル型で設けた場合を示したが、

Pチャネル型で設けてもよいし、CMOSで設けることも可能である。

したがこれに限られず、上記実施の形態2、実施の形態3で示した構成を適用することが

できる。

ンの一方が配線102に電気的に接続され、他方が配線103a(又は配線103b、配

線103c)に接続され且つトランジスタ112と並列するトランジスタ112bを設け

ればよい(図18参照)。

を新たに設け、ソース又はドレインの一方が配線104に電気的に接続され、他方が配線

103a(又は配線103b、配線103c)に接続されるトランジスタ114を設けれ

ばよい(図19参照)。

的に接続させ且つトランジスタ114のソース又はドレインの一方を配線104と電気的

に接続させる場合と、トランジスタ112のソース又はドレインの一方を配線104と電

気的に接続させ且つトランジスタ114のソース又はドレインの一方を配線102と電気

的に接続させる場合を、行方向において交互に設ける構成を示しているが限られない。全

ての行において、トランジスタ112のソース又はドレインの一方を配線102と電気的

に接続させ且つトランジスタ114のソース又はドレインの一方を配線104と電気的に

接続させてもよいし、トランジスタ112のソース又はドレインの一方を配線104と電

気的に接続させ且つトランジスタ114のソース又はドレインの一方を配線102と電気

的に接続させてもよい。

示した構成は、他の表示装置(有機EL表示装置等)のゲートドライバ及び/又はソース

ドライバにも適用可能である。例えば、図20に示すように、画素にトランジスタ121

、トランジスタ128及び発光素子129が設けられた有機EL表示装置のゲートドライ

バとして適用することができる。

103a〜103cのいずれかに電気的に接続され、ソース又はドレインの一方がトラン

ジスタ128のゲートに電気的に接続されている。なお、トランジスタ121は、スイッ

チングトランジスタと呼ばれることがある。また、トランジスタ128は、ソース又はド

レインの一方が配線142a、142bのいずれかに電気的に接続され、他方が発光素子

129の一方の電極に電気的に接続されている。なお、トランジスタ128は、駆動トラ

ンジスタと呼ばれることがある。

能である。

ース又はドレインの一方を電気的に接続させた構成とすることができる(図21(A)参

照)。また、図21(A)の構成において、トランジスタ111のゲートに他のトランジ

スタ(ここでは、トランジスタ162)のソース又はドレインの一方を電気的に接続させ

た構成とすることができる(図21(B)参照)。また、図21(A)の構成において、

トランジスタ112のゲートに他のトランジスタ(ここでは、トランジスタ163)のソ

ース又はドレインの一方を電気的に接続させた構成とすることができる(図21(C)参

照)。

れている配線は配線102と電気的に接続されていてもよいし、トランジスタ112とト

ランジスタ162のゲートが同一の配線に電気的に接続される構成としてもよい。

に接続(ダイオード接続)した構成としてもよい(図22(A)〜(C)参照)。

る。なお、図23では、シフトレジスタにおける第n段の構成を示す。

構成されている。なお、図23では、第1のトランジスタ201〜第7のトランジスタ2

07をNチャネル型で設けた場合を示しているが、Pチャネル型で設けてもよい。

ンジスタ203のソース又はドレインの一方、第4のトランジスタ204のソース又はド

レインの一方及び第5のトランジスタ205のゲートに電気的に接続され、ソース又はド

レインの一方が配線212aに電気的に接続され、他方が第3のトランジスタ203のゲ

ート、第6のトランジスタ206のゲート及び容量素子208の一方の電極に電気的に接

続されている。

、ソースが第1のトランジスタ201のゲート及び第5のトランジスタ205のゲートに

電気的に接続されている。また、ドレインにn−1段から出力された信号が入力される。

の他方及び容量素子208の一方の電極に電気的に接続され、ソース又はドレインの一方

が第5のトランジスタ205のゲートに電気的に接続され、他方が配線212aに電気的

に接続されている。

又はドレインの一方が第5のトランジスタ205のゲートに電気的に接続され、他方が配

線212aに電気的に接続されている。

ンジスタ202のソース、第3のトランジスタ203のソース又はドレインの一方及び第

4のトランジスタ204のソース又はドレインの一方に電気的に接続され、ソース又はド

レインの一方が配線211に電気的に接続され、他方が配線213と電気的に接続されて

いる。

の他方及び容量素子208の一方の電極に電気的に接続され、ソース又はドレインの一方

が配線212bに電気的に接続され、他方が配線213に電気的に接続されている。

ス又はドレインの一方に配線212cが電気的に接続され、他方が配線213に電気的に

接続されている。

スタ206のゲートに電気的に接続され、他方の電極が配線211に電気的に接続されて

いる。

レベル信号又は電位が変化するLレベル信号が入力される。なお、各配線に入力される信

号はこれに限られず適宜選択することができる。

を供給する非選択期間)には、第3のトランジスタ203及び第6のトランジスタ206

と、第7のトランジスタ207が交互にオンして動作する。そのため、上記実施の形態で

示したように、配線212b、212cに電位が変化するLレベル信号を入力し、第6の

トランジスタ206、第7のトランジスタ207を流れる電流の方向を入れ替える(ソー

スとドレインを入れ替える)ことによって、ソース側又はドレイン側への電界の集中を抑

制し、トランジスタの劣化を低減することができる。また、配線212aに電位が変化す

るLレベル信号を入力することにより、第3のトランジスタ203を流れる電流の方向を

入れ替える(ソースとドレインを入れ替える)構成としてもよい。

的に接続された構成としてもよい。配線212bと配線212cを電気的に接続する場合

には、第6のトランジスタ206と第7のトランジスタ207は、上記図5におけるトラ

ンジスタ112a、トランジスタ112bとして機能する。また、配線212bと配線2

12cを電気的に独立させてそれぞれ異なる信号を供給する場合には、第6のトランジス

タ206と第7のトランジスタ207は、図12におけるトランジスタ112、トランジ

スタ114として機能する。

に示すように、第1のトランジスタ221〜第12のトランジスタ232を各段(ここで

は、n段)に有する構成としてもよい。

され、ソース又はドレインの一方が配線241に電気的に接続され、他方が第4のトラン

ジスタ224のゲート、第8のトランジスタ228のゲート、第9のトランジスタ229

のゲート及び第11のトランジスタ231のゲートに電気的に接続されている。また、第

2のトランジスタ222は、ゲートにn+1段からの出力信号が入力され、ソース又はド

レインの一方が配線242aに電気的に接続され、他方が第4のトランジスタ224のゲ

ート、第8のトランジスタ228のゲート、第9のトランジスタ229のゲート及び第1

1のトランジスタ231のゲートに電気的に接続されている。また、第3のトランジスタ

223は、ゲートがドレインに電気的に接続(ダイオード接続)され、ソースが第5のト

ランジスタ225のゲートに電気的に接続され、ドレインが配線241と電気的に接続さ

れている。また、第4のトランジスタ224は、ソース又はドレインの一方が配線242

aに電気的に接続され、他方が第5のトランジスタ225のゲートに電気的に接続されて

いる。

接続され、他方が第7のトランジスタ227のゲート、第10のトランジスタ230のゲ

ート及び第12のトランジスタ232のゲートに電気的に接続されている。また、第6の

トランジスタ226は、ゲートにn−1段からの出力信号が入力され、ソース又はドレイ

ンの一方が配線242aに電気的に接続され、他方が第7のトランジスタ227のゲート

、第10のトランジスタ230のゲート及び第12のトランジスタ232のゲートに電気

的に接続されている。また、第7のトランジスタ227は、ソース又はドレインの一方が

配線242aに電気的に接続され、他方が第4のトランジスタ224のゲート、第8のト

ランジスタ228のゲート、第9のトランジスタ229のゲート及び第11のトランジス

タ231のゲートに電気的に接続されている。第8のトランジスタ228は、ソース又は

ドレインの一方が配線242aに電気的に接続され、他方が第7のトランジスタ227の

ゲート、第10のトランジスタ230のゲート及び第12のトランジスタ232のゲート

に電気的に接続されている。

)又はクロック反転信号(CLKB)が入力される。また、第10のトランジスタ230

は、ソース又はドレインの一方が配線242bに電気的に接続されている。また、第11

のトランジスタ231は、ソース又はドレインの一方にクロック信号又はクロック反転信

号が入力され、他方が配線243に電気的に接続されている。また、第12のトランジス

タ232は、ソース又はドレインの一方が配線242bに電気的に接続され、他方が配線

243に電気的に接続されている。

ンジスタ230及び第12のトランジスタ232がオン状態を維持する。そのため、配線

242a、配線242bにLレベル信号又は電位が変化するLレベル信号を入力し、第7

のトランジスタ227、第10のトランジスタ230及び第12のトランジスタ232を

流れる電流の方向を入れ替える(ソースとドレインを入れ替える)ことによって、ソース

側又はドレイン側への電界の集中を抑制し、トランジスタの劣化を低減することができる

。

ャネル型で設けた場合を示しているが、Pチャネル型で設けてもよい。また、第9のトラ

ンジスタ229及び第10のトランジスタ230を設けずに、配線243から出力される

信号をn−1段及びn+1段に出力してもよい。また、配線242aと配線242bを電

気的に接続する構成としてもよい。また、配線241に電位が変化するHレベル信号を入

力してもよい。この場合、第5のトランジスタ225を流れる電流の方向を入れ替える(

ソースとドレインを入れ替える)ことによって、ソース側又はドレイン側への電界の集中

を抑制し、トランジスタの劣化を低減することができる。なお、図24において、各配線

に入力される信号はこれに限られず適宜選択することができる。

段(ここでは、n段)に有する構成としてもよい。

が入力され、ソース又はドレインの一方にn−1段からの出力信号が入力され、他方が第

4のトランジスタ254のゲートに電気的に接続されている。また、第2のトランジスタ

252は、ゲートが配線263に電気的に接続され、ソース又はドレインの一方が配線2

62aと電気的に接続され、他方が第5のトランジスタ255のゲートと電気的に接続さ

れている。また、第3のトランジスタ253は、ゲートにクロック反転信号(CLKB)

が入力され、ソース又はドレインの一方が配線264と電気的に接続され、他方が第5の

トランジスタ255のゲートと電気的に接続されている。また、第4のトランジスタ25

4は、ゲートが第1のトランジスタ251のソース又はドレインの他方と電気的に接続さ

れ、ソース又はドレインの一方にクロック信号(CLK)が入力され、他方が配線263

と電気的に接続されている。また、第5のトランジスタ255は、ソース又はドレインの

一方が配線262bと電気的に接続され、他方が配線263と電気的に接続されている。

持する。そのため、配線262bに電位が変化するHレベル信号を入力し、第5のトラン

ジスタ255を流れる電流の方向を入れ替える(ソースとドレインを入れ替える)ことに

よって、ソース側又はドレイン側への電界の集中を抑制し、トランジスタの劣化を低減す

ることができる。

ネル型で設けた場合を示しているが、Nチャネル型で設けてもよい。また、配線262a

と配線262bは電気的に接続する構成としてもよい。また、図25において、各配線に

入力される信号はこれに限られず適宜選択することができる。

各段(ここでは、n段)に有する構成としてもよい。

、ソース又はドレインの一方に第1の入力信号が入力され、他方が第8のトランジスタ2

78のゲートと電気的に接続されている。また、第2のトランジスタ272は、ゲートに

第2のクロック信号が入力され、ソース又はドレインの一方に第2の入力信号が入力され

、他方が第8のトランジスタ278のゲートと電気的に接続されている。また、第3のト

ランジスタ273は、ソース又はドレインの一方が配線282aに電気的に接続され、他

方が第8のトランジスタ278のゲートと電気的に接続されている。また、第4のトラン

ジスタ274は、ソース又はドレインの一方が配線282aに電気的に接続され、他方が

第5のトランジスタ275のソース又はドレインの一方及び第6のトランジスタ276の

ソース又はドレインの一方に電気的に接続されている。また、第5のトランジスタ275

は、ゲートに第3のクロック信号が入力され、ソース又はドレインの一方が第4のトラン

ジスタ274のソース又はドレインの他方に電気的に接続され、他方が第8のトランジス

タ278のゲートと電気的に接続されている。

はドレインの一方が第4のトランジスタ274のソース又はドレインの他方に電気的に接

続され、他方が第9のトランジスタ279のゲートと電気的に接続されている。また、第

7のトランジスタ277は、ゲートがドレインに電気的に接続(ダイオード接続)され、

ソースが第3のトランジスタ273のゲート、第4のトランジスタ274のゲート及び第

10のトランジスタ280のゲートに電気的に接続され、ドレインに第3のクロック信号

が入力される。第8のトランジスタ278は、ソース又はドレインの一方が配線282a

に電気的に接続され、他方が第3のトランジスタ273のゲート、第4のトランジスタ2

74のゲート及び第10のトランジスタ280のゲートに電気的に接続されている。また

、第9のトランジスタ279は、ソース又はドレインの一方に第4のクロック信号が入力

され、他方が配線283と電気的に接続されている。また、第10のトランジスタ280

は、ソース又はドレインの一方が配線282bに電気的に接続され、他方が配線283に

電気的に接続されている。

維持する。そのため、配線282bに電位が変化するHレベル信号を入力し、第10のト

ランジスタ280を流れる電流の方向を入れ替える(ソースとドレインを入れ替える)こ

とによって、ソース側又はドレイン側への電界の集中を抑制し、トランジスタの劣化を低

減することができる。

ャネル型で設けた場合を示しているが、Nチャネル型で設けてもよい。また、配線282

aと配線282bは電気的に接続する構成としてもよい。また、図26において、各配線

に入力される信号はこれに限られず適宜選択することができる。

バ等の駆動回路に適用する場合を示したが、これに限られない。他にも、容量線の電位を

制御する場合、共通電極の電位を制御する場合にも適用可能である。

た構成を含む)と適宜組み合わせて実施することができる。

本実施の形態においては、上記実施の形態で示した回路に適用可能なトランジスタの構造

について説明する。トランジスタは、トランジスタが有する半導体層に用いる材料によっ

て大きく分類されることができる。半導体層に用いる材料としては、主成分としてシリコ

ンが含まれるシリコン系材料と、主成分としてシリコンを含まない非シリコン系材料に分

類できる。シリコン系材料には、アモルファスシリコン(a−Si:H)、マイクロクリ

スタルシリコン(μc−Si)、ポリシリコン(p−Si)、単結晶シリコン(c−Si

)等が挙げられる。非シリコン系材料としては、砒化ガリウム(GaAs)等の化合物半

導体、酸化亜鉛(ZnO)、インジウムとガリウムと亜鉛を含む酸化物(InGaZnO

)等の酸化物半導体等が挙げられる。

て用いる場合は、トランジスタの特性の均一性が高く、かつ、製造コストが小さいという

利点がある。特に、対角の長さが500mmを超えるような大型の基板にトランジスタを

作製する場合に有効である。以下に、半導体層としてアモルファスシリコンまたはマイク

ロクリスタルシリコンを用いるトランジスタおよび容量素子の構造の一例について説明す

る。

す図である。

側からの不純物が半導体層に影響を及ぼし、トランジスタの性質が変化してしまうことを

防ぐ下地膜としての機能を有することができる。なお、第1の絶縁膜としては、酸化シリ

コン膜、窒化シリコン膜又は酸化窒化シリコン膜(SiOxNy)などの単層、又はこれ

らの積層を用いることができる。特に、窒化シリコン膜は緻密な膜であり、高いバリア性

を有するため、第1の絶縁膜には窒化シリコンが含まれることが好ましい。なお、第1の

絶縁膜は必ずしも形成されなくても良い。第1の絶縁膜が形成されない場合は、工程数の

削減、製造コストの低減および歩留まりの向上を図ることができる。

)が形成される。導電層5143は、トランジスタ5158のソース及びドレインの一方

として機能する部分を含む。導電層5144は、トランジスタ5158のソース及びドレ

インの他方として機能する部分を含む。導電層5145は、容量素子5159の第1の電

極として機能する部分を含む。なお、第1の導電層としては、Ti、Mo、Ta、Cr、

W、Al、Nd、Cu、Ag、Au、Pt、Nb、Si、Zn、Fe、Ba、Geなど、

又はこれらの合金を用いることができる。あるいは、これらの元素(合金も含む)の積層

膜を用いることができる。

導体層5147)が形成される。半導体層5146は、ソースとドレインの一方として機

能する部分を含む。半導体層5147は、ソースとドレインの他方として機能する部分を

含む。なお、第1の半導体層としては、リン等を含んだシリコン等を用いることができる

。

層(半導体層5148)が形成される。そして、半導体層5148の一部は、導電層51

43上及び導電層5144上まで延長されている。半導体層5148は、トランジスタ5

158のチャネル領域として機能する部分を含む。なお、第2の半導体層としては、アモ

ルファスシリコン(a−Si:H)等の非結晶性を有する半導体層、又は微結晶シリコン

(μc−Si)等の半導体層などを用いることができる。

149及び絶縁膜5150)が形成される。第2の絶縁膜は、ゲート絶縁膜としての機能

を有する。なお、第2の絶縁膜としては、酸化シリコン膜、窒化シリコン膜又は酸化窒化

シリコン膜(SiOxNy)などの単層、又はこれらの積層を用いることができる。

とが望ましい。なぜなら、第2の半導体層と第2の絶縁膜とが接する界面におけるトラッ

プ準位が少なくなるからである。

シリコン膜を用いることが望ましい。なぜなら、酸化シリコン膜はMoを酸化させないか

らである。

導電層5151は、トランジスタ5158のゲート電極として機能する部分を含む。導電

層5152は、容量素子5159の第2の電極、又は配線としての機能を有する。なお、

第2の導電層としては、Ti、Mo、Ta、Cr、W、Al、Nd、Cu、Ag、Au、

Pt、Nb、Si、Zn、Fe、Ba、Geなど、又はこれらの合金を用いることができ

る。あるいは、これらの元素(合金も含む)の積層を用いることができる。

成されてもよい。

の断面構造を示す図である。特に、図27(B)に示すトランジスタは、チャネルエッチ

型と呼ばれる構造である。

側からの不純物が半導体層に影響を及ぼし、トランジスタの性質が変化してしまうことを

防ぐ下地膜としての機能を有することができる。なお、第1の絶縁膜としては、酸化シリ

コン膜、窒化シリコン膜又は酸化窒化シリコン膜(SiOxNy)などの単層、又はこれ

らの積層を用いることができる。特に、窒化シリコン膜は緻密な膜であり、高いバリア性

を有するため、第1の絶縁膜には窒化シリコンが含まれることが好ましい。なお、第1の

絶縁膜は必ずしも形成されなくても良い。第1の絶縁膜が形成されない場合は、工程数の

削減、製造コストの低減および歩留まりの向上を図ることができる。

導電層5163は、トランジスタ5178のゲート電極として機能する部分を含む。導電

層5164は、容量素子5179の第1の電極として機能する部分を含む。なお、第1の

導電層としては、Ti、Mo、Ta、Cr、W、Al、Nd、Cu、Ag、Au、Pt、

Nb、Si、Zn、Fe、Ba、Geなど、又はこれらの合金を用いることができる。あ

るいは、これらの元素(合金も含む)の積層を用いることができる。

第2の絶縁膜は、ゲート絶縁膜としての機能を有する。なお、第2の絶縁膜としては、酸

化シリコン膜、窒化シリコン膜又は酸化窒化シリコン膜(SiOxNy)などの単層、又

はこれらの積層を用いることができる。

ましい。なぜなら、半導体層と第2の絶縁膜とが接する界面におけるトラップ準位が少な

くなるからである。

シリコン膜を用いることが望ましい。なぜなら、酸化シリコン膜はMoを酸化させないか

らである。

フィ法、インクジェット法又は印刷法などによって、第1の半導体層(半導体層5166

)が形成される。そして、半導体層5166の一部は、第2の絶縁膜上のうち第1の導電

層と重なって形成されていない部分まで延長されている。半導体層5166は、トランジ

スタ5178のチャネル領域として機能する部分を含む。なお、半導体層5166として

は、アモルファスシリコン(a−Si:H)等の非結晶性を有する半導体層、又は微結晶

シリコン(μc−Si)等の半導体層などを用いることができる。

が形成される。半導体層5167は、ソースとドレインの一方として機能する部分を含む

。半導体層5168は、ソースとドレインの他方として機能する部分を含む。なお、第2

の半導体層としては、リン等を含んだシリコン等を用いることができる。

0及び導電層5171)が形成される。導電層5169は、トランジスタ5178のソー

スとドレインの一方として機能する部分を含む。導電層5170は、トランジスタ517

8のソースとドレインの他方として機能する部分を含む。導電層5171は、容量素子5

179の第2の電極として機能する部分を含む。なお、第2の導電層としては、Ti、M

o、Ta、Cr、W、Al、Nd、Cu、Ag、Au、Pt、Nb、Si、Zn、Fe、

Ba、Geなど、又はこれらの合金を用いることができる。あるいは、これらの元素(合

金も含む)の積層を用いることができる。

成されてもよい。

半導体層は連続して成膜されることができる。そして、第1の半導体層及び第2の半導体

層は、同じマスクを用いて形成されることができる。

体層の一部を除去することができる。または、第2の導電層に用いたマスクと同じマスク

を用いて第2の半導体層の一部を除去することで、トランジスタのチャネル領域を形成す

ることができる。こうすることで、第2の半導体層の一部を除去するためだけの新たなマ

スクを用いる必要がないため、製造工程が簡単となり、製造コストが低減できる。ここで

、除去される第2の半導体層の下部に形成されている第1の半導体層の一部がトランジス

タのチャネル領域となる。

の断面構造を示す図である。特に、図27(C)に示すトランジスタは、チャネル保護型

(エッチストップ型)と呼ばれる構造である。

側からの不純物が半導体層に影響を及ぼし、トランジスタの性質が変化してしまうことを

防ぐ下地膜としての機能を有することができる。なお、第1の絶縁膜としては、酸化シリ

コン膜、窒化シリコン膜又は酸化窒化シリコン膜(SiOxNy)などの単層、又はこれ

らの積層を用いることができる。特に、窒化シリコン膜は緻密な膜であり、高いバリア性

を有するため、第1の絶縁膜には窒化シリコンが含まれることが好ましい。なお、第1の

絶縁膜は必ずしも形成されなくても良い。第1の絶縁膜が形成されない場合は、工程数の

削減、製造コストの低減および歩留まりの向上を図ることができる。

導電層5183は、トランジスタ5198のゲート電極として機能する部分を含む。導電

層5184は、容量素子5199の第1の電極として機能する部分を含む。なお、第1の

導電層としては、Ti、Mo、Ta、Cr、W、Al、Nd、Cu、Ag、Au、Pt、

Nb、Si、Zn、Fe、Ba、Geなど、又はこれらの合金を用いることができる。あ

るいは、これらの元素(合金も含む)の積層を用いることができる。

第2の絶縁膜は、ゲート絶縁膜としての機能を有する。なお、第2の絶縁膜としては、酸

化シリコン膜、窒化シリコン膜又は酸化窒化シリコン膜(SiOxNy)などの単層、又

はこれらの積層を用いることができる。

ましい。なぜなら、半導体層と第2の絶縁膜とが接する界面におけるトラップ準位が少な

くなるからである。

シリコン膜を用いることが望ましい。なぜなら、酸化シリコン膜はMoを酸化させないか

らである。

フィ法、インクジェット法又は印刷法などによって、第1の半導体層(半導体層5186

)が形成される。そして、半導体層5188の一部は、第2の絶縁膜上のうち第1の導電

層と重なって形成されていない部分まで延長されている。半導体層5186は、トランジ

スタ5198のチャネル領域として機能する部分を含む。なお、半導体層5186として

は、アモルファスシリコン(a−Si:H)等の非結晶性を有する半導体層、又は微結晶

シリコン(μc−Si)等の半導体層などを用いることができる。

92は、トランジスタ5198のチャネル領域がエッチングによって除去されることを防

止する機能を有する。つまり、絶縁膜5192は、チャネル保護膜(エッチストップ膜)

として機能する。なお、第3の絶縁膜としては、酸化シリコン膜、窒化シリコン膜又は酸

化窒化シリコン膜(SiOxNy)などの単層、又はこれらの積層を用いることができる

。

7及び半導体層5188)が形成される。半導体層5187は、ソースとドレインの一方

として機能する部分を含む。半導体層5188は、ソースとドレインの他方として機能す

る部分を含む。なお、第2の半導体層としては、リン等を含んだシリコン等を用いること

ができる。

1)が形成される。導電層5189は、トランジスタ5198のソースとドレインの一方