JP4707947B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4707947B2 JP4707947B2 JP2003384654A JP2003384654A JP4707947B2 JP 4707947 B2 JP4707947 B2 JP 4707947B2 JP 2003384654 A JP2003384654 A JP 2003384654A JP 2003384654 A JP2003384654 A JP 2003384654A JP 4707947 B2 JP4707947 B2 JP 4707947B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- breakdown voltage

- semiconductor

- semiconductor region

- high breakdown

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 525

- 230000015556 catabolic process Effects 0.000 claims description 410

- 239000000758 substrate Substances 0.000 claims description 173

- 230000005669 field effect Effects 0.000 claims description 125

- 238000002955 isolation Methods 0.000 claims description 65

- 238000000926 separation method Methods 0.000 claims description 65

- 239000012535 impurity Substances 0.000 claims description 47

- 230000015572 biosynthetic process Effects 0.000 description 151

- 238000004519 manufacturing process Methods 0.000 description 116

- 238000000034 method Methods 0.000 description 107

- 230000005684 electric field Effects 0.000 description 37

- 230000002829 reductive effect Effects 0.000 description 29

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 26

- 229910052814 silicon oxide Inorganic materials 0.000 description 22

- 238000001459 lithography Methods 0.000 description 21

- 238000005468 ion implantation Methods 0.000 description 20

- 229910021332 silicide Inorganic materials 0.000 description 19

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 19

- 238000005229 chemical vapour deposition Methods 0.000 description 18

- 239000010410 layer Substances 0.000 description 18

- 238000007254 oxidation reaction Methods 0.000 description 16

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 15

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 15

- 229910052796 boron Inorganic materials 0.000 description 15

- 230000003647 oxidation Effects 0.000 description 15

- 229910052698 phosphorus Inorganic materials 0.000 description 15

- 239000011574 phosphorus Substances 0.000 description 15

- 229910052751 metal Inorganic materials 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 13

- 239000004020 conductor Substances 0.000 description 12

- 238000005530 etching Methods 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- 229910017052 cobalt Inorganic materials 0.000 description 9

- 239000010941 cobalt Substances 0.000 description 9

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 9

- 229910052710 silicon Inorganic materials 0.000 description 9

- 239000010703 silicon Substances 0.000 description 9

- 238000010438 heat treatment Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 238000000059 patterning Methods 0.000 description 5

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 239000000969 carrier Substances 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000018109 developmental process Effects 0.000 description 3

- 230000012447 hatching Effects 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 238000005549 size reduction Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- ZXEYZECDXFPJRJ-UHFFFAOYSA-N $l^{3}-silane;platinum Chemical compound [SiH3].[Pt] ZXEYZECDXFPJRJ-UHFFFAOYSA-N 0.000 description 2

- VLJQDHDVZJXNQL-UHFFFAOYSA-N 4-methyl-n-(oxomethylidene)benzenesulfonamide Chemical compound CC1=CC=C(S(=O)(=O)N=C=O)C=C1 VLJQDHDVZJXNQL-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- 229910019001 CoSi Inorganic materials 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 229910008484 TiSi Inorganic materials 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- KMTYGNUPYSXKGJ-UHFFFAOYSA-N [Si+4].[Si+4].[Ni++] Chemical compound [Si+4].[Si+4].[Ni++] KMTYGNUPYSXKGJ-UHFFFAOYSA-N 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000000994 depressogenic effect Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 125000001475 halogen functional group Chemical group 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229910021340 platinum monosilicide Inorganic materials 0.000 description 2

- 229910021339 platinum silicide Inorganic materials 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 229910021341 titanium silicide Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- QGZKDVFQNNGYKY-UHFFFAOYSA-N ammonia Natural products N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 1

- -1 ammonia peroxide Chemical class 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66659—Lateral single gate silicon transistors with asymmetry in the channel direction, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/0405—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising semiconducting carbon, e.g. diamond, diamond-like carbon

- H01L21/041—Making n- or p-doped regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H01L21/76229—Concurrent filling of a plurality of trenches having a different trench shape or dimension, e.g. rectangular and V-shaped trenches, wide and narrow trenches, shallow and deep trenches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823412—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823418—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823481—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type isolation region manufacturing related aspects, e.g. to avoid interaction of isolation region with adjacent structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7835—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with asymmetrical source and drain regions, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/665—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using self aligned silicidation, i.e. salicide

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Element Separation (AREA)

Description

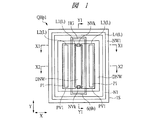

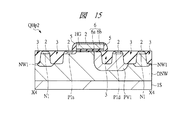

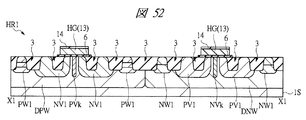

図1は本実施の形態1の高耐圧pMISQHp1の一例の要部平面図、図2は図1と同一箇所の平面図であって特に高耐圧pMISQHp1の電界緩和機能を持つp-型の半導体領域PV1とn+型の半導体領域NVkとの配置関係を示した要部平面図、図3は図1と同一箇所の平面図であって特に高耐圧pMISQHp1のゲート電極HGと活性領域Lとn+型の半導体領域NVkとの配置関係を示した要部平面図、図4は図1と同一箇所の平面図であって特に分離領域および活性領域Lを示した要部平面図、図5は図1〜図4のX1−X1線の断面図、図6は図1〜図4のX2−X2線の断面図、図7は図1〜図4のY1−Y1線の断面図をそれぞれ示している。なお、ここでは、高耐圧pMISに本発明を適用した場合について説明するが、p、nの導電型を逆にすることで、高耐圧nMISに適用することもできる。また、図4は平面図であるが図面を見易くするため分離領域にハッチングを付す。また、第1方向Xは、各図の左右横方向であってゲート長方向(チャネル長方向)またはゲート電極HGの短方向を示し、第2方向Yは、上記第1方向Xに直交する方向であり各図の上下縦方向であってゲート幅方向またはゲート電極HGの長手方向を示している。

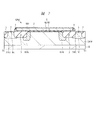

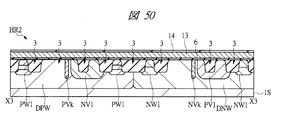

前記実施の形態1では、ソースおよびドレインの両方ともがウエルとの間で耐圧を確保できる構成について説明したが、本実施の形態2では、ソース−ウエル間に大きな耐圧を必要としない場合の高耐圧MIS構造の一例を説明する。すなわち、nMISの場合、p型ウェルが共通のGND (pMISの場合はn型ウエルが共通のVcc)に接続されているような回路では、ソース電位がp型ウェル電位と異なるため、ソース−ウエル間の耐圧を確保するために逆バイアス耐圧が必要となるので、ソース側をドレイン側と同じ構造としている。すなわち、例えばnMISの場合、p型ウエルに逆バイアス耐圧として−16.5V程度、nMISのソースに1.5V程度が印加されるのでソース−ウエル間の耐圧を確保するためソース側をドレイン側と同じ構造されており、40V以上の耐圧を確保できる構造とされている。このとき、低耐圧MISのソース−ウエル間の耐圧は10V程度を確保できる構造となっている。すなわち、高耐圧MISのソース−ウエル間の耐圧は、低耐圧MISのソース−ウエル間の耐圧よりも大きくなるように形成されている。このような回路としては、例えば出力回路や昇圧回路等が例示できる。しかしながら、ソース−ウエル間で電位差の生じないような回路では、ソース−ウエル間の耐圧を確保するための逆バイアス耐圧が必要とならないので、ドレイン側のみを高耐圧構造とすることができる。このような構造とすることで、MISのサイズを縮小することが可能となり、半導体チップ面積のサイズを縮小することができる。

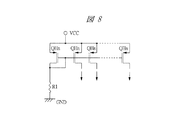

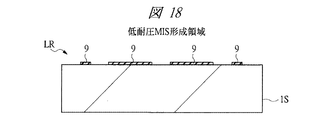

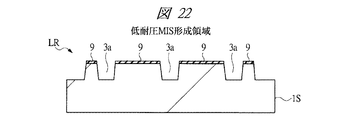

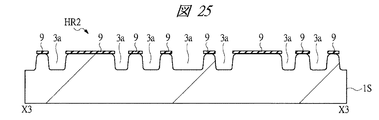

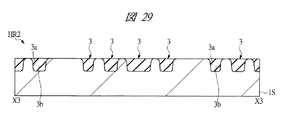

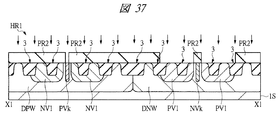

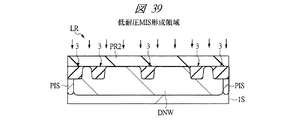

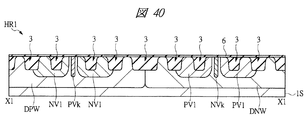

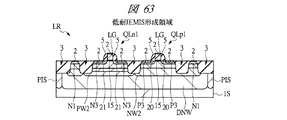

本実施の形態3では、前記実施の形態1,2の構造の高耐圧MISと、低耐圧MISとを同一の基板1Sに持つ半導体装置の製造方法の一例を図16〜図63により説明する。なお、図16〜図63中の符号HR1は前記実施の形態1の構造の高耐圧MISの形成領域、符号HR2は前記実施の形態2の構造の高耐圧MISの形成領域、符号LRは低耐圧MISの形成領域をそれぞれ示している。また、高耐圧MISの形成領域HR1,HR2の断面は、それぞれ図1のX−X1線、図10のX3−X3線に相当する箇所の断面図を示している。

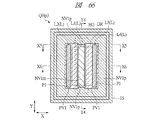

本実施の形態4では、高耐圧MISの変形例について説明する。図64はその高耐圧pMISQHp3の一例の要部平面図、図65は図64と同一箇所の平面図であって特に高耐圧pMISQHp3の電界緩和機能を持つp-型の半導体領域PV1とカウンタードープ領域DRとの配置関係を示した要部平面図、図66は図64と同一箇所の平面図であって特に高耐圧pMISQHp3の各半導体領域の様子を示した要部平面図、図67は図64と同一箇所の平面図であって特に活性領域L内における半導体領域の様子を示した要部平面図、図68は図64〜図67のX5−X5線の断面図、図69は図64〜図67のX6−X6線の断面図、図70は図64〜図67のY4−Y4線の断面図をそれぞれ示している。なお、ここでも、高耐圧pMISに本発明を適用した場合について説明するが、p、nの導電型を逆にすることで、高耐圧nMISに本発明を適用することもできるのは実施の形態1と同様である。また、図66および図67は平面図であるが図面を見易くするため各半導体領域にハッチングを付す。

本実施の形態5では、前記実施の形態4の高耐圧MISの変形例であって、ソース−ウエル間に大きな耐圧を必要としない場合の高耐圧MIS構造の一例を説明する。

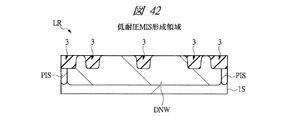

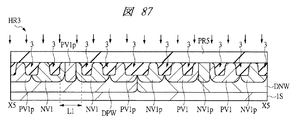

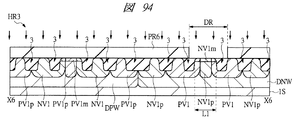

本実施の形態6では、前記実施の形態4,5の構造の高耐圧MISと、低耐圧MISとを同一の基板1Sに持つ半導体装置の製造方法の一例を図78〜図101により説明する。なお、図78〜図101中の符号HR3は前記実施の形態4の構造の高耐圧MISの形成領域(X5−X5)、符号HR4は前記実施の形態5の構造の高耐圧MISの形成領域(X7−X7)、符号LRは低耐圧MISの形成領域をそれぞれ示している。

本実施の形態7では、前記実施の形態4の半導体装置の溝型の分離部3を、LOCOS(Local Oxidization of Silicon)法で形成した分離部に代えた場合について説明する。

本実施の形態8では、前記実施の形態5の半導体装置の溝型の分離部3を、LOCOS法で形成した分離部に代えた場合について説明する。

2 シリサイド層

3 分離部

3a 溝

3b 絶縁膜

5 サイドウォール

6 ゲート絶縁膜

6a,6b 絶縁膜

8 絶縁膜

9 絶縁膜

10 絶縁膜

13 導体膜

14 絶縁膜

15 ゲート絶縁膜

16 多結晶シリコン膜

18 p-型の半導体領域

19 n-型の半導体領域

20 p-型の半導体領域

21 n-型の半導体領域

50 高耐圧MIS・FET

51 溝型の分離部

52 半導体基板

53 ゲート電極

54 深いウエル

QHp,QHp1,QHp2,QHp3,QHp4 高耐圧pチャネル型MIS・FET

QHp5,QHp6 高耐圧pチャネル型MIS・FET

QHn,QHn1,QHn2,QHn3,QHn4 高耐圧nチャネル型MIS・FET

QLn1 低耐圧nチャネル型MIS・FET

QLp1 低耐圧pチャネル型MIS・FET

DNW 深いn型ウエル

DPW 深いp型ウエル

PIS 分離用のp型の半導体領域

PW1,PW2 p+型ウエル

NW1,NW2 n+型ウエル

P1,P1s,P1d,P2,P3 p+型の半導体領域

PV1 p-型の半導体領域

PV1p p+型の半導体領域

PV1m p-型の半導体領域

N1,N1s,N1d,N2,N3 n+型の半導体領域

NV1 n-型の半導体領域

NV1p n+型の半導体領域

NV1m n-型の半導体領域

L,L1〜L5 活性領域

HG ゲート電極

LG ゲート電極

NVk n+型の半導体領域

PVk p+型の半導体領域

Vcc 高電位側の電源電位

GND 基準電位側の電源電位

R1,R2 抵抗

PR1〜PR6 フォトレジスト膜

DR カウンタードープ領域

S0 ソース領域

D0 ドレイン領域

V0 半導体領域

Claims (10)

- 高耐圧電界効果トランジスタの第1導電型のチャネル領域のゲート幅方向の両端の溝型の分離部と半導体基板との境界領域に、前記チャネル領域と同一導電型であり、前記チャネル領域よりも高不純物濃度の第1導電型の半導体領域を、前記高耐圧電界効果トランジスタの前記第1導電型とは逆の第2導電型のドレイン用の半導体領域に接しないように、前記ドレイン用の半導体領域から離れた位置に配置したことを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記第1導電型の半導体領域を、前記半導体基板の主面から前記溝型の分離部よりも深い位置まで延在させて形成したことを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記半導体基板に、前記高耐圧電界効果トランジスタよりも動作電圧の低い低耐圧電界効果トランジスタを設けたことを特徴とする半導体装置。

- 半導体基板の主面に溝型の分離部で規定された活性領域を備え、前記活性領域に高耐圧電界効果トランジスタのチャネル領域を配置した構成を有する半導体装置であって、

前記高耐圧電界効果トランジスタは、

(a)前記活性領域上にゲート絶縁膜を介して設けられたゲート電極と、

(b)前記活性領域のゲート長方向の両側に前記溝型の分離部を介して設けられたソースおよびドレイン用の第1導電型の第1半導体領域と、

(c)前記ソースおよびドレイン用の第1導電型の第1半導体領域よりも低不純物濃度の半導体領域であって、前記ソースおよびドレイン用の第1導電型の第1半導体領域の各々と前記活性領域のチャネル領域とを電気的に接続するように設けられたソースおよびドレイン用の第1導電型の第2半導体領域と、

(d)前記第1導電型とは逆の第2導電型の半導体領域であって、前記活性領域の前記ソースおよびドレイン用の第1導電型の第2半導体領域の間に一部が介在され、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域を内包するように設けられた第3半導体領域とを有し、

前記活性領域のゲート幅方向の両端の前記溝型の分離部と前記半導体基板との境界領域に、前記第3半導体領域よりも高不純物濃度の第2導電型の第4半導体領域を、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域に接しないように、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域から離れた位置に配置したことを特徴とする半導体装置。 - 半導体基板の主面に溝型の分離部で規定された活性領域を備え、前記活性領域に高耐圧電界効果トランジスタのチャネル領域を配置した構成を有する半導体装置であって、

前記高耐圧電界効果トランジスタは、

(a)前記活性領域上にゲート絶縁膜を介して設けられたゲート電極と、

(b)前記活性領域のゲート長方向の一方の片側に前記溝型の分離部を介して設けられた第1導電型のドレイン用の第1導電型の第1半導体領域と、

(c)前記活性領域のゲート長方向の他方の片側に前記溝型の分離部を介さずに隣接して設けられた第1導電型のソース用の第1導電型の第1半導体領域と、

(d)前記ドレイン用の第1導電型の第1半導体領域よりも低不純物濃度の半導体領域であって、前記ドレイン用の第1導電型の第1半導体領域を内包し、かつ、前記ドレイン用の第1導電型の第1半導体領域と前記活性領域のチャネル領域とを電気的に接続するように設けられたドレイン用の第1導電型の第2半導体領域と、

(e)前記第1導電型とは逆の第2導電型の半導体領域であって、前記活性領域の前記ソース用の第1導電型の第1半導体領域と前記ドレイン用の第2半導体領域との間に一部が介在され、前記ソース用の第1導電型の第1半導体領域と前記ドレイン用の第1導電型の第2半導体領域とを内包するように設けられた第3半導体領域とを有し、

前記活性領域のゲート幅方向の両端の前記溝型の分離部と前記半導体基板との境界領域に、前記第3半導体領域よりも高不純物濃度の第2導電型の第4半導体領域を、前記ドレイン用の第1導電型の第1、第2半導体領域に接しないように、前記ドレイン用の第1導電型の第1、第2半導体領域から離れた位置に配置したことを特徴とする半導体装置。 - 請求項4または5記載の半導体装置において、前記第4半導体領域を、前記半導体基板の主面から前記溝型の分離部よりも深い位置まで延在させて形成したことを特徴とする半導体装置。

- 請求項4または5記載の半導体装置において、前記半導体基板に、前記高耐圧電界効果トランジスタよりも動作電圧の低い低耐圧電界効果トランジスタを設けたことを特徴とする半導体装置。

- 半導体基板の主面に溝型の分離部で規定された第1、第2活性領域を備え、前記第1、第2活性領域の各々に第1、第2高耐圧電界効果トランジスタのそれぞれのチャネル領域を配置した構成を有する半導体装置であって、

前記第1高耐圧電界効果トランジスタは、

(a)前記第1活性領域上にゲート絶縁膜を介して設けられたゲート電極と、

(b)前記第1活性領域のゲート長方向の両側に前記溝型の分離部を介して設けられたソースおよびドレイン用の第1導電型の第1半導体領域と、

(c)前記ソースおよびドレイン用の第1半導体領域よりも低不純物濃度の半導体領域であって、前記ソースおよびドレイン用の第1導電型の第1半導体領域の各々と前記第1活性領域のチャネル領域とを電気的に接続するように設けられたソースおよびドレイン用の第1導電型の第2半導体領域と、

(d)前記第1導電型とは逆の第2導電型の半導体領域であって、前記第1活性領域の前記ソースおよびドレイン用の第1導電型の第2半導体領域の間に一部が介在され、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域を内包するように設けられた第3半導体領域と、

(e)前記第3半導体領域よりも高不純物濃度の半導体領域であって、前記第1活性領域のゲート幅方向の両端の前記溝型の分離部と前記半導体基板との境界領域に、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域に接しないように、前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域から離れた状態で設けられた第2導電型の第4半導体領域とを有し、

前記第2高耐圧電界効果トランジスタは、

(a)前記第2活性領域上にゲート絶縁膜を介して設けられたゲート電極と、

(b)前記第2活性領域のゲート長方向の一方の片側に前記溝型の分離部を介して設けられたドレイン用の第1導電型の第1半導体領域と、

(c)前記第2活性領域のゲート長方向の他方の片側に前記溝型の分離部を介さずに隣接して設けられたソース用の第1導電型の第1半導体領域と、

(d)前記第2高耐圧電界効果トランジスタの前記ドレイン用の第1導電型の第1半導体領域よりも低不純物濃度の半導体領域であって、前記第2高耐圧電界効果トランジスタの前記ドレイン用の第1導電型の第1半導体領域と前記第2活性領域のチャネル領域とを電気的に接続するように設けられたドレイン用の第1導電型の第2半導体領域と、

(e)前記第1導電型とは逆の第2導電型の半導体領域であって、前記第2活性領域の前記ソース用の第1導電型の第1半導体領域と前記第2高耐圧電界効果トランジスタの前記ドレイン用の第1導電型の第2半導体領域との間に一部が介在され、前記第2高耐圧電界効果トランジスタの前記ソース用の第1導電型の第1半導体領域と前記ドレイン用の第1導電型の第1、第2半導体領域とを内包するように設けられた第3半導体領域とを有し、

(f)前記第2高耐圧電界効果トランジスタの前記第3半導体領域よりも高不純物濃度の半導体領域であって、前記第2活性領域のゲート幅方向の両端の前記溝型の分離部と前記半導体基板との境界領域に、前記第2高耐圧電界効果トランジスタの前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域に接しないように、前記第2高耐圧電界効果トランジスタの前記ソースおよびドレイン用の第1導電型の第1、第2半導体領域から離れた状態で設けられた第2導電型の第4半導体領域とを有することを特徴とする半導体装置。 - 請求項8記載の半導体装置において、前記第1、第2高耐圧電界効果トランジスタの前記第4半導体領域を、前記半導体基板の主面から前記溝型の分離部よりも深い位置まで延在させて形成したことを特徴とする半導体装置。

- 請求項8記載の半導体装置において、前記半導体基板に、前記第1、第2高耐圧電界効果トランジスタよりも動作電圧の低い低耐圧電界効果トランジスタを設けたことを特徴とする半導体装置。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003384654A JP4707947B2 (ja) | 2003-11-14 | 2003-11-14 | 半導体装置 |

| TW093130160A TWI359492B (en) | 2003-11-14 | 2004-10-05 | A method of manufacturing a semiconductor device |

| CNB2004100909345A CN100463220C (zh) | 2003-11-14 | 2004-11-10 | 半导体器件 |

| CNB2006101431128A CN100440482C (zh) | 2003-11-14 | 2004-11-10 | 半导体器件的制造方法 |

| KR1020040091812A KR20050046568A (ko) | 2003-11-14 | 2004-11-11 | 반도체 장치 및 그 제조 방법 |

| US10/986,896 US7259054B2 (en) | 2003-11-14 | 2004-11-15 | Method of manufacturing a semiconductor device that includes a process for forming a high breakdown voltage field effect transistor |

| US11/776,380 US7592669B2 (en) | 2003-11-14 | 2007-07-11 | Semiconductor device with MISFET that includes embedded insulating film arranged between source/drain regions and channel |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003384654A JP4707947B2 (ja) | 2003-11-14 | 2003-11-14 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006300395A Division JP4648286B2 (ja) | 2006-11-06 | 2006-11-06 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005150331A JP2005150331A (ja) | 2005-06-09 |

| JP2005150331A5 JP2005150331A5 (ja) | 2006-12-21 |

| JP4707947B2 true JP4707947B2 (ja) | 2011-06-22 |

Family

ID=34567341

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003384654A Expired - Fee Related JP4707947B2 (ja) | 2003-11-14 | 2003-11-14 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7259054B2 (ja) |

| JP (1) | JP4707947B2 (ja) |

| KR (1) | KR20050046568A (ja) |

| CN (2) | CN100440482C (ja) |

| TW (1) | TWI359492B (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7485925B2 (en) * | 2005-08-30 | 2009-02-03 | United Microelectronics Corp. | High voltage metal oxide semiconductor transistor and fabricating method thereof |

| JP4784738B2 (ja) * | 2005-10-21 | 2011-10-05 | セイコーエプソン株式会社 | 半導体装置 |

| JP4784739B2 (ja) * | 2005-10-21 | 2011-10-05 | セイコーエプソン株式会社 | 半導体装置 |

| JP4784737B2 (ja) * | 2005-10-21 | 2011-10-05 | セイコーエプソン株式会社 | 半導体装置 |

| US8530355B2 (en) * | 2005-12-23 | 2013-09-10 | Infineon Technologies Ag | Mixed orientation semiconductor device and method |

| US7687370B2 (en) * | 2006-01-27 | 2010-03-30 | Freescale Semiconductor, Inc. | Method of forming a semiconductor isolation trench |

| KR100817084B1 (ko) * | 2007-02-02 | 2008-03-26 | 삼성전자주식회사 | 고전압 트랜지스터 및 그 제조방법 |

| US8072035B2 (en) | 2007-06-11 | 2011-12-06 | Renesas Electronics Corporation | Semiconductor device and method of manufacturing the same |

| US8420488B2 (en) * | 2007-09-11 | 2013-04-16 | United Microelectronics Corp. | Method of fabricating high voltage device |

| KR100954907B1 (ko) * | 2007-12-21 | 2010-04-27 | 주식회사 동부하이텍 | 반도체 소자의 테스트 패턴 및 그 제조방법 |

| JP5239548B2 (ja) * | 2008-06-25 | 2013-07-17 | 富士通セミコンダクター株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP2010062182A (ja) * | 2008-09-01 | 2010-03-18 | Renesas Technology Corp | 半導体集積回路装置 |

| JP5147654B2 (ja) * | 2008-11-18 | 2013-02-20 | パナソニック株式会社 | 半導体装置 |

| KR20100064264A (ko) * | 2008-12-04 | 2010-06-14 | 주식회사 동부하이텍 | 반도체 소자 및 이의 제조 방법 |

| KR101606930B1 (ko) * | 2008-12-30 | 2016-03-28 | 주식회사 동부하이텍 | 반도체소자 및 그 제조방법 |

| CN101710586B (zh) * | 2009-01-09 | 2011-12-28 | 深超光电(深圳)有限公司 | 提高开口率的储存电容及其制作方法 |

| JP2011071325A (ja) * | 2009-09-25 | 2011-04-07 | Seiko Instruments Inc | 半導体装置 |

| JP2011096862A (ja) * | 2009-10-30 | 2011-05-12 | Hitachi Ltd | 半導体装置及びその製造方法 |

| US8222093B2 (en) * | 2010-02-17 | 2012-07-17 | GlobalFoundries, Inc. | Methods for forming barrier regions within regions of insulating material resulting in outgassing paths from the insulating material and related devices |

| JP5734725B2 (ja) | 2011-04-27 | 2015-06-17 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US8716768B2 (en) * | 2011-10-20 | 2014-05-06 | Omnivision Technologies, Inc. | Transistor with self-aligned channel width |

| JP5481526B2 (ja) * | 2012-06-13 | 2014-04-23 | ラピスセミコンダクタ株式会社 | 高耐圧電界効果トランジスタ |

| CN104425376A (zh) * | 2013-08-28 | 2015-03-18 | 北大方正集团有限公司 | Cmos管的制造方法及cmos管 |

| JP6341802B2 (ja) * | 2014-08-21 | 2018-06-13 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| US9831134B1 (en) | 2016-09-28 | 2017-11-28 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of manufacturing a semiconductor device having deep wells |

| JP7156811B2 (ja) * | 2018-03-26 | 2022-10-19 | ラピスセミコンダクタ株式会社 | 半導体装置及び半導体装置の製造方法 |

| CN110890421A (zh) * | 2018-09-10 | 2020-03-17 | 长鑫存储技术有限公司 | 半导体器件 |

| CN112825327B (zh) * | 2019-11-21 | 2024-10-01 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| CN112349733B (zh) * | 2020-09-09 | 2022-09-06 | 湖北长江新型显示产业创新中心有限公司 | 阵列基板、阵列基板的制造方法及显示装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001144189A (ja) * | 1999-11-17 | 2001-05-25 | Nec Ic Microcomput Syst Ltd | 半導体集積回路装置及びその製造方法 |

| JP2001313389A (ja) * | 2000-05-01 | 2001-11-09 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| JP2002170888A (ja) * | 2000-11-30 | 2002-06-14 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2002343964A (ja) * | 2001-05-18 | 2002-11-29 | Denso Corp | 半導体装置及びその製造方法 |

| JP2005136169A (ja) * | 2003-10-30 | 2005-05-26 | Seiko Epson Corp | 半導体装置およびその製造方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5047358A (en) * | 1989-03-17 | 1991-09-10 | Delco Electronics Corporation | Process for forming high and low voltage CMOS transistors on a single integrated circuit chip |

| US4918026A (en) * | 1989-03-17 | 1990-04-17 | Delco Electronics Corporation | Process for forming vertical bipolar transistors and high voltage CMOS in a single integrated circuit chip |

| US5306652A (en) * | 1991-12-30 | 1994-04-26 | Texas Instruments Incorporated | Lateral double diffused insulated gate field effect transistor fabrication process |

| JP3252569B2 (ja) * | 1993-11-09 | 2002-02-04 | 株式会社デンソー | 絶縁分離基板及びそれを用いた半導体装置及びその製造方法 |

| JP3275569B2 (ja) * | 1994-10-03 | 2002-04-15 | 富士電機株式会社 | 横型高耐圧電界効果トランジスタおよびその製造方法 |

| JPH08316464A (ja) * | 1995-05-19 | 1996-11-29 | Sony Corp | Mosトランジスタおよびその製造方法 |

| JPH09237829A (ja) * | 1996-03-01 | 1997-09-09 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JPH1065153A (ja) | 1996-08-15 | 1998-03-06 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JPH10189762A (ja) * | 1996-12-20 | 1998-07-21 | Nec Corp | 半導体装置およびその製造方法 |

| TW395024B (en) * | 1998-08-28 | 2000-06-21 | United Microelectronics Corp | The method to shape up a shallow trench for isolation in IC |

| US6063674A (en) * | 1998-10-28 | 2000-05-16 | United Microelectronics Corp. | Method for forming high voltage device |

| JP2001160623A (ja) | 1999-12-02 | 2001-06-12 | Nec Ic Microcomput Syst Ltd | 半導体装置とその製造方法 |

| US6528850B1 (en) * | 2000-05-03 | 2003-03-04 | Linear Technology Corporation | High voltage MOS transistor with up-retro well |

| US6501139B1 (en) * | 2001-03-30 | 2002-12-31 | Matrix Semiconductor, Inc. | High-voltage transistor and fabrication process |

| KR100363101B1 (ko) * | 2001-04-16 | 2002-12-05 | 페어차일드코리아반도체 주식회사 | 고내압 아이솔레이션 영역을 갖는 고전압 반도체 소자 |

| US7091535B2 (en) * | 2004-03-05 | 2006-08-15 | Taiwan Semiconductor Manufacturing Company | High voltage device embedded non-volatile memory cell and fabrication method |

-

2003

- 2003-11-14 JP JP2003384654A patent/JP4707947B2/ja not_active Expired - Fee Related

-

2004

- 2004-10-05 TW TW093130160A patent/TWI359492B/zh not_active IP Right Cessation

- 2004-11-10 CN CNB2006101431128A patent/CN100440482C/zh not_active Expired - Fee Related

- 2004-11-10 CN CNB2004100909345A patent/CN100463220C/zh not_active Expired - Fee Related

- 2004-11-11 KR KR1020040091812A patent/KR20050046568A/ko not_active Application Discontinuation

- 2004-11-15 US US10/986,896 patent/US7259054B2/en not_active Expired - Fee Related

-

2007

- 2007-07-11 US US11/776,380 patent/US7592669B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001144189A (ja) * | 1999-11-17 | 2001-05-25 | Nec Ic Microcomput Syst Ltd | 半導体集積回路装置及びその製造方法 |

| JP2001313389A (ja) * | 2000-05-01 | 2001-11-09 | Seiko Epson Corp | 半導体装置およびその製造方法 |

| JP2002170888A (ja) * | 2000-11-30 | 2002-06-14 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2002343964A (ja) * | 2001-05-18 | 2002-11-29 | Denso Corp | 半導体装置及びその製造方法 |

| JP2005136169A (ja) * | 2003-10-30 | 2005-05-26 | Seiko Epson Corp | 半導体装置およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100463220C (zh) | 2009-02-18 |

| US20050104098A1 (en) | 2005-05-19 |

| US7592669B2 (en) | 2009-09-22 |

| CN1617353A (zh) | 2005-05-18 |

| JP2005150331A (ja) | 2005-06-09 |

| TWI359492B (en) | 2012-03-01 |

| KR20050046568A (ko) | 2005-05-18 |

| US20080258236A1 (en) | 2008-10-23 |

| US7259054B2 (en) | 2007-08-21 |

| CN100440482C (zh) | 2008-12-03 |

| TW200527652A (en) | 2005-08-16 |

| CN1953159A (zh) | 2007-04-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4707947B2 (ja) | 半導体装置 | |

| JP5487304B2 (ja) | 半導体装置およびその製造方法 | |

| US8722522B2 (en) | Electro-static discharge protection device, semiconductor device, and method for manufacturing electro-static discharge protection device | |

| US7514749B2 (en) | Semiconductor device and a method of manufacturing the same | |

| KR102068395B1 (ko) | 낮은 소스-드레인 저항을 갖는 반도체 소자 구조 및 그 제조 방법 | |

| JP2006278633A (ja) | 半導体装置の製造方法 | |

| US20090166744A1 (en) | Semiconductor device with deep trench structure | |

| JP5211132B2 (ja) | 半導体装置 | |

| JP4648286B2 (ja) | 半導体装置の製造方法 | |

| US20110254096A1 (en) | Semiconductor device having non-silicide region in which no silicide is formed on diffusion layer | |

| JP2010177292A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP4761032B2 (ja) | 半導体装置 | |

| JP2003051552A (ja) | 半導体集積回路装置の製造方法 | |

| KR100944587B1 (ko) | 반도체 소자의 제조 방법 | |

| JP4791101B2 (ja) | 半導体集積回路装置 | |

| JP2008218948A (ja) | 半導体装置とその製造方法 | |

| KR20060054577A (ko) | 고내압 트랜지스터 및 이의 제조 방법 | |

| JP2013247140A (ja) | 半導体装置およびその製造方法 | |

| KR19990025213A (ko) | 엠엠엘 반도체소자 및 그 제조방법 | |

| JP2007042760A (ja) | 半導体装置 | |

| JPH04115537A (ja) | 半導体装置の製造方法 | |

| JP2007208073A (ja) | 半導体装置およびその製造方法 | |

| KR20040059381A (ko) | 반도체 메모리 소자의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080729 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100713 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100826 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110222 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110316 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4707947 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D03 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |