JP2010206174A - 光電変換装置およびその製造方法ならびにカメラ - Google Patents

光電変換装置およびその製造方法ならびにカメラ Download PDFInfo

- Publication number

- JP2010206174A JP2010206174A JP2009293213A JP2009293213A JP2010206174A JP 2010206174 A JP2010206174 A JP 2010206174A JP 2009293213 A JP2009293213 A JP 2009293213A JP 2009293213 A JP2009293213 A JP 2009293213A JP 2010206174 A JP2010206174 A JP 2010206174A

- Authority

- JP

- Japan

- Prior art keywords

- region

- type

- photoelectric conversion

- conversion device

- buried layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 13

- 238000009792 diffusion process Methods 0.000 claims abstract description 49

- 239000012535 impurity Substances 0.000 claims abstract description 36

- 239000004065 semiconductor Substances 0.000 claims description 34

- 239000000758 substrate Substances 0.000 claims description 29

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical group [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 28

- 238000006243 chemical reaction Methods 0.000 claims description 28

- 229910052698 phosphorus Inorganic materials 0.000 claims description 28

- 239000011574 phosphorus Substances 0.000 claims description 28

- 238000012546 transfer Methods 0.000 claims description 21

- 229910052785 arsenic Inorganic materials 0.000 claims description 19

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 claims description 19

- 238000012545 processing Methods 0.000 claims description 16

- 238000000034 method Methods 0.000 claims description 13

- 230000008569 process Effects 0.000 claims description 8

- 230000005465 channeling Effects 0.000 claims description 4

- 238000005468 ion implantation Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 42

- 238000003384 imaging method Methods 0.000 description 39

- 230000003321 amplification Effects 0.000 description 32

- 238000003199 nucleic acid amplification method Methods 0.000 description 32

- 238000002955 isolation Methods 0.000 description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 11

- 229910052710 silicon Inorganic materials 0.000 description 11

- 239000010703 silicon Substances 0.000 description 11

- 238000005036 potential barrier Methods 0.000 description 10

- 230000006870 function Effects 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000005247 gettering Methods 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14689—MOS based technologies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14641—Electronic components shared by two or more pixel-elements, e.g. one amplifier shared by two pixel elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

Abstract

【解決手段】光電変換装置は、n型の表面領域18と、表面領域18の下に形成されたp型領域PRと、p型領域PRの下に形成されたn型の埋め込み層10とを含む。表面領域18、p型領域PRおよび埋め込み層10によって埋め込み型のフォトダイオードPDが構成される。表面領域18の主要不純物の拡散係数は、埋め込み層10の主要不純物の拡散係数より小さい。

【選択図】図4

Description

Claims (9)

- n型の表面領域と、

前記表面領域の下に形成されたp型領域と、

前記p型領域の下に形成されたn型の埋め込み層とを含み、

前記表面領域、前記p型領域および前記埋め込み層によって埋め込み型のフォトダイオードが構成され、前記表面領域の主要不純物の拡散係数が前記埋め込み層の主要不純物の拡散係数より小さいことを特徴とする光電変換装置。 - 前記表面領域の主要不純物が砒素であり、前記埋め込み層の主要不純物が燐であることを特徴とする請求項1に記載の光電変換装置。

- 前記p型領域は、第1領域と、少なくとも一部が前記第1領域と前記埋め込み層との間に配置された第2領域とを含み、前記第1領域のp型不純物の濃度が前記第2領域のp型不純物の濃度よりも高いことを特徴とする請求項1又は2に記載の光電変換装置。

- 浮遊拡散部を構成するp型の第3領域と、

前記第1領域と前記第3領域との間の領域の上に配置されたゲートとを更に備え、

前記第1領域、前記第3領域および前記ゲートによって、前記p型領域に蓄積された正孔を前記浮遊拡散部に転送するための転送トランジスタが構成されていることを特徴とする請求項3に記載の光電変換装置。 - 前記第2領域と前記第3領域とを分離するn型領域を含み、前記n型領域に前記転送トランジスタのチャネルが形成されることを特徴とする請求項4に記載の光電変換装置。

- 前記埋め込み層は、チャネリング現象を利用したイオン注入によって形成されることを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

- 裏面照射型の光電変換装置として構成されていることを特徴とする請求項1乃至6のいずれか1項に記載の光電変換装置。

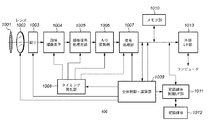

- 請求項1乃至7のいずれか1項に記載の光電変換装置と、

前記光電変換装置によって得られた信号を処理する信号処理部と、

を備えることを特徴とするカメラ。 - 請求項1乃至5のいずれか1項に記載の光電変換装置の製造方法であって、

p型の半導体基板の表面に前記埋め込み層を形成する工程と、

前記埋め込み層の上にp型の半導体層をエピタキシャル成長させる工程と、

前記半導体層の中に前記p型領域および前記表面領域を形成する工程と、

を含むことを特徴とする光電変換装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009293213A JP2010206174A (ja) | 2009-02-06 | 2009-12-24 | 光電変換装置およびその製造方法ならびにカメラ |

| US13/139,588 US8723285B2 (en) | 2009-02-06 | 2010-01-08 | Photoelectric conversion device manufacturing method thereof, and camera |

| PCT/JP2010/050450 WO2010090064A1 (en) | 2009-02-06 | 2010-01-08 | Photoelectric conversion device manufacturing method thereof, and camera |

| CN201080006235.1A CN102301476B (zh) | 2009-02-06 | 2010-01-08 | 光电转换装置、其制造方法和照相机 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009026701 | 2009-02-06 | ||

| JP2009293213A JP2010206174A (ja) | 2009-02-06 | 2009-12-24 | 光電変換装置およびその製造方法ならびにカメラ |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014233999A Division JP2015084425A (ja) | 2009-02-06 | 2014-11-18 | 光電変換装置およびその製造方法ならびにカメラ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010206174A true JP2010206174A (ja) | 2010-09-16 |

| JP2010206174A5 JP2010206174A5 (ja) | 2013-02-21 |

Family

ID=42062304

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009293213A Pending JP2010206174A (ja) | 2009-02-06 | 2009-12-24 | 光電変換装置およびその製造方法ならびにカメラ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8723285B2 (ja) |

| JP (1) | JP2010206174A (ja) |

| CN (1) | CN102301476B (ja) |

| WO (1) | WO2010090064A1 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8546174B2 (en) | 2011-03-25 | 2013-10-01 | Kabushiki Kaisha Toshiba | Method for manufacturing semiconductor device |

| JP2013203980A (ja) * | 2012-03-29 | 2013-10-07 | Japan Polyethylene Corp | 圧力容器ライナー用熱可塑性樹脂、圧力容器及びその製造方法 |

| WO2014002362A1 (ja) * | 2012-06-26 | 2014-01-03 | パナソニック株式会社 | 固体撮像装置及びその製造方法 |

| JP2014022463A (ja) * | 2012-07-13 | 2014-02-03 | Toshiba Corp | 固体撮像装置 |

| JP2016092137A (ja) * | 2014-10-31 | 2016-05-23 | キヤノン株式会社 | 撮像装置 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010206172A (ja) | 2009-02-06 | 2010-09-16 | Canon Inc | 撮像装置およびカメラ |

| JP2010206173A (ja) | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置およびカメラ |

| US8742311B2 (en) * | 2012-02-27 | 2014-06-03 | Omnivision Technologies, Inc. | Enhanced pixel cell architecture for an image sensor having a direct output from a buried channel source follower transistor to a bit line |

| US8883544B2 (en) * | 2012-05-04 | 2014-11-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming an image device |

| JP6118053B2 (ja) * | 2012-09-06 | 2017-04-19 | キヤノン株式会社 | 固体撮像装置の製造方法 |

| JP6159184B2 (ja) * | 2013-07-25 | 2017-07-05 | キヤノン株式会社 | 光電変換装置及び撮像システム |

| JP2015109343A (ja) * | 2013-12-04 | 2015-06-11 | キヤノン株式会社 | 半導体装置の製造方法 |

| JP2020088293A (ja) * | 2018-11-29 | 2020-06-04 | キヤノン株式会社 | 光電変換装置、光電変換システム、移動体 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0738140A (ja) * | 1993-07-19 | 1995-02-07 | Hamamatsu Photonics Kk | アバランシェホトダイオード |

| JP2004103704A (ja) * | 2002-09-06 | 2004-04-02 | Sharp Corp | 半導体受光装置およびこれを備えた光学装置 |

| JP2006108485A (ja) * | 2004-10-07 | 2006-04-20 | Sanyo Electric Co Ltd | 固体撮像装置 |

| JP2007109818A (ja) * | 2005-10-12 | 2007-04-26 | Sharp Corp | 固体撮像装置およびその製造方法、電子情報機器 |

| US20070108371A1 (en) * | 2005-11-16 | 2007-05-17 | Eastman Kodak Company | PMOS pixel structure with low cross talk for active pixel image sensors |

| JP2007201088A (ja) * | 2006-01-25 | 2007-08-09 | Fujifilm Corp | 固体撮像素子 |

| JP2008066480A (ja) * | 2006-09-06 | 2008-03-21 | Sharp Corp | 固体撮像素子および電子情報機器 |

Family Cites Families (90)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4549914A (en) | 1984-04-09 | 1985-10-29 | At&T Bell Laboratories | Integrated circuit contact technique |

| JP2662061B2 (ja) | 1989-12-15 | 1997-10-08 | キヤノン株式会社 | 光電変換装置 |

| EP0510604A3 (en) | 1991-04-23 | 2001-05-09 | Canon Kabushiki Kaisha | Semiconductor device and method of manufacturing the same |

| US6482719B1 (en) | 1994-06-03 | 2002-11-19 | Advanced Micro Devices, Inc. | Semiconductor field region implant methodology |

| JPH08130246A (ja) | 1994-10-28 | 1996-05-21 | Ricoh Co Ltd | 半導体装置とその製造方法 |

| JP3292657B2 (ja) | 1995-04-10 | 2002-06-17 | キヤノン株式会社 | 薄膜トランジスタ及びそれを用いた液晶表示装置の製造法 |

| US5614744A (en) | 1995-08-04 | 1997-03-25 | National Semiconductor Corporation | CMOS-based, low leakage active pixel array with anti-blooming isolation |

| US5864163A (en) | 1995-12-27 | 1999-01-26 | United Microelectrics Corp. | Fabrication of buried channel devices with shallow junction depth |

| JP3248470B2 (ja) | 1997-11-21 | 2002-01-21 | 日本電気株式会社 | 電荷転送装置および電荷転送装置の製造方法 |

| US6188106B1 (en) | 1998-09-03 | 2001-02-13 | Advanced Micro Devices, Inc. | MOSFET having a highly doped channel liner and a dopant seal to provide enhanced device properties |

| CN1159576C (zh) | 1999-05-10 | 2004-07-28 | 三星电子株式会社 | 制造磁共振成像系统用的主磁体总成的方法 |

| JP2000349096A (ja) | 1999-06-01 | 2000-12-15 | Matsushita Electric Ind Co Ltd | 化合物電界効果トランジスタおよびその製造方法 |

| WO2001026143A1 (fr) | 1999-10-04 | 2001-04-12 | Matsushita Eletric Industrial Co., Ltd. | Procédé de fabrication d'un dispositif à semi-conducteur |

| US20030235936A1 (en) | 1999-12-16 | 2003-12-25 | Snyder John P. | Schottky barrier CMOS device and method |

| WO2001067518A1 (en) | 2000-03-09 | 2001-09-13 | Koninklijke Philips Electronics N.V. | Solid state imaging sensor in a submicron technology and method of manufacturing and use of a solid state imaging sensor |

| AU2001244586A1 (en) | 2000-04-04 | 2001-10-15 | Hamamatsu Photonics K.K. | Semiconductor energy detector |

| TWI230392B (en) | 2001-06-18 | 2005-04-01 | Innovative Silicon Sa | Semiconductor device |

| JP3530159B2 (ja) | 2001-08-22 | 2004-05-24 | 松下電器産業株式会社 | 固体撮像装置およびその製造方法 |

| US6465768B1 (en) | 2001-08-22 | 2002-10-15 | United Microelectronics Corp. | MOS structure with improved substrate-triggered effect for on-chip ESD protection |

| US6784500B2 (en) | 2001-08-31 | 2004-08-31 | Analog Devices, Inc. | High voltage integrated circuit amplifier |

| JP4269033B2 (ja) | 2002-03-05 | 2009-05-27 | シャープ株式会社 | 受光素子及びその製造方法、並びに、回路内蔵型受光素子及びその製造方法 |

| JP3702854B2 (ja) * | 2002-03-06 | 2005-10-05 | ソニー株式会社 | 固体撮像素子 |

| US6965102B1 (en) | 2002-04-05 | 2005-11-15 | Foveon, Inc. | Large dynamic range, low-leakage vertical color pixel sensor |

| US6974737B2 (en) | 2002-05-16 | 2005-12-13 | Spinnaker Semiconductor, Inc. | Schottky barrier CMOS fabrication method |

| JP2004087089A (ja) | 2002-06-27 | 2004-03-18 | Sharp Corp | 光ピックアップ |

| JP2004039832A (ja) | 2002-07-03 | 2004-02-05 | Sony Corp | 光電変換装置及びその製造方法 |

| US6750489B1 (en) | 2002-10-25 | 2004-06-15 | Foveon, Inc. | Isolated high voltage PMOS transistor |

| JP2004165462A (ja) | 2002-11-14 | 2004-06-10 | Sony Corp | 固体撮像素子及びその製造方法 |

| JP4122960B2 (ja) | 2002-12-16 | 2008-07-23 | ソニー株式会社 | 固体撮像素子 |

| JP4155568B2 (ja) | 2003-08-07 | 2008-09-24 | キヤノン株式会社 | 固体撮像装置及びカメラ |

| JP2005072236A (ja) | 2003-08-25 | 2005-03-17 | Renesas Technology Corp | 半導体装置および半導体装置の製造方法 |

| JP2005150521A (ja) | 2003-11-18 | 2005-06-09 | Canon Inc | 撮像装置およびその製造方法 |

| JP4439888B2 (ja) * | 2003-11-27 | 2010-03-24 | イノテック株式会社 | Mos型固体撮像装置及びその駆動方法 |

| US7323731B2 (en) | 2003-12-12 | 2008-01-29 | Canon Kabushiki Kaisha | Photoelectric conversion device, method of manufacturing photoelectric conversion device, and image pickup system |

| KR100618820B1 (ko) | 2004-02-10 | 2006-09-12 | 삼성전자주식회사 | Pn 접합에 의해 분리된 수광부를 갖는 포토다이오드 및 그의 제조방법 |

| US7310404B2 (en) | 2004-03-24 | 2007-12-18 | Canon Kabushiki Kaisha | Radiation CT radiographing device, radiation CT radiographing system, and radiation CT radiographing method using the same |

| JP5224633B2 (ja) | 2004-03-30 | 2013-07-03 | キヤノン株式会社 | 半導体装置の製造方法 |

| WO2005109512A1 (en) | 2004-05-06 | 2005-11-17 | Canon Kabushiki Kaisha | Photoelectric conversion device and manufacturing method thereof |

| US7540198B2 (en) | 2004-06-15 | 2009-06-02 | Canon Kabushiki Kaisha | Semiconductor device |

| US7898010B2 (en) | 2004-07-01 | 2011-03-01 | Micron Technology, Inc. | Transparent conductor based pinned photodiode |

| KR100577312B1 (ko) | 2004-07-05 | 2006-05-10 | 동부일렉트로닉스 주식회사 | 씨모스 이미지 센서의 포토트랜지스터 및 그 제조 방법 |

| JP4739706B2 (ja) | 2004-07-23 | 2011-08-03 | 富士フイルム株式会社 | 固体撮像素子及びその製造方法 |

| JP4513497B2 (ja) | 2004-10-19 | 2010-07-28 | ソニー株式会社 | 固体撮像装置 |

| US8120077B2 (en) | 2004-12-16 | 2012-02-21 | Panasonic Corporation | Solid-state imaging device comprising doped channel stop at isolation regions to suppress noise |

| KR100672704B1 (ko) | 2004-12-30 | 2007-01-22 | 동부일렉트로닉스 주식회사 | 시모스 이미지 센서 및 그 제조방법 |

| JP4686201B2 (ja) | 2005-01-27 | 2011-05-25 | パナソニック株式会社 | 固体撮像装置及びその製造方法 |

| KR100657863B1 (ko) | 2005-02-07 | 2006-12-14 | 삼성전자주식회사 | 핑거드 타입 소스 폴로워 트랜지스터를 이용한 상보성금속 산화막 반도체 액티브 픽셀 센서 |

| TWI302754B (en) * | 2005-02-28 | 2008-11-01 | Magnachip Semiconductor Ltd | Complementary metal-oxide-semiconductor image sensor and method for fabricating the same |

| CN100536151C (zh) | 2005-03-11 | 2009-09-02 | 富士通微电子株式会社 | 具有嵌入式光电二极管区域的图像传感器及其制造方法 |

| KR100690884B1 (ko) * | 2005-04-28 | 2007-03-09 | 삼성전자주식회사 | 이미지 센서 및 그 제조 방법 |

| US8018015B2 (en) | 2005-06-29 | 2011-09-13 | Micron Technology, Inc. | Buried conductor for imagers |

| KR100746222B1 (ko) | 2005-07-11 | 2007-08-03 | 삼성전자주식회사 | 이미지 센서의 제조방법들 |

| US20070023796A1 (en) * | 2005-07-27 | 2007-02-01 | International Business Machines Corporation | Pinning layer for pixel sensor cell and method thereof |

| JP2007073544A (ja) | 2005-09-02 | 2007-03-22 | Matsushita Electric Ind Co Ltd | 固体撮像装置およびその製造方法 |

| US7423302B2 (en) | 2005-11-21 | 2008-09-09 | Digital Imaging Systems Gmbh | Pinned photodiode (PPD) pixel with high shutter rejection ratio for snapshot operating CMOS sensor |

| KR100761829B1 (ko) | 2005-12-15 | 2007-09-28 | 삼성전자주식회사 | 반도체 소자, 시모스 이미지 센서, 반도체 소자의 제조방법및 시모스 이미지 센서의 제조방법 |

| KR100660333B1 (ko) | 2005-12-28 | 2006-12-22 | 동부일렉트로닉스 주식회사 | Cmos 이미지 센서의 제조방법 |

| KR100660348B1 (ko) | 2005-12-28 | 2006-12-22 | 동부일렉트로닉스 주식회사 | Cmos 이미지 센서의 제조방법 |

| US7544533B2 (en) | 2006-01-09 | 2009-06-09 | Aptina Imaging Corporation | Method and apparatus for providing an integrated circuit having p and n doped gates |

| JP2007305925A (ja) | 2006-05-15 | 2007-11-22 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP5116264B2 (ja) | 2006-07-10 | 2013-01-09 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法および光電変換装置を用いた撮像システム |

| JP5110820B2 (ja) | 2006-08-02 | 2012-12-26 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法及び撮像システム |

| KR100837271B1 (ko) | 2006-08-10 | 2008-06-12 | 삼성전자주식회사 | 반도체 장치 및 그 제조방법 |

| JP5305622B2 (ja) | 2006-08-31 | 2013-10-02 | キヤノン株式会社 | 光電変換装置の製造方法 |

| JP2008153566A (ja) | 2006-12-20 | 2008-07-03 | Matsushita Electric Ind Co Ltd | 固体撮像装置及びその製造方法 |

| JP4137161B1 (ja) | 2007-02-23 | 2008-08-20 | キヤノン株式会社 | 光電変換装置の製造方法 |

| US7459668B2 (en) | 2007-03-06 | 2008-12-02 | Micron Technology, Inc. | Method, apparatus, and system to reduce ground resistance in a pixel array |

| US7915702B2 (en) | 2007-03-15 | 2011-03-29 | Eastman Kodak Company | Reduced pixel area image sensor |

| US7812339B2 (en) | 2007-04-23 | 2010-10-12 | Mears Technologies, Inc. | Method for making a semiconductor device including shallow trench isolation (STI) regions with maskless superlattice deposition following STI formation and related structures |

| JP5157259B2 (ja) | 2007-05-29 | 2013-03-06 | ソニー株式会社 | 固体撮像素子及び撮像装置 |

| KR100870821B1 (ko) * | 2007-06-29 | 2008-11-27 | 매그나칩 반도체 유한회사 | 후면 조사 이미지 센서 |

| JP4944699B2 (ja) | 2007-07-23 | 2012-06-06 | パナソニック株式会社 | キーユニット、キーユニット背板の製造方法及び携帯電話 |

| JP2009124514A (ja) | 2007-11-15 | 2009-06-04 | Sony Corp | 固体撮像素子、およびカメラシステム |

| JP5366396B2 (ja) | 2007-12-28 | 2013-12-11 | キヤノン株式会社 | 光電変換装置の製造方法、半導体装置の製造方法、光電変換装置、及び撮像システム |

| US20090201400A1 (en) | 2008-02-08 | 2009-08-13 | Omnivision Technologies, Inc. | Backside illuminated image sensor with global shutter and storage capacitor |

| JP4630907B2 (ja) | 2008-03-03 | 2011-02-09 | シャープ株式会社 | 固体撮像装置および電子情報機器 |

| JP5178266B2 (ja) | 2008-03-19 | 2013-04-10 | キヤノン株式会社 | 固体撮像装置 |

| JP4618342B2 (ja) | 2008-05-20 | 2011-01-26 | 日本テキサス・インスツルメンツ株式会社 | 固体撮像装置 |

| JP5407082B2 (ja) | 2008-06-03 | 2014-02-05 | 住友ゴム工業株式会社 | 建物 |

| US8618458B2 (en) * | 2008-11-07 | 2013-12-31 | Omnivision Technologies, Inc. | Back-illuminated CMOS image sensors |

| US7838956B2 (en) | 2008-12-17 | 2010-11-23 | Eastman Kodak Company | Back illuminated sensor with low crosstalk |

| JP2010206172A (ja) | 2009-02-06 | 2010-09-16 | Canon Inc | 撮像装置およびカメラ |

| JP5538922B2 (ja) | 2009-02-06 | 2014-07-02 | キヤノン株式会社 | 固体撮像装置の製造方法 |

| JP2010206173A (ja) | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置およびカメラ |

| JP5451098B2 (ja) | 2009-02-06 | 2014-03-26 | キヤノン株式会社 | 半導体装置の製造方法 |

| JP4832541B2 (ja) * | 2009-03-17 | 2011-12-07 | シャープ株式会社 | 固体撮像素子および電子情報機器 |

| JP5515434B2 (ja) | 2009-06-03 | 2014-06-11 | ソニー株式会社 | 半導体装置及びその製造方法、固体撮像素子 |

| US8294802B2 (en) | 2009-10-30 | 2012-10-23 | Truesense Imaging, Inc. | CCD image sensors having multiple lateral overflow drain regions for a horizontal shift register |

| JP5564909B2 (ja) | 2009-11-30 | 2014-08-06 | ソニー株式会社 | 固体撮像装置とその製造方法、及び電子機器 |

| JP5489855B2 (ja) | 2010-05-14 | 2014-05-14 | キヤノン株式会社 | 固体撮像装置の製造方法 |

-

2009

- 2009-12-24 JP JP2009293213A patent/JP2010206174A/ja active Pending

-

2010

- 2010-01-08 WO PCT/JP2010/050450 patent/WO2010090064A1/en active Application Filing

- 2010-01-08 CN CN201080006235.1A patent/CN102301476B/zh not_active Expired - Fee Related

- 2010-01-08 US US13/139,588 patent/US8723285B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0738140A (ja) * | 1993-07-19 | 1995-02-07 | Hamamatsu Photonics Kk | アバランシェホトダイオード |

| JP2004103704A (ja) * | 2002-09-06 | 2004-04-02 | Sharp Corp | 半導体受光装置およびこれを備えた光学装置 |

| JP2006108485A (ja) * | 2004-10-07 | 2006-04-20 | Sanyo Electric Co Ltd | 固体撮像装置 |

| JP2007109818A (ja) * | 2005-10-12 | 2007-04-26 | Sharp Corp | 固体撮像装置およびその製造方法、電子情報機器 |

| US20070108371A1 (en) * | 2005-11-16 | 2007-05-17 | Eastman Kodak Company | PMOS pixel structure with low cross talk for active pixel image sensors |

| JP2007201088A (ja) * | 2006-01-25 | 2007-08-09 | Fujifilm Corp | 固体撮像素子 |

| JP2008066480A (ja) * | 2006-09-06 | 2008-03-21 | Sharp Corp | 固体撮像素子および電子情報機器 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8546174B2 (en) | 2011-03-25 | 2013-10-01 | Kabushiki Kaisha Toshiba | Method for manufacturing semiconductor device |

| JP2013203980A (ja) * | 2012-03-29 | 2013-10-07 | Japan Polyethylene Corp | 圧力容器ライナー用熱可塑性樹脂、圧力容器及びその製造方法 |

| WO2014002362A1 (ja) * | 2012-06-26 | 2014-01-03 | パナソニック株式会社 | 固体撮像装置及びその製造方法 |

| JP2014022463A (ja) * | 2012-07-13 | 2014-02-03 | Toshiba Corp | 固体撮像装置 |

| JP2016092137A (ja) * | 2014-10-31 | 2016-05-23 | キヤノン株式会社 | 撮像装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102301476B (zh) | 2014-10-15 |

| US8723285B2 (en) | 2014-05-13 |

| WO2010090064A1 (en) | 2010-08-12 |

| CN102301476A (zh) | 2011-12-28 |

| US20110240835A1 (en) | 2011-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8953076B2 (en) | Photoelectric conversion device and camera having a photodiode cathode formed by an n-type buried layer | |

| JP5451098B2 (ja) | 半導体装置の製造方法 | |

| US11729530B2 (en) | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus | |

| KR101272423B1 (ko) | 화상 감지 디바이스 및 카메라 | |

| US8723285B2 (en) | Photoelectric conversion device manufacturing method thereof, and camera | |

| US8872949B2 (en) | Solid-state image pickup device, image pickup system including the same, and method for manufacturing the same | |

| JP5723094B2 (ja) | 固体撮像装置およびカメラ | |

| JP2011114302A (ja) | 半導体素子の製造方法及び半導体素子、並びに固体撮像素子及び固体撮像装置 | |

| WO2021117523A1 (ja) | 固体撮像素子及び電子機器 | |

| JP2015084425A (ja) | 光電変換装置およびその製造方法ならびにカメラ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140214 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140327 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140818 |