JP2005072236A - 半導体装置および半導体装置の製造方法 - Google Patents

半導体装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005072236A JP2005072236A JP2003299750A JP2003299750A JP2005072236A JP 2005072236 A JP2005072236 A JP 2005072236A JP 2003299750 A JP2003299750 A JP 2003299750A JP 2003299750 A JP2003299750 A JP 2003299750A JP 2005072236 A JP2005072236 A JP 2005072236A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- photodiode

- semiconductor device

- insulating film

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

Abstract

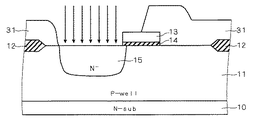

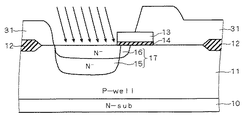

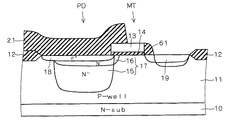

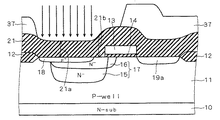

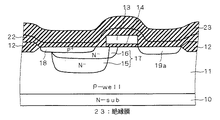

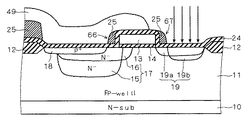

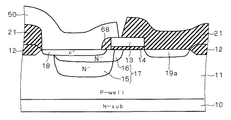

【解決手段】フォトダイオードPDのカソード、および、MOSトランジスタMTのソースとして機能するN型拡散領域17を、比較的深い第1拡散層15および比較的浅い第2拡散層16の2つの拡散層で構成する。第2拡散層16は、ゲート電極13と一部が重なるように形成される。この構造により、N型拡散領域17からチャネルへの電荷の転送経路を、表面シールド領域18が狭めることが無くなる。また、第2拡散層16は、質量数の比較的小さい不純物の注入により形成される。このため、第2拡散層16の形成時に不純物が広範囲に拡散するため、第2拡散層16がゲート電極13と重なる部分を比較的大きくすることができ、電荷の転送効率を向上できる。

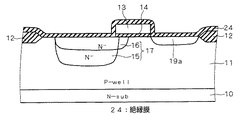

【選択図】図2

Description

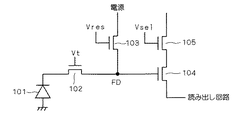

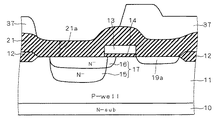

図1は、本発明の実施の形態1に係る半導体装置であるCMOSイメージセンサの1画素の構成を示す回路図である。図1に示すように、CMOSイメージセンサの1画素は、フォトダイオード101と、フォトダイオード101で発生した電荷をノードFDに転送するための転送MOSトランジスタ102と、フォトダイオード101およびノードFDの電位をリセットするためのリセットMOSトランジスタ103と、ノードFDの電位を増幅するためのソースフォロアMOSトランジスタ104と、読み出し行を選択するための選択MOSトランジスタ105とを備えて構成されている。

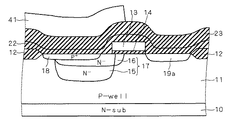

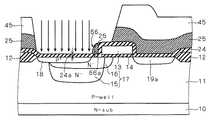

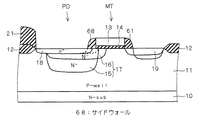

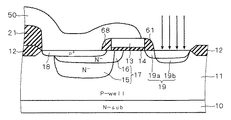

次に、実施の形態2について説明する。実施の形態2に係る半導体装置であるCMOSイメージセンサの1画素の回路図は、図1に示した回路図と同様である。図11は、実施の形態2に係るCMOSイメージセンサのうち、フォトダイオード101および転送MOSトランジスタ102が形成されている部分の断面構造を示す図である。なお、実施の形態1に係る半導体装置と同様の機能を有する要素については同一符号を付している。

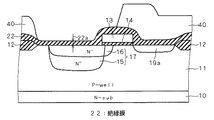

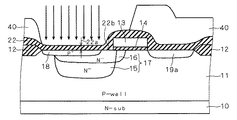

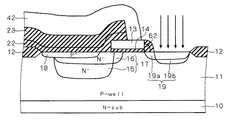

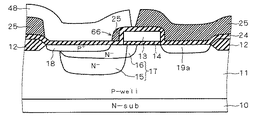

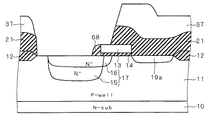

次に、実施の形態3について説明する。実施の形態3に係る半導体装置であるCMOSイメージセンサの1画素の回路図は、図1に示した回路図と同様である。図14は、実施の形態3に係るCMOSイメージセンサのうち、フォトダイオード101および転送MOSトランジスタ102が形成されている部分の断面構造を示す図である。なお、実施の形態1に係る半導体装置と同様の機能を有する要素については同一符号を付している。

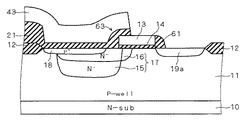

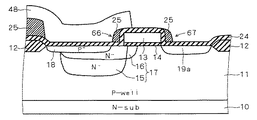

次に、実施の形態4について説明する。本実施の形態は、表面シールド領域18がゲート電極13から離間した構造の半導体装置を得るための製造方法の他の一例である。

次に、実施の形態5について説明する。本実施の形態は、表面シールド領域18がゲート電極13から離間した構造の半導体装置を得るための製造方法の他の一例である。

次に、実施の形態6について説明する。本実施の形態は、表面シールド領域18がゲート電極13から離間した構造の半導体装置を得るための製造方法の他の一例である。

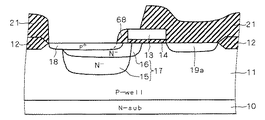

次に、実施の形態7について説明する。本実施の形態は、表面シールド領域18がゲート電極13から離間した構造の半導体装置を得るための製造方法の他の一例である。

次に、実施の形態8について説明する。実施の形態8に係る半導体装置であるCMOSイメージセンサの1画素の回路図は、図1に示した回路図と同様である。図48は、実施の形態8に係るCMOSイメージセンサのうち、フォトダイオード101および転送MOSトランジスタ102が形成されている部分の断面構造を示す図である。なお、実施の形態1に係る半導体装置と同様の機能を有する要素については同一符号を付している。

以上、本発明の実施の形態について説明してきたが、この発明は上記実施の形態に限定されるものではなく様々な変形が可能である。

Claims (15)

- 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置であって、

前記基板の主面上に形成された前記トランジスタのゲート電極と、

前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、前記基板の主面内に形成された第1導電型の拡散領域と、

前記拡散領域の上部の前記基板の主面内に形成された第2導電型の表面シールド領域と、

を備え、

前記拡散領域は、

第1不純物の注入により形成された第1拡散層と、

前記第1不純物よりも質量数の小さい第2不純物の注入により、前記第1拡散層よりも浅く、かつ、前記基板の深さ方向において前記ゲート電極と一部が重なるように形成された第2拡散層と、

を備えることを特徴とする半導体装置。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置であって、

前記基板の主面上に形成された前記トランジスタのゲート電極と、

前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、前記基板の主面内に形成された第1導電型の拡散領域と、

前記拡散領域の上部の前記基板の主面内に形成された第2導電型の表面シールド領域と、

を備え、

前記拡散領域は、

第1不純物の注入により形成された第1拡散層と、

前記第1不純物よりも質量数の大きい第2不純物の注入により、前記第1拡散層よりも浅く、かつ、前記基板の深さ方向において前記ゲート電極と一部が重なるように形成された第2拡散層と、

を備えることを特徴とする半導体装置。 - 請求項1または2に記載の半導体装置において、

前記表面シールド領域は、前記ゲート電極から離間していることを特徴とする半導体装置。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置であって、

前記基板の主面上に形成され、前記フォトダイオード側にサイドウォールが配置された前記トランジスタのゲート電極と、

前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、前記基板の主面内に形成された第1導電型の拡散領域と、

前記拡散領域の上部の前記基板の主面内に、前記ゲート電極から離間して形成された第2導電型の表面シールド領域と、

を備え、

前記表面シールド領域の前記ゲート電極側の端部は、前記サイドウォールの下部に位置することを特徴とする半導体装置。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置の製造方法であって、

(a)前記基板の主面上に、前記トランジスタのゲート電極を形成する工程と、

(b)前記基板の主面内に、前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、第1導電型の拡散領域を形成する工程と、

(c)前記工程(b)において生じた前記基板の結晶欠陥を、熱処理によって回復する工程と、

(d)前記拡散領域の上部の前記基板の主面内に、第2導電型の表面シールド領域を形成する工程と、

を備え、

前記工程(b)は、

(b−1)第1不純物を注入して、第1拡散層を形成する工程と、

(b−2)第2不純物を注入して、前記第1拡散層よりも浅く、かつ、前記基板の深さ方向において前記ゲート電極と一部が重なるように第2拡散層を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。 - 請求項5に記載の半導体装置の製造方法において、

前記第2不純物は、前記第1不純物よりも質量数が小さいことを特徴とする半導体装置の製造方法。 - 請求項5に記載の半導体装置の製造方法において、

前記第2不純物は、前記第1不純物よりも質量数が大きいことを特徴とする半導体装置の製造方法。 - 請求項7に記載の半導体装置の製造方法において、

前記工程(b)は、

前記工程(b−2)、前記工程(b−1)の順に実行されることを特徴とする半導体装置の製造方法。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置の製造方法であって、

(a)前記基板の主面上に、前記トランジスタのゲート電極を形成する工程と、

(b)前記基板の主面内に、前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、第1導電型の拡散領域を形成する工程と、

(c)前記フォトダイオードの形成予定領域上の膜厚が所定の第1膜厚となるように、前記基板の主面上の全面に第1絶縁膜を堆積する工程と、

(d)前記第1絶縁膜の前記第1膜厚を突き抜けるには十分で、前記ゲート電極のサイドに堆積した前記第1絶縁膜の第2膜厚を突き抜けるには不十分なエネルギーで不純物を注入して、前記拡散領域の上部の前記基板の主面内に第2導電型の表面シールド領域を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。 - 請求項9に記載の半導体装置の製造方法において、

(e)前記工程(d)の後に、前記第1絶縁膜に対してエッチングを行い、前記ゲート電極にサイドウォールを形成する工程、

をさらに備えることを特徴とする半導体装置の製造方法。 - 請求項9に記載の半導体装置の製造方法において、

(e)前記工程(d)の後に、前記第1絶縁膜上の全面に、第2絶縁膜をさらに堆積する工程と、

(f)前記第1および第2絶縁膜の双方に対してエッチングを行い、前記ゲート電極にサイドウォールを形成する工程と、

をさらに備えることを特徴とする半導体装置の製造方法。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置の製造方法であって、

(a)前記基板の主面上に、前記トランジスタのゲート電極を形成する工程と、

(b)前記基板の主面内に、前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、第1導電型の拡散領域を形成する工程と、

(c)前記基板の主面上の全面に絶縁膜を堆積する工程と、

(d)前記フォトダイオードの形成予定領域上の膜厚が所定の第1膜厚となるまで、前記絶縁膜に対してエッチングを行う工程と、

(e)前記絶縁膜の前記第1膜厚を突き抜けるには十分で、前記ゲート電極のサイドに堆積した前記絶縁膜の第2膜厚を突き抜けるには不十分なエネルギーで不純物を注入して、前記拡散領域の上部の前記基板の主面内に第2導電型の表面シールド領域を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置の製造方法であって、

(a)前記基板の主面上に、前記トランジスタのゲート電極を形成する工程と、

(b)前記基板の主面内に、前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、第1導電型の拡散領域を形成する工程と、

(c)前記基板の主面上の全面に第1絶縁膜を堆積する工程と、

(d)前記第1絶縁膜上の全面に、前記第1絶縁膜と阻止能が相違する第2絶縁膜をさらに堆積する工程と、

(f)前記第1および第2絶縁膜の双方に対してエッチングを行い、前記ゲート電極の前記フォトダイオードの形成予定領域側に、前記第1および第2絶縁膜を構成要素として含むサイドウォールを形成する工程と、

(g)前記サイドウォールを注入マスクの一部として用いて不純物を注入して、前記拡散領域の上部の前記基板の主面内に第2導電型の表面シールド領域を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。 - 基板と、フォトダイオードと、前記フォトダイオードの電荷を転送するトランジスタとを有する半導体装置の製造方法であって、

(a)前記基板の主面上に、前記トランジスタのゲート電極を形成する工程と、

(b)前記基板の主面内に、前記フォトダイオードの一の電極、かつ、前記トランジスタの一の電極として機能する、第1導電型の拡散領域を形成する工程と、

(c)前記基板の主面上の全面に第1絶縁膜を堆積する工程と、

(d)前記第1絶縁膜上の全面に、前記第1絶縁膜と阻止能が相違する第2絶縁膜をさらに堆積する工程と、

(f)前記フォトダイオードの形成予定領域上の前記第1絶縁膜の膜厚が所定の第1膜厚となるまで、前記第1および第2絶縁膜の双方に対してエッチングを行い、前記ゲート電極の前記フォトダイオードの形成予定領域側に、前記第1および第2絶縁膜を構成要素として含むサイドウォールを形成する工程と、

(g)前記第1絶縁膜の前記第1膜厚を突き抜けるには十分で、前記サイドウォールの第2膜厚を突き抜けるには不十分なエネルギーで不純物を注入して、前記拡散領域の上部の前記基板の主面内に第2導電型の表面シールド領域を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。 - 請求項14に記載の半導体装置の製造方法において、

前記工程(f)においては、前記第1絶縁膜よりも前記第2絶縁膜のほうがエッチングレートが高いことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003299750A JP2005072236A (ja) | 2003-08-25 | 2003-08-25 | 半導体装置および半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003299750A JP2005072236A (ja) | 2003-08-25 | 2003-08-25 | 半導体装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005072236A true JP2005072236A (ja) | 2005-03-17 |

| JP2005072236A5 JP2005072236A5 (ja) | 2006-09-21 |

Family

ID=34404878

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003299750A Pending JP2005072236A (ja) | 2003-08-25 | 2003-08-25 | 半導体装置および半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005072236A (ja) |

Cited By (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1648035A1 (en) * | 2004-10-15 | 2006-04-19 | OmniVision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| KR100679855B1 (ko) | 2005-05-02 | 2007-02-07 | (주) 픽셀플러스 | 암전류 억제를 위한 이미지 센서의 단위픽셀 및 그제조방법 |

| JP2007109818A (ja) * | 2005-10-12 | 2007-04-26 | Sharp Corp | 固体撮像装置およびその製造方法、電子情報機器 |

| KR100772316B1 (ko) | 2006-04-28 | 2007-10-31 | 매그나칩 반도체 유한회사 | 플라즈마손상으로부터 포토다이오드를 보호하는 씨모스이미지센서의 제조 방법 |

| FR2910713A1 (fr) * | 2006-12-26 | 2008-06-27 | St Microelectronics Sa | Photodiode verrouillee a grande capacite de stockage, par exemple pour un capteur d'image, procede de realisation associe, et capteur d'image comprenant une telle diode. |

| JP2008263041A (ja) * | 2007-04-11 | 2008-10-30 | Sharp Corp | 半導体装置の製造方法、半導体装置、固体撮像素子、mosトランジスタおよび電子情報機器 |

| CN100463141C (zh) * | 2005-06-07 | 2009-02-18 | 东部电子有限公司 | 制造cmos图像传感器的方法 |

| JP2010518629A (ja) * | 2007-02-07 | 2010-05-27 | フォベオン・インコーポレーテッド | ピン止めフォトダイオードcmos画素センサ |

| JP2010147193A (ja) * | 2008-12-17 | 2010-07-01 | Sharp Corp | 固体撮像装置およびその製造方法、並びに電子情報機器 |

| JP2010161236A (ja) * | 2009-01-08 | 2010-07-22 | Canon Inc | 光電変換装置の製造方法 |

| JP2010206178A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置、及び光電変換装置の製造方法 |

| JP2010206172A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 撮像装置およびカメラ |

| JP2010206173A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置およびカメラ |

| JP2010239075A (ja) * | 2009-03-31 | 2010-10-21 | Sony Corp | 固体撮像装置とその製造方法、及び電子機器 |

| JP2014063774A (ja) * | 2012-09-19 | 2014-04-10 | Canon Inc | 固体撮像素子およびその製造方法ならびにカメラ |

| US8723285B2 (en) | 2009-02-06 | 2014-05-13 | Canon Kabushiki Kaisha | Photoelectric conversion device manufacturing method thereof, and camera |

| US8779544B2 (en) | 2009-02-06 | 2014-07-15 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and imaging system having revision with multiple impurity densities |

| KR20150139787A (ko) * | 2014-06-04 | 2015-12-14 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치의 제조 방법 |

| JP2015233128A (ja) * | 2014-05-12 | 2015-12-24 | キヤノン株式会社 | 固体撮像装置およびその製造方法ならびにカメラ |

| JP2016046420A (ja) * | 2014-08-25 | 2016-04-04 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| CN105990387A (zh) * | 2015-03-19 | 2016-10-05 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

| JP2016178144A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

-

2003

- 2003-08-25 JP JP2003299750A patent/JP2005072236A/ja active Pending

Cited By (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7670865B2 (en) | 2004-10-15 | 2010-03-02 | Omnivision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| US7355228B2 (en) | 2004-10-15 | 2008-04-08 | Omnivision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| US7939357B2 (en) | 2004-10-15 | 2011-05-10 | Omnivision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| EP1648035A1 (en) * | 2004-10-15 | 2006-04-19 | OmniVision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| US7521738B2 (en) | 2004-10-15 | 2009-04-21 | Omnivision Technologies, Inc. | Image sensor pixel having photodiode with multi-dopant implantation |

| KR100679855B1 (ko) | 2005-05-02 | 2007-02-07 | (주) 픽셀플러스 | 암전류 억제를 위한 이미지 센서의 단위픽셀 및 그제조방법 |

| CN100463141C (zh) * | 2005-06-07 | 2009-02-18 | 东部电子有限公司 | 制造cmos图像传感器的方法 |

| JP2007109818A (ja) * | 2005-10-12 | 2007-04-26 | Sharp Corp | 固体撮像装置およびその製造方法、電子情報機器 |

| KR100772316B1 (ko) | 2006-04-28 | 2007-10-31 | 매그나칩 반도체 유한회사 | 플라즈마손상으로부터 포토다이오드를 보호하는 씨모스이미지센서의 제조 방법 |

| JP2007300084A (ja) * | 2006-04-28 | 2007-11-15 | Magnachip Semiconductor Ltd | プラズマ損傷からフォトダイオードを保護するcmosイメージセンサの製造方法 |

| US7629216B2 (en) | 2006-04-28 | 2009-12-08 | Han-Seob Cha | Method for fabricating CMOS image sensor with plasma damage-free photodiode |

| FR2910713A1 (fr) * | 2006-12-26 | 2008-06-27 | St Microelectronics Sa | Photodiode verrouillee a grande capacite de stockage, par exemple pour un capteur d'image, procede de realisation associe, et capteur d'image comprenant une telle diode. |

| JP2010518629A (ja) * | 2007-02-07 | 2010-05-27 | フォベオン・インコーポレーテッド | ピン止めフォトダイオードcmos画素センサ |

| JP2008263041A (ja) * | 2007-04-11 | 2008-10-30 | Sharp Corp | 半導体装置の製造方法、半導体装置、固体撮像素子、mosトランジスタおよび電子情報機器 |

| JP2010147193A (ja) * | 2008-12-17 | 2010-07-01 | Sharp Corp | 固体撮像装置およびその製造方法、並びに電子情報機器 |

| US8115851B2 (en) | 2008-12-17 | 2012-02-14 | Sharp Kabushiki Kaisha | Solid-state image capturing apparatus, method for manufacturing same, and electronic information device |

| JP2010161236A (ja) * | 2009-01-08 | 2010-07-22 | Canon Inc | 光電変換装置の製造方法 |

| US8698208B2 (en) | 2009-01-08 | 2014-04-15 | Canon Kabushiki Kaisha | Photoelectric conversion device |

| JP2010206178A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置、及び光電変換装置の製造方法 |

| US8953076B2 (en) | 2009-02-06 | 2015-02-10 | Canon Kabushiki Kaisha | Photoelectric conversion device and camera having a photodiode cathode formed by an n-type buried layer |

| JP2010206173A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 光電変換装置およびカメラ |

| US8670059B2 (en) | 2009-02-06 | 2014-03-11 | Canon Kabushiki Kaisha | Photoelectric conversion device having an n-type buried layer, and camera |

| US9076704B2 (en) | 2009-02-06 | 2015-07-07 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and manufacturing method for a photoelectric conversion apparatus |

| JP2010206172A (ja) * | 2009-02-06 | 2010-09-16 | Canon Inc | 撮像装置およびカメラ |

| US8723285B2 (en) | 2009-02-06 | 2014-05-13 | Canon Kabushiki Kaisha | Photoelectric conversion device manufacturing method thereof, and camera |

| US8779544B2 (en) | 2009-02-06 | 2014-07-15 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and imaging system having revision with multiple impurity densities |

| JP2010239075A (ja) * | 2009-03-31 | 2010-10-21 | Sony Corp | 固体撮像装置とその製造方法、及び電子機器 |

| US8957357B2 (en) | 2009-03-31 | 2015-02-17 | Sony Corporation | Solid-state imaging device, manufacturing method of the same, and electronic apparatus |

| US9437631B2 (en) | 2009-03-31 | 2016-09-06 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, manufacturing method of the same, and electronic apparatus |

| JP2014063774A (ja) * | 2012-09-19 | 2014-04-10 | Canon Inc | 固体撮像素子およびその製造方法ならびにカメラ |

| JP2015233128A (ja) * | 2014-05-12 | 2015-12-24 | キヤノン株式会社 | 固体撮像装置およびその製造方法ならびにカメラ |

| KR20150139787A (ko) * | 2014-06-04 | 2015-12-14 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치의 제조 방법 |

| KR102418456B1 (ko) * | 2014-06-04 | 2022-07-08 | 르네사스 일렉트로닉스 가부시키가이샤 | 반도체 장치의 제조 방법 |

| JP2016046420A (ja) * | 2014-08-25 | 2016-04-04 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| CN105990387A (zh) * | 2015-03-19 | 2016-10-05 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

| JP2016178144A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| JP2016178143A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| CN105990387B (zh) * | 2015-03-19 | 2021-03-30 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4051059B2 (ja) | Cmosイメージセンサ及びその製造方法 | |

| US7592579B2 (en) | Photoelectric conversion device manufacturing method, semiconductor device manufacturing method, photoelectric conversion device, and image sensing system | |

| JP2005072236A (ja) | 半導体装置および半導体装置の製造方法 | |

| US7217961B2 (en) | Solid-state image pickup device and method for producing the same | |

| US7005315B2 (en) | Method and fabricating complementary metal-oxide semiconductor image sensor with reduced etch damage | |

| US7939859B2 (en) | Solid state imaging device and method for manufacturing the same | |

| US8754458B2 (en) | Semiconductor device, manufacturing method thereof, solid-state imaging device, manufacturing method thereof, and electronic unit | |

| US20090212335A1 (en) | Complementary metal-oxide-semiconductor (cmos) image sensor and fabricating method thereof | |

| KR100696995B1 (ko) | 고체 촬상 장치 | |

| US20070221973A1 (en) | Solid-state imaging device and method for manufacturing the same | |

| JP5458135B2 (ja) | 固体撮像素子の製造方法 | |

| JP2008153566A (ja) | 固体撮像装置及びその製造方法 | |

| KR100562668B1 (ko) | 암신호 감소를 위한 이미지센서 제조 방법 | |

| US20230246043A1 (en) | Semiconductor device and imaging apparatus | |

| WO2014002365A1 (ja) | 固体撮像装置及びその製造方法 | |

| JP2002190586A (ja) | 固体撮像装置およびその製造方法 | |

| JP2007141937A (ja) | 固体撮像素子、半導体装置及び半導体装置の製造方法 | |

| JP2010021253A (ja) | 固体撮像素子の製造方法 | |

| JP2008016723A (ja) | 固体撮像装置の製造方法および固体撮像装置 | |

| JP2004356246A (ja) | 固体撮像素子の製造方法および固体撮像素子 | |

| JP2007311648A (ja) | 固体撮像装置及びその製造方法 | |

| JP2010287610A (ja) | 固体撮像装置およびその製造方法 | |

| JP2011258613A (ja) | 固体撮像装置及びその製造方法 | |

| KR100619408B1 (ko) | 크로스 토크를 방지할 수 있는 이미지센서 및 그 제조 방법 | |

| JP3105781B2 (ja) | 固体撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060807 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060807 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090918 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091006 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091110 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100302 |