JP5536414B2 - パネル構造体、パネル構造体を含む表示装置及びその製造方法 - Google Patents

パネル構造体、パネル構造体を含む表示装置及びその製造方法 Download PDFInfo

- Publication number

- JP5536414B2 JP5536414B2 JP2009238280A JP2009238280A JP5536414B2 JP 5536414 B2 JP5536414 B2 JP 5536414B2 JP 2009238280 A JP2009238280 A JP 2009238280A JP 2009238280 A JP2009238280 A JP 2009238280A JP 5536414 B2 JP5536414 B2 JP 5536414B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- insulating layer

- gate

- panel structure

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 35

- 239000010409 thin film Substances 0.000 claims description 29

- 239000000463 material Substances 0.000 claims description 25

- 238000000034 method Methods 0.000 claims description 23

- 229910044991 metal oxide Inorganic materials 0.000 claims description 13

- 150000004706 metal oxides Chemical class 0.000 claims description 13

- 230000000149 penetrating effect Effects 0.000 claims description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 8

- 239000003990 capacitor Substances 0.000 claims description 7

- 239000004065 semiconductor Substances 0.000 claims description 7

- 239000011701 zinc Substances 0.000 claims description 6

- 239000000203 mixture Substances 0.000 claims description 5

- 229910001218 Gallium arsenide Inorganic materials 0.000 claims description 4

- -1 GeSi Inorganic materials 0.000 claims description 4

- 229910052751 metal Inorganic materials 0.000 claims description 4

- 239000002184 metal Substances 0.000 claims description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 claims description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 217

- 239000000758 substrate Substances 0.000 description 14

- 238000005530 etching Methods 0.000 description 12

- 102100036464 Activated RNA polymerase II transcriptional coactivator p15 Human genes 0.000 description 6

- 101000713904 Homo sapiens Activated RNA polymerase II transcriptional coactivator p15 Proteins 0.000 description 6

- 229910004444 SUB1 Inorganic materials 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 4

- 229910005265 GaInZnO Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000005019 vapor deposition process Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Description

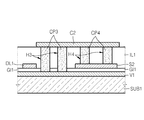

BG1、BG2 ゲート電極、

C1、C2 連結配線、

CP1〜CP5 導電プラグ、

D1、D2 ドレイン電極、

GI1 ゲート絶縁層、

GL1 ゲートライン、

H1〜H5 ホール(hole)、

IL1 絶縁層、

PE1 画素電極、

S1、S2 ソース電極、

SP1〜SP3 単位素子、

SUB1 基板、

V1 電源ライン。

Claims (30)

- 第1ゲート電極と、前記第1ゲート電極の位置の上部に対応する位置に形成された第1活性層と、前記第1活性層の両端に接触された第1ソース電極及び第1ドレイン電極と、を具備する第1薄膜トランジスタと、

前記第1ドレイン電極と離隔された第1導電層と、

画素電極と、

前記画素電極と離隔し、前記画素電極と同じ物質から形成された第1連結配線と、

前記第1連結配線の一端と前記第1ドレイン電極とを連結する第1導電プラグと、

前記第1連結配線の他端と前記第1導電層とを連結する第2導電プラグと、を含み、

前記第1導電層と離隔された第2導電層と、

前記第2導電層と離隔された第3導電層と、

前記画素電極と同じ物質から形成された第2連結配線と、をさらに含み、

前記第2連結配線の一端は前記第2導電層と連結され、前記第2連結配線の他端は前記第3導電層と連結され、

前記第1導電層は第2ゲート電極であり、

前記第3導電層は第2ソース電極であり、

前記第1ゲート電極及び前記第2ゲート電極を覆うゲート絶縁層と、

前記ゲート絶縁層上に備えられた第2活性層と、

前記第2活性層に接触する第2ドレイン電極と、

前記ゲート絶縁層上に、前記第1活性層、前記第1ソース電極、前記第1ドレイン電極、前記第2活性層、前記第2ソース電極及び前記第2ドレイン電極を覆う絶縁層と、をさらに含み、

前記第2ソース電極の一部は前記第2導電層の上部に位置し、

前記第2連結配線の一端と前記第2導電層とを連結し、前記ゲート絶縁層と前記絶縁層とを貫通する第3導電プラグと、

前記第2連結配線の他端と前記第2ソース電極とを連結し、前記絶縁層を貫通する第4導電プラグと、

をさらに含むことを特徴とするパネル構造体。 - 前記第1連結配線と前記画素電極は金属酸化物及び金属のうちの少なくとも一つによって形成され、前記金属酸化物はITO(indium tin oxide)、IZO(indium zinc oxide)、Sn酸化物、In酸化物、Zn酸化物及びそれらの混合物のうちの一つであることを特徴とする請求項1に記載のパネル構造体。

- 前記第1導電層を覆うゲート絶縁層と、

前記ゲート絶縁層上に、前記第1ドレイン電極を覆う絶縁層と、をさらに具備し、

前記第1連結配線は前記絶縁層上に形成され、

前記第1導電プラグは前記絶縁層を貫通し、前記第2導電プラグは前記ゲート絶縁層と前記絶縁層とを貫通することを特徴とする請求項1または請求項2に記載のパネル構造体。 - 前記第2導電層は電源ラインであることを特徴とする請求項1から3のいずれかに記載のパネル構造体。

- 前記第2ゲート電極の少なくとも一部は前記第1ゲート電極と前記第2導電層との間に備えられることを特徴とする請求項1から4のいずれかに記載のパネル構造体。

- 前記第2導電層は前記ゲート絶縁層によって覆われ、

前記第2連結配線は前記第2導電層上側の前記絶縁層上に備えられることを特徴とする請求項1から5のいずれかに記載のパネル構造体。 - 前記画素電極は、前記絶縁層上に、前記第2ドレイン電極と連結されるように備えられることを特徴とする請求項1から6のいずれかに記載のパネル構造体。

- 前記画素電極は、前記第2ゲート電極と前記第2導電層との間の前記絶縁層上に備えられることを特徴とする請求項1から7のいずれかに記載のパネル構造体。

- 前記第2ゲート電極、前記第2活性層、前記第2ソース電極及び前記第2ドレイン電極は第2薄膜トランジスタを構成し、

前記第1薄膜トランジスタはスイッチングトランジスタであり、前記第2薄膜トランジスタは駆動トランジスタであり、

前記第2ゲート電極の一部、前記第2ゲート電極の上部に対応する位置の前記第2ソース電極の一部、及び前記第2ゲート電極の一部と前記第2ソース電極の一部との間の前記ゲート絶縁層は、キャパシタとして作用することを特徴とする請求項1から8のいずれかに記載のパネル構造体。 - 前記第1活性層は、非晶質シリコン(a−Si)、多結晶シリコン(poly−Si)、GeSi、GaAs及び金属酸化物半導体のうちの少なくとも一つによって形成されることを特徴とする請求項1から9のいずれかに記載のパネル構造体。

- 前記第2活性層は前記第1活性層と同じ物質から形成されることを特徴とする請求項1から10のいずれかに記載のパネル構造体。

- 前記画素電極に連結される第2ドレイン電極を含む第2薄膜トランジスタをさらに具備することを特徴とする請求項1から11のいずれかに記載のパネル構造体。

- 前記第2ドレイン電極は前記画素電極と別途の導電プラグによって連結され、

前記別途の導電プラグは前記画素電極と一体をなすように形成されることを特徴とする請求項12に記載のパネル構造体。 - 前記第1導電層は前記第2薄膜トランジスタのゲート電極であることを特徴とする請求項12に記載のパネル構造体。

- 前記第1薄膜トランジスタはスイッチングトランジスタであり、

前記第2薄膜トランジスタは駆動トランジスタであることを特徴とする請求項12から14のいずれかに記載のパネル構造体。 - 前記第1連結配線と前記画素電極とは同一層上に備えられることを特徴とする請求項1から15のいずれかに記載のパネル構造体。

- 請求項1から請求項16のうちのいずれか1項に記載のパネル構造体を含むことを特徴とする表示装置。

- 第1ゲート電極、第1ソース電極及び第1ドレイン電極を具備する第1トランジスタと、

第2ゲート電極、第2ソース電極及び第2ドレイン電極を具備する第2トランジスタと、

前記第1ゲート電極に連結されたものであって、第1方向に延びた第1ゲートラインと、

前記第1ゲートラインと離隔して前記第1ゲートラインと並んだ方向に延びた電源ラインと、

画素電極と、

前記画素電極と同じ物質から形成され、前記第1ドレイン電極と前記第2ゲート電極とを電気的に連結するための少なくとも1つの第1コンタクトプラグと、

前記画素電極と同じ物質から形成され、前記電源ラインと前記第2ソース電極とを連結するための少なくとも1つの第2コンタクトプラグと、を含み、

前記第1ゲートラインと前記電源ラインとの間に前記第2ゲート電極及び前記画素電極が配置され、前記第2ゲート電極と前記電源ラインとの間に前記画素電極が配置されることを特徴とするパネル構造体。 - 前記第1トランジスタはスイッチングトランジスタであり、

前記第2トランジスタは駆動トランジスタであることを特徴とする請求項18に記載のパネル構造体。 - 前記少なくとも1つの第1コンタクトプラグに連結された第1連結配線がさらに備えられることを特徴とする請求項18または19に記載のパネル構造体。

- 前記画素電極と一体をなすように形成され、前記画素電極と前記第2ドレインとを連結する少なくとも1つの第3コンタクトプラグをさらに含むことを特徴とする請求項18から20のいずれかに記載のパネル構造体。

- 前記少なくとも1つの第2コンタクトプラグに連結された第2連結配線がさらに備えられることを特徴とする請求項18から21のいずれかに記載のパネル構造体。

- 第1ゲート電極と、前記第1ゲート電極の位置の上部に対応する位置に形成される第1活性層と、前記第1活性層の両端に接触された第1ソース電極及び第1ドレイン電極と、を具備する第1薄膜トランジスタと、前記第1ドレイン電極と離隔された第1導電層と、を含むパネル構造体の製造方法において、

画素電極を形成する段階と、

前記画素電極を形成する間、前記第1ドレイン電極に接触する第1導電プラグを形成する段階と、

前記画素電極を形成する間、前記第1導電層に接触する第2導電プラグを形成する段階と、

前記第1導電プラグ及び前記第2導電プラグを連結する第1連結配線を形成する段階と、を含み、

前記第1導電層と離隔される第2導電層を形成する段階と、

前記第2導電層と離隔される第3導電層を形成する段階と、

前記画素電極を形成する間、前記第2導電層に接触する第3導電プラグを形成する段階と、

前記画素電極を形成する間、前記第3導電層に接触する第4導電プラグを形成する段階と、

前記第3導電プラグ及び第4導電プラグを連結する第2連結配線を形成する段階と、をさらに含み、

前記第1導電層は第2ゲート電極であり、

前記第3導電層は第2ソース電極であり、

前記第1ゲート電極及び前記第2ゲート電極を覆うゲート絶縁層を形成する段階と、

前記ゲート絶縁層上に第2活性層を形成する段階と、

前記第2活性層に接触する第2ドレイン電極を形成する段階と、

前記ゲート絶縁層上に、前記第1活性層、前記第1ソース電極、前記第1ドレイン電極、前記第2活性層、前記第2ソース電極及び前記第2ドレイン電極を覆う絶縁層を形成する段階と、をさらに含み、

前記第2ソース電極の一部は前記第2導電層の上部に位置し、

第3導電プラグは前記第2連結配線の一端と前記第2導電層とを連結し、前記ゲート絶縁層と前記絶縁層とを貫通し、

前記第4導電プラグは前記第2連結配線の他端と前記第2ソース電極とを連結し、前記絶縁層を貫通し、

前記第1導電プラグ及び前記第4導電プラグは前記絶縁層を貫通するように形成され、前記第2導電プラグ及び前記第3導電プラグは前記絶縁層及び前記ゲート絶縁層を貫通するように形成されることを特徴とするパネル構造体の製造方法。 - 前記第1連結配線を形成する段階は、前記画素電極を形成する間に行われることを特徴とする請求項23に記載のパネル構造体の製造方法。

- 前記画素電極、前記第1導電プラグ及び前記第2導電プラグは、いずれも同じ物質によって形成することを特徴とする請求項23または24に記載のパネル構造体の製造方法。

- 前記第1連結配線は前記画素電極と同じ物質によって形成することを特徴とする請求項23から25のいずれかに記載のパネル構造体の製造方法。

- 前記第2連結配線を形成する段階は前記画素電極を形成する間に行われることを特徴とする請求項23から26のいずれかに記載のパネル構造体の製造方法。

- 前記第2連結配線は前記画素電極と同じ物質によって形成することを特徴とする請求項23から27のいずれかに記載のパネル構造体の製造方法。

- 前記第2導電層は電源ラインであることを特徴とする請求項23から28のいずれかに記載のパネル構造体の製造方法。

- 前記画素電極は、前記絶縁層上であって、第5導電プラグによって前記第2ドレイン電極と連結されるように形成されることを特徴とする請求項23から29のいずれかに記載のパネル構造体の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2008-0102151 | 2008-10-17 | ||

| KR1020080102151A KR101540341B1 (ko) | 2008-10-17 | 2008-10-17 | 패널 구조체, 패널 구조체를 포함하는 표시장치 및 이들의 제조방법 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010098317A JP2010098317A (ja) | 2010-04-30 |

| JP2010098317A5 JP2010098317A5 (ja) | 2012-10-25 |

| JP5536414B2 true JP5536414B2 (ja) | 2014-07-02 |

Family

ID=42107942

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009238280A Active JP5536414B2 (ja) | 2008-10-17 | 2009-10-15 | パネル構造体、パネル構造体を含む表示装置及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US8294150B2 (ja) |

| JP (1) | JP5536414B2 (ja) |

| KR (1) | KR101540341B1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011164196A (ja) * | 2010-02-05 | 2011-08-25 | Seiko Epson Corp | 電気光学装置用基板、電気光学装置及び電子機器 |

| KR101182232B1 (ko) | 2010-06-30 | 2012-09-12 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 |

| US8603841B2 (en) * | 2010-08-27 | 2013-12-10 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing methods of semiconductor device and light-emitting display device |

| WO2012044978A2 (en) | 2010-10-01 | 2012-04-05 | Applied Materials, Inc. | High efficiency solar cell device with gallium arsenide absorber layer |

| JP5825812B2 (ja) * | 2011-03-24 | 2015-12-02 | 株式会社Joled | 表示装置の製造方法 |

| WO2012136223A1 (en) * | 2011-04-07 | 2012-10-11 | 3Shape A/S | 3d system and method for guiding objects |

| KR20130092848A (ko) * | 2012-02-13 | 2013-08-21 | 삼성전자주식회사 | 박막 트랜지스터 및 이를 채용한 디스플레이 패널 |

| KR20130105392A (ko) * | 2012-03-14 | 2013-09-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN103325792A (zh) * | 2013-05-23 | 2013-09-25 | 合肥京东方光电科技有限公司 | 一种阵列基板及制备方法、显示装置 |

| KR102211966B1 (ko) * | 2013-10-14 | 2021-02-15 | 삼성디스플레이 주식회사 | 박막 트랜지스터 어레이 기판 및 이를 포함하는 유기 발광 표시 장치 |

| CN103700665B (zh) * | 2013-12-13 | 2016-03-02 | 京东方科技集团股份有限公司 | 金属氧化物薄膜晶体管阵列基板及其制作方法、显示装置 |

| KR101529934B1 (ko) * | 2014-07-01 | 2015-06-18 | 엘지전자 주식회사 | 반도체 발광 소자를 이용한 디스플레이 장치 |

| KR102596126B1 (ko) * | 2016-10-19 | 2023-10-31 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조방법 |

| CN106784014A (zh) | 2016-12-23 | 2017-05-31 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、显示基板、显示装置 |

Family Cites Families (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6124606A (en) * | 1995-06-06 | 2000-09-26 | Ois Optical Imaging Systems, Inc. | Method of making a large area imager with improved signal-to-noise ratio |

| US20010043175A1 (en) * | 1996-10-22 | 2001-11-22 | Masahiro Yasukawa | Liquid crystal panel substrate, liquid crystal panel, and electronic equipment and projection type display device both using the same |

| JP3279939B2 (ja) * | 1996-11-13 | 2002-04-30 | 三菱電機株式会社 | 液晶ディスプレイ装置 |

| US6949417B1 (en) * | 1997-03-05 | 2005-09-27 | Lg. Philips Lcd Co., Ltd. | Liquid crystal display and method of manufacturing the same |

| JP3856901B2 (ja) * | 1997-04-15 | 2006-12-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP3520396B2 (ja) * | 1997-07-02 | 2004-04-19 | セイコーエプソン株式会社 | アクティブマトリクス基板と表示装置 |

| KR100425858B1 (ko) * | 1998-07-30 | 2004-08-09 | 엘지.필립스 엘시디 주식회사 | 박막트랜지스터및그제조방법 |

| WO2000016153A1 (fr) * | 1998-09-10 | 2000-03-23 | Seiko Epson Corporation | Substrat pour panneau a cristaux liquides, panneau a cristaux liquides, appareil electronique comprenant ce panneau, et procede de fabrication d'un substrat pour panneau a cristaux liquides |

| JP3916823B2 (ja) * | 1999-04-07 | 2007-05-23 | シャープ株式会社 | アクティブマトリクス基板およびその製造方法、並びにフラットパネル型イメージセンサ |

| JP2001053283A (ja) * | 1999-08-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| JP4530450B2 (ja) * | 1999-09-29 | 2010-08-25 | 三洋電機株式会社 | El表示装置 |

| JP2001109404A (ja) * | 1999-10-01 | 2001-04-20 | Sanyo Electric Co Ltd | El表示装置 |

| KR100612994B1 (ko) * | 2000-05-12 | 2006-08-14 | 삼성전자주식회사 | 액정 표시 장치 및 그에 사용되는 기판 |

| US7804552B2 (en) * | 2000-05-12 | 2010-09-28 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device with light shielding portion comprising laminated colored layers, electrical equipment having the same, portable telephone having the same |

| JP2002076352A (ja) * | 2000-08-31 | 2002-03-15 | Semiconductor Energy Lab Co Ltd | 表示装置及びその作製方法 |

| JP2002108250A (ja) * | 2000-09-29 | 2002-04-10 | Sharp Corp | アクティブマトリックス駆動型自発光表示装置及びその製造方法 |

| KR20020043860A (ko) | 2000-12-04 | 2002-06-12 | 구본준, 론 위라하디락사 | 액정 표시 장치용 어레이 기판 및 그 제조 방법 |

| JP4741569B2 (ja) * | 2000-12-21 | 2011-08-03 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP2002311448A (ja) * | 2001-02-06 | 2002-10-23 | Advanced Display Inc | 液晶表示装置及びその製造方法 |

| JP4689851B2 (ja) * | 2001-02-23 | 2011-05-25 | Nec液晶テクノロジー株式会社 | アクティブマトリクス型液晶表示装置 |

| TWI271573B (en) * | 2001-08-22 | 2007-01-21 | Advanced Display Kk | Liquid crystal display device and method of producing the same |

| JP2003161957A (ja) * | 2001-11-26 | 2003-06-06 | Toshiba Corp | 液晶表示装置及びその製造方法 |

| US6909240B2 (en) * | 2002-01-18 | 2005-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| TW516240B (en) * | 2002-02-18 | 2003-01-01 | Ind Tech Res Inst | Method of fabricating film transistor on a transparent substrate |

| JP4604440B2 (ja) * | 2002-02-22 | 2011-01-05 | 日本電気株式会社 | チャネルエッチ型薄膜トランジスタ |

| US7592980B2 (en) * | 2002-06-05 | 2009-09-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP4640690B2 (ja) * | 2002-07-24 | 2011-03-02 | 日本電気株式会社 | アクティブマトリクス有機el表示装置の製造方法 |

| KR100878237B1 (ko) * | 2002-08-01 | 2009-01-13 | 삼성전자주식회사 | 박막 트랜지스터 기판 |

| KR100642491B1 (ko) * | 2003-12-26 | 2006-11-02 | 엘지.필립스 엘시디 주식회사 | 유기전계발광 소자 |

| US7372513B2 (en) * | 2003-12-30 | 2008-05-13 | Lg.Philips Lcd Co., Ltd. | Liquid crystal display device and method for fabricating the same |

| TWI247935B (en) * | 2004-01-07 | 2006-01-21 | Shih-Hsien Tseng | Liquid crystal display device |

| JP2005252228A (ja) * | 2004-02-05 | 2005-09-15 | Sharp Corp | 表示装置及びその製造方法 |

| TWI252445B (en) * | 2004-03-03 | 2006-04-01 | Toppoly Optoelectronics Corp | Mirror-surface display |

| KR100669720B1 (ko) * | 2004-08-06 | 2007-01-16 | 삼성에스디아이 주식회사 | 평판 디스플레이 장치 |

| KR101090250B1 (ko) * | 2004-10-15 | 2011-12-06 | 삼성전자주식회사 | 유기 반도체를 이용한 박막 트랜지스터 표시판 및 그 제조방법 |

| WO2006064789A1 (ja) * | 2004-12-14 | 2006-06-22 | Sharp Kabushiki Kaisha | 液晶表示装置および液晶表示装置の欠陥修正方法 |

| US7573537B2 (en) * | 2005-01-17 | 2009-08-11 | Samsung Electronics Co., Ltd. | Array substrate, liquid crystal display panel having the same and liquid crystal display device having the same |

| KR101100885B1 (ko) * | 2005-01-31 | 2012-01-02 | 삼성전자주식회사 | 유기 발광 표시 장치용 박막 트랜지스터 표시판 |

| US8253179B2 (en) * | 2005-05-13 | 2012-08-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| KR101128332B1 (ko) | 2005-06-17 | 2012-03-23 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판과 그 제조방법 |

| KR101167661B1 (ko) * | 2005-07-15 | 2012-07-23 | 삼성전자주식회사 | 배선 구조와 배선 형성 방법 및 박막 트랜지스터 기판과 그제조 방법 |

| JP4514674B2 (ja) * | 2005-08-16 | 2010-07-28 | シャープ株式会社 | 表示装置、表示パネル用基板および表示パネル用基板の製造方法 |

| KR101209041B1 (ko) * | 2005-11-25 | 2012-12-06 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR20070081829A (ko) * | 2006-02-14 | 2007-08-20 | 삼성전자주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| JP5060738B2 (ja) * | 2006-04-28 | 2012-10-31 | 株式会社ジャパンディスプレイイースト | 画像表示装置 |

| JP4277874B2 (ja) * | 2006-05-23 | 2009-06-10 | エプソンイメージングデバイス株式会社 | 電気光学装置の製造方法 |

| KR20070122317A (ko) * | 2006-06-26 | 2007-12-31 | 삼성전자주식회사 | 액정 모듈, 액정 모듈의 구동 방법 및 액정표시장치 |

| US7863612B2 (en) * | 2006-07-21 | 2011-01-04 | Semiconductor Energy Laboratory Co., Ltd. | Display device and semiconductor device |

| US8228273B2 (en) * | 2006-08-02 | 2012-07-24 | Sharp Kabushiki Kaisha | Active matrix substrate and display device having the same |

| KR101294260B1 (ko) * | 2006-08-18 | 2013-08-06 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR101326128B1 (ko) * | 2006-09-29 | 2013-11-06 | 삼성디스플레이 주식회사 | 표시 장치용 배선, 식각액, 박막 트랜지스터 표시판 및 그제조 방법 |

| US7507998B2 (en) | 2006-09-29 | 2009-03-24 | Tpo Displays Corp. | System for displaying images and method for fabricating the same |

| KR100740132B1 (ko) * | 2006-11-10 | 2007-07-16 | 삼성에스디아이 주식회사 | 유기 전계 발광 표시 장치 |

| KR101281167B1 (ko) * | 2006-11-22 | 2013-07-02 | 삼성전자주식회사 | 유기발광 디스플레이의 단위 화소부 구동소자 및 그제조방법 |

| KR20080050679A (ko) | 2006-12-04 | 2008-06-10 | 삼성전자주식회사 | 박막 트랜지스터 기판의 제조 방법 |

| KR20080053646A (ko) * | 2006-12-11 | 2008-06-16 | 삼성전자주식회사 | 유기 발광 표시 장치의 제조 방법 |

| KR101353269B1 (ko) | 2006-12-11 | 2014-01-20 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR101293570B1 (ko) * | 2007-03-21 | 2013-08-06 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 이를 포함하는 유기 발광 표시 장치 |

| TWI337754B (en) * | 2007-04-20 | 2011-02-21 | Au Optronics Corp | Semiconductor structure of display device and method for fabricating the same |

| JP5142831B2 (ja) * | 2007-06-14 | 2013-02-13 | 株式会社半導体エネルギー研究所 | 半導体装置及びその作製方法 |

| JP2009049135A (ja) * | 2007-08-17 | 2009-03-05 | Sony Corp | 表示装置 |

| JP5428142B2 (ja) * | 2007-09-11 | 2014-02-26 | カシオ計算機株式会社 | 表示パネルの製造方法 |

| US20090278121A1 (en) * | 2008-05-08 | 2009-11-12 | Tpo Displays Corp. | System for displaying images and fabrication method thereof |

-

2008

- 2008-10-17 KR KR1020080102151A patent/KR101540341B1/ko active IP Right Grant

-

2009

- 2009-10-08 US US12/588,247 patent/US8294150B2/en active Active

- 2009-10-15 JP JP2009238280A patent/JP5536414B2/ja active Active

-

2012

- 2012-09-17 US US13/621,531 patent/US8698159B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR101540341B1 (ko) | 2015-07-30 |

| US8294150B2 (en) | 2012-10-23 |

| US20100096634A1 (en) | 2010-04-22 |

| KR20100042932A (ko) | 2010-04-27 |

| US20130015454A1 (en) | 2013-01-17 |

| US8698159B2 (en) | 2014-04-15 |

| JP2010098317A (ja) | 2010-04-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5536414B2 (ja) | パネル構造体、パネル構造体を含む表示装置及びその製造方法 | |

| US9379170B2 (en) | Organic light emitting diode display device and method of fabricating the same | |

| CN104733499B (zh) | 有机发光二极管显示装置及其制造方法 | |

| US9570527B2 (en) | Organic light emitting diode display | |

| KR101961190B1 (ko) | 유기전압 발광소자 및 이의 제조방법 | |

| US10211264B2 (en) | Organic light emitting display device having a color filter on thin film transistor structure and method of manufacturing the same | |

| CN103155153B (zh) | 半导体装置、显示装置以及半导体装置和显示装置的制造方法 | |

| TWI553850B (zh) | 有機電致發光顯示器及其製造方法 | |

| US20150221674A1 (en) | Array substrate and manufacturing method thereof, display device | |

| TWI489191B (zh) | 畫素結構及薄膜電晶體 | |

| JP2019121598A (ja) | 上部発光型有機発光ダイオード表示装置 | |

| US9373650B2 (en) | TFT array substrate, manufacturing method thereof and display panel | |

| TW201705574A (zh) | 有機發光顯示裝置及製造有機發光顯示裝置之方法 | |

| US8890160B2 (en) | AMOLED display and manufacturing method thereof | |

| CN106920802B (zh) | 薄膜晶体管基板和使用该薄膜晶体管基板的显示器 | |

| KR20160059003A (ko) | 유기 발광 표시 장치 및 그 제조 방법 | |

| TW202001853A (zh) | 顯示面板 | |

| CN111863929A (zh) | 显示基板及其制备方法、显示装置 | |

| US20180053718A1 (en) | Layer stacking structure, array substrate and display device | |

| CN109427820A (zh) | 一种基板及其制备方法、显示面板 | |

| US10522780B2 (en) | Organic light emitting display device | |

| TWI621258B (zh) | 用於顯示設備的基板、包含該基板的顯示設備及製造該顯示設備的方法 | |

| US20240081115A1 (en) | Display substrate, manufacturing method thereof, and display device | |

| KR102294480B1 (ko) | 박막 트랜지스터 기판, 박막 트랜지스터 기판의 제조 방법 및 박막트랜지스터 기판을 포함하는 표시 장치 | |

| CN115497998A (zh) | 显示基板及其制备方法、显示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120906 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120906 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140401 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140424 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5536414 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |