JP2010021520A - 薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置 - Google Patents

薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置 Download PDFInfo

- Publication number

- JP2010021520A JP2010021520A JP2009058255A JP2009058255A JP2010021520A JP 2010021520 A JP2010021520 A JP 2010021520A JP 2009058255 A JP2009058255 A JP 2009058255A JP 2009058255 A JP2009058255 A JP 2009058255A JP 2010021520 A JP2010021520 A JP 2010021520A

- Authority

- JP

- Japan

- Prior art keywords

- film transistor

- thin film

- active layer

- compound semiconductor

- protective layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

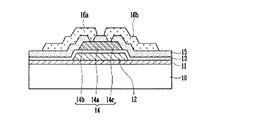

【解決手段】基板上に形成されたゲート電極と、ゲート絶縁膜によりゲート電極から絶縁され、酸素を含む化合物半導体からなる活性層と、活性層上に形成された保護層と、活性層と接触するソース電極及びドレイン電極とを備え、保護層が、酸素との結合力を有する無機物を含む酸化物からなる。

【選択図】図1

Description

11 バッファ層

12 ゲート電極

13 ゲート絶縁膜

14 活性層

14a チャネル領域

14b ソース領域

14c ドレイン領域

15,25 保護層

15a コンタクトホール

16a,26a ソース電極

16b,26b ドレイン電極

100,200 表示パネル

110,120,210 基板

130 液晶層

300 有機電界発光素子

400 封止基板

410 封止材

Claims (34)

- 基板と、

該基板上に形成されたゲート電極と、

ゲート絶縁膜により前記ゲート電極から絶縁され、酸素を含む化合物半導体からなる活性層と、

該活性層上に形成された保護層と、

前記活性層と接触するソース電極及びドレイン電極とを備え、

前記保護層が、酸素との結合力を有する無機物を含む酸化物からなることを特徴とする薄膜トランジスタ。 - 前記保護層が、前記活性層を含む上部に形成され、前記ソース電極及び前記ドレイン電極が、前記保護層に形成されたコンタクトホールを介して前記活性層と接触することを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記化合物半導体が、酸化亜鉛(ZnO)を含むことを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記化合物半導体に、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)のうちの少なくとも1つのイオンがドープされることを特徴とする請求項3に記載の薄膜トランジスタ。

- 前記酸素との結合力を有する無機物が、前記化合物半導体を構成する元素から選択されることを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記化合物半導体を構成する元素が、亜鉛(Zn)、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)からなる群から選択されることを特徴とする請求項5に記載の薄膜トランジスタ。

- 前記酸素との結合力を有する無機物が、シリコン(Si)及びアルミニウム(Al)のうちの1つを含む群から選択されることを特徴とする請求項1に記載の薄膜トランジスタ。

- 前記シリコン(Si)を含む無機物が、SiO2であり、前記アルミニウム(Al)を含む無機物が、AlOXまたはAlOXNYであることを特徴とする請求項7に記載の薄膜トランジスタ。

- 前記基板と前記ゲート電極との間に形成されたバッファ層をさらに備えることを特徴とする請求項1に記載の薄膜トランジスタ。

- 基板上にゲート電極を形成するステップと、

前記ゲート電極を含む上部にゲート絶縁膜を形成するステップと、

前記ゲート絶縁膜上に、酸素を含む化合物半導体で活性層を形成するステップと、

前記活性層上に、酸素との結合力を有する無機物を含む酸化物で保護層を形成するステップと、

前記活性層と接触するソース電極及びドレイン電極を形成するステップと

を含むことを特徴とする薄膜トランジスタの製造方法。 - 前記保護層を形成するステップが、

前記活性層を含む上部に保護層を形成するステップと、

前記保護層にコンタクトホールを形成するステップと

を含むことを特徴とする請求項10に記載の薄膜トランジスタの製造方法。 - 前記ソース電極及び前記ドレイン電極を形成するステップが、

前記コンタクトホールを埋め込むように、前記保護層上に導電層を形成するステップと、

前記導電層のパターニングを行い、前記コンタクトホールを介して前記活性層と接触する前記ソース電極及び前記ドレイン電極を形成するステップと

を含むことを特徴とする請求項11に記載の薄膜トランジスタの製造方法。 - 前記保護層を熱処理するステップをさらに含むことを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 前記化合物半導体が、酸化亜鉛(ZnO)を含むことを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 前記化合物半導体に、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)のうちの少なくとも1つのイオンがドープされることを特徴とする請求項14に記載の薄膜トランジスタの製造方法。

- 前記酸素との結合力を有する無機物が、前記化合物半導体を構成する元素から選択されることを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 前記化合物半導体を構成する元素が、亜鉛(Zn)、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)からなる群から選択されることを特徴とする請求項16に記載の薄膜トランジスタの製造方法。

- 前記酸素との結合力を有する無機物が、シリコン(Si)及びアルミニウム(Al)のうちの1つを含む群から選択されることを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 前記ソース電極及び前記ドレイン電極を形成するステップにおいて、前記保護層をエッチング停止層として用いることを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 前記基板上にバッファ層を形成するステップをさらに含むことを特徴とする請求項10に記載の薄膜トランジスタの製造方法。

- 複数の第1導電線と第2導電線とによって複数の画素が画定され、各画素に供給される信号を制御する薄膜トランジスタと、当該薄膜トランジスタに接続された第1電極とが形成された第1基板と、

第2電極が形成された第2基板と、

前記第1電極と前記第2電極との間の密封された空間に注入された液晶層とを備え、

前記薄膜トランジスタは、

前記第1基板上に形成されたゲート電極と、

ゲート絶縁膜により前記ゲート電極から絶縁され、酸素を含む化合物半導体からなる活性層と、

該活性層上に形成された保護層と、

前記活性層と接触するソース電極及びドレイン電極とを備え、

前記保護層が、酸素との結合力を有する無機物を含む酸化物からなることを特徴とする平板表示装置。 - 前記保護層が、前記活性層を含む上部に形成され、前記ソース電極及び前記ドレイン電極が、前記保護層に形成されたコンタクトホールを介して前記活性層と接触することを特徴とする請求項21に記載の平板表示装置。

- 前記化合物半導体が、酸化亜鉛(ZnO)を含むことを特徴とする請求項21に記載の平板表示装置。

- 前記化合物半導体に、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)のうちの少なくとも1つのイオンがドープされることを特徴とする請求項23に記載の平板表示装置。

- 前記酸素との結合力を有する無機物が、前記化合物半導体を構成する元素から選択されることを特徴とする請求項21に記載の平板表示装置。

- 前記化合物半導体を構成する元素が、亜鉛(Zn)、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)からなる群から選択されることを特徴とする請求項25に記載の平板表示装置。

- 前記酸素との結合力を有する無機物が、シリコン(Si)及びアルミニウム(Al)のうちの1つを含む群から選択されることを特徴とする請求項21に記載の平板表示装置。

- 第1電極、有機薄膜層及び第2電極からなる有機電界発光素子と、当該有機電界発光素子の動作を制御するための薄膜トランジスタとが形成された第1基板と、

該第1基板と対向するように配置された第2基板とを備え、

前記薄膜トランジスタは、

前記第1基板上に形成されたゲート電極と、

ゲート絶縁膜により前記ゲート電極から絶縁され、酸素を含む化合物半導体からなる活性層と、

該活性層上に形成された保護層と、

前記活性層と接触するソース電極及びドレイン電極とを備え、

前記保護層が、酸素との結合力を有する無機物を含む酸化物からなることを特徴とする平板表示装置。 - 前記保護層が、前記活性層を含む上部に形成され、前記ソース電極及び前記ドレイン電極が、前記保護層に形成されたコンタクトホールを介して前記活性層と接触することを特徴とする請求項28に記載の平板表示装置。

- 前記化合物半導体が、酸化亜鉛(ZnO)を含むことを特徴とする請求項28に記載の平板表示装置。

- 前記化合物半導体に、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)のうちの少なくとも1つのイオンがドープされることを特徴とする請求項30に記載の平板表示装置。

- 前記酸素との結合力を有する無機物が、前記化合物半導体を構成する元素から選択されることを特徴とする請求項28に記載の平板表示装置。

- 前記化合物半導体を構成する元素が、亜鉛(Zn)、ガリウム(Ga)、インジウム(In)、スズ(Sn)、ジルコニウム(Zr)、ハフニウム(Hf)及びバナジウム(V)からなる群から選択されることを特徴とする請求項32に記載の平板表示装置。

- 前記酸素との結合力を有する無機物が、シリコン(Si)及びアルミニウム(Al)のうちの1つを含む群から選択されることを特徴とする請求項28に記載の平板表示装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080066002A KR100963104B1 (ko) | 2008-07-08 | 2008-07-08 | 박막 트랜지스터, 그의 제조 방법 및 박막 트랜지스터를구비하는 평판 표시 장치 |

| KR10-2008-0066002 | 2008-07-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010021520A true JP2010021520A (ja) | 2010-01-28 |

| JP5542352B2 JP5542352B2 (ja) | 2014-07-09 |

Family

ID=41211906

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009058255A Active JP5542352B2 (ja) | 2008-07-08 | 2009-03-11 | 薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US8178884B2 (ja) |

| EP (1) | EP2144294B1 (ja) |

| JP (1) | JP5542352B2 (ja) |

| KR (1) | KR100963104B1 (ja) |

| CN (1) | CN101626036B (ja) |

Cited By (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011013561A1 (en) * | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP2011199273A (ja) * | 2010-02-26 | 2011-10-06 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2011222984A (ja) * | 2010-03-26 | 2011-11-04 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2011222982A (ja) * | 2010-03-26 | 2011-11-04 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2011233876A (ja) * | 2010-04-09 | 2011-11-17 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2011243972A (ja) * | 2010-04-23 | 2011-12-01 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法、及び半導体装置 |

| JP2011243973A (ja) * | 2010-04-23 | 2011-12-01 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2012015496A (ja) * | 2010-06-01 | 2012-01-19 | Semiconductor Energy Lab Co Ltd | 電界効果トランジスタおよびその作製方法 |

| JP2012028481A (ja) * | 2010-07-22 | 2012-02-09 | Fujifilm Corp | 電界効果型トランジスタ及びその製造方法 |

| JP2012160720A (ja) * | 2011-01-12 | 2012-08-23 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| JP2012231100A (ja) * | 2010-06-11 | 2012-11-22 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2012256941A (ja) * | 2010-05-21 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 記憶装置 |

| JP2012256902A (ja) * | 2010-03-26 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| KR101239231B1 (ko) | 2011-07-22 | 2013-03-11 | 한국과학기술연구원 | 금속을 포함하는 패시배이션 층을 갖는 박막 트랜지스터 및 그 제조 방법 |

| JP2013084939A (ja) * | 2011-09-29 | 2013-05-09 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| JP2013123045A (ja) * | 2011-11-11 | 2013-06-20 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2013153156A (ja) * | 2011-12-27 | 2013-08-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| JP2014175463A (ja) * | 2013-03-08 | 2014-09-22 | Fujifilm Corp | 薄膜トランジスタを備えた半導体装置の製造方法 |

| JP2014195103A (ja) * | 2010-04-23 | 2014-10-09 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2015504246A (ja) * | 2011-12-31 | 2015-02-05 | 京東方科技集團股▲ふん▼有限公司 | 薄膜トランジスタ、アレイ基板及びその製造方法、並びに表示装置 |

| JP2015062246A (ja) * | 2010-02-11 | 2015-04-02 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 薄膜トランジスタパネルおよびそれの製造方法 |

| JP2015097282A (ja) * | 2010-04-16 | 2015-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2015111667A (ja) * | 2013-11-06 | 2015-06-18 | 株式会社半導体エネルギー研究所 | 半導体装置及び該半導体装置を有する表示装置 |

| JP2015111697A (ja) * | 2010-04-28 | 2015-06-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法、及び半導体装置 |

| JP2016034033A (ja) * | 2010-08-27 | 2016-03-10 | 株式会社半導体エネルギー研究所 | 酸化物半導体膜の評価方法 |

| JP2016034027A (ja) * | 2010-04-02 | 2016-03-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2016136647A (ja) * | 2010-11-11 | 2016-07-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016192579A (ja) * | 2011-03-31 | 2016-11-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016197739A (ja) * | 2009-09-04 | 2016-11-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9576982B2 (en) | 2011-11-11 | 2017-02-21 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device, EL display device, and manufacturing method thereof |

| JP2017055134A (ja) * | 2010-04-02 | 2017-03-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI575751B (zh) * | 2011-06-16 | 2017-03-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| JP2017126760A (ja) * | 2010-03-26 | 2017-07-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2017135405A (ja) * | 2010-06-18 | 2017-08-03 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2017523593A (ja) * | 2014-06-26 | 2017-08-17 | インテル・コーポレーション | ドープサブフィン領域があるオメガフィンを有する非プレーナ型半導体デバイスおよびそれを製造する方法 |

| US9831351B2 (en) | 2012-09-24 | 2017-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US10043918B2 (en) | 2011-07-08 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2018186279A (ja) * | 2010-07-02 | 2018-11-22 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10158026B2 (en) | 2012-04-13 | 2018-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including oxide semiconductor stacked layers |

| US10304859B2 (en) | 2013-04-12 | 2019-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an oxide film on an oxide semiconductor film |

| JP2019117937A (ja) * | 2013-12-02 | 2019-07-18 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Families Citing this family (75)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010205987A (ja) * | 2009-03-04 | 2010-09-16 | Sony Corp | 薄膜トランジスタおよびその製造方法並びに表示装置 |

| KR102458127B1 (ko) | 2009-06-30 | 2022-10-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제조 방법 |

| CN102473728B (zh) | 2009-06-30 | 2014-11-26 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| KR101810699B1 (ko) | 2009-06-30 | 2018-01-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작 방법 |

| WO2011013523A1 (en) | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR102153841B1 (ko) | 2009-07-31 | 2020-09-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR102097932B1 (ko) | 2009-07-31 | 2020-04-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 디바이스 및 그 형성 방법 |

| WO2011013502A1 (en) | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101073543B1 (ko) * | 2009-09-04 | 2011-10-17 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| KR20170046186A (ko) * | 2009-09-16 | 2017-04-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| KR101147414B1 (ko) * | 2009-09-22 | 2012-05-22 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR20120106766A (ko) | 2009-11-20 | 2012-09-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| KR20240129225A (ko) | 2009-12-04 | 2024-08-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101649732B1 (ko) * | 2009-12-10 | 2016-08-22 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| KR101084192B1 (ko) | 2010-02-16 | 2011-11-17 | 삼성모바일디스플레이주식회사 | 유기 발광 표시 장치 |

| US9190522B2 (en) | 2010-04-02 | 2015-11-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an oxide semiconductor |

| US9147768B2 (en) | 2010-04-02 | 2015-09-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an oxide semiconductor and a metal oxide film |

| KR101977152B1 (ko) | 2010-04-02 | 2019-05-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US8884282B2 (en) | 2010-04-02 | 2014-11-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR20110114089A (ko) | 2010-04-12 | 2011-10-19 | 삼성모바일디스플레이주식회사 | 박막 트랜지스터, 이의 제조 방법 및 이를 포함하는 표시 장치 |

| KR101800844B1 (ko) | 2010-04-23 | 2017-11-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| CN103500709B (zh) | 2010-04-23 | 2015-09-23 | 株式会社半导体能源研究所 | 半导体装置的制造方法 |

| WO2011132591A1 (en) | 2010-04-23 | 2011-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101806271B1 (ko) | 2010-05-14 | 2017-12-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| US8629438B2 (en) | 2010-05-21 | 2014-01-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| WO2011158704A1 (en) | 2010-06-18 | 2011-12-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101789236B1 (ko) | 2010-12-24 | 2017-10-24 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 평판 표시 장치 |

| CN102157563B (zh) * | 2011-01-18 | 2012-09-19 | 上海交通大学 | 金属氧化物薄膜晶体管制备方法 |

| TWI541904B (zh) | 2011-03-11 | 2016-07-11 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| KR101781532B1 (ko) * | 2011-03-14 | 2017-10-24 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치와 그 제조방법 |

| TWI451573B (zh) | 2011-03-17 | 2014-09-01 | E Ink Holdings Inc | 顯示裝置及其薄膜電晶體結構 |

| US9634029B2 (en) | 2011-03-17 | 2017-04-25 | E Ink Holdings Inc. | Thin film transistor substrate and display device having same |

| CN102208441A (zh) * | 2011-05-03 | 2011-10-05 | 复旦大学 | 一种薄膜晶体管有源层及其生长方法 |

| US8709922B2 (en) * | 2011-05-06 | 2014-04-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9385238B2 (en) | 2011-07-08 | 2016-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Transistor using oxide semiconductor |

| KR102029389B1 (ko) * | 2011-09-02 | 2019-11-08 | 엘지디스플레이 주식회사 | 산화물 박막 트랜지스터를 구비한 평판표시장치 및 그 제조방법 |

| US9018629B2 (en) | 2011-10-13 | 2015-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| JP6226518B2 (ja) * | 2011-10-24 | 2017-11-08 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR20130049620A (ko) * | 2011-11-04 | 2013-05-14 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP6122275B2 (ja) | 2011-11-11 | 2017-04-26 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2013115098A (ja) * | 2011-11-25 | 2013-06-10 | Sony Corp | トランジスタ、トランジスタの製造方法、表示装置および電子機器 |

| CN102751240B (zh) * | 2012-05-18 | 2015-03-11 | 京东方科技集团股份有限公司 | 薄膜晶体管阵列基板及其制造方法、显示面板、显示装置 |

| CN102723344B (zh) * | 2012-06-12 | 2015-07-15 | 南京中电熊猫液晶显示科技有限公司 | 一种阵列基板及其制造方法和液晶显示器 |

| CN103578984B (zh) * | 2012-07-26 | 2016-10-26 | 瀚宇彩晶股份有限公司 | 半导体元件及其制造方法 |

| US8653516B1 (en) * | 2012-08-31 | 2014-02-18 | Eastman Kodak Company | High performance thin film transistor |

| CN102800709B (zh) * | 2012-09-11 | 2015-07-01 | 深圳市华星光电技术有限公司 | 薄膜晶体管主动装置 |

| CN102916051B (zh) * | 2012-10-11 | 2015-09-02 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制作方法、阵列基板和显示装置 |

| CN102955312B (zh) | 2012-11-14 | 2015-05-20 | 京东方科技集团股份有限公司 | 一种阵列基板及其制作方法、显示装置 |

| WO2014104267A1 (en) | 2012-12-28 | 2014-07-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2014181777A1 (ja) | 2013-05-09 | 2014-11-13 | 独立行政法人物質・材料研究機構 | 薄膜トランジスタおよびその製造方法 |

| KR101498522B1 (ko) * | 2013-07-17 | 2015-03-04 | 한국광기술원 | 마이크로 볼로미터용 고특성 산화물 박막 제조방법 |

| KR102130139B1 (ko) | 2013-07-30 | 2020-07-03 | 엘지디스플레이 주식회사 | 산화물 반도체를 이용한 박막 트랜지스터 기판을 포함하는 유기발광 다이오드 표시장치 및 그 제조 방법 |

| KR20150030034A (ko) * | 2013-09-11 | 2015-03-19 | 삼성디스플레이 주식회사 | 표시장치 및 그 제조방법 |

| TWI677989B (zh) | 2013-09-19 | 2019-11-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| DE102013111501B4 (de) | 2013-10-18 | 2024-02-08 | Universität Stuttgart | Dünnschichttransistor und Verfahren zu seiner Herstellung |

| TWI666770B (zh) | 2013-12-19 | 2019-07-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| KR102172972B1 (ko) * | 2014-02-26 | 2020-11-03 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 그의 제조방법 |

| CN104091809B (zh) * | 2014-06-26 | 2017-01-25 | 京东方科技集团股份有限公司 | 一种阵列基板、其制备方法、液晶显示屏及显示装置 |

| CN104538400B (zh) * | 2014-12-16 | 2017-08-04 | 深圳市华星光电技术有限公司 | 一种ltps阵列基板 |

| CN104900711B (zh) | 2015-06-08 | 2019-11-05 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法以及阵列基板、显示装置 |

| TWI650817B (zh) | 2015-08-28 | 2019-02-11 | 聯華電子股份有限公司 | 半導體元件及其製作方法 |

| KR20170027932A (ko) * | 2015-09-02 | 2017-03-13 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| KR102483953B1 (ko) * | 2015-10-16 | 2023-01-03 | 삼성디스플레이 주식회사 | 박막트랜지스터 기판 및 이를 구비한 유기 발광 표시 장치 |

| CN105633170A (zh) * | 2016-02-23 | 2016-06-01 | 广州新视界光电科技有限公司 | 金属氧化物薄膜晶体管及其制备方法以及阵列基板和显示装置 |

| CN105742297B (zh) * | 2016-04-13 | 2019-09-24 | 深圳市华星光电技术有限公司 | 薄膜晶体管阵列面板及其制作方法 |

| CN109417099A (zh) * | 2016-04-25 | 2019-03-01 | 堺显示器制品株式会社 | 薄膜晶体管、显示装置和薄膜晶体管制造方法 |

| KR102660292B1 (ko) * | 2016-06-23 | 2024-04-24 | 삼성디스플레이 주식회사 | 박막 트랜지스터 패널 및 그 제조 방법 |

| CN106252362B (zh) * | 2016-08-31 | 2019-07-12 | 深圳市华星光电技术有限公司 | 一种阵列基板及其制备方法 |

| US11257722B2 (en) | 2017-07-31 | 2022-02-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide containing gallium indium and zinc |

| CN107507850B (zh) * | 2017-08-11 | 2020-02-14 | 京东方科技集团股份有限公司 | 一种阵列基板及其制作方法、显示装置 |

| JP7147953B2 (ja) * | 2019-02-25 | 2022-10-05 | 株式会社ニコン | 半導体装置、pHセンサ及びバイオセンサ並びに半導体装置の製造方法 |

| KR102333694B1 (ko) * | 2020-04-28 | 2021-11-30 | 연세대학교 산학협력단 | 생체 구조 모방형 다공성 산화물 반도체 기반의 고감도 전기-화학 센서 제조 방법 |

| CN113838801B (zh) * | 2020-06-24 | 2024-10-22 | 京东方科技集团股份有限公司 | 半导体基板的制造方法和半导体基板 |

| US12439650B2 (en) * | 2021-01-15 | 2025-10-07 | Taiwan Semiconductor Manufacturing Co., Ltd. | CMOS fabrication methods for back-gate transistor |

| JP2025509535A (ja) * | 2022-03-14 | 2025-04-11 | ジュスン エンジニアリング カンパニー リミテッド | 薄膜トランジスター及びその製造方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005033172A (ja) * | 2003-06-20 | 2005-02-03 | Sharp Corp | 半導体装置およびその製造方法ならびに電子デバイス |

| JP2007073559A (ja) * | 2005-09-02 | 2007-03-22 | Kochi Prefecture Sangyo Shinko Center | 薄膜トランジスタの製法 |

| JP2007258675A (ja) * | 2006-02-21 | 2007-10-04 | Idemitsu Kosan Co Ltd | Tft基板及び反射型tft基板並びにそれらの製造方法 |

| JP2007281486A (ja) * | 2006-04-11 | 2007-10-25 | Samsung Electronics Co Ltd | ZnO薄膜トランジスタ |

| WO2008069056A1 (en) * | 2006-12-05 | 2008-06-12 | Canon Kabushiki Kaisha | Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus |

Family Cites Families (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6577011B1 (en) * | 1997-07-10 | 2003-06-10 | International Business Machines Corporation | Chip interconnect wiring structure with low dielectric constant insulator and methods for fabricating the same |

| KR100425858B1 (ko) * | 1998-07-30 | 2004-08-09 | 엘지.필립스 엘시디 주식회사 | 박막트랜지스터및그제조방법 |

| WO2001084230A1 (en) * | 2000-05-04 | 2001-11-08 | Schott Donnelly Llc | Chromogenic glazing |

| KR100367009B1 (ko) * | 2000-05-19 | 2003-01-09 | 엘지.필립스 엘시디 주식회사 | 액정표시소자 및 그 제조방법 |

| KR100720093B1 (ko) * | 2000-10-04 | 2007-05-18 | 삼성전자주식회사 | 액정 표시 장치 |

| KR100586241B1 (ko) * | 2000-10-28 | 2006-06-02 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 및 제조방법 |

| KR100413668B1 (ko) * | 2001-03-29 | 2003-12-31 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| US6794220B2 (en) * | 2001-09-05 | 2004-09-21 | Konica Corporation | Organic thin-film semiconductor element and manufacturing method for the same |

| KR100870697B1 (ko) * | 2002-03-07 | 2008-11-27 | 엘지디스플레이 주식회사 | 저저항 구리배선 형성방법 |

| KR100432544B1 (ko) * | 2002-03-18 | 2004-05-24 | 박병주 | 매트릭스형 3 극성 유기 el 표시장치 |

| KR20030078355A (ko) * | 2002-03-29 | 2003-10-08 | 삼성전자주식회사 | 수직 배향형 액정 표시 장치 |

| JP3501155B1 (ja) * | 2002-07-03 | 2004-03-02 | 富士電機ホールディングス株式会社 | 有機elディスプレイおよびその製造方法 |

| TWI224880B (en) * | 2002-07-25 | 2004-12-01 | Sanyo Electric Co | Organic electroluminescence display device |

| US7109119B2 (en) * | 2002-10-31 | 2006-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Scum solution for chemically amplified resist patterning in cu/low k dual damascene |

| JP4588445B2 (ja) * | 2002-11-11 | 2010-12-01 | 株式会社半導体エネルギー研究所 | 発光装置の作製方法 |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004335207A (ja) * | 2003-05-02 | 2004-11-25 | Fuji Electric Holdings Co Ltd | 有機el素子とその製造方法 |

| US7462514B2 (en) * | 2004-03-03 | 2008-12-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same, liquid crystal television, and EL television |

| US7531294B2 (en) * | 2004-03-25 | 2009-05-12 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming film pattern, method for manufacturing semiconductor device, liquid crystal television, and EL television |

| US7223641B2 (en) * | 2004-03-26 | 2007-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, method for manufacturing the same, liquid crystal television and EL television |

| EP1732054A4 (en) * | 2004-03-30 | 2009-03-18 | Idemitsu Kosan Co | ORGANIC ELECTROLUMINESCENCE DISPLAY INSTALLATION |

| WO2006025473A1 (en) * | 2004-08-31 | 2006-03-09 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| JP5110762B2 (ja) | 2004-09-24 | 2012-12-26 | 日本碍子株式会社 | 半導体積層構造およびhemt素子 |

| KR100670255B1 (ko) * | 2004-12-23 | 2007-01-16 | 삼성에스디아이 주식회사 | 박막 트랜지스터, 이를 구비한 평판표시장치, 상기 박막트랜지스터의 제조방법, 및 상기 평판 표시장치의 제조방법 |

| JP4631683B2 (ja) * | 2005-01-17 | 2011-02-16 | セイコーエプソン株式会社 | 発光装置、及び電子機器 |

| TWI562380B (en) * | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7645478B2 (en) * | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US7732330B2 (en) * | 2005-06-30 | 2010-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method using an ink-jet method of the same |

| KR101293564B1 (ko) * | 2005-07-27 | 2013-08-06 | 삼성디스플레이 주식회사 | 액정표시장치 |

| KR100719706B1 (ko) * | 2005-09-13 | 2007-05-17 | 삼성에스디아이 주식회사 | 평판표시장치 및 유기 발광표시장치 |

| KR101174780B1 (ko) * | 2005-09-14 | 2012-08-20 | 엘지디스플레이 주식회사 | 박막트랜지스터의 제조방법 및 이를 적용한 액정표시소자의제조방법 |

| KR100786498B1 (ko) * | 2005-09-27 | 2007-12-17 | 삼성에스디아이 주식회사 | 투명박막 트랜지스터 및 그 제조방법 |

| JP5064747B2 (ja) * | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| KR101217157B1 (ko) * | 2005-10-20 | 2012-12-31 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 그 제조 방법 |

| KR20070053060A (ko) * | 2005-11-19 | 2007-05-23 | 삼성전자주식회사 | 표시장치와 이의 제조방법 |

| EP1981085A4 (en) | 2006-01-31 | 2009-11-25 | Idemitsu Kosan Co | TFT SUBSTRATE, REFLECTIVE TFT SUBSTRATE AND MANUFACTURING PROCESS FOR SUCH SUBSTRATES |

| KR100754395B1 (ko) | 2006-02-10 | 2007-08-31 | 삼성전자주식회사 | 유기 전자발광 디스플레이 및 그 제조방법 |

| KR20080006304A (ko) * | 2006-07-12 | 2008-01-16 | 삼성전자주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| US20080023703A1 (en) | 2006-07-31 | 2008-01-31 | Randy Hoffman | System and method for manufacturing a thin-film device |

| JP5127183B2 (ja) * | 2006-08-23 | 2013-01-23 | キヤノン株式会社 | アモルファス酸化物半導体膜を用いた薄膜トランジスタの製造方法 |

| EP2064732A4 (en) * | 2006-10-19 | 2012-07-25 | Semiconductor Energy Lab | Semiconductor device and method for manufacturing the same |

| CN101563796B (zh) * | 2006-11-14 | 2011-07-06 | 出光兴产株式会社 | 有机薄膜晶体管和有机薄膜发光晶体管 |

| KR101031713B1 (ko) * | 2006-12-22 | 2011-04-29 | 엘지디스플레이 주식회사 | 박막트랜지스터 기판과 이의 제조방법 |

| KR20080077846A (ko) * | 2007-02-21 | 2008-08-26 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR101345378B1 (ko) * | 2007-05-17 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| KR20100047828A (ko) * | 2007-06-01 | 2010-05-10 | 노오쓰웨스턴 유니버시티 | 투명한 나노와이어 트랜지스터 및 그 제조 방법 |

| US7682882B2 (en) * | 2007-06-20 | 2010-03-23 | Samsung Electronics Co., Ltd. | Method of manufacturing ZnO-based thin film transistor |

-

2008

- 2008-07-08 KR KR1020080066002A patent/KR100963104B1/ko active Active

-

2009

- 2009-02-26 US US12/393,422 patent/US8178884B2/en active Active

- 2009-03-11 JP JP2009058255A patent/JP5542352B2/ja active Active

- 2009-04-14 CN CN200910133952.XA patent/CN101626036B/zh active Active

- 2009-07-08 EP EP09164894.9A patent/EP2144294B1/en active Active

-

2011

- 2011-10-19 US US13/276,884 patent/US8193535B2/en active Active

-

2012

- 2012-05-02 US US13/462,535 patent/US8728862B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005033172A (ja) * | 2003-06-20 | 2005-02-03 | Sharp Corp | 半導体装置およびその製造方法ならびに電子デバイス |

| JP2007073559A (ja) * | 2005-09-02 | 2007-03-22 | Kochi Prefecture Sangyo Shinko Center | 薄膜トランジスタの製法 |

| JP2007258675A (ja) * | 2006-02-21 | 2007-10-04 | Idemitsu Kosan Co Ltd | Tft基板及び反射型tft基板並びにそれらの製造方法 |

| JP2007281486A (ja) * | 2006-04-11 | 2007-10-25 | Samsung Electronics Co Ltd | ZnO薄膜トランジスタ |

| WO2008069056A1 (en) * | 2006-12-05 | 2008-06-12 | Canon Kabushiki Kaisha | Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus |

Cited By (144)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2022169538A (ja) * | 2009-07-31 | 2022-11-09 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US20180138211A1 (en) | 2009-07-31 | 2018-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing oxide semiconductor device |

| US11348949B2 (en) | 2009-07-31 | 2022-05-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9786689B2 (en) | 2009-07-31 | 2017-10-10 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP7304466B2 (ja) | 2009-07-31 | 2023-07-06 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| WO2011013561A1 (en) * | 2009-07-31 | 2011-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP2014225687A (ja) * | 2009-07-31 | 2014-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11728350B2 (en) | 2009-07-31 | 2023-08-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including transistor |

| US8822990B2 (en) | 2009-07-31 | 2014-09-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US12183743B2 (en) | 2009-07-31 | 2024-12-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8546180B2 (en) | 2009-07-31 | 2013-10-01 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing oxide semiconductor device |

| US9293601B2 (en) | 2009-07-31 | 2016-03-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US10854638B2 (en) | 2009-07-31 | 2020-12-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing display device |

| US9224870B2 (en) | 2009-07-31 | 2015-12-29 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor device |

| US10396097B2 (en) | 2009-07-31 | 2019-08-27 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing oxide semiconductor device |

| US12272697B2 (en) | 2009-09-04 | 2025-04-08 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| US11094717B2 (en) | 2009-09-04 | 2021-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| US10665615B2 (en) | 2009-09-04 | 2020-05-26 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| US11862643B2 (en) | 2009-09-04 | 2024-01-02 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| US9954007B2 (en) | 2009-09-04 | 2018-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| US10418384B2 (en) | 2009-09-04 | 2019-09-17 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and display device |

| JP2016197739A (ja) * | 2009-09-04 | 2016-11-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2015062246A (ja) * | 2010-02-11 | 2015-04-02 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 薄膜トランジスタパネルおよびそれの製造方法 |

| US9520412B2 (en) | 2010-02-11 | 2016-12-13 | Samsung Display Co., Ltd. | Thin film transistor panel having an etch stopper on semiconductor |

| US9443877B2 (en) | 2010-02-11 | 2016-09-13 | Samsung Display Co., Ltd. | Thin film transistor panel having an etch stopper on semiconductor |

| JP2011199273A (ja) * | 2010-02-26 | 2011-10-06 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US9269571B2 (en) | 2010-02-26 | 2016-02-23 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2015092621A (ja) * | 2010-02-26 | 2015-05-14 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2022027774A (ja) * | 2010-03-26 | 2022-02-14 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2020014023A (ja) * | 2010-03-26 | 2020-01-23 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9954084B2 (en) | 2010-03-26 | 2018-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2011222984A (ja) * | 2010-03-26 | 2011-11-04 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US9941414B2 (en) | 2010-03-26 | 2018-04-10 | Semiconductor Energy Laboratory Co., Ltd. | Metal oxide semiconductor device |

| JP2018078346A (ja) * | 2010-03-26 | 2018-05-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2018166210A (ja) * | 2010-03-26 | 2018-10-25 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2011222982A (ja) * | 2010-03-26 | 2011-11-04 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2019009467A (ja) * | 2010-03-26 | 2019-01-17 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| US8461584B2 (en) | 2010-03-26 | 2013-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with metal oxide film |

| JP2017126760A (ja) * | 2010-03-26 | 2017-07-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2017073558A (ja) * | 2010-03-26 | 2017-04-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2016021580A (ja) * | 2010-03-26 | 2016-02-04 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9425295B2 (en) | 2010-03-26 | 2016-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US8704219B2 (en) | 2010-03-26 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US9012908B2 (en) | 2010-03-26 | 2015-04-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with metal oxide film |

| JP7279141B2 (ja) | 2010-03-26 | 2023-05-22 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2012256902A (ja) * | 2010-03-26 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2017028315A (ja) * | 2010-03-26 | 2017-02-02 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2020065091A (ja) * | 2010-03-26 | 2020-04-23 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US10608116B2 (en) | 2010-04-02 | 2020-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US12249653B2 (en) | 2010-04-02 | 2025-03-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2017055134A (ja) * | 2010-04-02 | 2017-03-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016034027A (ja) * | 2010-04-02 | 2016-03-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US11411121B2 (en) | 2010-04-02 | 2022-08-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9431429B2 (en) | 2010-04-09 | 2016-08-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2018195858A (ja) * | 2010-04-09 | 2018-12-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2016021584A (ja) * | 2010-04-09 | 2016-02-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9059047B2 (en) | 2010-04-09 | 2015-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2020150266A (ja) * | 2010-04-09 | 2020-09-17 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2022111119A (ja) * | 2010-04-09 | 2022-07-29 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10008515B2 (en) | 2010-04-09 | 2018-06-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US10510777B2 (en) | 2010-04-09 | 2019-12-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2011233876A (ja) * | 2010-04-09 | 2011-11-17 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US10879274B2 (en) | 2010-04-09 | 2020-12-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP7302068B2 (ja) | 2010-04-09 | 2023-07-03 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2017123499A (ja) * | 2010-04-09 | 2017-07-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9698008B2 (en) | 2010-04-16 | 2017-07-04 | Semiconductor Energy Laboratory Co., Ltd. | Deposition method and method for manufacturing semiconductor device |

| JP2015097282A (ja) * | 2010-04-16 | 2015-05-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US10529556B2 (en) | 2010-04-16 | 2020-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Deposition method and method for manufacturing semiconductor device |

| JP2016106408A (ja) * | 2010-04-23 | 2016-06-16 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9147754B2 (en) | 2010-04-23 | 2015-09-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US9978878B2 (en) | 2010-04-23 | 2018-05-22 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| US9373707B2 (en) | 2010-04-23 | 2016-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device with steps of heat treatment in nitrogen containing atmosphere, oxygen doping treatment and heat treatment in oxygen containing atmosphere |

| JP2011243972A (ja) * | 2010-04-23 | 2011-12-01 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法、及び半導体装置 |

| US9390918B2 (en) | 2010-04-23 | 2016-07-12 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| JP2015065467A (ja) * | 2010-04-23 | 2015-04-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2014195103A (ja) * | 2010-04-23 | 2014-10-09 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2011243973A (ja) * | 2010-04-23 | 2011-12-01 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2015164225A (ja) * | 2010-04-23 | 2015-09-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2015111697A (ja) * | 2010-04-28 | 2015-06-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法、及び半導体装置 |

| US9449852B2 (en) | 2010-04-28 | 2016-09-20 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2016119488A (ja) * | 2010-04-28 | 2016-06-30 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2014207472A (ja) * | 2010-05-21 | 2014-10-30 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9299723B2 (en) | 2010-05-21 | 2016-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with light-blocking layers |

| JP2012256941A (ja) * | 2010-05-21 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 記憶装置 |

| JP2015195399A (ja) * | 2010-06-01 | 2015-11-05 | 株式会社半導体エネルギー研究所 | 電子機器の作製方法 |

| US9812560B2 (en) | 2010-06-01 | 2017-11-07 | Semiconductor Energy Laboratory Co., Ltd. | Field effect transistor and method for manufacturing the same |

| JP2017050572A (ja) * | 2010-06-01 | 2017-03-09 | 株式会社半導体エネルギー研究所 | 電子機器の作製方法 |

| JP2012015496A (ja) * | 2010-06-01 | 2012-01-19 | Semiconductor Energy Lab Co Ltd | 電界効果トランジスタおよびその作製方法 |

| JP2012231100A (ja) * | 2010-06-11 | 2012-11-22 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US9755082B2 (en) | 2010-06-11 | 2017-09-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including oxide semiconductor with an insulating film including galliium and oxygen |

| JP2017135405A (ja) * | 2010-06-18 | 2017-08-03 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2018186279A (ja) * | 2010-07-02 | 2018-11-22 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2012028481A (ja) * | 2010-07-22 | 2012-02-09 | Fujifilm Corp | 電界効果型トランジスタ及びその製造方法 |

| JP2016034033A (ja) * | 2010-08-27 | 2016-03-10 | 株式会社半導体エネルギー研究所 | 酸化物半導体膜の評価方法 |

| JP2017096959A (ja) * | 2010-08-27 | 2017-06-01 | 株式会社半導体エネルギー研究所 | 酸化物半導体膜の評価方法 |

| US11631756B2 (en) | 2010-11-11 | 2023-04-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US10153360B2 (en) | 2010-11-11 | 2018-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP2016136647A (ja) * | 2010-11-11 | 2016-07-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10811522B2 (en) | 2010-11-11 | 2020-10-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9673305B2 (en) | 2010-11-11 | 2017-06-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP2012160720A (ja) * | 2011-01-12 | 2012-08-23 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| US9882062B2 (en) | 2011-01-12 | 2018-01-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9349752B2 (en) | 2011-01-12 | 2016-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9917204B2 (en) | 2011-03-31 | 2018-03-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2016192579A (ja) * | 2011-03-31 | 2016-11-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI575751B (zh) * | 2011-06-16 | 2017-03-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| US11588058B2 (en) | 2011-07-08 | 2023-02-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US11011652B2 (en) | 2011-07-08 | 2021-05-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US10658522B2 (en) | 2011-07-08 | 2020-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US10043918B2 (en) | 2011-07-08 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US12132121B2 (en) | 2011-07-08 | 2024-10-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101239231B1 (ko) | 2011-07-22 | 2013-03-11 | 한국과학기술연구원 | 금속을 포함하는 패시배이션 층을 갖는 박막 트랜지스터 및 그 제조 방법 |

| JP2013084939A (ja) * | 2011-09-29 | 2013-05-09 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| US9159806B2 (en) | 2011-09-29 | 2015-10-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9343585B2 (en) | 2011-09-29 | 2016-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9576982B2 (en) | 2011-11-11 | 2017-02-21 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device, EL display device, and manufacturing method thereof |

| JP2024111158A (ja) * | 2011-11-11 | 2024-08-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2013123045A (ja) * | 2011-11-11 | 2013-06-20 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US12046604B2 (en) | 2011-11-11 | 2024-07-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device, EL display device, and manufacturing method thereof |

| US9502572B2 (en) | 2011-12-27 | 2016-11-22 | Semiconductor Energy Laboratory Co., Ltd. | Bottom-gate transistor including an oxide semiconductor layer contacting an oxygen-rich insulating layer |

| JP2013153156A (ja) * | 2011-12-27 | 2013-08-08 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| JP2015504246A (ja) * | 2011-12-31 | 2015-02-05 | 京東方科技集團股▲ふん▼有限公司 | 薄膜トランジスタ、アレイ基板及びその製造方法、並びに表示装置 |

| US11355645B2 (en) | 2012-04-13 | 2022-06-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising stacked oxide semiconductor layers |

| US12414335B2 (en) | 2012-04-13 | 2025-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising conductive layers functioning as first and second gate electrodes of a transistor |

| US10158026B2 (en) | 2012-04-13 | 2018-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including oxide semiconductor stacked layers |

| US10872981B2 (en) | 2012-04-13 | 2020-12-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising an oxide semiconductor |

| US10559699B2 (en) | 2012-04-13 | 2020-02-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US11929437B2 (en) | 2012-04-13 | 2024-03-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising various thin-film transistors |

| US10211345B2 (en) | 2012-09-24 | 2019-02-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US20180083140A1 (en) | 2012-09-24 | 2018-03-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US12125918B2 (en) | 2012-09-24 | 2024-10-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9831351B2 (en) | 2012-09-24 | 2017-11-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US11094830B2 (en) | 2012-09-24 | 2021-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2014175463A (ja) * | 2013-03-08 | 2014-09-22 | Fujifilm Corp | 薄膜トランジスタを備えた半導体装置の製造方法 |

| US11843004B2 (en) | 2013-04-12 | 2023-12-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having specified relative material concentration between In—Ga—Zn—O films |

| US10304859B2 (en) | 2013-04-12 | 2019-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having an oxide film on an oxide semiconductor film |

| US11063066B2 (en) | 2013-04-12 | 2021-07-13 | Semiconductor Energy Laboratory Co., Ltd. | C-axis alignment of an oxide film over an oxide semiconductor film |

| US12218144B2 (en) | 2013-04-12 | 2025-02-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having specified relative material concentration between In—Ga—Zn—O films |

| JP2015111667A (ja) * | 2013-11-06 | 2015-06-18 | 株式会社半導体エネルギー研究所 | 半導体装置及び該半導体装置を有する表示装置 |

| JP2019165251A (ja) * | 2013-11-06 | 2019-09-26 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2019117937A (ja) * | 2013-12-02 | 2019-07-18 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11276760B2 (en) | 2014-06-26 | 2022-03-15 | Intel Corporation | Non-planar semiconductor device having omega-fin with doped sub-fin region and method to fabricate same |

| US10355093B2 (en) | 2014-06-26 | 2019-07-16 | Intel Corporation | Non-planar semiconductor device having omega-fin with doped sub-fin region and method to fabricate same |

| JP2017523593A (ja) * | 2014-06-26 | 2017-08-17 | インテル・コーポレーション | ドープサブフィン領域があるオメガフィンを有する非プレーナ型半導体デバイスおよびそれを製造する方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20100005900A (ko) | 2010-01-18 |

| US20120220077A1 (en) | 2012-08-30 |

| US8728862B2 (en) | 2014-05-20 |

| CN101626036B (zh) | 2015-11-25 |

| EP2144294B1 (en) | 2018-11-21 |

| US20100006833A1 (en) | 2010-01-14 |

| US8193535B2 (en) | 2012-06-05 |

| EP2144294A1 (en) | 2010-01-13 |

| JP5542352B2 (ja) | 2014-07-09 |

| US20120033152A1 (en) | 2012-02-09 |

| US8178884B2 (en) | 2012-05-15 |

| KR100963104B1 (ko) | 2010-06-14 |

| CN101626036A (zh) | 2010-01-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5542352B2 (ja) | 薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置 | |

| JP5474372B2 (ja) | 薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置 | |

| JP5399274B2 (ja) | 薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備える平板表示装置 | |

| KR100975204B1 (ko) | 박막 트랜지스터, 그의 제조 방법 및 박막 트랜지스터를구비하는 평판 표시 장치 | |

| JP5474374B2 (ja) | 薄膜トランジスタ、その製造方法及び薄膜トランジスタを備える平板表示装置 | |

| KR100941850B1 (ko) | 박막 트랜지스터, 그의 제조 방법 및 박막 트랜지스터를구비하는 평판 표시 장치 | |

| US7994510B2 (en) | Thin film transistor, method of manufacturing the same and flat panel display device having the same | |

| KR100963003B1 (ko) | 박막 트랜지스터, 그의 제조 방법 및 박막 트랜지스터를구비하는 평판 표시 장치 | |

| JP2011082487A (ja) | 薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備える有機電界発光表示装置 | |

| KR100941855B1 (ko) | 박막 트랜지스터, 그의 제조 방법 및 박막 트랜지스터를구비하는 평판 표시 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120626 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120628 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20120924 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120925 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130524 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130917 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131022 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20131217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140305 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140408 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140507 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5542352 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |