CN1173218C - 液晶显示装置及其制造方法和驱动方法 - Google Patents

液晶显示装置及其制造方法和驱动方法 Download PDFInfo

- Publication number

- CN1173218C CN1173218C CNB981271723A CN98127172A CN1173218C CN 1173218 C CN1173218 C CN 1173218C CN B981271723 A CNB981271723 A CN B981271723A CN 98127172 A CN98127172 A CN 98127172A CN 1173218 C CN1173218 C CN 1173218C

- Authority

- CN

- China

- Prior art keywords

- electrode

- silicon layer

- insulating film

- gate insulating

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims abstract description 34

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 19

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 23

- 238000003860 storage Methods 0.000 claims abstract description 224

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 112

- 239000010703 silicon Substances 0.000 claims abstract description 112

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 107

- 239000000758 substrate Substances 0.000 claims abstract description 25

- 239000010408 film Substances 0.000 claims description 238

- 239000010410 layer Substances 0.000 claims description 149

- 239000011229 interlayer Substances 0.000 claims description 68

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 17

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 11

- 229920005591 polysilicon Polymers 0.000 claims description 10

- 239000010409 thin film Substances 0.000 claims description 10

- 238000010438 heat treatment Methods 0.000 claims description 7

- 238000009413 insulation Methods 0.000 claims description 7

- 239000003990 capacitor Substances 0.000 abstract description 106

- 229910052751 metal Inorganic materials 0.000 abstract description 81

- 239000002184 metal Substances 0.000 abstract description 81

- 238000002161 passivation Methods 0.000 abstract description 4

- 150000002500 ions Chemical class 0.000 description 17

- 238000005530 etching Methods 0.000 description 14

- 239000000463 material Substances 0.000 description 12

- 239000004020 conductor Substances 0.000 description 11

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 9

- 238000010586 diagram Methods 0.000 description 9

- 238000009825 accumulation Methods 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 238000002156 mixing Methods 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 5

- 238000010276 construction Methods 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- 238000002425 crystallisation Methods 0.000 description 4

- 230000008025 crystallization Effects 0.000 description 4

- 238000006073 displacement reaction Methods 0.000 description 4

- 230000009977 dual effect Effects 0.000 description 4

- 230000005611 electricity Effects 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000014509 gene expression Effects 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- DJQYKWDYUQPOOE-OGRLCSSISA-N (2s,3s)-2-[4-[(1s)-1-amino-3-methylbutyl]triazol-1-yl]-1-[4-[4-[4-[(2s,3s)-2-[4-[(1s)-1-amino-3-methylbutyl]triazol-1-yl]-3-methylpentanoyl]piperazin-1-yl]-6-[2-[2-(2-prop-2-ynoxyethoxy)ethoxy]ethylamino]-1,3,5-triazin-2-yl]piperazin-1-yl]-3-methylpentan- Chemical compound Cl.N1([C@@H]([C@@H](C)CC)C(=O)N2CCN(CC2)C=2N=C(NCCOCCOCCOCC#C)N=C(N=2)N2CCN(CC2)C(=O)[C@H]([C@@H](C)CC)N2N=NC(=C2)[C@@H](N)CC(C)C)C=C([C@@H](N)CC(C)C)N=N1 DJQYKWDYUQPOOE-OGRLCSSISA-N 0.000 description 2

- 101000746134 Homo sapiens DNA endonuclease RBBP8 Proteins 0.000 description 2

- 101000969031 Homo sapiens Nuclear protein 1 Proteins 0.000 description 2

- 229910016048 MoW Inorganic materials 0.000 description 2

- 102100021133 Nuclear protein 1 Human genes 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 150000003376 silicon Chemical class 0.000 description 2

- 206010021703 Indifference Diseases 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 239000004411 aluminium Substances 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- RVPVRDXYQKGNMQ-UHFFFAOYSA-N lead(2+) Chemical compound [Pb+2] RVPVRDXYQKGNMQ-UHFFFAOYSA-N 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 238000007669 thermal treatment Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- MEYZYGMYMLNUHJ-UHFFFAOYSA-N tunicamycin Natural products CC(C)CCCCCCCCCC=CC(=O)NC1C(O)C(O)C(CC(O)C2OC(C(O)C2O)N3C=CC(=O)NC3=O)OC1OC4OC(CO)C(O)C(O)C4NC(=O)C MEYZYGMYMLNUHJ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Nonlinear Science (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

Abstract

一种液晶显示装置及其制造方法和驱动方法,在绝缘衬底上形成存储电容的源电极和金属图案,衬底上形成具有掺杂的源极区和漏极区的硅层且源极区和漏极区直接与源电极和金属图案接触,其上形成栅极绝缘膜并在栅极绝缘膜上与金属图案相对形成存储电极。在存储电极上形成钝化膜及其上形成像素电极,像素电极直接与漏极区或金属图案连接。

Description

技术领域

本发明涉及含存储电容器的液晶显示装置及其制造方法和驱动方法。

背景技术

通常,薄膜晶体管液晶显示装置(TFT-LCD)包括传输显示信号的数据线、传输扫描信号的选通线、作为开关器件的薄膜晶体管(TFT)、液晶电容器和存储电容器。根据存储电容器的结构可将TFT-LCD分为两种模式。一种模式有一接至存储电极的隔离存储线,而另一种模式将存储电容器接至前一条选通线。

以下将描述在前一模式下驱动LCD的原理和一种传统结构。

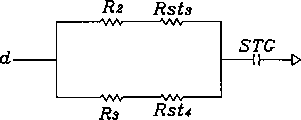

图1是一传统LCD的等效电路图。

多条选通线G1和G2与多条数据线D1、D2和D3分别沿水平方向和垂直方向延伸。选通线G1和G2与数据线D1、D2和D3相交以限定多个像素。存储线COM1和COM2穿过各像素,每个像素中形成一个TFT。TFT的栅电极(g)接至选通线G1和G2,该TFT的源电极和漏电极(s和d)分别接至数据线和液晶电容器(LC)。漏电极(d)接至存储线COM1或COM2以形成存储电容器(STG)。

若通过选通线G1将选通电压加到TFT的栅电极(g)上,则经TFT把来自数据线的显示信号电压传输给像素并在液晶电容器(LC)和存储电容器(STG)中充电。保持该充电电压,直到将下一帧中下一个选通电压加到像素中为止。通常,当栅极电压从开电平转到关电平时,充电电压稍有下降。存储电容器减小这一压降。

TFT具有作为有源层的非晶硅层或多晶硅层,根据栅电极和有源层之间的相对位置,将它们分为上栅极模式和下栅极模式。在TFT具有多晶硅层的情况下,主要采用上栅模式。

传统多晶硅TFT-LCD的一种存储电容器包括硅层中的掺杂存储区、与该存储区相交叠的存储电极和夹在二者之间的栅极绝缘膜。另外,用存储电极、与存储电极相交叠的像素电极和含夹在像素电极与存储电极之间的层间绝缘膜和钝化膜的电介质形成另一种存储电容器。但是,像素电极和存储电极之间的电容较小,可忽略不计,原因在于层间绝缘膜和钝化膜各自约为5000的厚度远大于栅极绝缘膜500~3000的厚度。

在该传统结构中,要求增加离子注入步骤以形成存储区。换句话说,要求有以下步骤,即:淀积感光膜;利用掩模对感光膜制作图案以形成开口;通过开口将离子注入硅层和对注入的离子进行热处理。

发明内容

因此,本发明的一个目的在于,通过在形成TFT和存储电容器的步骤中去掉光刻和离子注入的步骤来减少制造步骤。

本发明的另一个目的在于得到一个足够大的存储电容。

本发明还一目的在于减少像素间的存储电容差。

本发明的再一目的在于减小存储区中的有效电阻,存储区用作存储电容器的一个电极。

为实现这些目的,根据本发明的一种LCD的硅层包括:掺杂的源极区,掺杂的漏极区,未掺杂的沟道区和未掺杂的存储电容器区。沟道区位于源极区和漏极区之间,存储电容器区邻接漏极区。在硅层上形成栅极绝缘膜,在沟道区对面的栅极绝缘膜上形成栅电极,在存储电容器区对面形成一存储电极。换句话说,一存储电容器包括存储电容器区、存储电极和夹在其间的栅极绝缘膜。由于存储电容器区未掺杂,所以通过向存储电极施加等于或大于TFT阈值电压与显示信号电压最大值之和的电压,可以使用该存储电容器。

通过形成一硅层和一栅极绝缘膜、形成一栅电极和一存储电极以及用栅电极和存储电极作为掩模将离子注入硅层来制造LCD。

为实现上述目的,在根据本发明的另一种LCD中,形成一源电极的金属图案和存储电极的金属图案,在两图案上形成一硅层。掺杂接触这些图案的硅层各区,使它们变成源极区和漏极区。在硅层和存储电极的金属图案上形成一栅极绝缘膜,在存储电极金属图案对面的栅极绝缘膜上形成一存储电极。换句话说,一存储电容器包括存储电极的金属图案、存储电极和夹在其间的栅极绝缘膜。

由于在存储电极上形成一钝化膜,并且在存储电极对面的钝化膜上形成一像素电极,所以可以形成包括像素电极、存储电极和钝化膜的另一存储电容器。

像素电极可以接触硅层的漏极区和存储电极的金属图案。

在该制造方法中,通过形成由数据导线的金属制成的存储电极金属图案,然后在存储电极的金属图案上形成一硅层,就省去了形成接触孔以便将一硅层连接到存储电极的金属图案上的步骤。

为实现上述目的,在根据本发明的另一LCD中,在一栅极绝缘膜上形成一栅电极和一存储电极,该栅极绝缘膜形成于一绝缘衬底上,一个层间绝缘膜覆盖栅电极和存储电极。在层间绝缘膜上形成一钝化膜。由于去除了钝化膜的特定厚度以及存储电极上的层间绝缘膜,所以可以使存储电容器的电介质厚度更薄,即,可以使电容增大。

可以对层间绝缘膜采用双叠层结构或三叠层结构,以使厚度均匀。这样,最上层由具有与钝化膜类似蚀刻率的材料制成,而下层由具有比最上层更小蚀刻率的材料制成,以便去除最上层,而在去除存储电极之上的钝化膜的步骤中保留其它层。

为实现上述目的,根据本发明的LCD的硅层包括:一掺杂的源极区和漏极区、一未掺杂的沟道区、一掺杂的存储电容器区和分区。沟道区位于源极区和漏极区之间,存储区邻接漏极区而与沟道区隔开,分区邻接存储电容器区的边缘并接至漏极区。在硅层上形成一栅极绝缘膜,在各个沟道区和存储电容器区对面的栅极绝缘膜上形成一栅电极和一存储电极。换句话说,一存储电容器包括存储电容器区、存储电极和夹在其间的栅极绝缘膜。由于未掺杂,所以在截止状态下不能将存储电容器区用作一存储电容器的一个电极,但在导通状态下可将其用作一存储电容器的一个电极,其中在导通状态下,把等于或大于TFT阈值电压与图像信号最大值之和的电压施加到存储电极上。在该结构中,由于分区变成传输电荷路径的一部分,所以累积层的电阻减小。

通过形成一硅层和一栅极绝缘膜、于其上形成一栅电极和一存储电极、以及然后用栅电极和存储电极作为掩模将离子注入硅层中,可以制造这种LCD。

为实现上述目的,在本发明的另一种LCD中,在一绝缘衬底上形成一硅层,一栅极绝缘膜覆盖该硅层,该硅层包括一掺杂的源极区和漏极区以及夹在源极区与漏极区之间的未掺杂的沟道区。在沟道区对面的栅极绝缘膜上形成一栅电极,并且形成一存储电容,该存储电容包括:由选通导线的金属制成的下存储电容器电极;该存储电容器电极上的绝缘膜和该绝缘膜上的上存储电容器电极。把上存储电容器电极接至一透明像素电极。

要求形成上、下存储电容器电极和具有同样图案的绝缘膜。

此外,上、下存储电容器电极和夹在其间的绝缘膜中的每一个都可以是双叠层或多叠层。

在以上LCD的制造方法中,通过以下步骤制造存储电容器:按顺序淀积一选通导线的金属膜、存储电容器的绝缘膜和存储电容器的金属膜;对三层膜制作图案以形成一存储电容器和包括栅电极的选通导线;用栅电极作为掩模将离子注入一硅层中以形成一源极区和一漏极区;以及形成与存储电容器金属相接触的透明像素电极。

可以在存储电容器之上淀积一层间绝缘膜和一钝化膜。最好是通过把层间绝缘膜和钝化膜作为具有相同蚀刻率的材料同时去除层间绝缘膜和钝化膜的一部分,以露出存储电容器的金属膜。存储电容器的金属膜在蚀刻步骤中起阻蚀刻层的作用。

如上所述,由于存储电容器由上、下存储电容器电极和厚度较薄的绝缘膜构成,所以可以获得足够大的存储电容。由于像素中绝缘膜的厚度均匀,所以可以减小像素间的存储电容差。此外,由于无需将离子注入硅层以形成一存储电极,所以制造过程变得简单。

本发明提供一种液晶显示装置,包括:一绝缘衬底;一硅层,形成于衬底上;一栅极绝缘膜,覆盖硅层;一栅电极,形成于栅极绝缘膜上;一存储电极,形成于栅极绝缘膜上;一源电极,接至源极区;一漏电极,接至漏极区;一个层间绝缘膜,覆盖栅电极和存储电极,具有分别露出源极区和漏极区的第一接触孔和第二接触孔,其中源电极和漏电极形成于层间绝缘膜上并且分别通过第一接触孔和第二接触孔接至源极区和漏极区;以及一像素电极,它电连接到漏极区上;其中硅层包括:一掺杂的源极区;一掺杂的漏极区;未掺杂且位于源极区与漏极区之间的第一区;和未掺杂且与漏极区邻接而与第一区隔开的第二区;存储电极位于第二区的对面;其中栅极绝缘膜的厚度是500~3000。

本发明提供一种液晶显示装置的驱动方法,该液晶显示装置包括:一薄膜晶体管,具有含一掺杂的源极区、一掺杂的漏极区、位于源极区与漏极区之间的第一未掺杂区和邻接漏极区的第二未掺杂区的硅层,该薄膜晶体管还具有一栅电极和夹在硅层与栅电极之间的绝缘层;和一存储电极,它经绝缘层与第二未掺杂区相交叠,该方法包括以下步骤:把用来使薄膜晶体管导通的电压施加到栅电极上;把一显示信号电压施加到源电极上;以及施加等于或大于薄膜晶体管阈值电压和显示信号电压最大值之和的电压。

本发明提供一种液晶显示装置的制造方法,包括以下步骤:将一硅层形成于一绝缘衬底上;形成一栅极绝缘膜,它覆盖硅层;形成一栅电极和一存储电极,它们分别与栅极绝缘膜上的硅层相交叠;通过用栅电极和存储电极作为掩模掺杂硅层来形成一源极区和一漏极区;形成一个层间绝缘膜,它覆盖栅电极;形成一源电极和一漏电极,它们分别接至源极区和漏极区;形成一钝化膜,它覆盖源电极和漏电极;以及形成一像素电极,它接至漏电极,其中栅极绝缘膜的厚度是500~3000。

附图说明

图1是一传统液晶显示装置(LCD)的等效电路图;

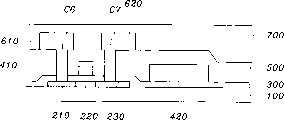

图2是根据本发明第一实施例的LCD布局图;

图3是沿图2中的线III-III′所取的断面图;

图4表示在根据第一实施例的LCD中形成一存储电容器的原理;

图5A至5J是根据第一实施例图2和3中所示LCD中间结构的断面图;

图6是根据本发明第二实施例的LCD布局图;

图7是沿图6中的线VII-VII′所取的断面图;

图8是沿图6中的线VIII-VIII′所取的断面图;

图9是根据本发明第三实施例的LCD布局图;

图10是沿图9中的线X-X′所取的断面图;

图11A到11H是根据第二实施例图6和7所示LCD的中间结构断面图;

图12是根据本发明第四到第六实施例的LCD布局图;

图13到15是沿分别根据第四到第六实施例的图12中的线XIII-XIII′所取的断面图;

图16A到16H是根据本发明第四实施例图13所示的LCD中间结构断面图;

图17A到17F是根据本发明第五实施例图14所示的LCD中间结构断面图;

图18A到18D是根据本发明第六实施例图15所示的LCD中间结构断面图;

图19是根据本发明第七实施例的LCD布局图;

图20是沿图19中的线XX-XX′所取的断面图;

图21是仅示出图19中一层硅层、一条存储线和一个栅电极的布局图;

图22是根据本发明第八实施例的LCD布局图;

图23是沿图22中的线XXII-XXII′所取的断面图;

图24是根据第八实施例的LCD断面图,其中示意性地表示出形成存储电容器的原理;

图25和26示出施加到根据第八实施例的LCD上的信号电压波形;

图27说明作为存储电压函数的存储电容的变化;

图28说明当在第八实施例中显示信号电压的最大值是10V而TFT的阈值电压是3.5V时,10V和14V存储电压下存储电容器的充电特性;

图29A到29J是根据第八实施例图22和23所示的LCD中间结构断面图;

图30是根据本发明第七和第八实施例的LCD等效电路图;

图31是一布局图,它示出根据本发明第九实施例的LCD的一层硅层、一条存储线和一个栅电极;

图32说明根据图21和31所示第七和第九实施例的像素充电特性;

图33是根据本发明第九实施例的LCD等效电路图;

图34是根据本发明第十实施例的LCD布局图;

图35是沿图34中的线XXXV-XXXV′所取的断面图;

图36是根据本发明第十一实施例的LCD布局图;

图37是沿图36中的线XXXVII-XXXVII′所取的断面图;

图38是根据本发明第十一实施例的LCD等效电路图;

图39和40是根据本发明第十二和十三实施例的LCD布局图;

图41是根据本发明第十四实施例的LCD布局图;

图42是沿图41中的线XLII-XLII′所取的断面图;

图43是根据本发明第十五实施例的LCD布局图;

图44是沿图43中的线XLIV-XLIV′所取的断面图;

图45是根据本发明第十六实施例的LCD布局图;

图46是沿图45中的线XLVI-XLVI′所取的断面图;

图47是根据本发明第十七实施例的LCD布局图;

图48是沿图47中的线XLVIII-XLVIII′所取的断面图;

图49是图48中部分P的放大图;

图50是根据本发明第十八实施例的LCD布局图;

图51是沿图50中的线LI-LI′所取的断面图;

图52A到52K是根据本发明第十七实施例图47和48所示的LCD中间结构断面图;

图53A到53C是图52G中所示结构的中间结构断面图。

具体实施方式

下文将参照附图更完整地描述本发明,附图中示出本发明的优选实施例。不过,本发明可以以不同的方式实现,而并不应把本发明视为限定于这里所述的实施例。更确切地说,提供这些实施例以便使本公开内容详尽和完整,对于本领域的那些技术人员来说,这些实施例完全地表达了本发明的范围。附图中,为清楚起见,扩大了层和区的厚度。

以下将描述根据第一实施例的液晶显示装置(LCD)的结构和驱动方法。

在第一实施例中,位于存储电极对面的硅层保持未掺杂状态,起存储电容器的一个电极的作用。

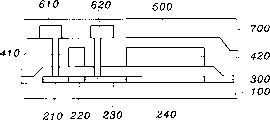

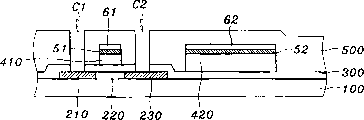

图2是根据本发明第一实施例的LCD布局图,图3是沿图2中的线III-III′所取的断面图。

如图2和3所示,在绝缘衬底100上形成多晶硅层200,在衬底100上形成SiO2或SiNx制成的栅极绝缘膜300,厚度为500~3000。

在栅极绝缘膜300上形成包括Al、Cr或MoW制成单层或双层的选通线400,它沿水平方向延伸。选通线400与硅层200相交,选通线400与硅层200相交的部分410起一栅电极的作用。由与选通线400相同的层制成的存储电极线430平行于选通线400延伸,与硅层200相交。存储电极线430与硅层200相交的部分420起一存储电极的作用。

位于栅电极410对面的硅层200的部分220未掺杂,而位于未掺杂区220外部的源极区210和漏极区230掺杂有n型掺杂物。与漏极区230邻接且位于存储电极420之下的区域240未受到掺杂,称之为“存储区”。

由SiO2或SiNx制成的层间绝缘膜500覆盖住含选通线400和存储电极线430的选通导线,其厚度为3000~10000。将接触孔C1和C2做在栅极绝缘膜300和层间绝缘膜500中,露出源极区210和漏极区230。

由Cr或Mo制成的数据线600形成于层间绝缘膜500,沿垂直方向延伸。源电极610从数据线600伸出,与硅层200的源极区210相交叠,而漏电极620形成于层间绝缘膜500上,相对于选通线400位于源电极610的对侧,并与漏极区240相交叠。源电极610和漏电极620分别通过接触孔C1和C2接至源极区210和漏极区230。

由SiO2或SiNx制成的钝化膜700覆盖住含数据线600和源电极610及漏电极620的数据导线,其厚度为3000~10000。由铟锡氧化物制成的透明像素电极800形成于其上,并位于数据线600和选通线400所包围的区域中。像素电极800通过做在钝化膜700中的通孔C3接至漏电极620,与存储电极线430相交叠。在反射型LCD的情况下,像素电极800可以不透明。

在包括存储区240、存储电极420和栅极绝缘膜300的存储电容器的结构中,由于存储区240未掺杂,所以需要一种专门的驱动方法来得到该存储电容器。

图4是一断面图,示意性示出把等于或大于TFT阈值电压Vth与显示信号电压之和的电压V加到存储电极上的情况。

若将一选通电压加到栅电极410上,则在源极区210和漏极区230之间产生传递电子的沟道,通过该沟道将一显示信号电压加到像素电极800上。将一直流或交流V加到存储电极420上。

在施加到存储电极420上的电压V等于或大于TFT阈值电压Vth与显示信号电压最大值之和的情况下,电荷累积层241形成于未掺杂的存储区240的表面附近。因此,该累积层241即使电阻很大也可导电,起存储电极的作用。

如上所述,由于未掺杂的硅区240可用作存储电容器的一个电极,所以可在LCD制造过程中减少一个掺杂步骤。

下面,将参照图2、5A到5J描述根据第一实施例的LCD制造方法。

图5A至5J是根据第一实施例的图2和3中所示LCD中间结构的断面图。

如图2和图5A所示,多晶硅层200形成于绝缘衬底100上。可对硅层200进行热处理或激光热处理以改善硅层200的结晶质量。

如图2和图5B所示,将SiO2或SiNx层淀积至500~3000厚,形成栅极绝缘膜300。

如图2和图5C所示,淀积选通导线的导电层并以其制作图案以形成选通线400、栅电极410、存储电极线430和存储电极420。如上所述,把作为选通线400一部分的栅电极410和作为存储电极线430一部分的存储电极420置于硅层200之上。

如图5D所示,借助作为注入掩模的导线400、410、420和430将离子注入硅层200,然后离子扩散,限定源极区210和漏极区230。位于栅电极410和存储电极420对面的未掺杂区分别是沟道区220和存储区240。存储区240与漏极区230邻接。

如图5E所示,形成层间绝缘膜500以使栅电极410与以后形成于其上的源电极和漏电极相绝缘。

如图5F所示,去除覆盖在硅层200的源极区210和漏极区230之上栅极绝缘膜300和层间绝缘膜500的那部分,以形成接触孔C1和C2。

如图2和图5G所示,淀积象Al、Cr、Mo或MoW这样的数据导线金属层并对其制作图案,以形成数据线600和源电极610以及漏电极620。

如图5H和5I所示,淀积和蚀刻一钝化膜,以在漏电极620之上形成通孔C3。

如图2和图5J所示,淀积诸如铟锡氧化物这样的材料制成的透明导电层并对其制作图案,以形成与存储电极420相交叠的像素电极800。像素电极800通过通孔C3接至漏电极。

如上所述,由于在存储电极420的电压受到有效控制的情况下,存储区240可用作存储电容器的一个电极,所以存储区240无需受掺杂。

下面,将描述根据本发明第二实施例的LCD。第二实施例中,不用硅层的一部分,而是将一附加金属图案用作存储电容器的一个存储电极,在最下层中形成一数据导线的金属图案和该附加金属图案。

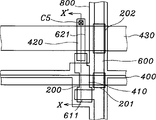

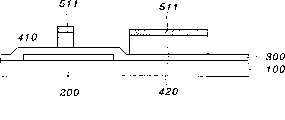

图6是根据本发明第二实施例的LCD布局图,图7是沿图6中的线VII-VII′所取的断面图,图8是沿图6中的线VIII-VIII′所取的断面图。

如图6到8所示,数据线600形成于绝缘衬底100上并沿垂直方向延伸,源电极611从数据线600伸出。由与数据线600相同的层制成的存储电极金属图案621形成于绝缘衬底100上并平行于数据线600延伸。硅层200从源电极611伸至存储电极621的金属图案上,并与源电极611和存储电极图案621接触。由SiO2或SiNx制成的栅极绝缘膜300形成于其上,厚度为500~3000。

选通线400形成于栅极绝缘膜300上并和源电极611与存储电极金属图案621之间的硅层220相交叠。选通线400的相交叠部分410起一栅电极作用。栅电极410对面硅层200的区220未掺杂,成为沟道区。硅层200的两个掺杂区210和230相对于沟道区220而相对设置。位于源电极611之上的一个区210是源极区,而位于源电极621之上的另一区230是漏极区。

由与选通线400相同层制成的存储电极线430形成于栅极绝缘膜300上并平行于选通线400延伸。存储电极420、存储电极线430的一部分与存储电极金属图案621相交叠,形成一存储电容器。

由SiO2或SiNx制成的钝化膜700形成于栅极绝缘膜300、栅电极410和存储电极金属图案420上,厚度为3000~10000。由铟锡氧化物制成的像素电极800形成于钝化膜700上,并位于选通线400和数据线600所包围的像素区内。像素电极800通过做在钝化膜700和栅极绝缘膜300内的接触孔C4与漏极区230相接触。

如上所述,由于源极区210和漏极区230分别直接与漏电极611和像素电极800相接触,所以无需附加层间绝缘膜和用来将源电极和漏电极接至源极区和漏极区的接触孔。

如图8所示,在只将栅极绝缘膜300置于数据线600和选通线400之间的情况下,可能在两线600和400之间发生短路故障。因此,可以在线600和400交会处设置硅图案201,以减少短路故障。

图9和10分别是根据本发明第三实施例的LCD布局图和断面图。根据第三实施例的LCD具有与根据第二实施例的LCD基本相同的结构,不同点在于其像素电极直接与存储电极金属图案而不是硅层相接触。

也就是说,根据第三实施例的LCD在TFT和存储电极方面具有与根据第二实施例的LCD相类似的结构。不过,像素电极800并不接触漏极区230,而是通过做在钝化膜700和栅极绝缘膜300内的接触孔C5接触存储电极金属图案621。

在第二和第三实施例中,设置了含金属图案621、栅极绝缘膜300和存储电极420的一个存储电容器,还设置了含存储电极420、钝化膜700和像素电极800的另一存储电容器。由于这些存储电容器的电介质300和700的厚度比传统结构的厚度薄,所以可以得到足够大的存储电容。

接着,以下将参照图6和图11A至11H描述根据第二和第三实施例的LCD制造方法。

图11A至11H是根据第二实施例的LCD中间结构断面图。

如图6和11A所示,将一数据导线的金属层淀积在绝缘衬底100上,并对其制作图案以形成数据线600、源电极611和存储电极金属图案621。

如图6和11B所示,将一硅层淀积于其上并对其制作图案以形成硅层200,它与源电极611、存储电极金属图案621相接触,还与源电极611和存储电极金属图案621之间衬底100的一部分相接触。可进行热处理或激光热处理以改善硅层200的结晶特性。此外,硅图案201和202可保持在导线的交会处,以防止数据线600与选通线400或存储电极线420之间发生短路故障。

如图6和11D所示,形成由SiO2或SiNx制成的栅极绝缘膜300,淀积一选通导线的金属层并对其制作图案以形成选通线400、栅电极410和存储电极。

如图11E所示,借助作为注入掩模的栅电极410将离子注入硅层200中,以形成源极区210和漏极区230。可进行热处理或激光热处理以使注入的离子扩散。

如图11F和11G所示,淀积钝化膜700,去除存储淀积金属图案621和漏极区230之上钝化膜700和栅极绝缘膜300的部分,形成接触孔C4和C5。

接着,如图6和11H所示,淀积一铟锡氧化物层并对其制作图案,以形成像素电极800。该像素电极通过接触孔C4直接接至漏极区230。

其间,像素电极800可通过接触孔C5直接接至存储电极金属图案621、

如上所述,由于硅层就形成于数据导线上,所以无需传统的用来形成接触孔的蚀刻步骤。此外,也除去了淀积一层间绝缘膜的步骤和用来形成一存储电极的掺杂步骤。

下面,将描述根据本发明第四到第六实施例的LCD。在这些实施例中,把一存储电极和一像素电极用于一存储电容器,夹在该存储电极和像素电极之间的电介质厚度较薄。

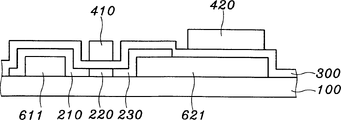

图12是一布局图,表示出根据第四到第六实施例的TFT和存储电容器,图13到15分别是根据第四到第六实施例沿图12中的线XIII-XIII′所取的断面图。

如图12和13所示,将部分掺杂的多晶硅层200形成于绝缘膜100上,而使SiO2或SiNx制成的栅极绝缘膜300形成于其上。选通线400形成于栅极绝缘膜300上并沿水平方向延伸,选通线400的一部分410起一栅电极的作用。沟道区220--硅层200位于栅电极410对面的部分未掺杂,而位于沟道区220之外的源极区210和漏极区230受到掺杂。

存储电极线430形成于栅极绝缘膜300上并平行于选通线400延伸,存储电极线430的一部分420起一存储电极的作用。

SiO2或SiNx制成的层间绝缘膜500形成于栅极绝缘膜300、栅电极410、选通线400、存储电极420和存储电极线430上,厚度为3000~10000。在栅极绝缘膜300和层间绝缘膜500内形成接触孔C6和C7,它们露出源极区210和漏极区230。数据线600和源电极610以及漏电极620形成于层间绝缘膜500上,漏电极610和漏电极620分别通过接触孔C6个C7接至源极区210和漏极区230。

钝化膜700形成于层间绝缘膜500和源电极610以及漏电极620上。在钝化膜700中形成露出漏电极620的接触孔C8,去除存储电极420之上钝化膜700的一部分和层间绝缘膜500的上部以形成孔C9。

铟锡氧化物像素电极800形成于钝化膜700上,并通过接触孔C8接至漏电极。

如上所述,存储电容器包括像素电极800、存储电极420和夹在两电极420与800之间的层间绝缘膜500。由于除了电极420和800相交叠部分之上钝化膜700的部分,并且层间绝缘膜500的厚度在该部分变得很小,所以存储电容增大。

但是,很难保持层间绝缘膜500局部去除部分的厚度均匀。

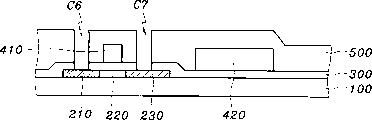

图14和15表示根据第五和第六实施例的结构,其中存储电极之上层间绝缘膜500的厚度均匀。

如图14和15所示,除层间绝缘膜是双叠层的一点不同之外,第五实施例的结构与第四实施例相同。该层间绝缘膜包括作为下层的第一膜510和作为上层的第二膜520,前者厚度为500~3000,而后者厚度为3000~10000。去除存储电极420之上第二膜520的那部分。

如图15所示,与第五实施例相同,第六实施例具有一双叠层层间绝缘膜511和520,但第一膜511仅形成于含栅电极410和存储电极420的选通导线之上。象在第五实施例中那样,去除存储电极420之上第二膜520的部分。

与第四实施例一样,在第五和第六实施例的结构中,可以通过减少存储电容器的电介质厚度来增大存储电容器。另外,可以实现电介质厚度均匀。

以下描述根据第四到第六实施例的LCD制造方法。

在这些方法中,由于未将一掺杂硅图案用作存储电容器的电极,所以省去了用来形成存储电容器的硅图案离子掺杂步骤,并且也不需要用来蚀刻层间绝缘膜的额外光刻步骤。

图16A到16H是根据第四实施例LCD的中间结构断面图。

如图12和16A所示,硅层200形成于绝缘衬底100上。象在前述实施例中那样,可以进行热处理或激光热处理以改善硅层200的结晶特性。栅极绝缘膜300形成于其上,厚度为500~3000。淀积一选通导线的金属并对其制作图案以形成选通线400、栅电极410和存储淀积420。

如图16B所示,借助作为注入掩模的栅电极410对硅层200进行离子掺杂,以形成源极区210和漏极区230。

如图16C和16D所示,淀积层间绝缘膜500,然后去除源极区210和漏极区230之上的栅极绝缘膜300和层间绝缘膜500,以形成接触孔C6和C7。

如图12和16E所示,淀积一数据导线的金属层并对其制作图案,以形成数据线600、源电极610和漏电极620。源电极610和漏电极620分别通过接触孔C6和C7接至源极区210和漏极区230。

如图16F所示,淀积一钝化膜700。钝化膜700由具有与层间绝缘膜500相同的蚀刻率的材料制成。

接着,如图16G所示,蚀刻钝化膜700以分别形成接触孔C8和C9,它们露出存储电极420之上的漏电极620和层间绝缘膜500。在该过程中,所暴露的层间绝缘膜511的厚度变小。因此,需要控制蚀刻时间以使层间绝缘膜的厚度保持在500~3000。

如图12和16H所示,淀积铟锡氧化物层并对其制作图案,以形成像素电极800。像素电极800通过接触孔C8接至漏电极620,并与存储电极420相交叠。

如上所述,在去除一漏电极620之上的钝化膜700的步骤中,通过部分去除层间绝缘膜来控制存储电极420之上的层间绝缘膜511的厚度,使其厚度较薄。但是,很难控制厚度达到均匀。

图17A到17F是根据第五实施例LCD的中间结构断面图。在第五实施例中,层间绝缘膜是双叠层,而各层的蚀刻率相互不同。

通过图16A和16B所示的同样步骤,形成源极区210和漏极区230,栅极绝缘膜300、选通线400、栅电极410和存储电极420。

然后,如图17A所示,依次淀积第一膜510和第二膜520,二者厚度分别达500~3000和3000~10000。第一膜510和第二膜520的蚀刻选择率优选足够大,第一膜510由蚀刻率比第二膜520小得多的材料制成。

如图17B所示,同时蚀刻和去除源极区210与漏极区230之上的栅极绝缘膜300、第一膜510和第二膜520的部分,以形成接触孔C6和C7。

如图12和17C所示,淀积一数据导线的金属层并对其制作图案,以形成数据线600、源电极610和漏电极620。源电极610和漏电极620分别通过接触孔C6和C7接至源极区210和漏极区230。

如图17D和17E所示,淀积蚀刻率与第二膜520相同的材料层,以形成钝化膜700,对钝化膜700制作图案以形成接触孔C8和通孔C9,接触孔C8露出漏电极620,通孔C9露出第二膜520。之后,去除第二膜520的暴露部分,以形成通孔C9。如上所述,由于第一膜510的蚀刻率比第二膜520的蚀刻率小得多,而第二膜与钝化膜700具有基本相同的蚀刻率,所以仅去除了第二膜520。

如图2和17F所示,淀积铟锡氧化物并对其制作图案,以形成像素电极800,像素电极800通过接触孔C8接至漏电极620并盖住通孔C9。

如上所述,由于层间绝缘膜含具有不同蚀刻率的双层,所以剩下的层间绝缘膜的厚度均匀。

图18A到18D是根据第六实施例LCD的中间结构断面图。在第六实施例中,双膜511和520具有与第五实施例不同的蚀刻率,但对下膜连同选通线一起制作图案。

如图12和18A所示,硅层200形成于绝缘衬底100上,而将栅极绝缘膜300淀积于其上。接着,按顺序淀积一选通导线和厚度为500~3000的第一膜511,并且同时对它们制作图案。换句话说,只剩下在含选通线400、栅电极410和存储电极420之上的第一膜511。

如图18B和18C所示,借助作为注入掩模的栅图案400、410和420将离子注入硅层200中,以形成源极区210和漏极区230,并且淀积第二膜520。第二膜520的蚀刻率大于第一膜511的蚀刻率,而与钝化膜700的蚀刻率相同。

接着,用与第五实施例相同的方法形成数据线600、源电极610和漏电极620以及钝化膜700。在蚀刻步骤中,保留具有小蚀刻率的第一膜511,而去除存储电极420之上的第二膜520和钝化膜700。

如图12和18D所示,像素电极800形成于钝化膜700和第一膜511上,一存储电容器由像素电极800、存储电极420和夹在电极800与420之间的第一层间绝缘膜511形成。

在第五和第六实施例中,将第一膜510和511用作过度蚀刻保护层。可以将第一膜510和511制成多层。

在以上实施例中,已经以具有隔离存储线的模式描述了LCD及其制造方法。这些实施例可用于其中将以前一选通线的一部分用作存储电容器一个电极的模式。此外,半导体层可以是非晶硅层。

下面,描述根据本发明第七实施例的结构。第七实施例,不需为一存储区掺杂硅层,但硅层可通过一特定的驱动方法起到存储电容器一个电极的作用。

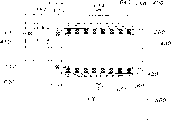

图19是根据本发明第七实施例的LCD布局图,图20是沿图19中的线XX-XX′所取的断面图,图21是仅表示出一条存储电极线、一硅层和一个栅电极的放大布局图。

如图19和20所示,多晶硅层200形成于绝缘膜100上并沿垂直方向延伸,而SiO2或SiNx制成的栅极绝缘膜300形成于衬底100和硅层200上,厚度为500~3000。

选通线400形成于栅极绝缘膜300上并沿水平方向延伸。选通线400扩展以形成栅电极410、栅电极410与硅层200的一部分220相交叠。由与选通线400相同层制成的存储电极线430形成于栅极绝缘膜300上并平行于选通线400延伸。存储电极线430与硅层200的一部分240相交叠,而存储电极线430与硅层200相交叠的部分420是一存储电极。

如图21所示,硅层200包括有一小宽度且与栅电极410相交叠的一部分,还包括位于栅电极410右侧有一大宽度且与存储电极420交叠长度为L的另一部分。存储电极420向上和向下扩展以增大总交叠面积,存储电极420的两边位于硅层200的外部。在该实施例中,存储电极420的宽度W1大于硅层200的宽度W0,而存储电极420的长度L大于宽度W1。

其间,硅层200与栅电极410和存储电极420相对的部分未掺杂,而硅层200的其余部分掺杂有n型掺杂物。相对于栅电极410和存储电极420将掺杂部分分成几个区。与栅电极相对的未掺杂部分是沟道区220,与存储电极相对的未掺杂部分是存储区240,而关于沟道区220对应于两侧的掺杂部分是源极区210和漏极区230。漏极区230邻接存储区240。此外,因硅层200和存储电极420之间在长度和宽度上的差而产生的分区250和260形成于存储电极420的外部。掺杂分区250、260,它们邻接存储区240而与漏极区230分开。

层间绝缘膜500覆盖住含选通线400、栅电极410和存储电极线430的选通导线,在栅极绝缘膜300和层间绝缘膜500内形成暴露源极区210和漏极区230的接触孔C1和C2。

数据线600形成于层间绝缘膜500上,沿垂直方向延伸,与选通线400和存储电极线430相交。数据线600通过接触孔C1接至源极区210。数据导线的金属制成的漏电极620关于数据线600形成于对面,并且通过接触孔C2接至漏极区230。

钝化膜700覆盖数据线600和层间绝缘膜500,露出漏电极620的通孔C3形成于钝化膜700内。铟锡氧化物制成的像素电极800形成于钝化膜700上,并且位于数据线600和选通线400所包围的像素区内部。像素电极800通过通孔C3接至漏电极620,与存储电极420相交叠。

其间,漏极区230可直接接至像素电极800。以下参照图22和23进行描述。

图22是根据本发明第八实施例LCD的布局图,图23是沿图22中的线XXIII-XXII′所取的断面图。在该实施例中,无需漏电极的金属图案。

如图22和23所示,除了以下一点之外,第八实施例结构与第七实施例相同,这一点是:露出漏极区230的接触孔C10形成于钝化膜700、层间绝缘膜500和栅极绝缘膜300内,像素电极800通过接触孔C10直接接至漏极区230。

如上所述,一存储电容器包括存储区240、存储电极420和夹在其间的栅极绝缘膜300。由于存储区240未掺杂,所以它不能起存储电容器一个电极的作用。因此,需要施加专门的电压。

图24是根据第八实施例的LCD断面图,它示意性地表示出当将电压施加到一存储电极上时形成存储电容器的原理。施加到存储电极上的电压V等于或大于TFT阈值电压Vth与显示信号电压之和。

若将选通电压施加到栅电极410上,则一沟道形成于位于源极区210和漏极区230之间的沟道区220内。通过该沟道把来自数据线600的显示信号电压从源极区210传输到漏极区230,并施加到像素电极800上。

若施加到存储电极420上的电压Vst等于或大于阈值电压Vth与显示信号电压Vds的最大值之和,则由于存储电极420起一场效应晶体管栅电极的作用,所以电荷累积层241产生于未掺杂存储区240的表面之下,未掺杂区240邻接漏极区230。电荷累积层241变得能导电并且起一存储电极的作用。

图25和26表示施加到LCD上的信号电压波形。将一栅极电压Vg和一显示信号电压Vds分别施加到一选通线和一数据线上,将一公共电压Vcom施加到一公共电压上,而将一存储电压Vst施加到一存储电极线和一存储电极上。

在一帧之内,把栅极电压Vg的高电平电压-选通电压按顺序施加到选通线上,将显示信号电压通过数据线施加到接至施加选通电压的选通线的像素上,对像素的液晶电容器充电。数据电压Vds相对于公共电压Vcom的极性可周期性翻转。

逐帧重复该过程。

如图25和26所示,施加到一条选通线上的栅极电压Vg具有周期性上升的脉冲,而施加到数据线上的显示信号电压Vds相对于公共电压Vcom周期性的翻转其极性。

其间,公共电压Vcom是如图25中的直流电压或是如图26中那样具有与栅极电压Vg相同翻转周期的交流电压。根据公共电压Vcom的类型,存储电压Vst的波形可改变。换句话说,若公共电压Vcom是如图5中的直流电压,则存储电压Vst是直流电压,而若公共电压是如图26中的交流电压,则存储电压Vst是交流电压。在后一情况下,最好在公共电压Vcom有低值时存储电压Vst有低值,而在公共电压Vcom有高值时存储电压Vst有高值。

在图25和26所示的两种情况下,施加到存储电极420上的存储电压Vst等于或大于阈值电压Vth和显示信号电压Vds最大值之和。

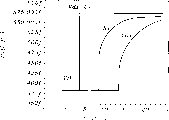

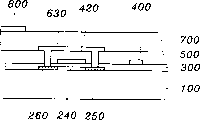

图27表示0V、5V和10V显示信号电压下电容Cst随存储电压Vst的变化情况。

在显示信号电压是0V的情况下,若存储电压Vst等于或大于TFT的阈值电压3.5V,则形成一存储电容器。该存储电容器的电容是575法拉,它几乎与用金属电极情况下的电容相同。在显示信号电压是5V和10V的情况下,当存储电压Vst分别等于或大于8.5V和13.5V时,形成存储电容Cst,8.5V和13.5V是各个显示信号电压与3.5V之和。与显示电压是0V的情况不同,存储电容Cst的值受存储电压Vst变化的影响。也就是说,当所施加的存储电压Vst具有比3.5V加上显示信号电压Vds更大的值时,存储电容Cst大大增加。随着存储电压Vst的增大,存储电容Cst的增长率降低,该存储电容接近0V显示信号电压的值。

图28表示当显示信号电压Vds是10V、TFT阈值电压是3.5V时10V和14V存储电压Vst的存储电容器充电特性。在施加选通电压的时刻T1开始对像素充电,像素电压Vpixel在很短的时间内达到最大值。像素电压Vpixel在施加截止电压的时刻T2骤然下降。压降ΔV1和ΔV2是一反冲电压。

如图28所示,若施加到存储电极420上的存储电压Vst是10V,则较之存储电压Vst是14V的情况,像素迅速充电,达到最大值。但是,10V存储电压Vst的压降ΔV1大于14V存储电压Vst的压降ΔV2。

因此,若存储电压等于或大于TFT阈值电压与显示信号电压最大值之和,则形成存储电容,从而使充电时间延迟,反冲电压减小。

如上所述,由于通过施加充分的电压而使未掺杂存储区240可用作存储电容器的一个电极,所以不需要对存储区240进行的额外掺杂步骤。

下面,将参见图19到23和图29A到29J描述根据第七和第八实施例的LCD的制造方法。

如图29A所示,多晶硅层200形成于绝缘衬底100上。然后,可执行热处理或激光热处理,以改善硅层200的结晶特性。

如图29B所示,形成SiNx或SiO2制成的栅极绝缘膜300,其厚度为500~3000。

如图19和29C所示,淀积一条导线的导电层,并对其制作图案,以形成含选通线400、栅电极410、存储电极线430和存储电极420的选通导线。如上所述,从选通线400伸出的栅电极410和从存储电极线430伸出的存储电极420位于硅层200之上。

如图21和29D所示,借助作为注入掩模的导线400、410、420和430将离子注入硅层200,使离子扩散以形成源极区210和漏极区230。在该步骤中,形成沟道区220--硅层200与栅电极410相对的部分,并形成存储区240-硅层200与存储电极相对的那部分。沟道220和存储区240未掺杂,存储区240邻接漏极区230。此外,形成邻接存储区240而与漏极区230隔开的分区250和260。

如图19和29E所示,形成将要使选通线400、栅电极410、存储电极420和存储电极线430与数据线和极相绝缘的层间绝缘膜500。

接着,如图29F所示,去除源极区210和漏极区230之上的栅极绝缘膜300和层间绝缘膜500,以形成接触孔C2。在第八实施例的情况下,无需接触孔C2。

如图19和29G所示,淀积象Cr和Mo这样的数据线金属层,并对其制作图案以形成数据线和漏电极620。数据线600和漏电极620分别通过接触孔C1和C2接至源极区210和漏极区230。在第八实施例的情况下,无需漏电极。

如图29H和29I所示,淀积钝化膜700,然后蚀刻钝化膜700以形成露出漏电极620的通孔C3。在第八实施例的情况下,去除栅极绝缘膜300、层间绝缘膜500和钝化膜700,以形成露出漏极区230的接触孔C4。

如图19和29J所示,淀积由象铟锡氧化物这样的材料制成的透明导电层,并对其制作图案以形成像素电极800。像素电极800与存储电极420相交叠并且通过通孔C3接至漏电极620。在第八实施例的情况下,像素电极800通过接触孔C4直接接至漏极区230。

如上所述,由于通过控制施加到存储电极420上的电压可将存储区240用作存储电容器的一个电极,所以存储区240无需掺杂。因此掩模数目减少。

参照图28再次论及充电过程,要花费一定时间对像素充电以使其具有最大电压。这可能是由导线和存储电容器的电阻以及存储电容引起的。

图30是根据上述第七和第八实施例的等效电路图。只考虑存储区240的电阻。

如图21和30所示,选通线G与数据线D相交并与它相绝缘。TFT的栅极端和源极端(g和s)分别接至选通线G和数据线D。液晶电容器LC和存储电容器STG并联接至TFT的漏极端(d),电阻Rst1接在漏电极(d)和存储电容器STG之间。

电阻Rst1取决于电荷运动路径的长度。

若将任意电压施加到漏极区230和存储电极420上,则电荷移动到并累积到存储区240。电荷从漏极区230移动到存储区240的距离是存储电极的长度L由于电阻Rst1正比于该距离而存储电容器的充电时间正比于电阻Rst1,所以需要减少电荷移动距离。

下面,将参照图31描述用来减小该长度的实施例。

图31是根据本发明第九实施例的LCD布局图,其中仅示出一硅层、一存储电极线、一存储电极和一栅电极。

如图31所示,存储电极420的宽度W3小于硅层200的宽度W2,存储电极420的边缘位于硅层200内部。为获得与图21中所示第七实施例结构中相同的存储电容,存储电极420的长度L保持与第七实施例相同,而存储电极420的宽度W3等于图21中硅层200的宽度W0。

在该结构中,掺杂后的分区250和260形成于硅层200内而其上、下边位于存储区240的外部。一个分区250接至漏极区230,而另一个分区260与漏极区230隔开。

若将存储电压Vst施加到存储电极420上,则电荷累积层240形成于存储区240的表面之下。由于掺杂后的分区250具有比电荷累积层241更小的电阻,所以漏极区230的电荷首先移入分区250,然后沿垂直方向移过累积层241。假定移动距离是存储电极420的宽度W3,由于宽度W3比长度L小,所以电荷移动距离更短,存储区240中的电阻比图21所示第七实施例中的电阻更小。

图32表示根据图21中第七实施例和图31中第九实施例的像素充电特性。虚线(a)代表第七实施例中的充电特性,实线(b)代表第九实施例中的充电特性。在存储电容和反冲电压方面两实施例之间无差别,但(b)的充电时间比(a)的充电时间短。

图33是第九实施例的等效电路图。

如图33所示,分区240的电阻R1接在存储区240的电阻Rst2和TFT的漏电极(d)之间。在该实施例中,存储区240的电阻Rst2因上述原因而减小,而分区240的电阻R1加到电阻Rst2上。

即使比存储区240电阻的减少量小,也需减小分区250的电阻R1以缩短充电时间。

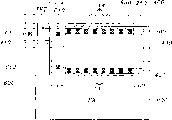

下面,将参照图34到38描述用来减小分区电阻的实施例。

图34是根据本发明第十实施例LCD的布局图,图35是沿图34中的线XXXV-XXXV′所取的断面图。除以下各点不同以外,第十实施例的结构与第九实施例基本相同,这些不同点即为:露出分区250的多个接触孔C11形成于栅极绝缘膜300、层间绝缘膜500和钝化膜700之中并沿水平方向设置,而分区250通过接触孔C11接至ITO像素电极800。

在该结构中,由于像素电极800的电阻比掺杂后的分区250小,电荷通过像素电极800在短时间内移至整个分区250,然后移入存储区240。因此,使分区250的电阻较小并且充电时间缩短。

图36是根据本发明第十一实施例的LCD布局图,图37是沿图36中的线XXXVII-XXXVII′所取的断面图。除以下各点不同以外,第十一实施例的结构与第九实施例基本相同,这些不同点是:接触孔C12形成于栅极绝缘膜300、层间绝缘膜500和钝化膜700之中,而下侧位于存储区240外部的掺杂后的分区260通过接触孔C12接至像素电极800。

在该结构中,电荷通过低电阻像素电极800移向分区250和260。然后,电荷在几乎相同的时间从上分区250和下分区260移至存储区240。因此,电荷移动距离变成存储区240宽度的一半,电阻减小,充电时间缩短。

图38是根据第十一实施例的等效电路图,表示出一存储电容器STG和电阻元件。

在图38中,R2和R3是上分区的电阻和下分区的电阻,Rst3和Rst4是存储区240上半区的电阻和存储区240下半区的电阻。假定图36中的结构与图31中的结构相同,则Rst3=Rst4=1/2Rst2,而R2=R1。假定下分区260的电阻类似上分区250的电阻,则R3=R2=R1,总电阻变成1/2R1+1/4rST2。因此,第十一实施例中的总电阻相对于第九实施例中的电阻充分减小。

下面,将参照图39和40描述根据第十二和第十三实施例的结构。在这些结构中,分区250和260的电阻变得低于以上实施例的电阻。

图39和40是根据本发明第十二和第十三实施例的LCD布局图。

如图39所示,露出掺杂后下分区260的多个接触孔C13形成于栅极绝缘膜300、层间绝缘膜500和钝化膜700之中,并且沿水平方向设置,分区260通过接触孔C13接至ITO像素电极800。

其间,在图40中,露出上分区250的多个接触孔C11和露出下分区260的多个接触孔C13形成于栅极绝缘膜300、层间绝缘膜500和钝化膜700之中。掺杂后的上分区250和下分区260通过接触孔C11和C13接至ITO像素电极800。

如上所述,由于其电阻低于分区250和260电阻的像素电极800变成电荷移动路径,所以可以减小电阻。

如41和46表示具有将分区接至像素电极的金属图案的结构。在这些结构中,将电荷引至电阻比分区低的金属图案上。

图41是根据本发明第十四实施例LCD的布局图,图42是沿图41中的线XLIII-XLII′所取的断面图。第十四实施例的结构类似于第十三实施例的结构。

如图41所示,金属图案630形成于层间绝缘膜500上,并与掺杂后分区250和260以及存储电极420相交叠。金属图案630通过多个接触孔C14和C15接至上分区250和下分区260,多个接触孔C14和C15做在栅极绝缘膜300和层间绝缘膜500之中。在该实施例中,像素电极并不与存储电极420和金属图案630相交叠。

由于金属图案630的电阻比像素电极800的小,所以该实施例的总电阻小于第十三实施例的总电阻。此外,由于存储电极420、层间绝缘膜500和金属图案630形成又一存储电容器,所以总存储电容增大。

图43和44是根据本发明第十五实施例的LCD布局图和断面图。

如图43和44所示,金属图案640和650形成于掺杂后的分区250和260之后,并且分别通过多个接触孔C14和C15接至上分区250和下分区260,多个接触孔C14和C15制作于栅极绝缘膜300和层间绝缘膜500之中。

在该实施例中,分区250和260的电阻可象第十四实施例那样减小。但是,由于金属图案640和650并未与存储电极420相交叠,所以无法由存储电极420与金属图案640和650形成额外的存储电极。

图45是根据本发明第十六实施例的LCD布局图,图46是沿图45中的线XLVI-XLVI′所取的断面图。

若ITO像素电极800与存储电极240相交叠,则第十六实施例中的结构和作用与第十四实施例基本相同。

除以下不同点之外,根据第九到第十六实施例的LCD制造方法与根据第一到第八实施例的方法相同,不同点在于:存储电极420形成于硅层200边缘的内部,而在形成数据线600的步骤中形成金属图案630、640和650。

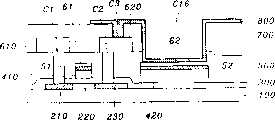

图47是根据本发明第十七实施例的LCD布局图,图48是沿图47中的线XLVIII-XLVIII′所取的断面图。

如图47和48所示,多晶硅层200形成于绝缘衬底100上,SiO2或SiNx制成的栅极绝缘膜300形成于硅层200和衬底100上,厚度为500~3000。

与硅层200相交的选通线400形成于栅极绝缘膜300上并且沿水平方向延伸。与硅层200相交的选通线400的一部分410是一栅电极。由与选通线400相同的层制成的存储电极线430形成于栅极绝缘膜300上并且平行于选通线400设置。存储电极线430的一部分变成存储电极420。

可将选通线400、栅电极410、存储电极420和存储电极线430制成双叠层膜或多叠层膜。

将硅层200分为几个区。硅层200位于栅电极410对面的未掺杂部分是沟道区220,硅层200位于沟道区220两侧的掺杂部分是源极区210和漏极区230。

厚度为500~2500的第一绝缘膜51和52形成于含选通线400、栅电极410、存储电极420和存储电极线430的导线上。第一绝缘膜51和52可以是多叠层膜。

金属图案61和62形成于绝缘膜51和52上。形成于与存储电极420相对的第一绝缘膜52上的金属图案62起存储电容器另一电极的作用。对第一绝缘膜51和52以及金属图案61和62制作图案,形状与导线400、410、420和430的相同。

第二绝缘膜,即层间绝缘膜500形成于第一绝缘膜51和52以及栅极绝缘膜300上,而露出源极区210和漏极区230的接触孔C1和C2形成于层间绝缘膜500和栅极绝缘膜500之内。

Ti或TiN制成的数据线600形成于层间绝缘膜500上并沿垂直方向设置。源电极610从数据线600伸出,并且通过接触孔C1接至源极区210。漏电极620形成于源电极610对面,并且通过接触孔C2接至漏极区230。

钝化膜700覆盖数据线600、源电极610和漏电极620,并且有一露出漏电极620的接触孔C3。露出存储电容器金属图案62的通孔C16形成于钝化膜700和层间绝缘膜500之中。

透明像素电极800形成于钝化膜700并且位于数据线600和选通线400所包围的一个像素内部。像素电极800通过接触孔C3接至漏电极620,而通过通孔C16接至一存储电容器的金属图案62。

可以把存储电极420、第一绝缘膜52和金属图案62制成一多叠层膜。以下将参照图49来描述它。

图49是图48中部分P的放大断面图,表示该多叠层结构。

如图49所示,由一选通导线的金属制成并且形成于栅极绝缘膜300上的存储电极420是一个双叠层膜,它包括铝膜421和钛膜422。

形成于存储电极420上的第一绝缘膜52具有包括SiO2膜152和SiNx膜252多叠层结构,或具有包括SiO2膜152、SiNx膜252和SiO2膜352的三叠层结构。

此外,形成于第一绝缘膜52上的金属图案62具有含一下膜162和一上膜262的双叠层结构,或具有多叠层结构。双叠层结构的上膜262或多叠层结构的最上层膜由蚀刻率比第一绝缘膜500和象Cr、Mo或Nd这样钝化膜700小的材料制成。

金属图案62接触像素电极800。

上述结构可用于这样一种模式,其中前一像素的选通线与一像素电极相交叠,并且起一存储电容器一个电极的作用。以下将参照图50和51描述它。

图50是根据本发明第十八实施例的LCD布局图,图51是沿图50中的线LI-LI′所取的断面图。

在该实施例中,前一选通线的一部分起一存储电极的作用。

如图50和51所示,一存储电容器包括第一存储电极440、存储电容器的绝缘膜54和第二存储电极64,第一存储电极440是前一选通线401的一部分,绝缘膜54形成于第一存储电极440上。像素电极800通过通孔C16接至第二像素电极64,通孔C16形成于钝化膜700和绝缘膜500之中。

除了以下不同点之外,本实施例的结构与第十七实施例的结构相同,不同点在于:前一选通线401和像素电极800相互交叠,形成一存储电容器。

由于一存储电容器的绝缘膜54厚度为500,所以存储电容器可增大。

下面,将参照图47、52A到52K描述根据本发明第十七实施例的LCD制造方法。

如图52A所示,多晶硅层200形成于绝缘衬底100上。可进行热处理或激光热处理以改善硅层200的结晶特性。

如图52B所示,SiO2或SiOx制成的栅极绝缘膜300形成于硅层200和衬底100上,厚度为500~3000。

如图47和52C所示,淀积Al制成的选通导线的导电膜402。按顺序在其上淀积厚度为500~3000的第一绝缘膜50和存储电容器金属膜60。通过按顺序淀积Al膜和Ti膜,可以将导电膜402制成双叠层结构,而可以将第一绝缘膜50制成含SiO2膜或SiOx膜的双叠层结构,或制成含SiO2、SiOx和SiO2的多叠层结构。此外,可将金属模60制成多叠层结构,而金属膜60的最上层可以由Mo、Nd或Cr制成,这些材料的蚀刻率相对于ITO的蚀刻剂来说较小。

如图47和52D所示,同时对导电膜402、第一绝缘膜50和金属膜60制作图案,以形成包括选通线400、栅电极410、存储电极420和存储电极线430的导线。因此,绝缘膜图案和金属膜图案与该导线的图案相同。在该步骤中,存储电容器由存储电极420、第一绝缘膜图案52和存储电容器的金属图案62制成。

如图52E所示,借助作为注入掩模的导线将离子注入硅层200中,形成源极区210和漏极区230。

如图52F和52G所示,淀积第二绝缘膜500。在栅极绝缘膜300和第二绝缘膜500中形成接触孔C1和C2,接触孔C1和C2露出源极区210和漏极区230。若需要露出栅电极410的任意接触孔,则通过三步形成露出源极区210和漏极区230的接触孔C1和C2。以后将参照图53A到53C详细描述它。

如图47和52H所示,淀积诸如Ti或TiN之类数据导线的金属层,并对其制作图案以形成数据线600、源电极610和漏电极620。源电极610和漏电极620分别接至源极区210和漏极区230。

如图52I所示,淀积钝化膜700。钝化膜700由蚀刻率与第二绝缘膜500相同的材料制成。

接着,如图52J所示,蚀刻钝化膜700和第二绝缘膜500,形成接触孔C3和通孔C16,接触孔C3露出漏电极620,通孔C16露出一存储电容器的金属图案62。在该步骤中,由于形成于金属图案62之上的绝缘层500和700比形成于漏电极620之上的绝缘层700厚,可以对漏电极620之上的绝缘层700进行过度蚀刻。

如图47和52K所示,淀积一铟锡氧化物层,并且对其制作图案以形成像素电极800。像素电极800通过接触孔C3接至漏电极620,而通过通孔C16接至金属图案62。如上所述,由于金属图案62的最上层由相对于ITO蚀刻剂来说具有低蚀刻率的材料制成,所以该层可以是阻蚀刻层。因此,可以在存储电极420之上形成均匀厚度的第一绝缘膜52。此外,由于漏电极620由Ti或TiN制成,所以甚至在ITO蚀刻剂通过过度蚀刻的接触孔C3渗到漏电极620中时,也不易发生漏电极腐蚀的现象。

以下将参照图53A到53C详细描述根据图52G形成露出一源极区和一漏极区的接触孔的步骤。

如图53A到53C所示,蚀刻源极区210、漏极区230和金属图案61之上的第二绝缘膜500,露出位于栅电极410之上的金属图案61,蚀刻所露出的金属图案61,露出第一绝缘膜51。蚀刻露出的第一绝缘膜51和栅极绝缘膜300,露出栅电极410、源极区210和漏极区230。

若需要将数据导线接至选通导线,则形成栅电极之上的接触孔C5。

在该实施例中,由于存储电容器的一个电极由选通导线的金属图案制成,所以无需离子掺杂步骤。此外,由于在形成选通导线的同时形成存储电容器,所以无需任何额外的步骤。

如本发明各实施例中所述,可以形成存储电容器而无需额外步骤。可以获得足够的存储电容,减小像素的电容偏差,原因在于可将存储电容器的电介质层厚度制作得很薄。此外,缩短了将显示信号电压充入像素的充电时间。

附图和说明书中,已经公开了本发明的典型优选实施例,尽管使用了特殊的术语,不过只是在一般和说明的意义上使用它们,而并不为了限制,以下的权利要求书中表示出本发明的范围。

Claims (8)

1.一种液晶显示装置,包括:

一绝缘衬底;

一硅层,形成于衬底上;

一栅极绝缘膜,覆盖硅层;

一栅电极,形成于栅极绝缘膜上;

一存储电极,形成于栅极绝缘膜上;

一源电极,接至源极区;

一漏电极,接至漏极区;

一个层间绝缘膜,覆盖栅电极和存储电极,具有分别露出源极区和漏极区的第一接触孔和第二接触孔,其中源电极和漏电极形成于层间绝缘膜上并且分别通过第一接触孔和第二接触孔接至源极区和漏极区;以及

一像素电极,它电连接到漏极区上;

其中硅层包括:一掺杂的源极区;一掺杂的漏极区;未掺杂且位于源极区与漏极区之间的第一区;和未掺杂且与漏极区邻接而与第一区隔开的第二区;存储电极位于第二区的对面;

其中栅极绝缘膜的厚度是500~3000。

2.根据权利要求1的液晶显示装置,其中硅层由多晶硅制成。

3.根据权利要求1的液晶显示装置,其中栅极绝缘膜由SiO2或SiNx制成。

4.一种液晶显示装置的驱动方法,该液晶显示装置包括:一薄膜晶体管,具有含一掺杂的源极区、一掺杂的漏极区、位于源极区与漏极区之间的第一未掺杂区和邻接漏极区的第二未掺杂区的硅层,该薄膜晶体管还具有一栅电极和夹在硅层与栅电极之间的绝缘层;和一存储电极,它经绝缘层与第二未掺杂区相交叠,该方法包括以下步骤:

把用来使薄膜晶体管导通的电压施加到栅电极上;

把一显示信号电压施加到源电极上;以及

施加等于或大于薄膜晶体管阈值电压和显示信号电压最大值之和的电压。

5.一种液晶显示装置的制造方法,包括以下步骤:

将一硅层形成于一绝缘衬底上;

形成一栅极绝缘膜,它覆盖硅层;

形成一栅电极和一存储电极,它们分别与栅极绝缘膜上的硅层相交叠;

通过用栅电极和存储电极作为掩模掺杂硅层来形成一源极区和一漏极区;

形成一个层间绝缘膜,它覆盖栅电极;

形成一源电极和一漏电极,它们分别接至源极区和漏极区;

形成一钝化膜,它覆盖源电极和漏电极;以及

形成一像素电极,它接至漏电极,

其中栅极绝缘膜的厚度是500~3000。

6.根据权利要求5的液晶显示装置的制造方法,还包括以下步骤:对硅层进行热处理或激光热处理。

7.根据权利要求5的液晶显示装置的制造方法,其中硅层由多晶硅制成。

8.根据权利要求7的液晶显示装置的制造方法,其中栅极绝缘膜的厚度是500~3000。

Applications Claiming Priority (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970079791A KR100552280B1 (ko) | 1997-12-31 | 1997-12-31 | 유지 축전기를 가지는 액정 표시 장치 및 그 제조 방법 |

| KR79791/1997 | 1997-12-31 | ||

| KR79791/97 | 1997-12-31 | ||

| KR1019980002311A KR100247270B1 (ko) | 1998-01-26 | 1998-01-26 | 유지 축전기를 가지는 액정 표시 장치 및 그 제조 방법 |

| KR2311/98 | 1998-01-26 | ||

| KR2311/1998 | 1998-01-26 | ||

| KR2312/98 | 1998-01-26 | ||

| KR1019980002312A KR100247271B1 (ko) | 1998-01-26 | 1998-01-26 | 유지 축전기를 가지는 액정 표시 장치 및 그 제조 방법 |

| KR2312/1998 | 1998-01-26 |

Related Child Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200410062130.4A Division CN100595657C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062132.3A Division CN1550838B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062131.9A Division CN100595658C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200810166498.3A Division CN101387802B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1224887A CN1224887A (zh) | 1999-08-04 |

| CN1173218C true CN1173218C (zh) | 2004-10-27 |

Family

ID=27349662

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200810166498.3A Expired - Lifetime CN101387802B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062132.3A Expired - Lifetime CN1550838B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062131.9A Expired - Lifetime CN100595658C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062130.4A Expired - Lifetime CN100595657C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CNB981271723A Expired - Lifetime CN1173218C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

Family Applications Before (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200810166498.3A Expired - Lifetime CN101387802B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062132.3A Expired - Lifetime CN1550838B (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062131.9A Expired - Lifetime CN100595658C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

| CN200410062130.4A Expired - Lifetime CN100595657C (zh) | 1997-12-31 | 1998-12-30 | 液晶显示装置及其制造方法和驱动方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (5) | US6317173B1 (zh) |

| JP (2) | JP3973787B2 (zh) |

| CN (5) | CN101387802B (zh) |

Families Citing this family (56)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6777716B1 (en) | 1999-02-12 | 2004-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor display device and method of manufacturing therefor |

| JP4402197B2 (ja) * | 1999-05-24 | 2010-01-20 | シャープ株式会社 | アクティブマトリクス型表示装置 |

| JP2001013523A (ja) * | 1999-06-30 | 2001-01-19 | Nec Corp | 液晶表示装置及びその製造方法 |

| JP4468529B2 (ja) | 1999-07-09 | 2010-05-26 | シャープ株式会社 | 液晶表示装置 |

| KR100342860B1 (ko) * | 1999-09-08 | 2002-07-02 | 구본준, 론 위라하디락사 | 액정 표시장치 제조방법 및 그 제조방법에 따른 액정표시장치 |

| JP4755748B2 (ja) * | 1999-09-24 | 2011-08-24 | 東芝モバイルディスプレイ株式会社 | 平面表示装置 |

| KR100660813B1 (ko) * | 1999-12-31 | 2006-12-26 | 엘지.필립스 엘시디 주식회사 | 엑스레이 디텍터용 어레이기판 제조방법 |

| KR100380141B1 (ko) * | 2000-09-25 | 2003-04-11 | 엘지.필립스 엘시디 주식회사 | 액정 표시 장치용 어레이 기판 및 그의 제조 방법 |

| JP4632522B2 (ja) * | 2000-11-30 | 2011-02-16 | Nec液晶テクノロジー株式会社 | 反射型液晶表示装置の製造方法 |

| KR100392850B1 (ko) * | 2000-12-29 | 2003-07-28 | 엘지.필립스 엘시디 주식회사 | 액정표시소자 및 그 제조방법 |

| TW490857B (en) * | 2001-02-05 | 2002-06-11 | Samsung Electronics Co Ltd | Thin film transistor array substrate for liquid crystal display and method of fabricating same |

| JP4662647B2 (ja) * | 2001-03-30 | 2011-03-30 | シャープ株式会社 | 表示装置及びその製造方法 |

| JP4306142B2 (ja) | 2001-04-24 | 2009-07-29 | 株式会社日立製作所 | 画像表示装置及びその製造方法 |

| GB0112561D0 (en) * | 2001-05-23 | 2001-07-18 | Koninl Philips Electronics Nv | Active plate |

| KR100797374B1 (ko) * | 2001-06-05 | 2008-01-22 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그의 제조방법 |

| US7285459B2 (en) | 2001-08-06 | 2007-10-23 | Samsung Sdi Co., Ltd. | Flat panel display with high capacitance and method of manufacturing the same |

| KR100699987B1 (ko) * | 2001-08-06 | 2007-03-26 | 삼성에스디아이 주식회사 | 높은 캐패시턴스를 갖는 평판표시소자 및 그의 제조방법 |

| KR100838185B1 (ko) * | 2001-09-24 | 2008-06-13 | 엘지디스플레이 주식회사 | 어레이 기판 및 이를 이용한 액정 표시 장치와, 이의 제조방법 |

| KR100557499B1 (ko) | 2002-12-31 | 2006-03-07 | 엘지.필립스 엘시디 주식회사 | 패턴형성방법 및 이를 이용한 액정표시소자와 그 제조방법 |

| GB0302485D0 (en) * | 2003-02-04 | 2003-03-05 | Plastic Logic Ltd | Pixel capacitors |

| KR100980010B1 (ko) | 2003-07-14 | 2010-09-03 | 삼성전자주식회사 | 박막 트랜지스터 표시판 |

| KR100659532B1 (ko) * | 2003-11-28 | 2006-12-19 | 삼성에스디아이 주식회사 | 평판표시장치 및 그의 제조방법 |

| US7379136B2 (en) * | 2003-12-29 | 2008-05-27 | Lg.Philips Lcd Co., Ltd. | Transflective type liquid crystal display device and method for fabricating the same |

| US7098091B2 (en) * | 2004-02-20 | 2006-08-29 | Au Optronics Corporation | Method for fabricating thin film transistors |

| TWI382452B (zh) * | 2004-03-19 | 2013-01-11 | Samsung Display Co Ltd | 薄膜電晶體陣列面板及其製造方法 |

| KR101043991B1 (ko) * | 2004-07-28 | 2011-06-24 | 엘지디스플레이 주식회사 | 액정표시소자 및 그 제조방법 |

| KR101050899B1 (ko) * | 2004-09-09 | 2011-07-20 | 엘지디스플레이 주식회사 | 액정표시소자 및 그 제조방법 |

| KR101073403B1 (ko) * | 2004-09-09 | 2011-10-17 | 엘지디스플레이 주식회사 | 액정표시소자 및 그 제조방법 |

| KR100647774B1 (ko) * | 2004-11-04 | 2006-11-23 | 엘지.필립스 엘시디 주식회사 | 폴리 실리콘형 박막 트랜지스터 기판 및 제조 방법 |

| KR101230299B1 (ko) * | 2005-01-07 | 2013-02-07 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 |

| JP4748441B2 (ja) * | 2005-03-08 | 2011-08-17 | セイコーエプソン株式会社 | 電気泳動表示装置、その製造方法及び電子機器 |

| KR101119186B1 (ko) * | 2005-04-06 | 2012-03-20 | 삼성전자주식회사 | 표시패널, 이를 갖는 표시장치 및 이의 제조 방법 |

| KR101217157B1 (ko) * | 2005-10-20 | 2012-12-31 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 그 제조 방법 |

| KR20070049742A (ko) * | 2005-11-09 | 2007-05-14 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판과 그 제조방법 |

| JP2007139948A (ja) * | 2005-11-16 | 2007-06-07 | Epson Imaging Devices Corp | 電気光学装置及び電子機器 |

| US8212953B2 (en) * | 2005-12-26 | 2012-07-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101230307B1 (ko) * | 2006-02-17 | 2013-02-06 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR20080001941A (ko) * | 2006-06-30 | 2008-01-04 | 삼성전자주식회사 | 표시패널 |

| DE102006060734B4 (de) * | 2006-06-30 | 2014-03-06 | Lg Display Co., Ltd. | Flüssigkristalldisplay und Verfahren zu dessen Herstellung |

| KR101250790B1 (ko) * | 2006-06-30 | 2013-04-04 | 엘지디스플레이 주식회사 | 액정표시장치의 제조방법 |

| JP5090693B2 (ja) * | 2006-09-04 | 2012-12-05 | 三菱電機株式会社 | 表示装置とその製造方法 |

| KR101335276B1 (ko) * | 2006-09-20 | 2013-11-29 | 삼성디스플레이 주식회사 | 어레이 기판, 이를 갖는 표시패널 및 그 제조 방법 |

| KR100978266B1 (ko) * | 2006-12-29 | 2010-08-26 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| TWI339443B (en) | 2007-04-13 | 2011-03-21 | Au Optronics Corp | A pixel and a storage capacitor of the pixel and a method of forming thereof |

| TWI376556B (en) * | 2007-05-30 | 2012-11-11 | Au Optronics Corp | Pixel structure and method for forming thereof |

| CN100464241C (zh) * | 2007-07-03 | 2009-02-25 | 友达光电股份有限公司 | 液晶显示器的像素结构及其制造方法 |

| TWI336806B (en) | 2007-11-02 | 2011-02-01 | Au Optronics Corp | Pixel of transflective liquid crystal display array substrate and method of fabricating the same |

| TWI413840B (zh) * | 2007-11-02 | 2013-11-01 | Au Optronics Corp | 半穿透反射式液晶顯示陣列基板之畫素結構及製造方法 |

| KR101710179B1 (ko) * | 2010-06-03 | 2017-02-27 | 삼성디스플레이 주식회사 | 평판 표시 장치 및 그 제조 방법 |

| KR20120129593A (ko) * | 2011-05-20 | 2012-11-28 | 삼성디스플레이 주식회사 | 유기발광표시장치 및 그 제조방법 |

| KR101818647B1 (ko) * | 2011-06-14 | 2018-01-16 | 삼성디스플레이 주식회사 | 유기 발광 표시장치의 제조방법 |

| KR101833235B1 (ko) * | 2011-07-14 | 2018-04-16 | 삼성디스플레이 주식회사 | 박막 트랜지스터 어레이 기판, 이를 포함하는 유기 발광 표시 장치 및 그 제조 방법 |

| US9012993B2 (en) * | 2011-07-22 | 2015-04-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR101942980B1 (ko) * | 2012-01-17 | 2019-01-29 | 삼성디스플레이 주식회사 | 반도체 디바이스 및 그 형성 방법 |

| KR101987384B1 (ko) * | 2012-11-23 | 2019-06-11 | 엘지디스플레이 주식회사 | 표시장치 |

| JP7139636B2 (ja) * | 2018-03-19 | 2022-09-21 | 株式会社リコー | 表示素子及びその製造方法、表示装置、システム |

Family Cites Families (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5910988A (ja) * | 1982-07-12 | 1984-01-20 | ホシデン株式会社 | カラ−液晶表示器 |

| JPH0622245B2 (ja) * | 1986-05-02 | 1994-03-23 | 富士ゼロックス株式会社 | 薄膜トランジスタの製造方法 |

| US5051570A (en) * | 1989-01-20 | 1991-09-24 | Nec Corporation | Liquid crystal light valve showing an improved display contrast |

| US5305128A (en) * | 1989-12-22 | 1994-04-19 | North American Philips Corporation | Active matrix electro-optic display device with storage capacitors and projection color apparatus employing same |

| JP2622183B2 (ja) * | 1990-04-05 | 1997-06-18 | シャープ株式会社 | アクティブマトリクス表示装置 |

| JP3092570B2 (ja) | 1990-04-11 | 2000-09-25 | セイコーエプソン株式会社 | 液晶表示パネルの製造方法 |

| US5402254B1 (en) * | 1990-10-17 | 1998-09-22 | Hitachi Ltd | Liquid crystal display device with tfts in which pixel electrodes are formed in the same plane as the gate electrodes with anodized oxide films before the deposition of silicon |

| KR930012126B1 (ko) | 1990-12-18 | 1993-12-24 | 삼성전자 주식회사 | Ccd형 이미지 센서의 제조방법 및 그 구조 |

| JP3106566B2 (ja) | 1991-07-26 | 2000-11-06 | ソニー株式会社 | 液晶表示装置および製造方法 |

| JPH0635004A (ja) | 1992-07-21 | 1994-02-10 | Sony Corp | 液晶表示装置 |

| JP2859784B2 (ja) | 1992-09-03 | 1999-02-24 | シャープ株式会社 | アクティブマトリクス基板 |

| CN1033252C (zh) * | 1992-12-29 | 1996-11-06 | 株式会社金星社 | 制造薄膜晶体管的方法 |

| JPH0728090A (ja) | 1993-07-14 | 1995-01-31 | Toshiba Corp | 液晶表示装置及びその製造方法 |

| JPH0764051A (ja) * | 1993-08-27 | 1995-03-10 | Sharp Corp | 液晶表示装置およびその駆動方法 |

| JP2875733B2 (ja) * | 1994-02-15 | 1999-03-31 | 松下電子工業株式会社 | 半導体装置の製造方法 |

| JPH07302912A (ja) * | 1994-04-29 | 1995-11-14 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP3105408B2 (ja) * | 1994-10-19 | 2000-10-30 | シャープ株式会社 | 液晶表示素子 |

| US5814529A (en) * | 1995-01-17 | 1998-09-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for producing a semiconductor integrated circuit including a thin film transistor and a capacitor |

| JP3375814B2 (ja) | 1995-02-15 | 2003-02-10 | 株式会社半導体エネルギー研究所 | アクティブマトリクス表示装置 |

| JP3792749B2 (ja) * | 1995-06-02 | 2006-07-05 | 株式会社東芝 | 液晶表示装置 |

| US5641974A (en) * | 1995-06-06 | 1997-06-24 | Ois Optical Imaging Systems, Inc. | LCD with bus lines overlapped by pixel electrodes and photo-imageable insulating layer therebetween |

| US5917563A (en) * | 1995-10-16 | 1999-06-29 | Sharp Kabushiki Kaisha | Liquid crystal display device having an insulation film made of organic material between an additional capacity and a bus line |

| JP3245527B2 (ja) | 1995-12-13 | 2002-01-15 | シャープ株式会社 | 液晶表示装置 |

| JP3212252B2 (ja) | 1996-06-13 | 2001-09-25 | シャープ株式会社 | 液晶表示装置 |

| JP3490216B2 (ja) | 1996-04-24 | 2004-01-26 | シャープ株式会社 | スイッチング素子基板の製造方法 |

| JPH09171196A (ja) | 1995-10-16 | 1997-06-30 | Sharp Corp | 液晶表示装置 |

| KR100364771B1 (ko) * | 1995-10-20 | 2003-04-07 | 엘지전자 주식회사 | 액정표시장치의구조및제조방법 |

| JPH09127556A (ja) * | 1995-10-31 | 1997-05-16 | Sony Corp | 表示装置及びその駆動方法 |

| KR100193653B1 (ko) * | 1995-11-20 | 1999-06-15 | 김영환 | 축적 캐패시터를 구비한 스태거 tft-lcd 및 그의 제조방법 |

| KR100192507B1 (ko) | 1996-01-18 | 1999-06-15 | 구자홍 | 티에프티-엘씨디의 구조 및 제조방법 |

| JP3413000B2 (ja) * | 1996-01-25 | 2003-06-03 | 株式会社東芝 | アクティブマトリックス液晶パネル |

| US6208400B1 (en) * | 1996-03-15 | 2001-03-27 | Canon Kabushiki Kaisha | Electrode plate having metal electrodes of aluminum or nickel and copper or silver disposed thereon |

| KR100198539B1 (ko) | 1996-05-02 | 1999-06-15 | 구자홍 | 액정표시장치용 박막트랜지스터 제조방법 |

| JP3126661B2 (ja) * | 1996-06-25 | 2001-01-22 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP3708637B2 (ja) * | 1996-07-15 | 2005-10-19 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| KR100224704B1 (ko) * | 1996-07-23 | 1999-10-15 | 윤종용 | 박막 트랜지스터-액정표시장치 및 그 제조방법 |

| KR100234892B1 (ko) * | 1996-08-26 | 1999-12-15 | 구본준 | 액정표시장치의 구조 및 그 제조방법 |

| KR100209620B1 (ko) * | 1996-08-31 | 1999-07-15 | 구자홍 | 액정 표시 장치 및 그 제조방법 |

| CN1148600C (zh) * | 1996-11-26 | 2004-05-05 | 三星电子株式会社 | 薄膜晶体管基片及其制造方法 |

-

1998

- 1998-12-28 JP JP37413198A patent/JP3973787B2/ja not_active Expired - Lifetime

- 1998-12-30 CN CN200810166498.3A patent/CN101387802B/zh not_active Expired - Lifetime

- 1998-12-30 CN CN200410062132.3A patent/CN1550838B/zh not_active Expired - Lifetime

- 1998-12-30 CN CN200410062131.9A patent/CN100595658C/zh not_active Expired - Lifetime

- 1998-12-30 CN CN200410062130.4A patent/CN100595657C/zh not_active Expired - Lifetime

- 1998-12-30 CN CNB981271723A patent/CN1173218C/zh not_active Expired - Lifetime

- 1998-12-30 US US09/222,783 patent/US6317173B1/en not_active Expired - Lifetime

-

2001

- 2001-09-20 US US09/956,145 patent/US6549249B2/en not_active Expired - Lifetime

-

2003

- 2003-02-19 US US10/367,769 patent/US6784950B2/en not_active Expired - Lifetime

- 2003-02-19 US US10/367,743 patent/US7271857B2/en not_active Expired - Lifetime

-

2005

- 2005-03-18 US US11/082,983 patent/US7227597B2/en not_active Expired - Lifetime

-

2007

- 2007-04-11 JP JP2007103355A patent/JP4884281B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| CN100595657C (zh) | 2010-03-24 |

| US20030147022A1 (en) | 2003-08-07 |

| CN101387802A (zh) | 2009-03-18 |

| CN1550837A (zh) | 2004-12-01 |

| US7227597B2 (en) | 2007-06-05 |

| JP3973787B2 (ja) | 2007-09-12 |

| US20050161677A1 (en) | 2005-07-28 |

| JPH11271812A (ja) | 1999-10-08 |

| CN100595658C (zh) | 2010-03-24 |

| CN1550838A (zh) | 2004-12-01 |

| US7271857B2 (en) | 2007-09-18 |

| CN1224887A (zh) | 1999-08-04 |

| US6784950B2 (en) | 2004-08-31 |

| US6317173B1 (en) | 2001-11-13 |

| US20030184686A1 (en) | 2003-10-02 |

| US20020012078A1 (en) | 2002-01-31 |

| JP4884281B2 (ja) | 2012-02-29 |

| CN1550838B (zh) | 2010-05-12 |

| US6549249B2 (en) | 2003-04-15 |

| JP2007199736A (ja) | 2007-08-09 |

| CN101387802B (zh) | 2012-05-16 |

| CN1550861A (zh) | 2004-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1173218C (zh) | 液晶显示装置及其制造方法和驱动方法 | |

| CN1261805C (zh) | 液晶显示装置 | |

| CN1169015C (zh) | 具有涂敷膜的薄膜器件、液晶屏以及薄膜器件的制造方法 | |

| CN1193403C (zh) | 半导体器件 | |

| CN1043702C (zh) | 半导体器件 | |

| CN1218401C (zh) | 半导体器件 | |

| CN1221845C (zh) | 采用横向电场的有源矩阵寻址液晶显示装置 | |

| CN1242489C (zh) | 半导体器件及其制造方法 | |

| CN1287207C (zh) | 平面内开关模式有源矩阵型液晶显示器件及其制造方法 | |

| CN1199080C (zh) | 液晶显示装置 | |

| CN1607432A (zh) | 薄膜晶体管阵列基板和液晶显示面板及它们的制造方法 | |

| CN1286493A (zh) | 半导体器件及其制造方法 | |

| CN1482591A (zh) | 驱动电路使用该驱动电路的显示器件及电子装置 | |

| CN1165806C (zh) | 有源矩阵型显示器 | |

| CN1648748A (zh) | 显示装置 | |

| CN1279519A (zh) | 电致发光显示器件及电子装置 | |

| CN101079397A (zh) | 制造半导体器件的方法 | |

| CN1601361A (zh) | 液晶显示器 | |

| CN1838433A (zh) | 半导体器件以及图像显示装置 | |

| CN101038729A (zh) | 像素电路与具有像素电路的图像显示装置 | |

| CN1607445A (zh) | 水平电场施加型液晶显示板及其制造方法 | |

| CN1341231A (zh) | Tft阵列基板及其制造方法以及使用它的液晶显示装置 | |

| CN1405805A (zh) | 电容器、半导体装置和其制造方法、电光装置及电子机器 | |

| CN1603929A (zh) | 液晶显示器及用于其的薄膜晶体管阵列板 | |

| CN1879054A (zh) | 薄膜晶体管阵列面板及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: SAMSUNG DISPLAY CO., LTD. Free format text: FORMER OWNER: SAMSUNG ELECTRONICS CO., LTD. Effective date: 20121102 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20121102 Address after: Gyeonggi Do, South Korea Patentee after: Samsung Display Co., Ltd. Address before: Gyeonggi Do, South Korea Patentee before: Samsung Electronics Co., Ltd. |

|

| CX01 | Expiry of patent term | ||

| CX01 | Expiry of patent term |

Granted publication date: 20041027 |