WO2010044315A1 - 貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置 - Google Patents

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置 Download PDFInfo

- Publication number

- WO2010044315A1 WO2010044315A1 PCT/JP2009/064886 JP2009064886W WO2010044315A1 WO 2010044315 A1 WO2010044315 A1 WO 2010044315A1 JP 2009064886 W JP2009064886 W JP 2009064886W WO 2010044315 A1 WO2010044315 A1 WO 2010044315A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- electrode substrate

- substrate

- hole

- metal material

- electrode

- Prior art date

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 200

- 239000004065 semiconductor Substances 0.000 title claims abstract description 27

- 238000000034 method Methods 0.000 title claims description 65

- 238000004519 manufacturing process Methods 0.000 title claims description 23

- 239000007769 metal material Substances 0.000 claims abstract description 71

- 239000013078 crystal Substances 0.000 claims description 59

- 238000009713 electroplating Methods 0.000 claims description 38

- 229910052751 metal Inorganic materials 0.000 claims description 26

- 239000002184 metal Substances 0.000 claims description 26

- 238000011049 filling Methods 0.000 claims description 16

- 230000035515 penetration Effects 0.000 claims description 12

- 230000000149 penetrating effect Effects 0.000 claims description 9

- 229910052710 silicon Inorganic materials 0.000 claims description 4

- 239000010703 silicon Substances 0.000 claims description 4

- 238000005259 measurement Methods 0.000 description 28

- 230000000052 comparative effect Effects 0.000 description 22

- 230000001133 acceleration Effects 0.000 description 18

- 239000010949 copper Substances 0.000 description 18

- 239000002245 particle Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 15

- 238000001887 electron backscatter diffraction Methods 0.000 description 15

- 238000007747 plating Methods 0.000 description 14

- 230000008569 process Effects 0.000 description 12

- 238000012545 processing Methods 0.000 description 11

- 238000009826 distribution Methods 0.000 description 10

- 238000006073 displacement reaction Methods 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 7

- 239000011651 chromium Substances 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 238000005530 etching Methods 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 238000005498 polishing Methods 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 239000010948 rhodium Substances 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000000708 deep reactive-ion etching Methods 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 238000000227 grinding Methods 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- XKRFYHLGVUSROY-UHFFFAOYSA-N argon Substances [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- -1 argon ions Chemical class 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000000994 depressogenic effect Effects 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000005553 drilling Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 238000002003 electron diffraction Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000005496 eutectics Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 239000002923 metal particle Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 238000000678 plasma activation Methods 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 238000005488 sandblasting Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/423—Plated through-holes or plated via connections characterised by electroplating method

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/147—Semiconductor insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group H01L27/00 or H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13025—Disposition the bump connector being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

- H01L2224/16146—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked the bump connector connecting to a via connection in the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16227—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16235—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a via metallisation of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

- H01L2224/171—Disposition

- H01L2224/1718—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/17181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73257—Bump and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0651—Wire or wire-like electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01024—Chromium [Cr]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01045—Rhodium [Rh]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01049—Indium [In]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09563—Metal filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/14—Related to the order of processing steps

- H05K2203/1476—Same or similar kind of process performed in phases, e.g. coarse patterning followed by fine patterning

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/14—Related to the order of processing steps

- H05K2203/1492—Periodical treatments, e.g. pulse plating of through-holes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/425—Plated through-holes or plated via connections characterised by the sequence of steps for plating the through-holes or via connections in relation to the conductive pattern

- H05K3/426—Plated through-holes or plated via connections characterised by the sequence of steps for plating the through-holes or via connections in relation to the conductive pattern initial plating of through-holes in substrates without metal

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/44—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits

- H05K3/445—Manufacturing insulated metal core circuits or other insulated electrically conductive core circuits having insulated holes or insulated via connections through the metal core

Definitions

- the present invention relates to a through electrode substrate provided with a through electrode penetrating the front and back of the substrate, a manufacturing method thereof, and a semiconductor device using the through electrode substrate.

- a semiconductor device refers to all devices that can function using semiconductor characteristics, and a semiconductor integrated circuit and an electronic device are included in the scope of the semiconductor device.

- Patent Document 1 a through electrode substrate having a conductive portion that conducts the front and back of the substrate as an interposer between LSI chips has been proposed (Patent Document 1).

- the through electrode substrate is formed by filling a through hole provided in the substrate with a conductive material (Cu) by electrolytic plating.

- the through electrode substrate When the through electrode substrate is used for connection between a plurality of LSI chips or between an LSI chip and a MEMS device, it is possible to reliably ensure conductivity at a conduction portion formed by electrolytic plating, and the resistance value is Improvements in electrical properties such as low properties are required.

- Patent Document 2 discloses a technique for reducing voids in the through electrode manufacturing process.

- Patent Document 2 an approach to ensuring the conductivity of the conductive portion is studied, but the electrical characteristics in the conductive portion are not studied.

- the present invention has been made in view of the above-described problems, and it is an object of the present invention to provide a through electrode substrate having improved electrical characteristics in a conducting portion that conducts the front and back of the substrate, and a semiconductor device using the same.

- a substrate having a through-hole penetrating the front and back, and a conductive portion filled in the through-hole and including a metal material, the conductive portion is an area-weighted average crystal grain

- a through electrode substrate including at least a metal material having a diameter of 13 ⁇ m or more.

- the conducting part preferably includes at least a metal material having a crystal grain size of 29 ⁇ m or more.

- One end of the conducting part preferably includes a metal material having an area-weighted average crystal grain size of less than 13 ⁇ m, and the other end of the conducting part preferably includes at least a metal material having an area-weighted average crystal grain size of 13 ⁇ m or more. .

- the substrate may be made of silicon, and the conductive portion may be formed on at least an insulating layer provided on the substrate side.

- the opening diameter of the through hole is preferably 10 ⁇ m to 100 ⁇ m, and the thickness of the substrate is preferably 20 to 100 ⁇ m.

- the opening diameter of the through hole is preferably 10 ⁇ m to 100 ⁇ m, and the thickness of the substrate is preferably 300 to 800 ⁇ m.

- a plurality of the through electrode substrates may be stacked.

- a semiconductor device may be configured by including at least one semiconductor chip provided with a connection terminal portion and connecting the connection terminal portion and a conduction portion of the through electrode substrate.

- a through hole penetrating front and back is formed in the substrate, an insulating film is formed on a surface of the substrate and the through hole, and at least one surface of the substrate and / or the through hole is formed.

- a method of manufacturing a through electrode substrate in which a metal material is filled in the through hole by an electrolytic plating method in which a seed film made of metal is formed in the hole and a pulse voltage is supplied to the seed film.

- the electrolytic plating method may be performed by periodically applying a positive voltage and a negative voltage to the seed film.

- the through hole After forming a metal material in the through hole by an electrolytic plating method for supplying a first time direct current to the seed film, the through hole is formed by an electrolytic plating method for supplying a second time pulse current to the seed film.

- the inside may be filled with a metal material.

- the current density of the pulse current may be increased stepwise to fill the through hole with the metal material.

- substrate which improved the electrical property in the conduction

- FIG. 3 is an area-weighted crystal grain size distribution diagram of the metal material of the conductive portion 106 of the through electrode substrate 100 of the present invention according to Example 1.

- FIG. 6 is an area weighted crystal grain size distribution diagram of a metal material of a conductive portion of a through electrode substrate according to Comparative Example 1.

- FIG. 6 is an area weighted crystal grain size distribution diagram of a metal material of a conductive portion of a through electrode substrate according to Comparative Example 2.

- FIG. FIG. 3 is an area weighted crystal grain size distribution diagram of a metal material in a direct current region 106b of a conduction part 106 of a through electrode substrate 100 of the present invention according to Example 1.

- 3 is an area weighted crystal grain size distribution diagram of a metal material in a DC-pulse switching region 106c of a conduction part 106 of a through electrode substrate 100 of the present invention according to Example 1.

- FIG. 3 is an area weighted crystal grain size distribution diagram of a metal material in a current initial region 106e of a conducting portion 106 of a through electrode substrate 100 of the present invention according to Example 1;

- FIG. 3 is an area weighted crystal grain size distribution diagram of a metal material in a pulse current late region 106d of a conduction part 106 of a through electrode substrate 100 of the present invention according to Example 1;

- It is a schematic diagram which shows the growth rate dispersion

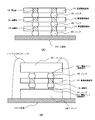

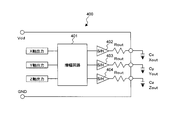

- FIG. 4 is a cross-sectional view for explaining a semiconductor device in which LSI chips are stacked on a through electrode substrate 100 according to the present invention and a stacked through electrode substrate 300 in which the through electrode substrate 100 according to the present invention is stacked. It is a figure which shows an example of the acceleration process circuit which processes the displacement signal of the acceleration detected by a physical quantity sensor. It is a figure which shows an example of the mobile terminal which mounted the sensor module.

- the through electrode substrate of the present invention can be implemented in many different modes, and is not construed as being limited to the description of the embodiments and examples shown below. Note that in the drawings referred to in this embodiment mode and examples, the same portions or portions having similar functions are denoted by the same reference numerals, and repetitive description thereof is omitted.

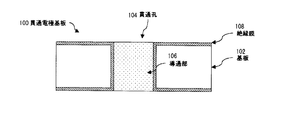

- FIG. 1 is a cross-sectional view of a through electrode substrate 100 of the present invention according to this embodiment.

- the through electrode substrate 100 of the present invention according to this embodiment includes a through hole 104 penetrating the front and back of the substrate 102 serving as a core.

- a conduction portion 106 is formed inside the through hole 104.

- the substrate 102 is made of a semiconductor material such as silicon, and a through hole 104 is formed by a method such as etching, laser, or sandblasting, which will be described later.

- the thickness of the substrate 102 is, for example, 10 to 800 ⁇ m, but is not limited thereto. In FIG.

- a substrate having a thickness in the range of 300 to 800 ⁇ m or 20 to 100 ⁇ m may be appropriately selected according to the application.

- an insulating film 108 for ensuring electrical insulation is provided on the inner wall of the through hole 104 and the surface of the substrate 102.

- the insulating film 108 is made of, for example, SiO 2 and is formed by a thermal oxidation method, a CVD method, or the like.

- the thickness of the insulating film 108 is about 0.1 to 2 ⁇ m, and the thickness is not particularly limited as long as sufficient insulation can be ensured.

- the opening diameter of the through hole 104 is about 10 to 100 ⁇ m.

- the opening diameter of the through hole 104 is not limited to this, and can be set as appropriate according to the use of the through electrode substrate 100 and the like.

- the conductive portion 106 is a wiring that provides conduction between the front and back of the through electrode substrate 100 and is filled with a conductive material including a metal material.

- the conductive portion 106 is filled with a metal material by electrolytic plating as will be described later.

- a metal material used for the conductive portion 106 for example, copper can be used.

- the metal material of the conductive portion 106 includes crystal grains having an area-weighted average crystal grain size of 13 ⁇ m or more, as will be described later. Further, in the through electrode substrate 100 of the present invention according to this embodiment, the metal material of the conductive portion 106 includes crystal grains having a maximum crystal grain size of 29 ⁇ m or more, as will be described later. In the through electrode substrate 100 of the present invention according to this embodiment, the electrical characteristics at the conductive portion 106 can be improved by the above configuration.

- a substrate 102 made of silicon is prepared.

- the thickness of the substrate 102 is not particularly limited, but is 300 to 800 ⁇ m.

- a mask (not shown) selected from a resist, a silicon oxide film, a silicon nitride film, a metal, or the like is formed on one surface side of the substrate 102, and then the substrate 102 is etched in the thickness direction through the mask and penetrated. Hole 104 is formed.

- an etching method an RIE method, a DRIE method, or the like can be used.

- the through-holes 104 penetrating the front and back of the substrate 102 may be formed only by etching, or the through-holes 104 are formed by forming a bottomed hole in the substrate 102 and then polishing and opening with a back grind. May be.

- the thickness of the substrate 102 may be reduced to 300 ⁇ m or less by polishing.

- the insulating film 108 is formed on the surface of the substrate 102.

- the insulating film 108 is a silicon oxide film and is formed by a thermal oxidation method or a CVD method.

- a silicon oxide film, a silicon nitride film, a silicon nitride oxide film, a stacked film thereof, or the like may be used.

- a seed layer 110 is formed on at least one surface of the substrate 102.

- the seed layer 110 is composed of a Ti layer on the substrate 102 side, a Cu layer (hereinafter referred to as Cu / Ti layer), a Cu layer / TiN layer, or a Cu / Cr layer thereon.

- a Cu / Cr layer is used for the seed layer 110.

- a method for forming the seed layer 110 can be appropriately selected from PVD, sputtering, and the like.

- the metal material used for the seed layer 110 can be appropriately selected depending on the metal material of the conductive portion 106.

- the seed layer 110 becomes a seed part and a power feeding part for forming the conductive part 106 by electrolytic plating.

- FIG. 2D Formation of conductive portion 106 (FIG. 2D) Electric power is supplied to the seed layer 110 using an electrolytic plating method, and the through hole 104 is filled with a metal material.

- copper (Cu) is used as the metal material that fills the through hole 104.

- the through hole 104 is filled with a metal material by an electrolytic plating method that supplies current to the seed layer 110 in a pulsed manner.

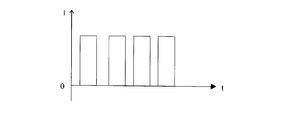

- the pulse current supply method shown in FIG. 4 is a method of supplying a pulse current that does not reverse the polarity to the seed layer 110.

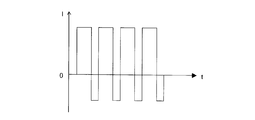

- the pulse current supply method shown in FIG. 5 is a method in which a pulse current whose polarity is periodically reversed is applied to the seed layer 110.

- the plating method by supplying a pulse current shown in FIG. 5 is called a PRC (Periodical Reversed Current) method.

- PRC Physical Reversed Current

- the current flowing through the seed layer 110 is constant. Forward (the state where the plating side, ie, the seed layer 110 side has a negative potential (a state where a positive current flows)) and reverse (the state where the plating side, ie, the seed layer 110 side becomes a positive potential)

- This is one of the plating methods performed by switching the flowing state

- the applied voltage, supply current, current density, and pulse switching time duty ratio

- the applied voltage, current density, and pulse switching time may be changed during the electrolytic plating.

- the current flowing through the seed layer 110 by supplying a pulse current flows from 0.5 A to 1.5 A when a positive voltage is applied, and from ⁇ 6 A to ⁇ 2 A when a negative voltage is applied.

- the current may flow.

- a lid is formed on the bottom of the through hole 104 on the surface where the seed layer 110 is formed by an electrolytic plating method in which a constant direct current is supplied to the seed layer 110.

- a metal layer may be formed.

- a metal material to fill the through hole 104 other than Cu, gold (Au), rhodium (Rh), silver (Ag), platinum (Pt), tin (Sn), aluminum (Al), nickel (Ni), A material selected and combined from metals such as chromium (Cr) and alloys thereof can be used.

- a lid-like metal layer When a lid-like metal layer is formed by supplying a direct current, the current density is reduced for a certain period of time in the initial stage of switching to a pulse current, and gradually (for example, stepwise with respect to the elapsed time or A method of increasing the current density proportionally) is preferred.

- a direct current When a direct current is supplied to form a lid-like metal layer, the growth of the metal layer tends to be faster at the portion in contact with the through hole 104. Therefore, the lid-like metal layer has a shape that is recessed toward the center.

- supplying a pulse current having a small current density for a certain period of time at the initial stage of switching to the pulse current it is considered that the growth of the metal layer that flattens the recess occurs.

- a through electrode excellent in electrical characteristics can be obtained, and the productivity of the through electrode substrate can be improved.

- the depth of the through hole is relatively shallow (for example, about 20 ⁇ m to 100 ⁇ m) or the thickness is 20 to 100 ⁇ m. It is often used when it is desired to obtain a through electrode substrate having a thin thickness.

- a mask (not shown) selected from a resist, a silicon oxide film, a silicon nitride film, a metal, and the like is formed on one surface side of the substrate 102, and then the substrate 102 is etched in the thickness direction through the mask. A bottomed hole 112 that does not penetrate 102 is formed.

- an etching method an RIE method, a DRIE method, or the like can be used.

- a seed layer 114 is formed on the surface of the substrate 102 over which the insulating film 108 is formed.

- the seed layer 114 is also formed inside the hole 112 as shown in FIG.

- the seed layer 114 is formed of a Cu layer / Ti layer or the like, similar to the seed layer 110 described above.

- the seed layer 114 serves as a seed portion and a power feeding portion for forming the conductive portion 106 by electrolytic plating.

- the seed layer 114 is formed by MOCVD, sputtering, vapor deposition, or the like.

- Formation of conductive portion 106 Power is supplied to the seed layer 114 using an electrolytic plating method, and the hole 112 is filled with a metal material. Also in the through electrode substrate manufacturing method 2 of the present embodiment, as in the through electrode substrate manufacturing method 1, as shown in FIG. 4 or FIG. 5, by an electroplating method for supplying current to the seed layer 110 in a pulsed manner, The through hole 112 is filled with a metal material. Before supplying the pulse current, a constant direct current may be supplied to the seed layer 110 as shown in FIG. In the present embodiment, copper (Cu) is used as the metal material filling the holes 112.

- a metal material filled in the through hole 104 in addition to copper, gold (Au), rhodium (Rh), silver (Ag), platinum (Pt), tin (Sn), aluminum (Al), nickel (Ni), A material selected and combined from metals such as chromium (Cr) and alloys thereof can be used.

- Example 1 Hereinafter, examples of the through electrode substrate 100 of the present invention will be described.

- a resist is applied to one surface side of the substrate 102, exposed, and developed to form a mask (not shown).

- the substrate 102 is etched in the thickness direction through the mask by the DRIE method to form a bottomed hole 112 having a thickness of 430 ⁇ m (FIG. 2A).

- the substrate 102 is polished to a thickness of 400 ⁇ m by back grinding.

- a thermal oxide film having a thickness of 1 ⁇ m is formed on the surface of the substrate 102 by thermal oxidation. Thereafter, a silicon nitride film having a thickness of 200 nm is formed by LPCVD. These thermal oxide film and silicon nitride film form the insulating film 108 (FIG. 2B).

- a seed layer 110 is formed by sequentially depositing Cr having a thickness of 30 nm and Cu having a thickness of 200 nm on one surface of the substrate 102 (FIG. 2C).

- Example 1 a direct current having a current of 1.54 A and a current density of 1 A / dm 2 was supplied, and then power was supplied to the seed layer 110 using an electrolytic plating method by applying a pulse voltage shown in FIG.

- the hole 104 is filled with Cu (FIG. 2D).

- the pulse switching time was such that a positive current was supplied for 80 msec and a negative current was supplied for 2 msec.

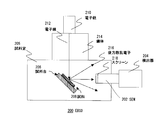

- FIG. 7 is a diagram illustrating the configuration of the EBSD device.

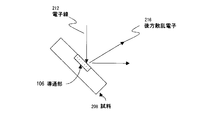

- FIG. 8 is a diagram for explaining the concept of sample measurement measured by an EBSD device. In measuring the crystal grain size of the conducting portion 106 according to the present embodiment, adjustment is made so that the electron beam 212 is irradiated to the cross-sectional portion of the penetrating portion 106.

- the EBSD device 200 is a technique in which a dedicated detector 204 is provided in a scanning electron microscope (SEM) 202 and a crystal orientation is analyzed from backscattered electrons of primary electrons. Specifically, when an electron beam 212 emitted from the electron gun 210 is incident (irradiated) on the sample 208 having a crystal structure placed on the sample stage 206 in the sample chamber 205 through the mirror body 214, the sample is irradiated. Inelastic scattering occurs at 208 and backscattered electrons 216 are generated. Among them, a linear pattern (generally called a Kikuchi image) peculiar to the crystal orientation by Bragg diffraction is also observed in the sample 208. The backscattered electrons 216 are detected by the detector 204 of the SEM 202 through the screen 218. Then, the crystal grain size of the sample 208 can be obtained by analyzing the detected Kikuchi image.

- SEM scanning electron microscope

- the crystal grain size measurement is repeated while moving the position of the electron beam irradiated to the sample 208 (mapping measurement), whereby the crystal grain size of the planar sample 208 is changed. Information can be obtained.

- the area (A) of the crystal grains is calculated by multiplying the number (N) of crystal grains by the area of the measurement point determined by the measurement step size (s).

- the measurement point is expressed as a hexagon, and the area (A) of the crystal grains can be expressed by the following formula (1).

- the crystal grain size (D) is calculated as the diameter of a circle having an area equal to the crystal grain area (A).

- the crystal grain size (D) can be expressed by the following formula (2).

- Crystal grain size refers to the value measured as described above. In the measurement of the crystal grain size, it is assumed that the edge grain is included.

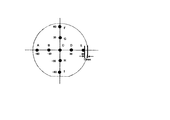

- FIG. 10 is an area-weighted crystal grain size distribution diagram of a metal material crystal constituting the conductive portion 106 of the through electrode substrate 100 of the present invention according to the first embodiment.

- the maximum value and the average value of the crystal grain sizes constituting the conducting portion 106 can be calculated by a histogram with the crystal grain size (D) on the horizontal axis and the area ratio (Rs) on the vertical axis.

- the area ratio Rs (ratio including crystal grain size (area weighting)) can be expressed by the following formula (3) using the area (Sm) of the measurement region.

- the horizontal axis of the histogram shown in FIG. 10 indicates the value (D) of the crystal grain size

- the vertical axis (area fraction) indicates the ratio including the crystal grains of that value by area weighting. For example, 0.15 on the vertical axis in FIG. 10 means a ratio of 15%.

- an average crystal grain size (Ds) weighted by area is determined.

- the crystal grain size is a value including the crystal grain (Grain) included in the edge (Edge) of the measurement region.

- the analysis result includes an error, the rounded down numerical value is used without considering the decimal point.

- the measurement conditions are as follows. Used analyzer SEM JSM JSM-7000 FEBSD TSL OIM Software Ver. 4.6 Observation condition EBSD measurement Acceleration voltage 25kV Sample tilt angle 70 ° Measurement step 0.3 ⁇ m

- the maximum particle size of the metal material of the conductive portion 106 of the through electrode substrate 100 of the present invention according to Example 1 was 29 ⁇ m, and the average particle size (area weighting) was 13 ⁇ m.

- the resistance value of the conductive portion 106 of the through electrode substrate 100 of the present invention according to Example 1 was 3.15 ⁇ 10 ⁇ 4 ⁇ . It was confirmed that it has characteristics and superiority.

- Example 1 Since the process up to filling the metal material into the through hole in Comparative Example 1 is the same as in Example 1, the diameter and length of the through part 106 in Example 1 (that is, the thickness of the substrate) And the diameter and length of the penetrating portion in the comparative example 1 (that is, the thickness of the substrate) are the same.))

- the area-weighted crystal grain size of the metal material constituting the conducting portion of the penetrating electrode substrate A distribution chart is shown in FIG.

- the maximum particle size of the metal material constituting the conductive portion of the through electrode substrate according to Comparative Example 1 was 10 ⁇ m, and the average particle size (area weighting) was 2 ⁇ m. Since the resistance value of the conductive portion 106 of the through electrode substrate according to Comparative Example 1 was 7.25 ⁇ 10 ⁇ 3 ⁇ , it can be seen that the electrical characteristics of the conductive portion are inferior to those of Example 1.

- the resistance of the conductive portion 106 of the through electrode substrate 100 of the present invention according to Example 1 was reduced to 1/23 as compared with the resistance of the conductive portion of Comparative Example 1.

- FIG. 12 shows an area weighted crystal grain size distribution diagram of the metal material crystal constituting the conductive portion of the through electrode substrate according to Comparative Example 2.

- the maximum particle size of the metal material constituting the conducting portion of the through electrode substrate according to Comparative Example 2 was 11 ⁇ m, and the average particle size (area weighting) was 2 ⁇ m.

- unnecessary portions of the seed layer 114 and the conductive portion 106 were removed and the side where the hole 112 was formed, as shown in FIG.

- the surface of the opposite substrate 102 was polished until the surface of the conductive portion 106 was exposed. Since the resistance value of the conductive portion 106 of the through electrode substrate according to Comparative Example 2 was 1.08 ⁇ 10 ⁇ 3 ⁇ , it can be seen that the electrical characteristics of the conductive portion are inferior to those of Example 1.

- Example 1 Comparative Example 1

- Comparative Example 2 Comparative Example 2

- Example 1 the metal filling start side of the conductive portion 106 in which a lid-like metal layer was formed by supplying a direct current and the metal filling end side filled with a metal material by supplying a pulse current The crystal grain size was measured and compared.

- FIG. 9 is a diagram showing a region where the crystal grain size of the metal material filled in the conductive portion 106 is measured.

- the measurement areas are a DC current area 106b, a DC-pulse switching area 106c, and a pulse current late area 106d from the plating start side.

- the direct current region 106b the filling speed of the portion in contact with the substrate 102 tends to be high, and at the boundary of switching from the direct current to the pulse current, the filling state of the crystal of the metal material such that the central portion of the conducting portion 106 is depressed. It becomes.

- the area-weighted average particle diameter was 1.92 ⁇ m.

- the area-weighted average particle size was 4.82 ⁇ m.

- the area-weighted average particle size is 5.84 ⁇ m, and the average particle size is significantly higher than that in the DC current region. You can see that it is getting bigger.

- the pulse current late region 106d as shown in FIG. 16, the area-weighted average particle diameter was 23.58 ⁇ m, and crystals having a particle diameter of 50 ⁇ m or more were also generated.

- Comparative Examples 1 and 2 described above will be described.

- Comparative Example 1 The process before filling the through hole with the metal material is the same as that of the first embodiment.

- the thickness of the substrate 102 before forming the thermal oxide film was 400 ⁇ m.

- the direct current shown in FIG. 6 is supplied to the seed layer using an electrolytic plating method, and the conductive portion is filled with a metal material.

- the current at this time was 1.54 A (current density 1 A / dm 2 ).

- Subsequent steps were the same as in Example 1.

- Comparative Example 2 Regarding the process before filling the through hole with the metal material, refer to 2-2.

- a direct current shown in FIG. 6 is supplied to the seed layer using an electrolytic plating method, and a conductive material is filled with a metal material.

- the current at this time was 1.54 A (current density 1 A / dm 2 ).

- Subsequent steps were the same as in Example 1.

- the thickness of the substrate 102 before forming the thermal oxide film was 70 ⁇ m.

- Example 1 and Comparative Example 1 uses an electrolytic plating method, and as shown in FIG. 17, the growth rate of filling plating is different for each conductive portion of the through electrode substrate.

- the electrolytic plating method as shown in FIG. 17A, a lid plating 107 made of a metal material is formed on the seed 110 side of the through-hole 104, and subsequently, the metal material is filled as shown in FIG. 17B.

- “cover plating” means that in the initial stage of electrolytic plating, a metal material is deposited on the surface of the seed layer, and the metal material is concentrated in the opening of the through hole having a high electrolytic density. The metal layer formed so that the opening part of this may be obstruct

- a metal layer grows from the lid plating 107 to above the through-hole 104 by electrolytic plating. At this time, the growth rate of the metal layer differs for each through hole 104.

- the filling of the metal material by the electrolytic plating method is performed while measuring the level difference between the insulating film 108 and the plating filled in the through hole 104, and the metal layer in the through hole 104 with the slowest growth as shown in FIG.

- the step between the upper surface of the substrate 102 and the surface of the insulating film 108 of the substrate 102 disappears, the process ends.

- the through electrode substrate in which all the through holes 104 are filled with the metal layer as shown in FIG. 17 (d)

- the thickness d of the metal layer that protrudes from the through electrode substrate and grows is measured for several conductive portions. Compared.

- Example 1 the film thickness d was measured for the conductive portions at the nine measurement points (A to I) shown in FIG.

- measurement was performed on three substrates, and in Comparative Example 1, measurement was performed using four substrates.

- the measurement results are shown in Table 2.

- the film thickness variation is represented by ⁇ (Max-Min) / ave / 2 ⁇ 100 ⁇ , where ave is the average film thickness, Max is the maximum film thickness, and Min is the minimum value.

- ave is the average film thickness

- Max is the maximum film thickness

- Min is the minimum value.

- Table 2 in Example 1, the variation in film thickness is as small as about 10% even when the variation between the substrates is seen, whereas in Comparative Example 1, the variation in film thickness is 50% or more and 70%. Some substrates showed a large variation of nearly%.

- the growth of the metal layer by supplying the pulse current of Example 1 has an excellent effect that it can realize uniform growth with less variation compared to the growth of the metal layer by supplying the direct current of Comparative Example 1. Play.

- FIG. 19A shows a semiconductor device according to this embodiment in which three through electrode substrates 100 according to the present invention according to the first embodiment are stacked.

- a semiconductor element such as a DRAM is formed on the through electrode substrate 100.

- the three through electrode substrates 100 are stacked and connected to each other through bumps 302.

- the through electrode substrate 100 plays a role as an interposer for electrically connecting the DRAMs formed therein.

- the through electrode substrate 100 laminated in three layers is connected to the LSI substrate 304 via the bumps 302. Note that the number of through electrode substrates 100 to be stacked is not limited to three layers.

- a metal such as In (indium), Cu, or Au can be used for the bump 304.

- a resin such as polyimide or BCB (benzocyclobutene) may be mainly used for application and baking to bond them. Moreover, you may use an epoxy resin for joining of the penetration electrode substrates 100. Further, for the bonding between the through electrode substrates 100, bonding by plasma activation, eutectic bonding, or the like may be used.

- the resistance of the conductive portion 106 (through hole) of the through electrode substrate 100 of the present invention is Ri, and the through electrode substrate 100 of the present invention is stacked and connected.

- the resistance of the entire conductive portion 106 (through hole) connected in series is N ⁇ Ri, and the resistance of the conductive portion 106 (through hole) can be reduced.

- FIG. 19B shows an example of a semiconductor device having a through electrode substrate 100 on which LSI chips (semiconductor chips) 306-1 and 306-2 such as a MEMS device, a CPU, and a memory are mounted.

- the electrode pads 308-1 and 308-2 which are connection terminals of the LSI chips 306-1 and 306-2, are electrically connected to the conductive portion 106 of the through electrode substrate 100 via the bumps 304, respectively.

- the through electrode substrate 100 on which the LSI chips 306-1 and 306-2 are mounted is mounted on the LSI substrate 306, and the LSI substrate 306 and the LSI chip 306-1 are connected by wire bonding.

- the through electrode substrate 100 according to the first embodiment of the present invention can be used as an interposer for three-dimensionally mounting a plurality of LSI chips.

- the through electrode substrate 100 of the present invention has a small resistance value of the conductive portion 106 and an improved electrical characteristic.

- the amount of heat generated in the conductive portion 106 can be reduced. Thereby, a semiconductor device in which the through electrode substrate 100 is mounted at a high density can be realized.

- FIG. 20 is a diagram showing a circuit configuration of an acceleration processing circuit 400 that processes an acceleration displacement signal detected by the physical quantity sensor 302-1.

- the physical quantity sensor is a piezoresistive acceleration sensor.

- the acceleration processing circuit 400 includes an amplifier circuit 401, sample and hold circuits (S / H) 402 to 404, an output resistor Rout, and capacitors Cx, Cy, Cz.

- the X-axis output, Y-axis output, and Z-axis output in the figure are displacement signals in the X-axis direction, Y-axis direction, and Z-axis direction that are output from the physical quantity sensor 302-1 according to the applied acceleration. is there.

- the output resistor Rout and the capacitors Cx, Cy, Cz function as a low-pass filter that allows a frequency component corresponding to the acceleration signal to pass.

- the amplification circuit 401 amplifies each displacement signal (capacitance change) in the X-axis direction, the Y-axis direction, and the Z-axis direction output from the physical quantity sensor 302-1 in accordance with the applied acceleration at a predetermined amplification factor. Are output to the sample and hold circuits 402 to 404, respectively.

- the sample hold circuit 402 samples / holds the X axis direction displacement signal amplified by the amplifier circuit 401 at a predetermined timing, and outputs an X direction acceleration detection signal Xout via the output resistor Rout and the capacitor Cx.

- the sample hold circuit 403 samples / holds the Y-axis direction displacement signal amplified by the amplifier circuit 401 at a predetermined timing, and outputs a Y-direction acceleration detection signal Yout through the output resistor Rout and the capacitor Cy.

- the sample hold circuit 404 samples / holds the Z-axis direction displacement signal amplified by the amplifier circuit 401 at a predetermined timing, and outputs an acceleration detection signal Zout in the Z direction via the output resistor Rout and the capacitor Cz.

- FIG. 21 shows an example of a portable information terminal 500 which is an example of a semiconductor device on which the through electrode substrate 100 of the present invention on which the physical quantity sensor 302-1 and the processing circuit 400 are mounted or the stacked through electrode substrate 300 of the present invention is mounted.

- the portable information terminal 500 includes a housing 501, a display unit 502, and a keyboard unit 503.

- the sensor module is mounted inside the keyboard unit 502.

- the portable information terminal 500 has a function of storing various programs therein and executing communication processing, information processing, and the like by the various programs.

- the acceleration at the time of falling is detected by using the acceleration and angular velocity detected by the sensor module in which the physical quantity sensor 302-1 and the processing circuit 400 are mounted in the application program.

- a function such as turning off the power can be added.

- Electrode pads 100: Through-electrode substrate 102: Substrate 104: Through-hole 106: Conductive portion 106a: Center portion 106b: DC current region 106c: DC-pulse switching region 106d: Pulse current late region 106e: Pulse current initial region 107: Cover plating 108: Insulating film 110: Seed layer 302: Bumps 304, 306: LSI substrates 306-1 and 306-2: Chips 308-1 and 308-2: Electrode pads

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Wire Bonding (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

Abstract

基板の表裏を導通する導通部における電気特性を向上した貫通電極基板、及びそれを用いた半導体装置を提供するために、本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。また、導通部106は、結晶粒径が29μm以上の金属材料を含む。また、導通部の一端は、面積重み付けした平均結晶粒径が13μmより小さい金属材料を含み、導通部の他端は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。

Description

本発明は、基板の表裏を貫通する貫通電極を備えた貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置に関する。本明細書において、半導体装置とは、半導体特性を利用して機能し得る装置全般を指し、半導体集積回路、電子機器は半導体装置の範囲に含むものとする。

近年、電子機器の高密度、小型化が進み、LSIチップが半導体パッケージと同程度まで縮小化しており、LSIチップを2次元配置することのみによる高密度化は限界に達しつつある。そこで実装密度を上げるためにLSIチップを分け、それらを3次元に積層する必要がある。また、LSIチップを積層した半導体パッケージ全体を高速動作させるために積層回路同士を近づけ、積層回路間の配線距離を短くする必要がある。

そこで、上記の要求に応えるべく、LSIチップ間のインターポーザとして基板の表裏を導通する導通部を備えた貫通電極基板が提案されている(特許文献1)。特許文献1によれば、貫通電極基板は、基板に設けられた貫通孔内部を電解めっきによって導電材(Cu)を充填することで形成される。

貫通電極基板を複数のLSIチップ間の接続あるいはLSIチップとMEMSデバイスなどとの間の接続に用いる場合には、電解めっきで形成された導通部において確実に導通性が確保できること、そして抵抗値が低いこと等の電気特性の向上が求められる。

一方、貫通電極の製造工程において、ボイド(空隙)を低減する技術が特許文献2などに開示されている。しかしながら、特許文献2では、導通部の導通性確保に対するアプローチが検討されているが、導通部における電気特性に関して検討がなされていない。

そこで、本発明は上記の課題を鑑みてなされたものであり、基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供することにある。

本発明の一実施形態によると、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含むことを特徴とする貫通電極基板が提供される。