JP5259270B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5259270B2 JP5259270B2 JP2008168093A JP2008168093A JP5259270B2 JP 5259270 B2 JP5259270 B2 JP 5259270B2 JP 2008168093 A JP2008168093 A JP 2008168093A JP 2008168093 A JP2008168093 A JP 2008168093A JP 5259270 B2 JP5259270 B2 JP 5259270B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- temperature

- memory cell

- temperature sensor

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/413—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing, timing or power reduction

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Static Random-Access Memory (AREA)

Description

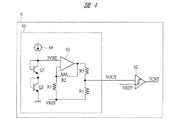

図1は本発明の実施の形態1による半導体装置において、SRAMモジュールの構成例を示すブロック図である。

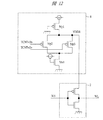

図9は、本発明の実施の形態2による半導体装置において、SRAMモジュールの構成例を示すブロック図、図10は、図9に示したワードドライバ2の構成例を示す回路図である。

図11は、本発明の実施の形態3による半導体装置において、SRAMモジュールの構成例を示すブロック図、図12は、図11に示したワードドライバ2及びドライバ電源回路8の構成例を示す回路図である。

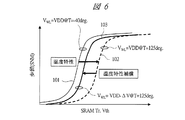

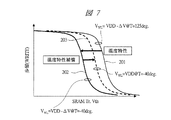

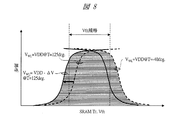

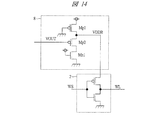

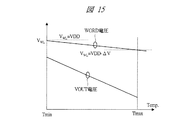

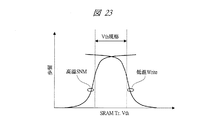

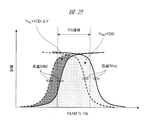

図13は、本発明の実施の形態4による半導体装置において、SRAMモジュールの構成例を示すブロック図、図14は、図13に示したワードドライバ2及びドライバ電源回路8の構成例を示す回路図、図15は、温度センサ部61の出力電圧VOUTとワード線WLのハイレベル電圧VWLの温度特性を示す図である。

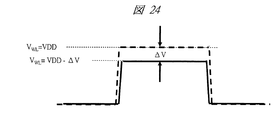

図16は、本発明の実施の形態5による半導体装置において、SRAMモジュールの構成例を示すブロック図、図17は、ライトアシスト回路を用いたメモリセルへの書き込み動作を示す波形図、図18は、図17の拡大図である。

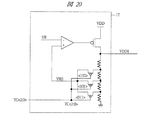

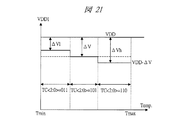

図19は、本発明の実施の形態6による半導体装置において、SRAMモジュールの構成例を示すブロック図、図20は、図19に示した降圧回路(2)17の構成例を示す回路図、図21は、降圧回路(2)17の出力電圧VDD1の温度特性を示す図である。

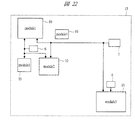

図22は、本発明の実施の形態7による半導体装置において、複数のSRAMモジュールを含むSOCの構成例を示すブロック図である。

2 ワードドライバ

3 ロウデコーダ(Row Decoder)

4 コントロールロジック(Control Logic)

5 メモリセルアレイ(Memory Array)

6 温度センサ回路

7 ヒューズ(FUSE)

8 ドライバ電源回路

10 SRAMモジュール

11 カラムデコーダ(Column Decoder)

12 カラムスイッチ(Column Switch)

13 ライトアンプ(Write Amp)

14 センスアンプ(Sense Amp)

15 SOC(System On a Chip)

16 ライトアシスト回路(Write Assist)

17 降圧回路(2)

61 温度センサ部

62 シュミットトリガ回路

63 差動アンプ

64 電流源

AX,AY アドレス選択信号

CK クロック

Mn1〜Mn3 n型MOSトランジスタ

Mp1〜Mp3,MP3〜MP5 p型MOSトランジスタ

Q1,Q2 バイポーラトランジスタ

R1〜R4 抵抗

VOUT 出力電圧

VREF 基準電圧

VWL ワード線WLのハイレベル電圧

WL ワード線

YS0 カラム選択信号

Claims (2)

- スタティック型メモリセルを有する半導体装置であって、

複数の前記スタティック型メモリセルが行列状に配置されたメモリセルアレイと、

前記半導体装置内の温度を検知する温度センサ回路と、

前記スタティック型メモリセルの書き込み又は読み出し動作時に、前記温度センサ回路の出力に基づいて、前記メモリセルアレイに供給される電圧を制御する電圧制御回路と、

ヒューズと、

前記メモリセルアレイと前記電圧制御回路とをそれぞれ備えた複数のメモリモジュールと、

前記複数のメモリモジュールの各メモリモジュールよりメモリ容量の大きい第2のメモリモジュールと、

第2の温度センサ回路と、を有し、

前記電圧制御回路により制御される電圧は、選択ワード線の電圧であり、

前記電圧制御回路は、前記半導体装置内の温度が第1温度より低い場合に、前記選択ワード線の電圧を第1電圧に設定し、前記半導体装置内の温度が前記第1温度より高い場合に、前記選択ワード線の電圧を前記第1電圧より低い第2電圧に設定し、

前記複数のメモリモジュールのそれぞれに対して、前記温度センサ回路の出力が共通に入力し、

前記電圧制御回路は、前記ヒューズと前記温度センサ回路の出力に基づいて前記メモリセルアレイに供給される電圧を制御し、

前記第2の温度センサ回路の出力が、前記第2のメモリモジュールの電圧制御回路に入力していることを特徴とする半導体装置。 - 高温にてリードマージンが小さくなり低温にてライトマージンが小さくなるような複数のスタティック型メモリセルを有する半導体装置であって、

複数の前記スタティック型メモリセルが行列状に配置されたメモリセルアレイと、

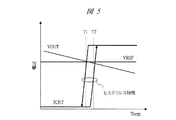

ヒステリシス特性を有するシュミットトリガ回路を備え、前記半導体装置内の温度を検知する温度センサ回路と、

前記スタティック型メモリセルの書き込み又は読み出し動作時に、前記温度センサ回路の出力に基づいて、前記メモリセルアレイの選択ワード線に供給される電圧を制御する電圧制御回路と、

前記メモリセルアレイと前記電圧制御回路とをそれぞれ備えた複数のメモリモジュールと、

前記複数のメモリモジュールの各メモリモジュールよりメモリ容量の大きい第2のメモリモジュールと、

ヒューズと、

第2の温度センサ回路と、を有し、

前記電圧制御回路は前記半導体装置の温度が第1の温度より低いときに前記選択ワード線の電圧を第1の電圧に設定し、前記半導体装置の温度が前記第1の温度より高いときに前記第1の電圧より低い第2の電圧に前記選択ワード線の電圧を設定し、高温時の前記リードマージンを大きくし、

前記複数のメモリモジュールのそれぞれに対して、前記温度センサ回路の出力が共通に入力しており、

前記電圧制御回路は、前記ヒューズと前記温度センサ回路の出力に基づいて前記メモリセルアレイに供給される電圧を制御し、

前記第2の温度センサ回路の出力が、前記第2のメモリモジュールの電圧制御回路に入力していることを特徴とする半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168093A JP5259270B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体装置 |

| US12/432,796 US7961500B2 (en) | 2008-06-27 | 2009-04-30 | Semiconductor device |

| US13/102,295 US8279696B2 (en) | 2008-06-27 | 2011-05-06 | Semiconductor device |

| US13/584,271 US8611166B2 (en) | 2008-06-27 | 2012-08-13 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168093A JP5259270B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010009674A JP2010009674A (ja) | 2010-01-14 |

| JP2010009674A5 JP2010009674A5 (ja) | 2011-04-28 |

| JP5259270B2 true JP5259270B2 (ja) | 2013-08-07 |

Family

ID=41447206

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008168093A Active JP5259270B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7961500B2 (ja) |

| JP (1) | JP5259270B2 (ja) |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5259270B2 (ja) * | 2008-06-27 | 2013-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2010282317A (ja) * | 2009-06-03 | 2010-12-16 | Elpida Memory Inc | 内部電源回路、半導体装置、及び半導体装置の製造方法 |

| JP5263015B2 (ja) * | 2009-06-08 | 2013-08-14 | 富士通セミコンダクター株式会社 | 半導体メモリ |

| JP2012059330A (ja) * | 2010-09-10 | 2012-03-22 | Toshiba Corp | 半導体装置 |

| JP5659893B2 (ja) * | 2011-03-16 | 2015-01-28 | 株式会社リコー | 半導体記憶装置 |

| US8755239B2 (en) * | 2011-11-17 | 2014-06-17 | Texas Instruments Incorporated | Read assist circuit for an SRAM |

| US8693235B2 (en) * | 2011-12-06 | 2014-04-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods and apparatus for finFET SRAM arrays in integrated circuits |

| US9939827B1 (en) * | 2011-12-16 | 2018-04-10 | Altera Corporation | Temperature dependent power supply circuitry |

| US8995218B2 (en) * | 2012-03-07 | 2015-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US8938573B2 (en) * | 2012-06-30 | 2015-01-20 | Intel Corporation | Row hammer condition monitoring |

| JP2014041668A (ja) | 2012-08-21 | 2014-03-06 | Fujitsu Semiconductor Ltd | 半導体記憶装置及び半導体記憶装置の制御方法 |

| WO2014045372A1 (ja) * | 2012-09-20 | 2014-03-27 | 株式会社日立製作所 | 半導体記憶装置 |

| JP2014086112A (ja) * | 2012-10-24 | 2014-05-12 | Fujitsu Semiconductor Ltd | 半導体記憶装置 |

| US9165668B1 (en) * | 2013-07-29 | 2015-10-20 | Western Digital Technologies, Inc. | Data retention monitoring using temperature history in solid state drives |

| US9330790B2 (en) | 2014-04-25 | 2016-05-03 | Seagate Technology Llc | Temperature tracking to manage threshold voltages in a memory |

| KR102251810B1 (ko) | 2014-09-30 | 2021-05-13 | 삼성전자주식회사 | 메모리 장치, 메모리 시스템 및 메모리 장치에 대한 제어 방법 |

| US9607676B2 (en) * | 2015-08-12 | 2017-03-28 | Avalanche Technology, Inc. | Method and apparatus for adjustment of current through a magnetoresistive tunnel junction (MTJ) based on temperature fluctuations |

| US9627041B1 (en) * | 2016-01-29 | 2017-04-18 | Qualcomm Incorporated | Memory with a voltage-adjustment circuit to adjust the operating voltage of memory cells for BTI effect screening |

| US9928898B2 (en) * | 2016-03-30 | 2018-03-27 | Qualcomm Incorporated | Wordline adjustment scheme |

| US9922700B2 (en) | 2016-05-24 | 2018-03-20 | Taiwan Semiconductor Manufacturing Co., Ltd. | Memory read stability enhancement with short segmented bit line architecture |

| US10403384B2 (en) | 2016-06-22 | 2019-09-03 | Darryl G. Walker | Testing a semiconductor device including a voltage detection circuit and temperature detection circuit that can be used to generate read assist and/or write assist in an SRAM circuit portion and method therefor |

| US20170372775A1 (en) | 2016-06-22 | 2017-12-28 | Darryl G. Walker | Semiconductor devices, circuits and methods for read and/or write assist of an sram circuit portion based on voltage detection and/or temperature detection circuits |

| US9633734B1 (en) * | 2016-07-14 | 2017-04-25 | Ememory Technology Inc. | Driving circuit for non-volatile memory |

| US10062431B2 (en) | 2016-11-07 | 2018-08-28 | Ambiq Micro, Inc. | SRAM with multiple power domains |

| US10714166B2 (en) * | 2018-08-13 | 2020-07-14 | Micron Technology, Inc. | Apparatus and methods for decoding memory access addresses for access operations |

| US10726926B2 (en) * | 2018-09-29 | 2020-07-28 | Sandisk Technologies Llp | Hot-cold VTH mismatch using VREAD modulation |

| US11435811B2 (en) * | 2019-12-09 | 2022-09-06 | Micron Technology, Inc. | Memory device sensors |

| US11972793B2 (en) | 2021-09-15 | 2024-04-30 | Mavagail Technology, LLC | Integrated circuit device including an SRAM portion having end power select circuits |

| WO2025013462A1 (ja) * | 2023-07-11 | 2025-01-16 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、センシングデータの読み出し方法及び電子機器 |

Family Cites Families (50)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4020358A (en) * | 1975-12-16 | 1977-04-26 | General Electric Company | Device system and method for controlling the supply of power to an electrical load |

| DE3622713A1 (de) * | 1986-07-05 | 1988-01-07 | Blaupunkt Werke Gmbh | Schaltungsanordnung mit einer brueckenendstufe |

| JPH0685159A (ja) * | 1992-09-02 | 1994-03-25 | Hitachi Ltd | 半導体記憶装置とそれを用いたメモリ装置 |

| JPH06314491A (ja) | 1993-04-30 | 1994-11-08 | Hitachi Ltd | 半導体記憶装置 |

| US5784328A (en) * | 1996-12-23 | 1998-07-21 | Lsi Logic Corporation | Memory system including an on-chip temperature sensor for regulating the refresh rate of a DRAM array |

| JP3963990B2 (ja) | 1997-01-07 | 2007-08-22 | 株式会社ルネサステクノロジ | 内部電源電圧発生回路 |

| JP2000155617A (ja) | 1998-11-19 | 2000-06-06 | Mitsubishi Electric Corp | 内部電圧発生回路 |

| US6446019B1 (en) * | 1998-12-29 | 2002-09-03 | Intel Corporation | Method and apparatus for calibrating analog sensor measurement |

| JP4027343B2 (ja) * | 1999-10-06 | 2007-12-26 | キヤノン株式会社 | ズームレンズ及びそれを用いた撮像装置 |

| US6128239A (en) * | 1999-10-29 | 2000-10-03 | Hewlett-Packard | MRAM device including analog sense amplifiers |

| US6476716B1 (en) * | 2000-11-15 | 2002-11-05 | Dallas Semiconductor Corporation | Temperature-controlled variable resistor |

| US6824307B2 (en) * | 2000-12-12 | 2004-11-30 | Harris Corporation | Temperature sensor and related methods |

| US6662136B2 (en) * | 2001-04-10 | 2003-12-09 | International Business Machines Corporation | Digital temperature sensor (DTS) system to monitor temperature in a memory subsystem |

| US6735546B2 (en) * | 2001-08-31 | 2004-05-11 | Matrix Semiconductor, Inc. | Memory device and method for temperature-based control over write and/or read operations |

| US6608790B2 (en) * | 2001-12-03 | 2003-08-19 | Hewlett-Packard Development Company, L.P. | Write current compensation for temperature variations in memory arrays |

| EP1420412B1 (en) * | 2002-11-18 | 2008-07-09 | STMicroelectronics S.r.l. | Circuit and method for temperature tracing of devices including an element of chalcogenic material, in particular phase change memory devices |

| US6954394B2 (en) * | 2002-11-27 | 2005-10-11 | Matrix Semiconductor, Inc. | Integrated circuit and method for selecting a set of memory-cell-layer-dependent or temperature-dependent operating conditions |

| JP2005108307A (ja) * | 2003-09-29 | 2005-04-21 | Nec Electronics Corp | 半導体記憶装置 |

| JP4497906B2 (ja) * | 2003-12-10 | 2010-07-07 | 株式会社東芝 | 半導体集積回路装置 |

| US7079438B2 (en) * | 2004-02-17 | 2006-07-18 | Hewlett-Packard Development Company, L.P. | Controlled temperature, thermal-assisted magnetic memory device |

| JP2005234935A (ja) * | 2004-02-20 | 2005-09-02 | Renesas Technology Corp | 情報記憶装置 |

| KR20050118952A (ko) * | 2004-06-15 | 2005-12-20 | 삼성전자주식회사 | 히스테리리스 특성을 갖는 온도 감지 회로 |

| JP4550053B2 (ja) * | 2004-06-22 | 2010-09-22 | 富士通セミコンダクター株式会社 | 半導体メモリ |

| US7142009B1 (en) * | 2004-09-15 | 2006-11-28 | Altera Corporation | Adaptive power supply voltage regulation for programmable logic |

| KR100882051B1 (ko) * | 2004-10-07 | 2009-02-09 | 야마하 가부시키가이샤 | 온도 센서 및 온도 센서의 보정 방법 |

| US7113424B2 (en) * | 2004-11-23 | 2006-09-26 | Infineon Technologies Ag | Energy adjusted write pulses in phase-change memories |

| US7184313B2 (en) * | 2005-06-17 | 2007-02-27 | Saifun Semiconductors Ltd. | Method circuit and system for compensating for temperature induced margin loss in non-volatile memory cells |

| JP5100035B2 (ja) | 2005-08-02 | 2012-12-19 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| CN101180683B (zh) * | 2005-09-21 | 2010-05-26 | 株式会社瑞萨科技 | 半导体器件 |

| JP2007193928A (ja) | 2005-12-19 | 2007-08-02 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| KR100655084B1 (ko) * | 2006-01-17 | 2006-12-08 | 삼성전자주식회사 | 센스앰프 인에이블 회로 및 이를 갖는 반도체 메모리 장치 |

| KR100842996B1 (ko) * | 2006-02-06 | 2008-07-01 | 주식회사 하이닉스반도체 | 온도에 따라 선택적으로 변경되는 워드 라인 전압을발생하는 워드 라인 전압 발생기와, 이를 포함하는 플래시메모리 장치 및 그 워드 라인 전압 발생 방법 |

| JP4821363B2 (ja) * | 2006-02-21 | 2011-11-24 | 日産自動車株式会社 | 組電池制御装置および組電池制御方法 |

| KR100744131B1 (ko) * | 2006-02-21 | 2007-08-01 | 삼성전자주식회사 | 냉온에서 동작 속도가 향상되는 메모리 집적회로 장치 |

| US7460394B2 (en) * | 2006-05-18 | 2008-12-02 | Infineon Technologies Ag | Phase change memory having temperature budget sensor |

| US7535786B1 (en) * | 2006-04-19 | 2009-05-19 | Darryl Walker | Semiconductor device having variable parameter selection based on temperature and test method |

| US7283414B1 (en) * | 2006-05-24 | 2007-10-16 | Sandisk 3D Llc | Method for improving the precision of a temperature-sensor circuit |

| KR100809334B1 (ko) * | 2006-09-05 | 2008-03-05 | 삼성전자주식회사 | 상변화 메모리 장치 |

| JP2008071440A (ja) * | 2006-09-14 | 2008-03-27 | Matsushita Electric Ind Co Ltd | 強誘電体メモリ装置及びその制御方法 |

| KR100851989B1 (ko) * | 2006-10-12 | 2008-08-13 | 주식회사 하이닉스반도체 | 반도체 메모리 장치의 온도정보 출력회로 및 방법 |

| ITRM20060652A1 (it) * | 2006-12-06 | 2008-06-07 | Micron Technology Inc | Compensazione di temperatura di segnali di memoria impiegando segnali digitali |

| ITRM20060675A1 (it) * | 2006-12-14 | 2008-06-15 | Micron Technology Inc | Sensore di temperatura su chip |

| US8018780B2 (en) * | 2007-01-18 | 2011-09-13 | Texas Instruments Incorporated | Temperature dependent back-bias for a memory array |

| KR100856060B1 (ko) * | 2007-04-06 | 2008-09-02 | 주식회사 하이닉스반도체 | 반도체메모리소자의 내부리프레쉬신호 생성장치 |

| US7796424B2 (en) * | 2007-06-21 | 2010-09-14 | Qimonda North America Corp. | Memory device having drift compensated read operation and associated method |

| WO2009008081A1 (ja) * | 2007-07-12 | 2009-01-15 | Fujitsu Microelectronics Limited | 半導体装置 |

| JP5259270B2 (ja) * | 2008-06-27 | 2013-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR101020282B1 (ko) * | 2008-07-09 | 2011-03-07 | 주식회사 하이닉스반도체 | 온도센서 |

| US8027187B2 (en) * | 2008-09-12 | 2011-09-27 | Micron Technology, Inc. | Memory sensing devices, methods, and systems |

| US7755965B2 (en) * | 2008-10-13 | 2010-07-13 | Seagate Technology Llc | Temperature dependent system for reading ST-RAM |

-

2008

- 2008-06-27 JP JP2008168093A patent/JP5259270B2/ja active Active

-

2009

- 2009-04-30 US US12/432,796 patent/US7961500B2/en active Active

-

2011

- 2011-05-06 US US13/102,295 patent/US8279696B2/en active Active

-

2012

- 2012-08-13 US US13/584,271 patent/US8611166B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20110211385A1 (en) | 2011-09-01 |

| JP2010009674A (ja) | 2010-01-14 |

| US8611166B2 (en) | 2013-12-17 |

| US8279696B2 (en) | 2012-10-02 |

| US7961500B2 (en) | 2011-06-14 |

| US20090323400A1 (en) | 2009-12-31 |

| US20120320664A1 (en) | 2012-12-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5259270B2 (ja) | 半導体装置 | |

| JP5197241B2 (ja) | 半導体装置 | |

| JP6161482B2 (ja) | 半導体記憶装置 | |

| US8331187B2 (en) | Memory with low power mode for write | |

| JP4768437B2 (ja) | 半導体記憶装置 | |

| US7948809B2 (en) | Regulator and semiconductor device | |

| US20050141289A1 (en) | Semiconductor memory device having the operating voltage of the memory cell controlled | |

| JP2007122814A (ja) | 半導体集積回路及びリーク電流低減方法 | |

| JP4416474B2 (ja) | 半導体記憶装置 | |

| JP2007213637A (ja) | 内部電源生成回路及びこれらを備えた半導体装置 | |

| JP2010015614A (ja) | 半導体装置 | |

| JP2011159365A (ja) | 半導体装置及び半導体装置を含む情報処理システム | |

| US6504784B1 (en) | Semiconductor memory device with reduced standby current | |

| US9001610B2 (en) | Semiconductor device generating internal voltage | |

| JP2000310672A (ja) | 半導体装置 | |

| US11581032B2 (en) | Apparatuses and methods of power supply control for temperature compensated sense amplifiers | |

| JP6469764B2 (ja) | 半導体記憶装置及びそのテスト方法 | |

| JP5974494B2 (ja) | 半導体記憶装置の内部電圧生成回路 | |

| JP5533264B2 (ja) | 半導体メモリ | |

| JP2013114546A (ja) | 半導体装置 | |

| KR101035174B1 (ko) | 반도체 메모리 소자 | |

| JPH03198296A (ja) | 半導体メモリ | |

| KR20020089606A (ko) | 반도체 메모리 장치 및 그것의 독출 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110315 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121010 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121023 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5259270 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |