-

QUERVERWEIS AUF VERWANDTE ANMELDUNGEN

-

Die Anmeldung beansprucht die Priorität der koreanischen Patentanmeldung Nr. 10-2011-0068825, eingereicht am 12. Juli 2011, die in ihrer Gesamtheit durch Bezugnahme hierin aufgenommen ist.

-

HINTERGRUND

-

1. Gebiet

-

Ausführungsbeispiele betreffen eine Halbleiter-Speichervorrichtung, und insbesondere betreffen sie eine nicht-flüchtige Speichervorrichtung und ein Löschverfahren dafür, ein Betriebsverfahren dafür, ein Speichersystem, das die nicht-flüchtige Speichervorrichtung enthält, und ein Betriebsverfahren für das Speichersystem.

-

2. Beschreibung der verwandten Technik

-

Eine Halbleitervorrichtung ist eine Speichervorrichtung, die unter Verwendung von Halbleitern, wie Silicium (Si), Germanium (Ge), Galliumarsenid (GaAs), Indiumphosphid (InP) und dergleichen, hergestellt wird. Halbleiter-Speichervorrichtungen werden nach flüchtigen Speichervorrichtungen und nicht-flüchtigen Speichervorrichtungen unterschieden.

-

Die flüchtigen Speichervorrichtungen können gespeicherte Inhalte verlieren, wenn ihre Leistungszufuhr unterbrochen wird. Zu den flüchtigen Speichervorrichtungen gehört beispielsweise ein statisches RAM (SRAM), ein dynamisches RAM (DRAM), ein synchrones DRAM (SDRAM) und dergleichen. Die nicht-flüchtigen Speichervorrichtungen können gespeicherte Inhalte auch bei einer Unterbrechung der Leistungsversorgung behalten. Zu den nicht-flüchtigen Speichervorrichtungen gehört beispielsweise ein Nur-Lese-Speicher (ROM), ein programmierbares ROM (PROM), ein elektrisch programmierbares ROM (EPROM), ein elektrisch löschbares und programmierbares ROM (EEPROM), eine Flash-Speichervorrichtung, ein Phasenänderungs-RAM (PRAM), ein magnetisches RAM (MRAM), einen resistives RAM (RRAM), ein ferroelektrisches RAM (FRAM) und dergleichen. Die Flash-Speichervorrichtung wird grob nach einem NOR-Typ und einen NAND-Typ unterschieden.

-

Vor Kurzem wurde eine Halbleiter-Speichervorrichtung mit einer dreidimensionalen Array-Struktur entwickelt, um die Integrität der Halbleiter-Speichervorrichtung zu verbessern.

-

KURZFASSUNG

-

Die vorliegende allgemeine erfinderische Idee schafft eine nicht-flüchtige Speichervorrichtung, ein Löschverfahren dafür, ein Speichersystem, das die nicht-flüchtige Speichervorrichtung aufweist, ein elektronisches Gerät, das die nicht-flüchtige Speichervorrichtung aufweist, und ein Betriebsverfahren für das Speichersystem und die elektronische Vorrichtung, die die nicht-flüchtige Speichervorrichtung aufweist.

-

Weitere Aspekte und Vorteile der vorliegenden allgemeinen erfinderischen Idee werden zum Teil in der folgenden Beschreibung dargelegt und gehen zum Teil aus der Beschreibung hervor oder können durch Ausführen der allgemeinen erfinderischen Idee erkannt werden.

-

Die genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können durch Schaffung eines Löschverfahrens für eine nicht-flüchtige Speichervorrichtung verwirklicht werden, wobei das Löschverfahren die Zufuhr einer Löschspannung zu einer Mehrzahl von Speicherzellen, die Durchführung einer Leseoperation mit einer Lesespannung an Wortleitungen der Mehrzahl von Speicherzellen und die Durchführung einer Löschungsverifizierungsoperation mit einer Löschungsverifizierungsspannung an mindestens einer von den Wortleitungen der Mehrzahl von Speicherzellen beinhaltet, wobei die Löschungsverifizierungsspannung niedriger ist als die Lesespannung.

-

Die Lesespannung kann einen oder mehrere Spannungspegel beinhalten, die an die jeweiligen Wortleitungen angelegt werden.

-

Die Lesespannung kann einen einzigen Spannungspegel beinhalten, der an die Wortleitungen angelegt wird.

-

Die Löschungsverifizierungsspannung kann in Bezug auf eine entsprechende von den Wortleitungen der Mehrzahl von Speicherzellen variabel sein, und die variable Löschungsverifizierungsspannung kann niedriger sein als die Lesespannung.

-

Die Lesespannung kann höher sein als eine Spannung einer Schwellenspannung eines Programmierungszustands der Mehrzahl von Speicherzellen.

-

Die Mehrzahl von Speicherzellen kann mindestens eine Leerzelle und eine oder mehrere reguläre Speicherzellen beinhalten. Die mindestens eine Leerzelle kann bei der Leseoperation und der Löschungsverifizierungsoperation mit einer Spannung beliefert werden, die sich von einer Betriebsspannung unterscheidet, die zu den regulären Speicherzellen geliefert wird.

-

Die genannten und/oder andere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch durch Schaffung eines Löschverfahrens für eine nicht-flüchtige Speichervorrichtung verwirklicht werden, wobei das Löschverfahren Folgendes beinhaltet: die Zufuhr einer Löschspannung zu einer Mehrzahl von Folgen bzw. Strings, die jeweils eine Mehrzahl von Speicherzellen beinhalten, die Durchführung einer Leseoperation mit einer Lesespannung an Wortleitungen der Mehrzahl von Speicherzellen, die Bestimmung gemäß der durchgeführten Leseoperation, dass eine oder mehrere Folgen Off-Strings sind, die Verarbeitung eines Löschungsverifizierungsschritts an dem Off-String und die Durchführung einer Löschungsverifizierungsoperation mit einer Löschungsverifizierungsspannung an den Wortleitungen der Mehrzahl von Folgen.

-

Das Löschverfahren kann ferner die Zufuhr einer modifizierten Löschspannung zu der Mehrzahl von Folgen gemäß der durchgeführten Löschungsverifizierungsoperation beinhalten.

-

Gemäß der Leseoperation kann bestimmt werden, ob die Mehrzahl von Speicherzellen ein Off-String oder ein Non-Off-String ist, und die Löschungsverifizierungsoperation kann beinhalten, dass die Durchführung einer Bitleitungs-Vorladungsoperation an dem Off-String verhindert wird.

-

Das Löschverfahren kann ferner die Zufuhr verschiedener Spannungen zu Bitleitungen des Off-Strings und des Non-Off-Strings als Vorladespannung und die Zufuhr der Löschungsverifizierungsspannung an die jeweiligen Wortleitungen der Mehrzahl von Speicherzellen in der Löschungsverifizierungsoperation beinhalten.

-

Die Mehrzahl von Speicherzellen kann mindestens eine Leerzelle und eine oder mehrere reguläre Speicherzellen beinhalten, und die mindestens eine Leerzelle kann bei der Leseoperation und der Löschungsverifizierungsoperation mit einer Spannung beliefert werden, die sich von einer Betriebsspannung unterscheidet, die zu den regulären Speicherzellen geliefert wird.

-

Die genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch durch Schaffung einer nichtflüchtigen Speichervorrichtung verwirklicht werden, die aufweist: ein Speicherzellen-Array mit einem Substrat und einer Mehrzahl von Blöcken, die jeweils eine Mehrzahl von Folgen mit jeweils einer Mehrzahl von Speicherzellen beinhalten, wobei die Mehrzahl von Folgen in senkrechter Richtung zum Substrat ausgebildet ist; eine Steuereinheit, um eine Leseoperation mit einer Spannung an Wortleitungen der Mehrzahl von Folgen durchzuführen, und eine Seitenpuffer- bzw. Seitenspeichereinheit, um Informationen über eine oder mehrere Off-Strings von der Mehrzahl von Folgen, die durch die Leseoperation bestimmt werden, zu speichern. Die Steuereinheit kann eine Löschungsverifizierungsoperation mit einer Löschungsverifizierungsspannung an mindestens einer der Wortleitungen von der Mehrzahl von Speicherzellen durchführen, und die Löschungsverifizierungsspannung kann niedriger sein als die Lesespannung

-

Jede von der Mehrzahl von Folgen weist die Mehrzahl von Speicherzellen mit jeweils unterschiedlichen Dimensionen auf, und benachbarte Folgen können durch eine Lücke voneinander beabstandet sein.

-

Die Steuereinheit kann unter den Folgen gemäß der Leseoperation einen ersten Off-String bestimmen und bestimmt einen zweiten Off-String gemäß der Löschungsverifizierungsoperation, und die Steuereinheit führt eine Löschoperation mit einer modifizierten Löschspannung an den ersten und zweiten Off-Strings durch.

-

Die Steuereinheit kann die Löschungsverifizierungsoperation an einem Non-Off-String durchführen, nachdem sie eine Löschoperation mit einer ersten Löschspannung an den Folgen durchgeführt hat, die den Off-String und den Non-Off-String beinhalten.

-

Die Steuereinheit kann gemäß der Löschungsverifizierungsoperation eine weitere Löschoperation mit einer modifizierten Löschspannung an dem Off-String durchführen.

-

Die Steuereinheit kann veranlassen, dass gemäß der durchgeführten Löschungsverifizierung eine weitere Löschoperation an der ausgewählten Folge durchgeführt wird, wenn bestimmt wird, dass die ausgewählte Folge eine abgeschaltete Folge ist, die eine Folge darstellt, bei der das Löschen fehlgeschlagen ist.

-

Die oben genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch dadurch verwirklicht werden, dass ein Betriebsverfahren für ein Speichersystem geschaffen wird, wobei das Verfahren beinhaltet: Erzeugen eines Controller-Befehls zur Durchführung einer Löschoperation an einer nicht-flüchtigen Speichervorrichtung, die ein Speicherzellen-Array aufweist, das ein Substrat und eine Mehrzahl von Folgen aufweist, die jeweils eine Mehrzahl von Speicherzellen beinhalten, wobei die Mehrzahl von Folgen in senkrechter Richtung zum Substrat ausgebildet ist, und Durchführen der Löschoperation in der nicht-flüchtigen Speichervorrichtung gemäß dem erzeugten Befehl, wobei die Löschoperation beinhaltet: die Durchführung einer Löschoperation an der Mehrzahl von Folgen, die Durchführung einer Leseoperation mit einer Lesespannung an Wortleitungen der Mehrzahl von Speicherzellen, die Bestimmung gemäß der durchgeführten Leseoperation, dass eine oder mehrere Folgen Off-Strings sind, die Verarbeitung eines Löschungsverifizierungs-Arbeitsgangs an dem Off-String und die Durchführung einer Löschungsverifizierungsoperation mit einer Löschungsverifizierungsspannung an den Wortleitungen der Mehrzahl von Folgen, wobei die Löschungsverifizierungsspannung niedriger ist als die Lesespannung.

-

Die Verarbeitung der Löschungsverifizierungsoperation kann beinhalten, dass die Durchführung der Löschungsverifizierungsoperation an dem Off-String der ersten Bestimmung verhindert wird.

-

Das Betriebsverfahren kann ferner die Durchführung einer zweiten Löschoperation mit einer zweiten Löschspannung an den Off-Strings der ersten Bestimmung und der zweiten Bestimmung beinhalten.

-

Die Leseoperation kann zwischen der Löschoperation und der Löschungsverifizierungsoperation ausgelassen werden.

-

Die Löschungsverifizierungsoperation an dem bestimmten Off-String kann weggelassen werden.

-

Das Betriebsverfahren kann ferner beinhalten, dass ein erstes Antwortsignal auf die Löschoperation von der nicht-flüchtigen Speichervorrichtung zum Controller gesendet wird, dass vom Controller ein zweiter Befehl erzeugt wird, um die nicht-flüchtige Speichervorrichtung so zu steuern, dass diese eine zweite Löschoperation durchführt, und dass von der nicht-flüchtigen Speichervorrichtung ein zweites Antwortsignal auf die zweite Löschoperation gesendet wird, damit der Controller eine Fehlerverarbeitung durchführt, um gemäß dem ersten Antwortsignal und dem zweiten Antwortsignal einen schädlichen Block zu bestimmen.

-

Das Betriebsverfahren kann ferner beinhalten, dass nach Abschluss der Löschoperation Off-String-Informationen an den Controller gesendet werden, damit der Controller die gesendeten Informationen verwendet, um vorhandene Informationen zu aktualisieren.

-

Das Betriebsverfahren kann ferner beinhalten, dass Off-String-Informationen an den Controller gesendet werden; dass an die nicht-flüchtige Speichervorrichtung ein Lesebefehl zur Durchführung einer zweiten Leseoperation gesendet wird, um Daten aus den Strings bzw. Folgen zu lesen, und dass ein Fehler gemäß den ausgelesenen Daten und den Off-String-Informationen korrigiert wird.

-

Das Betriebsverfahren kann ferner beinhalten, dass ein Befehl an die nicht-flüchtige Speichervorrichtung zur Durchführung einer Vorab-Leseoperation erzeugt wird, dass von der nicht-flüchtigen Speichervorrichtung gemäß der Vorab-Leseoperation Informationen über einen zweiten Off-String empfangen werden und dass die nicht-flüchtige Speichervorrichtung so gesteuert wird, dass sie die Informationen über den zweiten Off-String in einem Pufferspeicherbereich der nicht-flüchtigen Speichervorrichtung speichert.

-

Das Betriebsverfahren kann ferner beinhalten, dass ein zweiter Befehl an die nicht-flüchtige Speichervorrichtung zur Ausgabe der gespeicherten Off-String-Informationen an den Controller erzeugt wird, dass gemäß der Löschoperation zweite Off-String-Informationen empfangen werden und dass Informationen gemäß den zweiten Off-String-Informationen und den Off-String-Informationen aktualisiert werden.

-

Das Betriebsverfahren kann ferner beinhalten, dass eine Folgenansteuerungsleitung ausgewählt wird, die mit einer vorgegebenen Anzahl von Strings bzw. Folgen verbunden ist, um die Leseoperation an der vorgegebenen Anzahl der Folgen der ausgewählten Folgenansteuerungsleitung durchzuführen, bis bestimmt wird, dass die ausgewählte Folgenansteuerungsleitung eine letzte Folgenansteuerungsleitung der Folgen ist.

-

Die Mehrzahl von Folgen kann in eine Mehrzahl von Gruppen unterteilt sein, die mit einer Mehrzahl von Folgenansteuerungsleitungen verbunden sind, die Löschoperation kann das Ansteuern einer Ersten von der Mehrzahl von Folgenansteuerungsleitungen beinhalten, und die Leseoperation und die Löschungsverifizierungsoperation werden in Bezug auf die Folgen durchgeführt, die mit der ausgewählten Folgenansteuerungsleitungen verbunden sind.

-

Das Betriebsverfahren kann ferner das Iterieren bzw. Wiederholen der Durchführung der Leseoperation und der Erfassung der Off-Strings beinhalten, bis eine letzte Folgenansteuerungsleitungen unter einer Mehrzahl von Folgenansteuerungsleitungen ausgewählt worden ist, wobei die in Mehrzahl vorhandenen Folgenansteuerungsleitungen jeweils mit den entsprechenden Folgen verbunden sind und nacheinander ausgewählt werden.

-

Das Wiederholen kann beinhalten, dass eine zweite Folgenansteuerungsleitung aus einer Mehrzahl von Folgenansteuerungsleitungen ausgewählt wird; dass die Leseoperation durch Anlegen einer hohen Spannung an Wortleitungen der Folgen, die mit der zweiten Ansteuerungsleitung verbunden sind, durchgeführt wird, und dass gemäß der durchgeführten Leseoperation bestimmt wird, dass eine oder mehrere zweite Folgen Off-Strings sind.

-

Die oben genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch durch die Schaffung eines Speichersystems verwirklicht werden, das aufweist: eine nicht-flüchtige Speichervorrichtung, die ein Speicherzellen-Array mit einem Substrat und einer Mehrzahl von Folgen aufweist, die jeweils eine Mehrzahl von Speicherzellen beinhalten, wobei die Mehrzahl von Folgen in senkrechter Richtung zum Substrat ausgebildet ist, und einen Controller, der einen Befehl zur Durchführung einer Löschoperation an der nicht-flüchtigen Speichervorrichtung erzeugt, damit die nicht-flüchtige Speichervorrichtung die Mehrzahl von Folgen löscht bzw. leert, eine Leseoperation mit einer Lesespannung an Wortleitungen der Mehrzahl von Folgen durchführt, gemäß der durchgeführten Leseoperation bestimmt, dass es sich bei einer oder mehreren Folgen um Off-Strings handelt, einen Löschungsverifizierungs-Arbeitsschritt verarbeitet und eine Löschungsverifizierungsoperation mit einer Löschungsverifizierungsspannung an Wortleitungen von der Mehrzahl von Folgen durchführt, wobei die Löschungsverifizierungsspannung niedriger ist als die Lesespannung.

-

Die Folgen können durch eine Lücke voneinander beabstandet sein, in der eine Kanalschichteinheit ausgebildet ist, um die Speicherzellen der Folge miteinander zu verbinden, und die Kanalschichteinheit einen Defekt aufweist, der den Off-String bewirkt.

-

Die nicht-flüchtige Speichervorrichtung kann eine Kanalschichteinheit aufweisen, die mit den angrenzenden bzw. benachbarten Folgen verbunden ist, und der Off-String ist mit der Kanalschichteinheit ausgebildet, die keinen elektrischen Kontakt mit dem Substrat aufweist.

-

Die nicht-flüchtige Speichervorrichtung kann einen Drain und eine Kanalschichteinheit aufweisen, die mit der Folge verbunden ist, und der Off-String ist mit der Kanalschichteinheit ausgebildet, die keinen elektrischen Kontakt mit dem Substrat aufweist.

-

Die nicht-flüchtige Speichervorrichtung kann verhindern, dass die Löschungsverifizierungsoperation an dem Off-String der ersten Bestimmung durchführt.

-

Die genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch durch Schaffung eines Speichersystems erreicht werden, das eine nicht-flüchtige Speichervorrichtung und einen Controller, der die nicht-flüchtige Speichervorrichtung steuert, aufweist. Die nichtflüchtige Speichervorrichtung kann Folgendes aufweisen: ein Speicherzellen-Array mit einer Mehrzahl von Folgen, wobei jede Folge eine Mehrzahl von Speicherzellen aufweist, eine Schreib-/Leseeinheit, die so gestaltet ist, dass sie als Antwort auf einen Befehl, der vom Controller gesendet wird, eine Leseoperation durchführt und ein Leseergebnis ausgibt, wobei die Leseoperation durch Anlegen einer hohen Spannung an Wortleitungen, die mit der Mehrzahl von Folgen verbunden sind, erfolgt, eine Zähleinheit, die so gestaltet ist, dass sie das ausgegebene Leseergebnis empfangt und die Anzahl der Off-Strings zählt, die während der Leseoperation als abgeschaltet gelesen werden, und eine Daten-Eingabe-/Ausgabeschaltung, die so gestaltet ist, dass sie das Leseergebnis oder das Zählergebnis als Informationen ausgibt, die mit den Off-Strings assoziiert sind. Der Controller kann so ausgelegt sein, dass er die nicht-flüchtige Speichervorrichtung auf Basis von Informationen steuert, die mit den Off-Strings assoziiert sind.

-

Die nicht-flüchtige Speichervorrichtung kann ein Substrat aufweisen, und die Mehrzahl von Folgen kann in senkrechter Richtung zum Substrat angeordnet und in eine Mehrzahl von Folgengruppen unterteilt sein, wobei die Gruppen mit einer Mehrzahl von Folgenansteuerungsleitungen verbunden sind, wobei der Controller die nichtflüchtige Speichervorrichtung so steuert, dass diese eine Löschoperation an den Folgen der Gruppen der Mehrzahl von Folgenansteuerungsleitungen durchführt. Der Controller kann die nicht-flüchtige Speichervorrichtung so steuern, dass diese eine oder mehrere Off-Strings als erfolgreich gelöscht verarbeitet und eine Löschungsverifizierungsoperation an anderen Folgen in der Einheit jeder Gruppe durchführt.

-

Aneinander angrenzende bzw. benachbarte Folgen können durch eine Säule voneinander beabstandet sein, die eine Kanalschicht aufweist, die elektrisch mit den Speicherzellen jeder Folge verbunden ist.

-

Die Säule kann eine Breite aufweisen, die gemäß dem Abstand zum Substrat breiter ist.

-

Die Säule kann eine Breite aufweisen, die gemäß dem Abstand zum Substrat breiter ist.

-

Die Speicherzellen jeder Folge können eine Länge aufweisen, die gemäß einem Abstand zum Substrat kürzer ist.

-

Die oben genannten und/oder weitere Merkmale und Anwendungsmöglichkeiten der vorliegenden allgemeinen erfinderischen Idee können auch dadurch verwirklicht werden, dass ein Betriebsverfahren für ein Speichersystem geschaffen wird, das eine nicht-flüchtige Speichervorrichtung mit einer Mehrzahl von Folgen und einen Controller aufweist, der so gestaltet ist, dass er die nicht-flüchtige Speichervorrichtung steuert, wobei jede Folge eine Mehrzahl von Speicherzellen aufweist, wobei das Betriebsverfahren beinhaltet, dass ein Befehl vom Controller zur nicht-flüchtigen Speichervorrichtung gesendet wird, dass die nicht-flüchtige Speichervorrichtung als Antwort auf den Befehl eine Leseoperation durchführt, wobei die Leseoperation durch Anlegen einer hohen Spannung an sämtliche Wortleitungen, die mit der Mehrzahl von Folgen verbunden sind, durchgeführt wird, dass von der nicht-flüchtigen Speichervorrichtung Informationen, die mit den Off-Strings assoziiert sind, die während der Leseoperation als abgeschaltet gelesen werden, an den Controller gesendet werden, und dass die gesendeten Informationen im Controller gespeichert werden.

-

Das Betriebsverfahren kann ferner beinhalten, dass die gespeicherten Informationen, die mit den Off-Strings assoziiert sind, und ein Löschbefehl vom Controller an die nicht-flüchtige Speichervorrichtung gesendet werden und die nicht-flüchtige Speichervorrichtung als Antwort auf die gespeicherten Informationen, die mit den Off-Strings assoziiert sind, und den Lesebefehl eine Löschoperation durchführt.

-

Wenn ein Ergebnis der Löschoperation anzeigt, dass ein Löschen fehlgeschlagen ist, können das Senden eines Befehls, die Durchführung einer Leseoperation, das Senden von Informationen und das Speichern der gesendeten Informationen erneut ausgeführt werden.

-

Das Betriebsverfahren kann ferner beinhalten, dass ein Lesebefehl vom Controller an die nicht-flüchtige Speichervorrichtung gesendet wird, dass von der nicht-flüchtigen Speichervorrichtung ein Leseergebnis gemäß dem Lesebefehl an den Controller gesendet wird und dass ein Fehler des gesendeten Leseergebnisses unter Verwendung der gespeicherten Informationen, die mit den Off-Strings assoziiert sind, korrigiert wird, wobei die Korrektur durch den Controller durchgeführt wird.

-

Das Betriebsverfahren kann ferner beinhalten, dass ein Code-Wort unter Verwendung von Schreibdaten und der gespeicherten Informationen, die mit den Off-Strings assoziiert sind, erzeugt wird, wobei die Erzeugung durch den Controller vorgenommen wird, dass der Controller das erzeugte Code-Wort und einen Schreibbefehl an den nichtflüchtigen Speicher sendet, und dass das gesendete Code-Wort als Antwort auf den Schreibbefehl in die nicht-flüchtige Speichervorrichtung geschrieben wird.

-

Das Betriebsverfahren kann ferner beinhalten, dass der Controller die gespeicherten Informationen, die mit den Off-Strings assoziiert sind, und einen zweiten Befehl an die nicht-flüchtige Speichervorrichtung sendet, und dass die gesendeten Informationen, die mit den Off-Strings assoziiert sind, als Antwort auf den zweiten Befehl in die nichtflüchtige Speichervorrichtung geschrieben werden.

-

KURZE BESCHREIBUNG DER ZEICHNUNGEN

-

Diese und/oder weitere Aspekte und Vorteile der vorliegenden allgemeinen erfinderischen Idee werden aus der folgenden Beschreibung der Ausführungsformen in Zusammenschau mit den begleitenden Zeichnungen deutlicher und verständlicher, in denen:

-

1 ein Blockschema ist, das eine nicht-flüchtige Speichervorrichtung gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

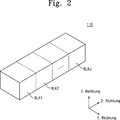

2 ein Diagramm ist, das ein Speicherzellen-Array der nicht-flüchtigen Speichervorrichtung von 1 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

3 ein Flächendiagramm eines Speicherblocks der nicht-flüchtigen Speichervorrichtung von 1 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

4 eine perspektivische Darstellung entlang einer Linie IV-IV' von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee ist;

-

5 eine Querschnittsdarstellung entlang einer Linie IV-IV' von 4 gemäß einem Ausführungsbeispiel der erfinderischen Idee ist;

-

6 ein Diagramm ist, das einen von Zellentransistoren von 5 darstellt;

-

7 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

8 ein Flussdiagramm ist, das ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

9 ein Diagramm ist, das eine Vorspannungsbedingung darstellt, die in dem Löschverfahren von 8 verwendet werden kann;

-

10 ein Zeitdiagramm ist, das Spannungsänderungen eines Substrats, von Kanalschichten und von Wortleitungen darstellt;

-

11 ein Zeitdiagramm ist, das eine Spannungsänderung eines Speicherzellen-Array während Schritten S113 und S114 von 8 darstellt;

-

12 ein Zeitdiagramm ist, das eine Spannungsänderung eines Speicherzellen-Array während Schritten S115 und S116 von 8 darstellt;

-

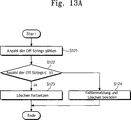

13A ein Flussdiagramm ist, das einen Off-String-Verarbeitungsschritt darstellt, der in dem Löschverfahren von 8 durchgeführt wird;

-

13B ein Flussdiagramm ist, das ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

14 ein Blockschema ist, das eine Seitenspeichereinheit von 1 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

15 ein Blockschema ist, das eine nicht-flüchtige Speichervorrichtung gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

16 ein Flussdiagramm ist, das ein Vorab-Leseverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

17 ein Flussdiagramm ist, das ein Vorab-Leseverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

18 ein Blockschema ist, das eine nicht-flüchtige Speichervorrichtung gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

19 ein Blockschema ist, das eine nicht-flüchtige Speichervorrichtung gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

20 ein Ablaufschema ist, das ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

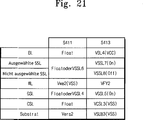

21 ein Diagramm ist, das eine Spannungsbedingung darstellt, die in dem Löschverfahren von 20 verwendet werden kann;

-

22 ein Blockschema ist, das eine nicht-flüchtige Speichervorrichtung gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

23 ein Flussdiagramm ist, das ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

24 ein Flussdiagramm ist, das ein Verfahren zur Erzeugung eines Summensignals und eines Übertragungssignals darstellt;

-

25 ein Blockschema eines Ripple-Carry-Kalkulators gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

26 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

27 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

28 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

29 ein Diagramm ist, das Spannungen darstellt, die zu einem Speicherblock geliefert werden, wenn Speicherzellen gemäß einem Verfahren gelöscht werden, das mit Bezug auf 8 bis 13 beschrieben ist;

-

30 ein Diagramm ist, das Spannungen darstellt, die zu einem Speicherblock geliefert werden, wenn Speicherzellen gemäß einem Verfahren gelöscht werden, das mit Bezug auf 20 und 21 beschrieben ist;

-

31 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

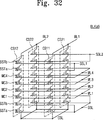

32 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

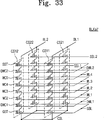

33 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

34 eine perspektivische Ansicht entlang einer Linie IV-IV' von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee ist;

-

35 eine Querschnittsansicht entlang einer Linie IV-IV' von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee ist;

-

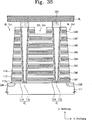

36 eine Draufsicht ist, die einen Speicherblock von 2 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

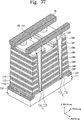

37 eine perspektivische Darstellung gemäß einer Linie XXXVII-XXXVII' von 36 ist;

-

38 eine Querschnittsdarstellung entlang der Linie XXXVII-XXXVII' von 36 ist;

-

39 eine Draufsicht ist, die einen der Speicherblöcke von 2 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

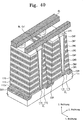

40 eine perspektivische Darstellung entlang einer Linie XXXX-XXXX' von 39 ist;

-

41 eine Querschnittsdarstellung gemäß einer Linie XXXX-XXXX' von 39 ist;

-

42 eine Draufsicht ist, die einen der Speicherblöcke von 2 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

43 eine perspektivische Ansicht entlang einer Linie XXXXIII-XXXXIII' von 42 ist;

-

44 eine Draufsicht ist, die einen der Speicherblöcke von 42 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

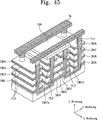

45 eine perspektivische Ansicht entlang einer Linie XXXXV-XXXXV' von 44 ist;

-

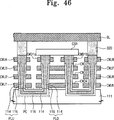

46 eine Querschnittsansicht entlang einer Linie XXXXV-XXXXV' von 44 ist;

-

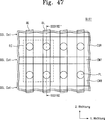

47 eine Draufsicht ist, die einen Speicherblock von 2 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

48 eine perspektivische Darstellung entlang einer Linie XXXXVIII-XXXXVIII' von 47 ist;

-

49 eine Querschnittsansicht entlang einer Linie XXXXVIII-XXXXVIII' von 47 ist;

-

50 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 47 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

51 eine perspektivische Ansicht entlang einer Linie XXXXVIII-XXXXVIII' von 47 ist;

-

52 eine Querschnittsdarstellung entlang einer Linie XXXXVIII-XXXXVIII' von 47 ist;

-

53 ein Schaltplan ist, der eine Ersatzschaltung eines Abschnitts EC von 47 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

54 ein Blockschema ist, das ein Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

55 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

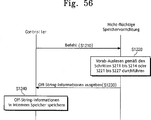

56 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

57 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

58 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

59 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

60 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

61 ein Flussdiagramm ist, das ein Betriebsverfahren eines Speichersystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

62 ein Blockschema ist, das ein Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

63 ein Diagramm ist, das eine Speicherkarte als elektronisches Gerät mit einer nicht-flüchtigen Speichervorrichtung und als Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

64 ein Diagramm ist, das ein Festzustands-Laufwerk als elektronisches Gerät mit einer nicht-flüchtigen Speichervorrichtung und als Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

65 ist ein Blockschema, das ein Rechensystem als elektronisches Gerät mit einer nicht-flüchtigen Speichervorrichtung und als Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

66 ist ein Blockschema, das ein Testsystem als elektronisches Gerät mit einer nicht-flüchtigen Speichervorrichtung und als Speichersystem gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

67 ist ein Flussdiagramm, das ein Testverfahren eines Testsystems gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt;

-

AUSFÜHRLICHE BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSFORMEN

-

Nun wird ausführlich auf die Ausführungsformen der vorliegenden allgemeinen erfinderischen Idee Bezug genommen, für die Beispiele in den beigefügten Zeichnungen dargestellt sind, wobei gleiche Bezugszahlen durchgehend verwendet werden, um gleiche Elemente zu bezeichnen. Die Ausführungsformen werden nachstehend unter Bezugnahme auf die Figuren beschrieben, um die vorliegende allgemeine erfinderische Idee zu erklären. Diese erfinderische Idee kann jedoch in vielen verschiedenen Formen verwirklicht werden und sollte nicht als beschränkt auf die hierin aufgeführten Ausführungsformen aufgefasst werden. Diese Ausführungsformen sollen die Offenbarung vielmehr gründlich und vollständig darstellen und ferner einem Fachmann den Bereich der erfinderischen Idee vollständig darstellen. In den Zeichnungen können die Größen und relativen Größen der Schichten und Regionen um der Deutlichkeit willen übertrieben dargestellt sein. Gleiche Zahlen sind durchgehend auf gleiche Elemente bezogen.

-

Man beachte, dass hierin zwar die Begriffe erster/erste/erstes, zweiter/zweite/zweites, dritter/dritte/drittes usw. verwendet werden können, um verschiedene Elemente, Komponenten, Regionen, Schichten und/oder Abschnitte zu bezeichnen, diese Elemente, Komponenten, Regionen, Schichten und/oder Abschnitte jedoch nicht als beschränkt auf diese Begriffe aufgefasst werden sollten. Diese Begriffe werden nur verwendet, um ein Element, eine Komponente, eine Region, eine Schicht oder einen Abschnitt von einer anderen Region oder Schicht oder einem anderen Abschnitt zu unterscheiden. Somit könnte ein erstes Element, eine erste Komponente, Region oder Schicht oder ein erster Abschnitt auch als zweites Element, zweite Komponente, Region oder Schicht oder zweiter Abschnitt bezeichnet werden, ohne von den Lehren der erfinderischen Idee abzuweichen.

-

Begriffe, die eine räumliche Beziehung bezeichnen, wie „unterer/-e/-es”, „unten”, „darunter” „unterhalb”, „über”, „oberer/-e/-es” und dergleichen, können hierin verwendet werden, um die Beschreibung zu erleichtern, um ein Element oder eine räumliche Beziehung eines Merkmals zu einem oder mehreren anderen Element(en) oder Merkmal(en) zu beschreiben, die in den Figuren dargestellt sind. Man beachte, dass die Ausdrücke, die eine räumliche Beziehung bezeichnen, zusätzlich zu der Ausrichtung, die in den Figuren dargestellt ist, auch andere Ausrichtungen der Vorrichtung im Gebrauch oder im Betrieb umfassen sollen. Wenn die Vorrichtung in den Figuren zum Beispiel umgedreht wird, wären dann Elemente, die als „unter” oder „darunter” oder „unterer/-e/-es” im Vergleich zu anderen Elementen oder Merkmalen beschrieben werden, bei dieser Ausrichtung „über” den anderen Elementen oder Merkmalen angeordnet. Somit können z. B. die Ausdrücke „unter” und „unterer/-e/-es” sowohl eine Ausrichtung nach oben als auch eine Ausrichtung nach unten umfassen. Die Vorrichtung kann auf andere Weise ausgerichtet (um 90 Grad gedreht oder anders ausgerichtet) werden, und die hierin verwendeten Bezeichnungen für eine räumliche Beziehung können entsprechend interpretiert werden. Außerdem ist zu beachten, dass eine Schicht, von der gesagt wird, dass sie „zwischen” zwei Schichten liegt, die einzige Schicht sein kann, die zwischen den beiden Schichten liegt, oder dass außerdem eine oder mehrere Zwischenschichten vorhanden sein können.

-

Die hierin verwendete Terminologie dient lediglich der Beschreibung bestimmter Ausführungsformen und soll die erfinderische Idee nicht beschränken. Wie hierin verwendet, sollen die Einzahlformen „ein/eine/ein” und „der/die/das” auch die Pluralformen umfassen, solange der Kontext nicht klar etwas anderes nahelegt. Ferner ist zu beachten, dass die Begriffe „aufweist” und/oder „aufweisen” bzw. „beinhalten”, wenn sie in dieser Schrift verwendet werden, das Vorhandensein der angegebenen Merkmale, ganzen Zahlen, Schritte, Operationen, Elemente und/oder Komponenten bezeichnen, aber das Vorhandensein oder die Hinzufügung von einem/einer oder mehreren anderen Merkmalen, ganzen Zahlen, Schritten, Operationen, Elementen, Komponenten und/oder Gruppen davon nicht ausschließen. Wie hierin verwendet, bezeichnet der Begriff „und/oder” beliebige und alle Kombinationen aus einem oder mehreren der im Zusammenhang damit aufgelisteten Gegenstände.

-

Man beachte, dass eine Bezeichnung eines Elements oder einer Schicht als „auf oder „verbunden mit” einem anderen Element oder einer anderen Schicht oder „angefügt an” oder „angrenzend an” ein anderes Element oder eine andere Schicht bedeutet, dass es direkt auf oder direkt verbunden mit dem anderen Element oder der anderen Schicht sein kann oder direkt an das andere Element oder die andere Schicht angefügt sein oder angrenzen kann oder dass Zwischenelemente oder -schichten vorhanden sein können. Wenn ein Element dagegen als „direkt auf” oder „direkt verbunden mit” einem anderen Element oder einer anderen Schicht oder als „direkt angefügt an” oder „unmittelbar angrenzend an” ein anderes Element oder eine andere Schicht bezeichnet wird, sind keine Zwischenelemente oder -schichten vorhanden.

-

Solange nichts anderes definiert ist, haben alle Begriffe (einschließlich von technischen und wissenschaftlichen Begriffen), die hierin verwendet werden, die gleiche Bedeutung, in der sie von einem Durchschnittsfachmann auf dem Gebiet, zu dem die erfinderische Idee gehört, verstanden werden. Man beachte ferner, dass Ausdrücke wie solche, die in herkömmlich verwendeten Wörterbüchern verwendet werden, in der Bedeutung verstanden werden sollen, die mit ihrer Bedeutung im Kontext der verwandten Technik und/oder der vorliegenden Schrift konsistent ist, und nicht in einem idealisierten oder übermäßig formalen Sinn interpretiert werden sollten, solange hierin nicht ausdrücklich etwas anderes angegeben ist.

-

Der Begriff „ausgewählte Bitleitung” oder „ausgewählte Bitleitungen” kann verwendet werden, um eine Bitleitung oder mehrere Bitleitungen zu bezeichnen, die mit einem Zellentransistor, der programmiert oder gelesen werden soll, verbunden ist bzw. sind. Der Begriff „nicht ausgewählte Bitleitung” oder „nicht ausgewählte Bitleitungen” kann verwendet werden, um unter einer Mehrzahl von Bitleitungen eine oder mehrere Bitleitungen zu bezeichnen, die mit einem Zellentransistor, dessen Programmierung oder Lesung gehemmt ist, verbunden ist bzw. sind.

-

Der Begriff „ausgewählte Folgenansteuerungsleitung” kann verwendet werden, um unter einer Mehrzahl von Folgenansteuerungsleitungen eine Folgenansteuerungsleitung zu bezeichnen, die mit einer Zellenfolge verbunden ist, die einen Zellentransistor aufweist, der programmiert oder gelesen werden soll. Der Begriff „nicht ausgewählte Folgenansteuerungsleitung” oder „nicht ausgewählte Folgenansteuerungsleitungen” kann verwendet werden, um unter einer Mehrzahl von Folgenansteuerungsleitungen eine oder mehrere verbliebene Folgenansteuerungsleitungen zu bezeichnen, bei der bzw. bei denen es sich nicht um die ausgewählte Folgenansteuerungsleitung handelt. Der Begriff „ausgewählte Folgenansteuerungstransistoren” kann verwendet werden, um Folgenansteuerungstransistoren zu bezeichnen, die mit einer ausgewählten Folgenansteuerungsleitung verbunden sind. Der Begriff „nicht ausgewählte Folgenansteuerungstransistoren” kann verwendet werden, um Folgenansteuerungstransistoren zu bezeichnen, die mit einer oder mehreren nicht ausgewählten Folgenansteuerungsleitungen verbunden sind.

-

Der Begriff „ausgewählte Masseansteuerungsleitung” kann verwendet werden, um unter einer Mehrzahl von Masseansteuerungsleitungen eine Masseansteuerungsleitung zu bezeichnen, die mit einer Zellenfolge verbunden ist, die einen Zellentransistor aufweist, der programmiert oder gelesen werden soll. Der Begriff „nicht ausgewählte Masseansteuerungsleitung” kann verwendet werden, um unter einer Mehrzahl von Masseansteuerungsleitungen eine oder mehrere verbliebene Masseansteuerungsleitungen zu bezeichnen, bei der bzw. bei denen es sich nicht die ausgewählte Masseansteuerungsleitung handelt. Der Begriff „ausgewählte Masseansteuerungstransistoren” kann verwendet werden, um Masseansteuerungstransistoren zu bezeichnen, die mit einer ausgewählten Masseansteuerungsleitung verbunden sind. Der Begriff „nicht ausgewählte Masseansteuerungstransistoren” kann verwendet werden, um Masseansteuerungstransistoren zu bezeichnen, die mit einer oder mehreren nicht ausgewählten Masseansteuerungsleitungen verbunden sind.

-

Der Begriff „nicht ausgewählte Wortleitung” kann verwendet werden, um unter einer Mehrzahl von Wortleitungen eine Wortleitung zu bezeichnen, die programmiert oder gelesen werden soll. Der Begriff „nicht ausgewählte Wortleitung” oder „nicht ausgewählte Wortleitungen” kann verwendet werden, um unter einer Mehrzahl von Wortleitungen eine oder mehrere verbliebene Wortleitungen zu bezeichnen, bei der bzw. bei denen es sich nicht um eine ausgewählte Wortleitung handelt.

-

Der Begriff „ausgewählte Speicherzelle” oder „ausgewählte Speicherzellen” kann verwendet werden, um unter einer Mehrzahl von Speicherzellen Speicherzellen zu bezeichnen, die programmiert oder gelesen werden sollen. Der Begriff „nicht ausgewählte Speicherzelle” oder „nicht ausgewählte Speicherzellen” kann verwendet werden, um unter einer Mehrzahl von Speicherzellen eine oder mehrere verbliebene Speicherzellen zu bezeichnen, bei der bzw. bei denen es sich nicht um eine ausgewählte Speicherzelle oder um ausgewählte Speicherzellen handelt.

-

Beispiele für Ausführungsformen der erfinderischen Idee werden mit Bezug auf einen NAND-Flash-Speicher beschrieben. Jedoch ist die erfinderische Idee nicht darauf beschränkt. Die erfinderische Idee kann auf nicht-flüchtige Speichervorrichtungen, wie ein elektrisch löschbares und programmierbares ROM (EEPROM), einen NOR-Flash-Speicher, ein Phasenänderungs-RAM (PRAM), ein magnetisches RAM (MRAM), ein resistives RAM (RRAM), ein ferroelektrisches RAM (FRAM) usw. angewendet werden.

-

1 ist ein Blockschema, das eine nicht-flüchtige Speichervorrichtung 100 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt. Wie in 1 dargestellt ist, kann die nicht-flüchtige Speichervorrichtung 100 ein Speicherzellen-Array 110, eine Adressen-Decodierungseinheit 120, eine Seitenspeichereinheit 130, eine Daten-Eingabe-/Ausgabeeinheit (I/O) 140, eine Zähleinheit 150, eine Pass/Fail (P/F)-Überprüfungseinheit 160 und eine Steuerlogik 170 aufweisen. Die Adressen-Decodierungseinheit 120, die Seitenspeichereinheit 130, die Daten-Eingabe-/Ausgabeeinheit 140, die Zähleinheit 150, die Pass/Fail-Überprüfungseinheit 160 und die Steuerlogik 170 können als Steuereinheit zum Steuern des Speicherzellen-Array 110 bezeichnet werden.

-

Das Speicherzellen-Array 100 kann eine Mehrzahl von Speichereinheiten mit einer Mehrzahl von Speicherzellen beinhalten. Die Mehrzahl von Speichereinheiten kann eine Mehrzahl von Zellenfolgen sein, die in einer Zeilenrichtung und einer Spaltenrichtung auf einem Substrat angeordnet sind. Jede Zellenfolge kann eine Mehrzahl von Speicherzellen aufweisen, die in senkrechter Richtung zum Substrat gestapelt sind. Das heißt, Speicherzellen können in Zeilen und Spalten am Substrat vorgesehen sein und senkrecht zum Substrat gestapelt sein, um eine dreidimensionale Struktur zu bilden. Das Speicherzellen-Array 110 kann mehrere Speicherzellen aufweisen, die jeweils eines oder mehrere Datenbits speichern.

-

Die Adressen-Decodierungseinheit 120 kann über Wortleitungen WL, Folgenansteuerungsleitungen SSL und Masseansteuerungsleitungen GSL mit dem Speicherzellen-Array 110 verbunden sein. Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie ansprechend auf die Steuerung der Steuerlogik 170 arbeitet. Die Adressen-Decodierungseinheit 120 kann eine Eingangsadresse ADDR von einer externen Vorrichtung empfangen.

-

Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie eine Zeilenadresse der eingegebenen Adresse ADDR decodiert. Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie unter den Wortleitungen WL eine Wortleitung auswählt, die der decodierten Zeilenadresse entspricht. Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie unter den Folgenansteuerungsleitungen SSL und den Masseansteuerungsleitungen GSL eine Folgenansteuerungsleitung und eine Masseansteuerungsleitung auswählt, die der decodierten Zeilenadresse entspricht.

-

Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie unter der eingegebenen Adresse ADDR eine Spaltenadresse decodiert. Die Adressen-Decodierungseinheit 120 kann die decodierte Spaltenadresse DCA in die Seitenspeichereinheit 130 überführen.

-

Die Adressen-Decodierungseinheit 120 kann so gestaltet sein, dass sie ein Vorab-Lesesignal PRS von der Steuerlogik 170 empfängt. Wenn das Vorab-Lesesignal PRS aktiviert ist, kann die Adressen-Decodierungseinheit 120 Spannungen zum Vorab-Lesen an die Folgenansteuerungsleitungen SSL, die Wortleitungen WL und die Masseansteuerungsleitungen GSL liefern.

-

Die Adressen-Decodierungseinheit 120 kann gemäß der Steuerung durch die Steuerlogik 170 Spannungen zum Löschen, Schreiben und Lesen an die Folgenansteuerungsleitungen SSL, die Wortleitungen WL und die Masseansteuerungsleitungen GSL liefern.

-

Obwohl in 1 nicht dargestellt, kann die Adressen-Decodierungseinheit 120 in dieser Ausführungsform einen Zeilen-Decoder, der so gestaltet ist, dass er eine Zeilenadresse decodiert, einen Spalten-Decoder, der so gestaltet ist, dass er eine Spaltenadresse decodiert, einen Adressenpufferspeicher bzw. Adressenspeicher, der so gestaltet ist, dass er die Eingabeadresse ADDR speichert, und dergleichen aufweisen.

-

Die Seitenspeichereinheit 130 kann über die Bitleitungen BL mit dem Speicherzellen-Array 110 verbunden sein. Die Seitenspeichereinheit 130 kann ansprechend auf die Steuerung durch die Steuerlogik 170 arbeiten. Die Seitenspeichereinheit 130 kann die decodierte Spaltenadresse DCA von der Adressen-Decodierungseinheit 120 empfangen. Die Seitenspeichereinheit 130 kann die Bitleitungen BL ansprechend auf die decodierte Spaltenadresse DCA empfangen.

-

Die Seitenspeichereinheit 130 kann mit der Adressen-Decodierungseinheit 120 Lese- und Schreiboperationen durchführen. Das Lesen und Beschreiben des Speicherzellen-Array 110 kann durch Steuern der Folgenansteuerungsleitungen SSL, der Wortleitungen WL und der Masseansteuerungsleitungen GSL über die Adressen-Decodierungseinheit 120 und durch Steuern der Bitleitungen BL über die Seitenspeichereinheit 130 durchgeführt werden.

-

Die Seitenspeichereinheit 130 kann (nicht dargestellte) Auffangregister bzw. Latches aufweisen, die den jeweiligen Bitleitungen BL entsprechen. Daten, die in das Speicherzellen-Array 110 geschrieben werden sollen, können in die Auffangregister der Seitenspeichereinheit 130 geladen werden. Daten, die aus dem Speicherzellen-Array 110 ausgelesen werden, können in den Auffangregistern der Seitenspeichereinheit 130 gespeichert werden.

-

Die Seitenspeichereinheit 130 kann Daten über Datenleitungen DL empfangen. Die Daten, die in die Seitenspeichereinheit 130 eingegeben worden sind, können in das Speicherzellen-Array 110 geschrieben werden. Die Seitenspeichereinheit 130 kann Daten aus dem Speicherzellen-Array 110 lesen, um die ausgelesenen Daten über die Datenleitungen DL an die Daten-Eingabe-/Ausgabeeinheit 140 auszugeben. Die Seitenspeichereinheit 130 kann Daten speichern, die aus einem ersten Speicherbereich des Speicherzellen-Array 110 ausgelesen werden. Die in der Seitenspeichereinheit 130 gespeicherten Daten können in einen zweiten Speicherbereich geschrieben werden. Das heißt, es kann ein Rückkopieroperation durchgeführt werden

-

Die Seitenspeichereinheit 130 kann die gelesenen Daten als Leseergebnis RR ausgeben. Beispielsweise kann die Seitenspeichereinheit 130 die gelesenen Daten in einer Löschungsverifizierungsoperation ausgeben oder die gelesenen Daten in einer Schreibverifizierungsoperation als Leseergebnis RR ausgeben.

-

Die Seitenspeichereinheit 130 kann so gestaltet sein, dass sie das Vorab-Lesesignal PRS von der Steuerlogik 170 empfängt. Wenn das Vorab-Lesesignal PRS aktiviert ist, kann die Seitenspeichereinheit 130 mit der Adressen-Decodierungseinheit 120 eine Vorab-Lesung durchführen. Daten, die bei der Vorab-Lesung gelesen werden, können als das Leseergebnis RR ausgegeben werden.

-

Die Daten-Eingabe-/Ausgabeeinheit 140 kann über die Datenleitungen DL mit der Seitenspeichereinheit 130 verbunden sein. Die Daten-Eingabe-/Ausgabeeinheit 140 kann so gestaltet sein, dass sie Daten mit einer externen Vorrichtung austauscht. Die Daten-Eingabe-/Ausgabeeinheit kann Daten, die aus der Seitenspeichereinheit 130 übertragen werden, über die Datenleitungen DL an die externe Vorrichtung ausgeben. Die Daten-Eingabe-/Ausgabeeinheit 140 kann Daten, die von der externen Vorrichtung eingegeben werden, über die Datenleitungen DL in die Seitenspeichereinheit 130 übertragen.

-

Die Zähleinheit 150 kann so gestaltet sein, dass sie das Leseergebnis RR von der Seitenspeichereinheit 130 empfängt und das Vorablesesignal PRS von der Steuerlogik 170 empfängt. Die Zähleinheit 150 kann so gestaltet sein, dass sie bei Aktivierung des Vorablesesignals PRS aufgrund des Leseergebnisses RR zählt, um einen Zählwert CV zu erzeugen, der an die Steuerlogik 170 gesendet wird.

-

Die Pass/Fail-Zähleinheit 160 kann so gestaltet sein, dass sie das Leseergebnis RR von der Seitenspeichereinheit 130 empfängt. Die Pass/Fail-Zähleinheit 160 kann so gestaltet sein, dass sie bei der Löschungsverifizierungsoperation oder der Schreibverifizierungsoperation ein Signal PASS, das ein Gelingen anzeigt, oder ein Signal FAIL, das einen Fehlschlag anzeigt, auf Basis des Leseergebnisses RR ausgibt.

-

Die Steuerlogik 170 kann so gestaltet sein, dass sie einen Betrieb der nichtflüchtigen Speichereinheit 100 insgesamt steuert. Die Steuerlogik 170 kann so gestaltet sein, dass sie das Vorab-Lesesignal PRS erzeugt. Die Steuerlogik 170 kann den Zählwert CV von der Zähleinheit 150 und das PASS- oder FAIL-Signal, das ein Gelingen bzw. einen Fehlschlag anzeigt, von der Pass/Fail-Zähleinheit 160 empfangen. Die Steuerlogik 170 kann den Zählwert CV mit einem Wert vergleichen, der in einem Register REG1 gespeichert ist, um die Löschoperation gemäß dem Ergebnis eines Vergleichs zwischen dem Zählwert CV und dem Wert, der im Register REGT gespeichert ist, zu steuern. Die Steuerlogik 170 kann eine Löschoperation ansprechend auf das von der Pass/Fail-Zähleinheit 160 eingegebene PASS- oder FAIL-Signal, das ein Gelingen bzw. einen Fehlschlag anzeigt, steuern.

-

Die Steuerlogik 170 kann gemäß Steuersignalen CTRL und einem Befehl CMD, der von der externen Vorrichtung eingegeben wird, arbeiten.

-

2 ist ein Diagramm, das ein Speicherzellen-Array 110 von 1 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt. Wie in 1 und 2 dargestellt ist, kann das Speicherzellen-Array 110 eine Mehrzahl von Speicherblöcken BLK1 bis BLKz aufweisen, die jeweils so ausgebildet sind, dass sie eine dreidimensionale Struktur (oder eine vertikale Struktur) aufweisen. Beispielsweise kann jeder von den Speicherblöcken BLK1 bis BLKz Strukturen aufweisen, die sich in einer ersten Richtung bis einer dritten Richtung erstrecken. Obwohl dies in 2 nicht dargestellt ist, kann jeder der Speicherblöcke BLK1 bis BLKz eine Mehrzahl von Zellenfolgen aufweisen, die sich in einer zweiten Richtung erstrecken. Obwohl dies in 2 nicht dargestellt ist, kann eine Mehrzahl von Zellenfolgen entlang den ersten Richtungen bis dritten Richtungen voneinander beabstandet sein.

-

Zellenfolgen innerhalb eines einzigen Speicherblocks können mit einer Mehrzahl von Bitleitungen BL, einer Mehrzahl von Folgenansteuerungsleitungen SSL, einer Mehrzahl von Wortleitungen WL, einer oder mehreren Masseansteuerungsleitungen GSL und einer gemeinsamen (nicht dargestellten) Source-Leitung verbunden sein. Zellenfolgen in der Mehrzahl von Speicherblöcken BLK1 bis BLKz können sich eine Mehrzahl von Bitleitungen teilen. Beispielsweise kann sich die Mehrzahl von Bitleitungen in der zweiten Richtung erstrecken, so dass sie von der Mehrzahl von Speicherblöcken BLK1 bis BLKz gemeinsam genutzt werden kann.

-

Die Mehrzahl von Speicherblöcken BLK1 bis BLKz kann durch die Adressen-Decodierungseinheit 120 von 1 ausgewählt werden. Beispielsweise kann die Adressen-Decodierungseinheit 120 so gestaltet sein, dass sie von der Mehrzahl von Speicherblöcken BLK1 bis BLKz einen Speicherblock auswählt, der einer Eingangsadresse ADDR entspricht. An einem ausgewählten Speicherblock kann ein Löschen, Programmieren und Lesen durchgeführt werden. Die Mehrzahl von Speicherblöcken BLK1 bis BLKz wird mit Bezug auf 3 bis 6 ausführlicher beschrieben.

-

3 ist ein Flächendiagramm, das einen Speicherblock BLKa von den Speicherblöcken von 1 gemäß einem Ausführungsbeispiel der erfinderischen Idee zeigt. 4 ist eine perspektivische Darstellung entlang einer Linie IV-IV' von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee. 5 ist eine Querschnittsdarstellung entlang einer Linie IV-IV' von 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee.

-

Wie in 3 bis 5 dargestellt ist, können dreidimensionale Strukturen vorgesehen sein, die sich in den Richtungen eins bis drei erstrecken.

-

Es ist ein Substrat 111 vorgesehen. Das Substrat 111 kann beispielsweise eine Wanne sein, die eine erste Art von Leitfähigkeit aufweist. Das Substrat 111 kann eine p-Wanne sein, in die das Element der Gruppe III, beispielsweise Bor, injiziert ist. Das Substrat 111 kann eine Taschen-p-Wanne sein, die innerhalb einer n-Wanne vorgesehen ist. Im Folgenden wird angenommen, dass das Substrat 111 eine p-Wanne (oder eine Taschen-p-Wanne) ist. Jedoch ist das Substrat nicht darauf beschränkt. Das Substrat 111 kann ein Substrat von einer anderen Art als ein Substrat vom P-Typ sein.

-

Eine Mehrzahl von gemeinsamen Source-Regionen CSR, die sich in der ersten Richtung erstrecken, kann im Substrat 111 vorgesehen sein. Die gemeinsamen Source-Regionen CSR können in der zweiten Richtung voneinander beabstandet sein. Die gemeinsamen Source-Regionen CSR können miteinander verbunden sein, um eine gemeinsame Source-Leitung zu bilden.

-

Die gemeinsamen Source-Regionen CSR können eine Leitfähigkeit einer zweiten Art aufweisen, die sich von der des Substrats 111 unterscheidet. Beispielsweise können die gemeinsamen Source-Regionen CSR zum n-Typ gehören. Nachstehend wird angenommen, dass die gemeinsamen Source-Regionen CSR zum n-Typ gehören. Jedoch sind die gemeinsamen Source-Regionen CSR nicht darauf beschränkt. Die gemeinsamen Source-Regionen CSR können von einer anderen Art als der n-Typ sein.

-

Zwischen zwei benachbarten Regionen der gemeinsamen Source-Regionen CSR kann in der dritten Richtung (d. h. einer Richtung, die senkrecht ist zum Substrat 111) eine Mehrzahl von hintereinander liegenden Isoliermaterialien 112 und 112a am Substrat 111 vorgesehen sein. Die Isoliermaterialien 112 und 112a können in der dritten Richtung voneinander beabstandet sein. Die Isoliermaterialien 112 und 112a können sich in der ersten Richtung erstrecken. Beispielsweise können die Isoliermaterialien 112 und 112a ein Isoliermaterial wie eine Halbleiter-Oxidschicht beinhalten. Eine Dicke des Isoliermaterials 112a, welches mit dem Substrat 111 Kontakt hat, kann geringer sein als die der anderen Isoliermaterialien 112.

-

Zwischen zwei benachbarten Regionen der gemeinsamen Source-Regionen CSR kann eine Mehrzahl von Säulen PL hintereinander in der ersten Richtung so angeordnet sein, dass sie in der zweiten Richtung durch die Mehrzahl von Isoliermaterialien 112 und 112a hindurch verlaufen. Beispielsweise können die Säulen PL durch die Isoliermaterialien 112 und 112a hindurch mit dem Substrat 111 in Kontakt stehen.

-

In einem Ausführungsbeispiel können die Säulen PL zwischen zwei benachbarten gemeinsamen Source-Regionen in der ersten Richtung voneinander beabstandet sein. Die Säulen PL können in der ersten Richtung in einer Reihe angeordnet sein.

-

In einem Ausführungsbeispiel können die Säulen PL jeweils aus einer Mehrzahl von Materialien gebildet sein. Jede der Säulen PL kann eine Kanalschicht 114 und ein inneres Material 115 innerhalb der Kanalschicht 114 aufweisen.

-

Die Kanalschichten 114 können ein Halbleitermaterial (z. B. Silicium) mit einer Leitfähigkeit von einer ersten Art aufweisen. Beispielsweise können die Kanalschichten 114 ein Halbleitermaterial (z. B. Silicium) beinhalten, dessen Leitfähigkeit zur gleichen Art gehört wie die des Substrats 111. Die Kanalschichten 114 können einen intrinsischen Halbleiter aufweisen, der ein Nicht-Leiter bzw. Isolator ist.

-

Die inneren Materialien 115 können ein Isoliermaterial beinhalten. Beispielsweise können die inneren Materialien 115 ein Isoliermaterial wie Siliciumoxid aufweisen. Alternativ dazu können die inneren Materialien 115 einen Luftspalt aufweisen.

-

Zwischen zwei benachbarten Regionen der gemeinsamen Source-Regionen CSR können Informationsspeicherschichten 116 an freiliegenden Oberflächen der Isoliermaterialien 112 und 112a und der Säulen PL vorgesehen sein. Die Informationsspeicherschichten 116 können Informationen durch Einfangen oder Entladen von Ladungen speichern.

-

Zwischen zwei benachbarten gemeinsamen Source-Regionen und zwischen den Isoliermaterialien 112 und 112a können leitende Materialien CM1 bis CM8 an freiliegenden Oberflächen der Informationsspeicherschichten 116 vorgesehen sein. Die leitenden Materialien CM1 bis CM8 können sich in der ersten Richtung erstrecken. Die leitfähigen Materialien CM1 bis CM8 auf den gemeinsamen Source-Regionen CSR können durch Wortleitungsunterbrechungen voneinander getrennt sein. Die gemeinsamen Source-Regionen CSR können durch die Wortleitungsunterbrechungen freigelegt sein. Die Wortleitungsunterbrechungen können sich in der ersten Richtung erstrecken.

-

In einem Ausführungsbeispiel können die leitenden Materialien CM1 bis CM8 ein metallisches leitfähiges Material beinhalten. Die leitfähigen Materialien CM1 bis CM8 können ein nicht-metallisches leitfähiges Material wie Polysilicium beinhalten.

-

In einem Ausführungsbeispiel können Informationsspeicherschichten 116 entfernt werden, die an einer Oberseite desjenigen Isoliermaterials, das unter den Isoliermaterialien an der obersten Schicht angeordnet ist, vorgesehen sind. Beispielsweise können Informationsspeicherschichten entfernt werden, die an denjenigen Seiten von den Seiten der Isoliermaterialien 112 und 112a vorgesehen sind, die den Säulen PL gegenüber liegen.

-

Eine Mehrzahl von Drains 320 kann jeweils an der Mehrzahl von Säulen PL vorgesehen sein. Die Drains 320 können ein Halbleitermaterial (z. B. Silicium) aufweisen, das beispielsweise eine Leitfähigkeit der zweiten Art aufweist. Die Drains 320 können ein Halbleitermaterial (z. B. Silicium) vom n-Typ aufweisen. Nachstehend wird angenommen, dass die Drains 320 Silicium vom n-Typ aufweisen. Jedoch ist die vorliegende Erfindung nicht darauf beschränkt. Die Drains 320 können bis zur Oberseite der Kanalschichten 114 der Säulen PL reichen.

-

Bitleitungen BL, die in der zweiten Richtung verlaufen, können an den Drains 320 so vorgesehen sein, dass sie in der ersten Richtung voneinander beabstandet sind. Die Bitleitungen BL können mit den Drains 320 verbunden sein. In dieser Ausführungsform können die Drains 320 und die Bitleitungen BL über Steckkontakte (nicht dargestellt) miteinander verbunden sein. Die Bitleitungen BL können ein metallisches leitendes Material aufweisen. Alternativ dazu können die Bitleitungen BL ein nicht-metallisches leitendes Material wie Polysilicium aufweisen.

-

Im Folgenden können die leitenden Materialien CM1 bis CM8 gemäß einem Abstand zum Substrat auf einer ersten Höhe bis einer achten Höhe 111 angeordnet sein.

-

Die Mehrzahl von Säulen PL kann zusammen mit den Informationsspeicherschichten 116 und der Mehrzahl von leitfähigen Materialien CM1 bis CM8 eine Mehrzahl von Zellenfolgen bilden. Jede der Säulen PL kann mit einer Informationsspeicherschicht 116 und einem benachbarten leitfähigen Material CMi eine Zellenfolge bilden (wobei i eines von 1 bis 8 ist).

-

Die Säulen PL können in Zeilen- und Spaltenrichtungen auf dem Substrat 111 angeordnet sein. Die achten leitfähigen Materialien CM8 können Zeilen bilden. Säulen, die mit dem gleichen leitfähigen Material von den achten leitfähigen Materialien CM8 verbunden sind, können eine Zeile bilden. Die Bitleitungen BL können Spalten bilden. Säulen, die mit der gleichen Bitleitung von den Bitleitungen BL verbunden sind, können eine Spalte bilden. Die Säulen PL können zusammen mit den Informationsspeicherschichten 116 und der Mehrzahl von leitfähigen Materialien CM1 bis CM8 eine Mehrzahl von Folgen bilden, die in Zeilen- und Spaltenrichtungen angeordnet sind. Jede Zellenfolge kann eine Mehrzahl von Zellentransistoren CT aufweisen, die in senkrechter Richtung zum Substrat 111 gestapelt sind.

-

6 ist ein Diagramm, das einen der Zellentransistoren CT von 5 darstellt. Wie in 3 bis 6 dargestellt ist, können die Zellentransistoren CT aus leitfähigen Materialien CM1 bis CM8, Säulen PL und Informationsspeicherschichten 116, die zwischen den leitfähigen Materialien CM1 bis CM8 und den Säulen PL vorgesehen sind, gebildet sein.

-

Die Informationsspeicherschichten 116 können sich von Regionen zwischen den leitfähigen Materialien CM1 bis CM8 und den Säulen PL bis zu Oberseiten und Unterseiten der leitfähigen Materialien CM1 bis CM8 erstrecken. Jede der Informationsspeicherschichten 116 kann erste bis dritte Unterisolierschichten 117, 118 und 119 aufweisen.

-

In den Zellentransistoren CT können die Kanalschichten 114 der Säulen PL das gleiche Silicium vom p-Typ aufweisen wie das Substrat 111. Die Kanalschichten 114 können als Bodies bzw. Substrate von Zellentransistoren CT dienen. Die Kanalschichten 114 können in senkrechter Richtung zum Substrat 111 ausgebildet sein. Die Kanalschichten 114 der Säulen PL können als vertikales Substrat dienen. Vertikale Kanäle können an den Kanalschichten 114 ausgebildet sein.

-

Die ersten Unterisolierschichten 117, die an die Säulen PL angrenzen, können als Tunnellungsisolierschichten der Zellentransistoren CT dienen. Beispielsweise können die ersten Unterisolierschichten 117 jeweils eine thermische Oxidschicht aufweisen. Die ersten Unterisolierschichten 117 können jeweils eine Siliciumoxidschicht aufweisen.

-

Die zweiten Unterisolierschichten 118 können als Ladungsspeicherschichten der Zellentransistoren CT dienen. Beispielsweise können die zweiten Unterisolierschichten 118 jeweils als Ladungsfallenschichten dienen. Beispielsweise können die zweiten Unterisolierschichten 118 jeweils eine Nitridschicht oder eine Metalloxidschicht aufweisen.

-

Die dritten Unterisolierschichten 119, die an die leitenden Materialien CM1 bis CM8 angrenzen, können als Sperrisolierschichten der Zellentransistoren CT dienen. In dieser Ausführungsform können die dritten Unterisolierschichten 119 aus einer einzigen Schicht oder aus mehreren Schichten gebildet sein. Die dritten Unterisolierschichten 119 können eine hoch-dielektrische Schicht (z. B. eine Aluminiumoxidschicht, eine Hafniumoxidschicht usw.) mit einer dielektrischen Konstante, die größer ist als diejenige der ersten und zweiten Unterisolierschichten 117 und 118, sein. Die dritten Unterisolierschichten 119 können jeweils eine Siliciumoxidschicht beinhalten.

-

In dieser Ausführungsform können die ersten bis dritten Unterisolierschichten 117 bis 119 ONA (Oxid-Nitrid-Aluminium-Oxid) oder ONO (Oxid-Nitrid-Oxid) bilden.

-

Die Mehrzahl von leitenden Materialien CM1 bis CM8 kann als Gate (bzw. als Steuer-Gate) dienen.

-

Das heißt, die Mehrzahl von leitenden Materialien CM1 bis CM8, die als Gates (bzw. als Steuer-Gates) dienen, die dritten Unterisolierschichten 119, die als Sperrisolierschichen dienen, die zweiten Unterisolierschichten 118, die als Ladungsspeicherschichten dienen, die ersten Unterisolierschichten 117, die als Tunnellungsisolierschichten dienen, und die Kanalschichten 114, die als vertikale Substrate dienen, können Zellentransistoren CT bilden, die in senkrechter Richtung zum Substrat 111 gestapelt sind. Beispielsweise können die Zellentransistoren CT ein Zellentransistor von der Art einer Ladungsfalle sein.

-

Die Zellentransistoren CT können entsprechend ihrer Höhe für verschiedene Zwecke verwendet werden. Beispielsweise können von den Zellentransistoren CT Zellentransistoren, die zumindest auf einer Höhe liegen und die an einem oberen Abschnitt angeordnet sind, als Folgenansteuerungstransistoren verwendet werden. Folgenansteuerungstransistoren können so gestaltet sein, dass sie Schaltoperationen zwischen den Zellenfolgen und Bitleitungen durchführen. Von den Zellentransistoren CT können Zellentransistoren, die zumindest auf einer Höhe liegen und die an einem unteren Abschnitt angeordnet sind, als Masseansteuerungstransistoren verwendet werden. Masseansteuerungstransistoren können so gestaltet sein, dass sie Schaltoperationen zwischen Zellenfolgen und einer gemeinsamen Source-Leitung, die aus gemeinsamen Source-Regionen CSR gebildet ist, durchführen. Zellentransistoren zwischen Zellentransistoren, die als Folgen- oder Masseansteuerungstransistoren verwendet werden, können als Speicherzellen und als Speicherleerzellen verwendet werden.

-

Die leitenden Materialien CM1 bis CM8 können sich in der ersten Richtung so erstrecken, dass sie mit der Mehrzahl von Säulen PL verbunden sind. Die leitenden Materialien CM1 bis CM8 können Leiterbahnen darstellen, die Zellentransistoren CT der Säulen PL miteinander verbinden. In dieser Ausführungsform können die leitenden Materialien CM1 bis CM8 entsprechend ihrer Höhe als Folgenansteuerungsleitung, als Masseansteuerungsleitung, als Wortleitung oder als Wortleerleitung verwendet werden.

-

Leiterbahnen, die als Folgenansteuerungstransistoren verwendete Zellentransistoren miteinander verbinden, können als Folgenansteuerungsleitungen verwendet werden. Leiterbahnen, die als Masseansteuerungstransistoren verwendete Zellentransistoren miteinander verbinden, können als Masseansteuerungsleitungen verwendet werden. Leiterbahnen, die als Speicherzellen verwendete Zellentransistoren miteinander verbinden, können als Wortleitungen verwendet werden. Leiterbahnen, die als Speicherleerzellen verwendete Zellentransistoren miteinander verbinden, können als Wortleerleitungen verwendet werden.

-

7 ist ein Schaltplan, der eine Ersatzschaltung eines Abschnitts EC einer Draufsicht in 3 gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt. Wie in 3 bis 7 dargestellt ist, können Zellenfolgen CS11, CS12, CS21 und CS22 zwischen Bitleitungen BL1 und BL2 und einer gemeinsamen Source-Leitung CSL vorgesehen sein. Zellenfolgen CS11 und CS21 können die erste Bitleitung BL1 und die gemeinsame Source-Leitung CSL verbinden, und Zellenfolgen CS12 und CS22 können die zweite Bitleitung BL2 und die gemeinsame Source-Leitung CSL verbinden.

-

Gemeinsame Source-Regionen CSR können gemeinsam verbunden sein, um eine gemeinsame Source-Leitung CSL zu bilden.

-

Die Zellenfolgen CS11, CS12, CS21 und CS22 können vier Säulen eines Abschnitts EC einer Draufsicht in 3 entsprechen. Die vier Säulen können zusammen mit leitenden Materialien CM1 bis CM8 und Informationsspeicherschichten 116 vier Zellenfolgen CS11, CS12, CS21 und CS22 bilden.

-

In dieser Ausführungsform können die ersten leitenden Materialien CM1 mit den Informationsspeicherschichten 116 und den Säulen PL Masseansteuerungstransistoren GST bilden. Die ersten leitenden Materialien CM1 können eine Masseansteuerungsleitung GSL bilden. Die ersten leitenden Materialien CM1 können miteinander verbunden sein, um eine Masseansteuerungsleitung GSL zu bilden.

-

Die zweiten bis siebten leitenden Materialien CM2 bis CM7 können mit den Informationsspeicherschichten 116 und den Säulen PL die ersten bis sechsten Speicherzellen MC1 bis MC6 bilden. Die zweiten bis siebten leitenden Materialien CM2 bis CM7 können als die ersten bis sechsten Wortleitungen WL1 bis WL6 verwendet werden.

-

Das zweite leitende Material CM2 kann so verbunden sein, dass es die erste Wortleitung WL1 bildet. Das dritte leitende Material CM3 kann so verbunden sein, dass es die zweite Wortleitung WL2 bildet. Das vierte leitende Material CM4 kann so verbunden sein, dass es die dritte Wortleitung WL3 bildet. Das fünfte leitende Material CM5 kann so verbunden sein, dass es die vierte Wortleitung WL4 bildet. Das sechste leitende Material CM6 kann so verbunden sein, dass es die fünfte Wortleitung WL5 bildet. Das siebte leitende Material CM7 kann so verbunden sein, dass es die sechste Wortleitung WL6 bildet.

-

Die achten leitenden Materialien CM8 können mit den Informationsspeicherschichten 116 und den Säulen PL Folgenansteuerungstransistoren SST bilden. Die achten leitenden Materialien CM8 können Folgenansteuerungsleitungen SSL1 und SSL2 bilden.

-

Speicherzellen, die auf der gleichen Höhe liegen, können gemeinsam mit einer Wortleitung verbunden werden. Somit kann eine Spannung, die an eine Wortleitung auf einer bestimmten Höhe angelegt wird, an alle Zellenfolgen CS11, CS12, CS21 und CS22 angelegt werden.

-

Zellenfolgen in unterschiedlichen Zeilen können mit unterschiedlichen Folgenansteuerungsleitungen SSL1 und SSL2 verbunden sein. Die Zellenfolgen CS11, CS12, CS21 und CS22 können durch Ansteuern oder Nicht-Ansteuern der Folgenansteuerungsleitungen SSL1 und SSL2 zeilenweise ausgewählt werden. Beispielsweise können Zellenfolgen (CS11 und CS12) oder (SC21 und CS22), die mit einer nicht ausgewählten Folgenansteuerungsleitung SSL1 oder SSL2 verbunden sind, elektrisch von den Bitleitungen BL1 und BL2 getrennt sein. Zellenfolgen (CS21 und CS22) oder (CS11 und CS12), die mit einer ausgewählten Folgenansteuerungsleitung SSL2 oder SSL1 verbunden sind, können elektrisch mit den Bitleitungen BL1 und BL2 verbunden sein.

-

Die Zellenfolgen CS11, CS12, CS21 und CS22 können als Spalten ausgebildet sein, die mit den Bitleitungen BL1 und BL2 verbunden sein können. Die Zellenfolgen CS11 und CS21 können mit der Bitleitung BL1 verbunden sein, und die Zellenfolgen CS12 und CS22 können mit der Bitleitung BL2 verbunden sein. Die Zellenfolgen CS11, CS12, CS21 und CS22 können Spalten sein, die durch Ansteuern und Nicht-Ansteuern der Bitleitungen BL1 und BL2 ausgewählt bzw. nicht ausgewählt werden.

-

Es kann passieren, dass Löcher für Säulen PL wegen eines Herstellungsfehlers bei der Ausbildung der Säulen PL keinen Kontakt mit einem ein Substrat 111 bekommen. Das heißt, es kann passieren, dass die Säulen PL nicht tief genug ausgebildet werden. Dadurch kann es sein, dass Kanalschichten 114 keinen Kontakt mit dem Substrat 111 bekommen. Das heißt, Zellenfolgen CS können Off-Strings aufweisen.

-

Es kann passieren, dass Drains 320 wegen eines Herstellungsfehlers bei der Ausbildung der Drains 320 keinen Kontakt mit den Kanalschichten 114 der Säulen PL bekommen. Das heißt, Zellenfolgen CS können Off-Strings aufweisen.

-

Wenn abgeschaltete Zellenfolgen (im Folgenden als Off-String bezeichnet) vorhanden sind, kann es passieren, dass ein Löschen, Lesen und Beschreiben eines Speicherblocks BLKa1 fehlerhaft durchgeführt wird. In der Ausführungsform der erfinderischen Idee kann eine Funktionsstörung wegen der Off-Strings unter Verwendung der Fehlerkorrekturfunktion, die von einem Fehlerkorrektur-Code (ECC) unterstützt wird, verhindert werden.

-

8 ist ein Flussdiagramm, das ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee darstellt. 9 ist ein Diagramm, das eine Vorspannungsbedingung gemäß dem Löschverfahren von 8 zeigt. Nachstehend wird ein Löschverfahren gemäß einem Ausführungsbeispiel der erfinderischen Idee ausführlicher mit Bezug auf 1 und 7 bis 9 beschrieben.

-

Im Schritt S111 kann eine Löschspannung geliefert werden.

-

Bitleitungen BL1 und BL2 können floaten, bzw. ihr Potential kann undefiniert gelassen werden, und Folgenansteuerungsleitungen SSL1 und SSL2 können floaten oder sie können mit der ersten Spannung VSSL1 für Folgenansteuerungsleitungen beliefert werden. Die erste Wortleitungs-Löschspannung Vwe1 kann jeweils an Wortleitungen WL1 bis WL6 angelegt werden. Die erste Wortleitungs-Löschspannung Vwe1 kann eine Massespannung VSS oder eine niedrige Spannung (beispielsweise eine niedrige positive Spannung oder eine niedrige negative Spannung) mit einem ähnlichen Pegel wie die Massespannung VSS sein. Eine Masseansteuerungsleitung GSL kann floaten oder sie kann mit der ersten Masseansteuerungsleitung VGSL1 beliefert werden. Eine gemeinsame Source-Leitung CSL kann floaten. Die erste Löschspannung Vers1 kann an ein Substrat 111 angelegt werden. Die erste Löschspannung Vers1 kann eine hohe Spannung sein. Die erste Spannung VSSL1 für Folgenansteuerungsleitungen und die erste Spannung VGSL1 für Masseansteuerungsleitungen können einen Pegel zwischen der ersten Löschspannung Vers1 und der Massespannung VSS aufweisen. Spannungsänderungen des Substrats 111, der Kanalschichten 114 und der Wortleitungen WL1 bis WL6 können in 10 dargestellt sein.

-

Zu einer Zeit T1 von 10 kann die erste Löschspannung Vers1, die zum Substrat 111 geliefert wird, an die Kanalschichten 114 angelegt werden. Die Kanalschichten 114 können auf die erste Löschspannung Vers1 aufgeladen werden. Ladungen, die in Speicherzellen MC1 bis MC6 gefangen sind, können aufgrund eines Spannungsunterschieds zwischen der ersten Wortleitungs-Löschspannung Vwe1, die zu den Wortleitungen WL1 bis WL6 geliefert wird, und der ersten Löschspannung Vers1, die zu den Kanalschichten 114 geliefert wird, entladen werden. Das heißt, Schwellenspannungen der Speicherzellen MC1 bis MC6 können sinken.

-

In Schritt S112 kann die erste Folgenansteuerungsleitung SSL1 ausgewählt werden. Eine Einschaltspannung kann an eine ausgewählte, d. h. die erste Folgenansteuerungsleitung SSL1 angelegt werden, und eine Ausschaltspannung kann an eine nicht ausgewählte Folgenansteuerungsleitung SSL2 angelegt werden.

-

In Schritt S113 kann eine Leseoperation durch Anlegen der ersten hohen Spannung VH1 an die Wortleitungen WL1 bis WL6 durchgeführt werden.

-

Die erste Bitleitungsspannung VBL1 kann zu den Bitleitungen BL1 und BL2 geliefert werden.

-

Die zweite Spannung VSSL2 für Folgenansteuerungsleitungen kann zur ausgewählten Folgenansteuerungsleitung (z. B. SSL1) geliefert werden. Die zweite Spannung VSSL2 für Folgenansteuerungsleitungen kann eine Spannung sein, die ausreicht, um die ersten Folgenansteuerungstransistoren SST1 (die Folgenansteuerungstransistoren, die mit der ersten Folgenansteuerungsleitung SSL1 verbunden sind) einzuschalten. Die zweite Spannung VSSL2 für Folgenansteuerungsleitungen kann eine Versorgungsspannung VCC oder Lesespannung Vread für nicht-ausgewählte Leitungen sein. Die Lesespannung Vread für nicht-ausgewählte Leitungen kann eine Spannung sein, die während einer Leseoperation an nicht ausgewählte Wortleitungen geliefert wird.

-

Die dritte Spannung VSSL3 für Folgenansteuerungsleitungen kann an eine nicht ausgewählte Folgenansteuerungsleitung (z. B. SSL2) geliefert werden. Die dritte Spannung VSSL3 für Folgenansteuerungsleitungen kann eine Spannung sein, die ausreicht, um die zweiten Folgenansteuerungstransistoren SST2 (die Folgenansteuerungstransistoren, die mit der zweiten Folgenansteuerungsleitung SSL2 verbunden sind) einzuschalten. Die dritte Spannung VSSL3 für Folgenansteuerungsleitungen kann eine Massespannung VSS oder eine niedrige Spannung (entweder eine positive Spannung oder eine negative Spannung) mit einem ähnlichen Pegel wie die Massespannung VSS sein.

-

Die erste hohe Spannung VH1 kann zu den Wortleitungen WL1 bis WL6 geliefert werden. Die erste hohe Spannung VH1 kann eine Spannung sein, die ausreicht, um die Speicherzellen MC1 bis MC6 unabhängig von den logischen Zuständen der Speicherzellen MC1 bis MC6 einzuschalten. Die erste hohe Spannung VH1 kann eine Lesespannung Vread für nicht-ausgewählte Leitungen sein.

-

Die zweite Spannung VGSL2 für Masseansteuerungsleitungen kann zur Masseansteuerungsleitung GSL geliefert werden. Die zweite Spannung VGSL2 für Masseansteuerungsleitungen kann eine Spannung sein, die ausreicht, um die Masseansteuerungstransistoren GST einzuschalten. Die zweite Spannung VGSL2 für Masseansteuerungsleitungen kann die Versorgungsspannung VCC oder die Lesespannung Vread für nicht-ausgewählte Leitungen sein.

-

Die erste Spannung VCSL1 für gemeinsame Source-Leitungen kann zur gemeinsamen Source-Leitung CSL geliefert werden. Die erste Spannung VCSL1 für gemeinsame Source-Leitungen kann die Massespannung VSS oder eine niedrige Spannung (eine positive Spannung oder eine negative Spannung) mit einem ähnlichen Pegel wie die Massespannung VSS sein.

-

Die erste Substratspannung VSUB1 kann zum Substrat 111 geliefert werden. Die erste Substratspannung VSUB1 kann die Massespannung VSS oder eine niedrige Spannung (eine positive Spannung oder eine negative Spannung) mit einem ähnlichen Pegel wie die Massespannung VSS sein.

-

Eine Spannungsänderung des Speicherzellen-Array 110 im Schritt S113 ist in 11 dargestellt.

-

Zu einer Zeit T1 können Bitleitungen BL mit der ersten Bitleitungsspannung VBL1 vorgeladen werden. Zu einer Zeit T2 können Spannungen an die Folgenansteuerungsleitungen SSL1 und SSL2, die Wortleitungen WL1 bis WL6, die Masseansteuerungsleitung GSL und die gemeinsame Source-Leitung CSL angelegt werden.

-