具体实施方式

以下参照附图详细说明本发明的实施例。

实施例1

参照图1,本发明实施例1的MRAM装置1响应来自外部的控制信号CMD和地址信号ADD进行随机存取,进行写入数据DIN的输入和读出数据DOUT的输出。

MRAM装置1具有响应控制信号CMD,控制MRAM装置1全部工作的控制电路5和具有按n行×m列矩阵状配置的多个MTJ存储单元的存储器阵列10。存储器阵列10的构成后面将详细说明,配置了分别与MTJ存储单元的行对应的多条写入字线WWL和读出字线RWL。并且,配置了分别与MTJ存储单元的列对应地设置的折叠型位线对。位线对由位线BL和/BL构成。下面将位线BL和/BL的组总称为位线对BLP。

MRAM装置1还具有:根据由地址信号ADD表示的行地址RA进行存储器阵列10的行选择的行译码器20;根据由地址信号ADD表示的列地址CA进行存储器阵列10的列选择的列译码器25;根据行译码器20的行选择结果有选择地激活读出字线RWL和写入字线WWL的字线驱动器30;在数据写入时使数据写入电流流过写入字线WWL的字线电流控制电路40;以及在数据读出和数据写入时,使数据写入电流±Iw和读出电流Is通过的读出/写入控制电路50、60。

参照图2,存储器阵列10按n行×m列(n,m:自然数)配置,具有图41所示构成的MTJ存储单元MC。与MTJ存储单元的行(以下简称为存储单元行)对应,分别设置读出字线RWL1~RWLn和写入字线WWL1~WWLn。

与MTJ存储单元的列(以下简称为存储单元列)对应,分别设置构成位线对的位线BL1,/BL1~BLm,/BLm。

以下,在总括地表示写入字线、读出字线、位线和位线对时,分别使用符号WWL、RWL、BL(/BL)和BLP表示,在表示特定的写入字线、读出字线、位线和位线对时,在其符号中附加下标,如表示为RWL1、WWL1。

写入字线WWL1~WWLn通过字线电流控制电路40与接地电位Vss连接。这样,通过字线驱动器30,数据写入电流Ip流过激活为选择状态(高电位状态:电源电位Vcc)的写入字线WWL。

列译码器25根据列地址CA的译码结果,使分别与存储单元列对应地设置的列选择线CSL1~CSLm的其中之一激活为选择状态(H电平)。

数据I/O线对DI/OP传输数据写入时的数据写入电流±Iw和数据读出时的读出电流Is.即,在数据读出时和数据写入时被共有。数据I/O线对DI/OP包含数据线IO和/IO。

下面对读出/写入控制电路50中包含的列选择门电路CSG1~CSGm、数据写入电流控制电路51以及数据读出电路52的构成予以说明。

列选择门电路CSG1~CSGm分别与存储单元列对应地配置。列选择门电路CSG1~CSGm中的某一个根据列译码器25的列选择结果成为导通状态,将构成数据I/O线对DI/OP的数据线IO和/IO分别连接对应的位线BL和/BL。

例如,列选择门电路CSG1具有连接在数据线IO和位线BL1之间的晶体管开关和在数据线/IO和位线/BL1之间进行电连接的晶体管开关。这些晶体管开关根据列选择线CSL1的电位电平进行导通/关断。即,当列选择线CSL1激活为选择状态(H电平)时,列选择门电路CSG1将数据线IO,/IO分别与位线BL1和BL1电连接。分别与其他存储单元列对应地设置的列选择门电路CSG2~CSGm也有同样的构成。

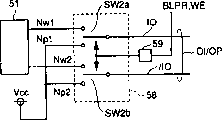

数据写入电流控制电路51响应数据写入时激活的控制信号WE而工作。

数据写入电流控制电路51包含:将一定电流供给内部节点Nwo的P型MOS晶体管151;构成用于控制晶体管151的通过电流的电流镜电路的P型MOS晶体管152和电流源153。

数据写入电流控制电路51还具有接受从内部节点Nwo供给的工作电流而工作的倒相器154、155和156。倒相器154将写入数据DIN的电位电平倒相并传输给内部节点Nw1。倒相器155将写入数据DIN的电位电平倒相并传输给倒相器156的输入节点。倒相器156将倒相器154的输出倒相并传输给内部节点Nw2。从而,数据写入电流控制电路51根据写入数据DIN的电位电平,将数据线IO和/IO的电位电平设定在电源电位Vcc或接地电位Vss。

数据读出电路52响应在数据读出时激活的控制信号RE而工作,输出读出数据DOUT。

数据读出电路52具有:接受电源电位Vcc并将一定电流分别供给内部节点Ns1和Ns2的电流源161和162;在内部节点Ns1和内部节点Nr1之间进行电连接的N型MOS晶体管163;在内部节点Ns2和内部节点Nr2之间进行电连接的N型MOS晶体管164;以及对内部节点Ns1和Ns2之间的电位电平差进行放大并输出读出数据DOUT的放大器165。

对晶体管163和164的栅提供参照电位Vref。电流源161和162的供给电流量和参照电位Vref,按照读出电流Is的电流量来设定。电阻166和167被设计成用于将内部节点Ns1和Ns2下拉到接地电位Vss。按照这种构成,数据读出电路52在数据读出时,将读出电流Is供给各数据线IO和/IO。根据通过列选择门电路和位线对连接的MTJ存储单元的存储数据电平,放大在数据线IO和/IO产生的电位差,输出读出数据DOUT。

读出/写入控制电路60夹住存储器阵列10,配置在列选择门电路CSG1~CSGm的相反一侧。

读出/写入控制电路60具有根据位线均衡化信号BLEQ而导通/关断的均衡化晶体管62-1~62-m。均衡化晶体管62-1~62-m分别与存储单元列对应地设置。例如,均衡化晶体管62-1与第1存储单元列对应地设置,响应位线均衡化信号BLEQ的激活(H电平),将位线BL1和/BL1进行电连接。

分别与其他存储单元列对应地设置的均衡化晶体管62-2~62-m也是一样,响应位线均衡化信号BLEQ的激活,在对应的存储单元列,将构成位线对的位线BL和/BL之间进行电连接。

位线均衡化信号BLEQ由控制电路5生成。位线均衡化信号BLEQ在MRAM装置1的备用期间、MRAM装置1的激活期间中,在存储器阵列10是非选择状态时以及在激活期间内的数据写入工作时,为了将构成按折叠型设置的位线对的位线BL和/BL在各存储单元列中短路,激活为H电平。

另一方面,在MRAM装置的激活期间中的数据读出工作时,位线均衡化信号BLEQ非激活为L电平。与此相呼应,在各存储单元列中,构成位线对的位线BL和/BL之间被断开。

首先,说明数据写入时的工作。以下,作为一个实例,将选择与列选择线CSL2对应的第2存储单元列的情况予以说明。

响应列选择结果,列选择线CSL2激活为选择状态(H电平),列选择门电路CSG2导通。这样,数据线IO和/IO分别与构成位线对BLP2的位线BL2和/BL2电连接。在数据写入时,均衡化晶体管62-2为导通状态,将位线BL2和/BL2之间短路。

如已经说明的一样,数据写入电流控制电路51将数据线IO和/IO的电位电平设定在电源电位Vcc或接地电位Vss。例如,当写入数据DIN的数据电平是L电平时,由于倒相器154和156的输出分别设定在电源电位Vcc(高电位状态)和接地电位Vss(低电位状态),则在数据线IO上流过用于写入L电平数据的数据写入电流-Iw。

数据写入电流-Iw通过列选择门电路CSG2供给位线BL2。传输给位线BL2的数据写入电流-Iw被均衡化晶体管62-2而转向,在另一条位线/BL2中作为反方向的数据写入电流+Iw被传输。位线/BL2中流过的数据写入电流+Iw通过列选择门电路CSG2传输给数据线/IO。

写入字线WWL1~WWLn中的某一条被激活为选择状态(H电平),流过数据写入电流Ip。从而,在列选择线CSL2对应的存储单元列中,对于在对应的写入数据线WWL中流过数据写入电流的MTJ存储单元进行数据写入。这时,对与位线BL2连接的MTJ存储单元MC,写入L电平数据,对与位线/BL2连接的MTJ存储单元MC,写入H电平数据。

另一方面,当写入数据DIN的数据电平是H电平时,内部节点Nw1和Nw2的电位电平的设定与上述情况相反,在位线BL2和/BL2中流过与上述方向相反的数据写入电流,写入与上述相反的数据电平。这样,具有按照写入数据DIN的数据电平的方向的数据写入电流±Iw被供给位线BL和/BL。

下面对数据读出予以说明。

MTJ存储单元MC在每1行中与位线BL和/BL的其中之一连接。例如,对属于第1存储单元列的MTJ存储单元予以说明,第1行的MTJ存储单元与位线BL1连接,第2行的MTJ存储单元与位线/BL1连接。以下同样,各MTJ存储单元,在奇数行与位线对的BL1~BLm连接,在偶数行与位线对的/BL1~/BLm连接。

其结果,当读出字线RWL根据行选择结果有选择地激活时,位线对的BL1~BLm和位线对的/BL1~/BLm的其中之一与MTJ存储单元MC连接。

存储器阵列10还有分别与位线BL1、/BL1~BLm、/BLm连接的多个虚设存储单元DMC。虚设存储单元与虚设读出字线DRWL1和DRWL2的其中之一连接,按2行×m列配置。与虚设读出字线DRWL1连接的虚设存储单元,分别与位线BL1、BL2~BLm连接。另外,与虚设读出字线DRWL2连接的剩余的虚设存储单元分别与位线/BL1、/BL2~/BLm连接。

虚设读出字线DRWL1和DRWL2有选择地激活,以便将在位线对的BL1~BLm和位线对的/BL1~BLm中的与属于被选择的存储单元行的MTJ存储单元MC非连接的一方,分别与虚设存储单元DMC连接。

其结果,位线对的BL1~BLm和位线对的/BL1~/BLm分别与被选择的存储单元行对应的m个MTJ存储单元和m个虚设存储单元连接。

如已经说明的一样,数据读出电路52对数据线IO和/IO供给同一方向的读出电流Is。

对在数据读出时选择了与列选择线CSL2对应的第2存储单元列的情况予以说明。

列选择线CSL2被激活为选择状态(H电平),列选择门电路CSG2导通。据此,构成数据I/O线对DI/OP的数据线IO和/IO与数据写入时同样,分别与位线BL2和/BL2连接。

然而,在数据读出时,由于均衡化晶体管62-2关断,故从数据读出电路52供给的读出电流Is按同一方向流过位线BL2和/BL2。

读出字线RWL1~RWLn的其中之一被激活为选择状态(H电平),对应的MTJ存储单元与位线BL2和/BL2其中一个连接。并且,虚设读出字线DRWL1和DRWL2中的某一个被激活,与MTJ存储单元非连接的位线BL2和/BL2的其中另一个与虚设存储单元DMC连接。

在根据行选择结果,选择奇数行,位线BL2与MTJ存储单元MC连接时,虚设读出字线DRWL2被激活,位线/BL2与虚设存储单元DMC连接。反之,在根据行选择结果选择偶数行,位线/BL2与MTJ存储单元MC连接时,虚设读出字线DRWL1被激活,位线BL2与虚设存储单元DMC连接。

如已经说明的一样,MTJ存储单元MC的电阻值随存储数据电平而变化。这里,在存储H电平数据时的MTJ存储单元MC的电阻值为Rh,在存储L电平数据时的MTJ存储单元MC的电阻值为RI,则将虚设存储单元DMC的电阻值Rd设定在RI和Rh的中间值。这样,通过将在和虚设存储单元连接的位线上产生的电位变化与在和MTJ存储单元MC连接的位线上产生的电位变化进行比较,即可检测作为数据读出对象的存储数据的电平。

在位线BL2和/BL2之间产生的电位差通过数据I/O线对DI/OP传输给数据读出电路52中的内部节点Ns1和Ns2。通过放大器165,内部节点Ns1和Ns2的电位电平差被放大,并作为读出数据DOUT输出。

因而,在与位线BL连接的MTJ存储单元中存储L电平数据时,以及在与位线/BL连接的MTJ存储单元MC中存储H电平数据时,在读出数据DOUT中都输出L电平。反之,在与位线BL连接的MTJ存储单元中存储H电平数据时,以及在与位线/BL连接的MTJ存储单元MC中存储L电平数据时,在读出数据DOUT中都输出H电平。

这样,与各存储单元列对应地配置折叠型位线对BLP,通过用均衡化晶体管使数据写入电流转向,只通过将各位线BL和/BL一端的电位电平控制在电源电位Vcc或接地电位Vss,即可供给不同方向的数据写入电流。因此,不必形成极性不同的电位(负电位),仅通过将数据线IO和/IO的电位设定在电源电位或接地电位,电流的方向即被转换,故可使数据写入电流控制电路51的电路构成简化。读出/写入控制电路60也可以仅用均衡化晶体管62-1~62-m简单地形成。

同时,由于用虚设存储单元进行数据读出,则在设置折叠型位线对BLP的构成中,可高效率地配置MTJ存储单元。

实施例2

参照图3,在实施例2的存储器阵列10中,与实施例1同样,在各存储单元列,设置折叠型位线对,在读出/写入控制电路60中,设置均衡化晶体管62-1~62-m。

在实施例2中,在数据写入时供给数据写入电流,对于激活数据写入电流控制电路51和字线WWL的字线驱动器30,对MRAM装置1直接供给从外部供给的外部电源电位Ext.Vcc.

MRAM装置1还具有使外部电源电位Ext.Vcc降压并生成内部电源电位Int.Vcc的电压降低电路(VDC:Voltage Down Converter)55。

电压降低电路55生成的内部电源电位Int.Vcc供给进行数据读出电路52、列译码器25、控制电路5、行译码器20等的数据读出和地址处理的内部电路。在数据读出时和数据写入时的各部分工作与实施例l同样,不再重复详细说明。

采用这种构成,在数据写入时,通过利用从外部施加的外部电源电压Ext.Vcc来驱动供给比较大的数据写入电流±Iw的数据写入电流控制电路51和将数据写入电流Ip供给写入字线WWL的字线驱动器30,可迅速供给这些数据写入电流。

另外,通过由已被降压的内部电源电位Int.Vcc来驱动供给数据写入电流的电路以外的内部电路,可以减少这些内部电路的功耗,并可确保与高集成化的装置的微细化对应的可靠性。

实施例3

在实施例1中,示出了在沿行方向配置的数据I/O线对DI/OP的一端分别连接数据写入电流控制电路51的输出节点Nw1及Nw2与数据线IO及/IO的构成。然而,在这种构成中,与选择的存储单元列对应,数据写入电流±Iw的路径长度变化了。

例如,在图2所示的构成中,在列选择线CSL1一侧,由于数据写入电流控制电路51的输出节点Nw1及Nw2和数据线IO及/IO分别连接,故在选择列选择线CSL1时的数据写入电流的路径长度变短了,而相反侧的列选择线CSLm在选择状态被激活时的数据写入电流的路径长度变长了。这样,由于根据被选择的存储单元列,传输数据写入电流的布线长度变化,故数据写入电流的路径电阻值变化,数据写入电流的电流量也变化了。其结果,根据存储单元列,在写入工作的容限方面产生了差别。

因而,在选择时数据写入电流的路径长度变长的存储单元列中,具有写入容限不足产生的可能性。然而,若与最担心写入容限不足的存储单元列(例如,在图2中包含的位于存储器阵列一端的第1列和第m列,或者包含由于存储单元的特性离散而形成容限不足的存储单元的存储单元列)相一致地设定数据写入电流,则在其他存储单元列的数据写入时,将所设定的数据写入电流大于必须的数据写入电流,浪费了功耗。

参照图4,在实施例3的构成中,数据写入电流控制电路5 1分别在最前面的存储单元列(第1列)一侧和最后面的存储单元列(第m列)一侧,分别与构成数据I/O线对DI/OP的数据IO和/IO连接。

采用这种构成,可与作为列选择对象的存储单元列的位置无关,使由节点Nw1(数据写入电流控制电路51)~数据线IO~位线BL~均衡化晶体管~位线/BL~数据线/IO~节点Nw2形成的数据写入电流±Iw的路径长度一定,防止电阻值变动,可将数据写入电流±Iw的电流值维持在一定电平。

这样,除了实施例1已说明的效果外,即使对于某个存储单元列抑制了无用的功耗,也可恰当地设定写入工作容限。

实施例3的变形例1

参照图5,在实施例3的变形例1中,在整个存储器阵列10中,设置多个数据I/O线对DI/OP。各数据I/O线对DI/OP被配置在每M个(M:自然数)存储单元列中。图5中,表示M=2时、即每2个存储单元列配置1对数据I/O线对DI/OP的构成。

图5中,代表性表示在这些数据I/O线对DI/OP中的对于第1列和第2列设置的数据I/O线对DI/OPa和对于第3列和第4列设置的数据I/O线对DI/OPb。

数据写入电流控制电路51和数据读出电路52与各数据I/O线对对应地设置。例如,与数据I/O线对DI/OPa对应,配置数据写入电流控制电路51a和数据读出电路52a。即,数据写入电流控制电路51和数据读出电路52,在全部存储器阵列10中各设置(m/M)个。

从这些数据写入电流控制电路51和数据读出电路52中,各激活与选择的存储单元列对应的1个,进行数据写入电流±Iw和读出电流Is的供给。其他部分的构成和工作与实施例1同样,不再重复详细说明。

这样,通过在每M个存储单元列中分段配置数据I/O线对DI/OP,可以有效防止通过数据写入电流的布线长度变化随作为列选择对象的存储单元列的位置而引起的电流电平变化,可以享受到与实施例3同样的效果。

实施例3的变形例2

参照图6,实施例3的变形例2与图4所示实施例3的构成相比较,其差别是:数据写入电流控制电路51的输出节点Nw1和Nw2在数据I/O线对DI/O的中央部分别与数据线IO和/IO电连接。

采用这种构成,可以防止因作为列选择对象的存储单元列的位置而引起的数据写入电流路径的电阻值变化,能够享受到与实施例3同样的效果。

实施例3的变形例3

参照图7,实施例3的变形例3与图5说明的实施例3的变形例1的情况同样,在每M个存储单元列中配置独立的数据输入输出线DI/OP。数据I/O线对DI/OP的配置数目和与其对应的数据写入电流控制电路51及数据读出电路52的配置和选择,已在图5中说明了,不再重复说明。

在实施例3的变形例3中,各数据I/O线对DI/OP被配置在对应的M个存储单元列的中央部。图7中,作为一个例子说明了M=2的情况,与第1列和第2列对应地设置的数据I/O线对DI/OPa被配置在存储单元列的第1列和第2列之间。

采用这种构成,与实施例3的变形例1的构成进行比较,进一步控制了依存于作为列选择对象的存储单元列的位置的数据写入电流的变动,对于任何存储单元列都可以进一步恰当地设定写入工作容限。

实施例4

在实施例1到3中,对于MTJ存储单元MC,已经说明了由共同的位线BL供给数据写入电流±Iw和读出电流Is的构成。

然而,由于数据写入电流±Iw和读出电流Is的电流量大不相同,故将位线BL分开地配置在数据读出时用于流过读出电流的读出位线RBL和在数据写入时用于流过数据写入电流±Iw的写入位线WBL中也是有效的。

关于MTJ存储单元构成的变化将在后面详细说明,在实施例4中说明当独立的配置流过数据写入电流±Iw的写入位线WBL时,与作为列选择对象的存储单元列的位置无关地用于抑制数据写入电流变动的构成。

参照图8,在实施例4的存储器阵列10中,与各存储单元列对应,设置形成用于流过数据写入电流±Iw的互补的写入位线对的WBL,/WBL。对于写入位线WBL,当总括表示时,用符号WBL表示,当表示特定的写入位线时,则在符号WBL中附加符号,表示为WBL1,/WBL1。

具有读出/写入控制电路60的均衡化晶体管62-1~62-m,在各存储单元列,电连接写入位线WBL和/WBL。均衡化晶体管62-1~62-m,与列选择门电路CSG1~CSGm同样,根据列选择线CSL1~CSLm的电位电平导通/关断。

采用这种构成,根据列选择结果,例如当列选择线CSL2被激活为选择状态(H电平)时,列选择门电路CSG2和均衡化晶体管62-2导通,形成节点Nw1(数据写入电流控制电路51)~数据线IO~写入位线WBL~均衡化晶体管62-2~写入位线/WBL2~数据线/IO~节点Nw2(数据写入电流控制电路51)的电流路径。

这样,对于形成写入位线对的互补的写入位线WBL和/WBL,由于流过由均衡化晶体管转向的反方向的数据写入电流,则可进行与实施例1同样的数据写入。

与图4所示的构成同样,数据写入电流控制电路51的内部节点Nw1和Nw2以及构成数据I/O线对DI/OP的数据线IO和/IO,分别连接在最前面的存储单元列(第1列)和最后面的存储单元列(第m列)。

因此,与作为列选择对象的存储单元列的位置无关的数据写入电流路径的布线长度即电阻值为一定值,可防止数据写入电流的变动。这样,与实施例3同样,对于各存储单元列,不会产生无用的功耗,可确保恰当的写入容限。

实施例4的变形例1

参照图9,实施例4的变形例1与图5的情况同样,数据I/O线对DI/OP按每M个存储单元列配置。数据写入电流控制电路51也在整个存储器阵列10中分别与(m/M)组配置的数据I/O线对DI/OP对应地配置。均衡化晶体管62-1~62-m与图8的情况同样,根据列选择线CSL1~CSLm的电位电平导通/关断,进行与实施例1同样的数据写入。

采用这样的构成,在将位线BL分开配置为读出位线RBL和写入位线WBL时,也可以享受到与实施例3的变形例1同样的效果。

实施例4的变形例2

参照图10,实施例4的变形例2与图6所示的构成同样,在各存储单元列中共同设置的数据I/O线对DI/OP的中央部,将数据线IO和/IO分别与数据写入电流控制电路51的输出节点Nw1和Nw2连接。均衡化晶体管62-1~62-m与图8的情况同样,根据列选择线CSL1~CSLm的电位电平导通/关断,进行与实施例1同样的数据写入。

采用这种构成,在将位线BL分开配置为读出位线RBL和写入位线WBL时,也可以得到与实施例3的变形例2同样的效果。

实施例4的变形例3

参照图11,实施例4的变形例3与图7的情况同样,数据I/O线对DI/OP按每M个存储单元列配置,各数据I/O线对DI/OP部配置在对应的M个存储单元列的中央部。均衡化晶体管62-1~62-m与图8的情况同样,根据列选择线CSL1~CSLm的电位电平导通/关断,进行与实施例1同样的数据写入。

采用这种构成,在将位线BL分开配置为读出位线RBL和写入位线WBL时,也可以得到与实施例3的变形例2同样的效果。

在实施例4和其变形例1到3中,省略了有关数据读出的构成的说明,与实施例1到3同样,可以根据在读出字线RBL产生的电位变化,进行使用了虚设存储单元DMC的数据读出。

在实施例1到4中,示出了使用虚设存储单元DMC进行数据读出、MTJ存储单元MC在各位线BL和/BL按每1行配置的构成,但也可在位线BL和/BL与字线的各交点处配置MTJ存储单元MC。这时,不设置虚设存储单元DMC也可以进行数据读出。

这样,由于在各存储单元行与位线BL、/BL的各交点处配置MTJ存储单元,故对于1位的存储数据配置2个MTJ存储单元。采用这种构成,响应读出字线RWL的激活,对于位线BL和/BL,分别连接存储互补的数据电平的2个MTJ存储单元。因此,由于通过比较由存储这些互补数据的MTJ存储单元产生的电位变化的差别设定读出数据的数据电平,故与使用虚设存储单元DMC检测读出数据DOUT的数据电平的情况进行比较,可充分地确保读出容限。

实施例5

参照图12,在实施例5中,与各存储单元列对应,配置非折叠型的开放型位线。即,与m个存储单元列对应,分别设置位线BL1~BLm。

MTJ存储单元MC在各存储单元行中被配置在每个与位线BL的交点。形成数据I/O线对DI/OP的数据线IO和/IO,与存储器阵列10在列方向邻接,被配置成分别夹住存储器阵列10地而对置。

列选择门电路CSG1~CSGm由列选择线CSL1~CSLm控制导通/关断,与数据I/O线对DI/OP之一的数据线IO对应的位线BL连接。

读出/写入控制电路60具有在位线BL1~BLm与数据I/O线对DI/OP之另一个的数据线/IO之间分别连接的电流控制晶体管64-1~64-m。电流控制晶体管64-1~64-m也与列选择门电路CSG1~CSGm同样,分别根据列选择线CSL1~CSLm导通/关断。

在数据写入电流控制电路51和数据读出电路52与数据I/O线对DI/OP之间,设置电流转换电路56。电流转换电路56有选择地将来自数据写入电流控制电路51的数据写入电流±Iw和来自数据读出电路52的读出电流Is供给数据I/O线对DI/OP。

参照图13,电流转换电路56具有用于有选择地连接数据写入电流控制电路51的输出节点Nw1和数据读出电路52的输出节点Nr1的其中之一与数据线IO的开关SW1a和有选择地将数据写入电流控制电路51的输出节点Nw2和电源电位Vcc的其中之一与数据线/IO连接的开关SW1b。

开关SW1a和SW1b根据共同的控制信号RWS工作。即,在数据读出时,根据控制信号RWS,开关SW1a和SW1b分别将数据读出电路52的输出节点Nr1和电源电位Vcc与数据线IO和/IO连接。

在实施例5中,数据读出电路52在将数据线/IO上拉到电源电位Vcc的状态下使读出电流Is流过数据线IO,将在数据线IO产生的电压降与作为基准的电压降低量ΔVr进行比较,检测读出数据DOUT的数据电平。ΔVr设定为ΔVh和ΔV1的中间值,其中:ΔVh为读出H电平数据时的数据线IO的电压降,ΔV1为读出L电平数据时的数据线IO的电压降。

数据读出控制电路的构成是在图2所示的数据读出电路52的构成中省略晶体管164和将节点Nr2与电源电位Vcc连接并设定电阻167的电阻值以使内部节点Ns2的电位电平为(Vcc-ΔVr)而实现的。

另外,在数据写入时,根据控制信号RWS,开关SW1a和SW1b将数据写入电流控制电路51的输出节点Nw1和Nw2分别与数据线IO和/IO连接。

再参照图12,在数据写入时,在节点Nw1(数据写入电流控制电路51)~数据线IO~位线BL~数据线/IO~节点Nw2(数据写入电流控制电路51)的路径上可以流过数据写入电流。在配置开放型位线的构成中,与实施例1同样,仅将数据写入电流控制电路51的输出节点Nw1和Nw2的电位电平控制在电源电位Vcc和接地电位Vss的其中之一,即可供给不同方向的数据写入电流。这样,不必产生极性不同的电位(负电位)即可简化数据写入电流控制电路51的电路构成。读出/写入控制电路60同样可以仅由电流控制晶体管64-1~64-m简单地形成。

数据写入电流控制电路51和形成数据I/O线对DI/OP的数据线IO及/IO,分别连接在最前面的存储单元列(第1列)一侧和最后面的存储单元列(第m列)一侧。因而,与实施例3和4同样,可与作为列选择对象的存储单元列的位置无关地将数据写入电流路径的布线长度即电阻值维持在一定值。可其结果,防止数据写入电流的变动,不导致无用功耗而确保对各存储单元的适当的写入容限。

实施例5的变形例

图14是表示存储器阵列10及其周边的实施例5的变形例构成的方框图。

参照图14,实施例5的变形例与图12的构成相比较,其不同是:读出/写入控制电路60包含的电流控制晶体管64-1~64-m根据位线预充电信号BLPR而导通/关断。位线预充电信号BLPR的信号电平被设定为与已说明的位线均衡化信号BLEQ一样。

代替电流转换电路56的电流转换电路58连接在数据写入电流控制电路51和数据I/O线对DI/OP之间。数据读出电路52响应控制信号RE而工作,并将读出电流I s供给数据I/O线对之一的数据线IO。

图15是表示电流转换电路58构成的方框图。

参照图15,电流转换电路58具有在数据写入电流控制电路51的输出节点Nw1和供给电源电位Vcc的预充电节点Np1与数据线IO之间配置的开关SW2a和在数据写入电流控制电路51的输出节点Nw2和供给电源电位Vcc的预充电节点Np2与数据线/IO之间配置的开关SW2b。

开关SW2a和SW2b在数据写入时分别将数据线IO和/IO与数据写入电流控制电路51的输出节点Nw1和Nw2电连接。并且,开关SW1b和SW2b在数据读出之前进行的预充电工作时,将数据线IO和/IO与预充电节点Np1和Np2分别进行电连接。

然而,在数据读出时,预充电的数据线IO和/IO通过开关SW1b和SW2b使数据写入电流控制电路51的输出节点Nw1,Nw2与预充电节点Np1,Np2都断开。

开关控制电路59根据已经说明的控制信号WE和位线预充电信号BLPR的信号电平判断是数据写入时、数据读出时和预充电工作时哪种情况,控制开关SW2a和SW2b的连接。

采用这种构成,在数据读出时,使位线预充电信号BLPR非激活为L电平,关断电流控制晶体管64-1~64-m,并使数据线IO和/IO与数据写入电流控制电路51和预充电节点Np1、Np2都断开。

利用具有与实施例5同样构成的数据读出电路52,通过与数据线IO和选择的存储单元列对应的列选择门电路,对位线BL供给读出电流Is。根据写入字线RWL的激活,利用与位线连接的MTJ存储单元MC,将在位线BL产生的电压降与基准电压降ΔVr进行比较,数据读出电路52即可检测读出数据DOUT的数据电平。

另外,在数据写入时,位线预充电信号BLPR被激活为H电平,电流控制晶体管64-1~64-m导通。因而,在选择的存储单元列中,形成节点Nw1(数据写入电流控制电路51)~数据线IO~位线BL~电流控制晶体管~数据线/IO~节点Nw2(数据写入电流控制电路51)的电流路径,可以使按照写入数据DIN的数据电平的数据写入电流±Iw流过位线BL。这样,即可进行与实施例5同样的数据写入工作。

实施例6

在实施例6中,将说明对于MTJ存储单元MC设置的布线的配置的变型。

参照图16,本发明实施例6的MRAM装置2与MRAM装置1同样,响应来自外部的控制信号CMD和地址信号ADD进行随机存取,进行写入数据DIN的输入和读出数据DOUT的输出。存储器阵列10具有n行×m列矩阵状配置的多个MTJ存储单元。存储器阵列10的构成后面将详细说明,分别与存储单元行对应地配置多条读出字线RWL和写入位线WBL,分别与存储单元列对应地配置多条写入字线WWL和读出位线RBL。

这样,在实施例6中,将流过数据写入电流±Iw和读出电流Is的位线BL分开为在数据读出时流过读出电流Is的读出位线RBL和在数据写入时流过数据写入电流±Iw的写入位线WBL。并且,读出字线RWL和写入字线WWL按相互不同的方向配置。

MRAM装置2具有:根据由地址信号ADD表示的行地址RA,进行存储器阵列10的行选择的行译码器20;根据由地址信号ADD表示的列地址CA,进行存储器阵列10的列选择的列译码器25;根据行译码器20的行选择结果,在数据读出时有选择地激活读出字线RWL的读出字线驱动器30r;根据行译码器20的行选择结果,在数据写入时,使数据写入电流流过写入位线WBL的写入控制电路50w和60w;根据列译码器25的列选择结果,在数据写入时有选择地激活写入字线WWL的写入字线驱动器30w;使数据写入电流流过被激活的写入字线WWL的字线电流控制电路40;以及在数据读出时将读出电流Is供给读出位线RBL的读出控制电路50r。

写入控制电路50w同时具有已在实施例1说明的数据写入电流控制电路51的功能和进行行选择的选择门电路的功能。写入控制电路60w与写入控制电路50w协调地工作,根据写入数据DIN的数据电平,通过控制存储器阵列10两端部的写入位线WBL的两端的电位来控制数据写入电流±Iw的方向。

读出控制电路50r同时具有图2已说明的数据读出电路52的功能和进行列选择的列选择门电路CSG1~CSGm的功能。

字线电流控制电路40,为了使数据写入电流流过激活为选择状态(高电位状态:H电平)的写入字线WWL,将各写入字线WWL与接地电位Vss连接。

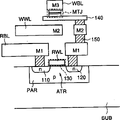

参照图17,实施例6的存储器阵列10具有n行×m列配置的多个MTJ存储单元MC。在实施例6的构成中,对于各MTJ存储单元MC配置读出字线RWL、写入字线WWL、读出位线RBL和写入位线WBL。读出字线RWL和写入位线WBL分别与存储单元行对应并按照行方向配置。写入字线WWL和读出位线RBL分别与存储单元列对应并按照列方向配置。

其结果,在整个存储器阵列10中,设置了读出字线RWL1~RWLn、写入字线WWL1~WWLm、读出位线RBL1~RBLm以及写入位线WBL1~WBLn。

以下,当总括地表示读出位线时,用RBL作为表示符号,当表示特定的读出位线时,在这些符号上附加下标,表示为RBL1,RBLm。

字线电流控制电路40将写入字线WWL1~WWLm与接地电位Vss连接。这样,当通过写入字线驱动器30w使写入字线WWL激活为选择状态(H电平:电源电位Vcc)时,可使数据写入电流Ip流过已激活的写入字线WWL。

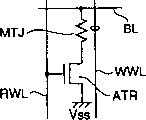

参照图18,在实施例6的MTJ存储单元中,对于由磁隧道结部MTJ和存取晶体管ATR组成的MTJ存储单元,设置读出字线RWL、写入字线WWL、写入位线WBL和读出位线RBL。如已经说明的一样,代表性应用在半导体衬底上形成的场效应晶体管的MOS晶体管作为存取晶体管ATR。

存取晶体管ATR的栅与读出字线RWL连接。存取晶体管ATR在读出字线RWL激活为选择状态(H电平:电源电位Vcc)时导通,形成包含磁隧道结部MTJ的电流路径。另外,当读出字线RWL非激活为非选择状态(L电平:接地电位Vss)时,由于存取晶体管ATR关断,故不形成包含磁隧道结部MTJ的电流路径。

写入字线WWL和写入位线WBL以与磁隧道结部MTJ邻近的方式在相互正交方向上配置。这样,由于在相互正交方向上配置读出字线RWL和写入字线WWL,故可以分开配置读出字线驱动器30r和写入字线驱动器30w。由于读出字线RWL和写入字线WWL在数据读出时和数据写入时分别独立地激活,故这些驱动器可以作为本来独立的装置来设计。因而,将写入字线驱动器30w和读出字线驱动器30r分开并小型化,由于可把每个驱动器配置在与存储器阵列10邻接的不同区中,故可提高布局的自由度,减少布局面积即MRAM装置的芯片面积。

磁隧道结部MTJ在读出位线RBL和存取晶体管ATR之间电连接。因而,在数据读出时,通过将不必流过电流的写入位线WBL的电位电平设定在接地电位Vss,响应存取晶体管ATR的导通,故形成读出位线RBL~磁隧道结部MTJ~存取晶体管ATR~写入位线WBL(接地电位Vss)的电流路径。通过在该电流路径中流过读出电流Is,在读出位线RBL中产生与磁隧道结部MTJ的存储数据电平对应的电位变化,可以读出存储数据。

在数据写入时,写入字线WWL和写入位线WBL中分别流过数据写入电流,在由这些数据写入电流分别产生的磁场的和达到超过一定磁场即图44所示的星状特性线的区时,在磁隧道结部MTJ中写入存储数据。

下面用图19说明对于实施例6的MTJ存储单元的数据写入和数据读出。

首先,说明数据写入时的工作。

写入字线驱动器30w根据列译码器25的列选择结果,将与选择列对应的写入字线WWL的电位驱动为选择状态(H电平)。在非选择列中,写入字线WWL的电位电平维持在非选择状态(L电平)。通过字线电流控制电路40,各写入字线WWL与接地电位Vss连接,故在选择列中,数据写入电流Ip流过写入字线WWL。

读出字线RWL在数据写入时维持在非选择状态(L电平)。在数据写入时,读出控制电路50r不供给读出电流Is,将读出位线RBL预充电到高电位状态(Vcc)。并且,由于存取晶体管ATR维持关断状态,故在数据写入时,在读出位线RBL上不流过电流。

写入控制电路50w和60w通过控制在存储器阵列10两端的写入位线WBL的电位,产生按照写入数据DIN的数据电平方向的数据写入电流。例如,当写入“1”的存储数据时,将写入控制电路60w侧的位线电位设定在高电位状态(电源电位Vcc),将相反侧的写入控制电路50w侧的位线电位设定在低电位状态(接地电位Vss)。这样,在从写入控制电路60w朝向50w的方向上,数据写入电流+Iw流过写入位线WBL。另外,当写入“0”的存储数据时,将写入控制电路50w侧和60w侧的位线电位分别设定在高电位状态和低电位状态,在从写入控制电路50w朝向60w的方向上,数据写入电流-Iw流过写入位线WBL。这时,数据写入电流±Iw根据行译码器20的行选择结果,有选择地流过与选择行对应的写入位线WBL。

这样,通过设定数据写入电流Ip和±Iw的方向,在数据写入时,根据写入的存储数据的电平“1”、“0”,选择方向相反的数据写入电流+Iw和-Iw的其中之一,即可与数据电平无关地将写入字线WWL的数据写入电流Ip固定在一定方向。这样,由于可常时地使流过写入字线WWL的数据写入电流Ip的方向一定,故如已经说明的一样,可以简化字线电流控制电路40的构成。

下面说明数据读出时的工作。

在数据读出时,写入字线WWL维持在非选择状态(L电平),其电位电平由字线电流控制电路40固定在接地电位Vss。在数据读出时,写入控制电路50w和60w停止使写入位线WBL设定在接地电位Vss的数据写入电流的供给。

另外,读出字线驱动器30r根据行译码器20的行选择结果,将与选择行对应的读出字线RWL驱动在选择状态(H电平)。在非选择行中,读出字线RWL的电位电平维持在非选择状态(L电平)。读出控制电路50r在数据读出时,将进行数据读出的一定量的读出电流Is供给选择列的读出位线RBL。由于读出位线RBL在数据读出前预充电为高电于预充电位状态(Vcc),故通过响应读出字线RWL激活的存取晶体管ATR的导通,在MTJ存储单元内形成读出电流Is的电流路径,在读出位线RBL中产生根据存储数据的电位变化(降低)。

在图19中,在作为一例的存储的数据电平是“1”的情况下,当固定磁性层FL和自由磁性层VL的磁场方向同一时,在存储数据是“1”时读出位线RBL的电位变化ΔV1较小,在存储数据是“0”时读出位线RBL的电位变化ΔV2大于ΔV1。通过检测这些电位降低ΔV1和ΔV2的差,即可读出MTJ存储单元的存储数据。

并且,在读出位线RBL中,由于使具有数据读出的预充电电压和数据写入时的设定电压与同一电源电压Vcc一致,故可使数据读出开始时的预充电工作的效率高,从而达到数据读出工作的高速化。

参照图20,实施例6的MTJ存储单元中,存取晶体管ATR在半导体主衬底SUB上的P型区PAR形成。写入位线WBL在第1金属布线层M1形成,与存取晶体管ATR的源/漏区之一110电连接。另一源/漏区120,经由在第1金属布线层M1上设置的金属布线、阻挡层金属140以及在接触孔形成的金属膜150,与磁隧道结部MTJ电连接。

读出位线RBL设置在第2金属布线层M2中,以便与磁隧道结部MTJ电连接。写入字线WWL配置在第3金属布线层M3中。写入字线WWL,由于可不与MTJ存储单元的其他部位连接而独立配置,故将其自由配置,以能提高与磁隧道结部MTJ之间的磁耦合。

采用这种构成,对于MTJ存储单元,在相互正交方向上配置读出字线RWL和写入字线WWL,故可独立配置分别与读出字线RWL和写入字线WWL对应的读出字线驱动器30r和写入字线驱动器30w,提高布局的自由度。并且,可防止数据读出时的字线驱动电流过大,防止产生不需要的磁噪声。

实施例6的变形例1

参照图21,存储器阵列10具有n行×m列配置的MTJ存储单元MC。分别与存储单元行对应地配置读出字线RWL和入位线WBL,分别与存储单元列对应地配置共同布线CML。共同布线CML是共有读出位线RBL和写入字线WWL的功能的布线。因此,在整个存储器阵列10中,配置了读出字线RWL1~RWLn、写入位线WBL1~WBLn以及共同布线CML1~CMLm。

字线电流控制电路40具有在共同布线CML1~CMLm和接地电位Vss之间分别连接的电流控制晶体管41-1~41-m。各个电流控制晶体管41-1~41-m,在数据写入时,为了使共同布线CML作为写入字线WWL工作,把各个共同布线CML1~CMLm与接地电位Vss连接。在数据写入时以外,电流控制晶体管41-1~41-m关断,共同布线CML与接地电位Vss断开。

这样,在实施例6的变形例1中,由于设置了电流控制晶体管41-1~41-m,故在数据读出时可将共同布线CML作为读出位线RBL使用,在数据写入时作为写入字线WWL使用。由于共同布线CML共有读出位线RBL和写入字线WWL的功能,故可削减布线数。

参照图22,存取晶体管ATR被电连接在磁隧道结部MTJ和写入位线WBL之间。磁隧道结部MTJ被连接在存取晶体管ATR和共同布线CML之间。存取晶体管ATR的栅与读出字线RWL连接。在图2的构成中,读出字线RWL和写入字线WWL在相互正交方向上配置。

用图23,对实施例6的变形例1的MTJ存储单元的数据写入和数据读出予以说明。

参照图23,在数据写入时,在写入位线WBL中流过数据写入电流±Iw。并且,通过电流控制晶体管41-1~41-m的导通,根据列选择结果,在与选择列对应的共同布线CML中流过数据写入电流Ip。这样,数据写入时的共同布线CML的电位和电流可与图19所示的写入字线WWL同样设定。因此,即可将按照写入数据DIN的数据电平的磁场写入磁隧道结部MTJ。如图19所示,读出位线RBL在数据写入时因无特别必要,可将两者合并在共同布线CML中。

在数据写入时以外,电流控制晶体管41-1~41-m关断。在数据读出前,共同布线CML预充电为接地电位Vss。

在数据读出时,将写入位线WBL的电位电平设定在接地电位电平Vss,通过激活为选择状态(H电平)读出字线RWL,存取晶体管ATR导通,故可在共同布线CML~磁隧道结部MTJ~存取晶体管ATR~写入位线WBL的路径上流过读出电流Is。

当读出电流Is的电流路径在MTJ存储单元内形成时,存储数据的电位变化(上升)在共同布线CML中产生。

图23中,作为一例在被存储的数据电平是“1”的情况下,当固定磁性层FL和自由磁性层VL的磁场方向同一时,存储数据是“1”时共同布线CML的电位变化ΔV1较小,存储数据是“0”时共同布线CML的电位变化ΔV2比ΔV1大。通过检测在共同布线CML中产生的电位变化ΔV1和ΔV2之差,即可读出MTJ存储单元的存储数据。

并且,在起到读出位线RBL的功能的共同布线CML中,由于使具有数据读出的预充电电压和数据写入时的设定电压与同一的接地Vss一致,故可使数据读出开始时的预充电工作的效率高,从而达到数据读出工作的高速化。

如图19所示,写入字线WWL在数据读出时因无特别必要,故可将写入字线WWL和读出位线RBL合并在共同布线CML中。

参照图24,在实施例6的变形例1的MTJ存储单元中,写入位线WBL被配置在第1金属布线层M1中,读出字线RWL与存取晶体管ATR的栅130被配置在同一层。

写入位线WBL与存取晶体管ATR的源/漏区110电连接。另一源/漏区120通过设置在第1金属布线层M1的金属布线、阻挡层金属140以及在接触孔设置的金属膜150,与磁隧道结部MTJ连接。

共同布线CML被设置在与磁隧道结部MTJ电连接的第2金属布线层M2中。这样,由于共同布线CML同时具备读出位线RBL和写入字线WWL的功能,增加了实施例6的MTJ存储单元所起的作用,故可削减布线数和金属布线层数,减少了制造成本。

实施例6的变形例2

参照图25,在实施例6的变形例2中,存储器阵列10具有n行×m列配置的MTJ存储单元MC。分别与存储单元行对应,设置读出字线RWL和写入位线WBL。并且,分别与存储单元列对应,设置读出位线RBL和写入字线WWL。因此,对于整个存储器阵列10,设置了读出字线RWL1~RWLn、写入位线WBL1~WBLn、读出位线RBL1~RBLm以及写入字线WWL1~WWLm。字线电流控制电路40将各写入字线WWL与接地电位Vss连接。

参照图26,在实施例6的变形例2的MTJ存储单元中,读出位线RBL通过存取晶体管ATR与磁隧道结部MTJ连接。磁隧道结部MTJ被连接在写入字线WWL和存取晶体管ATR之间。读出字线RWL与存取晶体管ATR的栅连接。在图26的构成中,读出字线RWL和写入字线WWL在相互正交方向上配置。

参照图27,在实施例6的变形例2的MTJ存储单元中,读出位线RBL被配置在第1金属布线层M1中。读出字线RWL与存取晶体管ATR的栅130在同一层形成。读出位线RBL与存取晶体管ATR的源/漏区110连接。源/漏区120通过在第1和第2金属布线层M1和M2设置的金属布线、阻挡层金属140以及在接触孔设置的金属膜150,与磁隧道结部MTJ连接。

写入位线WBL与磁隧道结部MTJ邻近并被设置在第2金属布线层M2中。写入字线WWL与磁隧道结部MTJ电连接,被配置在第3金属布线层M3中。

采用这种构成,读出位线RBL通过存取晶体管ATR与磁隧道结部MTJ连接。这样,读出位线RBL仅与属于作为数据读出对象即对应的读出字线RWL激活为选择状态(H电平)的存储单元行的MTJ存储单元MC电连接。其结果,抑制了读出位线RBL的电容量,可使数据读出工作高速化。

实施例6的变形例3

参照图28,实施例6的变形例3的存储器阵列10同样具有n行×m列配置的多个MTJ存储单元MC。实施例6的变形例3与图25~27所示的实施例6的变形例2比较,调换了写入字线WWL和读出位线RBL的配置。其他构成与实施例6的变形例2的情况一样,不再重复说明。

参照图29,实施例6的变形例3的MTJ存储单元与图26所示实施例6的变形例2的MTJ存储单元比较,调换了读出位线RBL和写入字线WWL的配置。其他布线的配置与图26一样,不再重复说明。对于这种构成,读出字线RWL和写入字线WWL可以在互相在正交方向上配置。

参照图30,实施例6的变形例3的MTJ存储单元与图27所示实施例6的变形例2的MTJ存储单元的结构比较,写入字线WWL和读出位线RBL的配置位置调换了。即,写入字线WWL被设置在第1金属布线层M1中,与存取晶体管ATR的源/漏区110连接。读出位线RBL被设置在与磁隧道结部MTJ电连接的第3金属布线层M3中。

这样,实施例6的变形例3中,由于读出位线RBL与磁隧道结部MTJ直接连接,故不可能实现实施例6的变形例2的数据读出工作的高速化。但是,在实施例6的变形例3的构成中,独立配置读出字线驱动器30r和写入字线驱动器30w,故可得到与实施例6同样的效果。

实施例6的变形例4

参照图31,实施例6的变形例4的存储器阵列10同样具有n行×m列配置的多个MTJ存储单元MC。分别与存储单元行对应地配置读出字线RWL和写入位线WBL,分别与存储单元列对应地配置共同布线CML。因此,对于整个存储器阵列10,配置了读出字线RWL1~RWLn、写入位线WBL1~WBLn以及共同布线CML1~CMLm。

字线电流控制电路40具有在共同布线CML1~CMLm和接地电位Vss之间分别电连接的电流控制晶体管41-1~41-m。各个电流控制晶体管41-1~41-m在数据写入时,将共同布线CML与接地电位Vss连接。在数据写入时以外,共同布线CML1~CMLm与接地电位Vss断开。在数据读出前,共同布线CML预充电为接地电位Vss。

参照图32,实施例6的变形例4的MTJ存储单元中,存取晶体管ATR被连接在共同布线CML和磁隧道结部MTJ之间。读出字线RWL与存取晶体管ATR的栅连接。写入位线WBL与读出字线RWL在同一方向配置,与磁隧道结部MTJ电连接。

共同布线CML在数据写入时与写入字线WWL一样,由写入字线驱动器30w有选择地激活。另外,在数据读出时,共同布线CML由读出控制电路50r供给读出电流Is。

在数据写入时,由于电流控制晶体管41-1~41-m的导通,在激活为选择状态(H电平)的共同布线CML中与写入字线WWL同样流过数据写入电流Ip。另外,在数据读出时,电流控制晶体管41-1~41-m关断,由于在共同布线CML~磁隧道结部MTJ~存取晶体管ATR~写入位线WBL(接地电位Vss)的路径中流过读出电流Is,故如图23的说明,在共同布线CML中产生与磁隧道结部MTJ的存储数据对应的电位变化。

因此,共同布线CML兼有在数据写入时的写入字线WWL功能和数据读出时的读出位线RBL功能,可以削减布线数。

并且,由于读出字线RWL与在数据写入时作为写入字线功能的共同布线CML在相互正交方向上配置,故可独立配置读出字线驱动器30r和写入字线驱动器30w,得到与实施例6同样的效果。

参照图33,实施例6的变形例4的MTJ存储单元中,共同布线CML被配置在第1金属布线层M1中,与存取晶体管ATR的源/漏区110电连接。读出字线RWL与存取晶体管ATR的栅130在同一层形成。

源/漏区120通过在第1金属布线层M1中形成的金属布线、阻挡层金属140以及在接触孔形成的金属膜150,与磁隧道结部MTJ连接。写入位线WBL配置在与磁隧道结部MTJ电连接的第2金属布线层M2中。

这样,采用通过存取晶体管ATR连接共同布线CML和磁隧道结部MTJ的构成,共同布线CML仅在存取晶体管ATR导通时与磁隧道结部MTJ连接。其结果,在数据读出时,削减了作为读出位线RBL功能的共同布线CML的电容,可进一步使数据读出工作高速化。

实施例6的变形例5

参照图34,实施例6的变形例5的存储器阵列10同样具有n行×m列配置的多个MTJ存储单元MC。分别与存储单元行对应地配置读出字线RWL和共同布线CML,分别与存储单元列对应地配置写入位线WBL.因此,对于整个存储器阵列10,设置了读出字线RWL1~RWLn、共同布线CML1~CMLn以及写入位线WBL1~WBLm。

字线电流控制电路40具有在共同布线CML1~CMLn和接地电位Vss之间分别电连接的电流控制晶体管41-1~41-n。各个电流控制晶体管41-1~41-n,在数据写入时连接共同布线CML和接地电位Vss。在数据写入时以外,共同布线CML1~CMLn与接地电位Vss断开。特别是在数据读出前,共同布线CML预充电于接地电位Vss。

参照图35,实施例6的变形例5的MTJ存储单元中,存取晶体管ATR被连接在写入位线WBL和磁隧道结部MTJ之间。读出字线RWL与存取晶体管ATR的栅连接。共同布线CML与读出字线RWL在同一方向上配置,与磁隧道结部MTJ电连接。

共同布线CML的工作与实施例6的变形例4一样,兼有在数据写入时的写入字线WWL的功能以及在数据读出时的读出位线RBL的功能。

因此,采用实施例6的变形例5的构成,由于共同布线CML和磁隧道结部MTJ直接电连接,故不能减少数据读出时的共同布线CML的电容,然而由于可将写入字线WWL和读出位线RBL汇集在共同布线CML上,故可削减制造时的金属布线层数,达到削减制成成本。

参照图36,实施例6的变形例5的MTJ存储单元中,写入位线WBL被配置在第1金属布线层M1中,与存取晶体管ATR的源/漏区110电连接。读出字线RWL与存取晶体管AR的栅130在同一层形成。源/漏区120通过在第1金属布线层M1形成的金属布线、阻挡层金属140以及在接触孔形成的金属膜150,与磁隧道结部MTJ连接。

共同布线CML被配置在与磁隧道结部MTJ电连接的第2金属布线层M2中。

实施例6的变形例6

参照图37,实施例6的变形例6的存储器阵列10具有n行×m列配置的多个MTJ存储单元MC。分别与存储单元行对应地配置读出字线RWL和写入位线WBL,分别与存储单元列对应地配置写入字线WWL和读出位线RBL.因此,在整个存储器阵列10,配置了读出字线RWL1~RWLn、写入位线WBL1~WBLn、写入位线RBL1~RBLm以及写入字线WWL1~WWLm。

参照图38,实施例6的变形例6的MTJ存储单元中,存取晶体管ATR的栅与读出字线RWL连接。存取晶体管ATR被电连接在读出位线RBL和磁隧道结部MTJ之间。磁隧道结部MTJ与和读出字线RWL同一方向配置的写入位线WBL连接。

将写入字线WWL在与写入位线WBL正交的方向上与磁隧道结部MTJ邻近设置。因此,可独立配置读出字线驱动器30r和写入字线驱动器30w,得到与实施例6同样的效果。

并且,由于写入字线WWL可不与MTJ存储单元的其他部位连接而独立配置,因此可按优先提高与磁隧道结部MTJ之间的磁耦合来配置。这样,可以抑制流过写入字线WWL的数据写入电流Ip,实现MRAM装置的低功耗。

同时,由于读出位线RBL通过存取晶体管ATR与磁隧道结部MTJ连接,故可削减在读出位线RBL上连接的磁隧道结部MTJ的数量,减低读出位线RBL的电容,使数据读出高速化。

参照图39,实施例6的变形例6的MTJ存储单元中,读出位线RBL被设置在第1金属布线层M1中,与存取晶体管ATR的源/漏区110电连接。读出字线RWL与存取晶体管ATR的栅130在同一层配置。存取晶体管ATR的源/漏区120通过设置在第1和第2金属布线层M1和M2的金属布线、阻挡层金属140以及在接触孔设置的金属膜150,与磁隧道结部MTJ连接。

磁隧道结部MTJ被配置在第2金属布线层M2和第3金属布线层M3之间。写入位线WBL与磁隧道结部MTJ电连接,并被配置在第3金属布线层M3中。写入字线WWL被设置在第2金属布线层中。这时,写入字线WWL的配置可以提高与磁隧道结部MTJ之间的磁耦合。

在图40所示的另一个构成中,按同一方向配置的读出位线RBL和写入字线WWL被配置在同一金属布线层中。磁隧道结部MTJ被设置在金属布线层M1和M2之间,写入字线WWL接近磁隧道结部MTJ,被配置在与读出位线RBL同一金属布线层M1。写入位线WBL与磁隧道结部MTJ电连接,被配置在第2金属布线层M2中。

因此,与图39所示的MTJ存储单元的结构比较,由于可减少金属布线层数,故除了由实施例6的变形例6产生的效果,还可以进一步削减制造成本。

如以上所述,在实施例6和其变形例1~4、6的MTJ存储单元的构成中,由于可将读出字线RWL和写入字线WWL在相互正交方向上配置,故可分开配置用于驱动各个字线的写入字线驱动器30w和读出字线驱动器30r,提高布局的自由度。

另外,在实施例6的变形例1、4和5的MTJ存储单元的构成中,由于将读出位线RBL和写入字线WWL汇集到共同布线CML中,故可削减布线数降低制造成本。

而且,在实施例6的变形例2,4和6的MTJ存储单元的构成中,由于通过存取晶体管ATR将读出位线RBL与磁隧道结部MTJ连接,故可抑制读出位线RBL的电容,使数据读出高速化。

以上,参照附图详细地说明了本发明,但这些说明始终是例示性的,而不是在任何意义上来限定本发明,本发明的要旨和范围只由后附的权利要求书来限定,包含与权利要求的范围均等的意义和范围内的全部的变更。