JP4726290B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP4726290B2 JP4726290B2 JP2000316867A JP2000316867A JP4726290B2 JP 4726290 B2 JP4726290 B2 JP 4726290B2 JP 2000316867 A JP2000316867 A JP 2000316867A JP 2000316867 A JP2000316867 A JP 2000316867A JP 4726290 B2 JP4726290 B2 JP 4726290B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- write

- read

- bit line

- line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 78

- 230000004044 response Effects 0.000 claims description 26

- 230000008878 coupling Effects 0.000 claims description 14

- 238000010168 coupling process Methods 0.000 claims description 14

- 238000005859 coupling reaction Methods 0.000 claims description 14

- 239000011159 matrix material Substances 0.000 claims description 11

- 244000062793 Sorghum vulgare Species 0.000 claims 5

- 235000019713 millet Nutrition 0.000 claims 5

- 238000005336 cracking Methods 0.000 claims 1

- 239000010979 ruby Substances 0.000 claims 1

- 229910001750 ruby Inorganic materials 0.000 claims 1

- 230000004048 modification Effects 0.000 description 100

- 238000012986 modification Methods 0.000 description 100

- 238000010586 diagram Methods 0.000 description 87

- 239000002184 metal Substances 0.000 description 64

- 230000000694 effects Effects 0.000 description 17

- 230000008859 change Effects 0.000 description 16

- 230000006870 function Effects 0.000 description 12

- 101100329534 Haloarcula marismortui (strain ATCC 43049 / DSM 3752 / JCM 8966 / VKM B-1809) csg1 gene Proteins 0.000 description 11

- 101100422777 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) SUR1 gene Proteins 0.000 description 11

- 101100166255 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CEP3 gene Proteins 0.000 description 10

- 230000004888 barrier function Effects 0.000 description 10

- 101150052142 CML1 gene Proteins 0.000 description 9

- 101100186490 Homo sapiens NAT8 gene Proteins 0.000 description 9

- 102100032394 N-acetyltransferase 8 Human genes 0.000 description 9

- 101100496428 Rattus norvegicus Cml6 gene Proteins 0.000 description 9

- 239000010408 film Substances 0.000 description 8

- 239000000758 substrate Substances 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 7

- 101100495436 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CSE4 gene Proteins 0.000 description 6

- 101100385368 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CSG2 gene Proteins 0.000 description 6

- 230000004913 activation Effects 0.000 description 6

- 102000000582 Retinoblastoma-Like Protein p107 Human genes 0.000 description 4

- 108010002342 Retinoblastoma-Like Protein p107 Proteins 0.000 description 4

- 230000003213 activating effect Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- 230000005669 field effect Effects 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 101000801068 Homo sapiens TM2 domain-containing protein 3 Proteins 0.000 description 1

- 102100033692 TM2 domain-containing protein 3 Human genes 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/14—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements

- G11C11/15—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements using multiple magnetic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1653—Address circuits or decoders

- G11C11/1655—Bit-line or column circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1653—Address circuits or decoders

- G11C11/1657—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1673—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1697—Power supply circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

- Semiconductor Memories (AREA)

Description

【発明の属する技術分野】

この発明は、薄膜磁性体記憶装置に関し、より特定的には、磁気トンネル接合(MTJ:Magnetic Tunneling Junction)を有するメモリセルを備えたランダムアクセスメモリに関する。

【0002】

【従来の技術】

低消費電力で不揮発的なデータの記憶が可能な記憶装置として、MRAM(Magnetic Random Memory)デバイスが注目されている。MRAMデバイスは、半導体集積回路に形成された複数の薄膜磁性体を用いて不揮発的なデータ記憶を行ない、薄膜磁性体の各々に対してランダムアクセスが可能な記憶装置である。

【0003】

特に、近年では磁気トンネル接合(MTJ:Magnetic Tunnel Junction)を利用した薄膜磁性体をメモリセルとして用いることによって、MRAM装置の性能が飛躍的に進歩することが発表されている。磁気トンネル接合を有するメモリセルを備えたMRAMデバイスについては、“A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell”, ISSCC Digest of Technical Papers, TA7.2, Feb. 2000.および“Nonvolatile RAM based on Magnetic Tunnel Junction Elements”, ISSCC Digest of Technical Papers, TA7.3, Feb. 2000.等の技術文献に開示されている。

【0004】

図41は、磁気トンネル接合部を有するメモリセル(以下単にMTJメモリセルとも称する)の構成を示す概略図である。

【0005】

図41を参照して、MTJメモリセルは、記憶データのデータレベルに応じて抵抗値が変化する磁気トンネル接合部MTJと、アクセストランジスタATRとを備える。アクセストランジスタATRは、電界効果トランジスタで形成され、磁気トンネル接合部MTJと接地電位Vssとの間に結合される。

【0006】

MTJメモリセルに対しては、データ書込を指示するためのライトワード線WWLと、データ読出を指示するためのリードワード線RWLと、データ読出時およびデータ書込時において記憶データのレベルに対応した電気信号を伝達するためのデータ線であるビット線BLとが配置される。

【0007】

図42は、MTJメモリセルからのデータ読出動作を説明する概念図である。

図42を参照して、磁気トンネル接合部MTJは、一定方向の固定磁界を有する磁性体層(以下、単に固定磁気層とも称する)FLと、自由磁界を有する磁性体層(以下、単に自由磁気層とも称する)VLとを有する。固定磁気層FLおよび自由磁気層VLとの間には、絶縁体膜で形成されるトンネルバリアTBが配置される。自由磁気層VLにおいては、記憶データのレベルに応じて、固定磁気層FLと同一方向の磁界および固定磁気層FLと異なる方向の磁界のいずれか一方が不揮発的に書込まれている。

【0008】

データ読出時においては、アクセストランジスタATRがリードワード線RWLの活性化に応じてターンオンされる。これにより、ビット線BL〜磁気トンネル接合部MTJ〜アクセストランジスタATR〜接地電位Vssの電流経路に、図示しない制御回路から一定電流として供給されるセンス電流Isが流れる。

【0009】

磁気トンネル接合部MTJの抵抗値は、固定磁気層FLと自由磁気層VLとの間の磁界方向の相対関係に応じて変化する。具体的には、固定磁気層FLの磁界方向と自由磁気層VLに書込まれた磁界方向とが同一である場合には、両者の磁界方向が異なる場合に比べて磁気トンネル接合部MTJの抵抗値は小さくなる。

【0010】

したがって、データ読出時においては、センス電流Isによって磁気トンネル接合部MTJで生じる電位変化は、自由磁気層VLに記憶された磁界方向に応じて異なる。これにより、ビット線BLを一旦高電位にプリチャージした状態とした後にセンス電流Isの供給を開始すれば、ビット線BLの電位レベル変化の監視によってMTJメモリセルの記憶データのレベルを読出すことができる。

【0011】

図43は、MTJメモリセルに対するデータ書込動作を説明する概念図である。

【0012】

図43を参照して、データ書込時においては、リードワード線RWLは非活性化され、アクセストランジスタATRはターンオフされる。この状態で、自由磁気層VLに磁界を書込むためのデータ書込電流がライトワード線WWLおよびビット線BLにそれぞれ流される。自由磁気層VLの磁界方向は、ライトワード線WWLおよびビット線BLをそれぞれ流れるデータ書込電流の向きの組合せによって決定される。

【0013】

図44は、データ書込時におけるデータ書込電流の方向と磁界方向との関係を説明する概念図である。

【0014】

図44を参照して、横軸で示される磁界Hxは、ライトワード線WWLを流れるデータ書込電流によって生じる磁界H(WWL)の方向を示す。一方、縦軸に示される磁界Hyは、ビット線BLを流れるデータ書込電流によって生じる磁界H(BL)の方向を示す。

【0015】

自由磁気層VLに記憶される磁界方向は、磁界H(WWL)とH(BL)との和が図中に示されるアステロイド特性線の外側の領域に達する場合においてのみ、新たに書込まれる。すなわち、アステロイド特性線の内側の領域に相当する磁界が印加された場合においては、自由磁気層VLに記憶される磁界方向は更新されない。

【0016】

したがって、磁気トンネル接合部MTJの記憶データを書込動作によって更新するためには、ライトワード線WWLとビット線BLとの両方に電流を流す必要がある。磁気トンネル接合部MTJに一旦記憶された磁界方向すなわち記憶データは、新たなデータ書込が実行されるまでの間不揮発的に保持される。

【0017】

データ読出動作時においても、ビット線BLにはセンス電流Isが流れる。しかし、センス電流Isは一般的に、上述したデータ書込電流よりは1〜2桁程度小さくなるように設定されるので、センス電流Isの影響によりデータ読出時においてMTJメモリセルの記憶データが誤って書換えられる可能性は小さい。

【0018】

上述した技術文献においては、このようなMTJメモリセルを半導体基板上に集積して、ランダムアクセスメモリであるMRAMデバイスを構成する技術が開示されている。

【0019】

【発明が解決しようとする課題】

図45は、行列状に集積配置されたMTJメモリセルを示す概念図である。

【0020】

図45を参照して、半導体基板上に、MTJメモリセルを行列状に配置することによって、高集積化されたMRAMデバイスを実現することができる。図45においては、MTJメモリセルをn行×m列(n,m:自然数)に配置する場合が示される。

【0021】

既に説明したように、各MTJメモリセルに対して、ビット線BL、ライトワード線WWLおよびリードワード線RWLを配置する必要がある。したがって、行列状に配されたn×m個のMTJメモリセルに対して、n本のライトワード線WWL1〜WWLnおよびリードワード線RWL1〜RWLnと、m本のビット線BL1〜BLmとを配置する必要がある。

【0022】

このように、MTJメモリセルに対しては、読出動作と書込動作とのそれぞれに対応して独立したワード線を設ける構成が一般的である。

【0023】

図46は、半導体基板上に配置されたMTJメモリセルの構造図である。

図46を参照して、半導体主基板SUB上のp型領域PARにアクセストランジスタATRが形成される。アクセストランジスタATRは、n型領域であるソース/ドレイン領域110,120とゲート130とを有する。ソース/ドレイン領域110は、第1の金属配線層M1に形成された金属配線を介して接地電位Vssと結合される。ライトワード線WWLには、第2の金属配線層M2に形成された金属配線が用いられる。また、ビット線BLは第3の金属配線層M3に設けられる。

【0024】

磁気トンネル接合部MTJは、ライトワード線WWLが設けられる第2の金属配線層M2とビット線BLが設けられる第3の金属配線層M3との間に配置される。アクセストランジスタATRのソース/ドレイン領域120は、コンタクトホールに形成された金属膜150と、第1および第2の金属配線層M1およびM2と、バリアメタル140とを介して、磁気トンネル接合部MTJと電気的に結合される。バリアメタル140は、磁気トンネル接合部MTJと金属配線との間を電気的に結合するために設けられる緩衝材である。

【0025】

既に説明したように、MTJメモリセルにおいては、リードワード線RWLはライトワード線WWLとは独立の配線として設けられる。また、ライトワード線WWLおよびビット線BLは、データ書込時において所定値以上の大きさの磁界を発生させるためのデータ書込電流を流す必要がある。したがって、ビット線BLおよびライトワード線WWLは金属配線を用いて形成される。

【0026】

一方、リードワード線RWLは、アクセストランジスタATRのゲート電位を制御するために設けられるものであり、電流を積極的に流す必要はない。したがって、集積度を高める観点から、リードワード線RWLは、独立した金属配線層を新たに設けることなく、ゲート130と同一の配線層において、ポリシリコン層やポリサイド構造などを用いて形成されていた。

【0027】

このように、MTJメモリセルを半導体基板上に集積化する場合は、メモリセルに必要とされる配線が多いことから、配線数および配線数が多くなり、製造コストが増大するという問題点がある。また、ビット線BLに多数のMTJメモリセルが常時接続される構成であるので、ビット線BLの寄生容量は比較的大きな値であり、リードワード線RWLがポリシリコン層やポリサイド構造によって形成されることと合わせて、読出動作の高速化が困難であった。

【0028】

また、データ書込時においても、ビット線BLに比較的大きなデータ書込電流を流す必要がある。また書込まれるデータのレベルに応じて、データ書込電流の方向を制御する必要があるため、データ書込電流を制御するための回路が複雑化するという問題点もあった。

【0029】

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、MTJメモリセルを有するMRAMデバイスにおいて、データ書込電流を供給するための制御回路の構成を簡素化して、製造コストの削減を図ることである。

【0030】

この発明の他の目的は、リードワード線およびライトワード線のドライブ回路を分割配置してレイアウトの自由度を向上させ、レイアウト面積すなわちチップ面積を減少させることである。

【0031】

この発明のさらに他の目的は、各メモリセルに必要な配線数を削減して、製造コストの削減を図ることである。

【0032】

【課題を解決するための手段】

請求項1記載の半導体集積回路は、複数行および複数列の行列状に配置された複数の磁性体メモリセルを有するメモリアレイを備え、複数の磁性体メモリセルの各々は、第1および第2のデータ書込電流によって印加されるデータ書込磁界が所定磁界よりも大きい場合に書込まれる記憶データのレベルに応じて異なる抵抗値を有する。半導体集積回路は、磁性体メモリセルの行にそれぞれ対応して設けられ、データ書込時において第1のデータ書込電流を流すためにアドレス選択結果に応じて選択的に活性化される書込ワード線と、磁性体メモリセルの列にそれぞれ対応して設けられたビット線対とを備え、ビット線対は、第1および第2のビット線を含み、複数の磁性体メモリセルの各々は、各書込ワード線が第1および第2のビット線と交差する位置の一方に対応させて行ごとに交互配置される。半導体集積回路は、データ書込時において、アドレス選択結果に応じて選択されるビット線対に含まれる第1および第2のビット線の一端を高電位状態および低電位状態の一方ずつに設定するためのデータ書込制御回路と、ビット線対にそれぞれ対応して設けられたビット線電流制御回路とをさらに備える。ビット線電流制御回路は、データ書込時において第2のデータ書込電流を流すために対応する第1および第2のビット線の他端の間を電気的に結合する。

【0033】

請求項2記載の半導体集積回路は、請求項1記載の半導体集積回路であって、データ書込制御回路は、半導体集積回路に対して外部から供給された外部電源電位によって駆動される。

【0034】

請求項3記載の半導体集積回路は、請求項2記載の半導体集積回路であって、複数行の書込ワード線をアドレス選択結果に応じて選択的に活性状態に駆動するためのワード線駆動回路と、各書込ワード線を複数の書込ワード線の非活性状態に対応する電位と結合するためのワード線電流制御回路とをさらに備え、ワード線駆動回路は、外部電源電位によって駆動される。

【0035】

請求項4記載の半導体集積回路は、請求項1記載の半導体集積回路であって、複数列のビット線対に共通に設けられ、第1および第2のデータ線によって形成されるデータ線対と、列にそれぞれ対応して設けられた列選択ゲート回路とさらに備える。列選択ゲート回路は、アドレス選択結果に応じて、対応する第1および第2のビット線を第1および第2のデータ線とそれぞれ接続し、データ書込制御回路は、データ書込時において、第1および第2の内部ノードを高電位状態および低電位状態の一方ずつに設定し、第1および第2の内部ノードと第1および第2のデータ線との接続点は、第2のデータ書込電流の経路を形成する配線の抵抗値が、アドレス選択の対象となる列の位置に関わらずほぼ一定となるように設けられる。

【0036】

請求項5記載の半導体集積回路は、請求項4記載の半導体集積回路であって、各ビット線対は、列に沿った方向に配置され、データ線対は、行に沿った方向に配置され、第1の内部ノードは、先頭の列側の領域において第1のデータ線と接続され、第2の内部ノードは、最終の列側の領域において第2のデータ線と接続される。

【0037】

請求項6記載の半導体集積回路は、請求項4記載の半導体集積回路であって、各ビット線対は、列に沿った方向に配置され、データ線対は、行に沿った方向に配置され、第1および第2の内部ノードは、中央の列周辺の領域において、第1および第2のデータ線とそれぞれ接続される。

【0038】

請求項7記載の半導体集積回路は、請求項1記載の半導体集積回路であって、複数列は、M個(M:2以上の自然数)の列ずつの列グループに分割され、半導体集積回路は、列グループごとに配置された、第1および第2のデータ線によって形成されるデータ線対と、列にそれぞれ対応して設けられた列選択ゲート回路とをさらに備える。各列選択ゲート回路は、アドレス選択結果に応じて、対応する第1および第2のビット線を対応する第1および第2のデータ線とそれぞれ接続するように動作し、データ書込制御回路は、列グループごとにデータ線対に対応して設けられ、各データ書込制御回路は、データ書込時においてアドレス選択結果に応じて動作して、対応する第1および第2のデータ線を高電位状態および低電位状態の一方ずつに設定する。

【0039】

請求項8記載の半導体集積回路は、請求項7記載の半導体集積回路であって、データ線対は、ビット線対と同一方向に沿って、対応する列グループに属するM個の列の中央部に配置される。

【0040】

請求項9記載の半導体集積回路は、請求項1記載の半導体集積回路であって、行にそれぞれ対応して設けられ、データ読出時においてアドレス選択結果に応じて活性化されて対応する磁性体メモリセルを対応するビット線対と結合するための読出ワード線と、データ読出時において、アドレス選択結果に応じて選択されるビット線対に含まれる第1および第2のビット線に対してデータ読出電流を供給するためのデータ読出制御回路とをさらに備える。データ読出時において、各ビット線電流制御回路は、対応する第1および第2のビット線の間を開放する。

【0041】

請求項10記載の半導体集積回路は、請求項9記載の半導体集積回路であって、第1のビット線にそれぞれ対応して設けられた第1のダミーメモリセルと、第2のビット線にそれぞれ対応して設けられた第2のダミーメモリセルと、複数列の第1のダミーメモリセルに共通に設けられ、各第1のダミーメモリセルを対応する第1のビット線とそれぞれ結合するために、データ読出時においてアドレス選択結果に応じて活性化される第1のダミー読出ワード線と、複数列の第2のダミーメモリセルに共通に設けられ、各第2のダミーメモリセルを対応する第2のビット線とそれぞれ結合するために、データ読出時においてアドレス選択結果に応じて活性化される第2のダミー読出ワード線と、データ読出時において、複数行の読出ワード線のうちの1つと第1および第2のダミー読出ワード線のうちの一方とを、アドレス選択結果に応じて選択的に活性化するワード線駆動回路をさらに備える。第1および第2のダミーメモリセルの各々は、磁性体メモリセルが記憶データのレベルに応じて有する第1および第2の抵抗値の中間の抵抗値を有する。

【0042】

請求項11記載の半導体集積回路は、請求項9記載の半導体集積回路であって、半導体集積回路に対して外部から供給された外部電源電位を降圧して内部電源電位を生成する電圧降下回路をさらに備え、データ書込制御回路は、外部電源電位によって駆動され、データ読出制御回路は、内部電源電位によって駆動される。

【0043】

請求項12記載の半導体集積回路は、複数行および複数列の行列状に配置された複数の磁性体メモリセルを有するメモリアレイを備え、複数の磁性体メモリセルの各々は、第1および第2のデータ書込電流によって印加されるデータ書込磁界が所定磁界よりも大きい場合に書込まれる記憶データのレベルに応じて異なる抵抗値を有する。半導体集積回路は、磁性体メモリセルの行にそれぞれ対応して設けられ、データ書込時においてアドレス選択結果に応じて第1のデータ書込電流を流すための書込ワード線と、磁性体メモリセルの列にそれぞれ対応して設けられるビット線と、複数列のビット線に共通に設けられたデータ線対とをさらに備え、データ線対は、第1および第2のデータ線によって形成される。半導体集積回路は、データ書込時において、第1および第2のデータ線を高電位状態および低電位状態の一方ずつに設定するためのデータ書込制御回路と、列にそれぞれ対応して設けられた列選択ゲート回路と、列にそれぞれ対応して設けられたビット線電流制御回路とをさらに備える。各列選択ゲート回路は、アドレス選択結果に応じて対応するビット線の一端を第1のデータ線と接続し、ビット線電流制御回路は、データ書込時において第2のデータ書込電流を流すために、対応するビット線の他端と第2のデータ線との間を電気的に結合する。

【0044】

請求項13記載の半導体集積回路は、請求項12記載の半導体集積回路であって、データ書込制御回路は、データ書込時において、第1および第2の内部ノードを高電位状態および低電位状態の一方ずつに設定し、各ビット線電流制御回路は、アドレス選択結果に応じて、対応するビット線と第2のデータ線との間を電気的に結合し、半導体集積回路は、データ読出時においてデータ読出電流を第3の内部ノードに供給するためのデータ読出制御回路と、データ書込時において、第1および第2の内部ノードと第1および第2のデータ線とをそれぞれ結合するための接続切換回路とをさらに備え、接続切換回路は、データ読出時において、第1および第2のデータ線を、第3の内部ノードおよび読出基準電位を供給する第4の内部ノードとそれぞれ電気的に結合し、データ読出制御回路は、読出基準電位と第3の内部ノードとの間の電位差に基づいてデータ読出を行なう。

【0045】

請求項14記載の半導体集積回路は、請求項12記載の半導体集積回路であって、データ書込制御回路は、データ書込時において、第1および第2の内部ノードを高電位状態および低電位状態の一方ずつに設定し、各ビット線電流制御回路は、データ読出前のプリチャージ時において対応するビット線と第2のデータ線との間を電気的に結合するとともに、データ読出時において対応するビット線と第2のデータ線との間を電気的に切り離し、半導体集積回路は、データ読出時においてデータ読出電流を第1のデータ線に供給するためのデータ読出制御回路と、データ書込時において、第1および第2の内部ノードと第1および第2のデータ線とをそれぞれ結合するための接続切換回路とをさらに備え、接続切換回路は、プリチャージ時において、第1および第2のデータ線を、読出基準電位を供給する第3および第4の内部ノードとそれぞれ電気的に結合するとともに、データ読出時において、第1および第2のデータ線を第1から第4の内部ノードから切り離し、データ読出制御回路は、読出基準電位と第1のデータ線との間の電位差に基づいてデータ読出を行なう。

【0051】

【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳細に説明する。

【0052】

[実施の形態1]

図1は、本発明の実施の形態1に従うMRAMデバイス1の全体構成を示す概略ブロック図である。

【0053】

図1を参照して、MRAMデバイス1は、外部からの制御信号CMDおよびアドレス信号ADDに応答してランダムアクセスを行ない、書込データDINの入力および読出データDOUTの出力を実行する。

【0054】

MRAMデバイス1は、制御信号CMDに応答してMRAMデバイス1の全体動作を制御するコントロール回路5と、n行×m列に行列状に配置された複数のMTJメモリセルを有するメモリアレイ10とを備える。メモリアレイ10の構成は後ほど詳細に説明するが、MTJメモリセルの行にそれぞれ対応して複数のライトワード線WWLおよびリードワード線RWLが配置される。また、MTJメモリセルの列にそれぞれ対応して設けられる折返し型で構成されるビット線対が配置される。ビット線対は、ビット線BLおよび/BLによって構成される。

なお以下においては、ビット線BLおよび/BLの組をビット線対BLPとも総称する。

【0055】

MRAMデバイス1は、さらに、アドレス信号ADDによって示されるロウアドレスRAに応じてメモリアレイ10における行選択を実行する行デコーダ20と、アドレス信号ADDによって示されるコラムアドレスCAに応じてメモリアレイ10における列選択を実行する列デコーダ25と、行デコーダ20の行選択結果に基づいてリードワード線RWLおよびライトワード線WWLを選択的に活性化するためのワード線ドライバ30と、データ書込時においてライトワード線WWLにデータ書込電流を流すためのワード線電流制御回路40と、データ読出およびデータ書込時において、データ書込電流±Iwおよびセンス電流Isを流すための読出/書込制御回路50,60とを備える。

【0056】

図2は、メモリアレイ10およびその周辺の実施の1に従う構成を詳細に説明するための図である。

【0057】

図2を参照して、メモリアレイ10は、n行×m列(n,m:自然数)に配列される、図41に示した構成を有するMJTメモリセルMCを有する。MTJメモリセルの行(以下、単にメモリセル行とも称する)に対応して、リードワード線RWL1〜RWLnおよびライトワード線WWL1〜WWLnがそれぞれ設けられる。

【0058】

MTJメモリセルの列(以下、単にメモリセル列とも称する)に対応して、ビット線対を構成するビット線BL1,/BL1〜BLm,/BLmがそれぞれ設けられる。

【0059】

なお、以下においては、ライトワード線、リードワード線、ビット線およびビット線対を総括的に表現する場合には、符号WWL、RWL、BL(/BL)およびBLPをそれぞれ用いて表記することとし、特定のライトワード線、リードワード線およびビット線を示す場合には、これらの符号に添字を付してRWL1,WWL1のように表記するものとする。

【0060】

ライトワード線WWL1〜WWLnは、ワード線電流制御回路40によって、接地電位Vssと結合される。これによって、ワード線ドライバ30によって選択状態(高電位状態:電源電位Vcc)に活性化されたライトワード線WWLにデータ書込電流Ipが流れる。

【0061】

列デコーダ25は、コラムアドレスCAのデコード結果に応じて、メモリセル列に対応してそれぞれ設けられるコラム選択線CSL1〜CSLmのうちの1本を選択状態(Hレベル)に活性化する。

【0062】

データI/O線対DI/OPは、データ書込時におけるデータ書込電流±Iwおよびデータ読出時におけるセンス電流Isを伝達する。すなわち、データ読出時とデータ書込時において共有される。データI/O線対DI/OPは、データ線IOおよび/IOを含む。

【0063】

次に、読出/書込制御回路50に含まれるコラム選択ゲートCSG1〜CSGm、データ書込電流制御回路51およびデータ読出回路52の構成について説明する。

【0064】

コラム選択ゲートCSG1〜CSGmは、メモリセル列に対応してそれぞれ配置される。コラム選択ゲートCSG1〜CSGmのうちのいずれか1個は、列デコーダ25の列選択結果に応じてオン状態となり、データI/O線対DI/OPを構成するデータ線IOおよび/IOを、対応するビット線BLおよび/BLとそれぞれ結合する。

【0065】

たとえば、コラム選択ゲートCSG1は、データ線IOとビット線BL1との間に結合されるトランジスタスイッチと、データ線/IOとビット線/BL1との間に電気的に結合されるトランジスタスイッチとを有する。これらのトランジスタスイッチは、コラム選択線CSL1の電位レベルに応じてオン/オフする。すなわち、コラム選択線CSL1が選択状態(Hレベル)に活性化された場合には、コラム選択ゲートCSG1は、データ線IO,/IOをビット線BL1および/BL1とそれぞれ電気的に結合する。その他のメモリセル列に対応してそれぞれ設けられるコラム選択ゲートCSG2〜CSGmも同様の構成を有する。

【0066】

データ書込電流制御回路51は、データ書込時において活性化される制御信号WEに応答して動作する。

【0067】

データ書込電流制御回路51は、内部ノードNw0に一定電流を供給するためのP型MOSトランジスタ151と、トランジスタ151の通過電流を制御するためのカレントミラー回路を構成するP型MOSトランジスタ152および電流源回路153とを含む。

【0068】

データ書込電流制御回路51は、さらに、内部ノードNw0から動作電流の供給を受けて動作するインバータ154、155および156を有する。インバータ154は、書込データDINの電位レベルを反転して内部ノードNw1に伝達する。インバータ155は、書込データDINの電位レベルを反転してインバータ156の入力ノードに伝達する。インバータ156は、インバータ154の出力を反転して内部ノードNw2に伝達する。したがって、データ書込電流制御回路51は、書込データDINの電位レベルに応じて、データ線IOおよび/IOの電位レベルを電源電位Vccおよび接地電位Vssの一方ずつに設定する。

【0069】

データ読出回路52は、データ読出時において活性化される制御信号REに応答して動作して、読出データDOUTを出力する。

【0070】

データ読出回路52は、電源電位Vccを受けて内部ノードNs1およびNs2に一定電流をそれぞれ供給するための電流源回路161および162と、内部ノードNs1と内部ノードNr1との間に電気的に結合されるN型MOSトランジスタ163と、内部ノードNs2と内部ノードNr2との間に電気的に結合されるN型MOSトランジスタ164と、内部ノードNs1およびNs2の間の電位レベル差を増幅して読出データDOUTを出力する増幅器165とを有する。

【0071】

トランジスタ163および164のゲートには参照電位Vrefが与えられる。電流源回路161および162の供給電流量および参照電位Vrefは、センス電流Isの電流量に応じて設定される。抵抗166および167は、内部ノードNs1およびNs2を接地電位Vssにプルダウンするために設けられる。このような構成とすることにより、データ読出回路52は、データ読出時において、データ線IOおよび/IOの各々にセンス電流Isを供給する。さらに、コラム選択ゲートおよびビット線対を介して接続されるMTJメモリセルの記憶データのレベルに応じて、データ線IOおよび/IOにそれぞれ生じる電位変化の差を増幅して、読出データDOUTを出力する。

【0072】

読出/書込制御回路60は、メモリアレイ10を挟んでコラム選択ゲートCSG1〜CSGmと反対側に配置される。

【0073】

読出/書込制御回路60は、ビット線イコライズ信号BLEQに応じてオン/オフされるイコライズトランジスタ62−1〜62−mを有する。イコライズトランジスタ62−1〜62−mは、メモリセル列にそれぞれ対応して設けられる。たとえば、イコライズトランジスタ62−1は、第1番目のメモリセル列に対応して設けられ、ビット線イコライズ信号BLEQの活性化(Hレベル)に応答して、ビット線BL1と/BL1とを電気的に結合する。

【0074】

その他のメモリセル列に対応してそれぞれ設けられるイコライズトランジスタ62−2〜62−mも同様に、ビット線イコライズ信号BLEQの活性化に応答して、対応するメモリセル列において、ビット線対を構成するビット線BLおよび/BLの間を電気的に結合する。

【0075】

ビット線イコライズ信号BLEQは、コントロール回路5によって生成される。ビット線イコライズ信号BLEQは、MRAMデバイス1のスタンバイ期間、MRAMデバイス1のアクティブ期間のうちメモリアレイ10が非選択状態である場合およびアクティブ期間内でデータ書込動作時において、折返し型で設けられるビット線対を構成するビット線BLおよび/BLを各メモリセル列において短絡するために、Hレベルに活性化される。

【0076】

一方、MRAMデバイスのアクティブ期間におけるデータ読出動作時においては、ビット線イコライズ信号BLEQはLレベルに非活性化される。これに応答して、各メモリセル列において、ビット線対を構成するビット線BLおよび/BLの間は遮断される。

【0077】

まず、データ書込時における動作について説明する。以下においては、一例としてコラム選択線CSL2に対応する第2番目のメモリセル列が選択された場合について説明する。

【0078】

列選択結果に応答して、コラム選択線CSL2が選択状態(Hレベル)に活性化されて、コラム選択ゲートCSG2がオンする。これにより、データ線IOおよび/IOは、ビット線対BLP2を構成するビット線BL2および/BL2とそれぞれ電気的に結合される。また、データ書込時においては、イコライズトランジスタ62−2はオン状態となって、ビット線BL2および/BL2の間を短絡する。

【0079】

すでに説明したように、データ書込電流制御回路51は、データ線IOおよび/IOの電位レベルを、電源電位Vccおよび接地電位Vssのいずれか一方ずつに設定する。たとえば、書込データDINのデータレベルがLレベルである場合には、インバータ154および156の出力は、それぞれ電源電位Vcc(高電位状態)および接地電位Vss(低電位状態)にそれぞれ設定されるので、データ線IOにLレベルデータを書込むためのデータ書込電流−Iwが流される。

【0080】

データ書込電流−Iwは、コラム選択ゲートCSG2を介してビット線BL2に供給される。ビット線BL2に伝達されるデータ書込電流−Iwは、イコライズトランジスタ62−2によって折返されてもう一方のビット線/BL2においては、反対方向のデータ書込電流+Iwとして伝達される。ビット線/BL2が流れるデータ書込電流+Iwは、コラム選択ゲートCSG2を介してデータ線/IOに伝達される。

【0081】

また、ライトワード線WWL1〜WWLnのうちのいずれか1個が選択状態(Hレベル)に活性化されて、データ書込電流Ipが流れる。したがって、コラム選択線CSL2に対応するメモリセル列において、対応するライトデータ線WWLにデータ書込電流が流されたMTJメモリセルにおいて、データ書込が実行される。このとき、ビット線BL2と結合されるMTJメモリセルMCに対してはLレベルデータが書込まれ、ビット線/BL2と結合されるMTJメモリセルMCに対してはHレベルデータが書込まれる。

【0082】

一方、書込データDINのデータレベルがHレベルである場合には、内部ノードNw1およびNw2の電位レベルの設定が上記の場合とは反対となり、ビット線BL2および/BL2には、上記と逆方向のデータ書込電流が流れて、上記とは逆のデータレベルが書込まれる。このようにして、書込データDINのデータレベルに応じた方向を有するデータ書込電流±Iwがビット線BLおよび/BLに供給される。

【0083】

次にデータ読出について説明する。

MTJメモリセルMCは、1行ごとにビット線BLおよび/BLのいずれか一方ずつと結合される。たとえば、第1番目のメモリセル列に属するMTJメモリセルについて説明すれば、第1行目のMTJメモリセルは、ビット線BL1と結合され、第2行目のMTJメモリセルは、ビット線/BL1と結合される。以下同様に、MTJメモリセルの各々は、奇数行においてビット線対の一方ずつのBL1〜BLmと接続され、偶数行においてビット線対の他方ずつの/BL1〜/BLmと接続される。

【0084】

この結果、リードワード線RWLが行選択結果に応じて選択的に活性化されると、ビット線対の一方ずつBL1〜BLmおよびビット線対の他方ずつ/BL1〜/BLmのいずれか一方が、MTJメモリセルMCと結合される。

【0085】

メモリアレイ10は、さらに、ビット線BL1,/BL1〜BLm,/BLmとそれぞれと結合される複数のダミーメモリセルDMCを有する。ダミーメモリセルは、ダミーリードワード線DRWL1およびDRWL2のいずれか一方と結合されて、2行×m列に配置される。ダミーリードワード線DRWL1と結合されるダミーメモリセルは、ビット線BL1,BL2〜BLmとそれぞれ結合される。一方、ダミーリードワード線DRWL2と結合される残りのダミーメモリセルは、ビット線/BL1,/BL2〜/BLmとそれぞれ結合される。

【0086】

ダミーリードワード線DRWL1およびDRWL2は、ビット線対の一方BL1〜BLmおよびビット線対の他方/BL1〜/BLmのうち、選択されたメモリセル行に属するMTJメモリセルMCと非接続となった一方をダミーメモリセルDMCとそれぞれ結合するように選択的に活性化される。

【0087】

この結果、ビット線対の一方ずつBL1〜BLmおよびビット線対の他方ずつ/BL1〜/BLmは、選択されたメモリセル行に対応するm個のMTJメモリセルおよびm個のダミーメモリセルとの一方ずつとそれぞれ結合される。

【0088】

すでに説明したように、データ読出回路52は、データ線IOおよび/IOに、同一方向のセンス電流Isを供給する。

【0089】

データ読出時においても、コラム選択線CSL2に対応する第2番目のメモリセル列が選択された場合について説明する。

【0090】

コラム選択線CSL2が選択状態(Hレベル)に活性化されて、コラム選択ゲートCSG2がオンする。これに応じて、データI/O線対DI/OPを構成するデータ線IOおよび/IOは、データ書込時と同様にビット線BL2および/BL2とそれぞれ結合される。

【0091】

しかし、データ読出時においては、イコライズトランジスタ62−2はターンオフされているので、データ読出回路52から供給されるセンス電流Isは、ビット線BL2および/BL2上を、同一の方向に流れる。

【0092】

リードワード線RWL1〜RWLnのうちのいずれか1つが選択状態(Hレベルレベル)に活性化されて、対応するMTJメモリセルがビット線BL2および/BL2の一方と結合される。また、ダミーリードワード線DRWL1およびDRWL2のいずれかが活性化されて、MTJメモリセルと非接続のビット線BL2および/BL2の他方は、ダミーメモリセルDMCと結合される。

【0093】

行選択結果に応じて奇数行が選択されて、ビット線BL2とMTJメモリセルMCとが結合される場合には、ダミーリードワード線DRWL2が活性化されて、ビット線/BL2とダミーメモリセルDMCとが結合される。反対に、行選択結果に応じて偶数行が選択されて、ビット線/BL2とMTJメモリセルMCとが結合される場合には、ダミーリードワード線DRWL1が活性化されて、ビット線BL2とダミーメモリセルDMCとが結合される。

【0094】

すでに説明したように、MTJメモリセルMCの抵抗値は、記憶データのレベルによって変化する。ここで、Hレベルデータを記憶した場合におけるMTJメモリセルMCの抵抗値をRhとし、Lレベルデータを記憶した場合におけるMTJメモリセルMCの抵抗値をRlとすると、ダミーメモリセルDMCの抵抗値Rdは、RlとRhの中間値に設定される。これにより、ダミーメモリセルに結合されたビット線の一方に生じる電位変化と、MTJメモリセルMCと結合されたビット線の他方に生じる電位変化とを比較することによって、データ読出の対象となった記憶データのレベルを検知することができる。

【0095】

ビット線BL2および/BL2の間に生じた電位差は、データI/O線対DI/OPを介して、データ読出回路52中の内部ノードNs1およびNs2に伝達される。増幅器165によって、内部ノードNs1およびNs2の電位レベル差は増幅されて読出データDOUTとして出力される。

【0096】

したがって、ビット線BLと結合されるMTJメモリセルにLレベルデータが記憶されている場合、およびビット線/BLと結合されるMTJメモリセルMCにHレベルデータが記憶されている場合において、読出データDOUTにLレベルが出力される。反対に、ビット線BLと結合されるMTJメモリセルにHレベルデータが記憶されている場合、およびビット線/BLと結合されるMTJメモリセルMCにLレベルデータが記憶されている場合において、読出データDOUTにHレベルが出力される。

【0097】

このように、折返し型のビット線対BLPを各メモリセル列に対応して配置し、データ書込電流をイコライズトランジスタによって折返して流すことにより、各ビット線BLおよび/BLの一端の電位レベルを電源電位Vccおよび接地電位Vssの一方ずつに制御するのみで、異なる方向のデータ書込電流を供給することができる。このように、極性の異なる電位(負電位)を必要とせず、また電流の方向は、データ線IOおよび/IOの電位を電源電位および接地電位のいずれか一方ずつに設定するのみで切換えられるので、データ書込電流制御回路51の回路構成を簡易にすることができる。さらに、読出/書込制御回路60も、イコライズトランジスタ62−1〜62−mのみで簡易に形成することができる。

【0098】

また、ダミーメモリセルを用いてデータ読出を行なうので、折返し型のビット線対BLPを設ける構成において、MTJメモリセルを効率的に配置できる。

【0099】

[実施の形態2]

図3は、実施の形態2に従う電源電位の供給系統を説明するブロック図である。

【0100】

図3を参照して、メモリアレイ10においては、実施の形態1と同様に、各メモリセル列において、折返し型のビット線対が設けられ、読出/書込制御回路60においては、イコライズトランジスタ62−1〜62−mが設けられる。

【0101】

実施の形態2においては、データ書込時にデータ書込電流を供給する、データ書込電流制御回路51およびワード線WWLを活性化するワード線ドライバ30に対して、MRAMデバイス1に対して外部から供給される外部電源電位Ext.Vccを直接供給する。

【0102】

また、MRAMデバイス1は、さらに、外部電源電位Ext.Vccを降圧して内部電源電位Int.Vccを生成する電圧降下回路(VDC:Voltage Down

Converter)55を備える。

【0103】

電圧降下回路55が生成する内部電源電位Int.Vccは、データ読出回路52、列デコーダ25、コントロール回路5、行デコーダ20等の、データ読出およびアドレス処理を行なう内部回路に供給される。なお、データ読出時およびデータ書込時における各部の動作は、実施の形態1と同様であるので詳細な説明は繰返さない。

【0104】

このような構成とすることにより、データ書込時において、比較的大きなデータ書込電流±Iwを供給するデータ書込電流制御回路51およびライトワード線WWLにデータ書込電流Ipを供給するワード線ドライバ30を外部から印加される外部電源電位Ext.Vccによって駆動して、これらのデータ書込電流を速やかに供給することができる。

【0105】

一方、データ書込電流を供給する回路以外の内部回路を降圧された内部電源電位Int.Vccによって駆動することにより、これらの内部回路の消費電力の低減および、高集積化のためのデバイス微細化に対応した信頼性の確保を図ることができる。

【0106】

[実施の形態3]

実施の形態1においては、行方向の沿って配置されるデータI/O線対DI/OPの一端において、データ書込電流制御回路51の出力ノードNw1およびNw2とデータ線IOおよび/IOとがそれぞれ接続される構成を示した。しかし、このような構成においては、選択されるメモリセル列に対応して、データ書込電流±Iwの経路長が変化してしまう。

【0107】

たとえば、図2に例示された構成においては、コラム選択線CSL1側において、データ書込電流制御回路51の出力ノードNw1およびNw2とデータ線IOおよび/IOとがそれぞれ接続されるので、コラム選択線CSL1が選択された場合におけるデータ書込電流の経路長は短い一方で、反対側のコラム選択線CSLmが選択状態に活性化された場合におけるデータ書込電流の経路長は長くなってしまう。このように、選択されるメモリセル列に応じて、データ書込電流が伝達される配線長が変化するので、データ書込電流の経路の抵抗値が変化して、データ書込電流の電流量が変化してしまう。この結果、メモリセル列によって、ライト動作マージンに差が生じてしまう。

【0108】

したがって、選択時にデータ書込電流の経路長が長くなるメモリセル列においては、ライトマージン不足が生じる可能性がある。しかし、このようにライトマージン不足が最も懸念されるメモリセル列(たとえば、図2においてメモリアレイ端に位置する第1列や第m列、あるいはメモリセルの特性ばらつきによってマージン不足になるメモリセルが含まれるメモリセル列)に合せてデータ書込電流を設定すれば、その他のメモリセル列に対するデータ書込時にデータ書込電流を必要以上に大きく設定することになり、無駄な消費電力が生じてしまう。

【0109】

図4は、メモリアレイ10およびその周辺の実施の形態3に従う構成を示すブロック図である。

【0110】

図4を参照して、実施の形態3に従う構成においては、データ書込電流制御回路51は、先頭のメモリセル列(第1列)側および最終のメモリセル列(第m列)側のそれぞれにおいて、データI/O線対DI/OPを構成するデータIOおよび/IOとそれぞれ結合される。

【0111】

このような構成とすることにより、列選択の対象となるメモリセル列の位置に関わらず、ノードNw1(データ書込電流制御回路51)〜データ線IO〜ビット線BL〜イコライズトランジスタ〜ビット線/BL〜データ線/IO〜ノードNw2(データ書込電流制御回路51)で形成されるデータ書込電流±Iwの経路長を一定にして抵抗値の変動を防ぎ、データ書込電流±Iwの電流値を一定レベルに維持することかできる。

【0112】

これにより、実施の形態1で説明した効果に加えて、いずれのメモリセル列に対しても無駄な消費電力の発生を抑制して、ライト動作マージンを適正に設定することができる。

【0113】

[実施の形態3の変形例1]

図5は、メモリアレイ10およびその周辺の実施の形態3の変形例1に従う構成を示すブロック図である。

【0114】

図5を参照して、実施の形態3の変形例1に従う構成においては、メモリアレイ10全体において、複数のデータI/O線対DI/OPが設けられる。各データI/O線対DI/OPは、M個(M:自然数)のメモリセル列ごとに配置される。図5においては、M=2の場合、すなわち2つのメモリセル列ごとに1対のデータI/O線対DI/OPが配置される構成が示される。

【0115】

図5においては、これらのデータI/O線対DI/OPのうち、第1列および第2列に対して設けられるデータI/O線対DI/OPaと、第3列および第4列に対して設けられるデータI/O線対DI/OPbとを代表的に示している。

【0116】

データ書込電流制御回路51およびデータ読出回路52は、各データI/O線対に対応して設けられる。たとえば、データI/O線対DI/OPaに対応して、データ書込電流制御回路51aおよびデータ読出回路52aが配置される。すなわち、データ書込電流制御回路51およびデータ読出回路52は、メモリアレイ10全体において(m/M)個ずつ設けられる。

【0117】

これらのデータ書込電流制御回路51およびデータ読出回路52のうちから、選択されたメモリセル列に対応する1個ずつが活性化されて、データ書込電流±Iwおよびセンス電流Isの供給を実行する。その他の部分の構成および動作は、実施の形態1と同様であるので詳細な説明は繰り返さない。

【0118】

このように、データI/O線対DI/OPをM個のメモリセル列ごとに細分化して配置することによっても、列選択の対象となるメモリセル列の位置に依存して、データ書込電流が通過する配線長が変化して、電流レベルが変化してしまうことを有効に防止して、実施の形態3と同様の効果を享受できる。

【0119】

[実施の形態3の変形例2]

図6は、メモリアレイ10およびその周辺の実施の形態3の変形例2に従う構成を示すブロック図である。

【0120】

図6を参照して、実施の形態3の変形例2においては、図4に示した実施の形態3に従う構成と比較して、データ書込電流制御回路51の出力ノードNw1およびNw2が、データI/O線対DI/Oの中央部において、データ線IOおよび/IOとそれぞれ電気的に結合される点が異なる。

【0121】

このような構成とすることによっても、列選択の対象となるメモリセル列の位置に応じて、データ書込電流経路の抵抗値が変化することを防止して、実施の形態3と同様の効果を享受できる。

【0122】

[実施の形態3の変形例3]

図7は、実施の形態3の変形例3に従うメモリアレイ10の構成を示すブロック図である。

【0123】

図7を参照して、実施の形態3の変形例3においては、図5で説明した実施の形態3の変形例1の場合と同様に、M個のメモリセル列ごとに独立のデータ入出力線DI/OPが配置される。データI/O線対DI/OPの配置本数およびこれらに対応するデータ書込電流制御回路51およびデータ読出回路52の配置および選択については、図5で説明したとおりであるので説明は繰返さない。

【0124】

実施の形態3の変形例3においては、各データI/O線対DI/OPは、対応するM個のメモリセル列の中央部に配置される。図7においては、一例としてM=2の場合について説明しているが、第1列および第2列に対応して設けられるデータI/O線対DI/OPaは、メモリセル列の第1列および第2列の間に配置される。

【0125】

このような構成とすることにより、実施の形態3の変形例1に従う構成と比較して、列選択の対象となるメモリセル列の位置に依存したデータ書込電流の変動をさらに抑制して、いずれのメモリセル列に対してもライト動作マージンをさらに適正に設定することができる。

【0126】

[実施の形態4]

実施の形態1から3においては、MTJメモリセルMCに対して、データ書込電流±Iwおよびセンス電流Isは、共通のビット線BLによって供給される構成を説明した。

【0127】

しかし、データ書込電流±Iwとセンス電流Isとの電流量は大きく異なるため、ビット線BLを、データ読出時にセンス電流を流すためのリードビット線RBLと、データ書込時においてデータ書込電流±Iwを流すためのライトビット線WBLとに分割して配置することも効果的である。

【0128】

このような、MTJメモリセルの構成のバリエーションについては後ほど詳細に説明するが、実施の形態4においては、データ書込電流±Iwを流すためのライトビット線WBLが独立に配置された場合において、列選択の対象となるメモリセル列の位置に関わらずデータ書込電流の変動を抑制するための構成について説明する。

【0129】

図8は、実施の形態4に従うメモリアレイ10およびその周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【0130】

図8を参照して、メモリセル列のそれぞれに対応して、データ書込電流±Iwを流すための相補のライトビット線対を形成するWBL,/WBLが設けられる。なお、ライトビット線WBLについても、総括的に表現する場合には、符号WBLを用いて表記し、特定のライトビット線を示す場合には、符号WBLに符号を付してWBL1,/WBL1のように表記するものとする。

【0131】

読出/書込制御回路60が有するイコライズトランジスタ62−1〜62−mは、それぞれのメモリセル列において、ライトビット線WBLおよび/WBLを電気的に結合する。イコライズトランジスタ62−1〜62−mは、コラム選択ゲートCSG1〜CSGmと同様に、コラム選択線CSL1〜CSLmの電位レベルに応じてオン/オフされる。

【0132】

このような構成とすることにより、列選択結果に応じて、たとえばコラム選択線CSL2が選択状態(Hレベル)に活性化されると、コラム選択ゲートCSG2およびイコライズトランジスタ62−2がオンして、ノードNw1(データ書込電流制御回路51)〜データ線IO〜ライトビット線WBL〜イコライズトランジスタ62−2〜ライトビット線/WBL2〜データ線/IO〜ノードNw2(データ書込電流制御回路51)の電流経路が形成される。

【0133】

これにより、ライトビット線対を形成する相補のライトビット線WBLおよび/WBLに対して、イコライズトランジスタによって折り返される逆方向のデータ書込電流を流すことにより、実施の形態1と同様のデータ書込を実行することができる。

【0134】

図4に示される構成と同様に、データ書込電流制御回路51の内部ノードNw1およびNw2と、データI/O線対DI/OPを構成するデータ線IOおよび/IOとは、先頭のメモリセル列(第1列)側および最終のメモリセル列(第m列)側のそれぞれにおいて結合される。

【0135】

したがって、列選択の対象となるメモリセル列の位置に関わらずデータ書込電流経路の配線長、すなわち抵抗値を一定として、データ書込電流の変動を防止することができる。これにより、実施の形態3と同様に、それぞれのメモリセル列に対して、無駄な電力消費を生じさせることなく適正なライトマージンを確保することができる。

【0136】

[実施の形態4の変形例1]

図9は、実施の形態4の変形例1に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【0137】

図9を参照して、実施の形態4の変形例1においては、図5の場合と同様に、データI/O線対DI/OPは、M個のメモリセル列ごとに配置される。データ書込電流制御回路51も、メモリアレイ10全体で(m/M)組配置されるデータI/O線対DI/OPに対応してそれぞれ配置される。イコライズトランジスタ62−1〜62−mは、図8の場合と同様に、コラム選択線CSL1〜CSLmの電位レベルに応じてオン/オフされて、実施の形態1と同様のデータ書込が実行される。

【0138】

このような構成とすることにより、ビット線BLをリードビット線RBLとライトビット線WBLとに分割配置する場合においても、実施の形態3の変形例1と同様の効果を享受することができる。

【0139】

[実施の形態4の変形例2]

図10は、実施の形態4の変形例2に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【0140】

図10を参照して、実施の形態4の変形例2においては、図6に示される構成と同様に、各メモリセル列に共通に設けられるデータI/O線対DI/OPの中央部において、データ線IOおよび/IOをデータ書込電流制御回路51の出力ノードNw1およびNw2とそれぞれ結合する。イコライズトランジスタ62−1〜62−mは、図8の場合と同様に、コラム選択線CSL1〜CSLmの電位レベルに応じてオン/オフされて、実施の形態1と同様のデータ書込が実行される。

【0141】

このような構成とすることにより、ビット線BLをリードビット線RBLとライトビット線WBLとに分割配置する場合においても、実施の形態3の変形例2と同様の効果を得ることができる。

【0142】

[実施の形態4の変形例3]

図11は、実施の形態4の変形例3に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【0143】

図11を参照して、実施の形態4の変形例3においては、データI/O線対DI/OPは、図7の場合と同様に、M個のメモリセル列ごとに配置され、各データI/O線対DI/OPは、対応するM個のメモリセル列の中央部に配置される。イコライズトランジスタ62−1〜62−mは、図8の場合と同様に、コラム選択線CSL1〜CSLmの電位レベルに応じてオン/オフされて、実施の形態1と同様のデータ書込が実行される。

【0144】

このような構成とすることにより、ビット線BLをリードビット線RBLとライトビット線WBLとに分割配置する場合においても、実施の形態3の変形例2と同様の効果を得ることができる。

【0145】

実施の形態4およびその変形例1から3においては、データ読出に関連する構成についての説明は省略したが、実施の形態1から3と同様に、ダミーメモリセルDMCを用いたデータ読出を、リードビット線RBLに生じる電位変化に基づいて行なうことができる。

【0146】

なお、実施の形態1から4においては、ダミーメモリセルDMCを用いてデータ読出を実行し、MTJメモリセルMCは、ビット線BLおよび/BLのそれぞれにおいて1行ごとに配置する構成を示したが、ビット線BLおよび/BLとワード線との交点の各々にMTJメモリセルMCを配置する構成とすることもできる。この場合には、ダミーメモリセルDMCを設けることなくデータ読出を実行することができる。

【0147】

このように、各メモリセル行においてビット線BL,/BLとの交点のそれぞれにMTJメモリセルを配置することにより、1ビットの記憶データに対して2個のMTJメモリセルが配置される。このような構成とすることにより、リードワード線RWLの活性化に応答して、ビット線BLおよび/BLに対して、互いに相補のデータレベルを記憶する2個のMTJメモリセルがそれぞれ結合されることになる。したがって、これらの相補のデータを記憶するMTJメモリセルによって生じる電位変化の差を比較することにより読出データのデータレベルを設定するため、ダミーメモリセルDMCを用いて読出データDOUTのデータレベルを検知する場合と比較して、読出マージンを十分に確保することができる。

【0148】

[実施の形態5]

図12は、メモリアレイ10およびその周辺の実施の形態5に従う構成を示すブロック図である。

【0149】

図12を参照して、実施の形態5においては、各メモリセル列に対応して、折返し型ではなく開放型のビット線が配置される。すなわち、m個のメモリセル列に対応してビット線BL1〜BLmがそれぞれ設けられる。

【0150】

MTJメモリセルMCは、各メモリセル行において、ビット線BLとの交点ごとに配置される。データI/O線対DI/OPを形成するデータ線IOおよび/IOは、メモリアレイ10と列方向に隣接して、メモリアレイ10を挟んで対向するようにそれぞれ配置される。

【0151】

コラム選択ゲートCSG1〜CSGmは、コラム選択線CSL1〜CSLmによってオン/オフ制御されて、データI/O線対DI/OPの一方であるデータ線IOと対応するビット線BLとを結合する。

【0152】

読出/書込制御回路60は、ビット線BL1〜BLmとデータI/O線対DI/OPの他方であるデータ線/IOとの間にそれぞれ結合される電流制御トランジスタ64−1〜64−mを有する。電流制御トランジスタ64−1〜64−mも、コラム選択ゲートCSG1〜CSGmと同様に、コラム選択線CSL1〜CSLmにそれぞれ応じてオン/オフする。

【0153】

データ書込電流制御回路51およびデータ読出回路52とデータI/O線対DIO/Pとの間には、電流切換回路56が設けられる。電流切換回路56は、データ書込電流制御回路51からのデータ書込電流±Iwおよびデータ読出回路52からのセンス電流Isを選択的にデータI/O線対DI/OPに供給する。

【0154】

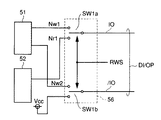

図13は、電流切換回路56の構成を示すブロック図である。

図13を参照して、電流切換回路56は、データ書込電流制御回路51の出力ノードNw1とデータ読出回路52の出力ノードNr1のいずれか一方とデータ線IOとを選択的に結合するためのスイッチSW1aと、データ書込電流制御回路51の出力ノードNw2および電源電位Vccのいずれか一方をデータ線/IOと選択的に結合するスイッチSW1bとを有する。

【0155】

スイッチSW1aおよびSW1bは、たとえば共通の制御信号RWSに応じて動作する。すなわち、データ読出時においては、制御信号RWSに応じて、スイッチSW1aおよびSW1bは、データ読出回路52の出力ノードNr1および電源電位Vccをデータ線IOおよび/IOとそれぞれ結合する。

【0156】

実施の形態5においては、データ読出回路52は、データ線/IOを電源電位Vccにプルアップした状態でデータ線IOにセンス電流Isを流し、データ線IOに生じる電圧降下を基準となる電圧降下量ΔVrと比較して読出データDOUTのデータレベルを検知する。ΔVrは、Hレベルデータを読出した場合におけるデータ線IOの電圧降下をΔVhとし、Lレベルデータを読出した場合におけるデータ線IOの電圧降下をΔVlとすると、ΔVhとΔVlとの中間値となるように設定される。

【0157】

このような、データ読出制御回路の構成は、たとえば図2に示したデータ読出回路52の構成において、トランジスタ164を省略するとともにノードNr2を電源電位Vccと結合し、さらに、内部ノードNs2の電位レベルが(Vcc−ΔVr)となるように抵抗167の抵抗値を設定することによって実現される。

【0158】

一方、データ書込時においては、制御信号RWSに応じて、スイッチSW1aおよびSW1bは、データ書込電流制御回路51の出力ノードNw1およびNw2を、データ線IOおよび/IOとそれぞれ結合する。

【0159】

再び図12を参照して、データ書込時においては、ノードNw1(データ書込電流制御回路51)〜データ線IO〜ビット線BL〜データ線/IO〜ノードNw2(データ書込電流制御回路51)の経路にデータ書込電流を流すことができる。これにより、開放型のビット線を配置する構成においても、実施の形態1と同様に、データ書込電流制御回路51の出力ノードNw1およびNw2の電位レベルを電源電位Vccおよび接地電位Vssの一方ずつに制御するのみで、異なる方向のデータ書込電流を供給することができる。このように、極性の異なる電位(負電位)を発生する必要がないので、データ書込電流制御回路51の回路構成を簡易にすることができる。読出/書込制御回路60も同様に、電流制御トランジスタ64−1〜64−mのみで簡易に形成することができる。

【0160】

また、データ書込電流制御回路51と、データI/O線対DI/OPを形成するデータ線IOおよび/IOとは、先頭のメモリセル列(第1列)側および最終のメモリセル列(第m列)側においてそれぞれ結合される。したがって、実施の形態3および4と同様に、列選択の対象となるメモリセル列の位置に関わらず、データ書込電流経路の配線長、すなわち抵抗値を一定に維持することができる。この結果、データ書込電流の変動を防止して、それぞれのメモリセルに対する適正なライトマージンを、無用な電力消費を招くことなく確保することが可能である。

【0161】

[実施の形態5の変形例]

図14は、メモリアレイ10およびその周辺の実施の形態5の変形例に従う構成を示すブロック図である。

【0162】

図14を参照して、実施の形態5の変形例においては、図12の構成と比較して、読出/書込制御回路60に含まれる電流制御トランジスタ64−1〜64−mは、ビット線プリチャージ信号BLPRに応じてオン/オフする点が異なる。ビット線プリチャージ信号BLPRの信号レベルは、すでに説明したビット線イコライズ信号BLEQと同様に設定される。

【0163】

また、電流切換回路56に代えて電流切換回路58が、データ書込電流制御回路51とデータI/O線対DI/OPとの間に結合される。データ読出回路52は、制御信号REに応答して動作してデータI/O線対の一方であるデータ線IOに対してセンス電流Isを供給する。

【0164】

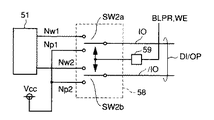

図15は、電流切換回路58の構成を示すブロック図である。

図15を参照して、電流切換回路58は、データ書込電流制御回路51の出力ノードNw1および電源電位Vccを供給するプリチャージノードNp1とデータ線IOとの間に配置されるスイッチSW2aと、データ書込電流制御回路51の出力ノードNw2および電源電位Vccを供給するプリチャージノードNp2とデータ線/IOとの間に配置されるスイッチSW2bとを有する。

【0165】

スイッチSW2aおよびSW2bは、データ書込時において、データ線IOおよび/IOと、データ書込電流制御回路51の出力ノードNw1およびNw2とを電気的にそれぞれ結合する。また、スイッチSW2aおよびSW2bは、データ読出に先立って実行されるプリチャージ動作時において、データ線IOおよび/IOをプリチャージノードNp1およびNp2と電気的にそれぞれ結合する。

【0166】

しかし、データ読出時においては、プリチャージされたデータ線IOおよび/IOは、スイッチSW1bおよびSW2bによって、データ書込電流制御回路51の出力ノードNw1,Nw2およびプリチャージノードNp1,Np2のいずれとも切り離される。

【0167】

スイッチ制御回路59は、すでに説明した制御信号WEおよびビット線プリチャージ信号BLPRの信号レベルに応じて、データ書込時、データ読出時およびプリチャージ動作時のいずれであるを判断して、スイッチSW2aおよSW2bの接続を制御する。

【0168】

このような構成とすることにより、データ読出時においては、ビット線プリチャージ信号BLPRをLレベルに非活性化して、電流制御トランジスタ64−1〜64−mをターンオフするとともに、データ線IOおよび/IOをデータ書込電流制御回路51およびプリチャージノードNp1,Np2のいずれとも切り離す。

【0169】

さらに、実施の形態5と同様の構成を有するデータ読出回路52によって、データ線IOおよび選択されたメモリセル列に対応するコラム選択ゲートを介して、ビット線BLに対してセンス電流Isが供給される。リードワード線RWLの活性化に応じてビット線と結合されたMTJメモリセルMCによってビット線BLに生じる電圧降下を基準の電圧降下ΔVrと比較することによって、データ読出回路52は、読出データDOUTのデータレベルを検知することができる。

【0170】

一方、データ書込時においては、ビット線プリチャージ信号BLPRはHレベルに活性化されて、電流制御トランジスタ64−1〜64−mはオンする。したがって、選択されたメモリセル列において、ノードNw1(データ書込電流制御回路51)〜データ線IO〜ビット線BL〜電流制御トランジスタ〜データ線/IO〜ノードNw2(データ書込電流制御回路51)の電流経路が形成されて、書込データDINのデータレベルに応じたデータ書込電流±Iwをビット線BLに流すことができる。これにより、実施の形態5と同様のデータ書込動作を実行することができる。

【0171】

[実施の形態6]

実施の形態6においては、MTJメモリセルMCに対して設けられる配線の配置のバリエーションについて説明する。

【0172】

図16は、本発明の実施の形態6に従うMRAMデバイス2の全体構成を示す概略ブロック図である。

【0173】

図16を参照して、MRAMデバイス2は、MRAMデバイス1と同様に、外部からの制御信号CMDおよびアドレス信号ADDに応答してランダムアクセスを行ない、書込データDINの入力および読出データDOUTの出力を実行する。メモリアレイ10は、n行×m列に行列状に配置された複数のMTJメモリセルを有する。メモリアレイ10の構成は、後ほど詳細に説明するが、メモリセル行にそれぞれ対応して複数のリードワード線RWLおよびライトビット線WBLが配置され、メモリセル列にそれぞれ対応して、複数のライトワード線WWLおよびリードビット線RBLとが配置される。

【0174】

このように、実施の形態6においては、データ書込電流±Iwおよびセンス電流Isを流すためのビット線BLを、データ読出時においてセンス電流Isを流すリードビット線RBLと、データ書込時においてデータ書込電流±Iwを流すためのライトビット線WBLとに分割する。また、リードワード線RWLおよびライトワード線WWLとは、互いに異なる方向に沿って配置される。

【0175】

MRAMデバイス2は、さらに、アドレス信号ADDによって示されるロウアドレスRAに応じて、メモリアレイ10における行選択を実行する行デコーダ20と、アドレス信号ADDによって示されるコラムアドレスCAに応じて、メモリアレイ10における列選択を実行する列デコーダ25と、行デコーダ20の行選択結果に基づいて、リードワード線RWLをデータ読出時において選択的に活性化するリードワード線ドライバ30rと、行デコーダ20の行選択結果に基づいて、データ書込時において、ライトビット線WBLにデータ書込電流を流すための書込制御回路50wおよび60wと、列デコーダ25の列選択結果に応じて、データ書込時においてライトワード線WWLを選択的に活性化するためのライトワード線ドライバ30wと、活性化されたライトワード線WWLにデータ書込電流を流すためのワード線電流制御回路40と、データ読出時において、リードビット線RBLにセンス電流Isを供給するための読出制御回路50rとを備える。

【0176】

書込制御回路50wは、実施の形態1で説明したデータ書込電流制御回路51の機能と行選択を実行する選択ゲートとの機能を併せ持ったものに相当する。書込制御回路60wは、書込制御回路50wと協調的に動作して、書込データDINのデータレベルに応じて、メモリアレイ10両端部におけるライトビット線WBLの両端の電位を制御することによって、データ書込電流±Iwの方向を制御する。

【0177】

読出制御回路50rは、図2で説明したデータ読出回路52の機能と、列選択を実行するコラム選択ゲートCSG1〜CSGmの機能とを併せ持ったものに相当する。

【0178】

ワード線電流制御回路40は、選択状態(高電位状態:Hレベル)に活性化されたライトワード線WWLにデータ書込電流を流すために、各ライトワード線WWLを接地電位Vssと結合する。

【0179】

図17は、実施の形態6に従うメモリアレイ10の構成を示すブロック図である。

【0180】

図17を参照して、メモリアレイ10は、n行×m列に配置された複数のMTJメモリセルMCを有する。実施の形態6に従う構成においては、各MTJメモリセルMCに対して、リードワード線RWL、ライトワード線WWL、リードビット線RBLおよびライトビット線WBLが配置される。リードワード線RWLおよびライトビット線WBLは、メモリセル行にそれぞれ対応して行方向に沿って配置される。一方、ライトワード線WWLおよびリードビット線RBLは、メモリセル列にそれぞれ対応して、列方向に沿って配置される。

【0181】

この結果、メモリアレイ10全体においては、リードワード線RWL1〜RWLn、ライトワード線WWL1〜WWLm、リードビット線RBL1〜RBLmおよびライトビット線WBL1〜WBLnが設けられる。

【0182】

なお、以下においては、リードビット線についても、総括的に表現する場合には、符号をRBLを用いて表記することとし、特定のリードビット線を示す場合には、これらの符号に添字を付して、RBL1,RBLmのように表記するものとする。

【0183】

ワード線電流制御回路40は、ライトワード線WWL1〜WWLmを接地電位Vssと結合する。これにより、ライトワード線ドライバ30wによってライトワード線WWLを選択状態(Hレベル:電源電位Vcc)に活性化した場合に、活性化されたライトワード線WWLにデータ書込電流Ipを流すことができる。

【0184】

図18は、実施の形態6に従うMTJメモリセルの接続態様を示す回路図である。

【0185】

図18を参照して、磁気トンネル接合部MTJおよびアクセストランジスタATRからなるMTJメモリセルに対して、リードワード線RWL、ライトワード線WWL、ライトビット線WBLおよびリードビット線RBLが設けられる。既に説明したように、アクセストランジスタATRには、半導体基板上に形成された電界効果トランジスタであるMOSトランジスタが代表的に適用される。

【0186】

アクセストランジスタATRのゲートは、リードワード線RWLと結合される。アクセストランジスタATRは、リードワード線RWLが選択状態(Hレベル:電源電位Vcc)に活性化されるとターンオンして、磁気トンネル接合部MTJを含む電流経路を形成する。一方、リードワード線RWLが非選択状態(Lレベル:接地電位Vss)に非活性化される場合には、アクセストランジスタATRはターンオフされるので、磁気トンネル接合部MTJを含む電流経路は形成されない。

【0187】

ライトワード線WWLおよびライトビット線WBLとは、磁気トンネル接合部MTJと近接するように、互いに直交する方向に配置される。このように、リードワード線RWLとライトワード線WWLとを互いに直交する方向に配置することによって、リードワード線ドライバ30rとライトワード線ドライバ30wとを分割して配置することができる。リードワード線RWLおよびライトワード線WWLは、データ読出時およびデータ書込時においてそれぞれ独立に活性化されるので、これらのドライバは元来独立なものとして設計することができる。したがって、ライトワード線ドライバ30wとリードワード線ドライバ30rとを分割して小型化し、それぞれをメモリアレイ10に隣接する異なる領域に配置することができるので、レイアウトの自由度を向上させて、レイアウト面積すなわちMRAMデバイスのチップ面積を減少させることができる。

【0188】

磁気トンネル接合部MTJは、リードビット線RBLとアクセストランジスタATRとの間に電気的に結合される。したがって、データ読出時において、電流を流す必要がないライトビット線WBLの電位レベルを接地電位Vssに設定することによって、アクセストランジスタATRのターンオンに応答して、リードビット線RBL〜磁気トンネル接合部MTJ〜アクセストランジスタATR〜ライトビット線WBL(接地電位Vss)の電流経路が形成される。この電流経路にセンス電流Isを流すことによって、磁気トンネル接合部MTJの記憶データのレベルに応じた電位変化をリードビット線RBLに生じさせて、記憶データを読出ことができる。

【0189】

データ書込時においては、ライトワード線WWLおよびライトビット線WBLにそれぞれデータ書込電流が流され、これらのデータ書込電流によってそれぞれ生じる磁界の和が、一定磁界すなわち図44に示されるアステロイド特性線を超える領域に達することによって、磁気トンネル接合部MTJに記憶データが書込まれる。

【0190】

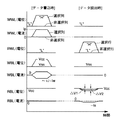

図19は、実施の形態6に従うMTJメモリセルに対するデータ書込およびデータ読出を説明するためのタイミングチャート図である。

【0191】

まず、データ書込時の動作について説明する。

ライトワード線ドライバ30wは、列デコーダ25の列選択結果に応じて、選択列に対応するライトワード線WWLの電位を選択状態(Hレベル)に駆動する。非選択列においては、ライトワード線WWLの電位レベルは非選択状態(Lレベル)に維持される。ワード線電流制御回路40によって各ライトワード線WWLは接地電位Vssと結合されているので、選択列においてライトワード線WWLにデータ書込電流Ipが流れる。

【0192】

リードワード線RWLは、データ書込時においては非選択状態(Lレベル)のままに維持される。データ書込時においては、読出制御回路50rは、センス電流Isを供給せず、リードビット線RBLを高電位状態(Vcc)にプリチャージする。また、アクセストランジスタATRはターンオフ状態を維持するので、データ書込時においては、リードビット線RBLに電流は流れない。

【0193】

書込制御回路50wおよび60wは、メモリアレイ10の両端におけるライトビット線WBLの電位を制御することによって、書込データDINのデータレベルに応じた方向のデータ書込電流を生じさせる。たとえば、“1”の記憶データを書込む場合には、書込制御回路60w側のビット線電位を高電位状態(電源電位Vcc)に設定し、反対側の書込制御回路50w側のビット線電位を低電位状態(接地電位Vss)に設定する。これにより、書込制御回路60wから50wに向かう方向にデータ書込電流+Iwがライトビット線WBLを流れる。一方、“0”の記憶データを書込む場合には、書込制御回路50w側および60w側のビット線電位を高電位状態および低電位状態にそれぞれ設定し、書込制御回路50wから60wへ向かう方向にデータ書込電流−Iwがライトビット線WBLを流れる。この際に、データ書込電流±Iwは、行デコーダ20の行選択結果に応じて、選択行に対応するライトビット線WBLに選択的に流される。

【0194】

このように、データ書込電流Ipおよび±Iwの方向を設定することにより、データ書込時において、書込まれる記憶データのレベル“1”,“0”に応じて、逆方向のデータ書込電流+Iwおよび−Iwのいずれか一方を選択して、ライトワード線WWLのデータ書込電流Ipをデータレベルに関係なく一定方向に固定することができる。これにより、ライトワード線WWLに流れるデータ書込電流Ipの方向を常に一定にすることができるので、既に説明したように、ワード線電流制御回路40の構成を簡略化することができる。

【0195】

次にデータ読出動作について説明する。

データ読出時においては、ライトワード線WWLは非選択状態(Lレベル)に維持され、その電位レベルはワード線電流制御回路40によって接地電位Vssに固定される。データ読出時において、書込制御回路50wおよび60wは非活性化されてデータ書込電流の供給を停止するので、ライトビット線WBLに電流は流れない。

【0196】

一方、リードワード線ドライバ30rは、行デコーダ20の行選択結果に応じて、選択行に対応するリードワード線RWLを選択状態(Hレベル)に駆動する。非選択行においては、リードワード線RWLの電位レベルは非選択状態(Lレベル)に維持される。読出制御回路50rは、データ読出時において、データ読出を実行するための一定量のセンス電流Isを選択列のリードビット線RBLに供給する。リードビット線RBLは、データ読出前において高電位状態(Vcc)にプリチャージされているので、リードワード線RWLの活性化に応答したアクセストランジスタATRのターンオンによって、センス電流Isの電流経路がMTJメモリセル内に形成され、記憶データに応じた電位変化(降下)がリードビット線RBLに生じる。

【0197】

図20においては、一例として記憶されるデータレベルが“1”である場合に、固定磁気層FLと自由磁気層VLとにおける磁界方向が同一であるとすると、記憶データが“1”である場合にリードビット線RBLの電位変化ΔV1は小さく、記憶データが“0”である場合のリードビット線RBLの電位変化ΔV2は、ΔV1よりも大きくなる。これらの電位降下ΔV1およびΔV2の差を検知することによって、MTJメモリセルの記憶データを読出すことができる。

【0198】

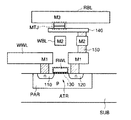

図20は、実施の形態6に従うMTJメモリセルの配置を説明する構造図である。

【0199】

図20を参照して、アクセストランジスタATRは、半導体主基板SUB上のp型領域PARに形成される。ライトビット線WBLは、第1の金属配線層M1に形成されて、アクセストランジスタATRのソース/ドレイン領域の一方110と電気的に結合される。他方のソース/ドレイン領域120は、第1の金属配線層M1に設けられた金属配線、バリアメタル140およびコンタクトホールに形成された金属膜150を経由して、磁気トンネル接合部MTJと電気的に結合される。

【0200】

リードビット線RBLは、磁気トンネル接合部MTJと電気的に結合するように、第2の金属配線層M2に設けられる。ライトワード線WWLは、第3の金属配線層M3に配置される。ライトワード線WWLは、MTJメモリセルの他の部位と結合することなく、独立して配置することができるので、磁気トンネル接合部MTJとの間の磁気カップリングを高めることができるように、自由に配置することができる。

【0201】

このような構成とすることにより、MTJメモリセルに対して、リードワード線RWLとライトワード線WWLとを互いに直交する方向に配置して、リードワード線RWLおよびライトワード線WWLにそれぞれ対応するリードワード線ドライバ30rおよびライトワード線ドライバ30wを独立に配置してレイアウトの自由度を高めることができる。データ読出時におけるワード線駆動電流が過大になることを防いで、不要な磁気ノイズの発生を防止することができる。

【0202】

[実施の形態6の変形例1]

図21は、実施の形態6の変形例1に従うメモリアレイ10の構成を示すブロック図である。

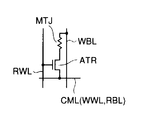

【0203】

図21を参照して、メモリアレイ10は、n行×m列に配置されたMTJメモリセルMCを有する。メモリセル行にそれぞれ対応して、リードワード線RWLおよびライトビット線WBLが配置され、メモリセル列にそれぞれ対応して、共通配線CMLが配置される。共通配線CMLは、リードビット線RBLおよびライトワード線WWLの機能を共有するための配線である。したがって、メモリアレイ10全体では、リードワード線RWL1〜RWLn、ライトビット線WBL1〜WBLnおよび共通配線CML1〜CMLmが配置される。

【0204】

ワード線電流制御回路40は、共通配線CML1〜CMLmと接地電位Vssとの間にそれぞれ結合される電流制御トランジスタ41−1〜41−mを有する。電流制御トランジスタ41−1〜41−mの各々は、データ書込時において、共通配線CMLをライトワード線WWLとして動作させるために、共通配線CML1〜CMLmの各々を接地電位Vssと結合する。データ書込時以外においては、電流制御トランジスタ41−1〜41−mはターンオフされて、共通配線CMLは接地電位Vssと切離される。

【0205】

このように、実施の形態6の変形例1においては、電流制御トランジスタ41−1〜41−mを設けることによって、共通配線CMLをデータ読出時においてリードビット線RBLとして使用するとともに、データ書込時においてライトワード線WWLとして使用することができる。これにより、リードビット線RBLおよびライトワード線WWLの機能を共通配線CMLに共有させることにより、配線数を削減することができる。

【0206】

図22は、実施の形態6の変形例1に従うMTJメモリセルの接続態様を示す回路図である。

【0207】

図22を参照して、アクセストランジスタATRは、磁気トンネル接合部MTJとライトビット線WBLとの間に電気的に結合される。磁気トンネル接合部MTJは、アクセストランジスタATRと共通配線CMLとの間に結合される。アクセストランジスタATRのゲートはリードワード線RWLと結合される。図22の構成においても、リードワード線RWLとライトワード線WWLとは互いに直交する方向に配置される。

【0208】

図23は、実施の形態6の変形例1に従うMTJメモリセルに対するデータ書込およびデータ読出を説明するためのタイミングチャート図である。

【0209】

図23を参照して、データ書込時においては、ライトビット線WBLにデータ書込電流±Iwが流される。また、電流制御トランジスタ41−1〜41−mのオンによって、行列選択結果に応じて選択列に対応する共通配線CMLにデータ書込電流Ipが流れる。このように、データ書込時における共通配線CMLの電位および電流は、図19に示されるライトワード線WWLと同様に設定される。これにより書込データDINのデータレベルに応じた磁界を磁気トンネル接合部MTJに書込むことができる。また、図19に示されるとおりリードビット線RBLはデータ書込時において特に必要とはされないので、両者を共通配線CMLに統合することができる。

【0210】

データ書込時以外においては、電流制御トランジスタ41−1〜41−mはターンオフされる。データ読出前においては、共通配線CMLは接地電位Vssにプリチャージされている。

【0211】

データ読出時においては、ライトビット線WBLの電位レベルを接地電位レベルVssに設定することにより、リードワード線RWLを選択状態(Hレベル)に活性化することによって、アクセストランジスタATRをターンオンして、共通配線CML〜磁気トンネル接合部MTJ〜アクセストランジスタATR〜ライトビット線WBLの経路にセンス電流Isを流すことができる。

【0212】

センス電流Isの電流経路がMTJメモリセル内に形成されると、記憶データに応じた電位変化(上昇)が共通配線CMLに生じる。

【0213】

図23においては、一例として記憶されるデータレベルが“1”である場合に、固定磁気層FLと自由磁気層VLとにおける磁界方向が同一であるとすると、記憶データが“1”である場合に共通配線CMLの電位変化ΔV1は小さく、記憶データが“0”である場合の共通配線CMLの電位変化ΔV2は、ΔV1よりも大きくなる。共通配線CMLに生じる電位変化ΔV1およびΔV2の差を検知することによって、MTJメモリセルの記憶データを読出すことができる。

【0214】

また、図19に示されるとおりライトワード線WWLははデータ読出時において特に必要とはされないので、ライトワード線WWLおよびリードビット線RBLを共通配線CMLに統合することができる。

【0215】

図24は、実施の形態6の変形例に従うMTJメモリセルの配置を説明する構造図である。

【0216】

図24を参照して、ライトビット線WBLは、第1の金属配線層M1に配置され、リードワード線RWLは、アクセストランジスタATRのゲート130と同一層に配置される。

【0217】

ライトビット線WBLは、アクセストランジスタATRのソース/ドレイン領域110と電気的に結合される。他方のソース/ドレイン領域120は、第1の金属配線層M1に設けられた金属配線、バリアメタル140およびコンタクトホールに設けられる金属膜150を介して、磁気トンネル接合部MTJと結合される。

【0218】

共通配線CMLは、磁気トンネル接合部MTJと電気的に結合するように第2の金属配線層M2に設けられる。このように、共通配線CMLにリードビット線RBLおよびライトワード線WWL機能の両方を併せ持つようにすることにより実施の形態6に従うMTJメモリセルが奏する効果に加えて、配線数および金属配線層の数を削減して製造コストの削減を図ることができる。

【0219】

[実施の形態6の変形例2]

図25は、実施の形態6の変形例2に従うメモリアレイ10の構成を示すブロック図である。

【0220】

図25を参照して、実施の形態6の変形例2においても、メモリアレイ10は、n行×m列に配置されたMTJメモリセルMCを有する。メモリセル行にそれぞれ対応して、リードワード線RWLおよびライトビット線WBLが設けられる。また、メモリセル列にそれぞれ対応して、リードビット線RBLおよびライトワード線WWLが設けられる。したがって、メモリアレイ10全体に対しては、リードワード線RWL1〜RWLn、ライトビット線WBL1〜WBLn、リードビット線RBL1〜RBLmおよびライトワード線WWL1〜WWLmが設けられる。ワード線電流制御回路40は、各ライトワード線WWLを接地電位Vssと結合する。

【0221】

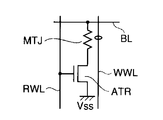

図26は、実施の形態6の変形例2に従うMTJメモリセルの接続態様を示す回路図である。

【0222】

図26を参照して、リードビット線RBLは、アクセストランジスタATRを介して磁気トンネル接合部MTJと結合される。磁気トンネル接合部MTJは、ライトワード線WWLおよびアクセストランジスタATRの間に結合される。リードワード線RWLは、アクセストランジスタATRのゲートと結合される。図26の構成においても、リードワード線RWLとライトワード線WWLとは互いに直交する方向に配置される。

【0223】

図27は、実施の形態6の変形例2に従うMTJメモリセルの配置を示す構造図である。

【0224】

図27を参照して、リードビット線RBL金属配線層M1にそれぞれ配置される。リードワード線RWLは、アクセストランジスタATRのゲート130と同一層に形成される。リードビット線RBLは、アクセストランジスタATRのソース/ドレイン領域110と結合される。ソース/ドレイン領域120は、第1および第2の金属配線層M1およびM2に設けられた金属配線、バリアメタル140およびコンタクトホールに設けられた金属膜150を介して磁気トンネル接合部MTJと結合される。

【0225】

ライトビット線WBLは、磁気トンネル接合部MTJと近接して第2の金属配線層M2に設けられる。ライトワード線WWLは、磁気トンネル接合部MTJと電気的に結合されて第3の金属配線層M3に配置される。

【0226】

このような構成とすることにより、リードビット線RBLは、アクセストランジスタATRを介して磁気トンネル接合部MTJと結合される。これにより、リードビット線RBLは、データ読出の対象となる、すなわち対応するリードワード線RWLが選択状態(Hレベル)に活性化されたメモリセル行に属するMTJメモリセルMCとのみ電気的に結合される。この結果、リードビット線RBLの容量を抑制して、データ読出動作を高速化することができる。

【0227】

[実施の形態6の変形例3]

図28は、実施の形態6の変形例3に従うメモリアレイ10の構成を示すブロック図である。

【0228】

図28を参照して、メモリアレイ10は、同様にn行×m列に配置された複数のMTJメモリセルMCを有する。実施の形態6の変形例3においては、図25〜27に示した実施の形態6の変形例2と比較して、ライトワード線WWLおよびリードビット線RBLの配置を入替えている。その他の構成については、実施の形態6の変形例2の場合と同様であるので説明は繰返さない。

【0229】

図29は、実施の形態6の変形例3に従うMTJメモリセルの接続態様を示す回路図である。

【0230】

図29を参照して、実施の形態6の変形例3に従うMTJメモリセルは、図26に示される実施の形態6の変形例2に従うMTJメモリセルと比較して、リードビット線RBLとライトワード線WWLとの配置を入替えた構成となっている。その他の配線の配置については、図26と同様であるので説明は繰返さない。このような構成としても、リードワード線RWLとライトワード線WWLとは互いに直交する方向に配置することができる。

【0231】

図30は、実施の形態6の変形例3に従うMJTメモリセルの配置を示す構造図である。

【0232】

図30を参照して、実施の形態6の変形例3に従うMTJメモリセルにおいては、図27に示した実施の形態6の変形例2に従うMTJメモリセルの構造と比較して、ライトワード線WWLとリードビット線RBLの配置される位置が入れ替わっている。すなわち、ライトワード線WWLは、第1の金属配線層M1に設けられて、アクセストランジスタATRのソース/ドレイン領域110と結合される。一方、リードビット線RBLは、磁気トンネル接合部MTJと電気的に結合するように第3の金属配線層M3に設けられる。

【0233】

このように、実施の形態6の変形例3においては、リードビット線RBLが磁気トンネル接合部MTJと直接結合されるので、実施の形態6の変形例2に示したようなデータ読出動作の高速化を図ることはできない。しかしながら、実施の形態6の変形例3に従う構成においても、リードワード線ドライバ30rとライトワード線ドライバ30wとを独立に配置して、実施の形態6と同様の効果を得ることができる。

【0234】

[実施の形態6の変形例4]

図31は、実施の形態6の変形例4に従うメモリアレイ10の構成を示すブロック図である。

【0235】

図31を参照して、メモリアレイ10は、同様にn行×m列に配置された複数のMTJメモリセルMCを有する。メモリセル行にそれぞれ対応してリードワード線RWLおよびライトビット線WBLが配置され、メモリセル列にそれぞれ対応しておよび共通配線CMLが配置される。したがって、メモリアレイ10全体に対しては、リードワード線RWL1〜RWLn、ライトビット線WBL1〜WBLnおよび共通配線CML1〜CMLmが配置される。

【0236】

ワード線電流制御回路40は、共通配線CML1〜CMLmと接地電位Vssとの間にそれぞれ電気的に結合される電流制御トランジスタ41−1〜41−mを有する。電流制御トランジスタ41−1〜41−mの各々は、データ書込時において、共通配線CMLと接地電位Vssとを結合する。データ書込時以外においては、共通配線CML1〜CMLmは接地電位Vssと切離される。データ読出前においては、共通配線CMLは、接地電位Vssにプリチャージされる。

【0237】

図32は、実施の形態6の変形例4に従うMTJメモリセルの接続態様を示す回路図である。

【0238】

図32を参照して、アクセストランジスタATRは共通配線CMLと磁気トンネル接合部MTJとの間に結合される。リードワード線RWLは、アクセストランジスタATRのゲートと結合される。ライトビット線WBLは、リードワード線RWLと同一方向に配置され、磁気トンネル接合部MTJと電気的に結合される。

【0239】

共通配線CMLは、データ書込時においてはライトワード線WWLと同様に、ライトワード線ドライバ30wによって選択的に活性化される。一方、データ読出時においては、共通配線CMLは、読出制御回路50rによってセンス電流Isを供給される。

【0240】

データ書込時においては、電流制御トランジスタ41−1〜41−mのターンオンによって、選択状態(Hレベル)に活性化された共通配線CMLは、ライトワード線WWLと同様にデータ書込電流Ipが流れる。一方、データ読出時においては、電流制御トランジスタ41−1〜41−mがターンオフされて、共通配線CML〜磁気トンネル接合部MTJ〜アクセストランジスタATR〜ライトビット線WBL(接地電位Vss)の経路に流されるセンス電流Isによって、図23で説明したように、磁気トンネル接合部MTJの記憶データに対応する電位変化が共通配線CMLに生じる。

【0241】

したがって、共通配線CMLに、データ書込時におけるライトワード線WWLの機能およびデータ読出時におけるリードビット線RBLの機能を併有させて、配線数を削減することができる。

【0242】

また、リードワード線RWLとデータ書込時にライトワード線として機能する共通配線CMLとを互いに直交する方向に配置するので、リードワード線ドライバ30rとライトワード線ドライバ30wとを独立に配置して、実施の形態6と同様の効果を得ることができる。

【0243】

図33は、実施の形態6の変形例4に従うMTJメモリセルの配置を示す構造図である。

【0244】

図33を参照して、共通配線CMLは、第1の金属配線層M1に配置されて、アクセストランジスタATRのソース/ドレイン領域110と電気的に結合される。リードワード線RWLは、アクセストランジスタATRのゲート130と同一層に形成される。

【0245】

ソース/ドレイン領域120は、第1の金属配線層M1に形成された金属配線、バリアメタル140およびコンタクトホールに形成された金属膜150を介して、磁気トンネル接合部MTJと結合される。ライトビット線WBLは、磁気トンネル接合部MTJと電気的に結合するように第2の金属配線層M2に配置される。

【0246】

これにより、アクセストランジスタATRを介して共通配線CMLと磁気トンネル接合部MTJとを結合する構成とすることによって、共通配線CMLは、アクセストランジスタATRのターンオン時においてのみ磁気トンネル接合部MTJと結合される。この結果、データ読出時においてリードビット線RBLとして機能する共通配線CMLの容量を削減して、データ読出動作の高速化をさらに図ることができる。

【0247】

[実施の形態6の変形例5]

図34は、実施の形態6の変形例5に従うメモリアレイ10の構成を示すブロック図である。

【0248】

図34を参照して、メモリアレイ10は、同様にn行×m列に配置された複数のMTJメモリセルMCを有する。メモリセル行にそれぞれ対応してリードワード線RWLおよび共通配線CMLが配置され、メモリセル列にそれぞれ対応してライトビット線WBLが配置される。したがって、メモリアレイ10全体に対しては、リードワード線RWL1〜RWLn、共通配線CML1〜CMLnおよびライトビット線WBL1〜WBLmが設けられる。

【0249】

ワード線電流制御回路は、共通配線CML1〜CMLnと接地電位Vssとの間にそれぞれ電気的に結合される電流制御トランジスタ41−1〜41−nを有する。電流制御トランジスタ41−1〜41−nの各々は、データ書込時において、共通配線CMLと接地電位Vssとを結合する。データ書込時以外においては、共通配線CML1〜CMLnは接地電位Vssと切離される。特に、データ読出前においては、共通配線CMLは、接地電位Vssにプリチャージされる。

【0250】

図35は、実施の形態6の変形例5に従うMTJメモリセルの接続態様を示す回路図である。

【0251】

図35を参照して、アクセストランジスタATRはライトビット線WBLと磁気トンネル接合部MTJとの間に結合される。リードワード線RWLは、アクセストランジスタATRのゲートと結合される。共通配線CMLは、リードワード線RWLと同一方向に配置され、磁気トンネル接合部MTJと電気的に結合される。

【0252】

共通配線CMLの動作は、実施の形態6の変形例4と同様であり、データ書込時におけるライトワード線WWLの機能およびデータ読出時におけるリードビット線RBLの機能を併有する。

【0253】

したがって、実施の形態6の変形例5に従う構成によれば、共通配線CMLと磁気トンネル接合部MTJとは直接電気的に結合されるので、データ読出時における共通配線CMLの容量を低減することできないが、ライトワード線WWLとリードビット線RBLとを共通配線CMLに集約できるので、製造時における金属配線層の数を削減して、製造コストの削減を図ることができる。

【0254】

図36は、実施の形態6の変形例5に従うMTJメモリセルの配置を示す構造図である。

【0255】

図36を参照して、ライトビット線WBLは、第1の金属配線層M1に配置されて、アクセストランジスタATRのソース/ドレイン領域110と電気的に結合される。リードワード線RWLは、アクセストランジスタATRのゲート130と同一層に形成される。ソース/ドレイン領域120は、第1の金属配線層M1に形成される金属配線、バリアメタル140およびコンタクトホールに形成される金属膜150を介して、磁気トンネル接合部MTJと結合される。

【0256】

共通配線CMLは、磁気トンネル接合部MTJと電気的に結合するように第2の金属配線層M2に配置される。

【0257】

[実施の形態6の変形例6]

図37は、実施の形態6の変形例6に従うメモリアレイ10の構成を示すブロック図である。

【0258】

図37を参照して、メモリアレイ10は、n行×m列に配置される複数のMTJメモリセルMCを有する。メモリセル行にそれぞれ対応してリードワード線RWLおよびライトビット線WBLが配置され、メモリセル列にそれぞれ対応してライトワード線WWLおよびリードビット線RBLが配置される。したがって、メモリアレイ10全体においては、リードワード線RWL1〜RWLn、ライトビット線WBL1〜WBLn、リードビット線RBL1〜RBLmおよびライトワード線WWL1〜WWLmが配置される。

【0259】

図38は、実施の形態6の変形例6に従うMTJメモリセルの接続態様を示す回路図である。

【0260】

図38を参照して、アクセストランジスタATRのゲートはリードワード線RWLと結合される。アクセストランジスタATRは、リードビット線RBLと磁気トンネル接合部MTJとの間に電気的に結合される。磁気トンネル接合部MTJは、リードワード線RWLと同一方向に配置されるライトビット線WBLと結合される。

【0261】

ライトワード線WWLは、ライトビット線WBLと直交する方向に、磁気トンネル接合部MTJと近接して設けられる。したがって、リードワード線ドライバ30rとライトワード線ドライバ30wとを独立に配置して、実施の形態6と同様の効果を得ることができる。

【0262】

また、ライトワード線WWLは、MTJメモリセルの他の部位と結合することなく、独立して配置することができるので、磁気トンネル接合部MTJとの間における磁気カップリングの向上を優先して配置することができる。これにより、ライトワード線WWLを流れるデータ書込電流Ipを抑制することができ、MRAMデバイスの低消費電力化を図ることができる。

【0263】

また、リードビット線RBLが、アクセストランジスタATRを介して磁気トンネル接合部MTJと接合されるので、リードビット線RBLに結合される磁気トンネル接合部MTJの数を削減して、リードビット線RBLの容量を低減して、データ読出を高速化することができる。

【0264】

図39は、実施の形態6の変形例6に従うMTJメモリセルの配置を示す構造図である。

【0265】

図39を参照して、リードビット線RBLは、第1の金属配線層M1に、アクセストランジスタATRのソース/ドレイン領域110と電気的に結合するように設けられる。リードワード線RWLは、アクセストランジスタATRのゲート130と同一層に配置される。アクセストランジスタATRのソース/ドレイン領域120は、第1および第2の金属配線層M1およびM2に設けられた金属配線、バリアメタル140およびコンタクトホールに設けられた金属膜150を介して、磁気トンネル接合部MTJと結合される。

【0266】

磁気トンネル接合部MTJは、第2の金属配線層M2および第3の金属配線層M3の間に配置される。ライトビット線WBLは、磁気トンネル接合部MTJと電気的に結合されて、第3の金属配線層M3に配置される。ライトワード線WWLは、第2の金属配線層に設けられる。この際に、ライトワード線WWLの配置は、磁気トンネル接合部MTJとの間における磁気カップリングを高めることができるように配置される。

【0267】

図40は、実施の形態6の変形例6に従うMTJメモリセルの配置の他の例を示す構造図である。

【0268】

図40に示される構成においては、同一方向に沿って配置されるリードビット線RBLおよびライトワード線WWLは、同一の金属配線層に配置される。したがって、磁気トンネル接合部MTJは、金属配線層M1およびM2の間に設けられ、ライトワード線WWLは、磁気トンネル接合部MTJと近接して、リードビット線RBLと同一の金属配線層M1に配置される。ライトビット線WBLは、磁気トンネル接合部MTJと電気的に結合されて、第2の金属配線層M2に配置される。

【0269】

したがって、図39に示したMTJメモリセルの構造と比較して、金属配線層数を減らすことができるので、実施の形態6の変形例6に従うMTJメモリセルの構成によって享受される効果に加えて、製造コストの削減がさらに可能になる。

【0270】

以上述べたように、実施の形態6およびその変形例1〜4,6に従うMTJメモリセルの構成によれば、リードワード線RWLとライトワード線WWLとを互いに直交する方向に配置できるので、それぞれのワード線を駆動するためのライトワード線ドライバ30wとリードワード線ドライバ30rとを分割配置して、レイアウトの自由度を向上することができる。

【0271】

また、実施の形態6の変形例1、4および5に従うMTJメモリセルの構成によれば、リードビット線RBLとライトワード線WWLとを共通配線CMLに集約できるので、配線数を削減して製造コストの低減を図ることができる。

【0272】

さらに、実施の形態6の変形例2、4および6に従うMTJメモリセルの構成によれば、リードビット線RBLをアクセストランジスタATRを介して磁気トンネル接合部MTJと結合するので、リードビット線RBLの容量を抑制してデータ読出を高速化することが可能である。

【0273】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0274】

【発明の効果】

請求項1記載の半導体集積回路は、データ書込時におけるデータ書込電流を短絡されたビット線対に往復電流として流すことができるので、データ書込電流を制御するための構成を簡素化できる。

【0275】

請求項2および3記載の半導体集積回路は、データ書込電流を供給するための回路を外部電源電位によって直接駆動するので、請求項1記載の半導体集積回路が奏する効果に加えて、データ書込電流を速やかに供給することができる。

【0276】

請求項4から8に記載の半導体集積回路は、アドレス選択の対象となるメモリセル列の位置に関わらずデータ書込電流の電流量をほぼ一定に維持することができる。この結果、請求項1記載の半導体集積回路が奏する効果に加えて、電力消費を無用に増加させることなくそれぞれのメモリセル列に対して書込動作マージンを確保できる。

【0277】

請求項9および10に記載の半導体集積回路は、請求項1記載の半導体集積回路が奏する効果に加えて、ビット線およびビット線電流回路を共有してデータ読出動作を実行することができる。

【0278】

請求項11記載の半導体集積回路は、データ書込電流を供給するための回路を外部電源電位によって直接駆動するとともに、データ読出に関する回路を外部電源電位を降圧した内部電源電位によって駆動するので、請求項9記載の半導体集積回路が奏する効果に加えて、データ書込電流の速やかな供給と、低消費電力化およびデバイスの微細化に対応した信頼性の確保とを両立することができる。

【0279】

請求項12記載の半導体集積回路は、データ線対を構成する第1および第2のデータ線の電位レベルの制御によって、開放型のビット線に流されるデータ書込電流の方向を設定できる。したがって、データ書込電流を制御するための構成を簡素化できる。

【0280】

請求項13および14に記載の半導体集積回路は、請求項12記載の半導体集積回路が奏する効果に加えて、ビット線およびビット線電流回路を共有してデータ読出動作をさらに実行することができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態1に従うMRAMデバイス1の全体構成を示す概略ブロック図である。

【図2】 メモリアレイ10およびその周辺の実施の形態1に従う構成を詳細に説明するための図である。

【図3】 実施の形態2に従う電源電位の供給系統を説明するブロック図である。

【図4】 メモリアレイ10およびその周辺の実施の形態3に従う構成を示すブロック図である。

【図5】 メモリアレイ10およびその周辺の実施の形態3の変形例1に従う構成を示すブロック図である。

【図6】 メモリアレイ10およびその周辺の実施の形態3の変形例2に従う構成を示すブロック図である。

【図7】 メモリアレイ10およびその周辺の実施の形態3の変形例3に従う構成を示すブロック図である。

【図8】 実施の形態4に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【図9】 実施の形態4の変形例1に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【図10】 実施の形態4の変形例2に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【図11】 実施の形態4の変形例3に従うメモリアレイ10周辺の構成のうち、データ書込に関連する部分を示すブロック図である。

【図12】 メモリアレイ10およびその周辺の実施の形態5に従う構成を示すブロック図である。

【図13】 電流切換回路56の構成を示すブロック図である。

【図14】 メモリアレイ10およびその周辺の実施の形態5の変形例に従う構成を示すブロック図である。

【図15】 電流切換回路58の構成を示すブロック図である。

【図16】 本発明の実施の形態6に従うMRAMデバイス2の全体構成を示す概略ブロック図である。

【図17】 実施の形態6に従うメモリアレイ10の構成を示すブロック図である。

【図18】 実施の形態6に従うMTJメモリセルの接続態様を示す回路図である。

【図19】 実施の形態6に従うMTJメモリセルに対するデータ書込およびデータ読出を説明するためのタイミングチャート図である。

【図20】 実施の形態6に従うMTJメモリセルの配置を説明する構造図である。

【図21】 実施の形態6の変形例1に従うメモリアレイ10の構成を示すブロック図である。

【図22】 実施の形態6の変形例1に従うMTJメモリセルの接続態様を示す回路図である。

【図23】 実施の形態6の変形例1に従うMTJメモリセルに対するデータ書込およびデータ読出を説明するためのタイミングチャート図である。

【図24】 実施の形態6の変形例1に従うMTJメモリセルの配置を説明する構造図である。

【図25】 実施の形態6の変形例2に従うメモリアレイ10の構成を示すブロック図である。

【図26】 実施の形態6の変形例2に従うMTJメモリセルの接続態様を示す回路図である。

【図27】 実施の形態6の変形例2に従うMTJメモリセルの配置を示す構造図である。

【図28】 実施の形態6の変形例3に従うメモリアレイ10の構成を示すブロック図である。

【図29】 実施の形態6の変形例3に従うMTJメモリセルの接続態様を示す回路図である。

【図30】 実施の形態6の変形例3に従うMJTメモリセルの配置を示す構造図である。

【図31】 実施の形態6の変形例4に従うメモリアレイ10の構成を示すブロック図である。

【図32】 実施の形態6の変形例4に従うMTJメモリセルの接続態様を示す回路図である。

【図33】 実施の形態6の変形例4に従うMTJメモリセルの配置を示す構造図である。

【図34】 実施の形態6の変形例5に従うメモリアレイ10の構成を示すブロック図である。

【図35】 実施の形態6の変形例5に従うMTJメモリセルの接続態様を示す回路図である。

【図36】 実施の形態6の変形例5に従うMTJメモリセルの配置を示す構造図である。

【図37】 実施の形態6の変形例6に従うメモリアレイ10の構成を示すブロック図である。

【図38】 実施の形態6の変形例6に従うMTJメモリセルの接続態様を示す回路図である。

【図39】 実施の形態6の変形例6に従うMTJメモリセルの配置を示す構造図である。

【図40】 実施の形態6の変形例6に従うMTJメモリセルの配置の他の例を示す構造図である。

【図41】 磁気トンネル接合部を有するメモリセルの構成を示す概略図である。

【図42】 MTJメモリセルからのデータ読出動作を説明する概念図である。

【図43】 MTJメモリセルに対するデータ書込動作を説明する概念図である。

【図44】 データ書込時におけるデータ書込電流の方向と磁界方向との関係を説明する概念図である。

【図45】 行列状に集積配置されたMTJメモリセルを示す概念図である。

【図46】 半導体基板上に配置されたMTJメモリセルの構造図である。

【符号の説明】

10 メモリアレイ、20 行デコーダ、25 列デコーダ、30 ワード線ドライバ、30r リードワード線ドライバ、30w ライトワード線ドライバ、40 ワード線電流制御回路、41−1〜41−m,41−n 電流制御トランジスタ、50,60 読出/書込制御回路、50w、60w 書込制御回路、50r 読出制御回路、51 データ書込電流制御回路、52 データ読出回路、55 電圧降下回路、62−1〜62−m イコライズトランジスタ、64−1〜64−m 電流制御トランジスタ、ATR アクセストランジスタ、BL,/BL ビット線、CSG1〜CSGm 列選択ゲート、FL 固定磁気層、MTJ 磁気トンネル接合部、RBL リードビット線、RWL リードワード線、TB トンネルバリア、VL 自由磁気層、WBL,/WBL ライトビット線、WWL ライトワード線、CML 共通配線。

Claims (14)

- 半導体集積回路であって、

複数行および複数列の行列状に配置された複数の磁性体メモリセルを有するメモリアレイを備え、

前記複数の磁性体メモリセルの各々は、第1および第2のデータ書込電流によって印加されるデータ書込磁界が所定磁界よりも大きい場合に書込まれる記憶データのレベルに応じて異なる抵抗値を有し、

前記磁性体メモリセルの行にそれぞれ対応して設けられ、データ書込時において前記第1のデータ書込電流を流すためにアドレス選択結果に応じて選択的に活性化される書込ワード線と、

前記磁性体メモリセルの列にそれぞれ対応して設けられたビット線対とを備え、

前記ビット線対は、第1および第2のビット線を含み、

前記複数の磁性体メモリセルの各々は、各前記書込ワード線が各前記第1および第2のビット線と交差する位置の一方に対応させて前記行ごとに交互配置され、

前記データ書込時において、アドレス選択結果に応じて選択される前記ビット線対に含まれる前記第1および第2のビット線の一端を高電位状態および低電位状態の一方ずつに設定するためのデータ書込制御回路と、

前記ビット線対にそれぞれ対応して設けられたビット線電流制御回路とをさらに備え、

前記ビット線電流制御回路は、前記データ書込時において前記第2のデータ書込電流を流すために対応する前記第1および第2のビット線の他端の間を電気的に結合する、半導体集積回路。 - 前記データ書込制御回路は、前記半導体集積回路に対して外部から供給された外部電源電位によって駆動される、請求項1記載の半導体集積回路。

- 前記複数行の前記書込ワード線を前記アドレス選択結果に応じて選択的に活性状態に駆動するためのワード線駆動回路と、

各前記書込ワード線を前記書込ワード線の非活性状態に対応する電位と結合するためのワード線電流制御回路とをさらに備え、

前記ワード線駆動回路は、前記外部電源電位によって駆動される、請求項2記載の半導体集積回路。 - 前記複数列の前記ビット線対に共通に設けられ、第1および第2のデータ線によって形成されるデータ線対と、

前記列にそれぞれ対応して設けられた列選択ゲート回路とさらに備え、

前記列選択ゲート回路は、前記アドレス選択結果に応じて、対応する前記第1および第2のビット線を前記第1および第2のデータ線とそれぞれ接続し、

前記データ書込制御回路は、前記データ書込時において、第1および第2の内部ノードを前記高電位状態および低電位状態の一方ずつに設定し、

前記第1および第2の内部ノードと前記第1および第2のデータ線との接続点は、前記第2のデータ書込電流の経路を形成する配線の抵抗値が、アドレス選択の対象となる前記列の位置に関わらずほぼ一定となるように設けられる、請求項1記載の半導体集積回路。 - 各前記ビット線対は、前記列に沿った方向に配置され、

前記データ線対は、前記行に沿った方向に配置され、

前記第1の内部ノードは、先頭の前記列側の領域において前記第1のデータ線と接続され、

前記第2の内部ノードは、最終の前記列側の領域において前記第2のデータ線と接続される、請求項4記載の半導体集積回路。 - 各前記ビット線対は、前記列に沿った方向に配置され、

前記データ線対は、前記行に沿った方向に配置され、

前記第1および第2の内部ノードは、中央の前記列周辺の領域において、前記第1および第2のデータ線とそれぞれ接続される、請求項4記載の半導体集積回路。 - 前記複数列は、M個(M:2以上の自然数)の列ずつの列グループに分割され、

前記半導体集積回路は、

前記列グループごとに配置された、第1および第2のデータ線によって形成されるデータ線対と、

前記列にそれぞれ対応して設けられた列選択ゲート回路とをさらに備え、

各前記列選択ゲート回路は、前記アドレス選択結果に応じて、対応する前記第1および第2のビット線を対応する前記第1および第2のデータ線とそれぞれ接続するように動作し、

前記データ書込制御回路は、前記列グループごとに前記データ線対に対応して設けられ、

各前記データ書込制御回路は、前記データ書込時においてアドレス選択結果に応じて動作して、対応する前記第1および第2のデータ線を前記高電位状態および低電位状態の一方ずつに設定する、請求項1記載の半導体集積回路。 - 前記データ線対は、前記ビット線対と同一方向に沿って、対応する前記列グループに属するM個の前記列の中央部に配置される、請求項7記載の半導体集積回路。

- 前記行にそれぞれ対応して設けられ、データ読出時においてアドレス選択結果に応じて活性化されて対応する磁性体メモリセルを対応するビット線対と結合するための読出ワード線と、

データ読出時において、アドレス選択結果に応じて選択される前記ビット線対に含まれる前記第1および第2のビット線に対してデータ読出電流を供給するためのデータ読出制御回路とをさらに備え、

前記データ読出時において、各前記ビット線電流制御回路は、対応する前記第1および第2のビット線の間を開放する、請求項1記載の半導体集積回路。 - 前記第1のビット線にそれぞれ対応して設けられた第1のダミーメモリセルと、

前記第2のビット線にそれぞれ対応して設けられた第2のダミーメモリセルと、

前記複数列の前記第1のダミーメモリセルに共通に設けられ、各前記第1のダミーメモリセルを対応する前記第1のビット線とそれぞれ結合するために、前記データ読出時においてアドレス選択結果に応じて活性化される第1のダミー読出ワード線と、

前記複数列の前記第2のダミーメモリセルに共通に設けられ、各前記第2のダミーメモリセルを対応する前記第2のビット線とそれぞれ結合するために、前記データ読出時においてアドレス選択結果に応じて活性化される第2のダミー読出ワード線と、

前記データ読出時において、前記複数行の前記読出ワード線のうちの1つと前記第1および第2のダミー読出ワード線のうちの一方とを、前記アドレス選択結果に応じて選択的に活性化するワード線駆動回路とをさらに備え、

前記第1および第2のダミーメモリセルの各々は、前記磁性体メモリセルが前記記憶データのレベルに応じて有する第1および第2の抵抗値の中間の抵抗値を有する、請求項9記載の半導体集積回路。 - 前記半導体集積回路に対して外部から供給された外部電源電位を降圧して内部電源電位を生成する電圧降下回路をさらに備え、

前記データ書込制御回路は、前記外部電源電位によって駆動され、

前記データ読出制御回路は、前記内部電源電位によって駆動される、請求項9記載の半導体集積回路。 - 半導体集積回路であって、

複数行および複数列の行列状に配置された複数の磁性体メモリセルを有するメモリアレイを備え、

前記複数の磁性体メモリセルの各々は、第1および第2のデータ書込電流によって印加されるデータ書込磁界が所定磁界よりも大きい場合に書込まれる記憶データのレベルに応じて異なる抵抗値を有し、

前記磁性体メモリセルの行にそれぞれ対応して設けられ、データ書込時においてアドレス選択結果に応じて前記第1のデータ書込電流を流すための書込ワード線と、

前記磁性体メモリセルの列にそれぞれ対応して設けられるビット線と、

前記複数列の前記ビット線に共通に設けられたデータ線対とをさらに備え、

前記データ線対は、第1および第2のデータ線によって形成され、

前記データ書込時において、前記第1および第2のデータ線を高電位状態および低電位状態の一方ずつに設定するためのデータ書込制御回路と、

前記列にそれぞれ対応して設けられた列選択ゲート回路と、

前記列にそれぞれ対応して設けられたビット線電流制御回路とをさらに備え、

各前記列選択ゲート回路は、前記アドレス選択結果に応じて対応する前記ビット線の一端を前記第1のデータ線と接続し、

前記ビット線電流制御回路は、前記データ書込時において前記第2のデータ書込電流を流すために、前記対応する前記ビット線の他端と前記第2のデータ線との間を電気的に結合する、半導体集積回路。 - 前記データ書込制御回路は、前記データ書込時において、第1および第2の内部ノードを前記高電位状態および低電位状態の一方ずつに設定し、

各前記ビット線電流制御回路は、前記アドレス選択結果に応じて、前記対応する前記ビット線と前記第2のデータ線との間を電気的に結合し、

前記半導体集積回路は、

データ読出時においてデータ読出電流を第3の内部ノードに供給するためのデータ読出制御回路と、

前記データ書込時において、前記第1および第2の内部ノードと前記第1および第2のデータ線とをそれぞれ結合するための接続切換回路とをさらに備え、

前記接続切換回路は、前記データ読出時において、前記第1および第2のデータ線を、前記第3の内部ノードおよび読出基準電位を供給する第4の内部ノードとそれぞれ電気的に結合し、

前記データ読出制御回路は、前記読出基準電位と前記第3の内部ノードとの間の電位差に基づいて前記データ読出を行なう、請求項12記載の半導体集積回路。 - 前記データ書込制御回路は、前記データ書込時において、第1および第2の内部ノードを前記高電位状態および低電位状態の一方ずつに設定し、

各前記ビット線電流制御回路は、データ読出前のプリチャージ時において前記対応する前記ビット線と前記第2のデータ線との間を電気的に結合するとともに、データ読出時において前記対応する前記ビット線と前記第2のデータ線との間を電気的に切り離し、

前記半導体集積回路は、

前記データ読出時においてデータ読出電流を前記第1のデータ線に供給するためのデータ読出制御回路と、

前記データ書込時において、前記第1および第2の内部ノードと前記第1および第2のデータ線とをそれぞれ結合するための接続切換回路とをさらに備え、

前記接続切換回路は、前記プリチャージ時において、前記第1および第2のデータ線を、読出基準電位を供給する第3および第4の内部ノードとそれぞれ電気的に結合するとともに、前記データ読出時において、前記第1および第2のデータ線を前記第1から第4の内部ノードから切り離し、

前記データ読出制御回路は、前記読出基準電位と前記第1のデータ線との間の電位差に基づいて前記データ読出を行なう、請求項12記載の半導体集積回路。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000316867A JP4726290B2 (ja) | 2000-10-17 | 2000-10-17 | 半導体集積回路 |

| US09/805,043 US6359805B1 (en) | 2000-10-17 | 2001-03-14 | Thin film magnetic memory device capable of easily controlling a data write current |

| DE10119499A DE10119499A1 (de) | 2000-10-17 | 2001-04-20 | Dünnfilm-Magnetspeichervorrichtung zum leichten Steuern eines Datenschreibstroms |

| CNB011220864A CN1207718C (zh) | 2000-10-17 | 2001-05-21 | 容易控制数据写入电流的薄膜磁性体存储器 |

| KR10-2001-0027670A KR100436669B1 (ko) | 2000-10-17 | 2001-05-21 | 데이터 기입 전류의 제어가 용이한 박막 자성체 기억 장치 |

| TW090112199A TW512336B (en) | 2000-10-17 | 2001-05-22 | Thin film magnetic memory device |

| US10/096,481 US6542402B2 (en) | 2000-10-17 | 2002-03-13 | Thin film magnetic memory device capable of easily controlling a data write current |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000316867A JP4726290B2 (ja) | 2000-10-17 | 2000-10-17 | 半導体集積回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010232642A Division JP5165040B2 (ja) | 2010-10-15 | 2010-10-15 | 半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002124079A JP2002124079A (ja) | 2002-04-26 |

| JP2002124079A5 JP2002124079A5 (ja) | 2007-11-22 |

| JP4726290B2 true JP4726290B2 (ja) | 2011-07-20 |

Family

ID=18795755

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000316867A Expired - Fee Related JP4726290B2 (ja) | 2000-10-17 | 2000-10-17 | 半導体集積回路 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US6359805B1 (ja) |

| JP (1) | JP4726290B2 (ja) |

| KR (1) | KR100436669B1 (ja) |

| CN (1) | CN1207718C (ja) |

| DE (1) | DE10119499A1 (ja) |

| TW (1) | TW512336B (ja) |

Families Citing this family (66)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6244331B1 (en) * | 1999-10-22 | 2001-06-12 | Intel Corporation | Heatsink with integrated blower for improved heat transfer |

| JP2002170377A (ja) * | 2000-09-22 | 2002-06-14 | Mitsubishi Electric Corp | 薄膜磁性体記憶装置 |

| JP4726292B2 (ja) | 2000-11-14 | 2011-07-20 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP4667594B2 (ja) | 2000-12-25 | 2011-04-13 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP2002270790A (ja) * | 2000-12-27 | 2002-09-20 | Toshiba Corp | 半導体記憶装置 |

| JP2002208682A (ja) * | 2001-01-12 | 2002-07-26 | Hitachi Ltd | 磁気半導体記憶装置及びその製造方法 |

| JP3812805B2 (ja) * | 2001-01-16 | 2006-08-23 | 日本電気株式会社 | トンネル磁気抵抗素子を利用した半導体記憶装置 |

| JP2002299584A (ja) * | 2001-04-03 | 2002-10-11 | Mitsubishi Electric Corp | 磁気ランダムアクセスメモリ装置および半導体装置 |

| JP5019681B2 (ja) * | 2001-04-26 | 2012-09-05 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP4731041B2 (ja) * | 2001-05-16 | 2011-07-20 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP2002368196A (ja) * | 2001-05-30 | 2002-12-20 | Internatl Business Mach Corp <Ibm> | メモリセル、記憶回路ブロック、データの書き込み方法及びデータの読み出し方法 |

| JP2003077282A (ja) * | 2001-08-31 | 2003-03-14 | Fujitsu Ltd | 不揮発性半導体記憶装置 |

| US6545906B1 (en) * | 2001-10-16 | 2003-04-08 | Motorola, Inc. | Method of writing to scalable magnetoresistance random access memory element |

| KR100446616B1 (ko) * | 2001-10-18 | 2004-09-04 | 삼성전자주식회사 | 단일 트랜지스터형 자기 랜덤 액세스 메모리 소자와 그구동 및 제조방법 |

| JP2003151262A (ja) * | 2001-11-15 | 2003-05-23 | Toshiba Corp | 磁気ランダムアクセスメモリ |

| JP2003196973A (ja) * | 2001-12-21 | 2003-07-11 | Mitsubishi Electric Corp | 薄膜磁性体記憶装置 |

| US6735111B2 (en) * | 2002-01-16 | 2004-05-11 | Micron Technology, Inc. | Magnetoresistive memory devices and assemblies |

| US6512689B1 (en) * | 2002-01-18 | 2003-01-28 | Motorola, Inc. | MRAM without isolation devices |

| US6760244B2 (en) * | 2002-01-30 | 2004-07-06 | Sanyo Electric Co., Ltd. | Magnetic memory device including storage elements exhibiting a ferromagnetic tunnel effect |

| JP4218527B2 (ja) * | 2002-02-01 | 2009-02-04 | 株式会社日立製作所 | 記憶装置 |

| US6791885B2 (en) * | 2002-02-19 | 2004-09-14 | Micron Technology, Inc. | Programmable conductor random access memory and method for sensing same |

| US6606263B1 (en) * | 2002-04-19 | 2003-08-12 | Taiwan Semiconductor Manufacturing Company | Non-disturbing programming scheme for magnetic RAM |

| JP4071531B2 (ja) * | 2002-04-23 | 2008-04-02 | 株式会社ルネサステクノロジ | 薄膜磁性体記憶装置 |

| KR100505104B1 (ko) * | 2002-04-30 | 2005-07-29 | 삼성전자주식회사 | 자기 램 셀들, 그 구조체들 및 그 구동방법 |

| US6940748B2 (en) * | 2002-05-16 | 2005-09-06 | Micron Technology, Inc. | Stacked 1T-nMTJ MRAM structure |

| KR100448853B1 (ko) * | 2002-05-20 | 2004-09-18 | 주식회사 하이닉스반도체 | 마그네틱 램 |

| JP2004013961A (ja) * | 2002-06-04 | 2004-01-15 | Mitsubishi Electric Corp | 薄膜磁性体記憶装置 |

| JP4208498B2 (ja) | 2002-06-21 | 2009-01-14 | 株式会社ルネサステクノロジ | 薄膜磁性体記憶装置 |

| JP4646485B2 (ja) * | 2002-06-25 | 2011-03-09 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| US6711052B2 (en) * | 2002-06-28 | 2004-03-23 | Motorola, Inc. | Memory having a precharge circuit and method therefor |

| US6657889B1 (en) * | 2002-06-28 | 2003-12-02 | Motorola, Inc. | Memory having write current ramp rate control |

| US6680863B1 (en) * | 2002-07-09 | 2004-01-20 | Western Digital (Fremont), Inc. | MRAM memory array having merged word lines |

| US7095646B2 (en) * | 2002-07-17 | 2006-08-22 | Freescale Semiconductor, Inc. | Multi-state magnetoresistance random access cell with improved memory storage density |

| JP4679036B2 (ja) * | 2002-09-12 | 2011-04-27 | ルネサスエレクトロニクス株式会社 | 記憶装置 |

| JP4632625B2 (ja) * | 2002-11-14 | 2011-02-16 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP4266302B2 (ja) | 2002-11-27 | 2009-05-20 | 株式会社ルネサステクノロジ | 不揮発性記憶装置 |

| KR20040083934A (ko) | 2003-03-25 | 2004-10-06 | 주식회사 하이닉스반도체 | 마그네틱 램의 형성방법 |

| ATE427550T1 (de) * | 2003-06-05 | 2009-04-15 | Nxp Bv | Integritatssteuerung fur in einem nichtfluchtigen speicher gespeicherte daten |

| US6956763B2 (en) * | 2003-06-27 | 2005-10-18 | Freescale Semiconductor, Inc. | MRAM element and methods for writing the MRAM element |

| US6967366B2 (en) * | 2003-08-25 | 2005-11-22 | Freescale Semiconductor, Inc. | Magnetoresistive random access memory with reduced switching field variation |

| US6947313B2 (en) * | 2003-08-27 | 2005-09-20 | Hewlett-Packard Development Company, L.P. | Method and apparatus of coupling conductors in magnetic memory |

| ATE366985T1 (de) * | 2003-09-04 | 2007-08-15 | Koninkl Philips Electronics Nv | Integrierte schaltung und verfahren zum cache- umabbilden |

| US6842365B1 (en) * | 2003-09-05 | 2005-01-11 | Freescale Semiconductor, Inc. | Write driver for a magnetoresistive memory |

| US6961263B2 (en) * | 2003-09-08 | 2005-11-01 | Hewlett-Packard Development Company, L.P. | Memory device with a thermally assisted write |

| CN100429721C (zh) * | 2004-04-01 | 2008-10-29 | 中国科学院物理研究所 | 一种基于垂直电流写入的磁随机存取存储器及其控制方法 |

| US7129098B2 (en) * | 2004-11-24 | 2006-10-31 | Freescale Semiconductor, Inc. | Reduced power magnetoresistive random access memory elements |

| US7239537B2 (en) * | 2005-01-12 | 2007-07-03 | International Business Machines Corporation | Method and apparatus for current sense amplifier calibration in MRAM devices |

| EP1844471A1 (en) * | 2005-01-24 | 2007-10-17 | Nxp B.V. | Magnetic rom information carrier with additional stabilizing layer |

| US20070076470A1 (en) * | 2005-09-13 | 2007-04-05 | Northern Lights Semiconductor Corp. | Magnetic Random Access Memory Device and Sensing Method Thereof |

| KR20080055879A (ko) * | 2005-10-07 | 2008-06-19 | 코니카 미놀타 옵토 인코포레이티드 | 셀룰로오스 에스테르 필름의 제조 방법, 셀룰로오스에스테르 필름, 편광판 및 액정 표시 장치 |

| US7206223B1 (en) * | 2005-12-07 | 2007-04-17 | Freescale Semiconductor, Inc. | MRAM memory with residual write field reset |

| US7280388B2 (en) * | 2005-12-07 | 2007-10-09 | Nahas Joseph J | MRAM with a write driver and method therefor |

| US7523366B2 (en) * | 2005-12-09 | 2009-04-21 | Taiwan Semiconductor Manufacturing Co., Ltd. | Storage efficient memory system with integrated BIST function |

| US7370250B2 (en) * | 2005-12-21 | 2008-05-06 | Etron Technology, Inc. | Test patterns to insure read signal integrity for high speed DDR DRAM |

| US20080068878A1 (en) * | 2006-09-14 | 2008-03-20 | Thomas Nirschl | Resistive memory having shunted memory cells |

| US7688616B2 (en) * | 2007-06-18 | 2010-03-30 | Taiwan Semicondcutor Manufacturing Company, Ltd. | Device and method of programming a magnetic memory element |

| JP5127435B2 (ja) * | 2007-11-01 | 2013-01-23 | パナソニック株式会社 | 半導体記憶装置 |

| JP5150936B2 (ja) * | 2007-12-28 | 2013-02-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5388525B2 (ja) * | 2008-09-25 | 2014-01-15 | 株式会社東芝 | プログラマブル論理回路 |

| JP4679627B2 (ja) * | 2008-10-29 | 2011-04-27 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| JP5010650B2 (ja) * | 2009-08-11 | 2012-08-29 | 株式会社東芝 | 磁気抵抗メモリ |

| JP2012069175A (ja) * | 2010-09-21 | 2012-04-05 | Renesas Electronics Corp | 半導体装置 |

| JP5698651B2 (ja) * | 2011-12-16 | 2015-04-08 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| US10043767B2 (en) * | 2013-10-24 | 2018-08-07 | Taiwan Semiconductor Manufacturing Co., Ltd | Semiconductor device including dummy conductive cells |

| CN106297875B (zh) * | 2016-08-18 | 2019-02-05 | 佛山中科芯蔚科技有限公司 | 一种静态随机存储器的读取方法及系统 |

| CN114974339A (zh) * | 2021-02-22 | 2022-08-30 | 联华电子股份有限公司 | 存储器阵列 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5640343A (en) | 1996-03-18 | 1997-06-17 | International Business Machines Corporation | Magnetic memory array using magnetic tunnel junction devices in the memory cells |

| US5650958A (en) | 1996-03-18 | 1997-07-22 | International Business Machines Corporation | Magnetic tunnel junctions with controlled magnetic response |

| US5835314A (en) | 1996-04-17 | 1998-11-10 | Massachusetts Institute Of Technology | Tunnel junction device for storage and switching of signals |

| US5734605A (en) | 1996-09-10 | 1998-03-31 | Motorola, Inc. | Multi-layer magnetic tunneling junction memory cells |

| JP3392657B2 (ja) * | 1996-09-26 | 2003-03-31 | 株式会社東芝 | 半導体記憶装置 |

| JPH11306750A (ja) * | 1998-04-20 | 1999-11-05 | Univ Kyoto | 磁気型半導体集積記憶装置 |

| US6055179A (en) * | 1998-05-19 | 2000-04-25 | Canon Kk | Memory device utilizing giant magnetoresistance effect |

| JPH11354728A (ja) * | 1998-06-09 | 1999-12-24 | Canon Inc | 磁性薄膜メモリおよびその記録再生駆動方法 |

| US6034887A (en) * | 1998-08-05 | 2000-03-07 | International Business Machines Corporation | Non-volatile magnetic memory cell and devices |

| US6172903B1 (en) * | 1998-09-22 | 2001-01-09 | Canon Kabushiki Kaisha | Hybrid device, memory apparatus using such hybrid devices and information reading method |

| TW440835B (en) * | 1998-09-30 | 2001-06-16 | Siemens Ag | Magnetoresistive memory with raised interference security |

| JP2000173269A (ja) * | 1998-12-08 | 2000-06-23 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US6191972B1 (en) * | 1999-04-30 | 2001-02-20 | Nec Corporation | Magnetic random access memory circuit |

| US6215707B1 (en) * | 2000-04-10 | 2001-04-10 | Motorola Inc. | Charge conserving write method and system for an MRAM |

| JP4020573B2 (ja) * | 2000-07-27 | 2007-12-12 | 富士通株式会社 | 磁性メモリデバイス、および磁性メモリデバイスにおけるデータ読み出し方法 |

-

2000

- 2000-10-17 JP JP2000316867A patent/JP4726290B2/ja not_active Expired - Fee Related

-

2001

- 2001-03-14 US US09/805,043 patent/US6359805B1/en not_active Expired - Lifetime

- 2001-04-20 DE DE10119499A patent/DE10119499A1/de not_active Ceased

- 2001-05-21 KR KR10-2001-0027670A patent/KR100436669B1/ko not_active IP Right Cessation

- 2001-05-21 CN CNB011220864A patent/CN1207718C/zh not_active Expired - Fee Related

- 2001-05-22 TW TW090112199A patent/TW512336B/zh not_active IP Right Cessation

-

2002

- 2002-03-13 US US10/096,481 patent/US6542402B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002124079A (ja) | 2002-04-26 |

| US6542402B2 (en) | 2003-04-01 |

| KR20020030696A (ko) | 2002-04-25 |

| US20020044481A1 (en) | 2002-04-18 |

| CN1349226A (zh) | 2002-05-15 |

| CN1207718C (zh) | 2005-06-22 |

| DE10119499A1 (de) | 2002-04-25 |

| US6359805B1 (en) | 2002-03-19 |

| KR100436669B1 (ko) | 2004-06-22 |

| TW512336B (en) | 2002-12-01 |

| US20020093849A1 (en) | 2002-07-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4726290B2 (ja) | 半導体集積回路 | |

| JP4726292B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4667594B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4656720B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4712204B2 (ja) | 記憶装置 | |

| JP4242117B2 (ja) | 記憶装置 | |

| KR100654266B1 (ko) | 자기 터널 접합부를 갖는 박막 자성체 기억 장치 | |

| JP4637388B2 (ja) | 薄膜磁性体記憶装置 | |

| KR100483409B1 (ko) | 고속 데이터 판독과 동작 안정화를 양립하는 박막 자성체기억 장치 | |

| US20040001353A1 (en) | Thin film magnetic memory device suppressing internal magnetic noises | |

| JP5138056B2 (ja) | 薄膜磁性体記憶装置 | |

| JP5230783B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4262954B2 (ja) | 薄膜磁性体記憶装置 | |

| JP5165040B2 (ja) | 半導体集積回路 | |

| JP5036854B2 (ja) | 半導体装置 | |

| JP5100807B2 (ja) | 薄膜磁性体記憶装置 | |

| JP5153844B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4524462B2 (ja) | 半導体装置 | |

| JP2008276943A (ja) | 記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071004 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071004 |

|

| A711 | Notification of change in applicant |