JP4242117B2 - 記憶装置 - Google Patents

記憶装置 Download PDFInfo

- Publication number

- JP4242117B2 JP4242117B2 JP2002202659A JP2002202659A JP4242117B2 JP 4242117 B2 JP4242117 B2 JP 4242117B2 JP 2002202659 A JP2002202659 A JP 2002202659A JP 2002202659 A JP2002202659 A JP 2002202659A JP 4242117 B2 JP4242117 B2 JP 4242117B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory cell

- lines

- row

- column

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000005291 magnetic effect Effects 0.000 claims description 60

- 230000004044 response Effects 0.000 claims description 16

- 230000004913 activation Effects 0.000 claims description 11

- 239000011159 matrix material Substances 0.000 claims description 6

- 230000008878 coupling Effects 0.000 claims description 3

- 238000010168 coupling process Methods 0.000 claims description 3

- 238000005859 coupling reaction Methods 0.000 claims description 3

- 239000002184 metal Substances 0.000 description 28

- 238000010586 diagram Methods 0.000 description 24

- 230000005415 magnetization Effects 0.000 description 23

- 230000005641 tunneling Effects 0.000 description 16

- 101100166255 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CEP3 gene Proteins 0.000 description 11

- 239000010408 film Substances 0.000 description 9

- 230000002093 peripheral effect Effects 0.000 description 9

- 239000012535 impurity Substances 0.000 description 8

- 101100329534 Haloarcula marismortui (strain ATCC 43049 / DSM 3752 / JCM 8966 / VKM B-1809) csg1 gene Proteins 0.000 description 7

- 101100422777 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) SUR1 gene Proteins 0.000 description 7

- 239000010409 thin film Substances 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 238000013500 data storage Methods 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 102100023388 ATP-dependent RNA helicase DHX15 Human genes 0.000 description 2

- 101000907886 Homo sapiens ATP-dependent RNA helicase DHX15 Proteins 0.000 description 2

- 101000907912 Homo sapiens Pre-mRNA-splicing factor ATP-dependent RNA helicase DHX16 Proteins 0.000 description 2

- 102100023390 Pre-mRNA-splicing factor ATP-dependent RNA helicase DHX16 Human genes 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000005294 ferromagnetic effect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 101100499346 Caenorhabditis elegans dld-1 gene Proteins 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

- Semiconductor Memories (AREA)

Description

【発明の属する技術分野】

この発明は、記憶装置に関し、より特定的には、薄膜磁性体記憶装置に代表される、記憶データのデータレベルに応じて異なる電気抵抗値を有するメモリセルを備えた記憶装置に関する。

【0002】

【従来の技術】

低消費電力で不揮発的なデータ記憶が可能な記憶装置として、MRAMデバイスが注目されている。MRAMデバイスは、半導体集積回路に形成された複数の薄膜磁性体を用いて、不揮発的なデータ記憶を行ない薄膜磁性体の各々をメモリセルとして、ランダムアクセスが可能な記憶装置である。

【0003】

特に、近年では磁気トンネル接合を利用した薄膜磁性体をメモリセルとして用いることによって、MRAMデバイスの性能が飛躍的に進歩することが発表されている。磁気トンネル接合を有するメモリセルを備えたMRAMデバイスについては、“A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell", ISSCC Digest of Technical Papers, TA7.2, Feb. 2000.、 “Nonvolatile RAM based on Magnetic Tunnel Junction Elements", ISSCC Digest of Technical Papers, TA7.3, Feb. 2000. 、および“A 256kb 3.0V 1T1MTJ Nonvolatile Magnetoresistive RAM", ISSCC Digest of Technical Papers, TA7.6, Feb. 2001.等の技術文献に開示されている。

【0004】

図16は、磁気トンネル接合部を有するメモリセル(以下、単に「MTJメモリセル」とも称する)の構成を示す概略図である。

【0005】

図16を参照して、MTJメモリセルは、磁気的に書込まれた記憶データのデータレベルに応じて電気抵抗が変化するトンネル磁気抵抗素子TMRと、アクセストランジスタATRとを含む。アクセストランジスタATRは、ビット線BLおよびソース線SLの間に、トンネル磁気抵抗素子TMRと直列に接続される。代表的には、アクセストランジスタATRとして、半導体基板上に形成された電界効果型トランジスタが適用される。

【0006】

MTJメモリセルに対しては、データ書込時に異なった方向のデータ書込電流をそれぞれ流すためのビット線BLおよびディジット線DLと、データ読出を指示するためのワード線WLと、データ読出時にトンネル磁気抵抗素子TMRを固定電圧(たとえば、接地電圧GND)にプルダウンするためのソース線SLとが設けられる。データ読出時においては、アクセストランジスタATRのターンオンに応答して、トンネル磁気抵抗素子TMRは、ソース線SLおよびビット線BLの間に電気的に結合される。

【0007】

図17は、MTJメモリセルに対するデータ書込動作を説明する概念図である。

【0008】

図17を参照して、トンネル磁気抵抗素子TMRは、固定された一定の磁化方向を有する強磁性体層(以下、単に「固定磁化層」とも称する)FLと、外部かの印加磁界に応じた方向に磁化される強磁性体層(以下、単に「自由磁化層」とも称する)VLとを有する。固定磁化層FLおよび自由磁化層VLの間には、絶縁体膜で形成されるトンネルバリア(トンネル膜)TBが設けられる。自由磁化層VLは、書込まれる記憶データのレベルに応じて、固定磁化層FLと同一方向または固定磁化層FLと反対方向に磁化される。これらの固定磁化層FL、トンネルバリアTBおよび自由磁化層VLによって、磁気トンネル接合が形成される。

【0009】

トンネル磁気抵抗素子TMRの電気抵抗は、固定磁化層FLおよび自由磁化層VLのそれぞれの磁化方向の相対関係に応じて変化する。具体的には、トンネル磁気抵抗素子TMRの電気抵抗は、固定磁化層FLの磁化方向と自由磁化層VLの磁化方向とが同じ(平行)である場合に最小値Rminとなり、両者の磁化方向が反対(反平行)方向である場合に最大値Rmaxとなる。

【0010】

データ書込時においては、ワード線WLが非活性化されて、アクセストランジスタATRはターンオフされる。この状態で、自由磁化層VLを磁化するためのデータ書込電流は、ビット線BLおよびディジット線DLのそれぞれにおいて、書込データのレベルに応じた方向に流される。

【0011】

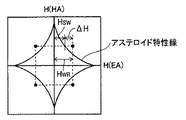

図18は、データ書込時におけるデータ書込電流とトンネル磁気抵抗素子の磁化方向との関係を示す概念図である。

【0012】

図18を参照して、横軸H(EA)は、トンネル磁気抵抗素子TMR内の自由磁化層VLにおいて磁化容易軸(EA:Easy Axis)方向に印加される磁界を示す。一方、縦軸H(HA)は、自由磁化層VLにおいて磁化困難軸(HA:Hard Axis)方向に作用する磁界を示す。磁界H(EA)およびH(HA)は、ビット線BLおよびディジット線DLをそれぞれ流れる電流によって生じる2つの磁界の一方ずつにそれぞれ対応する。

【0013】

MTJメモリセルにおいては、固定磁化層FLの固定された磁化方向は、自由磁化層VLの磁化容易軸に沿っており、自由磁化層VLは、記憶データのレベル(“1”および“0”)に応じて、磁化容易軸方向に沿って、固定磁化層FLと平行あるいは反平行(反対)方向に磁化される。MTJメモリセルは、自由磁化層VLの2通りの磁化方向と対応させて、1ビットのデータ(“1”および“0”)を記憶することができる。

【0014】

自由磁化層VLの磁化方向は、印加される磁界H(EA)およびH(HA)の和が、図18に示されるアステロイド特性線の外側の領域に達する場合においてのみ新たに書換えることができる。すなわち、印加されたデータ書込磁界がアステロイド特性線の内側の領域に相当する強度である場合には、自由磁化層VLの磁化方向は変化しない。

【0015】

アステロイド特性線に示されるように、自由磁化層VLに対して磁化困難軸方向の磁界を印加することによって、磁化容易軸に沿った磁化方向を変化させるのに必要な磁化しきい値を下げることができる。

【0016】

図18に示した例のようにデータ書込時の動作点を設計した場合には、データ書込対象であるMTJメモリセルにおいて、磁化容易軸方向のデータ書込磁界は、その強度がHWRとなるように設計される。すなわち、このデータ書込磁界HWRが得られるように、ビット線BLまたはディジット線DLを流されるデータ書込電流の値が設計される。一般的に、データ書込磁界HWRは、磁化方向の切換えに必要なスイッチング磁界HSWと、マージン分ΔHとの和で示される。すなわち、HWR=HSW+ΔHで示される。

【0017】

MTJメモリセルの記憶データ、すなわちトンネル磁気抵抗素子TMRの磁化方向を書換えるためには、ディジット線DLとビット線BLとの両方に所定レベル以上のデータ書込電流を流す必要がある。これにより、トンネル磁気抵抗素子TMR中の自由磁化層VLは、磁化容易軸(EA)に沿ったデータ書込磁界の向きに応じて、固定磁化層FLと平行もしくは、反対(反平行)方向に磁化される。トンネル磁気抵抗素子TMRに一旦書込まれた磁化方向、すなわちMTJメモリセルの記憶データは、新たなデータ書込が実行されるまでの間不揮発的に保持される。

【0018】

図19は、MTJメモリセルからのデータ読出動作を説明する概念図である。図19を参照して、データ読出動作時においては、アクセストランジスタATRは、ワード線WLの活性化に応答してターンオンする。これにより、トンネル磁気抵抗素子TMRは、所定電圧Vssへプルダウンされた状態でビット線BLと電気的に結合される。

【0019】

この状態で、ビット線BLを所定電圧へプルアップすれば、ビット線BLおよびトンネル磁気抵抗素子TMRを含む電流経路を、トンネル磁気抵抗素子TMRの電気抵抗に応じた、すなわちMTJメモリセルの記憶データのレベルに応じたメモリセル電流Icellが通過する。たとえば、このメモリセル電流Icellを所定の基準電流Iref(図示せず)と比較することにより、MTJメモリセルから記憶データを読出すことができる。

【0020】

このようにトンネル磁気抵抗素子TMRは、印加されるデータ書込磁界によって書換可能な磁化方向に応じてその電気抵抗が変化するので、トンネル磁気抵抗素子TMRの電気抵抗RmaxおよびRminと、記憶データのレベル(“1”および“0”)とそれぞれ対応付けることによって、不揮発的なデータ記憶を実行することができる。

【0021】

【発明が解決しようとする課題】

このように、MRAMデバイスにおいては、記憶データレベルの違いに対応したトンネル磁気抵抗素子TMRでの接合抵抗差である電気抵抗差ΔR=(Rmax−Rmin)を利用してデータ記憶が実行される。すなわち、選択メモリセルを通過するメモリセル電流の検知に基づいてデータ読出が実行される。

【0022】

データ読出には、このようなメモリセル電流と比較される基準電流を生成するためのリファレンスセルが、データ記憶を実行するための正規メモリセルとは別に設けられる。すなわち、このようなリファレンスセルは、MTJメモリセルの2種類の電気抵抗RmaxおよびRminの中間値を有するように設計される。

【0023】

データ読出時には、選択メモリセルを含むメモリセル電流の電流経路(以下、「メモリセル電流経路」とも称する)と、リファレンスセルを含む基準電流の電流経路(以下、「基準電流経路」とも称する)とが設けられ、それぞれの通過電流の比較に基づいてデータ読出が実行される。

【0024】

一般的には、トンネル磁気抵抗素子の電気抵抗は数十KΩレベルであり、データ読出時にはトンネル磁気抵抗素子の両端に0.5V程度の低電圧を印加することによって、20μA程度のメモリセル電流が発生する。この場合に、上記の電気抵抗差ΔRによって生じる電流差は数μA程度であるので、選択メモリセルとリファレンスセルとの間の電気抵抗差の検知は、高感度の電流比較が必要とされる。

【0025】

したがって、これらの2つの電流経路において、選択メモリセルおよびリファレンスセルを除く経路部分の電気抵抗(以下、「経路抵抗」とも称する)が大きく異なれば、選択メモリセルおよびリファレンスセルの電気抵抗差を精度よく読出すことができなくなってしまい、データ読出精度が低下してしまう。

【0026】

一般的に、MRAMデバイスにおいては、MTJメモリセルは行列状に集積配置されるため、アドレス選択結果によって示される選択メモリセルの位置に依存して、少なくともメモリセル電流経路は変化する。したがって、アドレス選択結果に依存して、メモリセル電流経路および基準電流経路の間で、経路抵抗の差が変化しないように考慮する必要がある。なお、このような問題点は、MRAMデバイスのみならず、記憶データのレベルに応じて電気抵抗値が変化するメモリセルを備えた記憶装置に共通する。

【0027】

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、リファレンスセルと選択メモリセルとの電気抵抗差に基づいたデータ読出を行なう記憶装置において、データ読出マージンの向上を図ることである。

【0028】

【課題を解決するための手段】

この発明に従う記憶装置は、各々が記憶データに応じて2つのレベルの電気抵抗の一方を有する複数のメモリセルと、各々が複数のメモリセルのうちのデータ読出時の選択メモリセルの比較対象として設けられる複数の参照セルとが行列状に配置されたメモリアレイを備える。複数の参照セルは、行および列の一方に沿って、行および列の他方を複数のメモリセルと共有するように配置される。記憶装置は、行にそれぞれ対応して配置され、選択行において活性化される複数のワード線と、列にそれぞれ対応して配置される複数のデータ線と、行および列の一方にそれぞれ対応して配置され、各々が固定電圧を供給する複数のソース線とをさらに備える。複数のメモリセルの各々は、複数のデータ線の対応する1本と複数のソース線の対応する1本との間に直列に接続された、記憶データに応じて電気抵抗が変化する記憶素子および対応するワード線の活性化に応答してオンするアクセス素子を含み、複数のデータ線は、データ読出時に、複数のメモリセルのうちの、データ読出対象に選択された選択メモリセルと接続される第1のデータ線と、データ読出時に、複数の参照セルのうちの、選択メモリセルとの間で行および列の他方を共有する選択参照セルと接続される第2のデータ線とを含む。記憶装置は、データ読出時に第1および第2のデータ線を固定電圧と異なる電圧と結合して、選択メモリセルおよび選択参照セルをそれぞれ通過する第1および第2の電流経路を形成させるデータ読出回路をさらに備え、データ読出回路は、第1および第2の電流経路の電気抵抗差に基いて、選択メモリセルから記憶データを読出す。

【0029】

好ましくは、複数のデータ線の単位長当たりの電気抵抗は、複数のソース線の単位長当たりの電気抵抗よりも小さい。

【0030】

さらに好ましくは、複数のデータ線は、金属配線によって形成され、複数のソース線は、半導体基板上に、行および列の一方に延在して設けられた不純物拡散層によって形成される。

【0031】

また好ましくは、記憶装置は、メモリアレイに隣接する領域において、行および列の他方に沿って配置される固定電圧配線をさらに備え、複数のソース線の各々は、固定電圧配線と電気的に結合される。

【0032】

あるいは好ましくは、固定電圧配線の単位長当たりの電気抵抗は、複数のソース線の単位長当たりの電気抵抗よりも小さい。

【0033】

さらに好ましくは、記憶装置は、メモリアレイに隣接する領域において、行に沿って配置される第1および第2のデータバスをさらに備える。データ読出時において、第1および第2のデータ線は、第1および第2のデータバスを介してデータ読出回路と電気的に接続され、固定電圧配線の単位長当たりの電気抵抗は、複数のデータ線およびデータバスのうちの、固定電圧配線と同じ方向に配置される一方の単位長当たりの電気抵抗と同等に設計される。

【0034】

この発明の他の構成に従う記憶装置は、各々が記憶データに応じて2つのレベルの電気抵抗の一方を有する複数のメモリセルと、各々が複数のメモリセルのうちのデータ読出時の選択メモリセルの比較対象として設けられる複数の参照セルとが行列状に配置されたメモリアレイを備え、複数の参照セルは、行に沿って、列を複数のメモリセルと共有するように配置される。記憶装置は、行にそれぞれ対応して配置され、選択行において活性化される複数のワード線と、列にそれぞれ対応して配置される複数のデータ線と、列にそれぞれ対応して配置され、各々が固定電圧を供給する複数のソース線とをさらに備える。複数のメモリセルの各々は、複数のデータ線の対応する1本と複数のソース線の対応する1本との間に直列に接続された、記憶データに応じて電気抵抗が変化する記憶素子および対応するワード線の活性化に応答してオンするアクセス素子とを含み、複数のデータ線は、データ読出時に、複数のメモリセルのうちの、データ読出対象に選択された選択メモリセルと接続される第1のデータ線と、データ読出時に、複数の参照セルのうちの、選択メモリセルとの間で列を共有する選択参照セルと接続される第2のデータ線とを含む。記憶装置は、データ読出時に第1および第2のデータ線を固定電圧と異なる電圧と結合して、選択メモリセルおよび選択参照セルをそれぞれ通過する第1および第2の電流経路を形成させるデータ読出回路をさらに備え、データ読出回路は、第1および第2の電流経路の電気抵抗差に基いて、選択メモリセルから記憶データを読出し、複数のデータ線の単位長当たりの電気抵抗は、複数のソース線の単位長当たりの電気抵抗と同等に設計される。

【0035】

この発明のさらに他の構成に従う記憶装置は、各々が記憶データに応じて2つのレベルの電気抵抗の一方を有する複数のメモリセルと、各々が複数のメモリセルのうちのデータ読出時の選択メモリセルの比較対象として設けられる複数の参照セルとが行列状に配置されたメモリアレイを備え、複数の参照セルは、列に沿って、行を複数のメモリセルと共有するように配置される。記憶装置は、行にそれぞれ対応して配置され、選択行において活性化される複数のワード線と、列にそれぞれ対応して配置される複数のデータ線と、行にそれぞれ対応して配置され、各々が固定電圧を供給する複数のソース線とをさらに備える。複数のメモリセルの各々は、複数のデータ線の対応する1本と複数のソース線の対応する1本との間に直列に接続された、記憶データに応じて電気抵抗が変化する記憶素子および対応するワード線の活性化に応答してオンするアクセス素子とを含み、複数のデータ線は、データ読出時に、複数のメモリセルのうちの、データ読出対象に選択された選択メモリセルと接続される第1のデータ線と、データ読出時に、複数の参照セルのうちの、選択メモリセルとの間で行を共有する選択参照セルと接続される第2のデータ線とを含む。記憶装置は、メモリアレイに隣接する領域に行に沿って配置され、データ読出時に第1および第2のデータ線と電気的に接続される第1および第2のデータバスと、データ読出時に第1および第2のデータバスを固定電圧と異なる電圧と結合して、選択メモリセルおよび選択参照セルをそれぞれ通過する第1および第2の電流経路を形成させるデータ読出回路をさらに備える。データ読出回路は、第1および第2の電流経路の電気抵抗差に基いて、選択メモリセルから記憶データを読出し、複数のソース線の単位長当たりの電気抵抗は、第1および第2のデータ線の単位長当たりの電気抵抗と同等に設計される。

【0036】

好ましくは、データ読出時において、第1の電流経路から選択メモリセルを除いた部分の電気抵抗は、第2の電流経路から選択参照セルを除外した部分の電気抵抗と均衡する。

【0037】

また好ましくは、記憶素子は、複数の磁性体膜を有し、複数の磁性体膜のうちの少なくとも1つは、記憶データに応じた方向に磁化される。

【0038】

あるいは好ましくは、データ読出時に、第1および第2のデータ線は、固定電圧と異なる共通の電圧と結合され、データ読出回路は、第1および第2のデータ線の通過電流差に基づいて、選択メモリセルから記憶データを読出す。

【0039】

また好ましくは、データ読出時に、第1および第2のデータ線は、同一の電流を供給され、データ読出回路は、第1および第2のデータ線の電圧差に基づいて、選択メモリセルから記憶データを読出す。

【0040】

【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳しく説明する。なお、図中における同一符号は同一または相当部分を示すものとする。

【0041】

[実施の形態1]

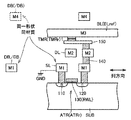

図1は、本発明の実施の形態に従うMRAMデバイス1の全体構成を示す概略ブロック図である。

【0042】

MRAMデバイス1は、本願発明に従う記憶装置の代表例として示される。なお、以下の説明で明らかになるように、本願発明の適用は、MRAMデバイスに限定されるものではなく、記憶データのレベルに応じて電気抵抗値が変化するメモリセルを備えた記憶装置に広く適用することができる。

【0043】

図1を参照して、MRAMデバイス1は、外部からの制御信号CMDおよびアドレス信号ADDに応答してランダムアクセスを行ない、書込データDINの入力および読出データDOUTの出力を実行する。

【0044】

MRAMデバイス1は、制御信号CMDに応答してMRAMデバイス1の全体動作を制御するコントロール回路5と、行列状に配置されたMTJメモリセルMCを含むメモリアレイ10とを備える。

【0045】

メモリアレイ10においては、MTJメモリセルの行(以下、単に「メモリセル行」とも称する)にそれぞれ対応して、リードワード線RWLおよびディジット線DLが配置され、MTJメモリセルの列(以下、単に「メモリセル列」と称する)にそれぞれ対応して、ビット線BLが配置される。あるいは、折返し型ビット線構成とするために、各メモリセル列に対応して、ビット線BLおよび/BLから構成されるビット線対BLPを配置する構成としてもよい。図1においては、代表的に示される1個のMTJメモリセルMCと、これに対応するリードワード線RWL、ディジット線DL、およびビット線BL(またはビット線対BLP)の配置が示される。

【0046】

MRAMデバイス1は、アドレス信号によって示されるロウアドレスRAをデコードして、メモリアレイ10における行選択を実行するための行デコーダ20と、アドレス信号ADDによって示されるコラムアドレスCAをデコードして、メモリアレイ10における列選択を実行するための列デコーダ25と、読出/書込制御回路30および35とをさらに備える。

【0047】

読出/書込制御回路30および35は、メモリアレイ10に対してデータ書込動作を行なうための回路群、およびメモリアレイ10からデータ読出を行なうための回路群を総称したものである。

【0048】

ディジット線DLは、メモリアレイ10を挟んで行デコーダ20と反対側の領域において、所定電圧Vss(たとえば、接地電圧)と結合される。

【0049】

図2は、メモリアレイおよびその周辺回路の実施の形態1に従う構成を説明する回路図である。

【0050】

図2を参照して、メモリアレイ10は、n行×m列(n,m:自然数)に配列される複数のMTJメモリセルMCを有する。なお、以下においては、MTJメモリセルを単にメモリセルとも称する。

【0051】

メモリセル行にそれぞれ対応してリードワード線RWL1〜RWLn、ディジット線DL1〜DLnおよびソース線SL1〜SLnが配置される。メモリセル列にそれぞれ対応して、相補のビット線BL1,/BL1〜BLm,/BLmが設けられる。

【0052】

ソース線SL1〜SLnの各々は、両端を接地配線GL1およびGL2と接続されて、メモリセルMCへ接地電圧GNDを供給する。なお、以下においては、リードワード線RWL1〜RWLn、ディジット線DL1〜DLn、ビット線BL1〜BLm,/BL1〜/BLmおよびソース線SL1〜SLnを総称して、リードワード線RWL、ディジット線DL、ビット線BL,/BLおよびソース線SLとも表記する。また、信号、信号線およびデータの2値的な高電圧状態(たとえば電源電圧Vcc)および低電圧状態(たとえば接地電圧GND)を、「Hレベル」および「Lレベル」ともそれぞれ称することとする。

【0053】

各メモリセルMCは、図16に示したのと同様に構成され、対応するビット線BLまたは/BLとソース線SLとの間に直列に接続されたトンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。アクセストランジスタATRのゲートは対応するリードワード線RWLと接続されている。トンネル磁気抵抗素子TMRは、記憶データ(“1”もしくは“0”)に応じた方向に磁化されて、電気抵抗RmaxおよびRminのいずれかを有する。なお、トンネル磁気抵抗素子TMRに相当する部分について、記憶データのレベルに応じて電気抵抗が変化する他の素子によって置換することも可能である。

【0054】

各メモリセルの電気抵抗は、厳密には、トンネル磁気抵抗素子TMR、アクセストランジスタATRのオン抵抗、およびその他の寄生抵抗の和であるが、トンネル磁気抵抗素子TMR以外の抵抗分は記憶データによらず一定であるので、以下においては、記憶データに応じた2種類の正規メモリセルの電気抵抗についても、RmaxおよびRminで示し、両者の差をΔR(すなわち、ΔR=Rmax−Rmin)と示すものとする。

【0055】

メモリセルMCは、1行ごとにビット線BL1〜BLmおよび/BL1〜/BLmのいずれか一方と結合される。奇数行(たとえば第1行)に属するメモリセルMCは、ビット線BL1〜BLmと結合され、偶数行(たとえば第2行)に属するメモリセルMCは、ビット線/BL1〜/BLmと接続される。

【0056】

メモリアレイ10には、さらに、2個のリファレンスセル行を形成するように行方向に沿って配置された2m個のリファレンスセルRMCが配置される。これらのリファレンスセルRMCは、ビット線BL1,/BL1,…,/BLmとそれぞれ接続される。2個のリファレンスセル行にそれぞれ対応して、ダミーリードワード線DRWL0,DRWL1と、ソース線SLd0,SLd1とが、リードワード線RWLおよびソース線SLと同様に、行方向に沿って設けられる。以下においては、ダミーリードワード線DRWL0,DRWL1およびソース線SLd0,SLd1を総称する場合には、ダミーリードワード線DRWLおよびソース線SLdと表記することとする。ソース線SLdは、ソース線SLと同様に、両端を接地配線GL1およびGL2と接続されて、リファレンスセルRMCへ接地電圧GNDを供給する。

【0057】

各リファレンスセルRMCは、対応するビット線BLまたは/BLと、対応するソース線SLdとの間に直列に接続される、基準抵抗TMRrおよびアクセス素子ATRrとを有する。アクセス素子ATRrは、MTJメモリセル中のアクセストランジスタATRと同様に、電界効果型トランジスタで形成され、そのゲートは、ダミーリードワード線DRWL0およびDRWL1の対応する一方と接続される。

【0058】

リファレンスセルRMCの電気抵抗は、各メモリセルMCの2種類の電気抵抗RmaxおよびRminの中間レベル、好ましくは(Rmax+Rmin)/2に設計される。たとえば、基準抵抗TMRrをMTJメモリセルMC内のトンネル磁気抵抗素子TMRと同様の設計とし、かつ電気抵抗Rminに対応する記憶データを予め書込んだ上で、アクセス素子ATRrを構成するトランジスタのサイズをアクセストランジスタATRと異ならせたり、アクセス素子ATRrのゲート電圧、すなわちダミーリードワード線DRWLのHレベル電圧を、リードワード線RWLとは異なるレベルに設定することにより、このような特性のリファレンスセルが実現される。

【0059】

なお、リファレンスセルRMCの記憶データは書換える必要がないため、図2に示された、リファレンスセル行にそれぞれ対応して設けられたディジット線DLd0およびDLd1の配置は必要ではないが、これらのディジット線を設けることにより、メモリアレイ10端部での形状パターンの連続性を確保して、メモリアレイ10内における製造寸法・形状の仕上りのばらつきを減少させることができる。

【0060】

リファレンスセルRMCは、ダミーリードワード線DRWL0およびDRWL1のいずれか一方によって選択される。ダミーリードワード線DRWL0によって選択されるリファレンスセル群において、アクセス素子ATRrは、ダミーリードワード線DRWL0の活性化に応答してオンする。ダミーリードワード線DRWL0は、偶数行が選択メモリセルを含む場合に、選択行のリードワード線RWLとともに活性化される。したがって、偶数行の選択時には、ビット線/BL1〜/BLmとソース線SLとの間にトンネル磁気抵抗素子TMRが電気的にそれぞれ結合される一方で、ビット線BL1〜BLmとソース線SLd0との間に基準抵抗TMRrが電気的にそれぞれ結合される。

【0061】

一方、ダミーリードワード線DRWL1によって選択される残りのリファレンスセル群において、アクセス素子ATRrは、ダミーリードワード線DRWL1の活性化に応答してオンする。ダミーリードワード線DRWL1は、奇数行が選択メモリセルを含む場合に、選択行のリードワード線RWLとともに活性化される。したがって、奇数行の選択時には、ビット線BL1〜BLmとソース線SLとの間にトンネル磁気抵抗素子TMRが電気的にそれぞれ結合される一方で、ビット線/BL1〜/BLmとソース線SLd1との間に基準抵抗TMRrが電気的にそれぞれ結合される。

【0062】

図3は、メモリセルMCおよびリファレンスセルRMC周辺の構造を示す断面図である。

【0063】

図3を参照して、半導体基板SUB上に形成されたアクセストランジスタATR(またはアクセス素子ATRr)は、不純物領域110および120と、ゲート130とを有する。不純物領域110は、接地電圧GNDと電気的に結合される。したがって、以下においては不純物領域110をソース領域と称し、不純物領域120をドレイン領域とも称することとする。

【0064】

同一のメモリセル行に属するアクセストランジスタATRのソース領域110は、互いに電気的に結合される。すなわち、ソース領域110に相当する不純物領域は、メモリアレイ10上に行方向に沿って延在するように配置され、図2に示したソース線SL(またはソース線SLd)を形成する。既に説明したようにソース線SL,SLdは、メモリアレイ10に隣接する領域において、接地配線GL1およびGL2によって接地電圧GNDと結合されている。

【0065】

ドレイン領域120は、金属配線層M1およびコンタクトホールに形成された金属膜140によって、導電性のストラップ150を介してトンネル磁気抵抗素子TMRと結合される。トンネル磁気抵抗素子TMRの下層側には、近接する金属配線層M1にディジット線DLが設けられ、トンネル磁気抵抗素子TMRの上層側には、金属配線層M2にビット線BLが形成される。ビット線BLはトンネル磁気抵抗素子TMRと電気的に結合されている。

【0066】

リードワード線RWLは、行方向に延在して設けられるポリシリコン配線として設けられるのが一般的である。当該ポリシリコン配線によって、同一のメモリセル行に属するアクセストランジスタATRのゲート130同士は、電気的に結合される。

【0067】

このように、データ書込電流を流すディジット線DLおよびビット線BLは比較的電気抵抗の小さい金属配線を形成する一方で、データ書込電流を流す必要のないソース線SLおよびリードワード線RWLを、金属配線を用いずに形成することによって、メモリセルMCおよびリファレンスセルRMCの構成に必要な金属配線層数を削減して、セルの小型化を図ることができる。この結果、メモリアレイの小面積化による装置の小型化が可能となる。

【0068】

次に、メモリアレイ10周辺の構成について説明する。

再び図2を参照して、メモリアレイ10の周辺において、各メモリセル行に対応して、電源電圧Vccとディジット線DLの一端との間に設けられたディジット線ドライバ41が設けられる。ディジット線ドライバ41は、たとえばNチャネルMOSトランジスタで構成される。ディジット線ドライバ41のゲートには、対応するメモリセル行が選択されたときにHレベルに活性化されるデコード信号を受ける。

【0069】

この結果、選択行のディジット線DLは、ディジット線ドライバ41のターンオンに応答して、その一端および他端を電源電圧Vccおよび接地電圧GNDとそれぞれ接続される。この結果、選択行のディジット線DLに、電源電圧Vccから接地電圧GNDに向かう所定方向のデータ書込電流を流すことができる。当該所定方向のデータ書込電流によって、対応するメモリセルにおいては、磁化困難軸(HA)方向に沿ったデータ書込磁界が作用する。

【0070】

メモリアレイ10に隣接する領域に、データバス対DBP1を構成するデータバスDB1,/DB1と、データバス対DBP2を構成するデータバスDB2,/DB2とが行方向に沿って配置される。データバス対DBP1およびDBP2は、メモリアレイ10を挟んで互いに反対側の領域に配置される。

【0071】

さらに、メモリセル列のそれぞれに対応して、コラム選択線CSL1〜CSLm、コラム選択ゲートCSG1,/CSG1〜CSGm,/CSGmが設けられ、ビット線BLおよび/BLの各々に対応してプリチャージトランジスタ67が設けられる。

【0072】

列デコーダ25は、コラムアドレスCAのデコード結果、列選択結果に応じてコラム選択線CSL1〜CSLmのうちの、列選択結果に対応する1本を選択状態(Hレベル)に活性化する。

【0073】

コラム選択ゲートCSG1,/CSG1〜CSGm,/CSGmは、図1に示した読出/書込制御回路30に相当する領域に設けられる。コラム選択ゲートCSG1〜CSGmは、ビット線BL1〜BLmとデータバスDB1との間にそれぞれ配置される。コラム選択ゲートCSG1〜CSGmの各々は、コラム選択線CSL1〜CSLmのうちの対応する1本の活性化に応答して、データバスDB1と対応するビット線BLとを接続する。

【0074】

同様に、コラム選択ゲート/CSG1〜/CSGmは、ビット線/BL1〜/BLmとデータバス/DB1との間にそれぞれ配置される。コラム選択ゲート/CSG1〜/CSGmの各々は、コラム選択線CSL1〜CSLmのうちの対応する1本の活性化に応答して、データバス/DB1と対応するビット線/BLとを接続する。

【0075】

プリチャージトランジスタ67は、読出/書込制御回路35に相当する領域に設けられ、プリチャージ電圧Vpcと各ビット線BL,/BLとの間に電気的に結合される。プリチャージトランジスタ67は、プリチャージ信号φPRに応答してオンする。たとえば、プリチャージ電圧Vpcとして接地電圧GNDを用いることができる。

【0076】

プリチャージ信号φPRは、MRAMデバイス1のスタンバイ期間と、MRAMデバイス1のアクティブ期間内におけるデータ書込動作およびデータ読出動作の前後等において、各ビット線BL,/BLをプリチャージするために活性化される。一方、MRAMデバイスのアクティブ期間におけるデータ書込およびデータ読出動作時においては、プリチャージ信号φPRはLレベルに非活性化される。これに応答して、各ビット線BL,/BLは、プリチャージ電圧Vpc(接地電圧GND)と切離される。

【0077】

ビット線BL1〜BLmの両端にそれぞれ対応して、ビット線ドライバBDVa1〜BDVamおよびBDVb1〜BDVbmがそれぞれ設けられる。ビット線ドライバBDVa1〜BDVamは、図1に示した読出/書込制御回路30に属し、各々の構成は同様である。ビット線ドライバBDVb1〜BDVbmは、図1に示した読出/書込制御回路35に属し、各々の構成は同様である。ここでは代表的にビット線ドライバBDVa1,BDVb1の構成について説明する。

【0078】

ビット線ドライバBDVa1は、電源電圧Vccとビット線BL1の一端側(列デコーダ25側)との間に接続されたトランジスタ51と、ビット線BL1の一端側と接地電圧GNDとの間に接続されたトランジスタ52と、トランジスタ51および52のゲート電圧をそれぞれ制御するための論理ゲート53および55とを有する。トランジスタ51および52は、たとえばNチャネルMOSトランジスタによって構成される。

【0079】

論理ゲート53は、データバスDB1、データ書込時にHレベルに設定される制御信号WEおよびコラム選択線CSL1の3つの電圧レベル間のAND論理演算結果をトランジスタ51のゲートに出力する。論理ゲート55は、データバスDB1の反転レベル、制御信号WEおよびコラム選択線CSL1の3つの電圧レベル間のAND論理演算結果をトランジスタ52のゲートに出力する。

【0080】

これに対して、ビット線ドライバBDVb1は、電源電圧Vccとビット線BL1の他端側(列デコーダ25の反対側)との間に接続されたトランジスタ61と、ビット線BL1の他端側と接地電圧GNDとの間に接続されたトランジスタ62と、トランジスタ61および62のゲート電圧をそれぞれ制御するための論理ゲート63および65とを有する。トランジスタ61および62は、たとえばNチャネルMOSトランジスタによって構成される。

【0081】

論理ゲート63は、データバスDB2の反転レベル、制御信号WEおよびコラム選択線CSL1の3つの電圧レベル間のAND論理演算結果をトランジスタ61のゲートに出力する。論理ゲート65は、データバスDB2、制御信号WEおよびコラム選択線CSL1の3つの電圧レベル間のAND論理演算結果をトランジスタ62のゲートに出力する。

【0082】

さらに、ビット線/BL1〜/BLmの両端にそれぞれ対応して、ビット線ドライバ/BDVa1〜/BDVamおよび/BDVb1〜/BDVbmがそれぞれ設けられる。ビット線ドライバ/BDVa1〜/BDVamは、図1に示した読出/書込制御回路30に属し、各々の構成は同様である。ビット線ドライバ/BDVb1〜/BDVbmは、図1に示した読出/書込制御回路35に属し、各々の構成は同様である。以下においては、ビット線ドライバBDVa1〜BDVamおよびBDVb1〜BDVbmを総称してビット線ドライバBDVaおよびBDVbbとも称し、ビット線ドライバ/BDVa1〜/BDVamおよび/BDVb1〜/BDVbmを総称して、ビット線ドライバ/BDVaおよび/BDVbとも称する。

【0083】

ビット線ドライバ/BDVaは、ビット線ドライバBDVaと比較して、論理ゲートへの入力の1つがデータバスDB1ではなくデータバス/DB1となる点のみが異なる。同様に、ビット線ドライバ/BDVbは、ビット線ドライバBDVbと比較して、論理ゲートへの入力の1つがデータバスDB2ではなくデータバス/DB2となる点のみが異なる。

【0084】

データ書込時において、データバスDB1および/DB1は、図示しないデータ書込回路によって、書込データDINに応じて、異なる電圧(たとえば電源電圧Vccおよび接地電圧GND)の一方ずつに駆動される。データバスDB2および/DB2の電圧も同様に相補なレベルへ駆動される。なお、データバスDB1とDB2とは同じ電圧に駆動され、/DB1および/DB2も同じ電圧に駆動される。

【0085】

たとえば、書込データが“1”のときには、データバスDB1およびDB2が電源電圧Vcc(Hレベル)へ駆動され、データバス/DB1および/DB2が接地電圧GND(Lレベル)へ駆動される。これに対して、書込データが“0”のときには、データバス/DB1および/DB2が電源電圧Vcc(Hレベル)へ駆動され、データバスDB1およびDB2が接地電圧GND(Lレベル)へ駆動される。

【0086】

このような構成とすることにより、データ書込時においては、選択列のビット線BLおよび/BLに、互いに反対方向の電流が流される。これらの電流の方向は、データバスDB1,DB2および/DB1,/DB2の電圧レベル、すなわち書込データDINのレベルに応じて制御される。

【0087】

具体的には、Hレベルデータの書込時(DIN=“1”)には、選択列のビット線BLには、ビット線ドライバBDVaからBDVbに向かう方向にデータ書込電流が流され、ビット線/BLにはビット線ドライバ/BDVbから/BDVaに向かう方向にデータ書込電流が流される。これに対して、Lレベルデータの書込時(DIN=“0”)には、選択列のビット線BLおよび/BLには、Hレベルデータの書込時とそれぞれ反対方向にデータ書込電流が流される。このような書込データDINに応じた方向のデータ書込電流によって、対応するメモリセルにおいては、磁化容易軸(EA)方向に沿ったデータ書込磁界が作用する。

【0088】

この結果、選択メモリセルに対しては、選択行のディジット線DLからの磁化困難軸に沿った磁界と、選択列のビット線BL,/BLからの書込データDINに応じた方向の磁化容易軸に沿った磁界との両方が作用するので、当該選択メモリセルにおいて、トンネル磁気抵抗素子TMRは書込データDINのレベルに応じた方向に磁化される。

【0089】

データ読出時においては、選択行のリードワード線RWLおよび選択列のコラム選択線CSLが活性化される。図2においては、一例として、リードワード線RWL2およびコラム選択線CSL1が活性化されるものとする。偶数行のリードワード線RWL2が活性化されるので、これに対応してダミーリードワード線DRWL0が活性化され、DRWL1は非活性化される。この結果、選択メモリセルMC♯は、ビット線/BL1およびソース線SL2の間に接続され、選択されたリファレンスセル(以下、「選択リファレンスセル」とも称する)は、ビット線BL1およびソース線SLd0の間に接続される。

【0090】

コラム選択線CSL1の活性化に応答して、選択列に対応するビット線BL1および/BL1は、データバスDB1および/DB1を介して、選択メモリセルから記憶データを読出すためのセンスアンプ(データ読出回路)70と接続される。

【0091】

以上説明した、リファレンスセルを備えたMRAMデバイス1におけるデータ書込およびデータ読出動作を図4および5を用いて説明する。

【0092】

図4を参照して、データ書込時については、選択メモリセルMC♯に対するデータ書込の動作波形が示される。

【0093】

データ書込時においては、各リードワード線RWLおよびダミーリードワード線DRWLはLレベル(接地電圧GND)に非活性化され、選択行のディジット線DLおよび選択列のコラム選択線CSLが活性化される(図示せず)。

【0094】

これにより、選択行のディジット線DLおよび選択列のビット線BL,/BLには、一定方向のデータ書込電流Ipおよび書込データに応じた方向のデータ書込電流±Iwがそれぞれ供給される。この結果、選択行のディジット線および選択列のビット線の交点に位置する選択メモリセルMC♯に対して、データ書込が実行される。なお、既に説明したように、リファレンスセルRMCに対するデータ書込は、実動作時には不要である。

【0095】

データ読出時においては、選択行に対応するリードワード線RWL、および対応するダミーリードワード線DRWLが、Hレベルに活性化される。一方、各ディジット線DLは、非活性化されて電流は流されない。また、図示しないが、選択列のコラム選択線CSLが活性化される。

【0096】

リードワード線RWLおよびダミーリードワード線DRWLのHレベル電圧は、リファレンスセルの構成に応じて設定される。たとえば、基準抵抗TMRrを電気抵抗RmaxおよびRminの中間的な抵抗で形成する場合には、リードワード線RWLおよびダミーリードワード線DRWLのHレベル電圧は、同一レベル(VDWL=Vcc)とすればよい。これに対して、基準抵抗TMRrをトンネル磁気抵抗素子TMRと同様に設計し、電気抵抗Rminに対応する方向に磁化する場合には、アクセス素子ATRrのオン抵抗をアクセストランジスタATRのオン抵抗よりも大きくする必要があるので、ダミーリードワード線DRWLのHレベル電圧VDWLは、リードワード線RWLのHレベル電圧(Vcc)よりも低く設定される。

【0097】

すでに説明したように、たとえば、偶数行が選択されたデータ読出時には、データバスDB1および/DB1は、選択メモリセルMC♯および選択リファレンスセルRMC♯をそれぞれ介して接地電圧GNDへプルダウンされる。センスアンプ70は、データバスDB1および/DB1を介して、選択列のビット線BLおよび/BLの各々を接地電圧GNDと異なる所定電圧Vrefと接続する。所定電圧Vrefは、トンネル磁気抵抗素子TMRの特性、たとえば、トンネル膜の信頼性や接合抵抗差ΔR(=Rmax−Rmin)の現われやすさを考慮して、一般的には0.5V程度に設定される。

【0098】

このとき、選択列のビット線BL,/BLのうちの選択メモリセルMC♯と接続された一方には、その記憶データに対応する2種類のレベルの一方がメモリセル電流Icellとして流れる。一方、選択列のビット線BL,/BLのうちの選択リファレンスセルRMC♯と接続された他方には、上記2種類のレベルの中間レベルを有する基準電流Irefが流れる。したがって、センスアンプ70は、メモリセル電流Icellおよび基準電流Irefの差を検知することによって、読出データDOUTを生成することができる。センスアンプ70としては、電流差を増幅・検知するための一般的な構成が適用可能であるので、その詳細な回路構成については説明を省略する。

【0099】

図5には、データ読出動作のバリエーションが示される。図5に示されたデータ読出動作においては、センスアンプ70は、データバスDB1および/DB1を介して、選択列のビット線BLおよび/BLの各々へ同一レベルの電流Isを供給する。これに応じて、選択列のビット線BL,/BLのうちの選択メモリセルMC♯と接続された一方には、その記憶データに対応する2種類の電気抵抗(Rmax,Rmin)に応じた電圧V1またはV0が発生する。一方、選択列のビット線BL,/BLのうちの選択リファレンスセルRMC♯と接続された他方には、電圧V1およびV0の中間レベルの電圧Vrが生じる。

【0100】

したがって、センスアンプ70は、ビット線BLおよび/BLの電圧差を検知することによって、読出データDOUTを生成することができる。センスアンプ70としては、電圧差を増幅・検知するための一般的な構成が適用可能であるので、その詳細な回路構成については説明を省略する。また、図5に示されたデータ書込動作については、図4と同様であるので説明は繰り返さない。

【0101】

図4および図5のいずれのデータ読出動作においても、センスアンプ70は、メモリセル電流経路および基準電流経路の電気抵抗差に基づいてデータ読出を実行する。したがって、データ読出マージンを確保するためには、メモリセル電流経路および基準電流経路の電気抵抗差が、選択メモリセルおよび選択リファレンスセル間の電気抵抗差を明確に反映していることが必要である。たとえば、アドレス選択に依存して、選択メモリセルおよび選択リファレンスを除いた部分の経路抵抗が変化すると、データ読出マージンの低下を招いてしまう。なお、図4および図5に示された、データ読出時におけるビット線の通過電流Is,Icell,Irefは、データ書込時におけるビット線の通過電流±Iwと比較してかなり小さいレベルである。

【0102】

次に、データ読出時におけるメモリセル電流経路および基準電流経路の経路抵抗を均衡させるための構成について説明する。

【0103】

再び図2を参照して、データ読出時にメモリセル電流は、センスアンプ70〜データバス/DB1〜ビット線/BL1〜選択メモリセルMC♯〜ソース線SL2〜接地配線GL1,GL2〜接地電圧GNDから構成されるメモリセル電流経路を流れる。これに対して、基準電流は、センスアンプ70〜データバスDB1〜ビット線BL1〜選択リファレンスセルRMC♯〜ソース線SLd0〜接地配線GL1,GL2〜接地電圧GNDから構成される基準電流経路を流れる。

【0104】

図3で説明したように、これらのソース線SL2およびSLd0は、比較的電気抵抗の高い拡散層によって形成される。したがって、これらの電流経路から選択メモリセルMC♯および選択リファレンスセルRMC♯をそれぞれ除いた経路抵抗は、ソース線SL(SL2)およびSLd上の電流経路長に応じて変化する。特に、メモリセル電流経路と基準電流経路との間で、ソース線SL(SL2)およびSLd上の電流経路長が大きく異なると、これらの電流経路間での経路抵抗に大きな差異を生じ、データ読出マージンを低下させてしまう。

【0105】

リファレンスセル行を設けた構成においては、選択メモリセルMC♯および選択リファレンスセルRMC♯は同一メモリセル列に属するので、メモリセル電流経路および基準電流経路の間で、行方向に沿った配線上での経路長は、列選択結果にかかわらず自然に均衡する。

【0106】

したがって、実施の形態1に従う構成においては、ソース線SL,SLdとリファレンスセルとの配置方向を一致させることによって、メモリセル電流経路および基準電流経路の経路抵抗を、列選択結果にかかわらず均衡させている。すなわち、ソース線SL,SLdを行方向に沿って配置することにより、メモリセル電流経路および基準電流経路の間において、電気抵抗の大きいソース線SLおよびSLd上の経路長を、列選択結果にかかわらず均衡させることができる。

【0107】

この結果、メモリセル電流経路および基準電流経路でのそれぞれの総電気抵抗の差が、選択メモリセルMC♯と選択リファレンスセルRMC♯との電気抵抗差を明確に反映するため、アドレス選択結果に依存したデータ読出マージンの低下を防ぐことができる。

【0108】

なお、リファレンスセル行を設けた構成においては、メモリセル電流経路および基準電流経路の間で、列方向に沿った配線上での経路長は、行選択結果に依存して変化してしまう。しかしながら、列方向に沿って設けられるビット線BL,/BLおよび接地配線GL1,GL2は、それぞれ低抵抗の金属配線で形成されるため、このような経路長差が、データ読出マージンに影響を与えるほどの経路抵抗差を生じる可能性は低い。

【0109】

あるいは、さらに望ましい構成として、列方向に沿って設けられるビット線BLおよび接地配線GL1,GL2の各々を単位長当たりの電気抵抗が同等になるように設計すれば、メモリセル電流経路および基準電流経路の間での、行選択結果に依存した経路抵抗差を抑制して、データ読出マージンをさらに向上させることができる。単位長当たりの電気抵抗を同等にするためには、たとえば、ビット線BLおよび接地配線GL1,GL2の各々を同一形状・同一材質で形成すればよい。

【0110】

さらに、図2に示されるように、接地配線GL1およびGL2の一端ずつを、対称形となるように接地電圧GNDと結合することによって、メモリセル電流経路および基準電流経路を対称形とすることができるので、さらにデータ読出動作を安定化できる。

【0111】

図6には、接地配線GL1およびGL2についての配置のアレンジが示される。

【0112】

図6(a)を参照して、接地配線GL1およびGL2の両端のそれぞれを接地電圧GNDと接続する構成とすることもできる。このような構成としても、メモリセル電流経路および基準電流経路の間で、アドレス選択結果にかかわらず経路抵抗を均衡することができる。

【0113】

図6(b)には、図2で示したと同様の構成、すなわち、接地配線GL1およびGL2の一端ずつが対称的に接地電圧GNDと接続される構成が示される。

【0114】

あるいは、図6(c)に示されるように、接地配線GL1およびGL2の両端の同一側を接地電圧GNDと接続する構成としても、接地配線GL1,GL2上の電流経路長は、メモリセル電流経路および基準電流経路の間で異なるものの、電気抵抗の大きいソース線SL,SLd上での電流経路長がバランスしているため、データ読出マージンが大きく低下することはない。

【0115】

したがって、リファレンスセルRMCの配置方向とソース線SL,SLdの配置方向とを一致させていれば、図6(d)に示されるように、メモリアレイ10の一方側に接地配線GL1のみを配置してその一端側を接地電圧GNDと接続する簡易な構成としても、メモリセル電流経路および基準電流経路のそれぞれの経路抵抗を、アドレス選択結果にかかわらず均衡させて、データ読出マージンを確保することができる。なお、実施の形態1に従う構成は、図3に示される、ソース線SLを拡散層として設けるメモリセル構造のみならず、ソース線SLを金属配線として設けるメモリセル構造に対しても同様に適用することが可能である。

【0116】

[実施の形態2]

図7は、メモリアレイおよびその周辺回路の実施の形態2に従う構成を説明する回路図である。

【0117】

図7を参照して、実施の形態2に従う構成においては、実施の形態1に従う構成と比較して、複数のリファレンスセルRMCが、リファレンスセル列を形成するように、列方向に沿って配置される点が異なる。複数のリファレンスセルRMCは、複数のメモリセルMCと、メモリセル行をそれぞれ共有するように配置される。

【0118】

これに伴って、ビット線BL1〜BLmは、メモリセルMCのみと接続されることになる。これに対して、リファレンスセル列に対応してリファレンスビット線BLrefが配置され、各リファレンスセルRMCは、リファレンスビット線BLrefとソース線SL1〜SLnの対応する1本の間に接続される。

【0119】

既に説明したように、リファレンスセルRMCの記憶データは書換える必要がないため、リファレンスセルRMCに対するデータ書込は必要ない。したがって、リファレンスビット線BLrefの両端に、ビット線ドライバの配置は本来必要ないが、図8に従う構成においては、形状ダミーとしてビット線ドライバBDVarおよびBDVbrが配置されている。すなわち、ビット線ドライバBDVarおよびBDVbrは実際にデータ書込動作に用いられることはないが、このような形状ダミーの配置によって、ビット線ドライバの配置領域における形状の連続性を確保して、メモリアレイ10周辺部における製造寸法・形状の仕上りのばらつきを減少させることができる。

【0120】

ソース線SLは、図2に示した構成と同様に行方向に沿って配置され、その両端の少なくとも一方は、接地配線によって接地電圧GNDと結合される。図7に示される例では、各ソース線の一端側(センスアンプ70の反対側)が列方向に沿って配置された接地配線GL1と接続される。

【0121】

また、ビット線BL1〜BLmは、コラム選択ゲートCSG1〜CSGmをそれぞれ介してデータバスDB1と接続され、リファレンスビット線BLrefはコラム選択ゲートCSGrを介してデータバス/DB1と接続される。コラム選択ゲートCSGrは、コラム選択線CSLrの活性化に応答してオンする。

【0122】

図7に従う構成においては、コラム選択線CSL1〜CSLmは、データ読出時およびデータ書込時の各々において、列選択結果に応じて選択的に活性化される。一方、コラム選択線CSLrは、列選択結果にかかわらず、データ読出時に活性化され、データ書込時には非活性化される。

【0123】

図7のその他の部分の構成は、図2に示したのと同様であるので詳細な説明は繰返さない。データ書込動作は、選択行のディジット線ドライバ41および選択列のビット線ドライバBDVa,BDVb,/BDVa,/BDVbを用いて、図2の構成と同様に実行される。

【0124】

次に、実施の形態2に従う構成におけるデータ読出動作について説明する。

図7においても、図2と同様に、リードワード線RWL2およびコラム選択線CSL1がHレベルに活性化されて、第2行・第1列のメモリセルが選択メモリセルMC♯として選択され、選択メモリセルMC♯と同一のメモリセル行を共有するリファレンスセルが選択リファレンスセルRMC♯として選択されるものとする。

【0125】

データ読出時にメモリセル電流は、センスアンプ70〜データバスDB1〜ビット線BL1〜選択メモリセルMC♯〜ソース線SL2〜接地配線GL1〜接地電圧GNDの経路から構成されるメモリセル電流経路(図7中の実線矢印)を流れる。これに対して、基準電流は、センスアンプ70〜データバス/DB1〜リファレンスビット線BLref〜選択リファレンスセルRMC♯〜ソース線SL2〜接地配線GL1〜接地電圧GNDの経路から構成される基準電流経路(図7中の点線矢印)を流れる。

【0126】

リファレンスセル列を設けた構成においては、選択メモリセルMC♯および選択リファレンスセルRMC♯は同一メモリセル行に属するので、メモリセル電流経路および基準電流経路の間で、列方向に沿った配線上での経路長、すなわちビット線BLおよびリファレンスビット線BLref上での経路長、および接地配線GL1上での経路長は、列選択結果にかかわらず自然に均衡する。これに対して、行方向に沿った配線上での経路長は、メモリセル電流経路および基準電流経路の間で異なってくる。

【0127】

したがって、実施の形態2のように、リファレンスセルの配置方向と、ソース線SLの配置方向とが一致しない構成においては、メモリセル電流経路および基準電流経路の間で、ソース線SL上の電流経路が必然的に異なってくるため、ソース線SLおよび、ソース線に平行に配置されかつメモリセル電流および基準電流経路に含まれるデータバスDB1,/DB1の各々を、単位長当りの電気抵抗が同様となるように設計する必要がある。

【0128】

図8は、実施の形態2に従うメモリセルおよびリファレンスセル周辺の構造を示す断面図である。

【0129】

図8を参照して、実施の形態2に従う構成においては、図3に示した実施の形態1に従う構成と比較して、ソース線SLが金属配線として配置される点が異なる。すなわち、実施の形態2に従う構成では、図3に示した構成と比較して金属配線層が1つ多く必要であり、たとえば、金属配線層M1、M2およびM3に、ソース線SL、ディジット線DLおよびビット線BLがそれぞれ設けられる。

【0130】

行方向に沿って設けられた金属配線であるソース線SLは、対応するメモリセル行に属する複数のアクセストランジスタATRのそれぞれのソース領域110と電気的に結合される。

【0131】

さらに、メモリアレイ10に隣接する領域において、たとえばソース線SLと同一の金属配線層M1を用いて、データバスDB1,/DB1を、ソース線SLと同一形状・同一材質で形成すれば、単位長当りの単位抵抗をソース線SLと同等にすることができる。あるいは、データバスDB1,/DB1を、ビット線BLよりも上層の金属配線層M4を用いて、ソース線SLと同一形状・同一材質で形成することもできる。なお、既に説明したように、図8に示された配線構造を有するメモリセルおよびリファレンスセルを、実施の形態1と組み合わせて構成することも可能である。

【0132】

このような構成とすることにより、ソース線SLとリファレンスセルRMCとの配置方向が一致しない構成においても、メモリセル電流経路および基準電流経路の経路抵抗を、アドレス選択結果にかかわらず均衡させることができる。この結果、メモリセル電流経路および基準電流経路でのそれぞれの総電気抵抗の差は、選択メモリセルMC♯と選択リファレンスセルRMC♯との電気抵抗差を明確に反映する。したがって、アドレス選択結果に依存したデータ読出マージンの低下を防止して、データ読出動作を安定化できる。

【0133】

図9には、メモリアレイ10の隣接領域に配置される接地配線の配置のバリエーションが示される。図9(a)には、図8と同様の構成が示され、接地配線GL1の一端側は、接地電圧GNDと接続される。

【0134】

あるいは、図9(b)に示されるように、接地配線GL1の両端を接地電圧GNDと接続する構成としてもよい。図9(b)の構成によれば、行選択結果に応じて変化する接地配線GL1上の電流経路長を平均的に短縮することができるので、データ読出電流の電流経路の総抵抗値を実質的に抑制して、低消費電力化を図ることができる。

【0135】

[実施の形態3]

実施の形態3においては、列方向に沿って配置されたリファレンスセルRMCに対して、ソース線SLも列方向に沿って配置された構成について説明する。

【0136】

図10は、メモリアレイおよびその周辺回路の実施の形態3に従う構成を説明する回路図である。

【0137】

図10を参照して、実施の形態3に従う構成においては、図7に示した実施の形態2に従う構成と比較して、行方向に沿って配置されたソース線SL1〜SLnに代えて、列方向に沿って配置されたソース線SL1〜SLm,SLrが配置される点で異なる。ソース線SL1〜SLmについても、総称する場合には、単にソース線SLと称することとする。ソース線SLrは、リファレンスセル列に対応して設けられ、複数のリファレンスセルRMCの各々は、リファレンスビット線BLrefおよびソース線SLrの間に接続される。

【0138】

ソース線SLおよびSLrは、列方向に沿って配置され、その両端の少なくとも一方は、接地配線によって接地電圧GNDと結合される。図10に示される例では、各ソース線SLおよびSLrの一端側(センスアンプ70の反対側)が行方向に沿って配置された接地配線GL1と接続される。接地配線GL1の両端は、接地電圧GNDと結合される。

【0139】

図10のその他の部分の構成は、図7に示したのと同様であるので詳細な説明は繰返さない。データ書込動作は、選択行のディジット線ドライバ41および選択列のビット線ドライバBDVa,BDVb,/BDVa,/BDVbを用いて、図2の構成と同様に実行される。

【0140】

次に、実施の形態2に従う構成におけるデータ読出動作について説明する。

図10においても、図2と同様に、リードワード線RWL2およびコラム選択線CSL1がHレベルに活性化されて、第2行・第1列のメモリセルが選択メモリセルMC♯として選択され、選択メモリセルMC♯と同一のメモリセル行を共有するリファレンスセルが選択リファレンスセルRMC#として選択されるものとする。

【0141】

データ読出時にメモリセル電流は、センスアンプ70〜データバスDB1〜ビット線BL1〜選択メモリセルMC♯〜ソース線SL1〜接地配線GL1〜接地電圧GNDの経路から構成されるメモリセル電流経路(図10中の実線矢印)を流れる。これに対して、基準電流は、センスアンプ70〜データバス/DB1〜リファレンスビット線BLref〜選択リファレンスセルRMC♯〜ソース線SLr〜接地配線GL1〜接地電圧GNDの経路から構成される基準電流経路(図10中の点線矢印)を流れる。

【0142】

すでに説明したように、リファレンスセル列を設けた構成においては、メモリセル電流経路および基準電流経路の間で、列方向に沿った配線上での経路長は、行選択結果にかかわらず自然に均衡する。したがって、実施の形態3に従う構成においては、ソース線SL,SLrを列方向に沿って配置することにより、メモリセル電流経路および基準電流経路のそれぞれにおけるソース線SLおよびSLr上の経路長を、列選択結果にかかわらず均衡させることができる。

【0143】

この結果、図2に示した構成と同様に、ソース線SLを新たな金属配線層を設けることなく列方向に延在して形成された拡散層として形成してもソース線SLを実現できる。

【0144】

図11は、実施の形態3に従うメモリセルおよびリファレンスセル周辺の構造例を示す断面図である。図11には、拡散層として設けられたソース線SLを有するMTJメモリセルの構造例が示される。

【0145】

図11を参照して、実施の形態3に従う構成においては、ソース線SL(またはSLr)は、列方向に隣接するメモリセルMC(またはリファレンスセルRMC)のアクセストランジスタATR(またはアクセス素子ATRr)間で互いに電気的に結合されたソース領域110を有する。

【0146】

すなわち、ソース領域110は、列方向に延在して設けられた拡散層として形成される。このようなソース領域110は、接地電圧GNDと電気的に結合することによりソース線SLまたはSLrとして用いることができる。

【0147】

ドレイン領域120は、図3に示した構造と同様に、コンタクトホールに設けられた金属膜140によって、導電性のストラップ150を介してトンネル磁気抵抗素子TMRと電気的に結合される。リードワード線RWLおよびディジット線DLは行方向に沿った金属配線として、金属配線層M1およびM2にそれぞれ配置される。アクセストランジスタATRのゲート130は、対応するリードワード線RWLとコンタクトホールに形成された金属膜141を介して電気的に結合される。

【0148】

あるいは、図12に示すように、ソース線SLを金属配線として設けることも可能である。

【0149】

図12を参照して、このような構造例では、各アクセストランジスタATR(またはアクセス素子ATRr)のソース領域110は、列方向に沿った金属配線であるソース線SLと電気的に結合される。これに対して、リードワード線RWLは、図3に示した構造と同様に、ゲート130を行方向に延在して配置されたポリシリコン配線によって形成することができる。図12に示した構造例のその他の部分の構造は図11と同様であるので詳細な説明は繰返さない。

【0150】

図12の構造例によれば、必要な金属配線層の数が増えるものの、ソース線SLの低抵抗化を図ることができるので、メモリセル電流経路および基準電流経路の総電気抵抗を抑制することが可能となる。

【0151】

このように、メモリセルMCおよびリファレンスセルRMCとして、図12および図13に示された構造のいずれを適用しても、メモリセル電流経路および基準電流経路のそれぞれの経路抵抗を、アドレス選択結果にかかわらず均衡させて、データ読出マージンを確保することができる。

【0152】

なお、リファレンスセル列を設けた構成においては、メモリセル電流経路および基準電流経路の間で、行方向に沿った配線上での経路長は、列選択結果に依存して変化してしまう。しかしながら、行方向に沿って設けられるデータバスDB1,/DB1および接地配線GL1は、それぞれ低抵抗材質の金属配線で形成されるため、このような経路長差が、データ読出マージンに影響を与えるほどの経路抵抗差を生じる可能性は低い。

【0153】

あるいは、さらに望ましい構成として、行方向に沿って設けられるデータバスDB1,/DB1および接地配線GL1を単位長当たりの電気抵抗が同等になるように設計すれば、メモリセル電流経路および基準電流経路の間での、列選択結果に依存した経路抵抗差を抑制して、データ読出マージンをさらに向上させることができる。単位長当たりの電気抵抗を同等にするためには、たとえば、データバスDB1,/DB1および接地配線GL1の各々を同一形状・同一材質で形成すればよい。

【0154】

図13には、接地配線GL1およびGL2についての配置のアレンジが示される。図13(a)には、図10と同様に、行方向に沿って設けられた接地配線GL1が、センスアンプ70と反対側のノードにおいて接地電圧GNDと接続される構成が示されている。この場合には、既に説明したように、メモリセル電流経路および基準電流経路のそれぞれにおいて、経路抵抗の不均衡を引起す最大の要因であるソース線SL,SLr上の電流経路長をアドレス選択結果にかかわらず均一化するのみならず、行方向に沿って配置される配線(接地配線GLおよびデータバスDB1,/DB1)上での電流経路長の合計についても、アドレス選択結果にかかわらず均一化できる。

【0155】

したがって、上述したように、接地配線GLとデータバスDB1,/DB1を,それぞれの単位長当りの電気抵抗が同等となるように設計すれば、データ読出精度をさらに向上させることができる。

【0156】

あるいは、図9(b)に示すように、メモリアレイ10の隣接領域に、列方向に沿った接地配線GL2をさらに設けることも可能である。これにより、選択メモリセルMC♯の位置に応じて変動するメモリセル電流経路の長さを実効的に短縮することができるので、当該電流経路の電気抵抗を抑制して低消費電力化を図ることが可能である。

【0157】

[実施の形態4]

実施の形態4においては、実施の形態1と同様に、リファレンスセルが行方向に沿って配置された構成において、ソース線SLが列方向に沿って配置された場合の構成について説明する。

【0158】

図14は、メモリアレイおよびその周辺回路の実施の形態4に従う構成を説明する回路図である。

【0159】

図14を参照して、実施の形態4に従う構成においては、図2に示した実施の形態1に従う構成と比較して、行方向に沿って配置されたソース線SL1〜SLn,SLd0,SLd1に代えて、列方向に沿って配置されたソース線SL1,/SL1,…,/SLmが配置される点で異なる。なお、ソース線SL1〜SLmを総称する場合には、単にソース線SLと表記し、ソース線/SL1〜/SLmを総称する場合には、単にソース線/SLと表記することとする。

【0160】

ソース線SLおよび/SLは、列方向に沿って配置され、その両端の少なくとも一方は、接地配線によって接地電圧GNDと結合される。図14に示される例では、各ソース線の一端側(センスアンプ70の反対側)が行方向に沿って配置された接地配線GL1と接続される。接地配線GL1の両端は、接地電圧GNDと結合される。

【0161】

各メモリセル列において、メモリセルMCおよびリファレンスセルRMCは、ビット線BL,/BLの一方と、ソース線SL,/SLの一方との間に接続される。

【0162】

図14のその他の部分の構成は、図2に示したのと同様であるので詳細な説明は繰返さない。データ書込動作は、選択行のディジット線ドライバ41および選択列のビット線ドライバBDVa,BDVb,/BDVa,/BDVbを用いて、図2の構成と同様に実行される。

【0163】

次に、実施の形態4に従う構成におけるデータ読出動作について説明する。

図14においても、図2と同様に、リードワード線RWL2およびコラム選択線CSL1がHレベルに活性化されて、第2行・第1列のメモリセルが選択メモリセルMC♯として選択され、選択メモリセルMC♯と同一のメモリセル列を共有するリファレンスセルが選択リファレンスセルRMC#として選択されるものとする。

【0164】

データ読出時にメモリセル電流は、センスアンプ70〜データバス/DB1〜ビット線/BL1〜選択メモリセルMC♯〜ソース線/SL1〜接地配線GL1〜接地電圧GNDの経路から構成されるメモリセル電流経路(図14中の実線矢印)を流れる。これに対して、基準電流は、センスアンプ70〜データバスDB1〜ビット線BL1〜選択リファレンスセルRMC♯〜ソース線SL1〜接地配線GL1〜接地電圧GNDの経路から構成される基準電流経路(図14中の点線矢印)を流れる。

【0165】

リファレンスセル行を設けた構成においては、選択メモリセルMC♯および選択リファレンスセルRMC♯は同一メモリセル列に属するので、メモリセル電流経路および基準電流経路の間で、行方向に沿った配線上での経路長、すなわち、データバスDB1,/DB1および接地配線GL1上での経路長は、行選択結果にかかわらず自然に均衡する。これに対して、列方向に沿った配線上での経路長は、メモリセル電流経路および基準電流経路の間で異なってくる。

【0166】

したがって、実施の形態4のように、リファレンスセルの配置方向と、ソース線SLの配置方向とが一致しない構成においては、メモリセル電流経路および基準電流経路の間で、ソース線SL,/SL上の電流経路長が必然的に異なってくる。このため、ソース線SL,/SLと、ソース線SL,/SLに平行に配置されかつメモリセル電流および基準電流経路に含まれるデータバスDB1,/DB1との各々を、単位長当りの電気抵抗が同様となるように設計する必要がある。すなわち、メモリセルMCおよびリファレンスセルRMCには、図12に示された構造を適用して、ソース線SLを金属配線で形成する必要がある。

【0167】

このような構成とすることにより、ソース線SLとリファレンスセルとの配置方向が一致しない構成においても、メモリセル電流経路および基準電流経路の経路抵抗を、アドレス選択結果にかかわらず均衡させることができる。この結果、アドレス選択結果に依存したデータ読出マージンの低下を防ぐことができる。

【0168】

図15には、メモリアレイ10の隣接領域に配置される接地配線の配置のバリエーションが示される。図15(a)には、図14と同様に、行方向に沿った接地配線GL1の両端側を接地電圧GNDと接続する構成がさらに示される。

【0169】

あるいは、図15(b)に示されるように、メモリアレイ10の隣接領域のそれぞれに、列方向に沿った接地配線GL2,GL2#をさらに設けることも可能である。接地配線GL2,GL2#の一端側(センスアンプ70側)を接地電圧GNDと結合し、他端側を接地配線GL1と接続することにより、メモリセル電流経路および基準電流経路を対称形とすることができるので、さらにデータ読出精度を向上することができる。

【0170】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0171】

【発明の効果】

請求項1または2に記載の記憶装置は、参照セルとソース線との配置方向を一致させることにより、選択メモリセルを含む第1の電流経路と選択参照セルを含む第2の電流経路の間で、比較的電気抵抗の大きいソース線上の経路長をアドレス選択結果にかかわらず均衡させることができる。したがって、第1および第2の電流経路のそれぞれの総電気抵抗の差が、選択メモリセルと選択参照セルとの電気抵抗差を表わすようになるため、アドレス選択結果に依存してデータ読出マージンが低下することを防止して、データ読出動作を安定化できる。さらに、固定電圧配線の配置によって、第1および第2の電流経路において、選択メモリセルおよび選択参照セルから固定電圧への経路を対称形にすることができるので、データ読出動作を安定化できる。さらに、第1および第2の電流経路の間で、参照セルおよびソース線と異なる方向に配置される配線上の電気抵抗を均衡させることによって、アドレス選択結果に依存したデータ読出マージンの低下をさらに強力に防止して、データ読出動作を安定化できる。

【0172】

請求項3に記載の記憶装置は、ソース線を金属配線層を用いずに配置できるので、請求項2に記載の記憶装置が奏する効果に加えて、メモリアレイの小面積化を図ることができる。

【0177】

請求項3に記載の記憶装置は、選択メモリセルと選択参照セルとの電気抵抗差を、第1および第2の電流経路の総電気抵抗の差により明確に反映することができるため、請求項1に記載の記憶装置が奏する効果に加えて、さらにデータ読出動作を安定化できる。

【0178】

請求項4に記載の記憶装置は、記憶データに応じた方向に磁化される磁性体膜を有するメモリセルを備えたMRAMデバイスにおいて、請求項1に記載の薄膜磁性体記憶装置が奏する効果を享受することができる。

【0179】

請求項5に記載の記憶装置は、電流比較型のセンスアンプをデータ読出回路として配置することによって、請求項1に記載の薄膜磁性体記憶装置が奏する効果を享受することができる。

【0180】

請求項6に記載の記憶装置は、電圧比較型のセンスアンプをデータ読出回路として配置することによって、請求項1に記載の薄膜磁性体記憶装置が奏する効果を享受することができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態に従うMRAMデバイス1の全体構成を示す概略ブロック図である。

【図2】 メモリアレイおよびその周辺回路の実施の形態1に従う構成を説明する回路図である。

【図3】 メモリセルおよびリファレンスセル周辺の構造を示す断面図である。

【図4】 リファレンスセルを備えたMRAMデバイスにおけるデータ書込およびデータ読出動作を説明する第1の動作波形図である。

【図5】 リファレンスセルを備えたMRAMデバイスにおけるデータ書込およびデータ読出動作を説明する第2の動作波形図である。

【図6】 実施の形態1に従う構成における接地配線の配置例を示す概念図である。

【図7】 メモリアレイおよびその周辺回路の実施の形態2に従う構成を説明する回路図である。

【図8】 実施の形態2に従うメモリセルおよびリファレンスセル周辺の構造を示す断面図である。

【図9】 実施の形態2に従う構成における接地配線の配置例を示す概念図である。

【図10】 メモリアレイおよびその周辺回路の実施の形態3に従う構成を説明する回路図である。

【図11】 実施の形態3に従うメモリセルおよびリファレンスセル周辺の構造例を示す断面図である。

【図12】 実施の形態3に従うメモリセルおよびリファレンスセル周辺の他の構造例を示す断面図である。

【図13】 実施の形態3に従う構成における接地配線の配置例を示す概念図である。

【図14】 メモリアレイおよびその周辺回路の実施の形態4に従う構成を説明する回路図である。

【図15】 実施の形態4に従う構成における接地配線の配置例を示す概念図である。

【図16】 MTJメモリセルの構成を示す概略図である。

【図17】 MTJメモリセルに対するデータ書込動作を説明する概念図である。

【図18】 データ書込時におけるデータ書込電流とトンネル磁気抵抗素子の磁化方向との関係を示す概念図である。

【図19】 MTJメモリセルからのデータ読出動作を説明する概念図である。

【符号の説明】

1 MRAMデバイス、10 メモリアレイ、20 行デコーダ、25 列デコーダ、70 センスアンプ、110 ソース領域(不純物領域)、120 ドレイン領域(不純物領域)、130 ゲート、ADD アドレス信号、ATR アクセストランジスタ、ATRr アクセス素子、BL,/BL ビット線、BLref リファレンスビット線、DB1,/DB1,DB2,/DB2 データバス、DIN 書込データ、DL ディジット線、DOUT 読出データ、DRWL0,DRWL1 ダミーリードワード線、FL 固定磁化層、GL,GL1,GL2 接地配線、GND 接地電圧、M1,M2,M3,M4 金属配線層、MC MTJメモリセル、MC♯ 選択メモリセル、RMC リファレンスセル、RMC♯ 選択リファレンスセル、RWL リードワード線、SL,/SL,SLd0,SLd1,SLr ソース線、TB トンネルバリア、TMR トンネル磁気抵抗素子、TMRr 基準抵抗、VL 自由磁化層、Vcc 電源電圧。

Claims (6)

- 各々が記憶データに応じて2つのレベルの電気抵抗の一方を有する複数のメモリセルと、各々が前記複数のメモリセルのうちのデータ読出時の選択メモリセルの比較対象として設けられる複数の参照セルとが行列状に配置されたメモリアレイを備え、

前記複数の参照セルは、前記行および列の一方に沿って、前記行および列の他方を前記複数のメモリセルと共有するように配置され、

前記行にそれぞれ対応して配置され、選択行において活性化される複数のワード線と、

前記列にそれぞれ対応して配置される複数のデータ線と、

前記行および列の前記一方にそれぞれ対応して配置され、各々が固定電圧を供給する複数のソース線とをさらに備え、

前記複数のメモリセルの各々は、前記複数のデータ線の対応する1本と前記複数のソース線の対応する1本との間に直列に接続された、前記記憶データに応じて電気抵抗が変化する記憶素子および対応するワード線の活性化に応答してオンするアクセス素子を含み、

前記複数のデータ線は、

前記データ読出時に、前記複数のメモリセルのうちの、データ読出対象に選択された選択メモリセルと接続される第1のデータ線と、

前記データ読出時に、前記複数の参照セルのうちの、前記選択メモリセルとの間で前記行および列の前記他方を共有する選択参照セルと接続される第2のデータ線とを含み、

前記データ読出時に前記第1および第2のデータ線を前記固定電圧と異なる電圧と結合して、前記選択メモリセルおよび前記選択参照セルをそれぞれ通過する第1および第2の電流経路を形成させるデータ読出回路と、

前記メモリアレイに隣接する領域において、前記行および列の前記他方に沿って配置される固定電圧配線と、

前記メモリアレイに隣接する領域において、前記行に沿って配置される第1および第2のデータバスとをさらに備え、

前記複数のソース線の各々は、前記固定電圧配線と電気的に結合され、

前記データ読出時において、前記第1および第2のデータ線は、前記第1および第2のデータバスを介して前記データ読出回路と電気的に接続され、

前記データ読出回路は、前記第1および第2の電流経路の電気抵抗差に基いて、前記選択メモリセルから前記記憶データを読出すように構成され、

前記固定電圧配線の単位長当たりの電気抵抗は、前記複数のデータ線および前記データバスのうちの、前記固定電圧配線と同じ方向に配置される一方の単位長当たりの電気抵抗と同等に設計される、記憶装置。 - 前記固定電圧配線の単位長当たりの電気抵抗は、前記複数のソース線の単位長当たりの電気抵抗よりも小さい、請求項1に記載の記憶装置。

- 前記データ読出時において、前記第1の電流経路から前記選択メモリセルを除いた部分の電気抵抗は、前記第2の電流経路から前記選択参照セルを除外した部分の電気抵抗と均衡する、請求項1に記載の記憶装置。

- 前記記憶素子は、複数の磁性体膜を有し、

前記複数の磁性体膜のうちの少なくとも1つは、前記記憶データに応じた方向に磁化される、請求項1に記載の記憶装置。 - 前記データ読出時に、前記第1および第2のデータ線は、前記固定電圧と異なる共通の電圧と結合され、

前記データ読出回路は、前記第1および第2のデータ線の通過電流差に基づいて、前記選択メモリセルから前記記憶データを読出す、請求項1に記載の記憶装置。 - 前記データ読出時に、前記第1および第2のデータ線は、同一の電流を供給され、

前記データ読出回路は、前記第1および第2のデータ線の電圧差に基づいて、前記選択メモリセルから前記記憶データを読出す、請求項1に記載の記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002202659A JP4242117B2 (ja) | 2002-07-11 | 2002-07-11 | 記憶装置 |

| US10/330,107 US6760251B2 (en) | 2002-07-11 | 2002-12-30 | Memory device reading data according to difference in electrical resistance between selected memory cell and reference cell |

| CNB031199712A CN1331155C (zh) | 2002-07-11 | 2003-03-14 | 基于选择存储单元与基准单元的电阻差读出数据的存储器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002202659A JP4242117B2 (ja) | 2002-07-11 | 2002-07-11 | 記憶装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008214203A Division JP4749453B2 (ja) | 2008-08-22 | 2008-08-22 | 記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004046962A JP2004046962A (ja) | 2004-02-12 |

| JP2004046962A5 JP2004046962A5 (ja) | 2005-10-20 |

| JP4242117B2 true JP4242117B2 (ja) | 2009-03-18 |

Family

ID=29997146

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002202659A Expired - Fee Related JP4242117B2 (ja) | 2002-07-11 | 2002-07-11 | 記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6760251B2 (ja) |

| JP (1) | JP4242117B2 (ja) |

| CN (1) | CN1331155C (ja) |

Families Citing this family (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6829158B2 (en) | 2001-08-22 | 2004-12-07 | Motorola, Inc. | Magnetoresistive level generator and method |

| JP4071531B2 (ja) * | 2002-04-23 | 2008-04-02 | 株式会社ルネサステクノロジ | 薄膜磁性体記憶装置 |

| CA2526467C (en) * | 2003-05-20 | 2015-03-03 | Kagutech Ltd. | Digital backplane recursive feedback control |

| US7369428B2 (en) * | 2003-09-29 | 2008-05-06 | Samsung Electronics Co., Ltd. | Methods of operating a magnetic random access memory device and related devices and structures |

| KR100615089B1 (ko) * | 2004-07-14 | 2006-08-23 | 삼성전자주식회사 | 낮은 구동 전류를 갖는 자기 램 |

| JP3935150B2 (ja) * | 2004-01-20 | 2007-06-20 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| JP4646636B2 (ja) * | 2004-02-20 | 2011-03-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US20050195629A1 (en) * | 2004-03-02 | 2005-09-08 | Leddige Michael W. | Interchangeable connection arrays for double-sided memory module placement |

| US7184341B2 (en) * | 2004-07-26 | 2007-02-27 | Etron Technology, Inc. | Method of data flow control for a high speed memory |

| DE102004047666B4 (de) * | 2004-09-30 | 2015-04-02 | Qimonda Ag | Speicher mit Widerstandsspeicherzelle und Bewertungsschaltung |

| JP4890016B2 (ja) * | 2005-03-16 | 2012-03-07 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| US7339814B2 (en) * | 2005-08-24 | 2008-03-04 | Infineon Technologies Ag | Phase change memory array having equalized resistance |

| JP4853735B2 (ja) * | 2005-10-18 | 2012-01-11 | 日本電気株式会社 | Mram、及びその動作方法 |

| JP4905839B2 (ja) * | 2005-10-18 | 2012-03-28 | 日本電気株式会社 | Mramの動作方法 |

| JP2008065972A (ja) * | 2006-08-10 | 2008-03-21 | Nec Electronics Corp | 半導体記憶装置 |

| US20080173975A1 (en) * | 2007-01-22 | 2008-07-24 | International Business Machines Corporation | Programmable resistor, switch or vertical memory cell |

| US8510633B2 (en) * | 2007-04-17 | 2013-08-13 | Nec Corporation | Semiconductor storage device and method of operating the same |

| US7859025B2 (en) * | 2007-12-06 | 2010-12-28 | International Business Machines Corporation | Metal ion transistor |

| US7706176B2 (en) * | 2008-01-07 | 2010-04-27 | Qimonda Ag | Integrated circuit, cell arrangement, method for manufacturing an integrated circuit and for reading a memory cell status, memory module |

| JP2009164390A (ja) * | 2008-01-08 | 2009-07-23 | Renesas Technology Corp | 磁気記録装置 |

| JP5150932B2 (ja) * | 2008-04-04 | 2013-02-27 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| JP5197477B2 (ja) * | 2009-04-30 | 2013-05-15 | 株式会社東芝 | 半導体記憶装置 |

| KR101068573B1 (ko) * | 2009-04-30 | 2011-09-30 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| JP2013026600A (ja) | 2011-07-26 | 2013-02-04 | Renesas Electronics Corp | 半導体装置及び磁気ランダムアクセスメモリ |

| US8593173B2 (en) | 2011-09-26 | 2013-11-26 | Qualcomm Incorporated | Programmable logic sensing in magnetic random access memory |

| US8743580B2 (en) | 2012-03-30 | 2014-06-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Apparatus for high speed ROM cells |

| US10497402B2 (en) | 2012-03-30 | 2019-12-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Apparatus for high speed ROM cells |

| KR102060488B1 (ko) * | 2012-12-27 | 2019-12-30 | 삼성전자주식회사 | 불휘발성 랜덤 액세스 메모리 장치 및 그것의 데이터 읽기 방법 |

| JP2013140667A (ja) * | 2013-03-11 | 2013-07-18 | Hitachi Ltd | 半導体装置 |

| US8723329B1 (en) * | 2013-03-15 | 2014-05-13 | Invensas Corporation | In-package fly-by signaling |

| US9741434B2 (en) | 2013-03-22 | 2017-08-22 | SK Hynix Inc. | Resistance change memory |

| JP2015185179A (ja) * | 2014-03-20 | 2015-10-22 | 株式会社東芝 | 抵抗変化メモリ |

| US20160254318A1 (en) * | 2015-02-27 | 2016-09-01 | Qualcomm Incorporated | MAGNETIC RANDOM ACCESS MEMORY (MRAM) BIT CELLS EMPLOYING SOURCE LINES (SLs) AND/OR BIT LINES (BLs) DISPOSED IN MULTIPLE, STACKED METAL LAYERS TO REDUCE MRAM BIT CELL RESISTANCE |

| JP6749021B2 (ja) | 2015-05-15 | 2020-09-02 | 国立大学法人東北大学 | 抵抗変化型素子を備えた記憶回路 |

| WO2019112068A1 (ja) | 2017-12-08 | 2019-06-13 | 国立大学法人東北大学 | 抵抗変化型素子を備えた記憶回路及びセンスアンプ |

| JP2019160368A (ja) * | 2018-03-13 | 2019-09-19 | 東芝メモリ株式会社 | 半導体記憶装置 |

| US11139012B2 (en) * | 2019-03-28 | 2021-10-05 | Samsung Electronics Co., Ltd. | Resistive memory device having read currents for a memory cell and a reference cell in opposite directions |

| US11705176B2 (en) | 2020-08-07 | 2023-07-18 | Tohoku University | Storage circuit provided with variable resistance type elements, and its test device |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6055178A (en) * | 1998-12-18 | 2000-04-25 | Motorola, Inc. | Magnetic random access memory with a reference memory array |

| JP3589346B2 (ja) | 1999-06-17 | 2004-11-17 | 松下電器産業株式会社 | 磁気抵抗効果素子および磁気抵抗効果記憶素子 |

| JP3415586B2 (ja) | 1999-12-16 | 2003-06-09 | エヌイーシーマイクロシステム株式会社 | 同期型dram |

| JP2003016777A (ja) * | 2001-06-28 | 2003-01-17 | Mitsubishi Electric Corp | 薄膜磁性体記憶装置 |

| US6606263B1 (en) * | 2002-04-19 | 2003-08-12 | Taiwan Semiconductor Manufacturing Company | Non-disturbing programming scheme for magnetic RAM |

| JP2004062922A (ja) * | 2002-07-25 | 2004-02-26 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

-

2002

- 2002-07-11 JP JP2002202659A patent/JP4242117B2/ja not_active Expired - Fee Related

- 2002-12-30 US US10/330,107 patent/US6760251B2/en not_active Expired - Fee Related

-

2003

- 2003-03-14 CN CNB031199712A patent/CN1331155C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1331155C (zh) | 2007-08-08 |

| JP2004046962A (ja) | 2004-02-12 |

| CN1467743A (zh) | 2004-01-14 |

| US20040008556A1 (en) | 2004-01-15 |

| US6760251B2 (en) | 2004-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4242117B2 (ja) | 記憶装置 | |

| US7233537B2 (en) | Thin film magnetic memory device provided with a dummy cell for data read reference | |

| KR100654266B1 (ko) | 자기 터널 접합부를 갖는 박막 자성체 기억 장치 | |

| JP4656720B2 (ja) | 薄膜磁性体記憶装置 | |

| KR100418160B1 (ko) | 전기 저항치 변화에 따라 데이터를 기억하는 데이터 판독마진이 큰 기억 장치 | |

| JP4570313B2 (ja) | 薄膜磁性体記憶装置 | |

| US6839269B2 (en) | Magnetic random access memory | |

| JP4726292B2 (ja) | 薄膜磁性体記憶装置 | |

| KR100514959B1 (ko) | 박막 자성체 기억 장치 | |

| JP4046513B2 (ja) | 半導体集積回路 | |

| JP2003017665A (ja) | 薄膜磁性体記憶装置 | |

| JP4450538B2 (ja) | 薄膜磁性体記憶装置 | |

| US6903965B2 (en) | Thin film magnetic memory device permitting high precision data read | |

| JP2004103060A (ja) | 不揮発性記憶装置 | |

| JP5230783B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4219141B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4219134B2 (ja) | 薄膜磁性体記憶装置 | |

| JP4749453B2 (ja) | 記憶装置 | |

| JP2004103202A (ja) | 薄膜磁性体記憶装置 | |

| JP5076182B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5355666B2 (ja) | 薄膜磁性体記憶装置 | |

| JP5036854B2 (ja) | 半導体装置 | |

| JP4315703B2 (ja) | 薄膜磁性体記憶装置 | |

| WO2011055420A1 (ja) | 半導体装置 | |

| JP2009134794A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050630 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050630 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080616 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080624 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080930 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081216 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081224 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130109 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130109 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140109 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |