JP2018085504A - Aldギャップ充填スペーサマスクを用いる自己整合型マルチパターニングプロセスフロー - Google Patents

Aldギャップ充填スペーサマスクを用いる自己整合型マルチパターニングプロセスフロー Download PDFInfo

- Publication number

- JP2018085504A JP2018085504A JP2017216857A JP2017216857A JP2018085504A JP 2018085504 A JP2018085504 A JP 2018085504A JP 2017216857 A JP2017216857 A JP 2017216857A JP 2017216857 A JP2017216857 A JP 2017216857A JP 2018085504 A JP2018085504 A JP 2018085504A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- core material

- spacer

- gap filler

- gap

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 205

- 125000006850 spacer group Chemical group 0.000 title claims abstract description 147

- 230000008569 process Effects 0.000 title claims abstract description 140

- 238000000059 patterning Methods 0.000 title claims abstract description 50

- 239000000758 substrate Substances 0.000 claims abstract description 161

- 239000011162 core material Substances 0.000 claims abstract description 123

- 238000000151 deposition Methods 0.000 claims abstract description 56

- 238000005530 etching Methods 0.000 claims abstract description 52

- 238000000231 atomic layer deposition Methods 0.000 claims abstract description 46

- 239000000463 material Substances 0.000 claims abstract description 27

- 239000000945 filler Substances 0.000 claims description 121

- 238000012545 processing Methods 0.000 claims description 47

- 239000002243 precursor Substances 0.000 claims description 38

- 230000008021 deposition Effects 0.000 claims description 24

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 22

- 229910052710 silicon Inorganic materials 0.000 claims description 22

- 239000010703 silicon Substances 0.000 claims description 21

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 16

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 13

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 13

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 13

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 13

- 229910052799 carbon Inorganic materials 0.000 claims description 12

- 230000001590 oxidative effect Effects 0.000 claims description 7

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 6

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 5

- 229910010271 silicon carbide Inorganic materials 0.000 claims description 5

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 5

- 239000007789 gas Substances 0.000 description 77

- 239000010410 layer Substances 0.000 description 68

- 235000012431 wafers Nutrition 0.000 description 53

- 238000010586 diagram Methods 0.000 description 37

- 239000012071 phase Substances 0.000 description 34

- 239000010408 film Substances 0.000 description 30

- 238000010926 purge Methods 0.000 description 22

- 239000011295 pitch Substances 0.000 description 19

- 239000000376 reactant Substances 0.000 description 19

- 239000007788 liquid Substances 0.000 description 18

- 238000004519 manufacturing process Methods 0.000 description 17

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 description 17

- 239000004065 semiconductor Substances 0.000 description 17

- 238000012546 transfer Methods 0.000 description 13

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 12

- 238000001704 evaporation Methods 0.000 description 11

- 239000012159 carrier gas Substances 0.000 description 10

- 230000008020 evaporation Effects 0.000 description 10

- 238000002156 mixing Methods 0.000 description 10

- 239000011261 inert gas Substances 0.000 description 9

- 150000002500 ions Chemical class 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 229910052760 oxygen Inorganic materials 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- 238000003860 storage Methods 0.000 description 8

- 238000009826 distribution Methods 0.000 description 7

- 238000011049 filling Methods 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical compound C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 6

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- -1 for example Substances 0.000 description 6

- 238000009616 inductively coupled plasma Methods 0.000 description 6

- 239000000203 mixture Substances 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 239000004215 Carbon black (E152) Substances 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 239000012792 core layer Substances 0.000 description 4

- 239000012530 fluid Substances 0.000 description 4

- 229930195733 hydrocarbon Natural products 0.000 description 4

- 150000002430 hydrocarbons Chemical class 0.000 description 4

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 4

- 239000007800 oxidant agent Substances 0.000 description 4

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 4

- 238000001179 sorption measurement Methods 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 239000006227 byproduct Substances 0.000 description 3

- KOPOQZFJUQMUML-UHFFFAOYSA-N chlorosilane Chemical compound Cl[SiH3] KOPOQZFJUQMUML-UHFFFAOYSA-N 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 238000001312 dry etching Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 238000011065 in-situ storage Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 238000011112 process operation Methods 0.000 description 3

- 238000012163 sequencing technique Methods 0.000 description 3

- FZHAPNGMFPVSLP-UHFFFAOYSA-N silanamine Chemical compound [SiH3]N FZHAPNGMFPVSLP-UHFFFAOYSA-N 0.000 description 3

- 239000002210 silicon-based material Substances 0.000 description 3

- 230000032258 transport Effects 0.000 description 3

- 238000011144 upstream manufacturing Methods 0.000 description 3

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 239000005046 Chlorosilane Substances 0.000 description 2

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 2

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 2

- 239000005977 Ethylene Substances 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 2

- 239000002194 amorphous carbon material Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000001273 butane Substances 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 239000012636 effector Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005672 electromagnetic field Effects 0.000 description 2

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 238000011068 loading method Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- VYIRVGYSUZPNLF-UHFFFAOYSA-N n-(tert-butylamino)silyl-2-methylpropan-2-amine Chemical compound CC(C)(C)N[SiH2]NC(C)(C)C VYIRVGYSUZPNLF-UHFFFAOYSA-N 0.000 description 2

- IJDNQMDRQITEOD-UHFFFAOYSA-N n-butane Chemical compound CCCC IJDNQMDRQITEOD-UHFFFAOYSA-N 0.000 description 2

- OFBQJSOFQDEBGM-UHFFFAOYSA-N n-pentane Natural products CCCCC OFBQJSOFQDEBGM-UHFFFAOYSA-N 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000000678 plasma activation Methods 0.000 description 2

- QQONPFPTGQHPMA-UHFFFAOYSA-N propylene Natural products CC=C QQONPFPTGQHPMA-UHFFFAOYSA-N 0.000 description 2

- 125000004805 propylene group Chemical group [H]C([H])([H])C([H])([*:1])C([H])([H])[*:2] 0.000 description 2

- 150000003254 radicals Chemical class 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- BEEYLGLWYXWFAG-UHFFFAOYSA-N 2-aminosilyl-2-methylpropane Chemical compound CC(C)(C)[SiH2]N BEEYLGLWYXWFAG-UHFFFAOYSA-N 0.000 description 1

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 1

- VUGMARFZKDASCX-UHFFFAOYSA-N 2-methyl-N-silylpropan-2-amine Chemical compound CC(C)(C)N[SiH3] VUGMARFZKDASCX-UHFFFAOYSA-N 0.000 description 1

- MNTMWHBQGOKGDD-UHFFFAOYSA-N 3-methylbutylsilane Chemical compound CC(C)CC[SiH3] MNTMWHBQGOKGDD-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- BIVNKSDKIFWKFA-UHFFFAOYSA-N N-propan-2-yl-N-silylpropan-2-amine Chemical compound CC(C)N([SiH3])C(C)C BIVNKSDKIFWKFA-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- ABIPMNCKZMKDKV-UHFFFAOYSA-N [tert-butyl(dimethyl)silyl] carbamate Chemical compound CC(C)(C)[Si](C)(C)OC(N)=O ABIPMNCKZMKDKV-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910003481 amorphous carbon Inorganic materials 0.000 description 1

- 150000001450 anions Chemical class 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- VQPFDLRNOCQMSN-UHFFFAOYSA-N bromosilane Chemical compound Br[SiH3] VQPFDLRNOCQMSN-UHFFFAOYSA-N 0.000 description 1

- AUOLYXZHVVMFPD-UHFFFAOYSA-N butan-2-yl(chloro)silane Chemical compound CCC(C)[SiH2]Cl AUOLYXZHVVMFPD-UHFFFAOYSA-N 0.000 description 1

- VBLDUBUUQYXSCG-UHFFFAOYSA-N butan-2-ylsilane Chemical compound CCC(C)[SiH3] VBLDUBUUQYXSCG-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- VNJCDDZVNHPVNM-UHFFFAOYSA-N chloro(ethyl)silane Chemical compound CC[SiH2]Cl VNJCDDZVNHPVNM-UHFFFAOYSA-N 0.000 description 1

- CRIVIYPBVUGWSC-UHFFFAOYSA-N chloro(propan-2-yl)silane Chemical compound CC(C)[SiH2]Cl CRIVIYPBVUGWSC-UHFFFAOYSA-N 0.000 description 1

- YGHUUVGIRWMJGE-UHFFFAOYSA-N chlorodimethylsilane Chemical compound C[SiH](C)Cl YGHUUVGIRWMJGE-UHFFFAOYSA-N 0.000 description 1

- AZFVLHQDIIJLJG-UHFFFAOYSA-N chloromethylsilane Chemical compound [SiH3]CCl AZFVLHQDIIJLJG-UHFFFAOYSA-N 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- UWGIJJRGSGDBFJ-UHFFFAOYSA-N dichloromethylsilane Chemical compound [SiH3]C(Cl)Cl UWGIJJRGSGDBFJ-UHFFFAOYSA-N 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- UCXUKTLCVSGCNR-UHFFFAOYSA-N diethylsilane Chemical compound CC[SiH2]CC UCXUKTLCVSGCNR-UHFFFAOYSA-N 0.000 description 1

- UBHZUDXTHNMNLD-UHFFFAOYSA-N dimethylsilane Chemical compound C[SiH2]C UBHZUDXTHNMNLD-UHFFFAOYSA-N 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- OGWXFZNXPZTBST-UHFFFAOYSA-N ditert-butyl(chloro)silane Chemical compound CC(C)(C)[SiH](Cl)C(C)(C)C OGWXFZNXPZTBST-UHFFFAOYSA-N 0.000 description 1

- LFLMSLJSSVNEJH-UHFFFAOYSA-N ditert-butyl(silyl)silane Chemical compound CC(C)(C)[SiH]([SiH3])C(C)(C)C LFLMSLJSSVNEJH-UHFFFAOYSA-N 0.000 description 1

- JTGAUXSVQKWNHO-UHFFFAOYSA-N ditert-butylsilicon Chemical compound CC(C)(C)[Si]C(C)(C)C JTGAUXSVQKWNHO-UHFFFAOYSA-N 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- KCWYOFZQRFCIIE-UHFFFAOYSA-N ethylsilane Chemical compound CC[SiH3] KCWYOFZQRFCIIE-UHFFFAOYSA-N 0.000 description 1

- XPBBUZJBQWWFFJ-UHFFFAOYSA-N fluorosilane Chemical compound [SiH3]F XPBBUZJBQWWFFJ-UHFFFAOYSA-N 0.000 description 1

- 150000002366 halogen compounds Chemical class 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 238000000671 immersion lithography Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- IDIOJRGTRFRIJL-UHFFFAOYSA-N iodosilane Chemical compound I[SiH3] IDIOJRGTRFRIJL-UHFFFAOYSA-N 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 239000012705 liquid precursor Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000001404 mediated effect Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- IFVRUKGTKXWWQF-UHFFFAOYSA-N methylaminosilicon Chemical compound CN[Si] IFVRUKGTKXWWQF-UHFFFAOYSA-N 0.000 description 1

- UIUXUFNYAYAMOE-UHFFFAOYSA-N methylsilane Chemical compound [SiH3]C UIUXUFNYAYAMOE-UHFFFAOYSA-N 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- OWKFQWAGPHVFRF-UHFFFAOYSA-N n-(diethylaminosilyl)-n-ethylethanamine Chemical compound CCN(CC)[SiH2]N(CC)CC OWKFQWAGPHVFRF-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 150000001282 organosilanes Chemical class 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- KNCYXPMJDCCGSJ-UHFFFAOYSA-N piperidine-2,6-dione Chemical compound O=C1CCCC(=O)N1 KNCYXPMJDCCGSJ-UHFFFAOYSA-N 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 1

- 229920000548 poly(silane) polymer Polymers 0.000 description 1

- 239000004926 polymethyl methacrylate Substances 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 230000002829 reductive effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000284 resting effect Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 238000006557 surface reaction Methods 0.000 description 1

- UTYRQCFTOYUATF-UHFFFAOYSA-N tert-butyl(chloro)silane Chemical compound CC(C)(C)[SiH2]Cl UTYRQCFTOYUATF-UHFFFAOYSA-N 0.000 description 1

- IPGXXWZOPBFRIZ-UHFFFAOYSA-N tert-butyl(silyl)silane Chemical compound CC(C)(C)[SiH2][SiH3] IPGXXWZOPBFRIZ-UHFFFAOYSA-N 0.000 description 1

- BCNZYOJHNLTNEZ-UHFFFAOYSA-N tert-butyldimethylsilyl chloride Chemical compound CC(C)(C)[Si](C)(C)Cl BCNZYOJHNLTNEZ-UHFFFAOYSA-N 0.000 description 1

- KNSVRQSOPKYFJN-UHFFFAOYSA-N tert-butylsilicon Chemical compound CC(C)(C)[Si] KNSVRQSOPKYFJN-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- ZGYICYBLPGRURT-UHFFFAOYSA-N tri(propan-2-yl)silicon Chemical compound CC(C)[Si](C(C)C)C(C)C ZGYICYBLPGRURT-UHFFFAOYSA-N 0.000 description 1

- ZDHXKXAHOVTTAH-UHFFFAOYSA-N trichlorosilane Chemical compound Cl[SiH](Cl)Cl ZDHXKXAHOVTTAH-UHFFFAOYSA-N 0.000 description 1

- 239000005052 trichlorosilane Substances 0.000 description 1

- VOSJXMPCFODQAR-UHFFFAOYSA-N trisilylamine group Chemical group [SiH3]N([SiH3])[SiH3] VOSJXMPCFODQAR-UHFFFAOYSA-N 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910001868 water Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3081—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their composition, e.g. multilayer masks, materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0337—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/042—Coating on selected surface areas, e.g. using masks using masks

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

- C23C16/45536—Use of plasma, radiation or electromagnetic fields

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

- H01L21/0274—Photolithographic processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0332—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their composition, e.g. multilayer masks, materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3085—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by their behaviour during the process, e.g. soluble masks, redeposited masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3086—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/32—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02167—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon carbide not containing oxygen, e.g. SiC, SiC:H or silicon carbonitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/0217—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02172—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides

- H01L21/02175—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal

- H01L21/02186—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal the material containing titanium, e.g. TiO2

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Inorganic Chemistry (AREA)

- Plasma & Fusion (AREA)

- Electromagnetism (AREA)

- Chemical Vapour Deposition (AREA)

- Formation Of Insulating Films (AREA)

- Drying Of Semiconductors (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【課題】自己整合型の複数のパターニングプロセスのための対称的なスペーサを形成する方法および装置を提供する【解決手段】方法には、コア材314およびターゲット層305を含むパターニングされた基板の上に原子層堆積によってギャップ充填材338を堆積させることと、基板を平坦化することと、コア材をエッチングして対称的なスペーサを形成することとが含まれる。ギャップ充填材は、フィーチャがアンダーフィルされるように、フィーチャを完全に充填するには不十分な期間において堆積されてよい。【選択図】図3L

Description

高度集積回路の製作には、半導体の大量生産において小さなフィーチャのパターニングが含まれることが多い。マルチパターニング技術は、193nm液浸リソグラフィなどのリソグラフィ技術に基づいてフィーチャサイズのスケーリングが可能であってよい。自己整合型ダブルパターニングは、マルチパターニング技術の一例である。

本明細書では、半導体基板などの基板を処理する方法が提供される。一態様は基板を処理する方法を含み、その方法は、ギャップ形成するようにパターニングされたコア材と、ターゲット層とを有する基板を提供することと、ギャップ充填材が基板上のギャップに堆積するように、ギャップ充填材をコア材の上に共形に堆積させることと、基板を平坦化してギャップ充填材およびコア材を含む平面を形成することと、コア材を選択的にエッチングしてターゲット層をエッチングするためのマスクとして用いられる対称形状のスペーサを形成することとを含む。

様々な実施形態では、ギャップ充填材は、原子層堆積によって堆積される。いくつかの実施形態では、ギャップ充填材は、ギャップを完全に充填するには不十分な期間において原子層堆積によって堆積される。

いくつかの実施形態では、ギャップは約x[nm]未満の開口を有し、ギャップ充填材は、ギャップ充填材を約0.4×x[nm]から約0.5×x[nm]の間の厚さに堆積させるのに十分な期間において堆積する。いくつかの実施形態では、xは50であり、いくつかの実施形態では、xは50未満である。

いくつかの実施形態では、ギャップ充填材は、酸化シリコン、窒化シリコン、炭化シリコン、および、酸化チタンのいずれか1つである。

いくつかの実施形態では、マスクにおける対称形状のスペーサ間の臨界寸法は、約50nm未満である。対称形状のスペーサは、複数のパターニング技術に用いられてよい。いくつかの実施形態では、ギャップ充填材を堆積することと基板を平坦化することは、ピッチウォーキングを低減させる。様々な実施形態では、対称形状のスペーサは、ギャップ充填材を含む。

この方法は、また、ギャップ充填材を堆積させる前に基板の上に別の共形膜を堆積し、別の共形膜を異方的にエッチングしてコア材の側壁上に側壁スペーサを形成することを含んでもよい。様々な実施形態では、基板を選択的にエッチングして対称形状のスペーサを形成することは、側壁スペーサに対して選択的にコア材およびギャップ充填材を除去することを含む。基板を選択的にエッチングして対称形状のスペーサを形成することは、ギャップ充填材に対して選択的にコア材を除去することを含んでよい。

様々な実施形態では、コア材は、スピンオン炭素、ダイヤモンド状炭素、および/または、ギャップ充填アッシング可能ハードマスクのいずれかであってよい。

様々な実施形態では、ギャップ充填材を堆積させることは、基板をシリコン含有前駆体および酸化プラズマの交互パルスに曝露することを含む。

別の態様が含む方法は、マスクを形成するスペーサを含む基板を提供することであって、各スペーサは、スペーサの上面に垂直な側壁を備え、スペーサは、ギャップ充填材をコア材のギャップに共形に堆積させることによって形成されることと、ギャップ充填材およびコア材を平坦化して平面を形成することと、コア材を選択的に除去することと、スペーサをマスクとして用いてターゲット層をエッチングすることとを含む。様々な実施形態では、マスクは約50nm未満のピッチを有する。

様々な実施形態では、ギャップ充填材は、原子層堆積によって堆積される。いくつかの実施形態では、ギャップ充填材は、ギャップを完全に充填するには不十分は期間において原子層堆積によって堆積される。

いくつかの実施形態では、ギャップ充填材は、酸化シリコン、窒化シリコン、炭化シリコン、および、酸化チタンからなる群より選択される。

対称形状のスペーサは、複数のパターニング技術に用いられてよい。いくつかの実施形態では、ギャップ充填材を堆積させることと基板を平坦化することとは、ピッチウォーキングを低減させる。様々な実施形態では、対称形状のスペーサは、ギャップ充填材を含む。

様々な実施形態では、コア材は炭素を含む。コア材は、スピンオン炭素、ダイヤモンド状炭素、および/または、ギャップ充填アッシング可能ハードマスクのいずれかであってよい。

様々な実施形態では、ギャップ充填材を堆積させることは、基板をシリコン含有前駆体および酸化プラズマの交互パルスに曝露することを含む。

別の態様が含む方法は、マスクを形成するスペーサを含む基板を提供することであって、各スペーサは、90°±5°の角度でスペーサの上面に交わる側壁を備え、スペーサは、ギャップ充填材をコア材のギャップに共形に堆積させることによって形成されることと、ギャップ充填材およびコア材を平坦化して平面を形成することと、コア材を選択的に除去することと、スペーサをマスクとして用いてターゲット層をエッチングすることとを含む。

様々な実施形態では、ギャップ充填材は、原子層堆積によって堆積される。いくつかの実施形態では、ギャップ充填材は、ギャップを完全に充填するには不十分な期間において原子層堆積によって堆積される。

いくつかの実施形態では、ギャップ充填材は、酸化シリコン、窒化シリコン、炭化シリコン、および、酸化チタンのいずれかである。

対称形状のスペーサは、複数のパターニング技術に用いられてよい。いくつかの実施形態では、ギャップ充填材を堆積させることと基板を平坦化することとは、ピッチウォーキングを低減させる。様々な実施形態では、対称形状のスペーサは、ギャップ充填材を含む。

様々な実施形態では、コア材は炭素を含む。コア材は、スピンオン炭素、ダイヤモンド状炭素、および/または、ギャップ充填アッシング可能ハードマスクのいずれかであってよい。

様々な実施形態では、ギャップ充填材を堆積させることは、基板をシリコン含有前駆体および酸化プラズマの交互パルスに曝露することを含む。

別の態様は、基板をパターニングする装置を含み、この装置は、1つ以上のプロセスチャンバと、1つ以上のプロセスチャンバおよび関連する流量制御ハードウェアへの1つ以上のガス流入口と、低周波無線周波数(LFRF)発生器と、高周波無線周波数(HFRF)発生器と、少なくとも1つのプロセッサおよびメモリを有するコントローラとを備え、少なくとも1つのプロセッサおよびメモリは、互いに通信可能に接続され、少なくとも1つのプロセッサは、流量制御ハードウェア、LFRF発生器、および、HFRF発生器と少なくとも動作可能に接続され、メモリは、流量制御ハードウェア、HFRF発生器、および、LFRF発生器を少なくとも制御するように少なくとも1つのプロセッサを制御するためのコンピュータ実行可能な命令を記憶して:ギャップ充填材前駆体を導入してターゲット層を含む基板のコア材の上にギャップ充填材を共形に堆積させ、コア材はギャップを形成するためにパターニングされ、堆積はギャップ充填材が基板上のギャップに堆積するように行われ、基板を平坦化してギャップ充填材およびコア材を含む平面を形成し、コア材を選択的にエッチングしてターゲット層をエッチングするためのマスクとして用いられる対称形状のスペーサを形成する。

別の態様は、基板をパターニングする装置を含み、この装置は、1つ以上のプロセスチャンバと、1つ以上のプロセスチャンバおよび関連する流量制御ハードウェアへの1つ以上のガス流入口と、低周波無線周波数(LFRF)発生器と、高周波無線周波数(HFRF)発生器と、少なくとも1つのプロセッサおよびメモリを有するコントローラとを備え、少なくとも1つのプロセッサおよびメモリは、互いに通信可能に接続され、少なくとも1つのプロセッサは、流量制御ハードウェア、LFRF発生器、および、HFRF発生器と少なくとも動作可能に接続され、メモリは、流量制御ハードウェア、HFRF発生器、および、LFRF発生器を少なくとも制御するように少なくとも1つのプロセッサを制御するためのコンピュータ実行可能な命令を記憶して:マスクを形成するスペーサを含む基板を1つ以上のプロセスチャンバに搬送し、各スペーサは、スペーサの上面に垂直な側壁を備え、スペーサは、ギャップ充填材をコア材のギャップに共形に堆積させることによって形成され、充填材およびコア材を平坦化して平面を形成し、コア材を選択的に除去し、スペーサをマスクとして用いてターゲット層をエッチングする。様々な実施形態では、マスクは約50nm未満のピッチを有する。

別の態様は、基板をパターニングする装置を含み、この装置は、1つ以上のプロセスチャンバと、1つ以上のプロセスチャンバおよび関連する流量制御ハードウェアへの1つ以上のガス流入口と、低周波無線周波数(LFRF)発生器と、高周波無線周波数(HFRF)発生器と、少なくとも1つのプロセッサおよびメモリを有するコントローラとを備え、少なくとも1つのプロセッサおよびメモリは、互いに通信可能に接続され、少なくとも1つのプロセッサは、流量制御ハードウェア、LFRF発生器、および、HFRF発生器と少なくとも動作可能に接続され、メモリは、流量制御ハードウェア、HFRF発生器、および、LFRF発生器を少なくとも制御するように少なくとも1つのプロセッサを制御するためのコンピュータ実行可能な命令を記憶して:マスクを形成するスペーサを含む基板を1つ以上のプロセスチャンバに搬送し、各スペーサは、90°±5°の角度でスペーサの上面に交わる側壁を備え、スペーサは、ギャップ充填材をコア材のギャップに共形に堆積させることによって形成され、充填材およびコア材を平坦化して平面を形成し、コア材を選択的に除去し、スペーサをマスクとして用いてターゲット層をエッチングする。

これらの態様および他の態様は、図面を参照して以下にさらに説明される。

以下の説明では、本実施形態の十分な理解を提供するために多くの特定の詳細が記載される。開示の実施形態は、これらの特定の詳細の一部または全てなしで実行されてよい。他の例では、周知のプロセス動作は、開示の実施形態を不必要に曖昧にしないように詳細には説明されていない。開示の実施形態は特定の実施形態と併せて説明されるが、開示の実施形態を限定する意図はないことが理解されるだろう。

多くの半導体製造プロセスでは、パターニング方法が用いられる。特に、マルチパターニングは、その光学的限界を超えてリソグラフィ技術を拡充するのに用いられてきた。ダブルパターニングおよびクアッドパターニングは、その光学的限界を超えてリソグラフィ技術を拡充するのに用いられる例示的な技術であり、ダブルパターニングは、今や業界内で約80nm未満のピッチに広く用いられている。現在のダブルパターニング技術は、トレンチをパターニングするために2つのマスキングステップを伴う側壁スペーサを用いることが多い。ポジ型およびネガ型両方のダブルパターニングプロセスにおけるダブルパターニング(特に、ラインパターニング)の方法は、スペーサおよびマスクの使用を含んでいる。スペーサは、パターニングされたコア上にプラズマ強化原子層堆積(PEALD)によって堆積され、より小さいピッチのパターンを形成するのに用いられてよい。装置が小型化し、ピッチが縮小するにつれて、スペーサの傾き、ラインの曲がり、および、パターニングされたスペーサの潰れなどの問題が起こり、その結果、装置の故障を引き起こす可能性がある。特に、コア層が焼成されて除去されるときに、スペーサの傾きによるピッチウォーキングが見られる。

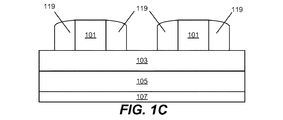

図1A〜図1Jは、ピッチウォーキングをもたらすクアッドパターニングスキームにおける基板の例示的な概略図である。図1Aは、第2のコア103、ターゲット層105、および、下層107の上に、リソグラフィによって画定されたまたはパターニングされた第1のコア101を有する基板を示す。当業者は、本明細書で説明される半導体処理に適した多層スタックには、エッチング停止層、キャップ層、および、他の下層などの他の層も含まれてよいことを理解するだろう。

パターニングされた第1のコア101は、フォトレジストであってよい、または、非晶質炭素材もしくは非晶質シリコン材を含んでよい。パターニングされた第1のコア101は、プラズマ強化化学気相堆積(PECVD)などの任意の適した堆積技術によって第2のコア103の上に堆積されてよく、堆積技術には、堆積チャンバ内で炭化水素前駆体を含む堆積ガスからプラズマを生成することが含まれてよい。炭化水素前駆体は、化学式CxHy(xは2から10の間の整数、yは2から24の間の整数)によって定義されてよい。例には、メタン(CH4)、アセチレン(C2H2)、エチレン(C2H4)、プロピレン(C3H6)、ブタン(C4H10)、シクロヘキサン(C6H12)、ベンゼン(C6H6)、および、トルエン(C7H8)が含まれる。高周波(HF)電力および低周波(LF)電力を含む二重無線周波数(RF)プラズマ源が用いられてよい。

第2のコア103の下にはターゲット層105がある。ターゲット層105は、最終的にパターニングされる層であってよい。ターゲット層105は、半導体、誘電体、または、他の層であってよく、例えば、シリコン(Si)、酸化シリコン(SiO2)、窒化シリコン(SiN)、または、窒化チタン(TiN)からなってよい。ターゲット層105は、原子層堆積(ALD)、PEALD、化学気相堆積(CVD)、または、他の適した堆積技術によって堆積されてよい。

図1Bでは、第1の共形膜109がパターニングされた第1のコア101の上に堆積されている。第1の共形膜109は、いくつかの実施形態では、ALDまたはPEALDによって堆積されてよい。第1の共形膜109は異方的にエッチングされて、図1Cに示されるような第1のスペーサ119が形成される。第1のスペーサ119は、酸化シリコン(SiO2)もしくは酸化チタン(TiO2)などの酸化物、または、窒化シリコン(SiN)などの窒化物であってよい。第1のスペーサ119のパターンは、次の層をパターニングするのに用いられる。本明細書で用いられる「スペーサ」との単語は、コア材に隣接するマスク材を意味することが理解されるだろう。

図1Dでは、パターニングされた第1のコア101が選択的にエッチングされて、基板上に自立する第1のスペーサ119が残される。本明細書で用いられる選択的除去または選択的エッチングは、ある材料の別の材料に対する選択的なエッチングとして定義される。例えば、図1Dでは、パターニングされた第1のコアは、第1のスペーサ119に対して選択的にエッチングされる。いくつかの実施形態では、第1の材料が第2の材料に選択的にエッチングされる場合、一定期間に第1の材料が第2の材料より多くエッチングされるように、第1の材料のエッチング速度は第2の材料のエッチング速度より速いことが理解されるだろう。

第1のスペーサ119のパターンは、約50nmのピッチを有してよい。臨界寸法がかなり大きいため、これより大きい臨界寸法ではピッチウォーキングのリスクはほとんどない。

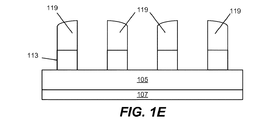

図1Eでは、第2のコア層103がパターニングされたスペーサ119をマスクとして用いてエッチングされることで、パターンが第2のコア層103に転写されて、パターニングされた第2のコア113が形成される。パターニングされた第2のコア113は、第2のコア層103をエッチングするのに適しているがパターニングされたスペーサ119をエッチングするのには適さない化学物質を用いてエッチングされてよい。パターニングされた第2のコア113は、非晶質炭素層、非晶質シリコン層、または、ポリメタクリル酸メチル、ポリメチルグルタルイミド(PMGI)、もしくは、フェノールホルムアルデヒド樹脂などのフォトレジストであってよい。

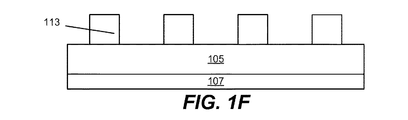

図1Fでは、第1のスペーサ119が選択的に除去されて、パターニングされた第2のコア113が残される。一例では、スペーサは、CHF3および/またはCF4を流入させることによって除去されてよい。

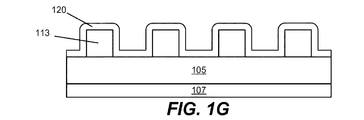

図1Gでは、第2の共形膜120が、パターニングされた第2のコア113の上に堆積される。第2の共形膜120は、ALDまたはPEALDによって堆積された誘電材料であってよい。例えば、いくつかの実施形態では、第2の共形膜120は酸化シリコンであってよい。いくつかの実施形態では、第2の共形膜120は、第1の共形膜109と同様または類似の組成物を有してよい。

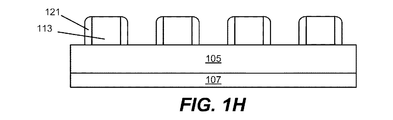

図1Hでは、第2の共形膜120が異方的にエッチングされて、パターニングされた第2のコア113の側面に位置する第2のスペーサ121が形成される。図1Iでは、パターニングされた第2のコア113が選択的に除去されて、自立する第2のスペーサ125が残される。ここで、パターニングされた第2のコア113は、図1Dにおいてパターニングされた第1のコア101のエッチングと同様または類似の化学物質を用いてエッチングされてよい。

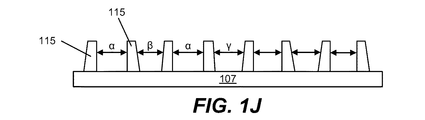

図1Jでは、第2のスペーサ125のパターンがターゲット層105に転写されるときは、パターニングされたターゲット層115は、全て異なる値であってよい様々な臨界寸法α、β、および、γを有する。スペーサ125の非対称性は、ターゲット層を形成するための不均一なエッチングを招き、それによってピッチウォーキングが起こる。非対称なスペーサ125を用いるターゲット層105のエッチングによって、ターゲット層の斜めエッチングを引き起こすエッチング種のイオン角度分布が起こる。パターニングされたコア材の除去中のドライエッチング条件がシャドーイング効果をもたらすため、このプロセスは部分的にピッチウォーキングを引き起こす。

現在のパターニングスキームおよび技術は、ピッチウォーキングなしでターゲット層をエッチングするのに用いられうるスペーサを形成するには不十分である。本明細書で提供されるのは、原子層堆積ギャップ充填技術を用いて対称的なスペーサを形成するための方法および装置である。対称的なスペーサは、ターゲット層をエッチングするためのスペーサのマスクとしての使用がピッチウォーキングをもたらさないように、および/または、ピッチウォーキングを低減させるように、改善された上部形状を提供する。対称的なスペーサは、約90°±5°の点で交わる鋭利な角部を含む。開示の実施形態は、スペーサの上面に垂直な、または、実質的に垂直な側壁を有するスペーサを形成する。実質的に垂直とは、本明細書では、90°±5°の角度を有するとして定義される。方法は、ALDを用いてパターニングされた基板の上のフィーチャを充填、または、部分的に充填して基板上に被りを形成することと、基板を平坦化することと、ギャップ充填材およびコア材を除去して対称的なスペーサを形成することとを含む。対称的とは、本明細書では、コア材が除去されて自立するスペーサが残った後に、スペーサの両側に実質的に同じ形状を有することとして定義される。例えば、対称的なスペーサは、スペーサの上部水平面から90°または約90°に配向されたスペーサの垂直面を備える平坦な上部形状を有してよい。

図2は、特定の開示の実施形態に従って実施される方法の動作を表すプロセスフロー図である。図2の1つ以上の動作は、様々な実施形態で実施されてよい。いくつかの実施形態では、図2で説明される動作の1つのみが実施される。例えば、いくつかの実施形態では、マスクとして形成された対称的なスペーサを備える基板が提供され、マスクを用いてターゲット層をエッチングするために動作215のみが実施される。別の例では、基板が提供され、コア材を除去して対称的なスペーサをマスクとして形成するために動作211のみが用いられる。これらの実施形態および他の実施形態は、図2に関連して説明されたいずれか1つ以上の動作を用いて実施されてよいことが理解されるだろう。

動作201では、パターニングされたコア材およびターゲット層を有する基板が提供される。パターニングされたコア材は、フォトレジストであってよい、または、非晶質炭素材もしくは非晶質シリコン材からなってよい。いくつかの実施形態では、コア材は透明であってよい。コア材は、プラズマ強化化学気相堆積(PECVD)などの堆積技術によって堆積され、その堆積技術には、基板を収容する堆積チャンバ内で炭化水素前駆体を含む堆積ガスからプラズマを生成することが含まれてよい。炭化水素前駆体は、化学式CaHb(aは2から10の間の整数、bは2から24の間の整数)によって定義されてよい。例には、メタン(CH4)、アセチレン(C2H2)、エチレン(C2H4)、プロピレン(C3H6)、ブタン(C4H10)、シクロヘキサン(C6H12)、ベンゼン(C6H6)、および、トルエン(C7H8)が含まれる。高周波(HF)電力および低周波(LF)電力を含む二重周波数(RF)プラズマ源が用いられてよい。コア材は、パターニングされる前にターゲット層の上に堆積される。ターゲット層は、最終的にパターニングされる層であってよい。ターゲット層は、半導体、誘電体、または、他の層であってよく、例えば、シリコン(Si)、酸化シリコン(SiO2)、窒化シリコン(SiN)、または、窒化チタン(TiN)からなってよい。ターゲット層は、原子層堆積(ALD)、プラズマ強化ALD(PEALD)、化学気相堆積(CVD)、または、別の適した堆積技術によって堆積されてよい。

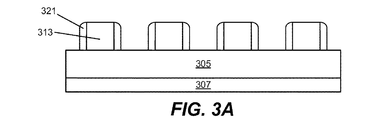

動作203では、スペーサ材を含む共形膜がパターニングされたコア材の上に堆積され、共形膜が異方的にエッチングされてパターニングされたコア材の側壁に水平なスペーサが形成される。図3Aは、下層307、ターゲット層305、パターニングされたコア材313、および、スペーサ321を含む例示的な基板の概略図を提供する。これは、図2の動作203実施後の基板上のパターンの例である。動作203は、図3J〜図3Oに関連して以下に説明されるように、いくつかの実施形態では任意であってよい。

図2に戻ると、動作206では、ギャップ充填材がALDによって基板の上に堆積される。ギャップ充填材は、シリコン含有材であってよい、または、いくつかの実施形態では、チタン含有材であってよい。例には、酸化シリコン、窒化シリコン、炭化シリコン、および、酸化チタンが含まれる。ギャップ充填材は、約50℃から約400℃の間、または、約100℃未満(例えば、約50℃)などの任意の適した温度で堆積されてよい。ギャップ充填材は、ビス(ジエチルアミノ)シラン、ビス(tert−ブチルアミノ)シラン、および、ジイソプロピルアミノシランなどの任意の適した前駆体を用いて堆積されてよい。

ギャップ充填材は、ALDを用いて共形に堆積される。ALDは、一連の自己制限反応を用いて材料の薄膜を堆積させる技術である。ALDプロセスは、表面媒介堆積反応を用いて膜を周期的に一層ベースで堆積させる。例として、ALDサイクルは次の動作を含んでよい:(i)前駆体の供給/吸着、(ii)チャンバからの前駆体のパージ、(iii)第2の反応剤の供給および任意でのプラズマ点火、および(iv)チャンバからの副生成物のパージ。基板の表面に膜を形成するための第2の反応剤と吸着した前駆体との間の反応は、膜の組成物および性質(不均一性、圧力、ウェットエッチング速度、ドライエッチング速度、電気特性(例えば、耐圧および漏洩電流)など)に影響を与える。

ALDプロセスの一例では、表面活性部位群を含む基板表面は、基板を収容するチャンバに供給された量でシリコン含有前駆体などの第1の前駆体の気相分布に曝露される。この第1の前駆体の化学吸着種、および/または、物理吸着分子を含む第1の前駆体の分子は、基板表面上に吸着する。本明細書に説明されるように化合物が基板表面に吸着するときは、吸着層は、化合物だけでなく化合物の派生物も含んでよいことを理解されたい。例えば、シリコン含有前駆体の吸着層は、シリコン含有前駆体だけでなくシリコン含有前駆体の派生物も含んでよい。第1の前駆体の投与後、チャンバは次に、主に吸着種または吸着種のみが残るように、気相に残る第1の前駆体のほとんどまたは全てを除去するように排気される。いくつかの実施形態では、チャンバは完全に排気されなくてもよい。例えば、リアクタは、気相中の第1の前駆体の分圧が反応を緩和するのに十分なほど低くなるように排気されてよい。酸素含有ガスなどの第2の反応剤は、これらの分子のいくつかが表面に吸着した第1の前駆体と反応するようにチャンバに導入される。いくつかのプロセスでは、第2の反応剤は、吸着した第1の前駆体と直ちに反応する。他の実施形態では、第2の反応剤は、プラズマなどの活性源が時間的に印加された後にのみ反応する。チャンバは次に、第2の反応剤の未結合分子を除去するために再び排気されてよい。上述のように、いくつかの実施形態では、チャンバは完全には排気されなくてもよい。膜厚を増やすために追加のALDサイクルが用いられてよい。

いくつかの実施形態では、ALD法はプラズマ活性化を含む。本明細書で説明されるように、本明細書で説明されるALD法および装置は、共形膜堆積(CFD)であってよく、2011年4月11日出願の「PLASMA ACTIVATED CONFORMAL FILM DEPOSITION」と題した米国特許出願第13/084,399号(現在は米国特許第8,728,956号)、および、2011年4月11日出願の「SILICON NITRIDE FILMS AND METHODS」と題した米国特許出願第13/084,305号に一般に記載されており、それらの全てが参照により本明細書に援用される。

酸化シリコンギャップ充填材の堆積のために、基板は以下のようにサイクルに曝露されてよい。シリコン含有前駆体は、シリコン含有前駆体を基板表面に吸着させるために導入される。開示の実施形態に従う使用に適したシリコン含有前駆体は、ポリシラン誘導体(H3Si−(SiH2)n−SiH3)(n≧0)を含む。シラン誘導体の例は、シラン(SiH4)、ジシラン(Si2H6)、ならびに、メチルシラン、エチルシラン、イソプロピルシラン、t−ブチルシラン、ジメチルシラン、ジエチルシラン、ジ−t−ブチルシラン、アリルシラン、sec‐ブチルシラン、テキシルシラン、イソアミルシラン、t−ブチルジシラン、ジ−t−ブチルジシランなどのオルガノシランである。

ハロシランは、少なくとも1つのハロゲン基を含み、水素および/または炭素基を含んでも含まなくてもよい。ハロシランの例は、ヨードシラン、ブロモシラン、クロロシラン、および、フルオロシランである。プラズマが生成されるときに、ハロシラン、特にフルオロシランは、シリコン材をエッチングできる反応性ハロゲン化合物種を形成してよいが、いくつかの実施形態では、プラズマが生成されるときにハロシランはチャンバに導入されなくてもよいため、ハロシランからの反応性ハロゲン化合物種の形成は低減されてよい。特定のクロロシランは、テトラクロロシラン、トリクロロシラン、ジクロロシラン、モノクロロシラン、クロロアリルシラン、クロロメチルシラン、ジクロロメチルシラン、クロロジメチルシラン、エチルクロロシラン、t−ブチルクロロシラン、ジ−t−ブチルクロロシラン、クロロイソプロピルシラン、クロロ−sec−ブチルシラン、t−ブチルジメチルクロロシラン、テキシルジメチルクロロシランなどである。

アミノシランは、ケイ素原子に結合した少なくとも1つの窒素原子を含むが、水素、酸素、ハロゲン、および、炭素を含んでもよい。アミノシランの例には、モノ−、ジ−、トリ−、および、テトラ−アミノシラン(それぞれ、H3Si(NH2)、H2Si(NH2)2、HSi(NH2)3、Si(NH2)4)だけでなく、置換モノ、置換ジ−、置換トリ−、および、置換テトラ−アミノシラン(例えば、t−ブチルアミノシラン、メチルアミノシラン、tert−ブチルシランアミン、ビス(tert−ブチルアミノ)シラン(SiH2(NHC(CH3)3)2(BTBAS)、tert−ブチルシリルカルバメート、SiH(CH3)−(N(CH3)2)2、SiHCl−(N(CH3)2)2、(Si(CH3)2NH)3など)が含まれる。アミノシランのさらなる例は、トリシリルアミン(N(SiH3))である。

処理されている基板を収容するチャンバは、基板表面に吸着されない前駆体を除去するためにパージされてよい。チャンバのパージは、他の動作で用いられるキャリアガスもしくは異なるガスであるパージガスまたはスイープガスを流入させることを含んでよい。例示的なパージガスには、アルゴン、窒素、水素、および、ヘリウムが含まれる。様々な実施形態では、パージガスは不活性ガスである。例示的な不活性ガスには、アルゴン、窒素、および、ヘリウムが含まれる。いくつかの実施形態では、パージはチャンバの排気を含む。いくつかの実施形態では、パージは、プロセスチャンバを排気するための1つ以上の排気サブフェーズを含んでよい。その代わりに、いくつかの実施形態では、パージが省略されてよいことが理解されるだろう。

シリコン含有前駆体の吸着層を備える基板は酸化体に曝露され、酸化プラズマを用いて吸着前駆体を酸化シリコンに変換する条件下でプラズマが点火される。例示的な酸化体には、酸素ガス、水、二酸化炭素、亜酸化窒素、および、それらの組み合わせが含まれる。様々な実施形態では、基板は、プラズマの点火中に、同時に酸化体および不活性ガスに曝露される。例えば、一実施形態では、酸素およびアルゴンの混合物は、プラズマの点火中に基板に導入される。次に、酸化シリコンを形成するための反応から発生する未反応の酸化体および/または副生成物を除去するために、チャンバは再びパージされてよい。これらの投与、パージ、変換、パージの動作は複数サイクル繰り返されて、基板の上に共形に一層ずつギャップ充填材を堆積させてよい。

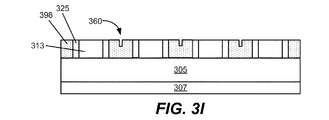

図3Bは、基板の上に共形に堆積されているギャップ充填材395の例示的な概略図を示す。より多くのサイクルが実施されるにつれて、スペーサ321の間のフィーチャは充填され、図3Cに示されるように側壁に堆積した材料が交わる継ぎ目360が形成されてよい。図3Cは、パターニングされたコア材313の上面の上の被りを有するように堆積されたギャップ充填材396を含む。いくつかの実施形態では、図2の動作205におけるギャップ充填材は、フィーチャをアンダーフィルするように、または、ギャップを完全に充填するには不十分な期間において堆積するように、多数のサイクルで実施されてよい。アンダーフィルについては、図3Hおよび図3Iに関連して以下にさらに説明される。いくつかの実施形態では、完全充填およびアンダーフィル両方の実施形態を示す図3J〜図3Oに関連して以下に説明されるように、動作205で堆積されたギャップ充填材は、対称的なスペーサを形成するための材料として用いられる。

図2に戻ると、動作207では、ギャップ充填材は、平坦面を形成するためにエッチバックされる。エッチバックまたは平坦化は、ウェットエッチングプロセス、ドライエッチングプロセス、または、化学機械平坦化(CMP)を用いて実施されてよい。様々な実施形態では、動作207は、ギャップ充填材、スペーサ材、および、パターニングされたコアにわたって平坦面を形成するように平坦化することをさらに含む。図3Dには、エッチングされたギャップ充填材399、スペーサ材325、および、コア材313が平坦化されている例が提供されている。エッチングされたギャップ充填材399に残った小さい継ぎ目360があってよいことに注意されたい。

別の実施形態では、基板上のフィーチャがアンダーフィルされるようにギャップ充填材を堆積させるために、図2の動作205が実施される。例えば、ALDの堆積サイクルは、側壁に堆積した膜の間の空間距離が約5nmから約50nmの間になるように、多数のサイクルで繰り返されてよい。アンダーフィルの実施形態を示す図3Bに続いてよい例が図3Hに示されている。微小ギャップ380がフィーチャの中央に残る図3Hに示されるように基板がアンダーフィルされるまで、ギャップ充填材は、図3BではALDによって基板の上に共形に堆積される。堆積されるギャップ充填材の量は、側壁に十分な厚さを少なくとも提供するように堆積された量に依存する。いくつかの実施形態では、フィーチャは、約x[nm]未満のフィーチャ開口部を有し、ギャップ充填材は、ギャップ充填材が約0.4×x[nm]から約0.5×x[nm]の間の厚さに堆積するのに十分な期間において堆積される。いくつかの実施形態では、フィーチャは、約5nm未満のフィーチャ開口部を有し、ギャップ充填材は、ギャップ充填材が約2nmから約2.5nmの間の厚さに堆積するのに十分な期間において堆積される。例えば、ギャップ充填材は、約50nmのフィーチャ開口部を有するフィーチャに対して約20nmから約30nmの間の厚さに堆積されてよい。フィーチャを完全に充填して図3Bに示されるような継ぎ目を形成する代わりに、基板は動作207でエッチバックされて、それでもなお微小ギャップ360を有するエッチングされたギャップ充填材398を形成してよい。しかし、ギャップ充填材は、対称的なスペーサ325を形成するために用いられる犠牲層であるため、いくつかの実施形態では、ギャップ充填材は、動作205において完全に充填されるのではなくアンダーフィルされてよい。

図2に戻ると、動作209では、ギャップ充填材は選択的に除去されて、基板上にパターニングされたコア材およびスペーサ材が残される。図3Eに例が提供されている。図のように、ギャップ充填材は除去されて、ターゲット層305の上にコア材313および側壁スペーサ325が生成される。ギャップ充填材が対称的なスペーサを形成するのに用いられる実施形態では、この動作は実施されないことに注意されたい。

図2に戻ると、動作211では、コア材が選択的にエッチングされて、対称的なスペーサがマスクとして形成される。図3Fに例が提供されている。図のように、スペーサ325は、図1Iに示されるスペーサ125と比べて対称的であり傾いていない。

図2に戻ると、動作215では、対称的なスペーサをマスクとして用いてターゲット層がエッチングされる。図3Gに例が提供されており、エッチングされたターゲット層315は、図1Jで生じた様々な臨界寸法と比べて一貫した臨界寸法αを有する。

図3J〜図3Rは、特定の開示の実施形態を実施するための別の実施形態を提供する。例えば、図3J〜図3Oは、図2の動作203が実施されないように基板の上にギャップ充填材を直接堆積させることによって、ギャップ充填材を用いて自立する対称的なスペーサを形成することを含む。図3P〜図3Rは、アンダーフィルを含む別の実施形態の例を示し、そこでは、図2の動作203が実施されず、ターゲット層をパターニングするためにアンダーフィルされたギャップ充填材がスペーサとして用いられる。これらの実施形態は、以下にさらに詳細に説明される。

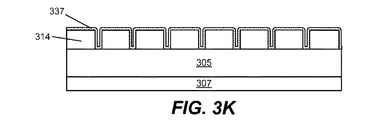

図3Jでは、下層307、ターゲット層305、および、パターニングされたコア314を含む基板が提供される。図3Kでは、ギャップ充填材337が原子層堆積を用いて基板の上に共形に堆積される。例示的な用いられてよいギャップ充填材および用いられてよい堆積技術は、図2の動作205に関連して上述されている。図3Lでは、パターニングされたコア314の間のフィーチャまたはギャップが完全に充填されることによって、側壁の堆積材が交わる継ぎ目361の形成をもたらすまで、ギャップ充填材338が堆積されている。いくつかの実施形態では、図3P〜図3Rに関連して以下に説明されるように、フィーチャの中間に微小ギャップを残すようにアンダーフィルが実施されてよい。

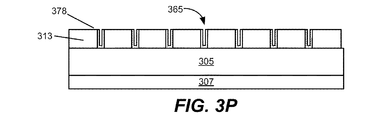

図3Mでは、基板が平坦化されて、たった今平坦化されたコア317およびギャップ充填材339を含む平坦面が生成される。ギャップ充填材339には継ぎ目361がまだ存在してよいことに注意されたい。図2に関連して上述されたように、平坦化は動作207に従って実施されてよい。図3Nでは、平坦化されたコア材317が選択的にエッチングされて、各々がいまだ継ぎ目361を有してよい自立する対称的なスペーサ339が残される。コア材は、図2の動作211に関連して上述したように除去されてよい。図3Oでは、対称的なスペーサがマスクとして用いられてターゲット層305をエッチングし、次にマスクが除去されて、パターニングされたターゲット層335が生成される。ターゲット層をエッチングするのに用いられたエッチング種のイオン角度分布は、ターゲット層を効果的にエッチングして一貫した臨界寸法βを有するパターンを生成できることに注意されたい。

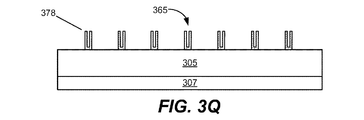

図3P〜図3Rは、ギャップ充填材を対称的なスペーサマスクとして用いながらフィーチャをアンダーフィルするための別の実施形態を提供する。例えば、図3Kの基板は複数サイクルの原子層堆積が施されてフィーチャを部分的に充填することによって、フィーチャ内にギャップ365が残されてよい。基板は図2の動作207によって平坦化されて、ギャップ充填材378のフィールド領域がコア材313のフィールド領域と面一になる平坦面を有する図3Pに示される基板が生成されてよい。図3Qでは、コア材は図2の動作211によって選択的に除去されて、各々がフィーチャのアンダーフィルでいまだギャップ365を備えてよい自立する対称的なスペーサ378が生成される。スペーサ378は、ターゲット層305をパターニングするのに用いられてよく、スペーサ378が対称的であるため、ターゲット層305をエッチングするのに用いられるエッチング種のイオン角度分布は角度エッチングを引き起こさず、そのため一貫した臨界寸法βを有するパターニングされたターゲット層345が形成される。

特定の開示の実施形態は、ギャップ充填材が約2nmから約200nmの間の臨界寸法を有する既存のフィーチャに堆積する用途に適している。開示の実施形態は、20nm未満のノードでの用途に適している。開示の実施形態は、ギャップ充填材が約20:1を超えるアスペクト比を有する既存のフィーチャに堆積するパターニングされた基板を形成するのにも適している。

装置:

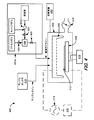

図4は、プロセスチャンバ402を有する原子層堆積(ALD)プロセスステーション400の実施形態の概略図を表す。プロセスチャンバ402は、低圧環境を維持するために用いられてよい。複数のALDプロセスステーションが、共通の低圧プロセスツール環境に含まれてよい。例えば、図5は、マルチステーション処理ツール500の実施形態を表している。いくつかの実施形態では、以下に詳細に述べられるものを含むALDプロセスステーション400の1つ以上のハードウェアパラメータが、1つ以上のコンピュータ制御装置450によってプログラムで調整されてよい。

図4は、プロセスチャンバ402を有する原子層堆積(ALD)プロセスステーション400の実施形態の概略図を表す。プロセスチャンバ402は、低圧環境を維持するために用いられてよい。複数のALDプロセスステーションが、共通の低圧プロセスツール環境に含まれてよい。例えば、図5は、マルチステーション処理ツール500の実施形態を表している。いくつかの実施形態では、以下に詳細に述べられるものを含むALDプロセスステーション400の1つ以上のハードウェアパラメータが、1つ以上のコンピュータ制御装置450によってプログラムで調整されてよい。

ALDプロセスステーション400は、プロセスガスを分配シャワーヘッド406に供給するための反応剤供給システム401aと流体連通する。反応剤供給システム401aは、シャワーヘッド406に供給するためのシリコン含有ガスまたは酸素含有ガスなどのプロセスガスを混合する、および/または、調整するための混合容器404を備える。1つ以上の混合容器吸入弁420は、混合容器404へのプロセスガスの導入を制御してよい。

例として、図4の実施形態は、混合容器404に供給される液体反応剤を蒸発させるための蒸発点403を含む。いくつかの実施形態では、蒸発点403は、加熱した蒸発器であってよい。かかる蒸発器から生成された飽和反応剤蒸気は、下流の供給配管に凝縮してよい。凝縮した反応剤への不和合ガスの曝露は、小粒子を生成する可能性がある。これらの小粒子は、配管を詰まらせ、弁動作を妨げ、基板を汚染するなどの可能性がある。これらの問題に対処するいくつかのアプローチには、残留反応剤を除去するための供給配管のパージおよび/または排気が含まれる。しかし、供給配管のパージは、プロセスステーションのサイクルタイムを増加させ、プロセスステーションのスループットを低下させる可能性がある。そのため、いくつかの実施形態では、蒸発点403の下流の供給配管がヒートトレースされてよい。いくつかの例では、混合容器404もヒートトレースされてよい。非限定的な一例では、蒸発点403の下流の配管は、混合容器404において約100℃から約150℃におよぶ昇温プロファイルを有する。

いくつかの実施形態では、液体前駆体または液体反応剤が液体注入器(図示せず)で蒸発されてよい。例えば、液体注入器は、液体反応剤のパルスを混合容器404の上流のキャリアガス流に注入してよい。一実施形態では、液体注入器は、液体をより高圧からより低圧に流すことによって反応剤を蒸発させてよい。別の例では、液体注入器は、加熱した供給配管で次に蒸発される分散微小液滴に液体を霧化してよい。小液滴は、大液滴より速く蒸発して、液体注入と完全蒸発との間の遅延を低減してよい。より急速な蒸発によって蒸発点403から下流の配管の長さが短縮されてよい。一つのシナリオでは、液体注入器は、混合容器404に直接取り付けられてよい。別のシナリオでは、液体注入器は、シャワーヘッド406に直接取り付けられてよい。

いくつかの実施形態では、蒸発およびプロセスチャンバ402への供給のための液体の質量流量を制御するために、蒸発点403の上流に液体流量コントローラ(LFC)が設けられてよい。例えば、LFCは、LFCの下流に位置する熱式質量流量計(MFM)を備えてよい。LFCのプランジャ弁は、次に、MFMと電気通信する比例積分微分(PID)コントローラによって提供される帰還制御信号に応答して調整されてよい。しかし、帰還制御を用いて液体流を安定させるのに1秒以上かかる可能性がある。これにより、液体反応剤を投与する時間が拡大する可能性がある。そのため、いくつかの実施形態では、LFCは、帰還制御モードと直接制御モードとの間で動的に切り替えられてよい。いくつかの実施形態では、これはLFCの認識チューブおよびPIDコントローラを停止させることによって実施されてよい。

シャワーヘッド406は、プロセスガスを基板412に向かって分配する。図4に示される実施形態では、基板412は、シャワーヘッド406の下に位置し、台座408の上に載っていることが示されている。シャワーヘッド406は、任意の適した形状であってよく、プロセスガスを基板412に分配するための任意の適した数および配置の給排気口を有してよい。

いくつかの実施形態では、台座408は上昇または下降されて、基板412を基板412とシャワーヘッド406との間の容積に曝露してよい。いくつかの実施形態では、台座408は、ヒータ410によって温度制御されてよい。台座408は、様々な開示の実施形態を実施するための動作中は、約25℃から約650℃の間などの任意の適した温度に設定されてよい。いくつかの実施形態では、台座の高さは、適したコンピュータ制御装置450によってプログラム調整されてよいことが理解されるだろう。

別のシナリオでは、台座408の高さの調整によって、特定の開示の実施形態で実施されるプラズマ活性化サイクルの際にプラズマ密度が変化してよい。プロセスフェーズの最後に、台座408は別の基板搬送フェーズ中に下降されて、基板412が台座408から除去されてよい。

いくつかの実施形態では、シャワーヘッド406の位置は、基板412とシャワーヘッド406との間の容積が変化するように台座408に対して調整されてよい。さらに、台座408および/またはシャワーヘッド406の垂直位置は、本開示の範囲内における任意の適した機構によって変更されてよいことが理解されるだろう。いくつかの実施形態では、台座408は、基板412の向きを回転させるための回転軸を備えてよい。いくつかの実施形態では、1つ以上のこれらの例示的な調整は、1つ以上の適したコンピュータ制御装置450によってプログラムで実施されてよい。コンピュータ制御装置450は、図5のコントローラ550に関連して以下に説明されるあらゆる特徴を含んでよい。

プラズマが上述のように用いられてよいいくつかの実施形態では、シャワーヘッド406および台座408は、プラズマを出力するための無線周波数(RF)電源414および整合ネットワーク416と電気的に連通する。いくつかの実施形態では、プラズマエネルギは、プロセスステーション圧力、ガス濃度、RF源電力、RF源周波数、および、プラズマ電力パルスタイミングのうちの1つ以上を制御することによって制御されてよい。例えば、RF電源414および整合ネットワーク416は任意の適した電力で操作されて、所望の組成のラジカル種を有するプラズマが形成されてよい。同様に、RF電源414は、任意の適した周波数のRF電力を提供してよい。いくつかの実施形態では、RF電源414は、互いに独立する高周波RF電源および低周波RF電源を制御するように構成されてよい。例示的な低周波RF周波数は、0kHzから500kHzの間の周波数を含んでよいが、それに限定されない。例示的な高周波RF周波数は、1.8MHzから2.45GHzの間、または約13.56MHzを超える、または27MHzを超える、または40MHzを超える、または60MHzを超える周波数を含んでよいが、それに限定されない。表面反応のためのプラズマエネルギを提供するために、任意の適したパラメータが別々にまたは連続して調整されてよいことが理解されるだろう。

いくつかの実施形態では、プラズマは、1つ以上のプラズマモニタによってin−situで監視されてよい。1つのシナリオでは、プラズマ電力は、1つ以上の電圧・電流センサ(例えば、VIプローブ)によって監視されてよい。別のシナリオでは、プラズマ密度および/またはプロセスガス濃度は、1つ以上の発光分光分析センサ(OES)によって測定されてよい。いくつかの実施形態では、1つ以上のプラズマパラメータは、かかるin−situのプラズマモニタからの測定値に基づいてプログラム調整されてよい。例えば、OESセンサは、プラズマ電力のプログラム制御を提供するためのフィードバックループで用いられてよい。いくつかの実施形態では、プラズマおよび他のプロセス特性を監視するのに他のモニタが用いられてよいことが理解されるだろう。かかるモニタは、赤外線(IR)モニタ、音響モニタ、および、圧力変換器を含んでよいが、それらに限定されない。

いくつかの実施形態では、コントローラ450のための命令は、入出力制御(IOC)シークエンシング命令によって提供されてよい。一例では、プロセスフェーズの条件を設定するための命令は、プロセスレシピの対応するレシピフェーズに含まれてよい。いくつかの場合では、プロセスフェーズのための全ての命令がそのプロセスフェーズと同時に実行されるように、プロセスレシピフェーズは順次配置されてよい。いくつかの実施形態では、1つ以上のリアクタパラメータを設定するための命令は、レシピフェーズに含まれてよい。例えば、第1のレシピフェーズは、不活性ガスおよび/または反応ガス(例えば、シリコン含有前駆体などの第1の前駆体)の流量を設定するための命令と、キャリアガス(アルゴンなど)の流量を設定するための命令と、第1のレシピフェーズのための時間遅延命令とを含んでよい。続く第2のレシピフェーズは、不活性ガスおよび/または反応ガスの流量を調節または停止するための命令と、キャリアガスまたはパージガスの流量を調節するための命令と、第2のレシピフェーズのための時間遅延命令とを含んでよい。第3のレシピフェーズは、酸素などの第2の反応ガスの流量を調節するための命令と、キャリアガスまたはパージガスの流量を調節するための命令と、高プラズマエネルギを有するプラズマを点火するための命令と、第3のレシピフェーズのための時間遅延命令とを含んでよい。続く第4のレシピフェーズは、不活性ガスおよび/または反応ガスの流量を調節または停止するための命令と、キャリアガスまたはパージガスの流量を調節するための命令と、第3のレシピフェーズのための時間遅延命令とを含んでよい。かかるレシピは、対称的なスペーサを順次形成するためにパターニングされた基板の上にギャップ充填材を堆積させるのに用いられてよい。いくつかのレシピは、パターニングされた基板をギャップ充填材と共にアンダーフィルするのに用いられてよい。これらのレシピフェーズは、本開示の範囲における任意の適した方法で、さらに細分化および/または反復されてよいことが理解されるだろう。

また、いくつかの実施形態では、プロセスステーション400の圧力制御がバタフライ弁418によって提供されてよい。図4の実施形態に示されるように、バタフライ弁418は、下流の真空ポンプ(図示せず)によって提供される真空を抑える。しかし、いくつかの実施形態では、プロセスステーション400の圧力制御は、プロセスステーション400に導入された1つ以上のガスの流量を変更することによって調整されてもよい。

上述のように、1つ以上のプロセスステーションがマルチステーション処理ツールに含まれてよい。図5は、搬入ロードロック502および搬出ロードロック504を備えるマルチステーション処理ツール500の実施形態の概略図を示し、搬入ロードロック502および搬出ロードロック504のいずれかまたは両方は、遠隔プラズマ源(図示せず)を備えてよい。ロボット506は、大気圧で、容器508を通って搬入されたカセットから大気口510を通ってウエハを搬入ロードロック502に移動するように構成される。ウエハ(図示せず)は搬入ロードロック502の台座512の上にロボット506によって設置され、大気口510が閉じられ、搬入ロードロック502がポンプダウンされる。搬入ロードロック502が遠隔プラズマ源を備える場合、ウエハは、処理チャンバ514に導入される前に、搬入ロードロック502で遠隔プラズマ処理に曝されてよい。また、ウエハは、例えば、水分および吸着したガスを除去するために、搬入ロードロック502で加熱されてもよい。次に、処理チャンバ514へのチャンバ搬送口516が開かれ、別のロボット(図示せず)が処理用のリアクタ内に示される第1のステーションの台座上のリアクタ内にウエハを設置する。図5に表された実施形態はロードロックを含むが、いくつかの実施形態では、ウエハがプロセスステーションに直接搬入されてよいことが理解されるだろう。

図の処理チャンバ514は、図5に示された実施形態では1から4まで番号が振られた4つのプロセスステーションを備える。各ステーションは、加熱された台座(ステーション1の518)およびガスライン吸入口を有する。いくつかの実施形態では、各プロセスステーションが異なるまたは複数の目的を有してよいことが理解されるだろう。例えば、いくつかの実施形態では、プロセスステーションは、ALDプロセスモードとプラズマ強化ALDプロセスモードとの間で切り替え可能であってよい。いくつかの実施形態では、堆積前駆体への曝露、ならびに、第2の反応剤およびプラズマへの曝露は、同じステーションで実施される。さらにまたはあるいは、いくつかの実施形態では、処理チャンバ514は、1つ以上の左右一対のALDおよびプラズマ強化ALDプロセスステーションを備えてよい。図の処理チャンバ514は4つのステーションを備えるが、本開示による処理チャンバは、任意の適した数のステーションを有してよいことが理解されるだろう。例えば、いくつかの実施形態では、処理チャンバは5つ以上のステーションを備えてよく、他の実施形態では、処理チャンバは3つ以下のステーションを有してよい。

図5は、処理チャンバ514内でウエハを搬送するためのウエハハンドリングシステム590の実施形態を表している。いくつかの実施形態では、ウエハハンドリングシステム590は、様々なプロセスステーションの間、および/または、プロセスステーションとロードロックとの間でウエハを搬送してよい。任意の適したウエハハンドリングシステムが採用されてよいことが理解されるだろう。非限定的な例には、ウエハ回転コンベアおよびウエハハンドリングロボットが含まれる。図5は、プロセスツール500のプロセス条件およびハードウェア状態を制御するために採用されたシステムコントローラ550の実施形態も表している。システムコントローラ550は、1つ以上のメモリ装置556、1つ以上の大容量記憶装置554、および、1つ以上のプロセッサ552を備えてよい。プロセッサ552は、CPUまたはコンピュータ、アナログおよび/またはデジタルの入出力接続部、ステッパモータコントローラ基板などを備えてよい。

いくつかの実施形態では、システムコントローラ550は、プロセスツール500の全ての動作を制御する。システムコントローラ550は、大容量記憶装置554に記憶され、記憶装置556に読み込まれ、プロセッサ552で実行されるシステム制御ソフトウェア558を実行する。あるいは、制御ロジックがコントローラ550でハードコード化されてよい。特定用途向け集積回路、プログラマブルロジックデバイス(例えば、フィールドプログラマブルゲートアレイ、すなわちFPGA)などがこれらの目的で用いられてよい。以下の説明では、「ソフトウェア」または「コード」が用いられるところはどこでも、その位置には機能的に同等のハードコード化されたロジックが用いられてよい。システム制御ソフトウェア558は、タイミング、ガスの混合、ガス流量、チャンバ圧および/またはステーション圧、チャンバ温度および/またはステーション温度、ウエハ温度、ターゲット電力レベル、RF電力レベル、基板台座、チャック位置および/またはサセプタ位置、ならびに、プロセスツール500によって実施される特定のプロセスの他のパラメータを制御するための命令を含んでよい。システム制御ソフトウェア558は、任意の適した方法で構成されてよい。例えば、様々なプロセスツール部品のサブルーチンまたは制御対象は、様々なプロセスツールのプロセスを実行するのに用いられるプロセスツール部品の動作を制御するように書き込まれてよい。システム制御ソフトウェア558は、任意の適したコンピュータ可読プログラミング言語でコード化されてよい。

いくつかの実施形態では、システム制御ソフトウェア558は、上述の様々なパラメータを制御するための入出力制御(IOC)シークエンシング命令を含んでよい。いくつかの実施形態では、システムコントローラ550と関連付けられた大容量記憶装置554および/または記憶装置556に記憶された他のコンピュータソフトウェアおよび/またはプログラムが採用されてよい。この目的のためのプログラムまたはプログラムの区分の例は、基板位置決めプログラム、プロセスガス制御プログラム、圧力制御プログラム、ヒータ制御プログラム、および、プラズマ制御プログラムを含む。

基板位置決めプログラムは、基板を台座518の上に搬入するのに用いられ、基板とプロセスツール500の他の部品との間の間隔を制御するのに用いられるプロセスツール部品のためのプログラムコードを含んでよい。

プロセスガス制御プログラムは、ガス組成(例えば、本明細書に記載されるシリコン含有ガス、酸素含有ガス、および、パージガス)および流量を制御するためのコード、ならびに、プロセスステーション内の圧力を安定させるために必要に応じて堆積前にガスを1つ以上のプロセスステーションに流入させるためのコードを含んでよい。圧力制御プログラムは、例えば、プロセスステーションの排気システム内の絞り弁、プロセスステーションへのガス流入などを調整することによって、プロセスステーション内の圧力を制御するためのコードを含んでよい。

ヒータ制御プログラムは、基板を加熱するのに用いられる加熱装置への電流を制御するためのコードを含んでよい。あるいは、ヒータ制御プログラムは、基板への伝熱ガス(ヘリウムなど)の供給を制御してよい。

プラズマ制御プログラムは、本明細書の実施形態に従って1つ以上のプロセスステーションの加工電極に印加されるRF電力レベルを設定するためのコードを含んでよい。

圧力制御プログラムは、本明細書の実施形態に従って反応チャンバ内の圧力を維持するためのコードを含んでよい。