CN108183071B - 采用ald填隙间隔物掩模的自对准多重图案化处理流程 - Google Patents

采用ald填隙间隔物掩模的自对准多重图案化处理流程 Download PDFInfo

- Publication number

- CN108183071B CN108183071B CN201711112653.9A CN201711112653A CN108183071B CN 108183071 B CN108183071 B CN 108183071B CN 201711112653 A CN201711112653 A CN 201711112653A CN 108183071 B CN108183071 B CN 108183071B

- Authority

- CN

- China

- Prior art keywords

- gap

- substrate

- core material

- spacers

- fill material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 183

- 125000006850 spacer group Chemical group 0.000 title claims abstract description 157

- 238000000059 patterning Methods 0.000 title claims abstract description 35

- 238000011049 filling Methods 0.000 title claims description 16

- 230000008569 process Effects 0.000 title abstract description 106

- 239000000463 material Substances 0.000 claims abstract description 170

- 239000000758 substrate Substances 0.000 claims abstract description 150

- 239000011162 core material Substances 0.000 claims abstract description 130

- 238000000151 deposition Methods 0.000 claims abstract description 66

- 238000000231 atomic layer deposition Methods 0.000 claims abstract description 51

- 238000005530 etching Methods 0.000 claims abstract description 36

- 238000012545 processing Methods 0.000 claims description 72

- 239000002243 precursor Substances 0.000 claims description 37

- 230000008021 deposition Effects 0.000 claims description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 21

- 229910052710 silicon Inorganic materials 0.000 claims description 21

- 239000010703 silicon Substances 0.000 claims description 20

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 16

- 229910052799 carbon Inorganic materials 0.000 claims description 16

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 13

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 12

- 230000001590 oxidative effect Effects 0.000 claims description 8

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 7

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 6

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 6

- 229910010271 silicon carbide Inorganic materials 0.000 claims description 6

- 239000000126 substance Substances 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 77

- 239000007789 gas Substances 0.000 description 64

- 235000012431 wafers Nutrition 0.000 description 53

- 239000000376 reactant Substances 0.000 description 23

- 230000001276 controlling effect Effects 0.000 description 18

- 239000007788 liquid Substances 0.000 description 18

- 238000010926 purge Methods 0.000 description 18

- 239000004065 semiconductor Substances 0.000 description 18

- 239000011295 pitch Substances 0.000 description 17

- 238000004519 manufacturing process Methods 0.000 description 16

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 description 13

- 238000012546 transfer Methods 0.000 description 13

- 238000010586 diagram Methods 0.000 description 11

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 230000008016 vaporization Effects 0.000 description 10

- 238000002156 mixing Methods 0.000 description 9

- 238000009834 vaporization Methods 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 8

- 150000002500 ions Chemical class 0.000 description 8

- 229910052760 oxygen Inorganic materials 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical compound C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 6

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 6

- 239000012159 carrier gas Substances 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 238000009826 distribution Methods 0.000 description 6

- 238000009616 inductively coupled plasma Methods 0.000 description 6

- 239000011261 inert gas Substances 0.000 description 6

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 6

- 229920002120 photoresistant polymer Polymers 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 5

- -1 diethyl aminosilane (bisdiethyl aminosilane) Chemical compound 0.000 description 5

- FZHAPNGMFPVSLP-UHFFFAOYSA-N silanamine Chemical compound [SiH3]N FZHAPNGMFPVSLP-UHFFFAOYSA-N 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 239000004215 Carbon black (E152) Substances 0.000 description 4

- 238000004140 cleaning Methods 0.000 description 4

- 229930195733 hydrocarbon Natural products 0.000 description 4

- 150000002430 hydrocarbons Chemical class 0.000 description 4

- 239000007800 oxidant agent Substances 0.000 description 4

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 4

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000001636 atomic emission spectroscopy Methods 0.000 description 3

- 239000006227 byproduct Substances 0.000 description 3

- KOPOQZFJUQMUML-UHFFFAOYSA-N chlorosilane Chemical class Cl[SiH3] KOPOQZFJUQMUML-UHFFFAOYSA-N 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 239000012792 core layer Substances 0.000 description 3

- 239000012530 fluid Substances 0.000 description 3

- 238000009472 formulation Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 238000011065 in-situ storage Methods 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 3

- 239000002210 silicon-based material Substances 0.000 description 3

- 238000011144 upstream manufacturing Methods 0.000 description 3

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 239000005046 Chlorosilane Substances 0.000 description 2

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 2

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 2

- 239000005977 Ethylene Substances 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 2

- 229910003481 amorphous carbon Inorganic materials 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000001273 butane Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- FIRQYUPQXNPTKO-UHFFFAOYSA-N ctk0i2755 Chemical class N[SiH2]N FIRQYUPQXNPTKO-UHFFFAOYSA-N 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 239000012636 effector Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005672 electromagnetic field Effects 0.000 description 2

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 150000004820 halides Chemical class 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- IJDNQMDRQITEOD-UHFFFAOYSA-N n-butane Chemical compound CCCC IJDNQMDRQITEOD-UHFFFAOYSA-N 0.000 description 2

- OFBQJSOFQDEBGM-UHFFFAOYSA-N n-pentane Natural products CCCCC OFBQJSOFQDEBGM-UHFFFAOYSA-N 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000000678 plasma activation Methods 0.000 description 2

- 238000011112 process operation Methods 0.000 description 2

- QQONPFPTGQHPMA-UHFFFAOYSA-N propylene Natural products CC=C QQONPFPTGQHPMA-UHFFFAOYSA-N 0.000 description 2

- 125000004805 propylene group Chemical group [H]C([H])([H])C([H])([*:1])C([H])([H])[*:2] 0.000 description 2

- 150000003254 radicals Chemical class 0.000 description 2

- 238000012163 sequencing technique Methods 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- MAYUMUDTQDNZBD-UHFFFAOYSA-N 2-chloroethylsilane Chemical compound [SiH3]CCCl MAYUMUDTQDNZBD-UHFFFAOYSA-N 0.000 description 1

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 1

- VUGMARFZKDASCX-UHFFFAOYSA-N 2-methyl-N-silylpropan-2-amine Chemical compound CC(C)(C)N[SiH3] VUGMARFZKDASCX-UHFFFAOYSA-N 0.000 description 1

- MNTMWHBQGOKGDD-UHFFFAOYSA-N 3-methylbutylsilane Chemical compound CC(C)CC[SiH3] MNTMWHBQGOKGDD-UHFFFAOYSA-N 0.000 description 1

- DKCRDQKHMMPWPG-UHFFFAOYSA-N 3-methylpiperidine-2,6-dione Chemical compound CC1CCC(=O)NC1=O DKCRDQKHMMPWPG-UHFFFAOYSA-N 0.000 description 1

- DLLBFAKYMTYRBD-UHFFFAOYSA-N CCCC(C)(C)[Si] Chemical compound CCCC(C)(C)[Si] DLLBFAKYMTYRBD-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000003848 UV Light-Curing Methods 0.000 description 1

- 238000001994 activation Methods 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000002194 amorphous carbon material Substances 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- VQPFDLRNOCQMSN-UHFFFAOYSA-N bromosilane Chemical compound Br[SiH3] VQPFDLRNOCQMSN-UHFFFAOYSA-N 0.000 description 1

- AUOLYXZHVVMFPD-UHFFFAOYSA-N butan-2-yl(chloro)silane Chemical compound CCC(C)[SiH2]Cl AUOLYXZHVVMFPD-UHFFFAOYSA-N 0.000 description 1

- VBLDUBUUQYXSCG-UHFFFAOYSA-N butan-2-ylsilane Chemical compound CCC(C)[SiH3] VBLDUBUUQYXSCG-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- CRIVIYPBVUGWSC-UHFFFAOYSA-N chloro(propan-2-yl)silane Chemical compound CC(C)[SiH2]Cl CRIVIYPBVUGWSC-UHFFFAOYSA-N 0.000 description 1

- KAADXUXXXANQKW-UHFFFAOYSA-N chloro-dimethyl-(2-methylpentan-2-yl)silane Chemical compound CCCC(C)(C)[Si](C)(C)Cl KAADXUXXXANQKW-UHFFFAOYSA-N 0.000 description 1

- YGHUUVGIRWMJGE-UHFFFAOYSA-N chlorodimethylsilane Chemical compound C[SiH](C)Cl YGHUUVGIRWMJGE-UHFFFAOYSA-N 0.000 description 1

- AZFVLHQDIIJLJG-UHFFFAOYSA-N chloromethylsilane Chemical compound [SiH3]CCl AZFVLHQDIIJLJG-UHFFFAOYSA-N 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000003750 conditioning effect Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000001723 curing Methods 0.000 description 1

- UWGIJJRGSGDBFJ-UHFFFAOYSA-N dichloromethylsilane Chemical compound [SiH3]C(Cl)Cl UWGIJJRGSGDBFJ-UHFFFAOYSA-N 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- UCXUKTLCVSGCNR-UHFFFAOYSA-N diethylsilane Chemical compound CC[SiH2]CC UCXUKTLCVSGCNR-UHFFFAOYSA-N 0.000 description 1

- UBHZUDXTHNMNLD-UHFFFAOYSA-N dimethylsilane Chemical compound C[SiH2]C UBHZUDXTHNMNLD-UHFFFAOYSA-N 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- PRWJWJFNTJLFKK-UHFFFAOYSA-N ditert-butyl(chloro)silicon Chemical compound CC(C)(C)[Si](Cl)C(C)(C)C PRWJWJFNTJLFKK-UHFFFAOYSA-N 0.000 description 1

- LFLMSLJSSVNEJH-UHFFFAOYSA-N ditert-butyl(silyl)silane Chemical compound CC(C)(C)[SiH]([SiH3])C(C)(C)C LFLMSLJSSVNEJH-UHFFFAOYSA-N 0.000 description 1

- JTGAUXSVQKWNHO-UHFFFAOYSA-N ditert-butylsilicon Chemical compound CC(C)(C)[Si]C(C)(C)C JTGAUXSVQKWNHO-UHFFFAOYSA-N 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- KCWYOFZQRFCIIE-UHFFFAOYSA-N ethylsilane Chemical compound CC[SiH3] KCWYOFZQRFCIIE-UHFFFAOYSA-N 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 238000000671 immersion lithography Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- IDIOJRGTRFRIJL-UHFFFAOYSA-N iodosilane Chemical compound I[SiH3] IDIOJRGTRFRIJL-UHFFFAOYSA-N 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000012705 liquid precursor Substances 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000001404 mediated effect Effects 0.000 description 1

- IFVRUKGTKXWWQF-UHFFFAOYSA-N methylaminosilicon Chemical compound CN[Si] IFVRUKGTKXWWQF-UHFFFAOYSA-N 0.000 description 1

- UIUXUFNYAYAMOE-UHFFFAOYSA-N methylsilane Chemical compound [SiH3]C UIUXUFNYAYAMOE-UHFFFAOYSA-N 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- VYIRVGYSUZPNLF-UHFFFAOYSA-N n-(tert-butylamino)silyl-2-methylpropan-2-amine Chemical compound CC(C)(C)N[SiH2]NC(C)(C)C VYIRVGYSUZPNLF-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 150000001282 organosilanes Chemical class 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 1

- 229920000548 poly(silane) polymer Polymers 0.000 description 1

- 239000004926 polymethyl methacrylate Substances 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- DNAJDTIOMGISDS-UHFFFAOYSA-N prop-2-enylsilane Chemical compound [SiH3]CC=C DNAJDTIOMGISDS-UHFFFAOYSA-N 0.000 description 1

- YYVGYULIMDRZMJ-UHFFFAOYSA-N propan-2-ylsilane Chemical compound CC(C)[SiH3] YYVGYULIMDRZMJ-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000284 resting effect Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 238000006557 surface reaction Methods 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- IPGXXWZOPBFRIZ-UHFFFAOYSA-N tert-butyl(silyl)silane Chemical compound CC(C)(C)[SiH2][SiH3] IPGXXWZOPBFRIZ-UHFFFAOYSA-N 0.000 description 1

- BCNZYOJHNLTNEZ-UHFFFAOYSA-N tert-butyldimethylsilyl chloride Chemical compound CC(C)(C)[Si](C)(C)Cl BCNZYOJHNLTNEZ-UHFFFAOYSA-N 0.000 description 1

- KNSVRQSOPKYFJN-UHFFFAOYSA-N tert-butylsilicon Chemical compound CC(C)(C)[Si] KNSVRQSOPKYFJN-UHFFFAOYSA-N 0.000 description 1

- QIMILRIEUVPAMG-UHFFFAOYSA-N tert-butylsilyl carbamate Chemical compound C(N)(O[SiH2]C(C)(C)C)=O QIMILRIEUVPAMG-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- ZDHXKXAHOVTTAH-UHFFFAOYSA-N trichlorosilane Chemical compound Cl[SiH](Cl)Cl ZDHXKXAHOVTTAH-UHFFFAOYSA-N 0.000 description 1

- 239000005052 trichlorosilane Substances 0.000 description 1

- VOSJXMPCFODQAR-UHFFFAOYSA-N trisilylamine group Chemical group [SiH3]N([SiH3])[SiH3] VOSJXMPCFODQAR-UHFFFAOYSA-N 0.000 description 1

- 239000006200 vaporizer Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910001868 water Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0337—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3081—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their composition, e.g. multilayer masks, materials

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/042—Coating on selected surface areas, e.g. using masks using masks

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

- C23C16/45523—Pulsed gas flow or change of composition over time

- C23C16/45525—Atomic layer deposition [ALD]

- C23C16/45527—Atomic layer deposition [ALD] characterized by the ALD cycle, e.g. different flows or temperatures during half-reactions, unusual pulsing sequence, use of precursor mixtures or auxiliary reactants or activations

- C23C16/45536—Use of plasma, radiation or electromagnetic fields

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/0228—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

- H01L21/0273—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers characterised by the treatment of photoresist layers

- H01L21/0274—Photolithographic processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0332—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their composition, e.g. multilayer masks, materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3085—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by their behaviour during the process, e.g. soluble masks, redeposited masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3086—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/32—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02167—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon carbide not containing oxygen, e.g. SiC, SiC:H or silicon carbonitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/0217—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02172—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides

- H01L21/02175—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal

- H01L21/02186—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing at least one metal element, e.g. metal oxides, metal nitrides, metal oxynitrides or metal carbides characterised by the metal the material containing titanium, e.g. TiO2

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Organic Chemistry (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Inorganic Chemistry (AREA)

- Plasma & Fusion (AREA)

- Electromagnetism (AREA)

- Chemical Vapour Deposition (AREA)

- Formation Of Insulating Films (AREA)

- Drying Of Semiconductors (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

本发明涉及一种采用ALD填隙间隔物掩模的自对准多重图案化处理流程。本文描述了一种形成用于自对准多重图案化工艺的对称间隔物的方法和装置。方法包括通过原子层沉积在包括核心材料和目标层的图案化衬底上沉积填隙材料、平坦化衬底以及蚀刻核心材料以形成对称的间隔物。填隙材料可沉积持续时间不足以完全填充特征,使得特征被欠填充。

Description

技术领域

本发明涉及半导体领域,更具体地涉及一种采用ALD填隙间隔物掩模

的自对准多重图案化处理流程。

背景技术

先进集成电路的制造通常涉及半导体大批量制造中的小特征的图案化。多重图案化技术可以基于诸如193nm浸没式光刻之类的光刻技术来实现特征尺寸缩放。自对准双重图案化是多重图案化技术的一个例子。

发明内容

本文提供了处理衬底诸如半导体衬底的方法。一个方面涉及处理衬底的方法,所述方法包括:提供具有被图案化以形成间隙的核心材料和目标层的衬底;将填隙材料保形地沉积在核心材料上,使得填隙材料沉积在衬底上的间隙中;平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;和选择性蚀刻核心材料以形成用作掩模来蚀刻目标层的对称形状的间隔物。

在各种实施方式中,通过原子层沉积来沉积填隙材料。在一些实施方式中,填隙材料通过原子层沉积沉积持续不足以完全填充间隙的持续时间。

在一些实施方式中,间隙具有小于约x nm的开口,并且填隙材料被沉积持续足以将填隙材料沉积到介于约0.4×x nm和约0.5×x nm之间的厚度的持续时间。在一些实施方式中,x是50。在一些实施方式中,x小于50。

在一些实施方式中,填隙材料是氧化硅、氮化硅、碳化硅和氧化钛中的任何一种。

在一些实施方式中,掩模中对称形状的间隔物之间的关键尺寸小于约50nm。对称形状的间隔物可用于多重图案化技术。在一些实施方式中,沉积填隙材料并平坦化衬底减少距变(pitch walking)。在各种实施方式中,对称形状的间隔物包括填隙材料。

该方法还可以包括在沉积填隙材料之前在衬底上沉积另一个保形膜并定向蚀刻另一个保形膜以在核心材料的侧壁上形成侧壁间隔物。在各种实施方式中,选择性蚀刻衬底以形成对称形状的间隔物包括去除对侧壁间隔物有选择性的核心材料和填隙材料。选择性地蚀刻衬底以形成对称形状的间隔物可包括去除对填隙材料有选择性的核心材料。

在各种实施方式中,核心材料包括碳。核心材料可以是旋涂碳、类金刚石碳和/或填隙可灰化硬掩模中的任何一种。

在各种实施方式中,沉积填隙材料包括将衬底暴露于含硅前体和氧化等离子体的交替脉冲。

另一方面涉及一种方法,该方法包括:提供包括形成掩模的间隔物的衬底,每个间隔物包括与间隔物的顶表面垂直的侧壁,通过在核心材料的间隙中保形地沉积填隙材料形成间隔物,平坦化填隙材料和核心材料以形成平坦表面,并选择性地去除核心材料;以及使用间隔物作为掩模来蚀刻目标层。在各种实施方式中,掩模具有小于约50nm的间距。

在各种实施方式中,通过原子层沉积来沉积填隙材料。在一些实施方式中,填隙材料通过原子层沉积沉积持续不足以完全填充间隙的持续时间。

在一些实施方式中,填隙材料选自由氧化硅、氮化硅、碳化硅和氧化钛组成的组。

对称形状的间隔物可以用于多重图案化技术。在一些实施方式中,沉积填隙材料并平坦化衬底减少距变。在各种实施方式中,对称形状的间隔物包括填隙材料。

在各种实施方式中,核心材料包括碳。核心材料可以是旋涂碳、类金刚石碳和/或填隙可灰化硬掩模中的任何一种。

在各种实施方式中,沉积填隙材料包括将衬底暴露于含硅前体和氧化等离子体的交替脉冲。

另一个方面涉及一种方法,其包括:提供包括形成掩模的间隔物的衬底,每个间隔物包括以90°±5°的角度与间隔物的顶表面相交的侧壁,通过将填隙材料保形地沉积在核心材料的间隙中形成间隔物,将填隙材料和核心材料平坦化以形成平坦表面,并选择性地去除核心材料;以及使用间隔物作为掩模来蚀刻目标层。

在各种实施方式中,通过原子层沉积来沉积填隙材料。在一些实施方式中,填隙材料通过原子层沉积来沉积持续不足以完全填充间隙的持续时间。

在一些实施例中,填隙材料是氧化硅、氮化硅、碳化硅和氧化钛中的任何一种。

对称形状的间隔物可以用于多重图案化技术。在一些实施方式中,沉积填隙材料并平坦化衬底减少了距变。在各种实施方式中,对称形状的间隔物包括填隙材料。

在各种实施方式中,核心材料包括碳。核心材料可以是旋涂碳,类金刚石碳和/或填隙可灰化硬掩模中的任何一种。

在各种实施方式中,沉积填隙材料包括将衬底暴露于含硅前体和氧化等离子体的交替脉冲。

另一个方面涉及用于图案化衬底的装置,所述装置包括:一个或多个处理室;进入到一个或多个处理室的一个或多个进气口和相关的流量控制硬件;低频射频(LFRF)发生器;高频射频(HFRF)发生器;以及具有至少一个处理器和存储器的控制器,由此所述至少一个处理器和所述存储器彼此通信地连接,所述至少一个处理器至少可操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:引入填隙材料前体以保形地在包括目标层的衬底的所述核心材料上沉积填隙材料,所述核心材料被图案化以形成间隙,使得填隙材料沉积在所述衬底上的所述间隙中;平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;并选择性地蚀刻核心材料以形成用作掩模来蚀刻目标层的对称形状的间隔物。

另一方面涉及用于图案化衬底的装置,所述装置包括:一个或多个处理室;进入到一个或多个处理室的一个或多个进气口和相关的流量控制硬件;低频射频(LFRF)发生器;高频射频(HFRF)发生器;以及具有至少一个处理器和存储器的控制器,由此所述至少一个处理器和所述存储器彼此通信地连接,所述至少一个处理器至少可操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:将衬底转移到所述一个或多个处理室中,所述衬底包括形成掩模的间隔物,每个间隔物包括垂直于间隔物的顶表面的侧壁,间隔物通过在核心材料的间隙中保形地沉积填隙材料而形成;平坦化所述填隙材料和所述核心材料以形成平坦表面,并且选择性地移除所述核心材料;并用间隔物作为掩模来蚀刻目标层。在各种实施方式中,掩模具有小于约50nm的间距。

另一个方面涉及用于图案化衬底的装置,所述装置包括:一个或多个处理室;进入到一个或多个处理室的一个或多个进气口和相关的流量控制硬件;低频射频(LFRF)发生器;高频射频(HFRF)发生器;以及具有至少一个处理器和存储器的控制器,由此所述至少一个处理器和所述存储器彼此通信地连接,所述至少一个处理器至少可操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:将衬底转移到所述一个或多个处理室中,所述衬底包括形成掩模的间隔物,每个间隔物包括以90°±5°的角度与间隔物的顶表面相交的侧壁,间隔物通过在核心材料的间隙中保形地沉积填隙材料形成,平坦化填隙材料和核心材料以形成平坦表面,并且选择性地移除核心材料;并用间隔物作为掩模来蚀刻目标层。

下面参照附图进一步描述这些和其他方面。本发明的一些方面可具体描述如下:

1.一种处理衬底的方法,所述方法包括:

提供具有被图案化以形成间隙的核心材料和目标层的衬底;

将填隙材料保形地沉积在所述核心材料上,使得所述填隙材料沉积在所述衬底上的所述间隙中;

平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;以及

选择性地蚀刻所述核心材料以形成用作掩模的对称形状的间隔物以蚀刻所述目标层。

2.根据条款1所述的方法,其中所述填隙材料通过原子层沉积来沉积。

3.根据条款1所述的方法,其中所述填隙材料通过原子层沉积来沉积持续不够完全填充所述间隙的持续时间。

4.根据条款1所述的方法,其中所述填隙材料选自由氧化硅、氮化硅、碳化硅和氧化钛构成的组。

5.根据条款1所述的方法,其中所述间隙具有小于约x nm的开口,并且所述填隙材料被沉积持续足以将所述填隙材料沉积至介于约0.4×x nm与约0.5×x nm之间的厚度的持续时间。

6.根据条款5所述的方法,其中x是50。

7.根据条款5所述的方法,其中x小于50。

8.根据条款1所述的方法,其中所述对称形状的间隔物包括所述填隙材料。

9.根据条款1所述的方法,其中所述核心材料包含碳。

10.根据条款9所述的方法,其中,所述核心材料选自由旋涂碳、类金刚石碳以及填隙可灰化硬掩模构成的组。

11.根据条款1所述的方法,其中沉积所述填隙材料包括将所述衬底暴露于含硅前体和氧化等离子体的交替脉冲。

12.一种方法,其包括:

提供包括形成掩模的间隔物的衬底,每个间隔物包括垂直于所述间隔物的顶表面的侧壁,所述间隔物通过在核心材料的间隙中保形地沉积填隙材料而形成;

平坦化所述填隙材料和核心材料以形成平坦表面;

选择性地移除所述核心材料;以及

使用所述间隔物作为所述掩模来蚀刻目标层。

13.一种方法,其包括:

提供包括形成掩模的间隔物的衬底,每个间隔物包括以90°±5°的角度与间隔物的顶表面相交的侧壁,所述间隔物通过在核心材料的间隙中保形地沉积填隙材料而形成;

平坦化所述填隙材料和所述核心材料以形成平坦表面;

选择性地移除所述核心材料;以及

使用所述间隔物作为所述掩模来蚀刻目标层。

14.一种方法,其包括:

提供具有被图案化以形成间隙的核心材料和目标层的衬底;

将填隙材料保形地沉积在所述核心材料上,使得所述填隙材料沉积在所述衬底上的所述间隙中;

平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;

选择性地蚀刻所述核心材料以形成对称形状的间隔物;以及

使用所述对称形状的间隔物作为所述掩模来蚀刻所述目标层,

其中所述对称形状的间隔物具有平坦的顶部轮廓,所述对称形状的间隔物的竖直表面定向为与所述对称形状的间隔物的顶部水平表面成90°或大约90°。

15.一种方法,其包括:

提供具有被图案化以形成间隙的核心材料和目标层的衬底;

将填隙材料保形地沉积在所述核心材料上,使得所述填隙材料沉积在所述衬底上的所述间隙中;

平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面,所述填隙材料具有水平平坦的顶部轮廓;以及

选择性地蚀刻所述核心材料以形成用作掩模以蚀刻所述目标层的对称形状的间隔物。

16.一种方法,其包括:

提供具有被图案化以形成间隙的核心材料和目标层的衬底;

将填隙材料保形地沉积在所述核心材料上,使得填隙材料沉积在所述衬底上的所述间隙中;

平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;以及

选择性地蚀刻核心材料以形成用作掩模来蚀刻所述目标层的对称形状的间隔物,

其中所述对称形状的间隔物具有与所述对称形状的间隔物的顶表面基本垂直的侧壁。

17.根据条款1至16中任一项所述的方法,其中所述掩模中的对称形状的间隔物之间的关键尺寸小于约50nm。

18.根据条款1至16中任一项所述的方法,其中所述对称形状的间隔物用于多重图案化技术。

19.如条款1-16中任一项所述的方法,其还包括在沉积所述填隙材料之前,在所述衬底上沉积另一个保形膜并定向蚀刻所述保形膜以在所述核心材料的所述侧壁上形成侧壁间隔物。

20.根据条款19所述的方法,其中选择性地蚀刻所述衬底以形成所述对称形状的间隔物包括移除对所述侧壁间隔物有选择性的所述核心材料和所述填隙材料。

21.根据条款1至16中任一项所述的方法,其中选择性地蚀刻所述衬底以形成所述对称形状的间隔物包括移除对所述填隙材料有选择性的所述核心材料。

22.一种用于图案化衬底的装置,所述装置包括:

一个或多个处理室;

进入到所述一个或多个处理室的一个或多个进气口和相关的流量控制硬件;

低频射频(LFRF)发生器;

高频射频(HFRF)发生器;和

具有至少一个处理器和存储器的控制器,

其中所述至少一个处理器和所述存储器彼此通信地连接,

所述至少一个处理器至少能操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且

所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:

致使引入填隙材料前体以在包含目标层的衬底的核心材料上保形地沉积填隙材料,所述核心材料被图案化以形成间隙,使得所述填隙材料沉积在所述衬底上的所述间隙中;

致使平坦化所述衬底以形成包括所述填隙材料和所述核心材料的平坦表面;以及

致使选择性蚀刻所述核心材料,以形成用作掩模以蚀刻所述目标层的对称形状的间隔物。

23.一种用于图案化衬底的装置,所述装置包括:

一个或多个处理室;

进入到所述一个或多个处理室的一个或多个进气口和相关的流量控制硬件;

低频射频(LFRF)发生器;

高频射频(HFRF)发生器;和

具有至少一个处理器和存储器的控制器,

其中所述至少一个处理器和所述存储器彼此通信地连接,

所述至少一个处理器至少能操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且

所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:

致使衬底转移到所述一个或多个处理室中,所述衬底包括形成掩模的间隔物,每个间隔物包括垂直于所述间隔物的顶表面的侧壁,所述间隔物通过在核心材料的间隙中保形地沉积填隙材料而形成;

致使平坦化所述填隙材料和所述核心材料以形成平坦表面,

致使选择性去除所述核心材料;和

致使用所述间隔物作为掩模来蚀刻目标层。

24.一种用于图案化衬底的装置,所述装置包括:

一个或多个处理室;

进入到所述一个或多个处理室的一个或多个进气口和相关的流量控制硬件;

低频射频(LFRF)发生器;

高频射频(HFRF)发生器;和

具有至少一个处理器和存储器的控制器,

其中所述至少一个处理器和所述存储器彼此通信地连接,

所述至少一个处理器至少能操作地与所述流量控制硬件、所述LFRF发生器和所述HFRF发生器连接,并且

所述存储器存储计算机可执行指令,所述计算机可执行指令用于控制所述至少一个处理器以至少控制所述流量控制硬件、所述HFRF发生器和所述LFRF发生器以:

致使所述衬底转移到所述一个或多个处理室中,所述衬底包括形成掩模的间隔物,每个间隔物包括与所述间隔物的顶表面以90°±5°的角度相交的侧壁,所述间隔物通过保形地沉积填隙材料在核心材料的间隙中;

致使平坦化所述填隙材料和所述核心材料以形成平坦表面;

致使选择性去除所述核心材料;以及

致使用所述间隔物作为掩模来蚀刻目标层。

25.根据条款22至24中任一项所述的装置,其中所述控制器还包括用于在沉积所述填隙材料之前致使在所述衬底上沉积另一保形膜和致使定向蚀刻所述保形膜以在所述核心材料的所述侧壁上形成侧壁间隔物的指令。

附图说明

图1A-1J是四重图案化方案的示例中的衬底的示意图。

图2是描绘根据某些公开的实施方式执行的方法的操作的过程流程图。

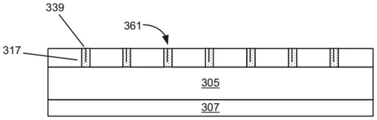

图3A-3G是根据某些公开的实施方式执行的图案化方案的示例中的衬底的示意图。

图3H和3I是根据某些公开的实施方式的用于欠填充特征的示例方案中的衬底的示意图。

图3J-3O是根据某些公开的实施方式执行的图案化方案的示例中的衬底的示意图。

图3P-3R是根据某些公开的实施方式的用于欠填充特征的示例方案中的衬底的示意图。

图4和6是用于执行某些公开的实施方式的示例性处理室的示意图。

图5和图7是用于执行某些公开的实施方式的示例性处理工具的示意图。

具体实施方式

在以下描述中,阐述了许多具体细节以提供对提出的实施方式的透彻理解。所公开的实施方式可以在没有这些具体细节中的一些或全部的情况下实践。在其他情况下,公知的处理操作没有被详细描述,以免不必要地使所公开的实施方式模糊不清。虽然所公开的实施方式将结合具体实施方式进行描述,但应该理解的是,这不意图限制所公开的实施方式。

在许多半导体制造工艺中使用图案化方法。特别是,多重图案化已经被用于将光刻技术扩展到超出其光学极限。双重图案化和四重图案化是用于将光刻技术扩展到超出其光学极限的示例性技术,并且双重图案化现在在工业中广泛用于小于约80nm的间距。目前的双重图案化技术通常使用侧壁间隔物以两个掩模化步骤(masking steps)来图案化沟槽。在正负双重图案化过程中双重图案化(特别是线图案化)的方法涉及使用间隔物和掩模。可以通过等离子体增强的原子层沉积(PEALD)在图案化的核心上沉积间隔物,并且可以用来产生更小的间距图案。随着器件收缩,间距减小,会出现诸如间隔物倾斜、线弯曲和图案化的间隔物崩坏等问题,从而可能导致器件失效。特别地,当核心层被烘烤并被去除时,由于间隔物倾斜而观察到距变(pitch walking)。

图1A-1J是导致距变的四重图案化方案中的衬底的示例性示意图。图1A示出了在第二核心103、目标层105和底层107上具有光刻限定的或图案化的第一核心101的衬底。本领域的普通技术人员将认识到,适于如本文所述的半导体加工的多层堆叠还可以包括其他层,诸如蚀刻停止层、覆盖层和其他底层。

图案化的第一核心101可以是光致抗蚀剂或可以包括无定形碳或非晶硅材料。可以通过诸如等离子体增强化学气相沉积(PECVD)之类的任何合适的沉积技术将图案化的第一核心101沉积在第二核心103之上,并且沉积技术可以涉及在沉积室中从包括烃前体的沉积气体生成等离子体。烃前体可以由式CxHy定义,其中x是2至10之间的整数,并且y是2至24之间的整数。实例包括甲烷(CH4)、乙炔(C2H2)、乙烯(C2H4)、丙烯(C3H6)、丁烷(C4H10)、环己烷(C6H12)、苯(C6H6)和甲苯(C7H8)。可以使用包括高频(HF)功率和低频(LF)功率的双射频(RF)等离子体源。

在第二核心103下是目标层105。目标层105可以是最终要被图案化的层。例如,目标层105可以是半导体、电介质或其他层,并且可以由硅(Si)、氧化硅(SiO2)、氮化硅(SiN)或氮化钛(TiN)制成。目标层105可以通过原子层沉积(ALD)、PEALD、化学气相沉积(CVD)或其他合适的沉积技术来沉积。

在图1B中,第一保形膜109沉积在图案化的第一核心101上方。在一些实施方式中,第一保形膜109可以通过ALD或PEALD沉积。如图1C所示,定向蚀刻第一保形膜109以形成第一间隔物119。第一间隔物119可以是诸如氧化硅(SiO2)或者氧化钛(TiO2)之类的氧化物,或者可以是诸如氮化硅(SiN)之类的氮化物。第一间隔物119的图案被用于图案化随后的层。应该理解的是,在此使用的术语“间隔物”是指与核心材料相邻的掩模材料。

在图1D中,图案化的第一核心101被选择性地蚀刻,在衬底上留下独立式(free-standing)的第一间隔物119。如本文所使用的选择性去除或选择性蚀刻被定义为相对于另一种材料选择性地蚀刻一种材料。例如,在图1D中,图案化的第一核心被相对于第一间隔物119选择性地蚀刻。应理解,在一些实施方式中,如果第一材料相对于第二材料被选择性地蚀刻,则第一材料的蚀刻速率比第二材料的蚀刻速率更快,使得对于给定的持续时间,相比第二材料而蚀刻更多的第一材料。

第一间隔物119的图案可以具有约50nm的间距。由于关键尺寸相当大,因此在这些较大的关键尺寸上距变的风险很小。

在图1E中,使用图案化的间隔物119作为掩模来蚀刻第二核心层103,由此将图案转移到第二核心层103以形成图案化的第二核心113。可以使用适用于蚀刻第二核心113而非图案化的间隔物119的化学物质来蚀刻图案化的第二核心113。图案化的第二核心113可以是非晶碳层、非晶硅层或光致抗蚀剂,例如聚(甲基丙烯酸甲酯)或聚(甲基戊二酰亚胺)(PMGI)或酚醛树脂。

在图1F中,选择性地移除第一间隔物119以留下图案化的第二核心113。在一个实例中,可通过流动的CHF3和/或CF4来移除间隔物。

在图1G中,第二保形膜120沉积在图案化的第二核心113上方。第二保形膜120可以是通过ALD或PEALD沉积的电介质材料。例如,在一些实施方式中,第二保形膜120可以是氧化硅。在一些实施方式中,第二保形膜120可具有与第一保形膜109相同或相似的组成。

在图1H中,第二保形膜120被定向蚀刻以形成位于图案化的第二核心113侧面的第二间隔物121。在图1I中,图案化的第二核心113被选择性地移除以留下独立的第二间隔物121。这里,图案化的第二核心113可以使用与蚀刻图1D中的图案化的第一核心101相同或类似的化学物质进行蚀刻。

在图1J中,当第二间隔物121的图案被转移到目标层105时,图案化的目标层115包括可能全部是不同值的变化的关键尺寸α、β和γ。间隔物121的不对称导致不均匀的蚀刻来形成目标层,从而导致距变。使用不对称的间隔物121蚀刻目标层105导致引起目标层的倾斜蚀刻的蚀刻物质的离子角分布(ion angular distribution)。该方法部分地导致距变,因为在移除图案化核心材料期间的干法蚀刻条件导致遮蔽效应(shadowing effect)。

当前的图案化方案和技术不足以形成可用于蚀刻目标层而没有距变的间隔物。本文提供了使用原子层沉积填隙技术形成对称间隔物的方法和装置。对称间隔物提供改进的顶部轮廓,使得使用间隔物作为掩模来蚀刻目标层不会导致距变和/或减少距变。对称间隔物包含以约90°±5°在某点处会聚的尖角。公开的实施方式形成具有垂直于或基本垂直于间隔物的顶表面的侧壁的间隔物。基本垂直在这里被定义为具有90°±5°的角度。方法涉及使用ALD在图案化衬底上填充或部分填充特征以在衬底上形成覆盖层,并平坦化衬底且去除填隙材料和核心材料以形成对称的间隔物。对称在本文中被定义为在去除核心材料以留下独立式间隔物之后在间隔物的任一侧上具有基本上相同的形状。例如,对称的间隔物可以具有平坦的顶部轮廓,其中间隔物的竖直表面与间隔物的顶部水平表面成90°或大约90°取向。

图2是描绘根据某些公开的实施方式执行的方法的操作的过程流程图。图2中的一个或多个操作可以在各种实施方式中执行。在一些实施方式中,仅执行图2中描述的操作之一。例如,在一些实施方式中,提供包括形成为掩模的对称间隔物的衬底,并且仅执行操作215以使用掩模来蚀刻目标层。在另一个例子中,提供衬底并且仅使用操作211去除核心材料并形成对称的间隔物作为掩模。应该理解的是,这些和其他实施方式可以使用关于图2描述的任何一个或多个操作来执行。

在操作201中,提供具有图案化的核心材料和目标层的衬底。图案化的核心材料可以是光致抗蚀剂或可以由非晶碳材料或非晶硅材料制成。在一些实施方式中,核心材料可以是透明的。核心材料通过诸如等离子体增强化学气相沉积(PECVD)之类的沉积技术来沉积,并且沉积技术可以涉及从包括烃前体的沉积气体在容纳衬底的沉积室中产生等离子体。烃前体可由式CaHb定义,其中a为2至10之间的整数,b为2至24之间的整数。实例包括甲烷(CH4)、乙炔(C2H2)、乙烯(C2H4)、丙烯(C3H6)、丁烷(C4H10)、环己烷(C6H12)、苯(C6H6)和甲苯(C7H8)。可以使用包括高频(HF)功率和低频(LF)功率的双射频(RF)等离子体源。核心材料在被图案化之前被沉积在目标层上。目标层可以是最终被图案化的层。例如,目标层可以是半导体、电介质或其他层,并且可以由硅(Si)、氧化硅(SiO2)、氮化硅(SiN)或氮化钛(TiN)制成。目标层可以通过原子层沉积(ALD)、等离子体增强ALD(PEALD)、化学气相沉积(CVD)或其他合适的沉积技术沉积。

在操作203中,包括间隔物材料的保形膜被沉积在图案化的核心材料上,并且定向蚀刻保形膜以在图案化的核心材料的侧壁上形成垂直间隔物。图3A提供了包括底层307、目标层305、图案化的核心材料313和间隔物321的示例性衬底的示意图。这是在执行图2的操作203之后在衬底上的图案的示例。注意,操作203可以在一些实施方式中是可选的,例如下面参考图3J-3O所述。

回到图2,在操作205中,通过ALD在衬底上方沉积填隙材料。填隙材料可以是含硅材料,或者在一些实施方式中是含钛材料。例子包括氧化硅、氮化硅、碳化硅和氧化钛。填隙材料可以在任何合适的温度下沉积,诸如在约50℃与约400℃之间沉积,或者在低于约100℃下沉积,诸如在约50℃沉积。可以使用任何合适的前体如双二乙基氨基硅烷(bisdiethylaminosilane)、双叔丁基氨基硅烷(bistertbutylaminosilane)和二异丙基氨基硅烷(diisopropylaminosilane)来沉积填隙材料。其他前体在下面描述。

填隙材料使用ALD保形沉积。ALD是一种利用顺序自限性反应沉积薄层材料的技术。ALD工艺使用表面介导的沉积反应来循环地逐层沉积膜。作为例子,ALD循环可以包括以下操作:(i)前体的输送/吸附,(ii)从室清除前体,(iii)第二反应物的输送和可选地点燃等离子体,和(iv)清除室中的副产物。在第二反应物和吸附的前体之间的用于在衬底表面上形成膜的反应影响膜组成和性能,例如不均匀性、应力、湿法蚀刻速率、干法蚀刻速率、电性质(例如,击穿电压和泄漏电流)等。

在ALD工艺的一个实例中,将包括多个表面活性位点的衬底表面暴露于以一定剂量提供给容纳衬底的室的第一前体(例如含硅前体)的气相分布。该第一前体的分子被吸附到衬底表面上,包括第一前体的化学吸附物质和/或物理吸附分子。应该理解的是,当如本文所述将化合物吸附到衬底表面上时,吸附层可以包括化合物以及化合物的衍生物。例如,含硅前体的吸附层可以包括含硅前体以及含硅前体的衍生物。在第一前体投配之后,将室抽空以除去大部分或全部保持在气相的第一前体,使得大部分或仅吸附物质保留。在一些实施方式中,室可不被完全抽空。例如,反应器可以被抽空,使得气相的第一前体的分压足够低以减轻反应。将第二反应物如含氧气体引入反应室,以使这些分子中的一些与吸附在表面上的第一前体反应。在一些方法中,第二反应物立即与吸附的第一前体反应。在其他实施方式中,第二反应物仅在临时施加诸如等离子体之类的激活源之后才起反应。然后可以将室再次抽空以去除未结合的第二反应物分子。如上所述,在一些实施方式中,室可不被完全抽空。额外的ALD循环可以用于建立膜厚度。

在一些实施方案中,ALD方法包括等离子体激活。如本文所述,本文所述的ALD方法和装置可以是保形膜沉积(CFD)方法和装置,其在2011年4月11日提交的题为“PLASMAACTIVATED CONFORMAL FILM DEPOSITION”的美国专利申请号No.13/084,399(现为美国专利号8,728,956)、以及在2011年4月11日提交的题为“SILICON NITRIDE FILMS ANDMETHODS”的美国专利申请13/084,305中被一般地描述,这些专利文件的全部内容通过引用并入本文。

对于氧化硅填隙材料的沉积,衬底可以如下暴露于周期。引入含硅前体以将含硅前体吸附到衬底表面上。适合根据所公开的实施方式使用的含硅前体包括其中n>0的聚硅烷(H3Si-(SiH2)n-SiH3)。硅烷的实例是硅烷(SiH4)、乙硅烷(Si2H6)和有机硅烷,该有机硅烷如甲基硅烷、乙基硅烷、异丙基硅烷、叔丁基硅烷、二甲基硅烷、二乙基硅烷、二叔丁基硅烷、烯丙基硅烷、仲丁基硅烷、叔己基硅烷、异戊基硅烷、叔丁基二硅烷、二叔丁基二硅烷等。

卤代硅烷包括至少一个卤素基团并且可以包括或不包括氢和/或碳基团。卤代硅烷的实例是碘代硅烷、溴代硅烷、氯代硅烷和氟代硅烷。尽管卤代硅烷特别是氟代硅烷可以在等离子体被激励时形成可以蚀刻硅材料的活性卤化物物质,但是在一些实施方式中,当等离子体被激励时,不能将卤代硅烷引入室中,因此可能会缓和从卤代硅烷形成活性卤化物物质。特定的氯硅烷为四氯硅烷、三氯硅烷、二氯硅烷、一氯硅烷、氯烯丙基硅烷、氯甲基硅烷、二氯甲基硅烷、氯二甲基硅烷、氯乙基硅烷、叔丁基氯硅烷(t-butylchlorosilane)、二叔丁基氯硅烷、氯异丙基硅烷、氯代仲丁基硅烷、叔丁基二甲基氯代硅烷、叔己基二甲基氯代硅烷等等。

氨基硅烷包括键合到硅原子上的至少一个氮原子,但也可以包含氢、氧、卤素和碳。氨基硅烷的例子是单氨基硅烷、二氨基硅烷、三氨基硅烷和四氨基硅烷(分别是H3Si(NH2)、H2Si(NH2)2、HSi(NH2)3和Si(NH2)4))以及经取代的单氨基硅烷、二氨基硅烷、三氨基硅烷和四氨基硅烷,例如,叔丁基氨基硅烷、甲基氨基硅烷、叔丁基硅烷胺、双(叔丁基氨基)硅烷(SiH2(NHC(CH3)3)2(BTBAS)、叔丁基甲硅烷基氨基甲酸酯、SiH(CH3)-(N(CH3)2)2、SiHCl-(N(CH3)2)2、(Si(CH3)2NH)3等等。氨基硅烷的另一个实例是三硅烷基胺(N(SiH3))。

容纳正被处理的衬底的室可被吹扫以去除未被吸附到衬底表面上的前体。吹扫室可以涉及使吹扫气体或清扫气体流动,吹扫气体或清扫气体可以是在其他操作中使用的载气,或者可以是不同的气体。吹扫气体的示例包括氩气、氮气、氢气和氦气。在各种实施方式中,吹扫气体是惰性气体。惰性气体的实例包括氩气、氮气和氦气。在一些实施方式中,吹扫可涉及抽空室。在一些实施方式中,吹扫可以包括用于抽空处理室的一个或多个抽空子阶段。可选地,将理解,在一些实施方式中吹扫可以被省略。

包括含硅前体的吸附层的衬底暴露于氧化剂,并且在使用氧化的等离子体将吸附的前体转化为氧化硅的条件下点燃等离子体。示例性的氧化剂包括氧气、水、二氧化碳、一氧化二氮及其组合。在各种实施方式中,当等离子体被点燃时,衬底同时暴露于氧化剂和惰性气体。例如,在一个实施方式中,当等离子体被点燃时,氧和氩的混合物被引入到衬底。然后可再次吹扫室以从用于形成氧化硅的反应中除去未反应的氧化剂和/或副产物。这些投配、吹扫、转化、吹扫操作可以在多个循环中重复以在衬底上保形地一层一层地沉积填隙材料。

图3B示出了在衬底上保形地沉积填隙材料395的示例性示意图。随着更多的循环被执行,间隔物321之间的特征被填充,并且接缝360可以形成在侧壁上的沉积材料会合处,如图3C所示。图3C包括填充材料396,所述填充材料396沉积为包括在图案化的核心材料313的顶部表面之上的覆盖层。注意,在一些实施方式中,图2的操作205中的沉积填隙材料可以执行多个循环,以便欠填充(underfill)特征或沉积持续不够完全填充间隙的时间。下面将参考图3H和3I进一步描述欠填充。在一些实施方式中,在操作205中沉积的填隙材料被用作形成对称间隔物的材料,如下面关于图3J至图3O所述,用于完全填充和欠填充的实施方式两者。

返回图2,在操作207中,填隙材料被回蚀刻以形成平坦表面。可以使用湿法蚀刻工艺、干法蚀刻工艺或化学机械平坦化(CMP)来执行回蚀刻或平坦化。在各种实施方式中,操作207进一步包括平坦化以形成跨填隙材料、间隔物材料和图案化核心之上的平坦表面。在图3D中提供了一个例子,由此经蚀刻的填隙材料399、间隔材料325和核心材料313已经被平坦化。注意,在经蚀刻的填隙材料399中可能留有小接缝360。

在替代实施方式中,执行图2的操作205以沉积填隙材料,使得欠填充衬底上的特征。例如,ALD的沉积循环可以重复多个循环,使得沉积在侧壁上的膜之间的空间中的距离在约5nm与约50nm之间。在图3H中示出了一个示例,其可以在图3B的欠填充实施方式之后进行。填隙材料通过ALD保形地沉积在图3B中的衬底上,直到如图3H所示衬底被欠填充,由此在特征的中心保留小的间隙380。要被沉积的填隙材料的量取决于为了至少在侧壁上提供足够的厚度而沉积的量。在一些实施方式中,特征具有小于约x nm的特征开口,并且填隙材料被沉积持续足以将填隙材料沉积至介于约0.4×x nm与约0.5×x nm之间的厚度的持续时间。在一些实施方式中,特征具有小于约5nm的特征开口,并且填隙材料被沉积持续足以将填隙材料沉积至介于约2nm与约2.5nm之间的厚度的持续时间。例如,对于具有大约50nm的特征开口的特征,可以将填隙材料沉积到介于约20nm和约30nm之间的厚度。代替如图3C所示完全填充特征以形成接缝,可以在操作207中回蚀衬底以形成仍然具有小的间隙380的经蚀刻的填隙材料398。然而,由于填隙材料是牺牲层以用于形成对称的间隔物325,所以在一些实施方式中操作205中的填隙材料可能是欠填充的,而不是完全填充的。

返回图2,在操作209中,选择性地移除填隙材料以在衬底上留下图案化的核心材料和间隔物材料。图3E提供了一个例子。如图所示,去除填隙材料以在目标层305上产生核心材料313和侧壁间隔物325。注意,在其中使用填隙材料形成对称间隔物的实施方式中,不执行该操作。

返回图2,在操作211中,核心材料被选择性蚀刻以形成对称的间隔物作为掩模。图3F提供了一个例子。如图所示,与图1I中所示的间隔物121相比,间隔物325是对称的并且不会倾斜。

返回图2,在操作215中,使用对称间隔物作为掩模来蚀刻目标层。图3G中提供了一个例子,与图1J中导致的变化的关键尺寸相比,蚀刻的目标层315具有一致的关键尺寸α。

图3J-3R提供了用于执行某些公开的实施方式的替代实施方式。例如,图3J-3O涉及通过将填隙材料直接沉积在衬底上来使用填隙材料形成独立式对称间隔物,使得不执行图2的操作203。图3P-3R示出了涉及欠填充的另一实施方式的示例,由此不执行图2的操作203,并且使用经欠填充的填隙材料作为间隔物来图案化目标层。下面进一步详细描述这些实施方式。

在图3J中,提供了包括底层307、目标层305和图案化核心314的衬底。在图3K中,使用原子层沉积在衬底上保形地沉积填隙材料337。上面关于图2的操作205描述了可以使用的示例性填隙材料和可以使用的沉积技术。在图3L中,填充材料338已经被沉积,直到图案化核心314之间的特征或者间隙被完全填充,从而导致在侧壁上的沉积材料会聚处形成接缝361。注意,在一些实施方式中,可以执行欠填充以便在特征的中间留下小间隙,如下面关于图3P-3R所述。

在图3M中,衬底被平坦化以产生包括现在平坦化的核心317和平坦化的填隙材料339的平坦表面。注意,接缝361仍可存在于填隙材料339中。平坦化可根据上述关于图2所述的操作207进行。在图3N中,平坦化的核心材料317被选择性地蚀刻以留下独立式的对称间隔物339,其中的每一个仍然可以包括接缝361。核心材料可以如上文关于图2所述的操作211来去除。在图3O中,对称间隔物用作掩模来蚀刻目标层305,然后去除掩模以产生图案化目标层335。注意,用于蚀刻目标材料的蚀刻物质离子角度分布可以有效地蚀刻目标层以产生具有一致关键尺寸β的图案。

图3P-3R提供了用于欠填充特征的替代实施方式,同时使用填隙材料作为对称间隔物掩模。例如,图3P中的衬底可以经历原子层沉积的多个循环以部分地填充特征,由此在特征中留下间隙365。可以根据图2的操作207平坦化衬底以产生图3P中所示的具有平坦化表面的衬底,由此填隙材料378的场区与核心材料313的场区齐平。在图3Q中,根据图2的操作211,核心材料被选择性地去除,以产生独立式对称间隔物378,根据欠填充特征,每个对称间隔物378可以仍然包括间隙365。间隔物378可以用于图案化目标层305,并且用于蚀刻目标层305的蚀刻物质的离子角分布不导致角蚀刻,因为间隔物378是对称的,从而形成具有一致的关键尺寸β的图案化的目标层345。

某些公开的实施方式适用于其中填隙材料被沉积到具有在约2nm和约200nm之间的关键尺寸的现有特征中的应用。所公开的实施方式适用于小于20nm的节点的应用。所公开的实施方式也适于形成图案化衬底,其中填隙材料被沉积到深宽比大于约20:1的现有特征中。

装置

图4描绘了具有处理室402的原子层沉积(ALD)处理站400的实施方式的示意图。处理室402可用于维持低压环境。多个ALD处理站可被包括在共同的低压处理工具环境中。例如,图5描绘了多站处理工具500的一个实施方式。在一些实施方式中,ALD处理站400的一个或多个硬件参数(包括在下面详细讨论的那些参数)可以由一个或多个计算机控制器450以编程方式进行调整。

ALD处理站400与反应物输送系统401a流体连通,以用于将工艺气体输送到分配喷头406。反应物输送系统401a包括用于混合和/或调节工艺气体(例如含硅气体或者含氧气体)以用于输送到喷头406的混合容器404。一个或多个混合容器入口阀420可控制工艺气体到混合容器404的引入。

作为示例,图4的实施方式包括汽化点403,用于汽化待供应到混合容器404的液体反应物。在一些实施方式中,汽化点403可以是加热汽化器。由这种汽化器产生的饱和反应物蒸气可能在下游输送管道中冷凝。不相容的气体暴露于冷凝的反应物可能会产生小颗粒。这些小颗粒可能堵塞管路、妨碍阀门操作、污染衬底等等。解决这些问题的一些方法涉及清扫和/或排空输送管道以去除残余反应物。但是,清扫输送管道可能会增加处理站循环时间,降低处理站的生产量。因此,在一些实施方式中,汽化点403下游的输送管道可以被热追踪。在一些示例中,混合容器404也可以被加热追踪。在一个非限制性示例中,汽化点403下游的管道在混合容器404处具有从大约100℃延伸到大约150℃的增加的温度分布。

在一些实施方式中,液体前体或液体反应物可在液体注射器(未示出)处被汽化。例如,液体注射器可将液体反应物的脉冲注入到混合容器404上游的载气流中。在一个实施方式中,液体注射器可通过使液体从较高压力闪蒸至较低压力而使反应物汽化。在另一个例子中,液体注射器可以将液体雾化成分散的微滴,随后在加热的输送管中汽化。较小的液滴会比较大的液滴蒸发得快,从而减少了液体注入和完全汽化之间的延迟。更快的蒸发可以减少汽化点403下游的管道的长度。在一种情况下,液体注射器可以直接安装到混合容器404。在另一种情况下,液体注射器可以直接安装到喷头406。

在一些实施方式中,可以提供汽化点403上游的液体流量控制器(LFC),用于控制液体的质量流量以用于汽化和递送至处理室402。例如,LFC可以包括位于LFC下游的热质量流量计(MFM)。LFC的柱塞阀然后可以响应于与MFM电通信的比例—积分—微分(PID)控制器提供的反馈控制信号进行调节。但是,使用反馈控制可能需要一秒或更长时间来稳定液体流量。这可能会延长液体反应物的投配时间。因此,在一些实施方式中,LFC可以在反馈控制模式和直接控制模式之间动态地切换。在一些实施方式中,这可以通过禁用LFC的感测管和PID控制器来执行。

喷头406将工艺气体分配到衬底412。在图4所示的实施方式中,衬底412位于喷头406下方并且示出为搁置在基座408上。喷头406可以具有任何合适的形状,并且可以具有任何合适的用于将工艺气体分配到衬底412的端口的数量和布置。

在一些实施方式中,可以升高或降低基座408以将衬底412暴露于衬底412和喷头406之间的体积。在一些实施方式中,基座408可以通过加热器410进行温度控制。基座408可以设置为在执行各种公开的实施方式的操作期间的任何合适的温度,诸如在约25℃和约650℃之间。应意识到,在一些实施方式中,基座高度可以由合适的计算机控制器450以编程方式进行调整。

在另一种情况下,调节基座408的高度可以允许在某些公开的实施方式中执行的等离子体激活周期期间改变等离子体密度。在处理阶段结束时,基座408可在另一衬底传送阶段期间降低以允许从基座408移除衬底412。

在一些实施方式中,喷头406的位置可以相对于基座408进行调节,以改变衬底412和喷头406之间的体积。此外,应理解的是,基座408和/或喷头406的垂直位置可以通过本公开范围内的任何合适的机制来改变。在一些实施方式中,基座408可以包括用于旋转衬底412的方位的旋转轴线。应理解的是,在一些实施方式中,这些示例性调整中的一个或多个可以由一个或多个合适的计算机控制器450以编程方式执行。计算机控制器450可以包括下面关于图5的控制器550描述的特征中的任一个。

在可以如上所述使用等离子体的一些实施方式中,喷头406和基座408与射频(RF)电源414和匹配网络416电连接,以为等离子体供电。在一些实施方式中,可以通过控制处理站压力、气体浓度、RF源功率、RF源频率和等离子体功率脉冲定时中的一个或多个来控制等离子体能量。例如,RF电源414和匹配网络416可以以任何合适的功率运行以形成具有期望组成的自由基物质的等离子体。类似地,RF电源414可以提供任何合适频率的RF功率。在一些实施方式中,RF电源414可以被配置为独立于彼此地控制高频和低频RF功率源。示例性的低频RF频率可以包括但不限于0kHz和500kHz之间的频率。高频RF频率的示例可以包括但不限于1.8MHz与2.45GHz之间的频率,或者大于约13.56MHz,或者大于27MHz,或者大于40MHz,或者大于60MHz。应该理解的是,可以离散地或连续地调制任何合适的参数以为表面反应提供等离子体能量。

在一些实施方式中,等离子体可以由一个或多个等离子体监控器原位监测。在一种情况下,等离子体功率可以由一个或多个电压传感器、电流传感器(例如,VI探头)来监测。在另一种情况下,可以通过一个或多个光发射光谱传感器(OES)来测量等离子体密度和/或工艺气体浓度。在一些实施方式中,一个或多个等离子体参数可以基于来自这种原位等离子体监控器的测量而被编程地调整。例如,OES传感器可以用在反馈回路中以提供对等离子体功率的编程控制。应该理解的是,在一些实施方式中,可以使用其他监控器来监控等离子体和其他处理特性。这种监控器可以包括但不限于红外(IR)监控器、声音监控器和压力传感器。

在一些实施方式中,可以经由输入/输出控制(IOC)排序指令来提供用于控制器450的指令。在一个示例中,用于设置工艺阶段的条件的指令可以被包括在工艺配方的对应配方阶段中。在某些情况下,工艺配方阶段可以被顺序排列,使得工艺阶段的所有指令与该工艺阶段同时执行。在一些实施方式中,用于设置一个或多个反应器参数的指令可以被包括在配方阶段中。例如,第一配方阶段可以包括用于设定惰性气体和/或反应物气体(例如,诸如含硅前体之类的第一前体)的流率的指令、用于设定载气的流率的指令(如氩气)和第一配方阶段的时间延迟指令。随后的第二配方阶段可包括用于调节或停止惰性气体和/或反应物气体的流率的指令以及用于调节载气或吹扫气体的流率的指令以及用于第二配方阶段的时间延迟指令。第三配方阶段可以包括用于调节诸如氧之类的第二反应物气体的流率的指令、用于调节载气或吹扫气体的流率的指令、用于点燃具有高等离子体能量的等离子体的指令以及用于第三配方阶段的时间延迟指令。随后的第四配方阶段可包括用于调节或停止惰性气体和/或反应物气体的流率的指令、以及用于调节载气或吹扫气体的流率的指令以及用于第四配方阶段的时间延迟指令。这样的配方可以用来在图案化的衬底上沉积填隙材料以随后形成对称的间隔物。一些配方可以用于用填充材料欠填充图案化的衬底。应该理解,在本公开的范围内,这些配方阶段可以以任何合适的方式被进一步细分和/或重复。

此外,在一些实施方式中,用于处理站400的压力控制可由蝶阀418提供。如图4的实施方式所示,蝶阀418对由下游真空泵(未示出)提供的真空进行节流。然而,在一些实施方式中,处理站400的压力控制也可以通过改变引入到处理站400的一种或多种气体的流率来调节。

如上所述,一个或多个处理站可被包括在多站处理工具中。图5示出了具有入站装载锁502和出站装载锁504的多工作站处理工具500的实施方式的示意图,所述入站装载锁502和出站装载锁504中的任一个或两个可以包括远程等离子体源(未示出)。在大气压力下的机械手506被配置为将晶片从通过晶舟(pod)508装载的盒子经由大气端口510移动到入站装载锁502中。在入站装载锁502中机械手506将晶片(未示出)放置在基座512上,大气端口510关闭,并且入站装载锁502被抽空。在入站装载锁502包括远程等离子体源的情况下,在被引入到处理室514中之前,可以将晶片暴露于入站装载锁502中的远程等离子体处理。此外,晶片还可以在入站装载锁502中加热,例如用于去除湿气和吸附的气体。接下来,打开到处理室514的室输送端口516,另一机械手(未示出)将晶片放入反应器中在示出的第一站的基座上以进行处理。虽然图5中描绘的实施方式包括装载锁,但是应该理解,在一些实施方式中,可以使晶片直接进入处理站。

所描绘的处理室514包括四个处理站,在图5所示的实施方式中从1到4编号。每个站具有加热的基座(针对站1以518示出)和气体管线入口。应该理解,在一些实施方式中,每个处理站可以用于不同的或多个目的。例如,在一些实施方式中,处理站可以在ALD和等离子体增强ALD处理模式之间切换。在一些实施方式中,暴露于沉积前体和暴露于第二反应物和等离子体是在相同的站中进行。另外地或替代地,在一些实施方式中,处理室514可以包括一个或多个匹配的成对的ALD和等离子体增强的ALD处理站。虽然所描绘的处理室514包括四个站,但应理解,根据本发明的处理室可具有任何合适数目的站。例如,在一些实施方式中,处理室可具有五个或更多个站,而在其他实施方式中,处理室可具有三个或更少的站。

图5描绘了用于在处理室514内传送晶片的晶片处理系统590的实施方式。在一些实施方式中,晶片处理系统590可以在各个处理站之间和/或在处理站与装载锁之间传送晶片。应理解,可以采用任何合适的晶片处理系统。非限制性示例包括晶片传送带和晶片处理机械手。图5还描绘了用于控制处理工具500的工艺条件和硬件状态的系统控制器550的实施方式。系统控制器550可以包括一个或多个存储器装置556、一个或多个大容量存储装置554以及一个或多个处理器552。处理器552可以包括CPU或计算机、模拟和/或数字输入/输出连接件、步进电机控制器板等。

在一些实施方式中,系统控制器550控制处理工具500的所有活动。系统控制器550执行存储在大容量存储装置554中、装载到存储装置556中并在处理器552上执行的系统控制软件558。或者,控制逻辑可以在控制器550中被硬编码。专用集成电路、可编程逻辑器件(例如现场可编程门阵列或FPGA)等等可以用于这些目的。在下面的讨论中,凡是使用“软件”或“编码”的地方,都可以在其中使用功能上可比较的硬编码逻辑。系统控制软件558可以包括用于控制时序、气体混合物、气体流量、室和/或站压力、室和/或站温度、晶片温度、目标功率水平、RF功率水平、衬底基座、卡盘和/或感测器位置以及由处理工具500执行的特定处理的其他参数。系统控制软件558可以以任何适当的方式来配置。例如,可以写入各种处理工具组件子例程或控制对象来控制用于执行各种处理工具处理的处理工具组件的操作。系统控制软件558可以用任何合适的计算机可读编程语言编码。

在一些实施方式中,系统控制软件558可以包括用于控制上述各种参数的输入/输出控制(IOC)排序指令。在一些实施方式中,可以采用存储在与系统控制器550相关联的大容量存储装置554和/或存储装置556上的其他计算机软件和/或程序。用于此目的的程序或程序段的例子包括衬底定位程序、工艺气体控制程序、压力控制程序、加热器控制程序和等离子体控制程序。

衬底定位程序可以包括用于处理工具部件的程序代码,其用于将衬底装载到基座518上并控制衬底与处理工具500的其他部分之间的隔离。

工艺气体控制程序可以包括用于控制气体组成(例如,如本文所述的含硅气体、含氧气体和吹扫气体)和流率的代码,并且可选地用于使气体在沉积之前流入一个或多个处理站以稳定处理站中的压力。压力控制程序可以包括用于通过调节例如处理站的排放系统中的节流阀、进入处理站的气流等来控制处理站中的压力的代码。

加热器控制程序可以包括用于控制流向用于加热衬底的加热单元的电流的代码。或者,加热器控制程序可以控制传热气体(例如氦气)向衬底的传送。

根据本文的实施方式,等离子体控制程序可以包括用于设置施加到一个或多个处理站中的处理电极的RF功率水平的代码。

根据本文的实施方式,压力控制程序可以包括用于保持反应室中的压力的代码。

在一些实施方式中,可以存在与系统控制器相关联的用户界面。用户界面可以包括显示屏、装置和/或工艺条件的图形软件显示器、以及诸如定点装置、键盘、触摸屏、麦克风等用户输入装置。

在一些实施方式中,由系统控制器550调节的参数可涉及工艺条件。非限制性实例包括工艺气体组成和流率、温度、压强、等离子体条件(例如,RF偏置功率电平)等。这些参数可以以配方的形式提供给用户,配方可以利用所述用户界面输入。

用于监控处理的信号可以由系统控制器550的模拟和/或数字输入连接件从各种处理工具传感器提供。用于控制处理的信号可以通过处理工具500的模拟和/或数字输出连接件输出。可被监控的处理工具传感器的非限制性实例包括质量流量控制器、压力传感器(例如压力计)、热电偶等等。经适当编程的反馈和控制算法可以与来自这些传感器的数据一起使用,以保持处理条件。

系统控制器550可以提供用于实现上述沉积过程的程序指令。程序指令可以控制诸如DC功率水平、RF偏置功率水平、压力、温度等各种处理参数。根据本文描述的各种实施方式,指令可以控制参数以操作膜堆叠的原位沉积。

系统控制器550通常将包括一个或多个存储器装置以及被配置为执行指令的一个或多个处理器,使得该装置将执行根据所公开的实施方式的方法。包含根据所公开的实施方式的用于控制处理操作的指令的机器可读介质可以耦合到系统控制器550。

在一些实施方案中,系统控制器550是系统的一部分,该系统的一部分可以是上述实施方式的一部分。这样的系统可以包括半导体处理装置,半导体处理装置包括一个或多个加工工具、一个或多个室、用于处理的一个或多个平台、和/或特定的处理部件(晶片基座、气体流动系统等)。这些系统可与电子器件集成,以便在半导体晶片或衬底的处理之前、期间或之后控制这些系统的操作。电子器件可以被称为“控制器”,其可以控制一个或多个系统的各种组件或子部分。根据处理要求和/或系统的类型,系统控制器550可以被编程,以控制本发明所公开的工艺中的任何一些,包括控制工艺气体的输送、温度的设置(例如,加热和/或冷却)、压力的设置、真空的设置、功率的设置、射频(RF)产生器的设置、RF匹配电路的设置、频率的设置、流率的设置、流体输送的设置、位置和操作的设置、晶片的进出工具和其他输送工具和/或连接到特定系统的或与特定系统接口的装载锁的传送。

从广义上讲,系统控制器550可以被定义为接收指令、发出指令、控制操作、使能清洁操作、使能终点测量等的具有各种集成电路、逻辑、存储器、和/或软件的电子器件。该集成电路可以包括固件形式的存储程序指令的芯片、数字信号处理器(DSP)、定义为专用集成电路(ASIC)的芯片和/或执行程序指令(例如,软件)的一个或多个微处理器或微控制器。程序指令可以是与各种单个的设置(或程序文件)形式的系统控制器550通信的指令,该设置定义在半导体晶片上或用于半导体晶片或向系统进行特定处理的操作参数。在一些实施方式中,所述操作参数可以是由工艺工程师定义的以完成晶片的一个或多个(种)层、材料、金属、氧化物、硅、硅氧化物、表面、电路和/或管芯的制造过程中的一个或多个处理步骤的配方的一部分。

在一些实施方案中,系统控制器550可以是与系统集成、耦接或者说是通过网络连接系统或它们的组合的计算机的一部分或者与该计算机耦接。例如,系统控制器550可以在“云端”或者是晶片厂(fab)主机系统的全部或一部分,它们可以允许远程访问晶片处理。计算机可以启用对系统的远程访问以监测制造操作的当前处理,检查过去的制造操作的历史,检查多个制造操作的趋势或性能标准,改变当前处理的参数,设置处理步骤以跟随当前的处理或者开始新的工艺。在一些实例中,远程计算机(例如,服务器)可以通过网络给系统提供工艺配方,网络可以包括本地网络或互联网。远程计算机可以包括允许输入或编程参数和/或设置的用户界面,这些输入或编程参数和/或设置然后从远程计算机传送到系统。在一些实例中,系统控制器550接收数据形式的指令,这些指令指明在一个或多个操作期间将要执行的每个处理步骤的参数。应当理解,这些参数可以针对将要执行的工艺类型以及工具类型,系统控制器550被配置成连接或控制该工具类型。因此,如上所述,系统控制器550可以例如通过包括一个或多个分立的控制器而分布,这些分立的控制器通过网络连接在一起并且朝着共同的目标(例如,本发明所述的工艺和控制)工作。用于这些目的的分布式控制器的实例可以是与一个或多个远程集成电路(例如,在平台水平或作为远程计算机的一部分)通信的室内的一个或多个集成电路,它们结合以控制室内工艺。

示例的系统可以包括但不限于,等离子体蚀刻室或模块、沉积室或模块、旋转冲洗室或模块、金属电镀室或模块、清洁室或模块、倒角边缘蚀刻室或模块、物理气相沉积(PVD)室或模块、化学气相沉积(CVD)室或模块、原子层沉积(ALD)室或模块、原子层蚀刻(ALE)室或模块、离子注入室或模块、轨道室或模块、以及在半导体晶片的制备和/或制造中可以关联上或使用的任何其他的半导体处理系统。

如上所述,根据工具将要执行的一个或多个工艺步骤,系统控制器550可以与一个或多个其他的工具电路或模块、其他工具组件、组合工具、其他工具界面、相邻的工具、邻接工具、位于整个工厂中的工具、主机、另一个控制器、或者在将晶片的容器往来于半导体制造工厂中的工具位置和/或装载口搬运的材料搬运中使用的工具通信。

在2011年4月11日提交的名称为“PLASMA ACTIVATED CONFORMAL FILMDEPOSITION”的美国专利申请No.13/084,399(现为美国专利8,728,956)和在2011年4月11日提交的名称为“SILICON NITRIDE FILMS AND METHODS”的美国专利申请No.13/084,305中进一步讨论和描述了用于执行本文公开的方法的适当装置,这些专利文件分别全部并入本文。

本文描述的装置/工艺可以与光刻图案化工具或工艺结合使用,例如用于制造或制备半导体器件、显示器、LED、光伏板等。典型地,但不必需地,这样的工具/工艺将被用于或者在共同的制造设施中一起进行。光刻图案化膜通常包括以下操作中的一些或全部,每种操作可用多个可能的工具实现:(1)使用旋涂或喷涂工具在工件(即衬底)上涂覆光致抗蚀剂;(2)使用热板或炉或UV固化工具固化光致抗蚀剂;(3)用诸如晶片步进机之类的工具将光致抗蚀剂暴露于可见或UV或X射线光;(4)使抗蚀剂显影以选择性地去除抗蚀剂,从而使用诸如湿台之类的工具对其进行图案化;(5)通过使用干式或等离子体辅助蚀刻工具将抗蚀剂图案转移到底层膜或工件中;和(6)使用诸如RF或微波等离子体抗蚀剂剥离器之类的工具去除抗蚀剂。

本文描述的蚀刻操作(诸如用于蚀刻对间隔物材料有选择性的核心材料)可以在任何合适的处理室中执行。在一些实施方式中,可以在感应耦合等离子体(ICP)反应器中蚀刻衬底,如下面关于图6所述。

现在描述在某些实施方式中可以适用于蚀刻操作的电感耦合等离子体(ICP)反应器。这种ICP反应器也在2013年10月12日提交的题为“IMAGE REVERSAL WITH AHM GAP FILLFOR MULTIPLE PATTERNING”的美国专利申请公开No.2014/0170853中描述,为了所有目的通过引用将其全部并入本文。尽管在此描述了ICP反应器,但是在一些实施方式中,应该理解,也可以使用电容耦合等离子体反应器。