JP2005293697A - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP2005293697A JP2005293697A JP2004106210A JP2004106210A JP2005293697A JP 2005293697 A JP2005293697 A JP 2005293697A JP 2004106210 A JP2004106210 A JP 2004106210A JP 2004106210 A JP2004106210 A JP 2004106210A JP 2005293697 A JP2005293697 A JP 2005293697A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- well

- nonvolatile semiconductor

- semiconductor memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

- G11C16/3459—Circuits or methods to verify correct programming of nonvolatile memory cells

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

Abstract

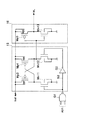

【解決手段】 高昇圧出力電圧VPPHとレギュレータ出力電圧VROの二種類の電圧を入力として、スイッチ制御信号に応じて、この二種類の電圧から1つを選択して出力する単位スイッチN(自然数)個から構成される電圧切換スイッチ回路17を備えることにより、消費電力を削減しつつ、書込み/書込みベリファイ動作の所要時間を短縮することができる高性能な不揮発性半導体記憶装置を提供する。

【選択図】 図1

Description

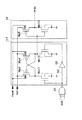

2 ロウデコーダ

3 カラムデコーダ

4 カラムゲート

5 アドレス/データバッファ

6 センスアンプ

7 高電圧発生用昇圧回路

8 低電圧発生用昇圧回路

9 レギュレータ回路

10、17 電圧切換スイッチ回路

11 制御回路

12〜14 スイッチ回路

15、117、25、27 レベルシフト回路

16、18、28 ドライバー回路

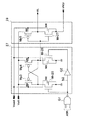

19 Nウェル電圧切換スイッチ

20 ディスチャージ回路

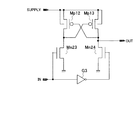

21 カレントミラー部

22 電圧検知比較部

23 検知結果増幅部

24 ディスチャージ部

26 負電圧切換スイッチ回路

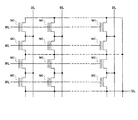

S1〜SN セクタ

MC メモリセル

BL ビット線

SL 共通ソース線

WL ワード線

XDEC1〜XDECN デコーダブロック

AD アドレス

DB データ

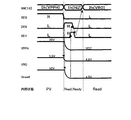

VPPL 低昇圧出力電圧

VPPH 高昇圧出力電圧

VRO レギュレータ出力電圧

Vwl1〜VwlN ワード線供給用電圧

MD モード信号

CEB チップイネーブル信号

WEB 書込みイネーブル信号

OEB 出力イネーブル信号

Mn1〜Mn6、Mn10〜Mn27 NMOSトランジスタ

VCC 電源電位

VSS 接地電位

Co 平滑容量

Dzh、Dzl ツェナーダイオード

CMP コンパレータ

Mp1〜Mp13 PMOSトランジスタ

R1〜R4 抵抗

VFB フィードバック電圧

VREF 基準電圧

NR、N1、N2 ノード

RDB モード制御信号

ADR 行アドレス

G1 NANDゲート

G2、G3 インバータゲート

NW Nウェルノード

τl1、τl、τs1、τs、τm1、τss セットアップ時間

U1X〜UMX(X=1、2、・・・、N) 単位デコーダ

Vnwell Nウェルノードの電圧

DEN ディスチャージ制御信号

RDY ディスチャージ判定信号

NW[1:0] Nウェル制御信号

Vgm ミラーゲート電位

VO 検知電圧

DENB ディスチャージ制御バー信号

VO1 NAND出力電圧

VO2 検知結果増幅出力電圧

IN 入力端子

SUPPLY 電圧供給端子

OUT 出力端子

VNG 負電圧

VNG1〜VNGN 非選択ワード線電圧

Claims (12)

- 複数のメモリセルがマトリクス状に配置され、複数のセクタに分割されるメモリセルアレイと、

前記メモリセルアレイの各前記セクタに対応するように設けられ、外部から入力してくるアドレス信号に基づいて、対応する前記セクタに含まれるメモリセルを選択する複数のロウデコード回路と、

複数種類の電圧の供給を受けており、複数の前記ロウデコード回路に対応するように設けられ、当該複数種類の電圧のうちいずれかの電圧を、対応する前記ロウデコード回路に対してそれぞれが独立に切換えて出力できる複数のスイッチとを備え、

各前記ロウデコード回路は、対応する前記スイッチから出力されてくる電圧を用いて前記メモリセルを選択することを特徴とする、不揮発性半導体記憶装置。 - 前記複数種類の電圧を、電源電圧を昇圧することにより生成する昇圧回路をさらに備える、請求項1に記載の不揮発性半導体記憶装置。

- 前記昇圧回路が生成した複数種類の電圧のうち少なくとも1種類の電圧を降圧することにより電圧値を安定化させて各前記スイッチに出力するレギュレータ回路をさらに備える、請求項2に記載の不揮発性半導体記憶装置。

- 前記アドレス信号に基づいて、各前記スイッチを切換えるためのスイッチ制御信号を生成する制御回路をさらに備え、

各前記スイッチは、前記スイッチ制御信号に基づいて、対応する前記ロウデコード回路に対して出力する電圧を切換えることを特徴とする、請求項1に記載の不揮発性半導体記憶装置。 - 前記複数種類の電圧は、少なくとも第1の電圧と当該第1の電圧よりも低い第2の電圧とを含み、

前記制御回路は、前記メモリセルにデータを書き込む際に、当該メモリセルを選択するための前記ロウデコード回路に対して前記第1の電圧を出力させ、当該ロウデコード回路以外の前記ロウデコード回路に対して前記第2の電圧を出力させるためのスイッチ制御信号を、前記アドレス信号に基づいて生成することを特徴とする、請求項4に記載の不揮発性半導体記憶装置。 - 各前記ロウデコード回路は、Nウェル中に構成された複数のPMOSトランジスタを含み、

前記昇圧回路が生成した前記複数種類の電圧のうちのいずれかの電圧を前記Nウェルに印加するためのNウェル入力端子と、

前記メモリセルにデータを書き込む前に前記Nウェル入力端子に対して電圧を印加するように前記昇圧回路を制御する昇圧制御回路とをさらに備える、請求項2に記載の不揮発性半導体記憶装置。 - 前記Nウェル入力端子には、データを書き込む前において、前記複数種類の電圧のうち最も大きい第3の電圧が印加されることを特徴とする、請求項6に記載の不揮発性半導体記憶装置。

- 前記Nウェル入力端子に出力する電圧を切換えるNウェル電圧切り替えスイッチと、

前記第3の電圧と、当該第3の電圧よりも小さな第4の電圧とを切換えて前記Nウェル電圧切り替えスイッチに出力させるスイッチ制御回路とをさらに備える、請求項7に記載の不揮発性半導体記憶装置。 - 前記スイッチ制御回路は、データを書き込む前には、前記第3の電圧を前記Nウェル入力端子に印加するように前記Nウェル電圧切り替えスイッチを制御し、データを読み出す際には、前記第4の電圧を当該Nウェル入力端子に印加するように当該Nウェル電圧切り替えスイッチを制御することを特徴とする、請求項8に記載の不揮発性半導体記憶装置。

- 前記第4の電圧を印加するように前記スイッチ制御回路が前記Nウェル電圧切り替えスイッチを切換えるときに、前記Nウェル入力端子の電圧を降下させる電圧降下回路と、

前記電圧降下回路が降下させた前記Nウェル入力端子の電圧と前記第4の電圧とを比較する比較回路とを備え、

前記スイッチ制御回路は、前記電圧降下回路が降下させた前記Nウェル入力端子の電圧と前記第4の電圧とが等しくなったと前記比較回路が判定した場合に、前記第4の電圧を前記Nウェル入力端子に印加するように前記Nウェル電圧切り替えスイッチを切換えることを特徴とする、請求項9に記載の不揮発性半導体記憶装置。 - 前記ロウデコーダは、

Nウェル中に形成された複数のPMOSトランジスタと、

前記Nウェル中に形成されたPウェル中に形成された複数のNMOSトランジスタとを含む、請求項1に記載の不揮発性半導体記憶装置。 - 前記昇圧回路が生成した複数の電圧に含まれる少なくとも1つの負電圧または接地電圧のうちのいずれかの電圧を、前記ロウデコード回路を介して前記メモリセルのコントロールゲートに印加するための負電圧入力端子と、

前記メモリセルに設けられる浮遊ゲートから電子を引き抜く際に、前記負電圧入力端子に対して負電圧を印加するように前記昇圧回路を制御する昇圧制御回路とをさらに備える、請求項11に記載の不揮発性半導体記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004106210A JP4426361B2 (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置 |

| US11/080,424 US7088620B2 (en) | 2004-03-31 | 2005-03-16 | Nonvolatile semiconductor memory device |

| CNB2005100600726A CN100401427C (zh) | 2004-03-31 | 2005-03-31 | 非易失性半导体存储器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004106210A JP4426361B2 (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005293697A true JP2005293697A (ja) | 2005-10-20 |

| JP2005293697A5 JP2005293697A5 (ja) | 2007-03-01 |

| JP4426361B2 JP4426361B2 (ja) | 2010-03-03 |

Family

ID=35050009

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004106210A Expired - Fee Related JP4426361B2 (ja) | 2004-03-31 | 2004-03-31 | 不揮発性半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7088620B2 (ja) |

| JP (1) | JP4426361B2 (ja) |

| CN (1) | CN100401427C (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010193688A (ja) * | 2009-02-20 | 2010-09-02 | Seiko Instruments Inc | 昇圧回路 |

| JP2011239482A (ja) * | 2010-04-30 | 2011-11-24 | Fujitsu Semiconductor Ltd | 電源回路 |

| JP2014179148A (ja) * | 2013-03-15 | 2014-09-25 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2017224374A (ja) * | 2016-06-17 | 2017-12-21 | 東芝メモリ株式会社 | 半導体記憶装置 |

| JP2019121413A (ja) * | 2018-01-11 | 2019-07-22 | ラピスセミコンダクタ株式会社 | 電源切替制御回路 |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100749736B1 (ko) * | 2005-06-13 | 2007-08-16 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 소거 방법 |

| US7466582B2 (en) * | 2005-08-15 | 2008-12-16 | International Business Machines Corporation | Voltage controlled static random access memory |

| US7352609B2 (en) * | 2005-08-15 | 2008-04-01 | International Business Machines Corporation | Voltage controlled static random access memory |

| JP2007310936A (ja) * | 2006-05-17 | 2007-11-29 | Toshiba Corp | 半導体記憶装置 |

| CN100536029C (zh) * | 2006-07-14 | 2009-09-02 | 威刚科技股份有限公司 | 非挥发性储存装置及其控制方法 |

| US7499325B2 (en) * | 2006-12-21 | 2009-03-03 | Intel Corporation | Flash memory device with improved erase operation |

| US7701784B2 (en) * | 2007-11-02 | 2010-04-20 | Kabushiki Kaisha Toshiba | Semiconductor memory device which includes memory cell having charge accumulation layer and control gate |

| US7551508B2 (en) * | 2007-11-16 | 2009-06-23 | International Business Machines Corporation | Energy efficient storage device using per-element selectable power supply voltages |

| JP5367977B2 (ja) * | 2007-12-12 | 2013-12-11 | セイコーインスツル株式会社 | 不揮発性半導体記憶装置およびその書き込み方法と読み出し方法 |

| US7916544B2 (en) | 2008-01-25 | 2011-03-29 | Micron Technology, Inc. | Random telegraph signal noise reduction scheme for semiconductor memories |

| US7978558B2 (en) * | 2008-03-24 | 2011-07-12 | Active-Semi, Inc. | In-circuit programming of output voltage and output current characteristics of a PSR power supply |

| JP2011211767A (ja) * | 2010-03-29 | 2011-10-20 | Toshiba Corp | 半導体集積回路装置 |

| KR101132018B1 (ko) * | 2010-07-09 | 2012-04-02 | 주식회사 하이닉스반도체 | 전압 스위치 회로 및 이를 이용한 불휘발성 메모리 장치 |

| DE102011056141A1 (de) * | 2010-12-20 | 2012-06-21 | Samsung Electronics Co., Ltd. | Negativspannungsgenerator, Dekoder, nicht-flüchtige Speichervorrichtung und Speichersystem, das eine negative Spannung verwendet |

| US8432752B2 (en) | 2011-06-27 | 2013-04-30 | Freescale Semiconductor, Inc. | Adaptive write procedures for non-volatile memory using verify read |

| US8509001B2 (en) * | 2011-06-27 | 2013-08-13 | Freescale Semiconductor, Inc. | Adaptive write procedures for non-volatile memory |

| KR101772582B1 (ko) | 2011-07-06 | 2017-08-30 | 삼성전자주식회사 | 음전압을 제공하는 비휘발성 메모리 장치 |

| JPWO2013128806A1 (ja) * | 2012-02-28 | 2015-07-30 | パナソニックIpマネジメント株式会社 | 昇圧回路 |

| US9053791B2 (en) * | 2012-03-07 | 2015-06-09 | Medtronic, Inc. | Flash memory with integrated ROM memory cells |

| US9607708B2 (en) | 2012-03-07 | 2017-03-28 | Medtronic, Inc. | Voltage mode sensing for low power flash memory |

| JP2013239215A (ja) * | 2012-05-11 | 2013-11-28 | Toshiba Corp | 半導体記憶装置 |

| CN105097035A (zh) * | 2014-04-25 | 2015-11-25 | 北京兆易创新科技股份有限公司 | 一种电压切换方法和装置 |

| JP5745136B1 (ja) * | 2014-05-09 | 2015-07-08 | 力晶科技股▲ふん▼有限公司 | 不揮発性半導体記憶装置とその書き込み方法 |

| US9728231B1 (en) | 2016-05-03 | 2017-08-08 | Taiwan Semiconductor Manufacturing Co., Ltd. | Device and method for data-writing |

| JP7065637B2 (ja) * | 2018-02-22 | 2022-05-12 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US10714166B2 (en) * | 2018-08-13 | 2020-07-14 | Micron Technology, Inc. | Apparatus and methods for decoding memory access addresses for access operations |

| CN111508546B (zh) * | 2019-01-31 | 2023-06-27 | 群联电子股份有限公司 | 解码方法、存储器控制电路单元与存储器存储装置 |

| CN113470710B (zh) * | 2020-03-31 | 2024-03-26 | 长鑫存储技术有限公司 | 半导体存储器 |

| CN111583982B (zh) * | 2020-05-13 | 2022-04-15 | 合肥中科智存科技有限公司 | 字线升压方法、装置、存储器和计算机存储介质 |

| JP7558123B2 (ja) * | 2021-07-21 | 2024-09-30 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体システム |

| CN115620769B (zh) * | 2022-10-08 | 2025-05-27 | 北京后摩集成电路科技有限公司 | 存储器控制电路、芯片及计算装置 |

| US12562227B2 (en) * | 2022-10-21 | 2026-02-24 | Micron Technology, Inc. | Voltage regulator supply for independent wordline reads |

| CN118072772A (zh) * | 2022-11-23 | 2024-05-24 | 长江存储科技有限责任公司 | 用于nand闪存存储器的高压开关 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0793026B2 (ja) * | 1989-09-20 | 1995-10-09 | 富士通株式会社 | デコーダ回路 |

| JP2835215B2 (ja) * | 1991-07-25 | 1998-12-14 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JPH05151789A (ja) * | 1991-11-29 | 1993-06-18 | Nec Corp | 電気的に書込・一括消去可能な不揮発性半導体記憶装置 |

| JPH05290587A (ja) | 1992-04-03 | 1993-11-05 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH06338193A (ja) * | 1993-05-28 | 1994-12-06 | Hitachi Ltd | 不揮発性半導体記憶装置 |

| EP0756286B1 (en) * | 1995-07-24 | 2000-01-26 | STMicroelectronics S.r.l. | Flash EEPROM with on-chip erase source voltage generator |

| JP3156618B2 (ja) * | 1997-01-30 | 2001-04-16 | 日本電気株式会社 | 不揮発性半導体記憶装置 |

| KR100290283B1 (ko) * | 1998-10-30 | 2001-05-15 | 윤종용 | 불휘발성 반도체 메모리 장치 및 그의 워드 라인 구동 방법 |

| JP4149637B2 (ja) * | 2000-05-25 | 2008-09-10 | 株式会社東芝 | 半導体装置 |

| KR100381962B1 (ko) * | 2000-08-07 | 2003-05-01 | 삼성전자주식회사 | 비휘발성 메모리 장치의 로우 디코더 |

| JP3756067B2 (ja) * | 2001-01-29 | 2006-03-15 | シャープ株式会社 | 不揮発性半導体記憶装置 |

-

2004

- 2004-03-31 JP JP2004106210A patent/JP4426361B2/ja not_active Expired - Fee Related

-

2005

- 2005-03-16 US US11/080,424 patent/US7088620B2/en not_active Expired - Lifetime

- 2005-03-31 CN CNB2005100600726A patent/CN100401427C/zh not_active Expired - Fee Related

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010193688A (ja) * | 2009-02-20 | 2010-09-02 | Seiko Instruments Inc | 昇圧回路 |

| US8203378B2 (en) | 2009-02-20 | 2012-06-19 | Seiko Instruments Inc. | Boosting circuit |

| KR101437201B1 (ko) * | 2009-02-20 | 2014-09-03 | 세이코 인스트루 가부시키가이샤 | 승압 회로 |

| JP2011239482A (ja) * | 2010-04-30 | 2011-11-24 | Fujitsu Semiconductor Ltd | 電源回路 |

| JP2014179148A (ja) * | 2013-03-15 | 2014-09-25 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2017224374A (ja) * | 2016-06-17 | 2017-12-21 | 東芝メモリ株式会社 | 半導体記憶装置 |

| JP2019121413A (ja) * | 2018-01-11 | 2019-07-22 | ラピスセミコンダクタ株式会社 | 電源切替制御回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100401427C (zh) | 2008-07-09 |

| JP4426361B2 (ja) | 2010-03-03 |

| US7088620B2 (en) | 2006-08-08 |

| US20050232013A1 (en) | 2005-10-20 |

| CN1677572A (zh) | 2005-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4426361B2 (ja) | 不揮発性半導体記憶装置 | |

| US6600692B2 (en) | Semiconductor device with a voltage regulator | |

| KR100420574B1 (ko) | 반도체집적회로장치 | |

| KR0159455B1 (ko) | 반도체 집적회로장치 | |

| JP5104118B2 (ja) | 内部電源回路 | |

| JPH097383A (ja) | 不揮発性半導体メモリ装置とそのワードライン駆動方法 | |

| US20030107919A1 (en) | Nonvolatile semiconductor memory and method for controlling programming voltage of nonvolatile semiconductor memory | |

| US6928000B2 (en) | Semiconductor memory device having a resistance adjustment unit | |

| JPH08235884A (ja) | 基準回路 | |

| JP4901204B2 (ja) | 半導体集積回路装置 | |

| JP2001210086A (ja) | 電圧発生回路 | |

| JP3207768B2 (ja) | 半導体装置 | |

| KR100605275B1 (ko) | 반도체 기억 장치 | |

| US6603700B2 (en) | Non-volatile semiconductor memory device having reduced power requirements | |

| JP2008262669A (ja) | 半導体記憶装置 | |

| JP4439530B2 (ja) | 半導体装置 | |

| JP4393529B2 (ja) | 半導体装置 | |

| US8264274B2 (en) | Non-volatile memory device and charge pump circuit for the same | |

| JP4680195B2 (ja) | 半導体装置及びソース電圧制御方法 | |

| KR20010085522A (ko) | 마이너스 전위 검지 회로, 및 마이너스 전위 검지 회로를구비한 반도체 기억 장치 | |

| JP3294153B2 (ja) | 半導体メモリ | |

| US7710806B2 (en) | Memory device and method for improving speed at which data is read from non-volatile memory | |

| JP3162214B2 (ja) | 半導体記憶装置 | |

| JPH04192196A (ja) | 不揮発性半導体記憶装置 | |

| JP2007058972A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070115 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070115 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090421 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090717 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4426361 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121218 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131218 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |