JP2005285197A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2005285197A JP2005285197A JP2004095876A JP2004095876A JP2005285197A JP 2005285197 A JP2005285197 A JP 2005285197A JP 2004095876 A JP2004095876 A JP 2004095876A JP 2004095876 A JP2004095876 A JP 2004095876A JP 2005285197 A JP2005285197 A JP 2005285197A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- current

- memory cell

- circuit

- node

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/24—Bit-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/06—Sense amplifier related aspects

- G11C2207/065—Sense amplifier drivers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/2227—Standby or low power modes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/563—Multilevel memory reading aspects

- G11C2211/5634—Reference cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5645—Multilevel memory with current-mirror arrangements

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Dram (AREA)

Abstract

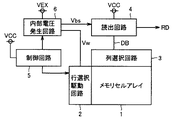

【解決手段】 読出回路(4)のセンスアンプに対し、電源電圧として、内部電圧発生回路(6)から内部電源電圧VCCよりも高い昇圧電圧Vbsを供給し、また内部データ線(DB)を介してのビット線プリチャージ電流は、内部電源電圧から供給する。

【選択図】 図1

Description

ここで、Vdsはドレイン−ソース間電圧を示し、Vgsはゲート−ソース間電圧を示し、Vthはしきい値電圧を示す。

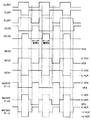

図1は、この発明の実施の形態1に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。図1において、この発明の実施の形態1に従う不揮発性半導体記憶装置は、行列状に配列される不揮発性メモリセルを有するメモリセルアレイ1を含む。メモリセルアレイ1においては、メモリセル行に対応してワード線が配置され、また、メモリセル列に対応してビット線が配置される。しかしながら、図1においては、図面を簡略化するために、これらのワード線およびビット線は、示していない。

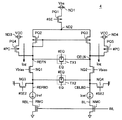

図5は、この発明の実施の形態1に従うセンスアンプの変更例の構成を示す図である。図5において、センスアンプは、内部ノードND1と内部ノードREFNの間に接続されかつそのゲートが内部ノードREFNに接続されるPチャネルMOSトランジスタPQ10と、内部ノードND1およびND10の間に接続されかつそのゲートが内部ノードREFNに接続されるPチャネルMOSトランジスタPQ11と、内部ノードND1と内部ノードND11の間に接続されかつそのゲートが内部ノードCELNに接続されるPチャネルMOSトランジスタPQ12と、内部ノードND1と内部ノードCELNの間に接続されかつそのゲートが内部ノードCELNに接続されるPチャネルMOSトランジスタPQ13と、相補イコライズ指示信号EQおよび♯EQに従って、内部ノードND10およびND11を電気的に短絡するCMOSトランスミッションゲートTX10と、内部ノードと接地ノードの間に接続されかつそのゲートが内部ノードND10に接続されるNチャネルMOSトランジスタNQ10と、内部ノードND11と接地ノードの間に接続されかつそのゲートが内部ノードND10に接続されるNチャネルMOSトランジスタNQ11を含む。

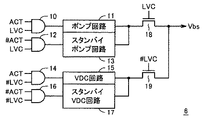

図6は、実施の形態1におけるセンスアンプに供給される昇圧電圧Vbsを発生する部分の構成を概略的に示す図である。図6に示す昇圧電圧発生部は、図1に示す内部電圧発生回路6に含まれる。

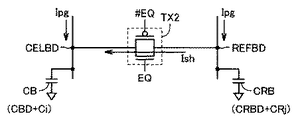

図11は、この発明の実施の形態3に従う不揮発性半導体記憶装置のデータ読出部の構成を概略的に示す図である。図11において、センスアンプ40は、図2または図5に示す構成を一例として有する。このセンスアンプ40に接続される内部読出データ線CELBDおよびおよび参照データ線REFBDには、それぞれ容量CBDおよびCRBDが接続される。

i=0−n,j=1−3

すなわち、セルセンスノードCELBDに接続される容量の値が、参照センスノードREFBDの容量値よりも常に大きくされる。次に、図11に示す不揮発性半導体記憶装置の4値データ読出時の動作について説明する。

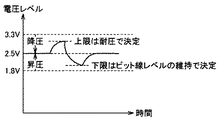

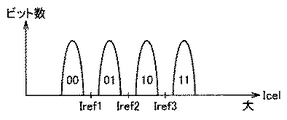

図15は、この発明の実施の形態4におけるメモリセルの記憶データのしきい値電圧の分布の一例を概略的に示す図である。図15においては、4値データを記憶するメモリセルのしきい値電圧の分布を示す。データ(11)を記憶するメモリセルのしきい値電圧は、電圧V3よりも低い。データ(10)を記憶するメモリセルのしきい値電圧は、電圧V2およびV3の間に分布する。データ(01)を記憶するメモリセルのしきい値電圧は、電圧V1およびV2の間に分布する。データ(00)を記憶するメモリセルのしきい値電圧は、電圧V1よりも高い電圧レベルであり、また、データ読出時にワード線に与えられるワード線読出電圧VWLよりも低い電圧レベルである。メモリセルのしきい値電圧が低いほど、ワード線読出電圧VWL印加時のメモリセル電流Icelが大きくなる。したがって、データ(11)を記憶するメモリセルの駆動電流が、データ(00)を記憶するメモリセルの駆動電流よりもデータ読出時大きくなる。

図20は、この発明の実施の形態5に従う不揮発性半導体記憶装置のセンスアンプに関連する部分の構成を示す図である。図20において、センスアンプ40は、実施の形態1に示すセンスアンプと同様の構成を備え、センスノードCELBDおよびREFBDが、それぞれ、メモリセルNMCおよび参照セルRMCにセンス動作時結合される。この図20に示す構成においては、センスアンプ40に対して、定電圧VRSAを生成する定電圧発生回路50と、選択信号SELNに従って定電圧VRSAを伝達するトランスファーゲートSQNと、センスノードCELBDに結合され、定電圧VRSAを転送ゲートSQNを介してゲートに受けて、センスノードCELBDから定電流を接地ノードへ放電するNチャネルMOSトランジスタQNと、選択信号SELRに従って、定電圧VRSAを伝達する転送ゲートSQRと、転送ゲートSQRを介してゲートに定電圧VRSAを受け、参照センスノードREFBDから定電流を接地ノードへ放電するNチャネルMOSトランジスタQRがさらに設けられる。

この状態においては、転送ゲートSQNがオフ状態、転送ゲートSQRがオン状態であり、参照セルRMCに対して設けられるトランジスタQRが定電流源として動作する。この状態において、参照セルRMCを選択しない状態で、メモリセルNMCを選択してセンスアンプ40でセンス動作を行なう。この場合、参照セルRMCが規定する参照電流値と異なる電流値でセンス動作を行なうことができる。したがって、この状態で、定電圧発生回路50のMOSトランジスタPQ30のサイズを変更して、定電圧VRSAを変更することにより、MOSトランジスタQRの駆動電流を変更することができ、メモリセルNMCを流れる電流値を詳細に解析することができる。

この状態においては、転送ゲートSQNがオン状態、転送ゲートSQRがオフ状態であり、MOSトランジスタQNが、定電圧VRSAに従って、定電流をセルセンスノードCELBDから駆動する。この状態においては、メモリセルNMCの選択は行なわず、参照セルRMCを選択して、センスアンプ40でセンス動作を行なう。MOSトランジスタPQ30のサイズ(チャネル幅)を変更してその駆動電流を変更することにより、定電圧発生回路50からの定電圧VRSAを変更して、MOSトランジスタQNが駆動する電流を変更することができる。したがって、この場合、参照セルRMCを流れる電流値を詳細に解析することができる。参照電流を所望の値に設定したい場合、このセンス動作の結果を用いて、所望の参照電流が得られるように、参照セルのしきい値電圧を制御することができる。

この状態においては、転送ゲートSQNおよびSQRがともにオン状態であり、MOSトランジスタQNおよびQRがともに定電流を駆動する。この状態において、メモリセルNMCおよび参照セルRMCをともに選択することにより、センスアンプ40のセンスノードCELBDおよびREFBDを流れる電流にオフセットを持たせることができる。

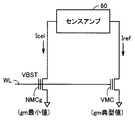

図22は、この発明の実施の形態6に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。図22において、センスアンプ60に、メモリセルNMCgおよびベリファイ参照セルVMCが結合される。これらのメモリセルNMCgおよびベリファイ参照セルVMCは、ワード線WLに共通に結合される。このベリファイ参照セルVMCは、その相互コンダクタンスgmが典型値を有し、メモリセルNMCgが、その相互コンダクタンスgmが、最小値を有する状態を考える。このメモリセルNMCgを消去する場合、ワード線WLに消去電圧を印加して、メモリセルNMCgのしきい値を変化させる。この消去動作は、ここでは、メモリセルNMCgの相互コンダクタンスgmを大きくする、すなわちメモリセルNMCgのしきい値電圧の絶対値を小さくする動作とする。

ここで、VTは、熱電圧であり、k・T/qで表される。kはボルツマン定数であり、qは電荷を示す。

このバイポーラトランジスタ83のベース−エミッタ間電圧Vbeは、負の温度係数を有しており、また抵抗素子R0−Rnは各々拡散抵抗で形成され、正の温度係数を有する。したがって、これらの抵抗素子R0−Rnを制御ビットTN[0]−TN[n]に従って選択的に短絡することにより、この基準電圧VREFの温度依存性を、正および負のいずれの方向にも調整することができる。

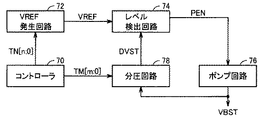

この分圧電圧DVSTが、基準電圧VREFと等しくなるように、レベル検出回路74において、ポンプイネーブル信号PENが選択的に活性化される。温度依存性を変更するために、図27に示すVREF発生回路72において、抵抗素子R0−Rnを選択的に短絡させた場合、基準電圧VREFの電圧レベルが変化する。この基準電圧VREFの電圧レベルの変化を、分圧電圧DVSTの変化により補償し、同一電圧レベルで、温度依存性の異なる基準電圧VREFを生成する。

=DVST・(Ra+k・Rb)/Ra

=VREF・(Ra+k・Rb)/Ra

={Icst・(R(RR)+m・R(R)+Vbe)・(Ra+k・Rb)/Ra

上式において、抵抗値RaおよびRbの項は、その分母および分子により、温度特性が相殺される。一方、{}内においては、ベース−エミッタ間電圧Vbeおよび抵抗値R(RR)+m・R(R)が、それぞれ負の温度特性およびおよび正の温度特性を有しており、この抵抗値R(RR)+m・R(R)を調整することにより、ベリファイ電圧VBSTの温度特性を、電圧レベルを変更することなく、変更することができる。

Claims (13)

- 複数のメモリセル、および

前記複数のメモリセルの選択メモリセルのデータを検出するためのセンス増幅回路を備え、

前記センス増幅回路は、

内部電源電圧よりも高い電圧を受ける昇圧電源ノードと、

前記昇圧電源ノードに動作時結合され、前記選択メモリセルを流れる電流に応じて前記選択メモリセルの記憶データを読出す読出部と、

前記内部電源電圧を受けるノードに結合され、プリチャージ指示信号に応答して前記選択メモリセルへ前記内部電源ノードからの電流を供給して前記選択メモリセルが接続されるデータ線を所定電位にプリチャージするプリチャージ段とを備える、半導体記憶装置。 - 外部から供給可能な外部電源電圧が前記昇圧電圧よりも高いときに動作可能とされ、活性化時、前記昇圧電圧を前記外部電源電圧の降圧により生成して前記昇圧電源ノードに供給する第1の電源と、

前記外部電源電圧が前記昇圧電圧よりも低いときに動作可能とされ、活性化時、前記外部電源電圧の昇圧動作により前記昇圧電圧を生成して前記昇圧電源ノードに供給する第2の電源とをさらに備える、請求項1記載の半導体記憶装置。 - 前記読出部は、埋込チャネル方式のPチャネル絶縁ゲート型電界効果トランジスタを備える、請求項1記載の半導体記憶装置。

- 前記半導体記憶装置は、前記選択メモリセルのデータ読出基準の参照電流を生成する参照セルをさらに備え、

前記センス増幅器は、

前記読出部として作用するカレントミラー段と、

基準バイアス電圧により伝達電圧レベルが制限され、前記プリチャージ段からの電流を前記選択メモリセルおよび前記参照セルに供給する電圧供給段と、

前記選択メモリセルおよび前記参照セルがそれぞれ結合されるデータ線を所定電位に初期設定する初期段と、

前記カレントミラー段の出力ノードをイコライズするイコライズ段とを備える、請求項1記載の半導体記憶装置。 - 前記半導体記憶装置は、前記選択メモリセルのデータ読出基準の参照電流を生成する参照セルをさらに備え、

前記センス増幅器は、

前記読出部として作用して、前記選択メモリセルに流れる電流を検出する第1のカレントミラー段と、

前記読出部として作用して、前記参照メモリセルに流れる電流を検出する第2のカレントミラー段と、

前記第1および第2のカレントミラー段をミラー結合して、前記選択メモリセルおよび前記参照セルの駆動電流の差に応じて前記選択メモリセルのデータを読出す第3のカレントミラー段と、

基準バイアス電圧により伝達電圧レベルが制限され、前記プリチャージ段からの電流を前記選択メモリセルおよび前記参照セルに供給する電圧供給段と、

前記選択メモリセルおよび前記参照セルがそれぞれ結合されるデータ線を所定電位に初期設定する初期段と、

前記プリチャージ段の出力ノードをイコライズする第1のイコライズ段と、

前記第3のカレントミラー段の出力ノードをイコライズする第2のイコライズ段を備える、請求項1記載の半導体記憶装置。 - 各々がゲートを有し、そのしきい値電圧によりデータを記憶するトランジスタで構成される複数のメモリセル、

前記メモリセルと同一構造の参照セル、

前記複数のメモリセルの選択メモリセルの駆動電流と前記参照セルの駆動電流をセンスして前記選択メモリセルのデータを読出すセンス増幅回路、および

前記参照セルおよび前記選択メモリセルのゲートに印加する電圧を生成するゲート電圧発生回路を備え、前記ゲート電圧発生回路は、前記選択メモリセルの通常データ読出モード時には前記参照セルおよび前記選択メモリセルのゲートに対する電圧として同一レベルの電圧を生成し、前記選択メモリセルの書込または消去の検証モード時には、メモリセルの駆動電流分布範囲の上下端の位置のメモリセルの検証時には通常モード時とは異なるレベルの電圧を前記選択メモリセルのゲート電圧として生成する、半導体記憶装置。 - 複数のメモリセル、

参照メモリセル、および

前記複数のメモリセルのうちの選択メモリセルに接続される第1のノードと前記参照セルに接続される第2のノードとを有し、前記第1および第2のノードを流れる電流に従って前記選択メモリセルのデータを読出すセンス増幅器を備え、前記第1のノードの容量値は、前記第2のノードの容量値よりも大きくされている、半導体記憶装置。 - 選択メモリセルに接続される第1のノードと参照セルに接続される第2のノードとを有し、前記第1および第2のノードを流れる電流に従って前記選択メモリセルのデータを検出するセンス増幅回路、および

前記第1および第2のノードにそれぞれ結合されかつ個々に活性化され、活性化時、定電流を駆動する第1および第2の定電流源を備える、半導体記憶装置。 - 動作モード指示信号に従って前記第1および第2の定電流源を選択的に活性化する活性制御回路をさらに備える、請求項8記載の半導体記憶装置。

- 前記第1および第2の定電流源は、各々、活性化時、定電流発生回路の電流/電圧変換トランジスタとカレントミラー回路を構成するトランジスタを備える、請求項8記載の半導体記憶装置。

- 少なくとも1行に整列して配置され、各々がゲートを有しかつそのゲート電圧/電流特性が温度依存性を有するトランジスタを含み、該トランジスタのしきい値電圧に応じてデータを記憶するメモリセル、および

前記メモリセルのトランジスタのゲート電圧−駆動電流特性の温度依存性を補償する温度依存性を有するワード線駆動電圧を発生する電圧発生回路を備え、前記ワード線駆動電圧は、その温度依存性が制御信号に従って正および負の方向に変更可能であり、

前記行に整列して配置されるメモリセルに対応して配置され、前記メモリセルトランジスタのゲートが接続される少なくとも1本のワード線、および

前記1本のワード線の選択時、前記電圧発生回路の発生するワード線駆動電圧を前記1本のワード線に伝達するワード線選択回路を備える、半導体記憶装置。 - 前記電圧発生回路は、

活性化時、電荷ポンプ動作により前記ワード線駆動電圧を生成する電圧生成回路、

前記電圧生成回路の生成するワード線駆動電圧を分圧する分圧回路、

温度依存性を有する基準電圧を発生する基準電圧発生回路、

前記基準電圧発生回路の生成する基準電圧の温度依存性を調整しかつ前記分圧回路の分圧比を調整する制御部と、

前記基準電圧発生回路からの基準電圧と前記分圧回路からの分圧電圧との比較に基づいて前記電圧生成回路を選択的に活性化するレベル判定回路とを備える、請求項11記載の半導体記憶装置。 - 前記基準電圧発生回路は、

定電流発生回路と、

ダイオード接続されるバイポーラトランジスタと、

前記定電流発生回路からの定電流を前記バイポーラトランジスタへ供給するその抵抗値が変更可能な抵抗素子とを備え、前記基準電圧は前記定電流発生回路と前記抵抗素子との間のノードに生成される、請求項12記載の半導体記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004095876A JP2005285197A (ja) | 2004-03-29 | 2004-03-29 | 半導体記憶装置 |

| US11/082,926 US7542363B2 (en) | 2004-03-29 | 2005-03-18 | Semiconductor memory device enhancing reliability in data reading |

| US12/437,021 US7885132B2 (en) | 2004-03-29 | 2009-05-07 | Semiconductor memory device enhancing reliability in data reading |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004095876A JP2005285197A (ja) | 2004-03-29 | 2004-03-29 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005285197A true JP2005285197A (ja) | 2005-10-13 |

| JP2005285197A5 JP2005285197A5 (ja) | 2006-10-19 |

Family

ID=34989616

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004095876A Pending JP2005285197A (ja) | 2004-03-29 | 2004-03-29 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7542363B2 (ja) |

| JP (1) | JP2005285197A (ja) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007134032A (ja) * | 2005-11-07 | 2007-05-31 | Samsung Electronics Co Ltd | 相変化メモリ装置及びそれの読み出し方法 |

| JP2007141273A (ja) * | 2005-11-14 | 2007-06-07 | Renesas Technology Corp | 不揮発性記憶装置 |

| JP2007172775A (ja) * | 2005-12-26 | 2007-07-05 | Toshiba Corp | センスアンプ及び半導体記憶装置 |

| JP2008199617A (ja) * | 2007-02-09 | 2008-08-28 | Fujitsu Ltd | カスコードバイアスされたチャージポンプ |

| JP2009129470A (ja) * | 2007-11-20 | 2009-06-11 | Toshiba Corp | 半導体記憶装置 |

| JP2009163798A (ja) * | 2007-12-28 | 2009-07-23 | Toshiba Corp | 半導体記憶装置 |

| JP2011118982A (ja) * | 2009-12-03 | 2011-06-16 | Toppan Printing Co Ltd | フラッシュメモリ |

| TWI391948B (zh) * | 2007-12-20 | 2013-04-01 | Sandisk Technologies Inc | 非揮發性記憶體裝置及感測記憶體單元頁之方法 |

| US8509002B2 (en) | 2009-05-29 | 2013-08-13 | Samsung Electronics Co., Ltd. | Semiconductor memory device and method of driving the same |

| JP2014149692A (ja) * | 2013-02-01 | 2014-08-21 | Rohm Co Ltd | 定電圧源 |

| CN108109647A (zh) * | 2016-11-25 | 2018-06-01 | 拉碧斯半导体株式会社 | 读出放大电路 |

Families Citing this family (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4253312B2 (ja) * | 2005-04-15 | 2009-04-08 | 株式会社東芝 | 半導体記憶装置 |

| EP1729302B1 (en) * | 2005-05-31 | 2019-01-02 | Micron Technology, Inc. | A circuit for retrieving data stored in semiconductor memory cells |

| US7518930B2 (en) * | 2006-04-21 | 2009-04-14 | Sandisk Corporation | Method for generating and adjusting selected word line voltage |

| US7391650B2 (en) * | 2006-06-16 | 2008-06-24 | Sandisk Corporation | Method for operating non-volatile memory using temperature compensation of voltages of unselected word lines and select gates |

| US7821859B1 (en) * | 2006-10-24 | 2010-10-26 | Cypress Semiconductor Corporation | Adaptive current sense amplifier with direct array access capability |

| US7573748B2 (en) * | 2007-01-12 | 2009-08-11 | Atmel Corporation | Column leakage compensation in a sensing circuit |

| US7639540B2 (en) * | 2007-02-16 | 2009-12-29 | Mosaid Technologies Incorporated | Non-volatile semiconductor memory having multiple external power supplies |

| WO2008133674A1 (en) * | 2007-04-27 | 2008-11-06 | Sandisk Corporation | Method and device for generating and adjusting selected word line voltage |

| US7995397B1 (en) | 2007-05-03 | 2011-08-09 | Cypress Semiconductor Corporation | Power supply tracking single ended sensing scheme for SONOS memories |

| US7764547B2 (en) | 2007-12-20 | 2010-07-27 | Sandisk Corporation | Regulation of source potential to combat cell source IR drop |

| KR101434400B1 (ko) * | 2008-07-09 | 2014-08-27 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 메모리 시스템 및 그것의 관리방법 |

| JP2010097344A (ja) * | 2008-10-15 | 2010-04-30 | Elpida Memory Inc | 半導体装置 |

| JP5437658B2 (ja) * | 2009-02-18 | 2014-03-12 | セイコーインスツル株式会社 | データ読出回路及び半導体記憶装置 |

| JP2011210348A (ja) * | 2010-03-11 | 2011-10-20 | Sony Corp | 制御電圧生成回路及びそれを備えた不揮発性記憶装置 |

| US9423814B2 (en) * | 2010-03-16 | 2016-08-23 | Macronix International Co., Ltd. | Apparatus of supplying power while maintaining its output power signal and method therefor |

| US8498141B2 (en) * | 2010-03-24 | 2013-07-30 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

| US8743630B2 (en) * | 2011-05-23 | 2014-06-03 | Infineon Technologies Ag | Current sense amplifier with replica bias scheme |

| US8630125B2 (en) * | 2011-06-02 | 2014-01-14 | Micron Technology, Inc. | Memory cell sensing using a boost voltage |

| US8773913B1 (en) * | 2011-12-02 | 2014-07-08 | Cypress Semiconductor Corporation | Systems and methods for sensing in memory devices |

| US8611157B2 (en) * | 2011-12-22 | 2013-12-17 | Sandisk Technologies Inc. | Program temperature dependent read |

| US9343146B2 (en) * | 2012-01-10 | 2016-05-17 | Micron Technology, Inc. | Apparatuses and methods for low power current mode sense amplification |

| US9208871B2 (en) * | 2012-01-30 | 2015-12-08 | HGST Netherlands B.V. | Implementing enhanced data read for multi-level cell (MLC) memory using threshold voltage-drift or resistance drift tolerant moving baseline memory data encoding |

| KR101998076B1 (ko) * | 2012-05-30 | 2019-07-09 | 삼성전자 주식회사 | 집적 회로 및 이를 포함하는 장치들 |

| JP5710561B2 (ja) * | 2012-08-29 | 2015-04-30 | 株式会社東芝 | 半導体記憶装置 |

| US8665651B1 (en) * | 2012-09-11 | 2014-03-04 | Winbond Electronics Corp. | Reference cell circuit and method of producing a reference current |

| TWI485713B (zh) * | 2012-12-11 | 2015-05-21 | Winbond Electronics Corp | 用以產生參考電流之參考單元電路以及方法 |

| US8760930B1 (en) * | 2013-02-18 | 2014-06-24 | Spansion Llc. | Memory device with source-side sensing |

| US9177663B2 (en) | 2013-07-18 | 2015-11-03 | Sandisk Technologies Inc. | Dynamic regulation of memory array source line |

| US9960672B2 (en) * | 2013-08-09 | 2018-05-01 | SK Hynix Inc. | High voltage generator |

| US9368224B2 (en) | 2014-02-07 | 2016-06-14 | SanDisk Technologies, Inc. | Self-adjusting regulation current for memory array source line |

| US9484809B2 (en) * | 2014-06-21 | 2016-11-01 | Brian Harold Floyd | Apparatus and methods for low voltage high PSRR systems |

| ITUB20155867A1 (it) * | 2015-11-24 | 2017-05-24 | St Microelectronics Srl | Circuito amplificatore di lettura con compensazione dell'offset per un dispositivo di memoria non volatile |

| WO2017122418A1 (ja) * | 2016-01-12 | 2017-07-20 | ソニー株式会社 | 半導体記憶装置、および、半導体記憶装置の制御方法 |

| US9727267B1 (en) * | 2016-09-27 | 2017-08-08 | Intel Corporation | Power management and monitoring for storage devices |

| US10095432B2 (en) | 2016-09-27 | 2018-10-09 | Intel Corporation | Power management and monitoring for storage devices |

| US10692581B2 (en) | 2017-01-18 | 2020-06-23 | Microchip Technology Incorporated | Circuits for bleeding supply voltage from a device in a power down state |

| CN108377091B (zh) * | 2018-04-12 | 2019-10-25 | 武汉新芯集成电路制造有限公司 | 电荷泵驱动电路 |

| KR102627994B1 (ko) * | 2018-10-04 | 2024-01-22 | 삼성전자주식회사 | 비휘발성 메모리 장치의 센싱 회로, 이를 포함하는 비휘발성 메모리 장치 및 비휘발성 메모리 장치의 동작 방법 |

| TWI830869B (zh) | 2019-04-05 | 2024-02-01 | 南韓商Sk海力士系統集成電路有限公司 | 動態電壓供應電路和包含其之非揮發性記憶體裝置 |

| KR102689654B1 (ko) * | 2019-07-10 | 2024-07-31 | 삼성전자주식회사 | 메모리 장치 |

| US11094386B1 (en) * | 2020-02-13 | 2021-08-17 | Intel Corporation | Device, system, and method to verify data programming of a multi-level cell memory based on one of temperature, pressure, wear condition or relative position of the memory cell |

| CN112542197A (zh) * | 2020-12-29 | 2021-03-23 | 深圳市芯天下技术有限公司 | 提高灵敏放大器读取可靠性方法、装置、存储介质和终端 |

| US11367468B1 (en) | 2021-02-26 | 2022-06-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Sense amplifier |

| CN113921046A (zh) * | 2021-09-29 | 2022-01-11 | 长江存储科技有限责任公司 | 存储器及其读取方法、存储器系统 |

| US20240329153A1 (en) * | 2023-03-29 | 2024-10-03 | Arm Limited | Current Measurement Architecture |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5784179A (en) | 1980-11-13 | 1982-05-26 | Nec Corp | Semiconductor memory device |

| JPH0793032B2 (ja) | 1989-04-27 | 1995-10-09 | 日本電気株式会社 | 半導体記憶装置 |

| IT1246241B (it) | 1990-02-23 | 1994-11-17 | Sgs Thomson Microelectronics | Circuito per la lettura dell'informazione contenuta in celle di memoria non volatili |

| JPH04362597A (ja) * | 1991-06-10 | 1992-12-15 | Nec Ic Microcomput Syst Ltd | 電流センスアンプ回路 |

| JPH05298884A (ja) * | 1992-04-15 | 1993-11-12 | Nec Corp | 半導体記憶装置 |

| JPH09282890A (ja) | 1996-02-16 | 1997-10-31 | Nkk Corp | 昇圧回路を有する半導体記憶装置 |

| JPH09245493A (ja) | 1996-03-07 | 1997-09-19 | Hitachi Ltd | 不揮発性半導体記憶装置 |

| EP0809256A3 (en) | 1996-05-21 | 1999-04-14 | Information Storage Devices, Inc. | Method and circuit for linearized reading of analog floating gate storage cell |

| US5734275A (en) * | 1996-07-18 | 1998-03-31 | Advanced Micro Devices, Inc. | Programmable logic device having a sense amplifier with virtual ground |

| JPH1173769A (ja) | 1997-08-27 | 1999-03-16 | Mitsubishi Electric Corp | 半導体装置 |

| US6025232A (en) * | 1997-11-12 | 2000-02-15 | Micron Technology, Inc. | Methods of forming field effect transistors and related field effect transistor constructions |

| JP2000090682A (ja) * | 1998-09-10 | 2000-03-31 | Toshiba Corp | 半導体記憶装置 |

| KR100295361B1 (ko) * | 1998-12-30 | 2001-07-12 | 윤종용 | 불 휘발성 반도체 메모리 장치 |

| JP3954245B2 (ja) | 1999-07-22 | 2007-08-08 | 株式会社東芝 | 電圧発生回路 |

| JP3836279B2 (ja) * | 1999-11-08 | 2006-10-25 | 株式会社東芝 | 半導体記憶装置及びその制御方法 |

| KR100347067B1 (ko) | 1999-12-06 | 2002-08-03 | 삼성전자 주식회사 | 안정된 읽기 동작을 수행하는 반도체 메모리 장치 |

| US6205074B1 (en) | 2000-02-29 | 2001-03-20 | Advanced Micro Devices, Inc. | Temperature-compensated bias generator |

| JP3651767B2 (ja) | 2000-04-24 | 2005-05-25 | シャープ株式会社 | 半導体記憶装置 |

| JP3633864B2 (ja) | 2000-11-29 | 2005-03-30 | Necマイクロシステム株式会社 | 不揮発性メモリの基準電圧発生回路 |

| JP2002319286A (ja) | 2001-04-19 | 2002-10-31 | Hitachi Ltd | 不揮発性記憶装置および記憶システム |

| JP2003217287A (ja) | 2002-01-21 | 2003-07-31 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置 |

| KR100476888B1 (ko) * | 2002-04-04 | 2005-03-17 | 삼성전자주식회사 | 온도보상기능을 가진 멀티비트 플래쉬메모리 |

| JP2003308698A (ja) * | 2002-04-12 | 2003-10-31 | Toshiba Corp | 不揮発性半導体メモリ装置 |

-

2004

- 2004-03-29 JP JP2004095876A patent/JP2005285197A/ja active Pending

-

2005

- 2005-03-18 US US11/082,926 patent/US7542363B2/en not_active Expired - Fee Related

-

2009

- 2009-05-07 US US12/437,021 patent/US7885132B2/en not_active Expired - Fee Related

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007134032A (ja) * | 2005-11-07 | 2007-05-31 | Samsung Electronics Co Ltd | 相変化メモリ装置及びそれの読み出し方法 |

| JP2007141273A (ja) * | 2005-11-14 | 2007-06-07 | Renesas Technology Corp | 不揮発性記憶装置 |

| JP2007172775A (ja) * | 2005-12-26 | 2007-07-05 | Toshiba Corp | センスアンプ及び半導体記憶装置 |

| JP2008199617A (ja) * | 2007-02-09 | 2008-08-28 | Fujitsu Ltd | カスコードバイアスされたチャージポンプ |

| JP2009129470A (ja) * | 2007-11-20 | 2009-06-11 | Toshiba Corp | 半導体記憶装置 |

| TWI391948B (zh) * | 2007-12-20 | 2013-04-01 | Sandisk Technologies Inc | 非揮發性記憶體裝置及感測記憶體單元頁之方法 |

| JP2009163798A (ja) * | 2007-12-28 | 2009-07-23 | Toshiba Corp | 半導体記憶装置 |

| US8509002B2 (en) | 2009-05-29 | 2013-08-13 | Samsung Electronics Co., Ltd. | Semiconductor memory device and method of driving the same |

| JP2011118982A (ja) * | 2009-12-03 | 2011-06-16 | Toppan Printing Co Ltd | フラッシュメモリ |

| JP2014149692A (ja) * | 2013-02-01 | 2014-08-21 | Rohm Co Ltd | 定電圧源 |

| CN108109647A (zh) * | 2016-11-25 | 2018-06-01 | 拉碧斯半导体株式会社 | 读出放大电路 |

| CN108109647B (zh) * | 2016-11-25 | 2023-12-05 | 拉碧斯半导体株式会社 | 读出放大电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7885132B2 (en) | 2011-02-08 |

| US20050213387A1 (en) | 2005-09-29 |

| US7542363B2 (en) | 2009-06-02 |

| US20090213667A1 (en) | 2009-08-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005285197A (ja) | 半導体記憶装置 | |

| CN1848299B (zh) | 非易失性半导体存储装置的基准电流生成电路 | |

| US6438038B2 (en) | Read circuit of nonvolatile semiconductor memory | |

| JP3583703B2 (ja) | 半導体装置 | |

| US9053805B2 (en) | Semiconductor memory device | |

| US6788601B2 (en) | Semiconductor memory device and current mirror circuit | |

| TWI431635B (zh) | 驅動字元線的電路及其方法 | |

| JP4305960B2 (ja) | 強誘電体メモリ装置 | |

| JP2006309756A (ja) | 温度依存電圧を生成する基準回路 | |

| JPH06104672A (ja) | クランプ回路 | |

| TWI258769B (en) | Semiconductor readout circuit | |

| JP2001229687A (ja) | 電圧レギュレータ回路および半導体メモリ装置 | |

| US6121812A (en) | Delay circuit having delay time free from influence of operation environment | |

| JP2016513852A (ja) | 高速・低電力センス増幅器 | |

| JP2007087512A (ja) | 不揮発性半導体記憶装置、及び、不揮発性半導体記憶装置の動作方法 | |

| JP2002025285A (ja) | 不揮発性半導体記憶装置 | |

| US6865110B1 (en) | Program voltage generation circuit for stably programming flash memory cell and method of programming flash memory cell | |

| US7898897B2 (en) | Circuit and method for generating word line off voltage | |

| JP7273599B2 (ja) | 半導体装置およびメモリの読み出し方法 | |

| US6937529B2 (en) | Semiconductor memory device performing reliable data sensing | |

| US20040125670A1 (en) | Circuit for biasing an input node of a sense amplifier with a pre-charge stage | |

| US7298199B2 (en) | Substrate bias voltage generating circuit for use in a semiconductor memory device | |

| JP2008090885A (ja) | 半導体集積装置 | |

| KR20140080943A (ko) | 비휘발성 메모리 장치 | |

| JPWO2007125590A1 (ja) | 半導体装置およびその制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060831 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060831 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090310 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090421 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090602 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091013 |