CN1186820C - 半导体存储阵列及其制造方法 - Google Patents

半导体存储阵列及其制造方法 Download PDFInfo

- Publication number

- CN1186820C CN1186820C CNB011357045A CN01135704A CN1186820C CN 1186820 C CN1186820 C CN 1186820C CN B011357045 A CNB011357045 A CN B011357045A CN 01135704 A CN01135704 A CN 01135704A CN 1186820 C CN1186820 C CN 1186820C

- Authority

- CN

- China

- Prior art keywords

- raceway groove

- material layer

- layer

- stop block

- polysilicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000007667 floating Methods 0.000 title claims abstract description 71

- 239000004065 semiconductor Substances 0.000 title claims abstract description 23

- 238000000034 method Methods 0.000 claims abstract description 125

- 239000000758 substrate Substances 0.000 claims abstract description 77

- 239000004020 conductor Substances 0.000 claims abstract description 72

- 125000006850 spacer group Chemical group 0.000 claims abstract description 26

- 239000000463 material Substances 0.000 claims abstract description 20

- 238000005530 etching Methods 0.000 claims description 113

- 238000005192 partition Methods 0.000 claims description 100

- 230000003647 oxidation Effects 0.000 claims description 68

- 238000007254 oxidation reaction Methods 0.000 claims description 68

- 239000012774 insulation material Substances 0.000 claims description 39

- 230000015572 biosynthetic process Effects 0.000 claims description 34

- 229910052710 silicon Inorganic materials 0.000 claims description 29

- 239000010703 silicon Substances 0.000 claims description 29

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 27

- 230000004888 barrier function Effects 0.000 claims description 27

- 229910052751 metal Inorganic materials 0.000 claims description 27

- 239000002184 metal Substances 0.000 claims description 27

- 238000009413 insulation Methods 0.000 claims description 11

- 239000011810 insulating material Substances 0.000 claims description 7

- 238000002161 passivation Methods 0.000 claims description 5

- 238000011049 filling Methods 0.000 claims description 4

- 238000002955 isolation Methods 0.000 abstract description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 266

- 229920005591 polysilicon Polymers 0.000 description 256

- 239000010410 layer Substances 0.000 description 238

- 238000006396 nitration reaction Methods 0.000 description 49

- 238000005516 engineering process Methods 0.000 description 44

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 26

- 229920002120 photoresistant polymer Polymers 0.000 description 25

- 238000001020 plasma etching Methods 0.000 description 20

- 238000000151 deposition Methods 0.000 description 18

- 229910052581 Si3N4 Inorganic materials 0.000 description 16

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 16

- 150000002500 ions Chemical class 0.000 description 15

- 238000001465 metallisation Methods 0.000 description 14

- 229910021332 silicide Inorganic materials 0.000 description 14

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 14

- 239000000377 silicon dioxide Substances 0.000 description 13

- 235000012239 silicon dioxide Nutrition 0.000 description 11

- 238000002347 injection Methods 0.000 description 8

- 239000007924 injection Substances 0.000 description 8

- 239000005380 borophosphosilicate glass Substances 0.000 description 7

- 150000004767 nitrides Chemical class 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 239000003795 chemical substances by application Substances 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 230000000295 complement effect Effects 0.000 description 5

- 238000001259 photo etching Methods 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 230000005611 electricity Effects 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 239000010941 cobalt Substances 0.000 description 3

- 229910017052 cobalt Inorganic materials 0.000 description 3

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 206010011469 Crying Diseases 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- -1 silicon nitrides Chemical class 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000002224 dissection Methods 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 239000003292 glue Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000000452 restraining effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42324—Gate electrodes for transistors with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

一种在半导体衬底上形成浮栅存储单元的半导体存储阵列的自对准方法,在衬底上有多个在列方向上基本互相平行的间隔隔离区和有源区。通过形成一导电材料层在每个有源区形成浮栅。在行方向上穿过有源区形成沟道,并且用导电材料填满以形成导电材料阻块,导电材料阻块是控制栅。沿着浮栅阻块到浮栅上的浮栅突出部分形成导电材料侧壁隔片。

Description

技术领域

本发明涉及形成裂栅型浮栅存储单元的半导体存储阵列的自对准方法,本发明也涉及前述类型的浮栅存储单元的半导体存储阵列。

发明背景

使用浮栅在其上存储电荷的非易失性半导体存储单元和形成在半导体衬底上的这种非易失性存储单元的存储阵列是本领域公知的。典型地,已经有裂栅型或叠栅型或者它们的结合的这种浮栅存储单元。

半导体浮栅存储单元阵列的制造所面临的一个问题是各种部件例如源、漏、控制栅和浮栅的对准。由于半导体集成工艺的设计尺寸减小,减少最小的光刻特征结构,精确对准的需要变得更挑剔。各种部件的对准也决定半导体产品的制造领域。

自对准是本领域公知。自对准指工序进行涉及一种或多种材料的一个或更多的步骤以至于这些特征结构在该结构进行中自动互相对准。由此,本发明使用自对准技术完成浮栅存储单元型的半导体存储阵列的制造。

在裂栅结构中,都知道在干扰镜像单元中和影响源侧注入闪存单元的编程注入效率中控制栅扮演一个主要的任务。对Lcg(也叫WL(字线)多晶硅长度,该长度是设置在沟道上的控制栅或选择栅的长)好的工艺控制能保证控制栅器件全关断,因此在编程期间能有效地阻止镜像单元的任何干扰(程序干扰)。本发明是实现具有增强的控制栅器件的全关断和有良好的程序干扰特性的自对准快速单元的方法。本发明还涉及这样一种器件。

发明概述

在本发明中,WL(控制/选择栅)多晶硅(poly)长度由光刻工艺控制,与由间隔刻蚀工艺形成的WL多晶硅相比较,该工艺对WL多晶硅长度提供优异的比例能力和控制。因为对光刻工艺的紧密(tight)控制是逻辑工艺的副产品,本发明对WL多晶硅长度提供一个良好的控制,因此在镜像单元中很好的抑制程序干扰。本发明附加的优点是允许在同一晶片上形成不同WL多晶硅长度的单元。

本发明也导致形成一个有基本矩形形状或平面侧壁部分的WL多晶硅,这些使之更容易或有更多的控制能力以形成侧壁隔片和寻址WL-到-BL(位线)&WL-到-源阻块(WL-to-soure block)短路。而且,WL多晶硅被WL沟槽而不是被隔片刻蚀定义。这样,由于绝缘或沟槽氧化-到-有源(trench oxide-to-active)形状使存储单元免于WL-WL短路,WL多晶硅有与形成在WL带上的扁平表面接触更容易的(WL不需要包裹)。本发明进一步表现一个优于现有技术的优点是对临界尺寸的检查它有能力选择以进行“形成之后检查”,亦即在WL尺寸光刻定义之后。如果对临界尺寸WL的控制超出目标,可以检查出错误和该晶片可以重新工作以正确定义这个临界尺寸。

本发明是一个电可编程和可擦除的存储器件阵列,该器件包括第一导电类型的半导体材料衬底,在衬底上形成的间隔隔离区,该隔离区基本上是互相平行的并且在第一方向延伸和每对相邻的隔离区之间的有一个有源区,和多个导电控制栅。每个有源区包括在第一方向延伸的存储一列单元。每一个存储单元包括在具有第二导电类型的衬底内形成的第一和第二间隔端子并且有在其间的衬底内形成的沟道区,第一绝缘层设置在所说的衬底上包括在所说的沟道区之上,导电浮栅设置在所说的第一绝缘层之上并延伸到部分所说的沟道区上和部分第二端子子上,第二绝缘层设置在浮栅上并邻近浮栅,并且有一个允许福勒-诺尔德哈姆隧穿电荷通过的厚度,和导电的控制栅有第一部分和第二部分。第一部分有一个基本平面侧壁部分和处于邻近浮栅的位置并与浮栅绝缘,第二部分基本上是连接基本平面侧壁部分和设置在浮栅上并与浮栅绝缘的一个隔片。

本发明的另一个目标是在半导体衬底上形成浮栅存储单元的半导体存储阵列的自对准方法,每一个存储单元有浮栅、第一端子子、第二端子子、第一端子子和第二端子子之间有沟道区,和控制栅。在本发明的一个方法中,在衬底上形成的多个基本上是互相平行的并在第一方向延伸的间隔隔离区,和每一对邻近的隔离区之间有一个有源区,每个有源区包括在半导体衬底上的第一绝缘材料层和第一绝缘材料层上的第一导电材料层。穿过有源区和隔离区形成多个基本上是相互平行的和在基本上是垂直于第一方向的第二方向上延伸的多个间隔的第一沟道,每个第一沟道使每个有源区内的第一导电材料层暴露。在每个有源区内形成第二绝缘材料层,设置该层在第一导电材料层上并邻近它。用第二导电类型材料填满每个第一沟道以形成第二导电材料的阻块,每个阻块都有一个基本平面侧壁部分,其中对于每个有源区,每个阻块邻近第二绝缘材料层并与衬底绝缘。沿着第二方向形成直接邻近和接近每个基本平面的侧壁部分的导电材料侧壁隔片,其中对于每个有源区,每个隔片是设置在第二绝缘材料层和第一导电材料层上。在衬底内形成多个第一端子子,其中每个有源区内每个第一端子邻近一个阻块。和,在衬底内形成多个第二端子,其中每个有源区内每个第二端子与第一端子间隔并在第一导电材料层下。

本发明的更多目标中的一个,在衬底上形成多个基本上互相平行的并在第一方向延伸的间隔隔离区,每对邻近的隔离区之间有一个有源区。穿过有源区和隔离区形成多个基本上互相平行并在与第一方向基本上垂直的第二方向上延伸的多个间隔的第一沟道。每个有源区内形成第一导电材料层,该层邻近第一沟道和设置在第一绝缘材料层上。在每个有源区内形成第二绝缘材料层,设置该层邻近和覆盖第一导电材料层。用第二导电材料填满每个第一沟道以形成第二导电材料阻块,每个阻块有基本平面侧壁部分,其中对于每个有源区,每个阻块是邻近第二绝缘材料层并与衬底绝缘。沿第二方向形成直接邻近和接近基本平面的侧壁部分的导电材料侧壁隔片。其中对于每个有源区,每个隔片是设置在第二绝缘材料层和第一导电材料层上。在衬底内形成多个第一端子,其中在每个有源区内每个第一端子邻近一个阻块。和,在衬底内形成多个第二端子,其中在每个有源区内,每个第二端子与第一端子隔开并在第一导电材料层下。

通过回顾说明书、权利要求书和附图将明白本发明的其他目标和特点。

附图简述

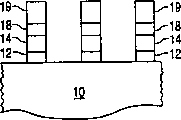

图1A是本发明方法的第一步骤中用来形成隔离区的半导体衬底的俯视图。

图1B是沿1-1线的截面图。

图1C是图1B结构的下一步工序的俯视图,在该工序中形成隔离区。

图1D是图1C结构沿1-1线的截面图,表示在该结构中形成的隔离带。

图1E是图1C结构沿1-1线的截面图,表示可以在半导体衬底内形成两种类型的隔离区,LOCOS或浅沟道。

图2A-2L是图1C结构沿2-2线的截面图,表示在形成裂栅型浮栅存储单元的非易失性存储阵列时图1C所示结构的下一步工艺。

图2M是一个俯视图,表示在形成中的端子互连裂栅型浮栅存储单元的非易失性存储阵列中行线和位线与有源区。

图3A-3D是沿2-2线的截面图,表示在图2A所示结构的第一替换工艺顺序步骤以形成图2B所示的结构。

图4A-4E是沿2-2线的截面图,表示在图2A所示结构的第二替换工艺顺序步骤以形成图2F所示的结构。

图5A-5F是沿2-2线的截面图,表示在图2F所示结构的第三替换工艺顺序步骤的顺序步骤以形成邻近控制栅和上浮栅的氧化隔片。

图6A-6I是沿2-2线的截面图示出图2A-2C所示结构的第四替换工艺顺序步骤以形成裂栅型浮栅存储单元的非易失性存储阵列。

图7A-7S是沿2-2线的截面图示出图2A所示结构的第五替换工艺顺序步骤以形成裂栅型浮栅存储单元的非易失性存储阵列。

优选实施例详述

参考图1A,显示一个半导体衬底10的俯视图,衬底优选P型,是本领域公知的。如图1B所示在衬底上淀积第一绝缘材料层12,例如二氧化硅(氧化物)。用公知的技术例如氧化或淀积(亦即化学气相淀积或CVD)在衬底10上形成第一绝缘层12,形成一个二氧化硅层(以下叫“氧化物”)。在第一绝缘材料层的上部淀积第一多晶硅层14(FG poly)。可以用公知的工艺例如低压CVD或LPCVD在第一绝缘材料层的上部淀积和形成第一多晶硅层14。在多晶硅层14上淀积氮化硅层18(以下叫“氮化”),优选用CVD。在形成隔离的过程中氮化硅层18用来限定有源区。当然,前面所述的所有参数和后面所述的参数,取决于设计尺寸和工艺技术生成。这里所述的是针对0.18微米工艺。然而,所属领域的技术人员能理解本发明既不限于任何特别的工艺技术生成,也不局限于以下所述的任何工艺参数的任何特别的值。

一旦第一绝缘层12,第一多晶硅层14,和氮化硅层18已经形成,在氮化硅层18上涂敷合适的光刻胶材料19和进行掩模步骤以从某些区域(带16)选择性地去掉光刻胶材料。这里光刻胶材料19被去掉,使用标准的刻蚀技术(亦即各向异性刻蚀工艺),在形成在Y方向或列方向的带16内氮化硅18,多晶硅14和下面的绝缘材料12被刻蚀掉,如图1C所示。邻近的带16之间的距离W可以与该工艺所使用的最小的光刻特征一样小。这里光刻胶19没有被去掉,氮化硅18,多晶硅14和下面的绝缘区12仍保留。所得结构如图1D所示。如上所述,隔离区的形成有两种实施例:LOCOS和STI实施例。在STI实施例,刻蚀持续到衬底10内。

进一步加工该结构以去掉剩下的光刻胶19。然后,在区或“沟道”16内形成绝缘材料20a或20b,例如二氧化硅。然后选择性的去掉氮化层18以形成图1E所示的结构。通过公知的LOCOS工艺最终可以在局部场氧化物20a内(亦即通过氧化暴露衬底)形成隔离,或者也可以通过浅沟道工艺(STI)最终用二氧化硅在区20b内(亦即通过淀积一氧化层,接着用化学机械抛光或CMP刻蚀)形成隔离。应该注意到LOCOS形成过程中,在局部场氧化物20a形成过程中对于保护多晶硅14的侧壁可能需要一个隔片。

剩下的第一多晶硅层14和下面的第一绝缘材料层12形成有源区。这样,在这点上,衬底10有有源区和隔离区的交替带,隔离区既可以是由LOCOS绝缘材料20a形成的也可以是由浅沟道绝缘材料20b形成的。尽管图1E都显示了LOCOS区20a和浅沟道区20b的形成,但LOCOS工艺(20a)或浅沟道工艺(20b)只有一种被使用。在优选实施例中,将形成浅沟道20b。浅沟道20b是优选的,因为在更小的尺寸设计时它能更精确地形成。

图1E的结构代表自对准结构,该结构比用非自对准的方法形成的结构更紧凑。形成图1E所示结构的非自对准方法是公知的和常规的,如下。首先在衬底10内形成隔离区20。这些可以通过在衬底10上淀积一层氮化硅层,淀积光刻胶,使用第一掩模步骤构图氮化硅以暴露衬底10的选择部分,然后既可以使用LOCOS工艺也可以使用STI工艺氧化暴露的衬底并进行硅沟道形成和沟道填满。之后,去掉氮化硅,在衬底10上淀积第一二氧化硅层12(以形成栅氧化物)。在栅氧化层12上淀积第一多晶硅层14,然后使用第二掩模步骤构图第一多晶硅层14和去掉选择部分。这样,多晶硅14没有与隔离区20自对准,并且需要第二掩模步骤。而且,附加的掩模步骤要求多晶硅14的尺寸有一个关于隔离区20的对准偏差。应该注意到非自对准方法不利用氮化层18。

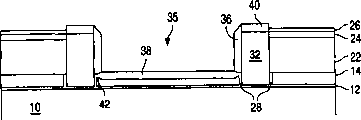

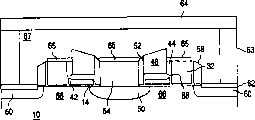

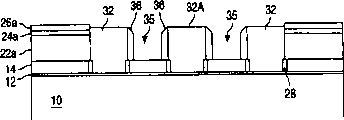

图1E所示的结构既可以使用自对准方法制造也可以使用非自对准方法制造。该结构进一步的工序如下。参考图2A,显示了一个垂直于图1B和1E所示的结构,本发明下一步工序如图。在该结构上形成三个绝缘层。特别,穿过该结构的整个表面淀积厚氮化硅层22,接着淀积焊盘氧化层24(SiO2)。氮化硅层22的厚度接近2000-3000,焊盘氧化层24的厚度接近200-400,然后在氧化层24上淀积上氮化层26,厚度接近800。

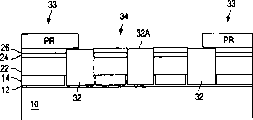

在氮化硅26的上部应用光刻胶进行WL掩模操作。在定义为X或行方向的带内(亦即掩模区)应用掩模步骤。邻近的带之间的距离Z由要制造的器件的需要尺寸决定。该计划的结构可以含有三个“特征结构”,亦即在距离Z内有两个栅和一个“间隔”。在定义的掩模区内去掉光刻胶,亦即行方向上的带,之后使用公知的刻蚀工艺在去掉的光刻胶的带下面选择性的去掉层26、24、22和14。特别,使用氮化各向异性刻蚀工艺去掉氮化硅层26的暴露部分直到观察到焊盘氧化层24,该层作为一个刻蚀停止层,因此使刻蚀工艺停止。接着,进行各向异性氧化刻蚀步骤以去掉暴露的焊盘氧化层24,直到观察到氮化层22,该层作为刻蚀停止层。然后使用另一个氮化各向异性刻蚀工艺去掉氮化硅层22的暴露部分,直到观察到多晶硅层14,该层作为刻蚀停止层,因此使刻蚀工艺停止。接着用各向异性多晶硅刻蚀工艺去掉多晶硅层(FG poly)14的暴露部分,直到观察绝缘层12,该层作为刻蚀停止层。这四个刻蚀工艺结果形成第一沟道30,被距离Z隔开,向下延伸到绝缘层12。最后用一个氧化步骤氧化暴露在第一沟道30内的多晶硅层14的侧面以形成FG氧化侧壁28,和去掉剩下的光刻胶。所得的结构如图2B所示。

然后进行多晶硅淀积步骤,该步骤用多晶硅阻块32填满第一沟道30。淀积在第一沟道30外的过量的多晶硅被刻蚀掉,优选用CMP深刻蚀工艺,留下多晶硅阻块32的上部基本上与氮化层26的上部齐平,如图2C所示,阻块32基本上是矩形。

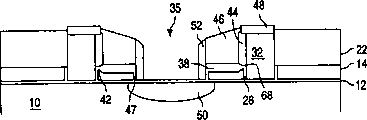

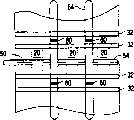

现在参考图2D,一种氮化刻蚀掩模光刻胶PR(可以作为选择使用的硬掩模)放置在该结构上以覆盖交替的中间区33(该区在存储单元邻近的镜像部件之间最终形成间隔),留下交替的中间区34暴露,从而有效地选择在存储单元相匹配的镜象部件内相联系的阻块对32,交替的中间区33将最终用作匹配的存储单元对的隔离和位线连接。应该注意到光刻胶掩模PR精确的位置是不严格的,只要它的边缘是位于阻块32上的某处即可。进行氮化刻蚀工艺(湿或干),接着用氧化刻蚀工艺,和另一种氮化刻蚀工艺,以刻蚀掉暴露的交替中间区34内的氮化层26,焊盘氧化层24,和氮化层22。因为刻蚀剂是选择性的刻蚀剂,多晶硅阻块32和FG多晶硅层14不受影响,留下第二沟道35和暴露在它底部的FG多晶硅层14。对于每一步刻蚀工序,下面的层都作为刻蚀停止层,并且PR掩模阻止在交替的中间区33内任何刻蚀。然后剥离掉刻蚀掩模PR。

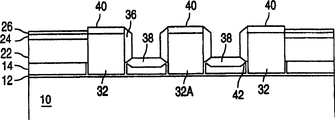

然后沿着面对第二沟道35的多晶硅阻块32的表面形成氮化物隔片36。隔片的形成在本领域是公知的,包括在一个结构的轮廓上淀积材料,接着用各向异性刻蚀工艺,由此从该结构的水平面去掉材料,尽管在该结构垂直方向平面上材料保持大量完好。这样,通过在该结构暴露的平面上淀积一层薄氮化层完成氮化隔片36的形成,接着用一个各向异性刻蚀工艺,例如本领域公知的反应离子刻蚀(RIE),直到氮化层不再覆盖FG多晶硅层14。在这个工序,在氧化硅24上的一些氮化硅26也可能被刻蚀,留下阻块32突出在氮化层26平面上。所得结构如图2E所示。

下一步是氧化工序,氧化暴露的多晶硅表面(亦即第二沟道35内的多晶硅层14,和多晶硅阻块32)以形成在多晶硅层14上的氧化层38和在多晶硅阻块32上的另一氧化层40,如图2F所示。这些氧化步骤导致氧化层38形成一个透镜形状和它的侧边缘连接FG侧氧化壁28以形成一个邻近和在多晶硅层14上的绝缘层,向上突出的尖边缘42形成在位于第二沟道35内的多晶硅层14的每个侧边缘上。由层28/38形成的尖边缘42和绝缘层40的厚度允许福勒-诺尔德哈姆隧穿电荷通过。尽管没有表示出,在氧化层38形成之前可以进行一个可选择的多晶硅刻蚀工艺。这种可选择定制的各向异性多晶硅刻蚀工艺刻蚀掉多晶硅层14的部分上表面,但是在邻近多晶硅阻块32的区域的上表面内留下一个锥形,这些有助于尖边缘42的开始形成。

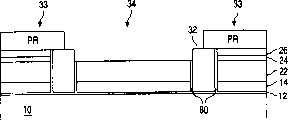

然后剥离掉氮化物隔片36和氮化层26,优选使用湿法刻蚀工艺(或其他各向同性刻蚀工艺)。然后增加WL薄多晶硅隔片44,如图2G所示。WL薄多晶硅隔片44是这样形成的,首先淀积一层薄多晶硅层,接着用一个各向异性刻蚀工艺(亦即RIE),该工艺去掉除了WL薄多晶硅隔片44以外的所有多晶硅薄层。多晶硅阻块32和WL薄多晶硅隔片44形成控制栅(之后描述),控制栅有面对相应的尖边缘42的凹口,但是通过FG氧化侧壁28和氧化层38与它绝缘。然后在部分氧化层38上形成厚绝缘内侧壁隔片46,并且向上面对WL薄多晶硅隔片44。厚绝缘内侧壁隔片46既可以用氧化淀积步骤的氧化物形成,也可以用氮化淀积步骤的氮化物形成,接着用各向异性刻蚀工艺(亦即RIE)。通过使用氮淀积和刻蚀工艺形成图2G中所示结构,该结构也是上层26中剩下的氮化物去掉之后的结果。

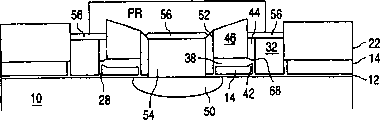

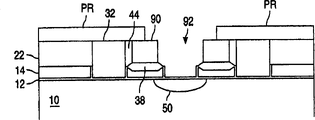

然后进行各向异性刻蚀工艺以去掉氧化层24,38和40的暴露部分。接着用多晶硅刻蚀工艺,去掉在第二沟道35的底部暴露在隔片46之间的部分多晶硅。然后进行氧化刻蚀步骤,去掉第二沟道35的底部暴露的部分绝缘层12,直到观察到衬底10。然后进行氧化工序,氧化暴露在第二沟道35内的层14的侧面以形成一个氧化区47。通过氧化淀积和RIE刻蚀工艺也能形成这些同样的区,参照下面图5A-5F所进行的描述。氧化工序这里也在多晶硅阻块32的上表面形成一个氧化层48,和在第二沟道35的底部沿着衬底10的表面重新形成氧化层12。然后进行适当的离子注入穿过该结构的整个表面。这里该离子有足够的能量以穿透第一二氧化硅层12,然后在衬底10内形成第一区(第二端子)50。在所有其他区域,离子被氮化层22,氧化层48,多晶硅阻块32和氮化侧壁隔片46吸收,在那里它们不受影响。然后通过淀积氮化物,在第二沟道35的侧边上形成内隔片52。接着通过各向异性氮化物刻蚀工艺(亦即RIE)从除了第二沟道35的侧壁之外的所有表面去掉氮化物。尽管图示的是氮化物,其他类型的材料,例如氧化物也可以用来形成隔片52。所得结构如图2H所示。

在图2H的结构上进行氧化刻蚀工艺,去掉暴露的氧化层48向下到多晶硅阻块32,多晶硅阻块32形成一个刻蚀停止层。去掉第二沟道35内的氧化层12向下到硅衬底,硅衬底形成刻蚀停止层。然后进行多晶硅淀积步骤,该步骤用多晶硅阻块54填满第二沟道35,多晶硅也既可以通过就地的方法和也可以通过常规注入适当掺杂。淀积在第二沟道35外的过量的多晶硅被刻蚀掉,优选CMP深刻蚀工艺,留下多晶硅阻块54的上部与多晶硅阻块32的上部相齐平。如图2I所示。然后进行氧化步骤以氧化多晶硅阻块54和多晶硅阻块56的上表面,这样形成氧化层56。所得结构如图2I所示。

在该结构上放置氮化光刻胶刻蚀掩模PR,至少覆盖氮化侧壁隔片46,但是露出氮化层22的剩下部分,如图2J所示。然后使用氮化刻蚀工艺以去掉氮化层22的剩下部分,露出多晶硅层14(第二沟道35外),该层作为刻蚀停止层。接着多晶硅刻蚀工艺去掉多晶硅阻块对32外的多晶硅层14的剩下部分。然后去掉刻蚀掩模PR,留下如图2K所示的结构。

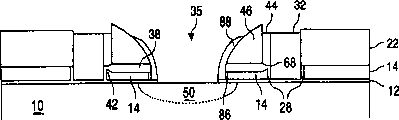

为了完成存储单元,邻近多晶硅阻块32形成氮化侧壁隔片58,首先通过用热氧化或CVD形成一氧化层以覆盖/密封多晶硅阻块32,接着通过淀积一氮化层覆盖该结构,并进行各向异性氮化刻蚀。然后使用离子掺杂(亦即N+)以在衬底内形成第二区(亦即第一端子)60,所形成的方法与形成第一区50相同。紧接着氧化刻蚀去掉邻近隔片58和暴露在衬底10上的层12和氧化层56。然后形成金属淀积步骤,使用导电金属如钨、钴、钛、镍、铂和钼,该结构被退火,允许热金属流入和渗透到衬底10露出的上部以形成金属化硅区62,和流入和渗透到多晶硅阻块32/54露出的上部以形成金属化硅区65(该区在行方向上促进导电)。衬底10上的金属化硅区62可以叫自对准硅化物(salicide),因为它通过隔片58自对准第二区60。在多晶硅阻块32/54上的金属化硅区65通常叫多晶硅-金属硅化物(polycide)。通过金属刻蚀工艺去掉淀积在剩下结构上的金属。钝化,例如使用BPSG67覆盖整个结构。进行掩模步骤以定义自对准硅化物区(salicide)62上的刻蚀区。在掩模区中BPSG67被选择性地刻蚀向下到自对准硅化物区(salicide)62,通过金属淀积和平面化深刻蚀工艺用导电金属63填满所得沟道。自对准硅化物(salicide)层62促进导体63和第二区60之间导电。通过在BPSG 67上掩模金属增加位线64,以连接存储单元列上的所有导体63。最终的存储单元结构如图2L所示。第一和第二区50/60形成每一个单元的源区和漏区(本领域的技术人员都知道在操作过程中源和漏可以互换)。每个单元的沟道区66是源和漏50/60之间的衬底内的一部分。多晶硅阻块32和多晶硅隔片44组成控制栅,和多晶硅层14组成浮栅。控制栅32有一侧面,对准第二区60的边缘,并且设置在部分沟道区66上。部分延伸到浮栅14上(浮栅14的尖边缘延伸到凹口68内)的控制栅32/44(这里多晶硅阻块32附着多晶硅隔片44)的拐角处形成凹口68。浮栅14覆盖部分沟道区66,由控制栅32/44部分交迭在一端,它的另一端部分交迭第一区50。如图2L所示,本发明的工艺形成彼此镜像的存储单元对。通过氮化内隔片52和在浮栅14的一端的边上的氧化层,该镜像存储单元是彼此绝缘的。

参考图2M,显示一个所得结构的俯视图和到第二区的位线64和在X或行方向延伸的控制线32和最终连接衬底10内的第一区的源线的连接。尽管源线54(本领域的技术人员都知道“源”和“漏”可以互换)在整个行方向上与衬底10接触,亦即接触有源区也接触隔离区,源线54仅仅电连接衬底10内的第一区50。此外,两个邻近的存储单元之间连接到“源”线54的每个第一区50是共享的。同样地,来自存储单元不同的镜像部件相邻近的存储单元之间,连接到位线64的第二区60是共享的。

结果是裂栅型的多个非易失性存储单元有浮栅14、是一个隔片控制栅32,该控制栅直接邻近浮栅但是与浮栅分开并连接一个沿着行的长度方向延伸连接同一列上其他存储单元的控制栅的基本矩形形状结构、沿行方向延伸,连接同一行方向上的存储单元对的第一区50的源线54、以及沿列或Y方向延伸,连接同一列方向上的存储单元的第二区60的的位线64。控制栅、浮栅、源线、位线的形成所有的都是自对准。非易失性存储单元是有浮栅的裂栅型的一种以控制栅隧穿,如美国专利US5572054所述,这里引入用来参考所谈到的非易失性存储单元的操作和形成的阵列。

图3A-3D表示形成图2B所示结构的一种替代工艺。上面的优选实施例所描述的是使用光刻析象工艺在层26,24,22和14内确定第一沟道30。但是,可以从图2A所示的结构开始用一种亚微细光刻工艺代替以形成第一沟道30,第一沟道的宽度比通过掩模步骤原始确定的更小。从图2A所示的结构开始,在氮化层26上形成或淀积两个附加层70和72。在图3A所示的实施例中,层70是多晶硅层,层72是氧化层。下一步,在氧化层72的上部应用光刻胶进行WL掩模操作。掩模步骤应用于定义为X或行方向上的带上。在确定的选择区中去掉光刻胶,即行方向的带,氧化刻蚀工艺之后接着用多晶硅刻蚀工艺选择性地去掉暴露于带内的氧化层72和多晶硅70以确定第一沟道30。接着用WL照相剥离步骤去掉光刻胶。然后在第一沟道30的侧面上形成隔片76,隔片76既可以是由氧化物也可以是由多晶硅形成。在图3B所示的实施例中是用一般的淀积工艺形成多晶硅隔片76,因此,在该结构上淀积一层多晶硅,使用反应离子刻蚀去掉除了隔片76以外的多晶硅。最后,在隔片76之间进行氮化刻蚀以去掉第一沟道30底部的氮化层26,所得结构如图3B所示。

下一步,进行RIE氧化刻蚀步骤以去掉氧化层72,和暴露在第一沟道30底部的部分氧化层24,直到观察到氮化层22。然后,进行厚氮化RIE刻蚀步骤以去掉暴露第一沟道30底部的部分氮化层22,直到观察到多晶硅层14,如图3C所示。接着用多晶硅RIE刻蚀去掉多晶硅层70、隔片76和在第一沟道30底部的部分暴露的多晶硅14,直到观察到氧化层12。最后,进行氧化步骤以氧化暴露在第一沟道30内的多晶硅14的侧面以形成FG氧化侧壁28,所得结构如图3D所示,该图与图2B所示的结构是一样的,但是第一沟道30的宽度比图2B小。隔片76的使用允许形成的第一沟道30的宽度比使用掩模步骤最初定义第一沟道的上部的宽度小,这就是为什么该工艺是指亚微细光刻工艺。

图4A到4E表示形成图2F所示结构的一个替代工艺,除了附加一个衬在多晶硅阻块32外侧的氧化层(如图4E所示)。在上面所述的优选实施例中,最后进行步骤是氧化步骤所得结构如图2B所示。氧化步骤开始之前,接着可以用以下的替代工艺代替上面所述的这些步骤,参考图2C-2F。代替形成氧化侧壁28的氧化步骤是进行HTO氧化淀积以形成沿第一沟道的侧壁的高延伸的氧化侧壁80,如图4A所示。然后进行多晶硅淀积步骤,用多晶硅阻块32填满第一沟道30,刻蚀掉淀积在第一沟道30外过量的多晶硅,优选使用CMP深刻蚀工艺,留下多晶硅阻块32的上部基本上与氮化层26的上部齐平,如图4B所示。

现在参考图4C,在该结构上放置氮化刻蚀掩模PR(可以选择使用的硬掩模)以覆盖交替的中间区33(该区最终在相邻近的存储单元镜像部件之间形成间隔),留下交替区34暴露,从而有效地选择在存储单元相匹配的镜象部件内相联系的阻块对32,对于选择的匹配的存储单元对来说交替的中间区33将最终用作隔离和位线连接。然后,进行氮化刻蚀工艺(湿或干),接着通过氧化刻蚀工艺以刻蚀掉暴露在交替中间区34内的氮化层26和焊盘氧化层24,留下第二沟道35和暴露在它底部的氮化层22。对每个刻蚀工艺,下面的层作为刻蚀停止层,PR掩模阻止在交替中间区33内的任何刻蚀,所得结构如图4C所示。

下一步,进行厚氮刻蚀工艺以刻蚀掉从第二沟道35的底部暴露的氮化层22,直到观察到多晶硅层14,如图4D所示。然后刻蚀掩模PR被剥离掉。然后沿着面对第二沟道35的多晶硅阻块32的表面形成氮化隔片36。通过在该结构的暴露表面淀积一薄的氮化层完成氮化隔片36的形成,接着用一个各向异性刻蚀工艺,例如本领域公知的反应离子刻蚀(RIE),直到氮化层不再覆盖FG多晶硅层14。下一步是氧化工序,氧化暴露的多晶硅表面(亦即在第二沟道35内的多晶硅层14和多晶硅阻块32)以形成覆盖多晶硅层14的氧化层38和覆盖多晶硅阻块32的另一氧化层40,如图4E所示。这些氧化步骤导致氧化层38形成一个透镜形状和它的侧边缘连接FG侧氧化壁28以形成一个邻近和覆盖多晶硅层14的绝缘层,向上突出的尖边缘42形成在位于第二沟道35内的多晶硅层14的每个侧边缘上。由尖边缘42和绝缘层形成的厚度允许通过福勒-诺尔德哈姆隧穿电荷。尽管没有表示出,在氧化层38形成之前可以进行一个可选择的多晶硅刻蚀工艺,这种可选择定制的各向异性多晶硅刻蚀工艺刻蚀掉多晶硅层14的部分上表面,但是在邻近多晶硅阻块32的区域的上表面内留下一个锥形,这样有助于进行尖边缘42的开始形成。然后从图2F所论述的优选实施例开始进行剩下的工序步骤,以完成最终结构的形成。

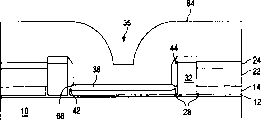

图5A-5F表示形成存储单元替换工艺,该存储单元有隔片46,邻近控制栅隔片44和在浮栅14上,用氧化代替氮化。在图2G所示的优选实施例中,通过在该结构上淀积一厚氮化层形成隔片46,接着进行各向异性氮化刻蚀步骤。然而,隔片可以使用如下的步骤氧化而成。薄多晶硅隔片44形成之后(看图2G),在该结构上淀积厚氧化层84,如图5A所示。接着用各向异性刻蚀工艺(RIE)去掉除了那里形成内侧壁(氧化)隔片46之外的氧化层84。氧化层24和40也被去掉,第二沟道35中央的部分氧化层38也一样被去掉。所得结构如图5B所示。

然后进行多晶硅RIE刻蚀工艺,去掉第二沟道35底部暴露的部分多晶硅层14。这些多晶硅刻蚀工艺也从多晶硅阻块32和多晶硅隔片44的上部的去掉一小部分,所得结构如图5C所示。

下一步,氧化暴露的多晶硅以在浮栅14开始的内侧壁上形成氧化层86。接着用合适的离子注入穿过该结构的整个表面。这里该离子有足够的能量以穿透第一二氧化硅层12,然后在衬底10上形成第一区(第二端子)50,在其他所有区域,离子被吸收,不受影响。既可以通过氧化淀积也可以通过氮化淀积沿着第二沟道35的侧壁形成内侧壁隔片88。在图5D所示的实施例中,内侧壁88是通过氧化淀积形成的,接着用各向异性刻蚀去掉除了内侧壁88之外的淀积的氧化物。这个氧化刻蚀步骤也去掉在第二沟道35底部暴露的氧化层12,以暴露出衬底10,所得结构如图5D所示。

然后进行多晶硅淀积步骤,用多晶硅阻块54填满第二沟道35。多晶硅是适当掺杂,既可以通过就地的方法,也可以通过常规的注入法。淀积在第二沟道35外过量的多晶硅被刻蚀掉,优选使用CMP深刻蚀工艺,留下多晶硅阻块54的上部与多晶硅阻块32和多晶硅隔片44的上部相齐平,如图5E所示。然后进行氧化步骤以氧化多晶硅阻块54和32的上表面和多晶硅隔片44,这样形成氧化层56。所得结构如图5E所示。

使用氮化刻蚀工艺去掉氮化层22厚的剩下部分以暴露出多晶硅层14(第二沟道35外),该层作为刻蚀停止层。接着用多晶硅刻蚀工艺以去掉经选择的多晶硅阻块对32外面的多晶硅层14的剩下部分。所得结构如图5F所示,该图对应于图2K所示的优选实施例的结构。可以使用优选实施例剩下的步骤来完成最终的存储单元结构。

图6A-6I表示形成存储单元的镜像部件的一种替换工艺。除了每对镜像存储单元形成三个第一沟道30代替两个外,该替换工艺开始与图2A-2C所描述的步骤一样。这样每对存储单元形成三个多晶硅阻块,附加的阻块与32A相同,如图6A所示。

现在参考图6A,在该结构上放置氮化刻蚀掩模光刻胶PR(一种可以作为选择使用的硬掩模)以覆盖交替的中间区33(在邻近的存储单元镜像部件之间最终形成间隔),留下交替的中间区34暴露,从而有效地选择在存储单元相匹配的镜象部件中相联系的阻块对32。交替的中间区33将最终用作匹配的存储单元对的隔离和位线连接。应该注意到光刻胶掩模PR精确的位置是不挑剔的,只要它的边缘位于阻块32上的某处即可。进行氮化刻蚀工艺(湿或干),接着用氧化刻蚀工艺,和另一种氮化刻蚀工艺,以刻蚀掉暴露在交替的中间区34内的氮化层26,焊盘氧化层24,和氮化层22。因为刻蚀剂是选择性的刻蚀剂,多晶硅阻块32和FG多晶硅层14不受影响,每个存储单元对留下一对第二沟道35,和暴露在它底部的FG多晶硅层14。对于每一个刻蚀工序,下面的层都作为刻蚀停止层,并且PR掩模阻止交替的中间区33内的任何刻蚀。然后剥离掉刻蚀掩模PR。

然后沿着面对第二沟道35的多晶硅阻块32和32A的表面形成氮化隔片36。通过在该结构的暴露面上淀积一薄氮化层完成氮化隔片36的形成,接着用各向异性刻蚀工艺,例如本领域公知的反应离子刻蚀(RIE),直到氮化层不再覆盖第二沟道35中央的FG多晶硅层14。在该工艺,氧化硅24顶上的一些氮化硅26也可能被刻蚀,留下突出在氮化层26的平面上的阻块32和32A。所得结构如图6B所示。

下一步是氧化工序,该工序氧化暴露的多晶硅表面(亦即第二沟道35内的多晶硅层14,和多晶硅阻块32和32A)以在多晶硅层14上形成的氧化层38和在多晶硅阻块32和32A上形成的另一氧化层40,如图6C所示。这些氧化步骤导致氧化层38形成一个透镜形状和它的侧边缘连接FG侧氧化壁28以形成一个邻近和覆盖多晶硅层14的绝缘层,向上突出的尖边缘42形成在位于第二沟道35内的多晶硅层14的每个侧边缘上。尖边缘42和由层28/38形成的绝缘层40的厚度由允许福勒-诺尔德哈姆隧穿电荷通过。尽管没有表示出,在氧化层38形成之前可以进行一个可选择的多晶硅刻蚀工艺,这种可选择定制的各向异性多晶硅刻蚀工艺刻蚀掉多晶硅层14的部分上表面,但是在邻近多晶硅阻块32的区域的上表面内留下一个锥形,这样有助于尖边缘42的开始形成。

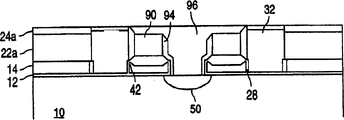

然后剥离掉氮化隔片36和氮化层26,优选使用湿法刻蚀工艺(或其他各向同性刻蚀工艺)。然后增加WL薄多晶硅隔片44,如图6D所示。WL薄多晶硅隔片44是这样形成的,首先淀积一层薄多晶硅层,接着用一个各向异性刻蚀工艺(亦即RIE),该工艺去掉除了WL薄多晶硅隔片44以外的所有薄多晶硅层,连同多晶硅层24。多晶硅阻块32和部分WL薄多晶硅隔片44形成控制栅(之后描述),控制栅有面对相应的尖边缘42的凹口,但是通过由FG氧化侧壁28和氧化层38形成的绝缘层从那里绝缘。然后进行绝缘淀积步骤如氧化淀积,该步骤用氧化物阻块90填满第二沟道35。刻蚀掉第二沟道35外过量的氧化淀积,优选用CMP深刻蚀工艺,留下氧化物阻块90的上部与多晶硅阻块32和32A和WL多晶硅隔片44相齐平。所得结构如图6D所示。

在该结构上放置多晶硅光刻胶刻蚀掩模PR,每个存储单元对仅留下中间的多晶硅阻块32A暴露,多晶硅隔片44直接邻近中间的多晶硅阻块32A。如图6E所示。然后使用多晶硅刻蚀工艺以去掉中间的多晶硅阻块32A和邻近的多晶硅隔片44,形成向下延伸到绝缘层12的沟道92。然后进行适当的离子注入穿过该结构的整个表面,该离子有足够的能量以穿透沟道92内的第一二氧化硅层12,然后在衬底10内形成第一区50(亦即第二端子)。在其他所有区域,离子被刻蚀掩模或氧化层,多晶硅层或氮化层吸收,在那里它们不受影响。所得结构如图6E所示。

下一步,刻蚀掩模PR被剥离掉,沟道92的侧壁上形成绝缘隔片94。绝缘隔片94优选是通过在该结构上淀积一层氧化层,和进行各向异性刻蚀以去掉除了隔片94之外淀积的氧化层形成的氧化隔片,,沟道92底部的氧化层12也被去掉以使衬底暴露。然后进行多晶硅淀积步骤,该步骤用多晶硅阻块96填满沟道92,多晶硅也可以通过就地的方法或常规的注入法适当掺杂。淀积在沟道92外的过量的多晶硅被刻蚀掉,优选用CMP深刻蚀工艺,留下多晶硅阻块32和96的上部和多晶硅隔片44稍低于氮化层22和氧化阻块90的上表面。所得结构如图6F所示。

然后进行氧化步骤以氧化多晶硅阻块32和96和多晶硅隔片44上表面,这样形成氧化层56,如图6G所示。接着用氮化刻蚀去掉氮化层22的剩下部分以使多晶硅层14暴露(多晶硅阻块32外),该层作为刻蚀停止层。接着用多晶硅刻蚀工序去掉多晶硅阻块对32外的多晶硅层14的剩下部分。所得结构如图6H所示。

为了完成存储单元,邻近多晶硅阻块32形成氮化侧壁隔片58,首先通过用热氧化或CVD形成一氧化层以覆盖/密封多晶硅阻块32,接着通过在该结构上淀积一氮化层,并进行各向异性氮化刻蚀。然后使用离子注入(亦即N+)以在衬底内形成第二区(亦即第一端子)60,与形成第一区50相同的方法。使用氧化刻蚀以去掉氧化层56,氧化物阻块90和隔片94的上部,和邻近隔片58的氧化层12以使衬底10暴露。接着用多晶硅刻蚀去掉多晶硅阻块32和96部分上部,和多晶硅隔片44。然后形成金属淀积步骤,使用导电金属例如钨,钴,钛,镍,铂,钼等。该结构被退火,允许热金属流入和渗透到衬底10露出的上部以形成金属化硅区(salicide)62,和流入和渗透到多晶硅阻块32/96露出的上部以形成金属化硅(polycide)区65(该区在行方向上促进导电)。淀积在剩下结构上的金属通过金属刻蚀工艺被去掉。衬底10上的金属化硅区(salicide)62通过隔片58自对准第二区60。使用钝化例如BPSG67,以覆盖整个结构。进行掩模步骤以定义金属化硅区(salicide)62上的刻蚀区。在掩模区的BPSG 67是选择性的向下刻蚀到金属化硅区(salicide)62,用金属淀积的导体金属63和平面化深刻蚀工艺填满所得沟道。金属化硅区(salicide)62促进导体63和第二区60之间导电。通过在BPSG67上掩模金属增加位线64,连接存储单元列上的所有导体63。最后的存储单元的结构如图6I所示。对于每个单元第一和第二区50/60形成源区和漏区(本领域的技术人员都知道在操作过程中源和漏可以互换)。对于每个单元,沟道区66是源和漏50/60中间的部分衬底。多晶硅阻块32和多晶硅隔片44组成控制栅,多晶硅层14组成浮栅。控制栅32有一侧面对准第二区60的边缘,并且设置在部分沟道区66上。在部分延伸到浮栅14上(浮栅14的尖边缘42延伸到凹口68内)的控制栅32/44(多晶硅阻块32附着多晶硅隔片44)的拐角处形成凹口68。浮栅14覆盖部分沟道区66,由控制栅32/44部分交迭在一边,和另一边部分交迭第一区50。如图6I所示,本发明的工艺形成彼此镜像的存储单元对。通过氮化隔片94和浮栅14一端的氧化层28该镜像存储单元是彼此绝缘。

这个实施例是唯一的,尽管在该实施例中浮栅的长度还是由光刻步骤所定义,浮栅多晶硅被刻蚀掩模保护,代替浮栅多晶硅暴露于掩模开口。WL掩模同时确定字线、浮栅和源的尺寸。浮栅的长度由照相光刻步骤决定代替隔片刻蚀工艺,并且比前者更可控制。

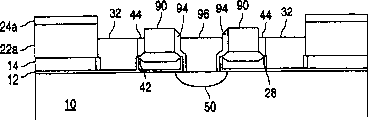

图7A-7I表示与图6A-6I所示工艺十分相似的一种替代工艺,但是进一步包括自对准接触图形(SAC)。这个替代工艺开始除了绝缘层22a和26a是氧化形成代替氮化形成,绝缘层24a是氮化形成代替氧化形成之外,其余与图2A所描述的步骤一样,如图7A所示。层24a和26a是可选的,但是包括在所述的实施例中。

在氧化层26a的上部应用光刻胶进行WL掩模操作。在定义为X或行方向的带内(亦即掩模区)应用掩模步骤。在定义的掩模区去掉光刻胶,亦即行方向上的带内,之后在去掉的光刻胶的带下面使用公知的各向异性氧化,多晶硅和氮化刻蚀工艺选择性地去掉绝缘层26a、24a和22a,多晶硅14也被去掉,直到观察到绝缘层12,该层作为刻蚀停止层。这些刻蚀工艺导致每对镜像存储单元形成三个第一沟道30。接着进行氧化步骤,氧化暴露在第一沟道30和32A内的多晶硅层14的侧边以形成FG氧化侧壁28。然后去掉剩下的光刻胶。所得结构如图7B所示。

然后进行多晶硅淀积步骤,对于每对镜像存储单元用多晶硅阻块填满外面的两个第一沟道30,中间的第一沟道30用多晶硅阻块32A填满。淀积在第一沟道30外过量的多晶硅被刻蚀掉,优选使用CMP深刻蚀工艺,使用上氧化层26a作为CMP刻蚀停止层,留下多晶硅阻块32和32A上部与氧化层26a基本上齐平。阻块32和32A基本上是矩形,如图7C所示。然后进行多晶硅深刻蚀步骤,以刻蚀掉多晶硅阻块32和32A的上部,如图7D所示。

现在参考图7E,一种氧化刻蚀掩模光刻胶PR(一种可以选择性使用的硬掩模)放置在该结构上以覆盖交替的中间区33(该区在存储单元邻近的镜像部件之间最终形成间隔),留下交替的中间区34暴露,从而有效地选择存储单元相匹配的镜象部件内相联系的阻块对32,交替的中间区33将最终用作相匹配的存储单元对的隔离和位线连接。应该注意到光刻胶PR的精确位置是不挑剔的,只要它的边缘是位于阻块32上的某处即可。进行氧化刻蚀工艺,接着用氮化刻蚀工艺(湿或干),和另一种氧化刻蚀工艺,以刻蚀掉暴露在交替的中间区34内的氧化层26a、氮化层24a、和氧化层22a。因为刻蚀剂是选择性的刻蚀剂,多晶硅阻块32和32A以及FG多晶硅层14不受影响,每对存储单元留下一对第二沟道35和暴露在它底部的FG多晶硅层14。对于每一步刻蚀工序,下面的层都作为刻蚀停止层,并且PR掩模阻止在交替的中间区33的任何刻蚀。所得结构如图7E所示。

然后剥离掉刻蚀掩模PR。然后沿着组成第二沟道35的侧壁的多晶硅阻块32和32A的表面形成氮化隔片36。形成氮化隔片36是通过在该结构暴露的表面上淀积一层薄氮化层,接着通过一个各向异性刻蚀工序,例如本领域所公知的反应离子刻蚀(RIE),直到氮化层不再覆盖第二沟道35中间的FG多晶硅层14。所得结构如图7F所示。

下一步是氧化工序,氧化暴露的多晶硅表面(亦即第二沟道35内的多晶硅层14,多晶硅阻块32和32A)以在多晶硅层14上形成的氧化层38和在多晶硅阻块32和32A上形成的另一氧化层40,如图7G所示。该氧化步骤导致氧化层38形成一个透镜形状和它的侧边缘连接FG侧氧化壁28以形成一个邻近和覆盖多晶硅层14的绝缘层,向上地突出的尖边缘42形成在位于第二沟道35内的多晶硅层14的每个侧边缘上。尖边缘42和由层28/38形成的绝缘层的厚度由允许福勒-诺尔德哈姆隧穿电荷通过。尽管没有表示出,在氧化层38形成之前可以进行一个可选择的多晶硅刻蚀工艺,这种可选择定制的各向异性多晶硅刻蚀工艺刻蚀掉多晶硅层14的部分上表面,但是在邻近多晶硅阻块32的区域的上表面内留下一个锥形,这样有助于开始形成尖边缘42。

然后剥离掉氮化隔片36,优选使用湿法刻蚀工艺(或其他各向同性刻蚀工艺)。然后增加WL薄多晶硅隔片44,如图7H所示。WL薄多晶硅隔片44是这样形成的,首先淀积一层薄多晶硅层,接着用一个各向异性刻蚀工艺(亦即RIE),该工艺去掉除了WL薄多晶硅隔片44以外的所有多晶硅薄层。多晶硅阻块32和部分WL薄多晶硅隔片44形成有面对相应的尖边缘42的凹口的控制栅(之后描述),但是通过FG氧化侧壁28和氧化层38形成一绝缘层从那里绝缘。然后进行绝缘淀积步骤,例如氧化物淀积,用氧化物阻块90填满第二沟道35,和形成覆盖该结构的厚氧化层91。所得结构如图7H所示。

淀积在第二沟道35外(氧化层91)的过量的氧化物被刻蚀掉,连同氧化层26a和大部分氧化层40,优选使用CMP深刻蚀工艺,留下氧化物阻块90的上部与氮化层24a和氧化层40的上部相齐平(图7I),然后使用氧化深刻蚀步骤以去掉多晶硅阻块32上的氧化层40,和去掉氧化阻块90的上部。所得结构如图7J所示。

在该结构上放置多晶硅光刻胶刻蚀掩模PR,每对存储单元仅留下中间的多晶硅阻块32A暴露,和多晶硅隔片44直接邻近中间的多晶硅阻块32A,如图7K所示。然后,用多晶硅刻蚀工艺以去掉中间的多晶硅阻块32A和邻近的多晶硅隔片44,形成向下延伸到绝缘层12的沟道92。进行合适的离子注入穿过该结构的整个表面。该离子有足够的能量穿透沟道92内的第一二氧化硅层12,然后在衬底10内形成第一区50(亦即第二端子)。在其他区,离子被刻蚀掩模或氧化层吸收,在那里它们不受影响。所得结构如图7K所示。

下一步,刻蚀掩模PR被刻蚀掉,在沟道92的侧壁上形成绝缘隔片94,绝缘隔片94优选是氧化隔片,通过在该结构上淀积一层薄氧化层,和进行各向异性刻蚀以去掉除了隔片94,氧化物阻块90的上部之外淀积的氧化层,沟道92底部的氧化层12也被刻蚀掉以露出衬底。然后进行多晶硅淀积步骤,该步骤用多晶硅阻块96填满沟道92,多晶硅阻块96延伸到氧化阻块90上和多晶硅阻块32上。多晶硅既可以通过就地的方法也可以通过常规的掺杂法适当掺杂。淀积在沟道92外的过量的多晶硅被刻蚀掉,优选用CMP深刻蚀工艺,留下多晶硅阻块96和32的上部与氮化层24a的上表面齐平。所得结构如图7L所示。然后进行多晶硅深刻蚀工序以去掉多晶硅阻块32和96的上部,和多晶硅隔片44。留下氧化阻块90和氧化隔片94以使上面的多晶硅32/96的表面和多晶硅44隔片上很好延伸,如图7M所示。

然后通过在该结构上淀积一种金属例如钨,钴,钛,镍,铂或钼等在多晶硅阻块32和96的上部形成一层金属化多晶硅(polycide)层100。该结构被退火,允许热金属流入和渗透到多晶硅阻块32/96暴露的上部以形成促进行方向导电的金属化多晶硅(polycide)区100。淀积在剩下结构上的金属通过金属刻蚀工艺去掉。然后在该结构上淀积厚氮化层102,如图7N所示。进行氮化深刻蚀工艺,例如CMP,以从氧化层22a的上部去掉氮化层24a和102,和使氮化层102剩下的上表面与氧化层22a的上表面匹配。所得结构如图7O所示。

使用各向异性氧化刻蚀工艺以从镜像单元部件的每个侧面去掉氧化层22a剩下的暴露部分,以露出多晶硅层14(多晶硅阻块32外),该层作为刻蚀停止层。接着多晶硅刻蚀工艺去掉多晶硅阻块对32外的多晶硅层14剩下的暴露部分。然后使用可选的氧化刻蚀工艺去掉多晶硅阻块对32外的氧化层12剩下的暴露部分。所得结构如图7P所示。

为了完成存储单元,邻近多晶硅阻块32形成氮化侧壁隔片58,首先通过用热氧化或CVD形成氧化层104以覆盖/密封多晶硅阻块32。然后在该结构上淀积一氮化层,并进行各向异性氮化刻蚀以去掉除隔片58外的所有的氮化物。进行薄氧化刻蚀以去掉薄氧化层104的任意暴露部分。所得结构如图7Q所示。

然后使用离子注入(亦即N+)以在衬底内形成第二区(亦即第一端子)60,所形成的方法与第一区50相同。然后通过在该结构上淀积一种金属,在衬底10的上部邻近侧壁隔片58形成金属化硅(salicide)层62。该结构被退火,允许热金属流入和渗透到衬底10露出的上部以形成金属化硅区62。通过金属刻蚀工序去掉淀积在剩下结构上的金属。衬底上的金属化硅区62通过隔片58自对准第二区60。所得结构如图7R所示。

钝化,使用例如BPSG67以覆盖整个结构。进行掩模步骤以定义自对准硅化物(salicide)区62上的刻蚀区。BPSG 67在掩模区选择性刻蚀以产生一个在相邻近的存储单元对之间形成的自对准硅化物(salicide)区62的正上方并比自对准硅化物区62宽的接触开口。在刻蚀过程中氮化层102用作保护多晶硅阻块32和多晶硅层100。然后通过金属淀积和平面化深刻蚀用导体金属63填满接触开口,由此,存储单元对的邻近部件的氮化隔片58之间的整个区域用淀积的金属填满以形成接触导体63,接触导体63通过氮化隔片58自对准salicide区62(亦即自对准接触图形或SAC),导体63和第二区60之间的自对准硅化物(salicide)区62促进导电。通过在BPSG 67上覆盖金属掩模增加位线64,以连接存储单元列上的所有导体63。最后的存储单元结构如图7S所示。

自对准接触点图形(SAC)除去存储单元对的邻近部件之间对于最小间隔需要的重要约束。特别,尽管图7S图示的接触区(和这里的导体63)优选在自对准硅化物(salicide)区62的中央上,实际上形成没有任何不希望的相对于自对准硅化物(salicide)区62的水平移动的接触开口是非常困难的。如果该水平移动变得非常大足以阻止接触63填满隔片58之间的间隔,可能会发生一个致命的连接。用一个非自对准接触点图形,例如图2L图示的实施例所使用的,BPSG形成以前该结构上没有氮化保护层,如果接触63移动到金属化-多晶硅(polycide)层65和多晶硅阻块32上并形成在上面,可能发生电短路。为了防止在非自对准接触图形内电短路,接触开口离氮化隔片58足够远以至于在接触区即使有最大可能的移动,它们也不会延伸到氮化隔片58或在其上面。为了在镜像单元对的邻近部件之间提供一个足够的容差距离,对于图2L所示的实施例这些当然产生一个关于隔片58之间的最小距离的约束

图7S的实施例使用SAC,通过在BPSG下面使用一个保护材料(氮化层102)层消除这些约束。用这个保护层,形成在BPSG内的接触开口有一个足够的宽度以保证接触开口和自对准硅化物(salicide)区62重叠,即使在形成过程中接触开口有一个显著的水平移动。氮化层102允许在多晶硅阻块32或多晶硅层100上形成部分接触63,其间没有任何短路。宽的接触开口保证接触63完全填满隔片58之间的窄间隔,并且与自对准硅化物(salicide)区62有好的电接触。这样,隔片58之间接触区的宽度可以最小化,允许整个单元尺寸的比例减小。应该注意到SAC可以与这些应用中图例的任何方法一起使用。

如图7S所示,第一区和第二区50/60形成每个单元的源区和漏区(本领域的技术人员都知道在操作过程中源和漏可以互换)。每个单元的沟道区66是源和漏50/60中间的衬底的一部分。多晶硅阻块32和多晶硅隔片44组成控制栅,和多晶硅层14组成浮栅。控制栅32/44有一侧面对准第二区60的边缘,并且设置在部分沟道区66上。在控制栅的拐角处形成一个凹口68,它部分延伸到浮栅14上(浮栅14的尖边缘42延伸到凹口68内)。浮栅14在部分沟道区66上,通过控制栅32/44部分交迭在一边,它的另一边部分交迭第一区50。如图7S所示,本发明的工艺形成彼此镜像的存储单元对。通过氧化层104和氧化隔片58,每个镜像存储单元对与邻近的镜像存储单元对彼此绝缘。

这些实施例是唯一的,尽管浮栅长度还是由光刻步骤所定义,通过刻蚀掩模浮栅多晶硅被保护,代替浮栅多晶硅暴露于开口。WL掩模同时定义字线、浮栅和源尺寸。此外,该实施例利用一个自对准接触点图形以使导体63对准合适的自对准硅化物(salicide)区62,该区自对准第二区60。这样,存储单元中所有挑剔的部件,也就是浮栅、第一源区、字线(控制栅)和接触导体都是自对准在一起。同样,与这里所描述的所有实施例一样,这个实施例进一步形成控制栅,也就是有一个面对浮栅的平面侧壁部分的控制栅。控制栅侧壁提供一个平面表面部分以附着那里的多晶硅隔片40以形成连续的控制栅整体外延,以至于控制栅作为一个整体是邻近和部分在浮栅上。该实施例进一步形成一个有面对第二区和促进绝缘侧壁隔片58的形成和附着的平面侧壁部分的控制栅。

应该明白本发明并不限于上述实施例和图例,而是各种围绕和所有的变化都是在所附权利要求的范围内。例如,尽管前面所述的方法使用适当的掺杂多晶硅作为导电材料以形成存储单元,本领域的普通技术人员应当清楚,任何合适的导电材料都可以使用。此外,在二氧化硅或氮化硅的地方可以使用任何适合的绝缘体。而且,在氮化硅的地方可以使用任何刻蚀特性与二氧化硅(或任何绝缘体)不同的和与多晶硅(任何导体)不同的合适的材料。进一步,同样权利要求是显然的,并不是所有的方法步骤都需要按图例或权利要求严格的顺序进行,而是任何顺序都允许形成适合的本发明的存储单元。例如,可以形成第一沟道30和多晶硅阻块32,随后它们的侧壁被刻蚀掉之后,所有的这些都是邻近多晶硅阻块32的多晶硅层14形成之前。最后,可以结合上述实施例所述各种目标以形成希望的存储单元结构。

Claims (26)

1.一种电可编程和可擦除的存储器件阵列,包括:

第一导电类型的半导体材料衬底;

在衬底上形成的间隔隔离区,该隔离区基本上是互相平行的并且在第一方向延伸,每对相邻的隔离区之间的有源区包括在第一方向延伸的多个存储单元;每一个存储单元包括:

衬底内形成的第二导电类型的第一和第二间隔端和其间的衬底内形成的沟道区,

设置在所说的衬底上包括在所说的沟道区之上的第一绝缘层,

设置在所说的第一绝缘层上、并在部分所说的沟道区上和部分第二端子上延伸的导电的浮栅,

设置在浮栅上并邻近浮栅的第二绝缘层,并且有一个允许福勒-诺尔德哈姆隧穿电荷通过的厚度,和

有第一部分和第二部分的导电控制栅,第一部分有一个基本平面侧壁部分并处于邻近浮栅位置且与浮栅绝缘,第二部分基本上是连接基本平面侧壁部分并设置在浮栅上且与浮栅绝缘的一个隔片。

2.权利要求1所述的器件,其特征在于:每个控制栅穿过相邻的隔离区在基本上是垂直于第一方向的第二方向上延伸,并电连接邻近的有源区内的控制栅。

3.权利要求1所述的器件,其特征在于:对于每个控制栅,第一部分基本上是矩形。

4.权利要求1所述的器件,其特征在于:第一部分和第二部分之间的连接处控制栅形成一个凹口。

5.在半导体衬底上形成浮栅存储单元的半导体存储阵列的自对准方法,每一个存储单元有浮栅、第一端子、第二端子、第一端子和第二端子之间有沟道区、和控制栅,该方法包括以下步骤:

a)、在衬底上形成多个基本上是互相平行的并在第一方向延伸的间隔隔离区,每一对相互邻近的隔离区之间有一个有源区,每个有源区包括半导体衬底上的第一绝缘材料层和第一绝缘材料层上的第一导电材料层;

b)、形成穿过有源区和隔离区、并基本上是在垂直于第一方向的第二方向上延伸的多个间隔平行的第一沟道;每个第一沟道暴露每个有源区内的第一导电材料层;

c)、在每个有源区内形成第二绝缘材料层,设置该层邻近并且在第一导电材料层上;

d)、用第二导电材料填满每个第一沟道以形成第二导电材料的阻块,每一个阻块都有基本平面侧壁部分,其中对于每个有源区,每个阻块邻近第二绝缘材料层并与衬底绝缘;

e)、沿着第二方向形成导电材料的侧壁隔片,直接邻近和接近每个基本平面侧壁部分,其中对于每个有源区,每个隔片是设置在第二绝缘材料层和第一导电材料层上;

f)、在衬底内形成多个第一端子,其中每个有源区内每个第一端子邻近一个阻块;和

g)、在衬底内形成多个第二端子,其中在每个有源区内每个第二端子与第一端子间隔并在第一导电材料层下。

6.权利要求5所述的方法,其特征在于:第二绝缘材料层的形成包括氧化每个有源区内的第一导电材料的上部和侧面部分。

7.权利要求5所述的方法,更进一步包括以下步骤:

h)、形成多个基本上是互相平行并在第二方向延伸并穿过有源区和隔离区的间隔的第二沟道,在选择的阻块对之间形成每个第二沟道和贯通第一导电材料层和第一绝缘材料层以露出第二端子;

i)、沿第二沟道的侧壁形成第三绝缘材料层;

j)、用导电材料填满每个第二沟道,通过第三绝缘材料层第二沟道与第一导电层绝缘。

8.权利要求7所述的方法,其特征在于:第三绝缘材料层的形成包括氧化面对第二沟道的第一导电材料层的端部。

9.权利要求7所述的方法,其特征在于:第三绝缘材料层的形成包括沿每个第二沟道的侧壁形成一对绝缘材料内侧壁隔片。

10.权利要求7所述的方法,其特征在于:第三绝缘材料层的形成包括以下步骤:

氧化面对第二沟道的第一导电材料层端部;和

沿着每个第二沟道的侧壁形成一对绝缘材料内侧壁隔片。

11.权利要求5所述的方法,其特征在于:每个阻块和相应的隔片连续地形成,随其在阻块和隔片之间的连接外形成有一个凹口的控制栅。

12.权利要求5所述的方法,更进一步包括在每个第二导电材料的阻块上形成金属化硅层的步骤。

13.权利要求5所述的方法,其特征在于:第一沟道的形成包括以下步骤:

在第一导电材料层上形成至少一个材料层;

选择性地刻蚀穿过至少一个材料层以形成第一沟道的上部;

在每个第一沟道的侧壁上形成一对侧壁隔片;

在每个第一沟道的每对侧壁之间刻蚀并且穿过第一导电材料层以形成第一沟道的底部,

其中第一沟道底部的宽度比第一沟道的上部的宽度小。

14.权利要求5所述的方法,其特征在于:通过沿着第一沟道的整个侧壁形成一绝缘材料层而形成第二绝缘材料层的至少一部分。

15.权利要求5所述的方法,其特征在于:通过在第一导电材料层的上表面形成一绝缘材料层而形成第二绝缘材料层的至少一部分。

16.权利要求5所述的方法,其特征在于:

第一沟道的形成包括穿过有源区和隔离区在第一沟道的选择对之间形成中间沟道,中间沟道基本上是相互平行并在第二方向上延伸;和

第一沟道的填满包括用第二导电材料填满中间沟道以在中间沟道内形成第二导电材料的阻块。

17.权利要求16所述的方法,进一步包括在每个第二导电材料阻块上形成一层金属化硅层的步骤。

18.权利要求16所述的方法,进一步包括以下步骤:

h)、穿过有源区和隔离区,形成多个基本上互相平行的、并在第二方向延伸的间隔的第二沟道,通过去掉中间沟道内的第二导电材料形成第二沟道,和使中间沟道贯通第一导电材料层和第一绝缘材料层以露出第二端子;

i)、沿第二沟道的侧壁形成第三绝缘材料层;

j)、用导电材料填满每个第二沟道,通过第三绝缘材料层使第二沟道与第一导电层绝缘。

19.权利要求5所述的方法,更进一步包括以下步骤:

沿每个导电材料阻块的侧壁形成第二绝缘材料侧壁隔片;和

在每个第一端子上形成金属化硅层直接邻近一个第二侧壁隔片,其中每个金属化硅层自对准一个第二侧壁。

20.权利要求5所述的方法,更进一步包括以下步骤:

在每个第二导电材料阻块上形成一金属化硅层,其中对于每个第一沟道,第一沟道的侧壁使金属化硅层的边缘对准第二导电材料阻块的边缘。

21.权利要求5所述的方法,更进一步包括以下步骤:

在金属化硅层上形成第三绝缘材料层,其中对于每个第一沟道,第一沟道的侧壁使第三绝缘材料层的边缘对准第二导电材料阻块的边缘。

22.权利要求19所述的方法,更进一步包括以下步骤:在每个金属化硅层上形成导电材料并面对与之自对准的第二侧壁隔片。

23.权利要求19所述的方法,其特征在于:每个第二侧壁的形成包括在第二侧壁隔片和导电材料阻块的侧壁之间形成一绝缘材料层。

24.权利要求5所述的方法,更进一步包括以下步骤:

沿着每个导电材料阻块的侧壁形成第二绝缘材料侧壁隔片,以至于第二侧壁隔片对彼此是相邻近的但又是间隔的并且其间有一个第一端子;

在对应于第一端子的一对第二侧壁之间的每个第一端子上形成一个金属化硅层,以至于通过相应的第二侧壁隔片对使该金属化硅层自对准一个第一端子;

在有源区上形成一钝化材料层;

形成穿过钝化材料层的接触开口,其中对于每个接触开口:

接触开口向下延伸并露出金属化硅层之一;

接触开口有一个由相应的第二侧壁隔片对限定的更低部分,和

接触开口有一个比相应的第二侧壁隔片对之间间隔宽的向上部分;和

用导体材料填满每个接触开口。

25.权利要求5所述的方法,其特征在于:每个第一沟道和每个第二导电材料阻块都有基本矩形形状。

26.在半导体衬底上形成浮栅存储单元的半导体存储阵列的自对准方法,每一个存储单元有浮栅、第一端子、第二端子、第一端子和第二端子之间有沟道区,和控制栅,该方法包括以下步骤:

a)在衬底上形成多个基本上互相平行的并在第一方向延伸的间隔隔离区,每对邻近的隔离区之间有一个有源区;

b)形成穿过有源区和隔离区、并在与第一方向基本上垂直的第二方向延伸的多个间隔的平行第一沟道,每个有源区内形成第一导电材料层,该层邻近第一沟道和设置在第一绝缘材料层上;

c)在每个有源区内形成第二绝缘材料层,该层邻近和在第一导电材料层上;

d)用第二导电材料填满每个第一沟道以形成第二导电材料阻块,每个阻块有基本平面侧壁部分,其中对于每个有源区,每个阻块是邻近第二绝缘材料层并与衬底绝缘;

e)沿第二方向形成直接邻近和接近基本平面侧壁部分的导电材料侧壁隔片,其中对于每个有源区,每个隔片是设置在第二绝缘材料层和第一导电材料层上;

f)在衬底内形成多个第一端子,其中在每个有源区内的每个第一端子邻近一个阻块。和,

g)在衬底内形成多个第二端子,其中每个有源区内的每个第二端子与第一端子分开并在第一导电材料层下。

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US23398800P | 2000-09-20 | 2000-09-20 | |

| US23431400P | 2000-09-20 | 2000-09-20 | |

| US60/233988 | 2000-09-20 | ||

| US60/234314 | 2000-09-20 | ||

| US24209600P | 2000-10-19 | 2000-10-19 | |

| US60/242096 | 2000-10-19 | ||

| US09/916619 | 2001-07-26 | ||

| US09/916,619 US6868015B2 (en) | 2000-09-20 | 2001-07-26 | Semiconductor memory array of floating gate memory cells with control gate spacer portions |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1351382A CN1351382A (zh) | 2002-05-29 |

| CN1186820C true CN1186820C (zh) | 2005-01-26 |

Family

ID=27499707

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB011357045A Expired - Lifetime CN1186820C (zh) | 2000-09-20 | 2001-09-19 | 半导体存储阵列及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US6868015B2 (zh) |

| EP (1) | EP1191585A2 (zh) |

| JP (1) | JP5140219B2 (zh) |

| KR (1) | KR100821495B1 (zh) |

| CN (1) | CN1186820C (zh) |

| TW (1) | TW514994B (zh) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6803624B2 (en) * | 2002-07-03 | 2004-10-12 | Micron Technology, Inc. | Programmable memory devices supported by semiconductive substrates |

| KR100435261B1 (ko) * | 2002-08-07 | 2004-06-11 | 삼성전자주식회사 | 스플릿 게이트형 플래쉬 메모리소자의 제조방법 |

| US7049188B2 (en) * | 2002-11-26 | 2006-05-23 | Advanced Micro Devices, Inc. | Lateral doped channel |

| US6806531B1 (en) * | 2003-04-07 | 2004-10-19 | Silicon Storage Technology, Inc. | Non-volatile floating gate memory cell with floating gates formed in cavities, and array thereof, and method of formation |

| US7550800B2 (en) * | 2003-06-06 | 2009-06-23 | Chih-Hsin Wang | Method and apparatus transporting charges in semiconductor device and semiconductor memory device |

| US7759719B2 (en) * | 2004-07-01 | 2010-07-20 | Chih-Hsin Wang | Electrically alterable memory cell |

| US7613041B2 (en) * | 2003-06-06 | 2009-11-03 | Chih-Hsin Wang | Methods for operating semiconductor device and semiconductor memory device |

| US7009244B2 (en) | 2003-07-02 | 2006-03-07 | Integrated Memory Technologies, Inc. | Scalable flash EEPROM memory cell with notched floating gate and graded source region |

| KR100539247B1 (ko) * | 2004-02-04 | 2005-12-27 | 삼성전자주식회사 | 스플릿 게이트형 비휘발성 반도체 메모리 소자 및 그제조방법 |

| JP2005260071A (ja) * | 2004-03-12 | 2005-09-22 | Sharp Corp | 半導体記憶装置の製造方法 |

| KR100546405B1 (ko) * | 2004-03-18 | 2006-01-26 | 삼성전자주식회사 | 스플릿 게이트형 비휘발성 반도체 메모리 소자 및 그제조방법 |

| US20080203464A1 (en) * | 2004-07-01 | 2008-08-28 | Chih-Hsin Wang | Electrically alterable non-volatile memory and array |

| US7411244B2 (en) | 2005-06-28 | 2008-08-12 | Chih-Hsin Wang | Low power electrically alterable nonvolatile memory cells and arrays |

| KR100634006B1 (ko) * | 2005-09-05 | 2006-10-16 | 동부일렉트로닉스 주식회사 | 스플리트 게이트형 비휘발성 기억 장치 및 그 제조방법 |

| US8138524B2 (en) * | 2006-11-01 | 2012-03-20 | Silicon Storage Technology, Inc. | Self-aligned method of forming a semiconductor memory array of floating memory cells with source side erase, and a memory array made thereby |

| US7641226B2 (en) * | 2006-11-01 | 2010-01-05 | Autoliv Development Ab | Side airbag module with an internal guide fin |

| US20080157170A1 (en) * | 2006-12-29 | 2008-07-03 | Atmel Corporation | Eeprom cell with adjustable barrier in the tunnel window region |

| US8072023B1 (en) | 2007-11-12 | 2011-12-06 | Marvell International Ltd. | Isolation for non-volatile memory cell array |

| US8120088B1 (en) | 2007-12-07 | 2012-02-21 | Marvell International Ltd. | Non-volatile memory cell and array |

| US9634019B1 (en) * | 2015-10-01 | 2017-04-25 | Silicon Storage Technology, Inc. | Non-volatile split gate memory cells with integrated high K metal gate, and method of making same |

| CN107305892B (zh) * | 2016-04-20 | 2020-10-02 | 硅存储技术公司 | 使用两个多晶硅沉积步骤来形成三栅极非易失性闪存单元对的方法 |

| CN107359163B (zh) * | 2016-05-05 | 2020-06-02 | 中芯国际集成电路制造(天津)有限公司 | 存储单元的制备方法 |

| US11043492B2 (en) | 2016-07-01 | 2021-06-22 | Intel Corporation | Self-aligned gate edge trigate and finFET devices |

| TWI805336B (zh) * | 2022-04-25 | 2023-06-11 | 華邦電子股份有限公司 | 半導體結構及其形成方法 |

Family Cites Families (50)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5808328A (en) | 1977-02-21 | 1998-09-15 | Zaidan Hojin Handotai Kenkyu Shinkokai | High-speed and high-density semiconductor memory |

| US4757360A (en) | 1983-07-06 | 1988-07-12 | Rca Corporation | Floating gate memory device with facing asperities on floating and control gates |

| US4947221A (en) | 1985-11-29 | 1990-08-07 | General Electric Company | Memory cell for a dense EPROM |

| IT1191566B (it) | 1986-06-27 | 1988-03-23 | Sgs Microelettronica Spa | Dispositivo di memoria non labile a semiconduttore del tipo a porta non connessa (floating gate) alterabile elettricamente con area di tunnel ridotta e procedimento di fabbricazione |

| US4794565A (en) | 1986-09-15 | 1988-12-27 | The Regents Of The University Of California | Electrically programmable memory device employing source side injection |

| KR910000139B1 (ko) | 1986-10-27 | 1991-01-21 | 가부시키가이샤 도시바 | 불휘발성 반도체기억장치 |

| US5268319A (en) | 1988-06-08 | 1993-12-07 | Eliyahou Harari | Highly compact EPROM and flash EEPROM devices |

| JP2600301B2 (ja) | 1988-06-28 | 1997-04-16 | 三菱電機株式会社 | 半導体記憶装置およびその製造方法 |

| JPH0760866B2 (ja) * | 1988-10-19 | 1995-06-28 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

| US5051793A (en) | 1989-03-27 | 1991-09-24 | Ict International Cmos Technology, Inc. | Coplanar flash EPROM cell and method of making same |

| JPH0352267A (ja) * | 1989-07-20 | 1991-03-06 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| KR940006094B1 (ko) | 1989-08-17 | 1994-07-06 | 삼성전자 주식회사 | 불휘발성 반도체 기억장치 및 그 제조방법 |

| US5572054A (en) | 1990-01-22 | 1996-11-05 | Silicon Storage Technology, Inc. | Method of operating a single transistor non-volatile electrically alterable semiconductor memory device |

| US5029130A (en) | 1990-01-22 | 1991-07-02 | Silicon Storage Technology, Inc. | Single transistor non-valatile electrically alterable semiconductor memory device |

| US5021848A (en) | 1990-03-13 | 1991-06-04 | Chiu Te Long | Electrically-erasable and electrically-programmable memory storage devices with self aligned tunnel dielectric area and the method of fabricating thereof |

| JP3099887B2 (ja) * | 1990-04-12 | 2000-10-16 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2815495B2 (ja) | 1991-07-08 | 1998-10-27 | ローム株式会社 | 半導体記憶装置 |

| US5544103A (en) | 1992-03-03 | 1996-08-06 | Xicor, Inc. | Compact page-erasable eeprom non-volatile memory |

| KR950011983B1 (ko) | 1992-11-23 | 1995-10-13 | 삼성전자주식회사 | 반도체 장치의 제조방법 |

| US5371028A (en) | 1993-08-02 | 1994-12-06 | Chartered Semiconductor Manufacturing Pte Ltd. | Method for making single transistor non-volatile electrically alterable semiconductor memory device |

| JP3060272B2 (ja) * | 1993-11-01 | 2000-07-10 | 日本電気株式会社 | 半導体記憶装置の製造方法 |

| JPH08213486A (ja) * | 1995-01-31 | 1996-08-20 | Matsushita Electron Corp | 半導体記憶装置の製造方法 |

| JP3133667B2 (ja) * | 1995-02-23 | 2001-02-13 | 三洋電機株式会社 | スプリットゲート型トランジスタ、スプリットゲート型トランジスタの製造方法、不揮発性半導体メモリ |

| KR0161399B1 (ko) * | 1995-03-13 | 1998-12-01 | 김광호 | 불휘발성 메모리장치 및 그 제조방법 |

| US5780892A (en) | 1995-03-21 | 1998-07-14 | Winbond Electronics Corporation | Flash E2 PROM cell structure with poly floating and control gates |

| KR0144906B1 (ko) | 1995-03-31 | 1998-07-01 | 김광호 | 불휘발성 메모리 소자 및 그 제조방법 |

| JPH08321564A (ja) * | 1995-05-25 | 1996-12-03 | Sanyo Electric Co Ltd | 不揮発性半導体記憶装置およびその製造方法 |

| JP2950212B2 (ja) * | 1995-08-25 | 1999-09-20 | 日本電気株式会社 | 不揮発性半導体記憶装置およびその製造方法 |

| US5597751A (en) | 1995-12-20 | 1997-01-28 | Winbond Electronics Corp. | Single-side oxide sealed salicide process for EPROMs |

| US5814853A (en) | 1996-01-22 | 1998-09-29 | Advanced Micro Devices, Inc. | Sourceless floating gate memory device and method of storing data |

| JP3081543B2 (ja) * | 1996-03-29 | 2000-08-28 | 三洋電機株式会社 | スプリットゲート型トランジスタ、スプリットゲート型トランジスタの製造方法、不揮発性半導体メモリ |

| JP3342338B2 (ja) * | 1996-07-22 | 2002-11-05 | 三洋電機株式会社 | 不揮発性半導体記憶装置の製造方法 |

| US5780341A (en) | 1996-12-06 | 1998-07-14 | Halo Lsi Design & Device Technology, Inc. | Low voltage EEPROM/NVRAM transistors and making method |

| JPH1131801A (ja) * | 1996-12-27 | 1999-02-02 | Sanyo Electric Co Ltd | トランジスタ、トランジスタアレイ、半導体メモリおよびトランジスタアレイの製造方法 |

| US5841162A (en) * | 1997-03-24 | 1998-11-24 | Nec Corporation | Non-volatile semiconductor memory with floating gate and control gate and fabrication process therefor |

| US6252799B1 (en) * | 1997-04-11 | 2001-06-26 | Programmable Silicon Solutions | Device with embedded flash and EEPROM memories |

| US5889700A (en) * | 1997-05-05 | 1999-03-30 | National Semiconductor Corporation | High density EEPROM array using self-aligned control gate and floating gate for both access transistor and memory cell and method of operating same |

| JP2000022115A (ja) * | 1998-04-28 | 2000-01-21 | Sanyo Electric Co Ltd | 半導体メモリ及びその製造方法 |

| KR100264816B1 (ko) * | 1998-03-26 | 2000-09-01 | 윤종용 | 비휘발성 메모리 장치 및 그 동작 방법 |

| JPH11274329A (ja) * | 1998-03-26 | 1999-10-08 | Sanyo Electric Co Ltd | 不揮発性半導体記憶装置の製造方法 |

| KR100276651B1 (ko) * | 1998-04-21 | 2001-02-01 | 윤종용 | 비휘발성반도체소자제조방법 |

| US6140182A (en) | 1999-02-23 | 2000-10-31 | Actrans System Inc. | Nonvolatile memory with self-aligned floating gate and fabrication process |

| US6091104A (en) | 1999-03-24 | 2000-07-18 | Chen; Chiou-Feng | Flash memory cell with self-aligned gates and fabrication process |

| US6103573A (en) | 1999-06-30 | 2000-08-15 | Sandisk Corporation | Processing techniques for making a dual floating gate EEPROM cell array |

| US6222227B1 (en) | 1999-08-09 | 2001-04-24 | Actrans System Inc. | Memory cell with self-aligned floating gate and separate select gate, and fabrication process |

| US6525371B2 (en) | 1999-09-22 | 2003-02-25 | International Business Machines Corporation | Self-aligned non-volatile random access memory cell and process to make the same |

| US6329685B1 (en) | 1999-09-22 | 2001-12-11 | Silicon Storage Technology, Inc. | Self aligned method of forming a semiconductor memory array of floating gate memory cells and a memory array made thereby |

| US6627946B2 (en) * | 2000-09-20 | 2003-09-30 | Silicon Storage Technology, Inc. | Semiconductor memory array of floating gate memory cells with control gates protruding portions |

| US6563167B2 (en) | 2001-01-05 | 2003-05-13 | Silicon Storage Technology, Inc. | Semiconductor memory array of floating gate memory cells with floating gates having multiple sharp edges |

| KR100550779B1 (ko) * | 2003-12-30 | 2006-02-08 | 주식회사 하이닉스반도체 | 플래쉬 메모리 소자의 제조 방법 |

-

2001

- 2001-07-26 US US09/916,619 patent/US6868015B2/en not_active Expired - Lifetime

- 2001-09-19 EP EP01307977A patent/EP1191585A2/en not_active Withdrawn

- 2001-09-19 CN CNB011357045A patent/CN1186820C/zh not_active Expired - Lifetime

- 2001-09-19 TW TW090123061A patent/TW514994B/zh not_active IP Right Cessation

- 2001-09-19 JP JP2001284960A patent/JP5140219B2/ja not_active Expired - Lifetime

- 2001-09-20 KR KR1020010058275A patent/KR100821495B1/ko active IP Right Grant

-

2004

- 2004-05-18 US US10/848,982 patent/US7018897B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| CN1351382A (zh) | 2002-05-29 |

| US20020034846A1 (en) | 2002-03-21 |

| US7018897B2 (en) | 2006-03-28 |

| KR20020022628A (ko) | 2002-03-27 |

| US6868015B2 (en) | 2005-03-15 |

| KR100821495B1 (ko) | 2008-04-11 |

| JP2002151608A (ja) | 2002-05-24 |

| JP5140219B2 (ja) | 2013-02-06 |

| US20040214395A1 (en) | 2004-10-28 |

| TW514994B (en) | 2002-12-21 |

| EP1191585A2 (en) | 2002-03-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1186820C (zh) | 半导体存储阵列及其制造方法 | |

| CN1222992C (zh) | 半导体存储器阵列的自对准方法以及由此制造的存储器阵列 | |

| CN100464430C (zh) | 制造垂直场效应晶体管的方法和场效应晶体管 | |

| US6750090B2 (en) | Self aligned method of forming a semiconductor memory array of floating gate memory cells with floating gates having multiple sharp edges, and a memory array made thereby | |

| US8269266B2 (en) | Semiconductor device and a method of manufacturing the same | |

| US7091087B2 (en) | Optimized flash memory cell | |

| KR0121783B1 (ko) | 플래쉬메모리 및 그의 제조방법 | |

| JPH04229654A (ja) | 無接点フローティングゲートメモリアレイを製造する方法 | |

| US6211012B1 (en) | Method of fabricating an ETOX flash memory | |

| US6967372B2 (en) | Semiconductor memory array of floating gate memory cells with vertical control gate sidewalls and insulation spacers | |

| US4964143A (en) | EPROM element employing self-aligning process | |

| CN1207776C (zh) | 有控制栅突出部的浮栅存储器阵列自对准法及存储器阵列 | |

| US20090035907A1 (en) | Method of forming stacked gate structure for semiconductor memory | |

| US6893917B2 (en) | Structure and fabricating method to make a cell with multi-self-alignment in split gate flash | |

| US7094648B2 (en) | Method for fabricating an NROM memory cell array | |

| CN101207091A (zh) | 闪存器件的制造方法 | |

| KR20040087929A (ko) | 양방향 판독/프로그램 비휘발성 부동 게이트 메모리 셀 및그 어레이와 형성 방법 | |

| US20050196922A1 (en) | Method for producing semiconductor memory devices and integrated memory device | |

| TWI693699B (zh) | 具有在專用之溝中的浮閘之非揮發性記憶體單元 | |

| US6218246B1 (en) | Fabrication method of triple polysilicon flash eeprom arrays | |

| KR100297938B1 (ko) | 비휘발성메모리장치및그제조방법 | |

| US20060214214A1 (en) | Scalable spilt-gate flash memory cell with high source-coupling ratio |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CX01 | Expiry of patent term | ||

| CX01 | Expiry of patent term |

Granted publication date: 20050126 |