KR100261640B1 - 동기형 다이나믹형 반도체 기억 장치 - Google Patents

동기형 다이나믹형 반도체 기억 장치 Download PDFInfo

- Publication number

- KR100261640B1 KR100261640B1 KR1019970037180A KR19970037180A KR100261640B1 KR 100261640 B1 KR100261640 B1 KR 100261640B1 KR 1019970037180 A KR1019970037180 A KR 1019970037180A KR 19970037180 A KR19970037180 A KR 19970037180A KR 100261640 B1 KR100261640 B1 KR 100261640B1

- Authority

- KR

- South Korea

- Prior art keywords

- signal

- clock signal

- circuit

- input

- data

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

Abstract

본 발명은, 칩 중앙부에 입출력 단자가 배치되어 있는 SDRAM에 있어서, 고속 동작을 가능하게 하는 SDRAM을 제공한다.

외부 클럭 입력 패드(112)에 부여되는 외부 클럭 신호(ext. CLK)는, 독립한 2개의 입력 초단 회로(200, 202)를 매개로 독립한 2개의 내부 클럭 발생 회로(102, 204)에 전달된다. 행계 회로 및 열계 회로 등의 동작을 제어하는 내부 클럭 신호(int. CLK1)는 제1 클럭 발생 회로(102)에 의해 공급되고, 출력 버퍼 회로(118)를 제어하는 내부 클럭 신호(int. CLK2)는 제2 클럭 발생 회로(204)로부터 공급된다.

Description

본 발명은 외부 클럭 신호에 동기하여 동작하는 동기형 다이나믹형 반도체 기억 장치에 관한 것으로, 특히 외부 클럭 신호에 따라 데이타 판독 동작을 제어하는 동기형 다이나믹형 반도체 기억 장치의 구성에 관한 것이다.

도 17은 종래의 LOC(리드·온·칩)구조에 적용한 패드배선을 갖는 반도체 기억 장치의 칩 레이아웃을 개략적으로 나타낸 도면이다. 도 17에 있어서, 반도체 기억 장치 칩(1)의 제2방향(이하, 간단히 짧은 변 방향으로 칭함)의 중앙 영역(CR)에, 제1방향(이하, 간단히 긴 변 방향으로 칭함)에 따라 패드(PD)가 정렬되어 배치된다. 이 반도체 기억 장치 칩(1)의 중앙 영역(CR)의 양측에, 메모리셀 어레이를 포함하는 메모리셀 플레인(M#0 ~ M#3)이 배치된다. 패드(PD)는 이 반도체 기억 장치 칩(1)상에 걸쳐 중앙부까지 연장하는 리드프레임(FR)과, 중앙 영역(CR) 근변에서 본딩와이어에 의해 접속된다.

즉, LOC구조에 있어서는, 패키지의 외부 단자와 접속되어 있는 리드프레임이 칩의 상면에 실리는 구조가 된다. 종래에는, 리드프레임의 상부에 칩이 실리는 구조였기 때문에, 리드프레임단의 본딩부분으로부터 칩 주변부에 있는 본딩 패드부에 금선으로 본딩을 하지 않을 수 없고, 수용하는 칩 크기의 상한이 있었다.

LOC구조에 있어서는, 리드프레임을 칩상에 덮도록 되어 칩의 중앙부까지 연장하고, 거기서부터 본딩이 되기 때문에, 칩상의 본딩 패드의 위치를 종래의 칩 주변부로부터 칩의 중앙부로 옮기는 것이 가능하다. 이로 인해, 수용 가능한 칩의 크기를 크게 하기도 하고, 패키지 단자의 자기인덕턴스와 정전수용을 작게 할 수 있다. 더욱이, 칩의 본딩 패드로부터 버퍼 회로까지의 알루미늄 인출선을 짧게 할 수 있기 때문에, 이 부분의 배선 지연을 짧게 할 수도 있다. 또한, 후술하는 바와 같이, 본딩 패드와 주변 회로의 양자를 칩의 한중간에 십자형으로 배치할 수 있고, 주변 회로내의 회로 블럭간의 평균적인 배선 길이를 가장 짧게 할 수 있으며, 고속설계를 행하는 것이 용이하다.

즉, 도 17에 나타낸 바와 같이, 반도체 기억 장치 칩(1)은, 본딩 패드와 주변 회로를 메모리셀 플레인(M#0 ~ M#3)을 배치한 후의 빈 영역인 칩 중앙부의 십자영역에 배치한 구성으로 되어 있다. 이와 같은 구성은, 이하에 설명하는 바와 같이 주변 회로의 배선 지연을 줄이기 위해 유효하다.

주변 회로내의 지연을 줄이기 위해 회로의 배치 및 배선의 배치에 있어서 유의해야 할 것은, 본딩 패드와 입출력 패드를 근접 배치하는 것, 관련 회로를 집중·근접 배치하여 속도를 지배하는 신호 경로(크리티컬·패스)의 배선을 가능한 한 국소화하는 것, 크리티컬·패스가 아닌 신호는 가능한 한 글로벌 배선으로 돌리는 것, 그래도 글로벌 배선이 크리티컬·패스가 되는 경우는 그 길이가 가능한 한 짧게 되도록 주변 회로 전체의 배선을 행하는 것 등이다.

행과 열 어느 쪽 방향에서 보아도, 상술한 바와 같은 이들의 조건을 모두 만족시키는 경우에는, 본딩 패드와 주변 회로를 행의 중심과 열의 중심에 배치하는, 즉 이들을 칩의 중심부에 십자형으로 배치·배선하는 것이 바람직하다.

도 18은 JEDEC(Joint Electron Device Engineering Council)의 기준에 의해 표준화된 256MDRAM의 패키지의 핀 배치를 나타내는 모식도이다.

도 18에 나타낸 핀 배치의 표준에 있어서는, 억세스 시간의 고속화를 목적으로 하여 패키지의 핀 배치에 있어서는, 클럭 신호, 제어 신호(예컨대, ext. /RAS, ext. /CAS 등), 어드레스 신호용 핀을 패키지의 양단부측에 배치된 데이타 입출력용 DQ핀의 내측에 배치하는 구성으로 되어 있다.

이 구성에 있어서는, 외부 클럭 신호(ext. CLK) 핀은 패키지의 중심 위치, 즉 동기형 다이나믹형 반도체 기억 장치의 칩 중심보다도 어긋난 위치에 존재한다(핀번호 50번 또는 51번).

이와 같이, 외부 클럭 신호 입력핀이 칩 중심부보다도 어긋난 위치에 존재하는 것은, 이하에 설명하는 바와 같이 동기형 다이나믹형 반도체 기억 장치의 데이타 출력 동작에 있어서, 신호의 스큐의 발생 등의 문제를 초래하고, 이것이 동작 속도의 향상을 저해하는 요인으로 된다.

이하에서는, 종래의 동기형 다이나믹형 반도체 기억 장치의 동작에 관하여 간단히 설명한다.

일반적으로, 주기억으로서 이용되는 다이나믹형 랜덤 억세스 메모리(이하, DRAM으로 칭함)는 고속화되어 있지만, 그 동작 속도는 마이크로 프로세서(이하, MPU로 칭함)의 동작 속도에 따를 수 없다. 이 때문에, DRAM의 억세스 시간 및 사이클시간이 보틀넥으로 되고, 시스템 전체의 성능이 저하한다는 문제점이 존재하였다. 근래, 고속 MPU를 위한 주기억으로서 클럭 신호에 동기하여 동작하는 동기형 DRAM(동기형 다이나믹형 랜덤 억세스 메모리: 이하, 적의(適宜) SDRAM으로 칭함)이 시스템에 이용되도록 되어 있다.

SDRAM에 있어서는, 고속으로 억세스하기 때문에, 시스템 클럭 신호(외부 클럭 신호)에 동기하여, 연속한 예컨대 1개의 데이타 입출력 단자당 8비트의 연속 비트에 억세스하는 방법이 존재한다. 이 연속 억세스의 방법을 만족시키는 표준적인 타이밍차트를 도 19에 나타낸다. 도 19에 있어서는, 데이타 입출력 단자(DQ0 내지 DQ7)의 8비트(1바이트)의 데이타 입력 및 출력이 가능한 SDRAM에 있어서는, 연속하여 8비트의 데이타를 판독하는 동작을 나타내고 있다. 즉, 8비트 × 8 = 64비트의 데이타를 연속하여 기록하는 것이 가능하다.

연속하여 판독 또는 기록이 행해지는 데이타의 비트수는 버스트 길이(BL)로 불려지고, SDRAM에 있어서는 모드 레지스터에 의해 변경될 수 있다.

도 19에 나타낸 바와 같이, SDRAM에 있어서는 예컨대 외로부터의 클럭 신호(CLK)의 상승 에지로 외부로부터의 제어 신호, 즉 행어드레스 스트로브 신호(/RAS), 열어드레스 스트로브 신호(/CAS), 어드레스신호(Add)가 취득된다.

어드레스신호(Add)는 시분할적으로 다중화된 행 어드레스 신호(Xa)와 열 어드레스 신호(Yb)를 포함한다.

사이클(1)에서의 클럭 신호(CLK)의 상승 에지에 있어서, 외부 행어드레스 스트로브 신호(ext. /RAS)가 활성 상태의 "L"레벨, 외부 열어드레스 스트로브 신호(ext. /CAS) ALC 외부 라이트 인에이블 신호(ext. /WE)가 "H"레벨이면, 그 때의 어드레스신호(Add)가 행 어드레스 신호(Xa)로서 취득된다.

다음에, 사이클(4)에서의 클럭 신호(CLK)의 상승 에지에 있어서, 외부 열어드레스 스트로브 신호(ext. /CAS)가 활성 상태인 "L"레벨이면, 그 때의 어드레스신호(Add)가 열 어드레스 신호(Yb)로서 취득된다. 이 취득된 행 어드레스 신호(Xa) 및 열 어드레스 신호(Yb)에 따라서, SDRAM내에 있어서 행 및 열의 선택동작이 실시된다. 외부 행어드레스 스트로브 신호(ext. /RAS)가 "L"레벨로 하강하기 때문에, 소정의 클럭기간(도 19에 있어서는 클럭사이클)이 경과한 후, 데이타 입출력 단자(DQ)로부터 출력되는 8비트 데이타중 최초의 데이타(b0)가 출력된다.

이후, 클럭 신호(CLK)의 상승에 응답하여 데이타(b1 ~ b7)가 출력된다.

도 20은 SDRAM에 있어서, 1개의 데이타 입출력 단자(DQ)당 연속해서 8비트의 데이타를 기록하는 동작을 행하는 경우의 외부 신호의 상태를 나타낸 타이밍차트이다.

기록 동작에 있어서는, 행 어드레스 신호(Xa)의 취득은 데이타 판독시와 마찬가지이다. 즉, 사이클(1)에서의 클럭 신호(CLK)의 상승 에지에 있어서 신호(ext. /RAS)가 활성 상태의 "L"레벨, 신호(ext. /CAS) 및 신호(ext. WE)가 "H"레벨이면, 그 때의 어드레스신호(Add)가 행 어드레스 신호(Xa)로서 취득된다.

사이클(4)에서의 클럭 신호(CLK)의 상승 에지에 있어서, 신호(ext. /CAS) 및 신호(ext. /WE)가 모두 활성 상태의 "L"레벨이면, 열 어드레스 신호(Yb)가 취득됨과 더불어, 그 때에 데이타 입출력 단자(DQ)에 부여되어 있던 데이타(b0)가 연속해서 기록된 8비트의 데이타중 최초의 기록데이타로서 취득된다.

이 신호(ext. /RAS) 및 신호(ext. /CAS)의 상승 에지에 응답하여 SDRAM내에 있어서 행 및 열선택 동작이 실행된다. 이후는, 클럭 신호(CLK)에 동기하여 순차 입력데이타(b1 ~ b7)가 취득되고, 순차 응답하는 메모리셀에 이 입력데이타가 기록되어 간다.

상술한 바와 같이, SDRAM에 있어서는, 종래의 DRAM에서의 행어드레스 스트로브 신호(ext. /RAS) 및 열어드레스 스트로브 신호(ext. /CAS)라는 외부제어 신호에 동기하여 어드레스신호 및 입력데이타 등을 취득하여 동작시키는 방식과 다르고, 외부로부터 부여되는 시스템 클럭인 클럭 신호(CLK)의 상승 에지에서 어드레스 스트로브 신호(ext. /RAS, ext. /CAS), 어드레스신호 및 입력데이타 등의 외부 신호의 취득이 행해진다.

이와 같이, SDRAM은 외부로부터의 클럭 신호에 동기하여 제어 신호 및 데이타신호를 취득하는 동기동작을 행하기 때문에, 어드레스신호의 스큐(타이밍의 어긋남)에 의한 데이타 입출력시간에 대한 마진을 확보할 필요가 없다. 따라서, 사이클시간을 단축할 수 있다는 이점을 갖는다. 이와 같이, 클럭 신호에 동기하여 연속 데이타의 기록 및 판독을 실행할 수 있기 때문에, 연속한 어드레스에 대해 연속 억세스를 행하는 경우의 억세스 시간의 단축이 가능하게 된다.

도 21은 종래의 SDRAM(4000)의 구성의 일부를 나타내는 개략 블럭도이다.

도 21에 있어서는, 도 17에 있어서 나타낸 복수의 패드(PD)중에서 칩의 짧은 변 근변에 각각 존재하는 2개의 데이타 입출력 단자(DQ)와, 외부 클럭 신호(ext. CLK)가 입력되는 외부 클럭 입력 단자의 3개의 입출력 단자만을 나타내고, 다른 입출력 단자, 예컨대 어드레스신호 입력단자 등은 도시하지 않았다.

종래의 SDRAM(4000)은 4개의 메모리셀 플레인(M#0 ~ M#3)으로 분할된 메모리셀 어레이와, 각 메모리셀 플레인마다 설치되어 외부로부터 부여되는 행 어드레스 신호(Xa)에 따라 대응하는 행의 선택을 행하는 행 디코더(106), 각 메모리셀 플레인마다 설치되어 외부로부터 부여되는 열 어드레스 신호(Yb)에 따라 대응하는 열의 선택을 행하는 열디코터(108), 외부로부터 부여되는 제어 신호, 칩선택신호(ext. /CS), 클럭 인에이블 신호(ext. CK), 행어드레스 스트로브 신호(ext. /RAS), 열어드레스 스트로브 신호(ext. /CAS), 라이트 인에이블 신호(ext. /WE) 등을 수신하여 내부 회로의 판독 동작 및 기록 동작을 제어하는 제어 회로(100), 외부 클럭 입력 패드(112)를 매개로 부여되는 외부 클럭 신호(ext. /CLK)를 수신하는 초단의 입력버퍼 회로(104), 초단입력버퍼 회로(104)의 출력을 배선(116)을 매개로 수신하여 내부 클럭 신호를 발생하는 클럭 발생 회로(102), 외부로부터 선택된 메모리셀로부터 판독되고, 입출력 회로(110)를 매개로 출력되는 판독 데이타를 수신하여 클럭 발생 회로(102)로부터의 내부 클럭 신호에 동기하여 판독 데이타를 출력하는 출력 버퍼(118) 및, 출력 버퍼(118)의 출력을 수신하여 판독 데이타를 출력하는 데이타 입출력 패드(114)를 포함한다.

이하에서는, 편의상 칩 좌측에 존재하는 데이타 입출력 패드를 특히 DQL로, 칩 우측에 존재하는 데이타 입출력 패드를 DQR로 표시하기로 한다.

여기서, 상기 제어 신호중, 신호(ext. /CKE)는 그것이 활성 상태("L"레벨)인 기간은 셀프 리플레시 모드인 것을 지정하기 위한 신호이고, 신호(ext. /CS)는 그것이 활성 상태("L"레벨)일 때에 행계의 회로의 동작을 활성 상태로 하는 것을 지정하기 위한 신호이며, 신호(ext. /CAS)는 그것이 활성 상태("L"레벨)일 때에 열계의 회로의 동작을 활성으로 하는 것을 지시하기 위한 신호이고, 신호(ext. /WE)는 그것이 활성 상태인 것으로 데이타 기록모드의 개시를 지정하기 위한 신호이다.

단, 상술한 바와 같은 각 제어 신호의 기능은, 원칙적인 것으로 그들의 특수한 조합에 의해서는 후에 설명하는 바와 같이 제어 회로(100)에 대해 일정의 동작모드의 개시 또는 종료를 지시하는 것이 된다.

일반적으로는, 신호의 입출력을 행하는 패드 근변에 입력 초단 버퍼 회로를 설치하고, 그 출력을 칩 중앙부근에 존재하는 마스터 제어 회로군에 입력하여 이 마스터 제어 회로군이 칩 전체를 제어하는 신호를 발생한다. 이와 같은 구성은, 내부 클럭 발생 회로(102)에 대해서도 일반적으로 이용되고 있고, 외부 클럭 입력 패드(112) 근변에 있는 입력 초단 회로(104)는 외부로부터 부여되는 외부 클럭 신호를 외부레벨(예컨대, 풀스윙으로 5V)로부터, 칩 내부레벨(예컨대, 풀스윙으로 3.3V)로 변환한 후, 마스터 제어 회로군내에 있는 클럭 발생 회로(102)에 대해 외부 클럭 신호를 전달한다.

클럭 발생 회로(102)는 클럭 신호의 펄스폭의 조정과 더불어, 칩 내부에 사용목적에 따른 내부 클럭 신호를 공급한다. 이 내부 클럭 신호가 공급되는 상대측의 회로로서는, 크게 분류하면 행계 회로, 열계 회로, 데이타출력계 회로 등이 존재한다.

즉, SDRAM 등의 외부 클럭 동기형 메모리에 있어서는, 외부 클럭 신호에 동기하면서, 행 선택동작, 열선택동작, 데이타 판독 동작, 데이타 출력 동작 등이 행해지게 되지만, 이중에서 데이타출력계 회로에 공급되는 내부 클럭 신호를 데이타 출력패드(114)에 대한 데이타 출력 버퍼 회로(118)에 대해 얼마나 짧은 지연시간으로 도달시키는가가 칩 성능에 크게 관계하고 있다.

즉, 이 데이타 출력 버퍼에 대한 내부 클럭 신호공급의 고속화는, 칩의 억세스 시간 등의 성능향상을 위한 중요한 포인트가 된다.

도 21에 나타낸 바와 같이, 종래의 SDRAM(4000)에 있어서는, 외부 클럭 신호입력 패드(112)로부터 일단 칩 중앙부근까지 이 외부 클럭 신호가 전달된 후, 클럭 발생 회로(102)가 데이타출력 버퍼에 대한 내부 클럭 신호와, 다른 행계 또는 열계 회로에 대해 공급하는 내부 클럭 신호를 동시에 발생하는 구성으로 되어 있다.

따라서, 데이타 출력 버퍼에 대해 부여되는 내부 클럭 신호를 고속화하기 위해서는, 입력 초단 버퍼 회로(104)를 구성하는 트랜지스터의 전류 구동 능력을 크게 할 필요가 있다. 이것은 환언하면, 입력 초단 버퍼 회로(104)를 구성하는 트랜지스터 크기(게이트폭)를 크게 할 필요가 있는 것을 의미한다.

그러나, 입력 초단 버퍼 회로(104)는, 다른 내부 클럭 신호에 관해서도 공유되는 구성으로 되어 있기 때문에, SDRAM(4000)이 동작중에는 항상 이 입력 초단 버퍼 회로(104)는 대전류를 소비하게 된다.

도 22는 외부 클럭 신호입력버퍼(112) 및 입력 초단 버퍼 회로(104) 및 클럭 발생 회로(102)만을 구성 부분을 추출하여 나타낸 개략 블럭도이다.

도 18에 나타낸 바와 같은 핀 배치의 표준에 대응하여 칩내에 패드를 배치한 경우, 외부 클럭 신호 입력 패드(112)의 근변에 설치되어 있는 입력 초단 버퍼 회로(104)로부터 칩 중앙부에 설치되어 있는 클럭 발생 회로(102)를 접속하는 배선(116)의 배선 길이(1)는 1 ~ 2mm에 달하는 경우가 있다.

따라서, 상술한 바와 같이 입력 초단 버퍼 회로(104)는, 이 비교적 길은 배선(116)을 구동하는 만큼의 전류 구동 능력이 필요하게 된다.

도 23은 초단입력버퍼 회로(104) 및 내부 클럭 발생 회로(102)의 구성을 나타낸 개략 블럭도이다.

도 23에 나타낸 바와 같이, 입력 초단 회로(104)는 차동증폭회로(1042)와 드라이버 회로(1044)를 포함한다.

차동증폭회로(1042)는 한쪽의 입력단에 기준전위(Vref)를 수신하고, 다른 입력단에 외부 클럭 입력 패드(112)로부터의 외부 클럭 신호의 전위레벨을 수신하는 구성으로 되어 있다. 또한, 차동증폭회로(1042)는 전원 파워 온시에 활성 상태("L"레벨)로 되는 파워 다운모드 활성화 신호(/PDE)에 의해 제어되는 구성으로 되어 있다.

즉, SDRAM(4000)에 대해 전원공급이 개시되고, 파워 다운모드 활성화 신호(/PDE)가 불활성 상태("H"레벨)로 되었던 경우에만 차동증폭회로(1042)는 동작한다.

드라이버 회로(1044)는 차동증폭회로(1042)의 출력을 수신하여 배선(116)의 전위레벨 및, 클럭 발생 회로(102)의 패드(DQL)에 대한 데이타 출력 버퍼로의 내부 클럭 신호를 공급하는 드라이버 회로(1022)와, 패드(DQR)에 대한 데이타 출력 버퍼로의 내부 클럭 신호를 공급하는 드라이버 회로(1044), 다른 행계 또는 열계의 회로로의 내부 클럭 신호를 발생하는 드라이버 회로(1026)를 동시에 구동할 필요가 있다.

즉, 입력 초단 버퍼 회로(104)는 데이타 출력 버퍼로의 내부 클럭 및 다른 내부 회로로의 내부 클럭을 발생하는 모든 회로에 대해 공통으로 외부 클럭 신호를 전달하는 것이 가능한 정도로 이 입력 초단 회로(104)를 구성하는 트랜지스터의 트랜지스터 크기를 크게 할 필요가 있다. 입력 초단 버퍼 회로는 도 23에 나타낸 바와 같이, 차동앰프형의 구성을 갖기 때문에, 항상 관통전류가 흐르고, 이 때문에 대기상태에 있어서도 이 입력 초단 버퍼 회로에 있어서 큰 전류가 소비되며, SDRAM(4000)의 대기전류의 증대를 초래한다는 문제점이 있었다.

본 발명은 상기한 점을 감안하여 발명된 것으로, 그 목적은 동기형 다이나믹형 반도체 기억 장치에 있어서는, 데이타출력의 타이밍을 규정하는 내부 클럭 신호를 고속으로 데이타출력 버퍼에 대해 전달하는 것이 가능한 동기형 다이나믹형 반도체 기억 장치를 제공함에 있다.

본 발명의 다른 목적은, 대기상태에 있어서, 소비전력의 절감을 도모하는 것이 가능한 동기형 다이나믹형 반도체 기억 장치를 제공함에 있다.

도 1은 본 발명의 실시 형태1의 SDRAM(1000)의 구성을 나타낸 개략 블럭도.

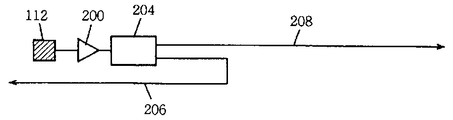

도 2는 SDRAM(1000)의 내부 클럭 발생의 주요부를 나타낸 블록도.

도 3은 도 2에 나타낸 내부 클럭 발생의 주요부의 구성을 더욱 상세히 나타낸 개략 블럭도.

도 4는 SDRAM(1000)의 동작을 설명하기 위한 타이밍차트.

도 5는 제어 회로(100)에 포함되는 제1 부분 회로(1100)의 구성을 나타낸 개략 블럭도.

도 6은 제어 회로(100)에 포함되는 제2 부분 회로(1200)의 구성을 나타낸 개략 블럭도.

도 7은 본 발명의 실시 형태2의 SDRAM의 제어 회로(100)에 포함되는 제1 부분 회로(1300)의 구성을 나타낸 개략 블럭도.

도 8은 실시 형태2의 SDRAM의 제어 회로(100)에 포함되는 제2 부분 회로(1400)의 구성을 나타낸 개략 블럭도.

도 9는 실시 형태2의 SDRAM의 동작을 설명하기 위한 타이밍차트.

도 10은 실시 형태3의 SDRAM(2000)의 구성을 나타낸 개략 블럭도.

도 11은 SDRAM(2000)의 열계의 회로 구성을 꺼내어 나타낸 부분확대도.

도 12는 도 11에 나타낸 버퍼 회로의 구성을 나타낸 회로도.

도 13은 실시 형태3의 SDRAM(2000)의 동작을 설명하기 위한 타이밍차트.

도 14는 실시 형태3의 SDRAM(2000)의 변형예의 SDRAM(3000)의 구성을 나타낸 개략 블럭도.

도 15는 클럭 신호를 전달하기 위한 배선을 모식적으로 나타낸 도면.

도 16은 배선 피치와 배선 지연 및 배선 면적의 관계를 나타낸 도면.

도 17은 종래의 SDRAM의 패드배선의 일례를 나타낸 모식도.

도 18은 종래의 SDRAM의 핀 배선을 설명하기 위한 모식도.

도 19는 종래의 SDRAM의 판독 동작을 설명하기 위한 타이밍차트.

도 20은 종래의 SDRAM의 기록 동작을 설명하기 위한 타이밍차트.

도 21은 종래의 SDRAM(4000)의 구성을 나타낸 개략 블럭도.

도 22는 종래의 SDRAM(4000)중, 내부 클럭을 발생하는 구성 부분을 취출하여 나타낸 개략 블럭도.

도 23은 도 22에 나타낸 개략 블럭도를 보다 상세히 설명하기 위한 회로도.

<도면의 주요 부분에 대한 부호의 설명>

100 : 제어 회로

102 : 제1 클럭 발생 회로

106 : 행 디코더

180 : 열 디코더

110 : 입출력 회로

112 : 외부 클럭 입력 패드

114 : 데이타 입출력 패드

116 : 클럭 신호용 배선

118 : 출력 버퍼 회로

200 : 제2 입력 초단 회로

202 : 제1 입력 초단 회로

204 : 제2 클럭 발생 회로

206, 208 : 클럭 신호용 배선

M#0 ~ M#3 : 메모리 플레인

1000, 2000, 3000, 4000 : SDRAM

청구항 제1항 기재의 동기형 다이나믹형 반도체 기억 장치는, 일련의 펄스열로 이루어진 외부 클럭 신호에 동기하여 제어 신호 및 어드레스신호를 포함하는 복수의 외부 신호를 취득하고, 또한 기억 데이타를 출력하는 장방형 형상의 동기형 다이나믹형 반도체 기억 장치에 있어서, 행렬 형상으로 배치되는 복수의 메모리셀을 갖는 메모리셀 어레이와, 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제1 클럭 발생 수단, 내부 클럭 신호 및 외부 신호에 따라 동기형 다이나믹형 반도체 기억 장치의 데이타 출력 동작을 제어하는 제어 수단 및, 복수의 외부 신호를 수신하고, 또는 상기 기억 데이타를 출력하여 상기 장방형 형상의 제1변 방향에 따라 배치되는 복수의 입출력 단자를 구비하고; 복수의 입출력 단자는 외부 클럭 신호를 수신하는 외부 클럭 입력 단자와, 외부 클럭 입력 단자 및 제어 수단을 끼우도록 배치되는 제1 및 제2 데이타 입출력 단자를 포함하며; 제어 수단에 의해 제어되고, 제1 클럭 발생 수단으로부터의 내부 클럭 신호에 동기하여 외부로부터의 행 어드레스 신호에 따라 메모리셀 어레이의 대응하는 행을 선택하는 행 선택 수단과, 제어 수단에 의해 제어되고, 제1 클럭 발생 수단으로부터의 내부 클럭 신호에 동기하여 열 어드레스 신호에 따라 메모리셀 어레이의 대응하는 복수의 열을 선택하며, 선택된 행 및 열에 대응하는 복수의 메모리셀의 기억 데이타를 판독하는 열선택 수단, 외부 클럭 입력 단자로부터의 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제2 클럭 발생 수단 및, 열선택 수단으로부터의 대응하는 기억 데이타를 수신하여 제2 클럭 발생 수단으로부터 직접 수신하는 내부 클럭 신호에 동기하여, 대응하는 제1 및 제2 데이타 입출력 단자에 기억 데이타를 각각 출력하는 제1 및 제2 데이타출력 수단을 더 구비하는 것을 특징으로 한다.

청구항 제2항 기재의 동기형 다이나믹형 반도체 기억 장치는, 일련의 펄스열로 이루어진 외부 클럭 신호에 동기하여 제어 신호 및 어드레스신호를 포함하는 복수의 외부 신호를 취득하고, 또한 기억 데이타를 출력하는 장방형 형상의 동기형 다이나믹형 반도체 기억 장치에 있어서, 장방형 형상의 적어도 긴 변 방향의 중심축 및 짧은 변 방향의 중심축의 어느 한쪽에 따라 소정의 폭을 갖는 여유영역을 남기도록 배치하고, 각각이 행렬 형상으로 배치되는 복수의 메모리셀을 포함하는 짝수개의 메모리셀 플레인을 구비하고; 여유영역은, 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제1 클럭 발생 수단과, 내부 클럭 신호 및 외부 신호에 따라 동기형 다이나믹형 반도체 기억 장치의 데이타 출력 동작을 제어하는 제어 수단 및, 복수의 외부 신호를 수신하고, 또는 기억 데이타를 출력하며, 상기 여유영역에 따른 중심축 방향에 따라 배치되는 복수의 입출력 단자를 포함하며; 복수의 입출력 단자는, 외부 클럭 신호를 수신하는 외부 클럭 입력 단자와, 외부 클럭 입력 단자 및 제어 수단을 끼우도록 배치되는 제1 및 제2 데이타 입출력 단자를 갖추고; 여유영역은, 제어 수단에 의해 제어되고, 제1 클럭 발생 수단으로부터의 내부 클럭 신호에 동기하여 외부로부터의 행 어드레스 신호에 따라 메모리셀 플레인의 대응하는 행을 선택하는 행 선택 수단과, 제어 수단에 의해 제어되고, 제1 클럭 발생 수단으로부터의 내부 클럭 신호에 동기하여 열 어드레스 신호에 따라 메모리셀 플레인의 대응하는 복수의 열을 선택하며, 선택된 행 및 열에 대응하는 복수의 메모리셀에 기억 데이타를 판독하는 열선택 수단, 외부 클럭입출력 단자로부터의 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제2 클럭 발생 수단 및, 열선택 수단으로부터의 대응하는 기억 데이타를 수신하여 제2 클럭 발생 수단으로부터 직접 수신하는 내부 클럭 신호에 동기하여, 대응하는 제1 및 제2 데이타 입출력 단자에 기억 데이타를 각각 출력하는 제1 및 제2 데이타 출력 수단을 더 포함하는 것을 특징으로 한다.

(실시 형태1)

도 1은 본 발명의 실시 형태1의 동기형 다이나믹형 반도체 기억 장치, 예컨대 SDRAM(1000)의 구성을 나타낸 개략 블럭도이다.

SDRAM(1000)은 4개의 메모리셀 플레인(M#0 ~ M#3)으로 분할된 메모리셀 어레이를 포함한다. 각 메모리셀 플레인(M#0 ~ M#3)은, 칩 중앙부에 패드와 주변 회로의 양자를 칩의 한중간에 십자형 형상으로 배치할 수 있도록 소정의 여유영역을 남겨 배치되어 있다.

SDRAM(1000)은 또한 각 메모리셀 플레인(M#0 ~ M#3)에 대응하여 설치되고, 외부로부터 부여되는 행 어드레스 신호(Xa)에 따라 대응하는 메모리셀 플레인의 행을 선택하는 행 디코더(106)와, 메모리셀 플레인(M#0 ~ M#3)에 대응하여 설치되고, 내부로부터의 열 어드레스 신호(Yb)에 따라 대응하는 메모리셀 플레인의 열을 선택하는 열 디코더(108), 판독 동작에 있어서 선택된 메모리셀로부터의 데이타의 판독을 행하고, 기록 동작에 있어서 선택된 메모리셀에 대해 데이타의 기록을 행하는 입출력 회로(110), 외부로부터 부여되는 제어 신호(ext. CKE, ext. /CS, ext. /RAS, ext. /CAS, ext. /WE)에 따라 각 내부 회로의 동작을 제어하고, 예컨대 셀프 리플레시 모드에 있어서는 활성의 셀프 리플레시 모드 지정신호(/REFS)를 출력하며, 후에 설명하는 바와 같이 데이타 출력 동작을 제어하는 신호(/CACT)를 활성 상태("L"레벨)로 하는 제어 회로(100), 외부 클럭 신호(ext. CLK)가 부여되는 외부 클럭 입력 패드(112), 외부 클럭 입력 패드로부터의 외부 클럭 신호(ext. CLK)를 수신하여 버퍼 처리하여 출력하는 제1 입력 초단 버퍼 회로(202), 입력 초단 버퍼 회로(202)의 출력을 수신하여 제1 내부 클럭 신호(int. CLK1)를 출력하는 제1 클럭 발생 회로(102), 외부 클럭 입력 패드(112)로부터의 외부 클럭 신호를 수신하여 버퍼 처리하여 출력하는 제2 입력 초단 버퍼 회로(200), 입력 초단 버퍼 회로(200)의 출력을 수신하여 데이타 출력 동작을 제어하는 제2 내부 클럭 신호(int. CLK2)를 출력하는 제2 클럭 발생 회로(204), 메모리셀 플레인(M#0)으로부터 판독된 데이타를 수신하여 제2 내부 클럭 신호(CLK2)로 제어되어 데이타 입출력 패드(114)를 구성하는 출력 버퍼 회로(118), 제2 클럭 발생 회로와 칩 좌측에 존재하는 데이타 입출력 패드(DQL)에 대응하는 출력 버퍼(118)와의 사이를 접속하는 배선(206) 및, 칩 우측에 존재하는 데이타 입출력 패드(DQR)에 대응하는 출력 버퍼 회로(118)와 제2 클럭 발생 회로(204)와의 사이를 접속하는 배선(208)을 포함한다.

또한, 도 1에 있어서는, 메모리셀 플레인(M#0 ~ M#3)은 4개 존재하고, 패드와 주변 회로의 양자를 칩 한중간에 십자형 형상으로 배치할 수 있도록 소정의 여유영역을 남겨서 배치되어 있는 구성으로 하였지만, 이하의 설명에서 분명하게 되는 바와 같이, 본 발명은 이와 같은 구성에 한정되는 것은 아니고, 보다 일반적인 메모리셀 플레인의 개수 및 배치에 대하여 적용할 수 있다. 예컨대, 메모리셀 플레인은 2개 존재하고, 패드와 주변 회로의 양자를 칩의 한중간에 일자 형상으로 배치할 수 있도록 소정의 여유영역을 남겨서 배치되어 있는 구성으로 할 수도 있다.

여기서, 제1 클럭 발생 회로(102)로부터 출력되는 내부 클럭 신호(int. CLK1)는 SDRAM(1000)의 행계 회로, 예컨대 행 디코더(106) 등의 동작이나, 열계 회로, 예컨대 열 디코더(108)나 입출력 회로(110) 등의 동작의 제어에 이용된다.

또한, 제1 입력 초단 회로(202)의 동작은, 신호(/REFS)가 활성 상태("L"레벨)인 기간에는 불활성 상태로 되는 것으로 한다.

한편, 제2 입력 초단 버퍼 회로(200)의 동작은, 후에 설명하는 바와 같이 신호(/CACT)에 의해 제어되고, 판독 동작 기간중에 있어서만 활성 상태로 하는 것으로 한다.

여기서, 신호(/REFS)나 신호(/CACT)가 활성 상태로 되는지 또는 불활성 상태로 되는지는, 후에 설명하는 바와 같이 제어 회로(100)에 부여되는 외부로부터의 제어 신호의 조합에 의해 규정되는 것으로 한다.

도 1에 나타낸 SDRAM(1000)의 구성이 도 21에 나타낸 종래의 SDRAM(4000)의 구성과 다른 점은 이하와 같다.

우선 제1로, 외부 클럭 신호(ext. CLK)가 부여되는 외부 클럭 입력 패드(112)에 접속하는 입력 초단 버퍼 회로는, 제1의 입력 초단 버퍼 회로(202) 및 제2 입력 초단 버퍼 회로(200)의 2개로 분할되고, 제1 입력 초단 버퍼 회로(202)는 상술한 바와 같이 행계 또는 열계 또는 다른 내부 회로 등을 제어하기 위한 내부 클럭 신호를 발생하는 제1 클럭 발생 회로(102)에 대해 외부 클럭 신호를 전달한다. 이에 대해, 제2 입력 초단 버퍼 회로(200)는 출력 버퍼 회로(118)의 동작을 제어하는 내부 클럭 신호를 출력하는 제2 클럭 발생 회로(204)에 대해 외부 클럭 신호(ext. CLK)를 전달한다.

제2로는, 상기 제2 입력 초단 버퍼 회로(200)는, 제1 입력 초단 버퍼 회로(202)에 비해 전류 구동 능력이 크게 되도록 구성되어 있는 점이다. 즉, 제2 입력 초단 버퍼 회로(200)를 구성하는 트랜지스터의 트랜지스터 크기는 제1 입력 초단 버퍼 회로(202)를 구성하는 트랜지스터의 트랜지스터 크기에 비해 크게 되도록 설정되어 있다.

제3으로는, 제1 입력 초단 버퍼 회로(202)는, 신호(/REFS)로 제어되어 리플레시 기간 이외는 활성 상태로 되는 구성으로 되어 있고, 제2 입력 초단 버퍼 회로(200)는 신호(/CACT)로 제어되어 판독 동작기간중에 있어서만 활성 상태로 되는 구성으로 되어 있는 점이다.

제4로는, 제2 클럭 발생 회로(204)로부터 출력되는 신호를 패드(DQL)에 대응하는 출력 버퍼(118)에 대해 전달하는 배선(206)은, 한번 칩 중앙부까지 연장한 후, 접어져 출력 버퍼(118)에 도달하도록 형성되어 있는 점이다.

도 2는 도 1에 나타낸 SDRAM(1000)의 구성중, 외부 클럭 입력 패드(112), 제2 입력 초단 버퍼 회로(200), 제2 클럭 발생 회로(204), 출력 버퍼(118)로 내부 클럭 신호를 전달하는 배선(206 및 208)의 부분을 추출하여 나타낸 개략 블럭도이다.

상술한 바와 같이, 배선(206)은 일단 배선(208)과 동일방향으로 연장한 후, 접어져 배선(208)과는 반대방향으로 향하도록 형성되어 있다.

도 3은 도 2에 나타낸 제2 입력 초단 버퍼 회로(200) 및 제2 클럭 발생 회로(204)의 구성을 보다 상세히 나타낸 블럭도이다.

제2 입력 초단 버퍼 회로(200)는, 함께 소스에 전원전위(Vcc)를 수신하고, 전류미러회로를 구성하는 p채널 MOS트랜지스터쌍(2002, 2004)과, p채널 MOS트랜지스터(2002)의 드레인과 드레인을 접속하고, 게이트에 기준전위(Vref)를 수신하는 n채널 MOS트랜지스터(2008), p채널 MOS트랜지스터(2004)의 드레인과 드레인을 접속하고, 게이트에 외부 클럭 신호(ext. CLK)를 수신하는 n채널 MOS트랜지스터(2010), 소스가 접지전위(GND)와 접속하고, 드레인이 n채널 MOS트랜지스터(2008, 2010)의 소스와 공통으로 접속하며, 게이트에 신호(/CACT)가 인버터(2014)에 의해 반전된 신호를 수신하는 n채널 MOS트랜지스터(2012), 게이트에 인버터(2014)의 출력을 수신하고, p채널 MOS트랜지스터(2004)와 병렬로 접속되는 p채널 MOS트랜지스터(2006) 및, p채널 MOS트랜지스터(2004) 및 n채널 MOS트랜지스터(2010)의 접속점의 전위를 수신하고, 외부에 반전하여 출력하는 드라이버 회로(2016)를 포함한다.

한편, 제2 클럭 발생 회로(204)는, 드라이버 회로(2016)의 출력을 수신하여 배선(208)에 대해 내부 클럭 신호를 출력하는 드라이버 회로로서 동작하는 인버터(2042)와, 드라이버 회로(2016)의 출력을 수신하여 배선(206)에 대해 내부 클럭 신호(int. CLK)를 출력하는 드라이버 회로로서 동작하는 인버터(2044)를 포함한다.

또한, 제1 입력 초단 버퍼 회로(202)의 구성도, 제어 신호가 신호(/REFS)로 되어 있는 점을 제외하고는 기본적으로 제2 입력 초단 버퍼 회로(200)의 구성과 동일하다.

도 3에 나타낸 본 발명의 실시 형태1의 제2 입력 초단 버퍼 회로 및 제2 클럭 발생 회로의 구성을, 도 23에 나타낸 종래의 입력 초단 버퍼 회로 및 클럭 발생 회로의 구성과 비교하면, 이하의 유리한 점이 존재한다.

즉, 제1로는, 제2 입력 초단 버퍼 회로(200)는, 신호(/CACT)에 의해 제어되고, 신호(/CACT)가 활성인 기간, 즉 판독 동작모드가 지정되어 있는 기간에만 활성 상태로 되기 때문에, 제2 입력 초단 버퍼 회로(200)를 구성하는 트랜지스터 크기 등을 크게 한 경우에서도, 대기상태에서의 SDRAM(1000)의 동작전류를 증대시키는 일이 없다.

환언하면, 제1 입력 초단 버퍼 회로와 제2 입력 초단 버퍼 회로를 독립해서 구성하고 있기 때문에, 데이타 출력 동작의 크리티컬패스에 있어서, 큰 전류 구동 능력이 요구되는 제2 입력 초단 버퍼 회로(200) 등에 충분한 전류 구동 능력을 갖도록 설계를 행한 경우에도, 제2 입력 초단 버퍼 회로는 판독기간밖에 동작하지 않기 때문에, SDRAM (1000)의 대기동작중의 동작전류가 증대하는 일이 없다.

더욱이, 제2 클럭 발생 회로(204)는, 제2 입력 초단 버퍼 회로(200)의 근변에 인접하여 설치되어 있기 때문에, 드라이버 회로(2016)는 큰 배선용량을 구동할 필요가 없고, 게다가 드라이버 회로(2016)는 배선(206, 208)을 구동하는 인버터(2042, 2044)만을 구동하면 되기 때문에, 이 드라이버 회로(2016)의 전류 구동 능력 등에 대한 설계의 자유도를 넓힐 수 있다.

또한, 상술한 바와 같이, 배선(206)은 칩 중앙부 근변까지 배선(208)과 동일방향으로 지나간 후, 배선(208)과는 역방향으로 지나가고, 출력 버퍼 회로(118)와 접속되는 구성으로 되어 있기 때문에, 배선(206)의 총배선 길이를 적당한 값으로 설정하는 것으로, 제2 클럭 발생 회로(204)로부터 출력된 내부 클럭 신호(int. CLK2)가 칩 양단에 존재하는 출력 버퍼 회로(118)에 각각 도달하는 시간의 시간차를 억제하도록 구성할 수 있다.

이 때문에, 데이타 출력시에 발생하는 출력데이타의 스큐 등이 절감되고, 보다 빠른 사이클시간에 대응하여 동작시킬 수 있다.

도 4는 도 1에 나타낸 SDRAM(1000)의 동작을 설명하기 위한 타이밍차트이다.

시각(t0) ~ 시각(t1)의 기간에 있어서, 신호(ext.CKE)가 활성 상태("L" 레벨)로 변화한다.

시각(t1)에서의 외부 클럭 신호(ext. CLK)의 상승 에지에 있어서, 신호(ext. CKE), 신호(ext. /CS, ext. RAS, ext. /CAS)가 모두 활성 상태("L"레벨)이고, 또한 신호(ext. /WE)가 비활성 상태("H"레벨)인 것에 따라 제어 회로(100)는 셀프 리플레시 모드가 지정된 것을 검지하여, 신호(/REFS)를 활성 상태("L"레벨)로 한다.

이때, 도 1에 있어서 설명한 바와 같이, 제1 입력 초단 버퍼 회로(202)는 신호(/REFS)가 활성 상태가 되는 것에 따라 비활성 상태로 된다.

한편, 신호(/CACT)는 비활성 상태("H"레벨)이기 때문에, 제2 입력 초단 버퍼 회로(200)도 비활성 상태이다.

셀프 리플레시 모드에 있어서는, 제어 회로(100)로부터 출력되는 내부어드레스신호에 따라 메모리셀 플레인(M#0 ~ M#3)중의 각 행이 순차 선택되고, 데이타의 재기록 동작, 즉 리플레시동작이 행해지게 된다.

시각(t3) ~ 시각(t4)의 기간에 있어서, 신호(ext. CKE)가 비활성 상태("H"레벨)로 변화한다.

따라서, 시각(t4)에서의 외부 클럭 신호(ext. CLK)의 상승 에지에 있어서, 제어 신호(ext. CKE, ext. /CS, ext. /RAS, ext. /CAS, ext. /WE)가 비활성 상태("H"레벨)인 것에 따라, 제어 회로(100)는 셀프 리플레시 모드의 종료가 지정된 것을 검출하여, 셀프리플레시동작을 종료한다.

시각(t6)에서의 외부 클럭 신호(ext. CLK)의 상승 에지에 있어서, 신호(ext. /CS, ext. /RAS)가 모두 활성 상태("L"레벨)이고, 신호(ext. CKE, ext. /CAS, ext. /WE)가 불활성 상태("H"레벨)인 것에 따라, 제어 회로(100)는 이 시점에 있어서 외부어드레스 입력단자(패드)에 부여되어 있는 신호를 행 어드레스 신호로 취득하도록 제어한다.

이 시점에 있어서는, 신호(/REFS)는 불활성 상태("H"레벨)이고, 제1 입력 초단 버퍼 회로(202)는 동작하고 있으며, 그에 따라 제1 클럭 발생 회로(102)도 동작하여 내부 클럭 신호(int. CLK1)를 대응하는 내부 회로에 공급하고 있다.

시각(t8)에서의 외부 클럭 신호(ext. CLK)의 상승 에지에 있어서, 제어 신호(ext. /CS, ext. /CAS)가 모두 활성 상태("L"레벨)이고, 신호(ext. CKE, ext. /RAS, ext. /WE)가 모두 불활성 상태("H"레벨)인 것에 따라, 제어 회로(100)는 이 시점에서 어드레스신호 입력단자(패드)에 부여되어 있는 신호를 열 어드레스 신호로서 취득되도록 지시한다.

도 4에 나타낸 경우에 있어서는, CAS 레이텐시, 즉 이렇게 함으로써 열 어드레스 신호가 취득되는 사이클로부터 데이타 출력이 개시되기까지의 사이클수(CL)가 2이도록 지정되어 있는 것으로 한다.

이와 같은 지정은, 예컨대 판독 동작의 세트사이클(도시하지 않음)에 있어서, 제어 신호와 어드레스신호의 조합에 의해 지정되어 있는 것으로 한다.

신호(ext. /CS, ext. /CAS)가 모두 활성 상태인 것에 따라, 제어 회로(100)는 신호(/CACT)를 활성 상태("L"레벨)로 변화시킨다. 이에 따라, 도 3에 있어서 설명한 바와 같이, 제2 입력 초단 버퍼 회로(200)는 활성 상태로 변화한다.

따라서, 제2 클럭 발생 회로(204)로부터 출력 버퍼 회로(118)에 대해 제2 내부 클럭 신호(int. CLK2)의 공급이 개시되게 된다.

시각(t8)으로부터 2사이클 경과한 후의 시각(t10)에 있어서, 선택된 메모리셀로부터 판독된 데이타의 출력 동작이 개시된다.

본 실시 형태에 있어서는, 1회의 판독 동작에 있어서 1개의 데이타 출력단자(패드)당 출력되는 데이타수, 즉 버스트 길이(BL)는 2가 지정되어 있는 것으로 한다.

이 버스트 길이의 지정도, 판독 동작모드의 세트사이클(도시하지 않음)에서의 제어 신호의 조합 및 어드레스신호의 조합에 의해 지정되어 있는 것으로 한다.

시각(t10)에 있어서, 1비트째의 판독 데이타가 출력된 후, 시각(t11)에 있어서 2비트째의 데이타의 출력이 행해진다. 이 때, 동시에 시각(t11)에 있어서, 제어 신호(ext. /CS, ext. /RAS, ext. /WE)가 모두 활성 상태이고, 신호(ext. CKE) 및 신호(ext. /CAS)가 불활성 상태인 것에 따라, 판독 동작의 종료가 지정되며, 이에 따라 제어 회로(100)는 시각(t12)에 있어서 신호(/CACT)를 불활성 상태("H"레벨)로 변화시킨다.

이상의 동작에 있어서 설명한 바와 같이, 실시 형태1의 SDRAM(1000)에 있어서는, 리플레시 동작기간중에 있어서는 제1 및 제2 입력 초단 버퍼 회로(202, 200)는 함께 비활성 상태이기 때문에, 이 기간중에 있어서 차동 증폭기에 의한 관통전류에 의한 소비전류의 증가가 제어된다.

더욱이, 제2 입력 초단 버퍼 회로(200)의 전류 구동 능력을 크게 하기 위해, 그를 구성하는 트랜지스터의 트랜지스터 크기를 크게 한 경우에도, 제2 입력 초단 버퍼 회로는 판독 동작모드 기간에만 활성 상태로 되기 때문에, 대기상태에서의 소비전류가 증대하는 일이 없다.

도 5는 도 4에 나타낸 바와 같이, 판독 동작 기간에만 신호(CACT)를 활성 상태로 하기 위해 제어 회로(100)에 포함되는 부분 회로(1100)를 나타낸 도면이다.

도 6은 도 5에 나타낸 회로로부터의 출력을 수신하여 소정의 사이클수의 기간에만 신호(/CACT)를 활성 상태로 하기 위한 제어 회로(100)의 부분 회로(1200)의 구성을 나타낸 개략 블럭도이다.

도 5를 참조하여, 회로(1100)는, 신호(ext. /RAS)의 반전 신호인 신호(RAS), 신호(ext. /CAS), 신호(ext. /CS) 및 신호(ext. /WE)의 반전 신호인 신호(WE)를 수신하는 4입력 NAND회로(1002)와, NAND회로(1002)의 출력을 수신하고, 내부 클럭 신호(int. CLK1) 및 그 반전 신호(int. /CLK1)로 제어되어 신호(READ)를 출력하는 클럭인버터회로(1104)를 포함한다.

도 6을 참조하여, 회로(1200)는, CAS 레이텐시(CL) 및 내부 클럭 신호(int. CLK1)를 수신하여 신호(READ)의 활성화에 따라, 계수동작을 개시하고, 계수한 내부 클럭 신호(int. CLK1)의 사이클수가 CAS 레이텐시(CL)와 일치하는 것에 따라, 출력신호의 레벨을 활성 상태로 하는 카운터(1202)와, 카운터(1202)의 출력신호 레벨의 활성화에 따라 계수동작을 개시하여 내부 클럭 신호(int. CLK1)의 사이클수를 계수하고, 버스트 길이(BL)와 일치한 시점에서 출력신호 레벨을 활성 상태로 하는 카운터(1204) 및, 신호(READ)의 활성화에 따라 신호(/CACT)를 활성 상태로 하고, 카운터(1204)의 출력신호의 활성화에 따라 신호(/CACT)를 불활성 상태로 하는 래치회로(1206)를 포함한다.

도 5 및 도 6에 나타낸 회로(1100, 1200)의 구성에 의해 도 4에 나타낸 바와 같은 신호(/CACT)를 생성할 수 있게 된다.

(실시 형태2)

실시 형태1에서의 SDRAM(1000)에 있어서는, 제2 입력 초단 버퍼 회로(200)는 판독 동작모드에 있어서만 활성 상태로 되는 구성이었다.

실시 형태2의 SDRAM에 있어서는, 제2 입력 초단 버퍼 회로(200)는 SDRAM(1000)이 활성 상태, 즉 행계 회로의 동작이 활성 상태로 된 후, 판독 동작이 종료하여 행계 회로 등의 프리챠지 동작이 개시되기까지의 기간에 있어서 제2 입력 초단 버퍼 회로(200)가 활성 상태로 되는 구성으로 되어 있다.

그 외의 다른 점은 도 1에 나타낸 SDRAM(1000)의 구성과 동일하기 때문에, 그에 대한 설명은 생략한다.

도 7은 제어 회로(100)에 포함되고, 제2 입력 초단 버퍼 회로(200)의 동작을 제어하기 위한 제어 신호(/CACT)를 발생하는 초단버퍼제어 회로의 제1 부분 회로(1300)를 나타낸 도면이고, 도 8은 초단버퍼제어 회로의 제2 부분 회로(1400)의 구성을 나타낸 개략 블럭도이다.

제1 부분 회로(1300)는, 신호(ext. /RAS), 신호(ext. /CAS)의 반전 신호의 신호(/CAS), 신호(ext. /CS), 신호(ext. /WE)의 반전 신호의 신호(WE)를 수신하는 4입력 NAND회로(1302)와, NAND회로(1302)의 출력을 수신하여 신호(int. CLK1) 및 그 반전 신호(int. /CLK1)로 제어되어 신호(ACT)를 출력하는 클럭인버터회로(1304), 신호(ext. /RAS), 신호(CAS), 신호(ext. /CS) 및 신호(ext. /WE)를 수신하는 4입력 NAND회로(1306) 및, NAND회로(1306)의 출력을 수신하여 신호(int. CLK1, int. /CLK1)로 제어되어 신호(PRC)를 출력하는 클럭인버터회로(1308)를 포함한다.

도 8을 참조하여, 제2 부분 회로(1400)는 신호(PRC)의 반전 신호와 신호(ACT)를 수신하는 NOR회로(1402)와, 신호(PRC)와 신호(ACT)의 판정신호를 수신하는 NOR회로(1404) 및, NOR회로(1406, 1408)를 교차 접속시켜 구성시키는 SR 플립플롭회로(1410)를 포함한다.

여기서, NOR회로(1402)의 출력은, SR 플립플롭회로(1410)의 리세트신호로서 입력하고, NOR회로(1404)의 출력은 SR 플립플롭회로의 세트신호(S)로서 입력한다. SR 플립플롭회로(1410)의 반전출력이 신호(/CACT)로서 출력된다.

도 9는 본 발명의 실시 형태2의 SDRAM의 동작을 설명하기 위한 타이밍차트이다.

도 4에 나타낸 실시 형태1의 SDRAM(1000)의 동작과 다른 점은 이하와 같다.

즉, 본 실시 형태에 있어서는, 시각(t1)에 있어서 신호(ext. /CS) 및 신호(ext. /RAS)가 활성 상태로 되어 행 어드레스 신호가 취득된 후, 시각(t3)에 있어서 신호(ext. /CS) 및 신호(ext. /CAS)가 활성 상태로 되어 열 어드레스 신호가 취득되면, 시각(t5)에 있어서 데이타의 출력이 개시되는 점에서는 실시 형태1의 SDRAM(1000)의 동작과 동일하다.

그러나, 버스트 길이(BL)가 2이고, 시각(t6)에 있어서 2비트째의 판독 데이타(DQ2)가 출력되는 시점에 있어서는, 신호(ext. /CS, ext. /RAS, ext. /WE)는 활성 상태로 되지 않고, 프리챠지상태의 지정은 행해지지 않는다. 계속해서, 시각(t13)에 있어서 재차 데이타의 판독이 행해지고, 버스트 길이로 지정된 데이타만큼 데이타의 출력이 행해지는 시각(t14)에 있어서, 신호(ext. /CS, ext. /RAS, ext. /WE)가 활성 상태로 되어 행계 회로의 프리챠지동작의 지정이 행해진다.

즉, 도 9에 나타낸 실시 형태2의 SDRAM의 동작에 있어서는, 시각(t1)에 있어서 행계 회로의 활성화가 지시된 후, 시각(t14)에 있어서 프리챠지동작이 지정되어 행계 회로의 프리챠지동작이 지시되기까지의 기간은, 그 사이에 2회 내지는 그 이상의 회수의 판독 동작이 존재하는 경우에 있어서도 신호(/CACT)는 활성 상태를 유지한다.

이에 대해, 실시 형태1의 SDRAM(1000)에 있어서는, 리드동작이 종료할 때에 프리챠지동작이 개시되기 때문에, 계속해서 판독 동작을 행할 경우에는, 이 프리챠지동작이 완료하기까지의 기간만큼 여분으로 시간이 필요하게 된다.

즉, 실시 형태2의 SDRAM은, 연속해서 판독 모드가 지정되도록 한 경우에 있어서, 보다 고속의 동작을 행할 수 있다.

(실시 형태3)

도 10은 본 발명의 실시 형태3의 SDRAM(2000)의 구성을 나타낸 개략 블럭도이다.

도 1에 나타낸 실시 형태1의 SDRAM(1000)의 구성과 다른 점은, 이하와 같다.

제1로는, 각 메모리셀 플레인(M#0 ~ M#3)이 각각 4개의 메모리셀 블록(MB0 ~ MB3)으로 분할되어 있는 점이다.

더욱이, 각 메모리셀 블록(MB0 ~ MB3)마다 대응하여, 행 디코더(106a ~ 106d)가 각각 설치되고, 각 메모리셀 블록에 대응하여 각각 열 디코더(108a ~ 108d) 및 입출력 회로(110a ~ 110d)가 설치되어 있다.

여기서, 도 10에 있어서는, 열 디코더 및 입출력 회로를 1개의 블록으로 나타내고 있다.

더욱이, 메모리셀 블럭쌍(MB0, MB1) 및 또 1개의 메모리셀 블럭쌍(MB2, MB3)마다 로컬클럭 발생 회로(300, 302)가 설치되는 구성으로 되어 있다. 즉, 제2 클럭 발생 회로(204)의 출력의 내부 클럭 신호는, 출력 버퍼(118)에서가 아니라, 로컬클럭 발생 회로(300, 302)에 대해 부여되는 구성으로 되어 있다. 이에 따라, 로컬클럭 발생 회로(300, 302)는 대응하는 메모리셀 블록에 대해 내부 클럭 신호를 공급한다.

또한, 입출력 회로(110)로부터 출력된 데이타는, 일단 각 메모리셀 블록에 대응하여 설치되어 있는 버스 드라이버 회로(304a ~ 304d)에 있어서 그 값이 유지되는 구성으로 되어 있다. 더욱이, 선택된 메모리셀에 따라 버스 드라이버 회로(304a ~ 304d)의 어느 한쪽으로부터 출력된 판독 데이타는, 버스 드라이버 회로(304a ~ 304d)에 대해 공통으로 접속하는 중간래치회로(306)에 있어서 재차 유지되는 구성으로 되어 있다.

중간 버퍼 회로(306)는 유지되어 있는 판독 데이타를 출력 버퍼(118)에 대해 부여되는 구성으로 되어 있다.

또한, 도 10에 있어서는, 메모리셀 플레인(M#2, M#3)에 대응하는 구성만을 나타냈지만, 동일한 구성이 메모리셀 플레인(M#0, M#1)에 대응해서도 존재하고 있다.

또한, 도 10에 있어서는, 출력 버퍼(118)에는 도시를 용이하게 하기 위해, 메모리셀 플레인(M#2, M#3)으로부터의 판독 데이타가 부여되는 구성이지만, 도 1의 구성과 본질적으로 상위하지는 않다.

그 외, 도 1에 나타낸 실시 형태1의 SDRAM(1000)과 동일부분에는 동일 참조부호를 부치고, 그에 대한 설명은 생략한다.

도 11은 도 10에 나타낸 SDRAM(2000)의 구성에 있어서, 도시되지 않은 외부어드레스 입력 패드 및 열어드레스버퍼를 포함하여, 메모리셀 블록으로부터 출력 버퍼까지의 신호의 흐름을 나타내기 위한 모식도이다.

이하에서는, 외부로부터 부여된 행 어드레스 신호에 따라, 1개의 워드선(WL)이 이미 선택되어 있는 것으로 한다.

계속해서, 외부어드레스 입력 패드(310)에 부여된 열 어드레스 신호(Yb)를 수신하여, 열어드레스버퍼(312)는 프리디코더(314)에 대해 열 어드레스 신호를 출력한다.

여기서, 프리디코더(314)중에는 래치회로가 포함되고, 열어드레스버퍼(312)로부터 출력된 열 어드레스 신호는 도 10에 나타낸 제1 클럭 발생 회로(102)로부터의 내부 클럭 신호(int. CLK1)의 활성화에 따라, 어드레스버퍼(312)로부터의 데이타의 래치 동작을 행한다.

계속해서, 프리디코더(314)에 있어서 선택된 메모리셀 블록에 대해, 대응하는 열 어드레스 신호가 부여된다. 이에 따라, 열 디코더(108)는 대응하는 열의 선택을 행한다.

즉, 선택된 워드선(WL)에 접속하는 메모리셀(MC)의 기억 데이타에 따라, 센스앰프(316)는 대응하는 비트선쌍(BL, /BL)의 전위차를 증폭한다. 이 센스앰프(316)에 의해 증폭된 전위레벨은, 열 디코더(108)에 의해 제어된 트랜스퍼 게이트(320)를 매개로 로컬 IO선쌍(도시하지 않음)에 전달된 후, 글로벌 IO선쌍(GI/O, /GI/O)으로 전달된다.

글로벌 IO선쌍(GI/O, /GI/O)까지 판독된 기억 데이타는 프리앰프(318)에 의해 증폭되고, 버스 드라이버(304)로 전달된다. 버스 드라이버(304)에는, 후에 설명하는 바와 같이 래치회로가 포함되어 있고, 이 버스 드라이버(304)의 래치회로는 로컬 클럭 발생 회로(300 또는 302)로부터 출력되는 내부클럽신호(int. CLKL)에 의해 제어된다.

계속해서, 버스 드라이버(320)에 의해 구동되는 데이타버스의 출력에 따라, 중간 버퍼(306)는 내부 클럭 신호(int. CLKL)에 따라 동작하는 래치회로에 의해 그 데이타를 유지하고, 또한 출력한다.

중간 버퍼(306)로부터의 출력을 수신하여, 출력 버퍼(118)는 제1 클럭 발생 회로로부터의 내부 클럭 신호(int. CLK1)에 따라 데이타를 유지하고, 또한 대응하는 데이타 입출력 패드(114)의 전위레벨을 판독 데이타에 따라 구동한다.

즉, 실시 형태3의 SDRAM(2000)에 있어서는, 메모리셀 블록으로부터 판독되고, 프리앰프에 의해 증폭된 판독 데이타의 버스 드라이버(304)에서의 데이타 래치 동작 및 중간 버퍼(306)가 데이타 래치 동작은, 로컬 클럭 발생 회로(300 또는 302)로부터의 내부 클럭 신호(int. CLKL)에 의해 제어되는 구성으로 되어 있다.

도 12는 도 11에 나타낸 버스 드라이버(304), 중간 버퍼(306) 및 출력 버퍼 회로(118)의 구성을 나타낸 블럭도이다.

이하에서는, 버스 드라이버(304)의 구성으로서 설명하지만, 중간 버퍼 또는 출력 버퍼에 있어서도 그 제어되는 내부 클럭 신호만이 다르고, 그 기본적인 구성은 전부 동일하다.

버스 드라이버(304)는, 클럭 신호(CLKL)가 "L"레벨에 있어서 도통상태로 되는 트랜스미션 게이트(3042)와, 트랜스미션 게이트(3042)의 출력을 수신하여 유지하는 래치회로(3044), 래치회로(3044)의 출력을 수신하여 반전시키는 인버터(3046), 인버터(3046)의 출력을 수신하여 내부 클럭 신호(int. CLKL)가 "H"레벨에 있어서 도통상태로 되는 트랜스미션 게이트(3048), 트랜스미션 게이트(3048)의 출력을 수신하여 유지하는 래치회로(3050) 및, 래치회로(3050)의 출력을 수신하여 반전시켜 출력하는 인버터(3052)를 포함한다.

즉, 래치회로(3050) 및 인버터(3052)로, 출력측을 구동하는 인버터회로가 구성된다.

도 12에 나타낸 그 구성으로부터 분명한 바와 같이, 버스 드라이버(304)는 내부 클럭 신호(int. CLKL)가 "L"레벨인 상태에 있어서 데이타의 취득을 행하고, 그 데이타를 클럭 신호(int. CLKL)가 "H"레벨인 시점에서 래치회로(3050)로 전달하며, 그 데이타를 외부로 출력하는 구성으로 되어 있다.

도 13은 도 10 및 도 11에 나타낸 SDRAM(2000)의 동작을 설명하기 위한 타이밍차트이다.

시각(t1)에 있어서 신호(ext. /CS) 및 신호(ext. /RAS)가 활성 상태로 되는 것에 따라 행 어드레스 신호가 취득되고, 시각(t3)에 있어서 신호(ext. /CS) 및 신호(ext. /CAS)가 활성 상태로 되는 것으로 열 어드레스 신호의 취득이 행해지는 것은 실시 형태1의 SDRAM(1000)과 동일하다.

또한, 본 실시 형태에 있어서는, 시각(t1)에 있어서 행계 회로가 활성으로 되는 것에 따라, 제2 입력 초단 버퍼 회로(200)의 동작을 활성화하는 신호(/CACT)가 활성 상태("L"레벨)로 되는 것으로 한다.

단, 도 4에 나타낸 바와 같이, 판독 동작에 있어서만 이 신호(/CACT)가 활성 상태로 되는 구성으로 하는 것도 가능하다.

도 13에 나타낸 구성에 있어서는, CAS 레이텐시(CL)는 4로 설정되어 있는 것으로 한다.

따라서, 시각(t3)으로부터 4사이클 후의 시각(t7)에 있어서 데이타의 출력이 개시되게 된다.

이하에서는, 도 11을 참조하여 신호(ext. /CAS)가 활성 상태로 되어 열 어드레스 신호(Yb)가 취득되는 시각(t3)으로부터 데이타출력이 개시되는 시각(t7)까지의 동작에 관하여 보다 상세히 설명하기로 한다.

시각(t3)에 있어서, 열 어드레스 신호가 취득되는 시점에서는, 제1 클럭 발생 회로(102)로부터의 내부 클럭 신호(int. CLK1)에 따라 프리디코더(314)에서의 열 어드레스 신호의 래치 동작 및 프리디코드 동작이 행해진다.

프리디코더(314)로부터 출력되는 내부 열 어드레스 신호에 따라, 열 디코더(108)가 대응하는 열의 선택을 행하고, 글로벌 IO선쌍(GI/O, /GI/O)에 판독 데이타가 전달되며, 프리앰프(318)에 의해 증폭동작이 행해진다.

시각(t4)에 있어서는, 프리앰프(318)에 의해 동작된 판독 데이타는, 내부 클럭 신호(int. CLKL)에 의해 증폭되는 버스 드라이버(304)에 있어서 래치되고, 대응하는 데이타가 데이타버스로 출력된다.

계속해서, 시각(t5)에 있어서 데이타버스상의 판독 데이타는, 중간 버퍼(306)에 있어서 내부 클럭 신호(int. CLKL)에 동기하여 래치되고, 출력 버퍼(118)에 대해 출력된다.

시각(t6)에 있어서, 출력 버퍼(118)는 제1 클럭 발생 회로로부터의 내부 클럭 신호(int. CLK1)에 따라, 중간 버퍼(306)로부터의 데이타를 래치하고, 또한 데이타 입출력 패드(114)에 대해 판독 데이타의 출력을 행한다.

즉, 실시 형태3의 SDRAM(1000)에 있어서는, 프리앰프에서 증폭후, 출력 버퍼 회로에 데이타가 전달되기까지의 SDRAM의 파이프라인 동작에서의 데이타 래치 동작이, 로컬 클럭 발생 회로(300 또는 302)로부터 출력되는 내부 클럭 신호(int. CLKL)에 의해 제어되는 구성으로 되어 있다.

이 때문에, 실시 형태1의 SDRAM(1000)에 있어서는, 외부 클럭 신호가 제1 입력 초단 버퍼 회로(202)에 의해 버퍼 처리된 후, 제1 클럭 발생 회로(102)에 의해 발생되는 내부 클럭 신호(int. CLK1)에 있어서, 상기 일련의 동작이 동기하여 제어되는 구성으로 되어 있다. 이 때문에, 이들 동작의 고속화를 도모하기 위해서는, 제1 입력 초단 버퍼 회로 및 제1 클럭 발생 회로(102)의 동작 능력을 증대시킬 필요가 있고, 이들 회로를 구성하는 트랜지스터 크기를 크게 하기도 하며, 또는 버퍼를 구성하는 인버터 등의 단수를 증가시킬 필요가 있었다.

이에 대해, 실시 형태2의 SDRAM(2000)에 있어서는 도 13에 나타낸 제2 스테이지(프리앰프(318)로부터의 판독 데이타를 버스 드라이버가 래치하는 사이클) 및 제3 스테이지(버스 드라이버(304)로부터의 판독 데이타를 중간 버퍼(306)가 유지하는 사이클)의 동작이, 독립한 로컬 클럭 발생 회로(300 또는 302)로부터의 출력의 내부 클럭 신호(int. CLKL)에 의해 제어되는 구성으로 되어 있기 때문에, 칩 중앙부로부터 로컬 클럭 발생 회로까지의 배선 길이가 메모리용량의 대용량화와 더불어 길게 되고, 이 배선의 시정수가 판독 동작의 크리티컬버스로 된 경우에서도, 이 배선의 전위를 구동하는 구동 회로의 단수의 삭감이나, 내부 클럭 신호의 스큐의 발생 등을 완화하는 것으로, 저소비전력으로 고속의 동작을 도모할 수 있게 된다.

도 14는 실시 형태3의 SDRAM(2000)의 변형예의 SDRAM(3000)의 구성을 나타낸 개략 블럭도이다.

도 10에 나타낸 실시 형태3의 SDRAM(2000)의 구성과 다른 점은, 출력 버퍼 회로(118)가 제2 클럭 발생 회로(204)로부터의 내부 클럭 신호(int. CLK2)에 의해 제어되는 구성으로 되어 있는 점이다.

그 외는, 도 10에 나타낸 실시 형태3의 SDRAM(2000)의 구성과 동일하기 때문에, 동일부분에는 동일 부호를 부치고 그에 대한 설명은 생략한다.

실시 형태3의 SDRAM(3000)에 있어서는, 출력 버퍼 회로(118)가 제2 클럭 발생 회로(204)로부터 출력되는 내부 클럭 신호(int. CLK2)에 의해 제어되는 구성으로 되어 있기 때문에, 실시 형태1에 있어서 설명한 바와 같이, 출력 버퍼 회로가 칩 중앙부로부터 떨어진 칩 단부에 위치하고 있는 경우에도, 외부 클럭 신호에 따라 발생되는 내부 클럭 신호의 전달에 필요한 지연시간을 절감할 수 있고, 동작 가능한 클럭주파수를 증가시킬 수 있게 된다.

더욱이는, 이와 같은 구성으로 한 경우에 있어서도, 제2 클럭 발생 회로(204)에 대해 외부 클럭 신호를 전달하는 입력 초단 버퍼 회로(200)는, 신호(/CACT)에 의해 제어되고, SDRAM(3000)의 데이타 판독 모드 기간 또는 활성기간에만 있어서 동작하는 구성으로 되어 있기 때문에, 고속의 억세스를 할 수 있기 때문에 그를 구성하는 트랜지스터 크기 등을 증가시킨 경우에도 대기상태에서의 소비전력의 증대를 제어할 수 있게 된다.

(실시 형태4)

실시 형태의SDRAM의 기본적인 구성은, 이하에 설명하는 점을 제하면, 도 1에 나타낸 SDRAM(1000)의 구성과 동일하다.

즉, 실시 형태4의 SDRAM에 있어서는, 실시 형태1의 SDRAM(1000)의 구성에 있어서, 제2 클럭 발생 회로(204)로부터 출력 버퍼 회로(118)에 대해 내부 클럭 신호(int. CLK2)를 전달하는 배선(206 또는 208)의 배선폭 또는 인접하는 배선과의 배선각 거리를 보다 고속 동작에 적당한 구성으로 하고 있다.

도 15는 배선(206 또는 208)과 인접하는 다른 배선과의 관계를 모식적으로 나타낸 도면이다.

여기서, 배선폭을 L, 배선간 거리를 S로 표시하기로 한다.

도 16은 배선 피치, 즉 배선폭(L)과 배선간 거리(S)의 합에 대한 배선 지연시간과 배선 면적의 관계를 나타낸 그래프이다.

여기서는, 배선폭(L)과 배선간 거리(S)의 비를 1로 고정한 경우에 관하여 나타내고 있다.

배선폭에 대한 배선간 거리가 일정치로 유지되어 있는 경우, 배선 지연은 피치의 증가에 따라 초기적으로는 감소해 간다. 이는, 배선폭의 증대에 따라 배선저항이 감소하기 때문이다.

단, 배선 피치가 4㎛를 초과하면, 반대로 배선 지연량은 증대해 간다. 이는, 배선폭이 증대함으로써, 대지용량이 증대하고, 반대로 배선 지연량이 증가해 가기 때문이다.

즉, 배선 지연에는, 배선폭과 배선간 거리를 일정하게 한 경우, 최적치가 존재하게 된다.

그러나, 배선 지연의 크기만으로 배선폭을 결정하는 것은, 배선 면적의 관점에서 보면 타당하지 않다.

즉, 배선 피치가 증대함에 따라, 배선 면적은 동일하게 증가해 가기 때문에, 단순히 배선 지연의 최적점이 칩 면적 등도 고려한 경우의 최적점인 것으로 한정되지 않는다.

여기서, 반대로 칩 면적 등도 고려하여 배선 지연을 결정하는 것으로 하면, L/S=1㎛/1㎛ 정도가 최적점으로 된다.

이 때문에, 칩 내부의 신호선은, 거의 이 피치로 레이아웃되어 있다. 그러나, 클럭 신호를 전달하는 배선은 고속성이 요구되기 때문에, 배선 피치를 최적점으로 설정하는 것으로 하면, 도 16에 나타낸 바와 같이 L/S=2㎛/2㎛가 최적으로 된다.

L/S의 비가 1인 경우, 상술한 바와 같이 L/S=2㎛/2㎛ 정도가 최적으로 되지만, L/S<1로 하면 배선 지연은 더 작게 할 수 있게 된다.

또한, 배선폭(L) 및 배선간 거리(S)의 최적점은, 배선의 두께, 배선주위 절연막의 유전율 등에 의해서도 변화한다.

따라서, 클럭배선에 대한 배선폭(L) 또는 배선간 거리(S)는, 그 주위에 사용되어 있는 배선의 배선폭 혹은 배선간 거리보다도 크게 할 필요가 있고, 클럭배선의 배선폭 또는 배선간 거리는 주위의 배선에 비해 1.5배 이상의 값으로 할 필요가 있다.

이와 같은 갑으로 함으로써, 다른 신호 배선보다도 고속 동작이 요구되는 클럭 신호 배선의 배선 지연을, 칩전체로서 나타난 경우에 최적화할 수 있게 된다.

청구항 제1항 기재의 동기형 다이나믹형 반도체 기억 장치는, 출력 버퍼 회로를 구동하기 위한 내부 클럭 신호를 발생하는 클럭 발생 수단을 독립한 구성으로 했기 때문에, 출력 버퍼 회로로의 내부 클럭 신호의 전달이, 데이타 판독 동작에 있어서 크리티컬패스로 되는 경우에 있어서도, 그 동작 속도를 향상시킬 수 있다.

청구항 제2항 기재의 동기형 다이나믹형 반도체 기억 장치는, 제어 회로나, 제1 및 제2 클럭 발생 수단이, 짝수개의 메모리셀 플레인의 배치되어 있지 않은 칩 중앙의 여유영역에 배치되는 구성으로 되어 있기 때문에, 칩의 행 및 열의 어느 한쪽의 방향으로부터 보아도, 각 메모리셀 플레인에 대한 제어 수단 등으로부터의 배선 길이가 최단으로 되도록 배치할 수 있고, 배선 지연에 의한 억세스 시간의 증대를 억제할 수 있다. 더욱이, 데이타 출력 수단으로의 내부 클럭 신호는, 독립한 제2 클럭 발생 수단에 의해 공급되기 때문에, 데이타 출력 수단으로의 내부 클럭 신호의 전달지연을 억제할 수 있고, 억세스 시간의 증대를 억제할 수 있다.

Claims (2)

- 일련의 펄스열로 이루어진 외부 클럭 신호에 동기하여 제어 신호 및 어드레스 신호를 포함하는 복수의 외부 신호를 취득하고, 또한 기억 데이타를 출력하는 장방형 형상의 동기형 다이나믹형 반도체 기억 장치에 있어서,행렬 형상으로 배치된 복수의 메모리셀을 갖는 메모리셀 어레이와,상기 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제1 클럭 발생 수단과,상기 내부 클럭 신호 및 상기 외부 신호에 따라, 상기 동기형 다이나믹형 반도체 기억 장치의 데이타 출력 동작을 제어하는 제어 수단 및,상기 복수의 외부 신호를 수신하고, 또는 상기 기억 데이타를 출력하여 상기 장방형 형상의 제1변 방향에 따라 배치되는 복수의 입출력 단자를 구비하고,상기 복수의 입출력 단자는,상기 외부 클럭 신호를 수신하는 외부 클럭 입력 단자와,상기 외부 클럭 입력 단자 및 상기 제어 수단을 끼우도록 배치되는 제1 및 제2 데이타 입출력 단자를 포함하며,상기 제어 수단에 의해 제어되고, 상기 제1 클럭 발생 수단으로부터의 상기 내부 클럭 신호에 동기하여 외부로부터의 행 어드레스 신호에 따라 상기 메모리셀 어레이의 대응하는 행을 선택하는 행 선택 수단과,상기 제어 수단에 의해 제어되고, 상기 제1 클럭 발생 수단으로부터의 상기 내부 클럭 신호에 동기하여 열 어드레스 신호에 따라 상기 메모리셀 어레이의 대응하는 복수의 열을 선택하고, 선택된 상기 행 및 열에 대응하는 복수의 상기 메모리셀의 기억 데이타를 판독하는 열선택 수단과,상기 외부 클럭 입력 단자로부터의 상기 외부 클럭 신호를 수신하여, 내부 클럭 신호를 출력하는 제2 클럭 발생 수단, 및상기 열선택 수단으로부터의 대응하는 상기 기억 데이타를 수신하여, 상기 제2 클럭 발생 수단으로부터 직접 수신하는 상기 내부 클럭 신호에 동기하여, 대응하는 상기 제1 및 제2 데이타 입출력 단자에 상기 기억 데이타를 각각 출력하는 제1 및 제2 데이타 출력 수단을 더 구비하는 것을 특징으로 하는 동기형 다이나믹형 반도체 기억 장치.

- 일련의 펄스열로 이루어진 외부 클럭 신호에 동기하여, 제어 신호 및 어드레스 신호를 포함하는 복수의 외부 신호를 취득하고, 또한 기억 데이타를 출력하는 장방형 형상의 동기형 다이나믹형 반도체 기억 장치에 있어서,상기 장방형 형상의, 적어도 긴 변 방향의 중심축 및 짧은 변 방향의 중심축의 어느 한쪽을 따르는 소정의 폭을 갖는 여유 영역을 남기도록 배치되고, 각각이 행렬 형상으로 배치되는 복수의 메모리셀을 포함하는 짝수개의 메모리셀 플레인을 구비하고,상기 여유 영역은,상기 외부 클럭 신호를 수신하여, 내부 클럭 신호를 출력하는 제1 클럭 발생 수단과,상기 내부 클럭 신호 및 상기 외부 신호에 따라, 상기 동기형 다이나믹형 반도체 기억 장치의 데이타 출력 동작을 제어하는 제어 수단, 및상기 복수의 외부 신호를 수신하고, 또는 상기 기억 데이타를 출력하여, 상기 여유 영역에 연하는 중심축 방향을 따라 배치되는 복수의 입출력 단자를 포함하며,상기 복수의 입출력 단자는,상기 외부 클럭 신호를 수신하는 외부 클럭 입력 단자와,상기 외부 클럭 입력 단자 및 상기 제어 수단을 끼우도록 배치되는 제1 및 제2 데이타 입출력 단자를 갖고,상기 여유 영역은,상기 제어 수단에 의해 제어되고, 상기 제1 클럭 발생 수단으로부터의 상기 내부 클럭 신호에 동기하여 외부로부터의 행 어드레스 신호에 따라 상기 메모리셀 플레인의 대응하는 행을 선택하는 행 선택 수단과,상기 제어 수단에 의해 제어되고, 상기 제1 클럭 발생 수단으로부터의 상기 내부 클럭 신호에 동기하여 열 어드레스 신호에 따라 상기 메모리셀 플레인의 대응하는 복수의 열을 선택하고, 선택된 상기 행 및 열에 대응하는 복수의 상기 메모리셀의 기억 데이타를 판독하는 열선택 수단,상기 외부 클럭 입출력 단자로부터의 상기 외부 클럭 신호를 수신하여 내부 클럭 신호를 출력하는 제2 클럭 발생 수단, 및상기 열선택 수단으로부터의 대응하는 상기 기억 데이타를 수신하여, 상기 제2 클럭 발생 수단으로부터 직접 수신하는 상기 내부 클럭 신호에 동기하여, 대응하는 상기 제1 및 제2 데이타 입출력 단자에 상기 기억 데이타를 각각 출력하는 제1 및 제2 데이타 출력 수단을 더 포함하는 것을 특징으로 하는 동기형 다이나믹형 반도체 기억 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04388897A JP3825862B2 (ja) | 1997-02-27 | 1997-02-27 | 同期型ダイナミック型半導体記憶装置 |

| JP97-043888 | 1997-02-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980069874A KR19980069874A (ko) | 1998-10-26 |

| KR100261640B1 true KR100261640B1 (ko) | 2000-07-15 |

Family

ID=12676251

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970037180A KR100261640B1 (ko) | 1997-02-27 | 1997-08-04 | 동기형 다이나믹형 반도체 기억 장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5812490A (ko) |

| JP (1) | JP3825862B2 (ko) |

| KR (1) | KR100261640B1 (ko) |

Families Citing this family (50)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3099931B2 (ja) * | 1993-09-29 | 2000-10-16 | 株式会社東芝 | 半導体装置 |

| KR0158762B1 (ko) * | 1994-02-17 | 1998-12-01 | 세키자와 다다시 | 반도체 장치 |

| JP3421441B2 (ja) * | 1994-09-22 | 2003-06-30 | 東芝マイクロエレクトロニクス株式会社 | ダイナミック型メモリ |

| US6804760B2 (en) | 1994-12-23 | 2004-10-12 | Micron Technology, Inc. | Method for determining a type of memory present in a system |

| US6525971B2 (en) | 1995-06-30 | 2003-02-25 | Micron Technology, Inc. | Distributed write data drivers for burst access memories |

| US5526320A (en) | 1994-12-23 | 1996-06-11 | Micron Technology Inc. | Burst EDO memory device |

| US5610864A (en) | 1994-12-23 | 1997-03-11 | Micron Technology, Inc. | Burst EDO memory device with maximized write cycle timing |

| US6401186B1 (en) | 1996-07-03 | 2002-06-04 | Micron Technology, Inc. | Continuous burst memory which anticipates a next requested start address |

| JP4090088B2 (ja) * | 1996-09-17 | 2008-05-28 | 富士通株式会社 | 半導体装置システム及び半導体装置 |

| US5959937A (en) * | 1997-03-07 | 1999-09-28 | Mitsubishi Semiconductor America, Inc. | Dual clocking scheme in a multi-port RAM |

| US6072743A (en) | 1998-01-13 | 2000-06-06 | Mitsubishi Denki Kabushiki Kaisha | High speed operable semiconductor memory device with memory blocks arranged about the center |

| US6151257A (en) * | 1998-01-26 | 2000-11-21 | Intel Corporation | Apparatus for receiving/transmitting signals in an input/output pad buffer cell |

| JPH11219598A (ja) * | 1998-02-03 | 1999-08-10 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US5936877A (en) | 1998-02-13 | 1999-08-10 | Micron Technology, Inc. | Die architecture accommodating high-speed semiconductor devices |

| KR100306881B1 (ko) * | 1998-04-02 | 2001-10-29 | 박종섭 | 동기 반도체 메모리를 위한 인터페이스 |

| JP3125749B2 (ja) * | 1998-06-11 | 2001-01-22 | 日本電気株式会社 | 同期型半導体メモリ |

| JP4540137B2 (ja) * | 1998-07-24 | 2010-09-08 | ルネサスエレクトロニクス株式会社 | 同期型半導体記憶装置 |

| US6081477A (en) * | 1998-12-03 | 2000-06-27 | Micron Technology, Inc. | Write scheme for a double data rate SDRAM |

| JP3557114B2 (ja) * | 1998-12-22 | 2004-08-25 | 株式会社東芝 | 半導体記憶装置 |

| JP2000207900A (ja) * | 1999-01-12 | 2000-07-28 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| US6356981B1 (en) * | 1999-02-12 | 2002-03-12 | International Business Machines Corporation | Method and apparatus for preserving data coherency in a double data rate SRAM |

| US6088254A (en) * | 1999-02-12 | 2000-07-11 | Lucent Technologies Inc. | Uniform mesh clock distribution system |

| KR100358121B1 (ko) | 1999-05-13 | 2002-10-25 | 주식회사 하이닉스반도체 | 반도체장치의 신호 입력회로 |

| KR100324821B1 (ko) | 1999-06-29 | 2002-02-28 | 박종섭 | 반도체 메모리 소자의 자동 리프레쉬 방법 및 장치 |

| KR100299187B1 (ko) * | 1999-07-15 | 2001-11-01 | 윤종용 | 반도체 메모리 장치 및 이 장치의 데이터 리드 방법 |

| DE19933540C2 (de) | 1999-07-16 | 2001-10-04 | Infineon Technologies Ag | Synchroner integrierter Speicher |

| JP3668064B2 (ja) | 1999-08-27 | 2005-07-06 | 株式会社東芝 | 半導体記憶装置 |

| JP2001067866A (ja) | 1999-08-30 | 2001-03-16 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| JP4353324B2 (ja) * | 1999-08-31 | 2009-10-28 | エルピーダメモリ株式会社 | 半導体装置 |

| JP2001084762A (ja) * | 1999-09-16 | 2001-03-30 | Matsushita Electric Ind Co Ltd | 半導体メモリ装置 |

| KR100374638B1 (ko) | 2000-10-25 | 2003-03-04 | 삼성전자주식회사 | 입출력데이타의 전파경로 및 전파경로들 간의 차이를최소화하는 회로를 구비하는 반도체 메모리장치 |

| KR100382739B1 (ko) * | 2001-04-13 | 2003-05-09 | 삼성전자주식회사 | 비대칭 데이터 경로를 갖는 반도체 메모리 장치 |

| KR100463202B1 (ko) * | 2002-07-02 | 2004-12-23 | 삼성전자주식회사 | 반도체 메모리 장치의 패드 및 주변 회로 레이아웃 |

| US7006402B2 (en) * | 2003-08-29 | 2006-02-28 | Hynix Semiconductor Inc | Multi-port memory device |

| KR100550643B1 (ko) * | 2004-09-06 | 2006-02-09 | 주식회사 하이닉스반도체 | 반도체메모리소자 |

| US7382591B2 (en) * | 2005-05-20 | 2008-06-03 | Intel Corporation | Cascode protected negative voltage switching |

| US7369453B2 (en) * | 2006-02-28 | 2008-05-06 | Samsung Electronics Co., Ltd. | Multi-port memory device and method of controlling the same |

| JP4267006B2 (ja) * | 2006-07-24 | 2009-05-27 | エルピーダメモリ株式会社 | 半導体記憶装置 |

| US20090109772A1 (en) * | 2007-10-24 | 2009-04-30 | Esin Terzioglu | Ram with independent local clock |

| KR100940838B1 (ko) * | 2008-06-04 | 2010-02-04 | 주식회사 하이닉스반도체 | 반도체 집적회로의 클럭 신호 발생 장치 및 방법 |

| JP5695895B2 (ja) * | 2010-12-16 | 2015-04-08 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体装置 |

| KR102167609B1 (ko) * | 2014-05-13 | 2020-10-20 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그것의 프로그램 방법 |

| JP2020047325A (ja) | 2018-09-18 | 2020-03-26 | キオクシア株式会社 | 半導体記憶装置 |

| US10811057B1 (en) * | 2019-03-26 | 2020-10-20 | Micron Technology, Inc. | Centralized placement of command and address in memory devices |

| US10978117B2 (en) | 2019-03-26 | 2021-04-13 | Micron Technology, Inc. | Centralized placement of command and address swapping in memory devices |

| US10811059B1 (en) | 2019-03-27 | 2020-10-20 | Micron Technology, Inc. | Routing for power signals including a redistribution layer |

| US11031335B2 (en) | 2019-04-03 | 2021-06-08 | Micron Technology, Inc. | Semiconductor devices including redistribution layers |

| JP6734962B1 (ja) * | 2019-04-17 | 2020-08-05 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置 |

| CN114121083A (zh) * | 2020-08-26 | 2022-03-01 | 长鑫存储技术(上海)有限公司 | 接口电路、数据传输电路以及存储器 |

| KR20220028888A (ko) * | 2020-08-31 | 2022-03-08 | 에스케이하이닉스 주식회사 | 저장 장치 및 그 동작 방법 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02194545A (ja) * | 1989-01-23 | 1990-08-01 | Nec Corp | 半導体集積回路 |

| JPH0722511A (ja) * | 1993-07-05 | 1995-01-24 | Mitsubishi Electric Corp | 半導体装置 |

| US5604710A (en) * | 1994-05-20 | 1997-02-18 | Mitsubishi Denki Kabushiki Kaisha | Arrangement of power supply and data input/output pads in semiconductor memory device |

| JP2697634B2 (ja) * | 1994-09-30 | 1998-01-14 | 日本電気株式会社 | 同期型半導体記憶装置 |

| JP3252678B2 (ja) * | 1995-10-20 | 2002-02-04 | 日本電気株式会社 | 同期式半導体メモリ |

-

1997

- 1997-02-27 JP JP04388897A patent/JP3825862B2/ja not_active Expired - Fee Related

- 1997-08-04 KR KR1019970037180A patent/KR100261640B1/ko not_active IP Right Cessation

- 1997-08-18 US US08/912,200 patent/US5812490A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP3825862B2 (ja) | 2006-09-27 |

| KR19980069874A (ko) | 1998-10-26 |

| US5812490A (en) | 1998-09-22 |

| JPH10241363A (ja) | 1998-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100261640B1 (ko) | 동기형 다이나믹형 반도체 기억 장치 | |

| US5537354A (en) | Semiconductor memory device and method of forming the same | |

| US7113446B2 (en) | Latch circuit and synchronous memory including the same | |

| JP3251882B2 (ja) | 半導体記憶装置 | |

| KR100702982B1 (ko) | 반도체 장치 | |

| JP3758860B2 (ja) | 同期型バーストマスクロム及びそのデータ読出方法 | |

| US7826304B2 (en) | Simplified power-down mode control circuit utilizing active mode operation control signals | |

| US6353549B1 (en) | Architecture and package orientation for high speed memory devices | |

| US8059484B2 (en) | Semiconductor storage device and high-speed address-latching method | |

| JP4025488B2 (ja) | 半導体集積回路およびその制御方法 | |

| US11056171B1 (en) | Apparatuses and methods for wide clock frequency range command paths | |

| JP3189745B2 (ja) | 同期式半導体記憶装置 | |

| US20040100856A1 (en) | Semiconductor memory device adaptive for use circumstance | |

| US6636443B2 (en) | Semiconductor memory device having row buffers | |

| KR100499844B1 (ko) | 정렬데이타저장장치및본딩패드를구비한dram구조 | |

| KR100266465B1 (ko) | 내부동작주파수설정가능한dram | |

| US6339560B1 (en) | Semiconductor memory based on address transitions | |

| JP3569417B2 (ja) | 半導体メモリ | |

| KR100536598B1 (ko) | 클럭활성화 시점을 선택하는 반도체메모리장치 | |

| JP4216778B2 (ja) | 半導体装置 | |

| JP3926506B2 (ja) | 半導体記憶装置 | |

| JPH11297072A (ja) | 半導体記憶装置とその制御方法 | |

| JPH09251773A (ja) | 半導体記憶装置 | |

| JP2001101864A (ja) | 同期型半導体記憶装置 | |

| JPH11304892A (ja) | 半導体集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20120418 Year of fee payment: 13 |

|

| FPAY | Annual fee payment |

Payment date: 20130404 Year of fee payment: 14 |

|

| LAPS | Lapse due to unpaid annual fee |