JP5982097B2 - 積層半導体メモリ装置、これを含むメモリシステム及び貫通電極の欠陥リペア方法 - Google Patents

積層半導体メモリ装置、これを含むメモリシステム及び貫通電極の欠陥リペア方法 Download PDFInfo

- Publication number

- JP5982097B2 JP5982097B2 JP2011121586A JP2011121586A JP5982097B2 JP 5982097 B2 JP5982097 B2 JP 5982097B2 JP 2011121586 A JP2011121586 A JP 2011121586A JP 2011121586 A JP2011121586 A JP 2011121586A JP 5982097 B2 JP5982097 B2 JP 5982097B2

- Authority

- JP

- Japan

- Prior art keywords

- input

- defect

- electrode

- memory device

- semiconductor memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

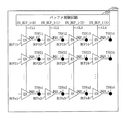

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

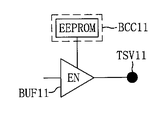

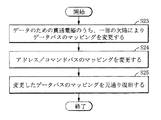

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/70—Masking faults in memories by using spares or by reconfiguring

- G11C29/702—Masking faults in memories by using spares or by reconfiguring by replacing auxiliary circuits, e.g. spare voltage generators, decoders or sense amplifiers, to be used instead of defective ones

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

- H01L22/22—Connection or disconnection of sub-entities or redundant parts of a device in response to a measurement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

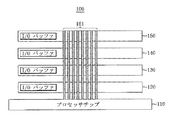

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/18—Assemblies consisting of a plurality of semiconductor or other solid state devices the devices being of the types provided for in two or more different main groups of the same subclass of H10B, H10D, H10F, H10H, H10K or H10N

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Memories (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100051733A KR101728068B1 (ko) | 2010-06-01 | 2010-06-01 | 적층 반도체 메모리 장치, 이를 포함하는 메모리 시스템, 및 관통전극 결함리페어 방법 |

| KR10-2010-0051733 | 2010-06-01 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011253607A JP2011253607A (ja) | 2011-12-15 |

| JP2011253607A5 JP2011253607A5 (enExample) | 2014-06-05 |

| JP5982097B2 true JP5982097B2 (ja) | 2016-08-31 |

Family

ID=45022037

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011121586A Active JP5982097B2 (ja) | 2010-06-01 | 2011-05-31 | 積層半導体メモリ装置、これを含むメモリシステム及び貫通電極の欠陥リペア方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8654593B2 (enExample) |

| JP (1) | JP5982097B2 (enExample) |

| KR (1) | KR101728068B1 (enExample) |

| CN (1) | CN102270504B (enExample) |

| TW (1) | TWI532051B (enExample) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012061633A2 (en) | 2010-11-03 | 2012-05-10 | Netlist, Inc. | Method and apparatus for optimizing driver load in a memory package |

| JP6083576B2 (ja) * | 2011-12-23 | 2017-02-22 | インテル・コーポレーション | メモリデバイス、方法、およびシステム |

| KR20130098681A (ko) * | 2012-02-28 | 2013-09-05 | 삼성전자주식회사 | 반도체 메모리 장치 |

| US9312257B2 (en) | 2012-02-29 | 2016-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9298573B2 (en) | 2012-03-30 | 2016-03-29 | Intel Corporation | Built-in self-test for stacked memory architecture |

| JP2014063974A (ja) * | 2012-08-27 | 2014-04-10 | Ps4 Luxco S A R L | チップ積層体、該チップ積層体を備えた半導体装置、及び半導体装置の製造方法 |

| TWI501361B (zh) | 2012-12-27 | 2015-09-21 | 財團法人工業技術研究院 | 矽穿孔修補電路 |

| US9679615B2 (en) | 2013-03-15 | 2017-06-13 | Micron Technology, Inc. | Flexible memory system with a controller and a stack of memory |

| US8890607B2 (en) | 2013-03-15 | 2014-11-18 | IPEnval Consultant Inc. | Stacked chip system |

| US9136843B2 (en) | 2013-04-21 | 2015-09-15 | Industrial Technology Research Institute | Through silicon via repair circuit of semiconductor device |

| KR102273094B1 (ko) * | 2013-05-16 | 2021-07-05 | 어드밴스드 마이크로 디바이시즈, 인코포레이티드 | 영역-특정 메모리 액세스 스케줄링을 가진 메모리 시스템 |

| US9170296B2 (en) | 2013-08-06 | 2015-10-27 | Globalfoundries U.S.2 Llc | Semiconductor device defect monitoring using a plurality of temperature sensing devices in an adjacent semiconductor device |

| KR102104578B1 (ko) * | 2013-08-30 | 2020-04-27 | 에스케이하이닉스 주식회사 | 데이터 비트 인버전 기능을 갖는 반도체 장치 |

| KR102111742B1 (ko) | 2014-01-14 | 2020-05-15 | 삼성전자주식회사 | 적층 반도체 패키지 |

| KR101583939B1 (ko) | 2014-06-10 | 2016-01-22 | 한양대학교 에리카산학협력단 | 리페어 가능한 관통 전극을 갖는 반도체 장치 |

| KR102125340B1 (ko) | 2014-06-19 | 2020-06-23 | 삼성전자주식회사 | 신호 전달을 위한 주 경로 및 우회 경로를 갖는 집적 회로 및 그것을 포함하는 집적 회로 패키지 |

| KR20160006991A (ko) * | 2014-07-10 | 2016-01-20 | 에스케이하이닉스 주식회사 | 복수의 채널 및 관통 비아를 포함하는 반도체 장치 |

| KR101503737B1 (ko) * | 2014-07-15 | 2015-03-20 | 연세대학교 산학협력단 | 반도체 장치 |

| KR102313949B1 (ko) * | 2014-11-11 | 2021-10-18 | 삼성전자주식회사 | 스택 반도체 장치 및 이를 포함하는 메모리 장치 |

| TWI556247B (zh) | 2014-11-12 | 2016-11-01 | 財團法人工業技術研究院 | 錯誤容忍穿矽孔介面及其控制方法 |

| US9627088B2 (en) * | 2015-02-25 | 2017-04-18 | Ememory Technology Inc. | One time programmable non-volatile memory and read sensing method thereof |

| US10832127B2 (en) * | 2015-11-30 | 2020-11-10 | Samsung Electronics Co., Ltd. | Three-dimensional integration of neurosynaptic chips |

| WO2017137015A2 (zh) * | 2016-02-13 | 2017-08-17 | 成都海存艾匹科技有限公司 | 含有三维存储阵列的处理器 |

| KR102451996B1 (ko) * | 2016-03-31 | 2022-10-07 | 삼성전자주식회사 | 기준 전압의 셀프 트레이닝을 수행하는 수신 인터페이스 회로 및 이를 포함하는 메모리 시스템 |

| KR102416942B1 (ko) * | 2017-11-13 | 2022-07-07 | 에스케이하이닉스 주식회사 | 적층 반도체 장치 및 반도체 시스템 |

| KR102498883B1 (ko) * | 2018-01-31 | 2023-02-13 | 삼성전자주식회사 | 전류를 분산시키는 관통 전극들을 포함하는 반도체 장치 |

| KR20190105346A (ko) * | 2018-03-05 | 2019-09-17 | 삼성전자주식회사 | 메모리 패키지 및 메모리 장치 |

| KR102471416B1 (ko) * | 2018-05-23 | 2022-11-29 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 메모리 모듈 |

| US12300688B2 (en) * | 2018-07-02 | 2025-05-13 | Shanghai Denglin Technologies Co. Ltd | Configurable random-access memory (RAM) array including through-silicon via (TSV) bypassing physical layer |

| CN109817540B (zh) * | 2019-01-30 | 2021-06-08 | 上海华虹宏力半导体制造有限公司 | 晶圆检测缺陷的分类方法 |

| US11164856B2 (en) | 2019-09-19 | 2021-11-02 | Micron Technology, Inc. | TSV check circuit with replica path |

| KR102818456B1 (ko) * | 2019-09-23 | 2025-06-10 | 삼성전자주식회사 | 솔리드 스테이트 드라이브 장치 및 그 제조 방법 |

| US10916489B1 (en) * | 2019-10-02 | 2021-02-09 | Micron Technology, Inc. | Memory core chip having TSVS |

| US11393790B2 (en) * | 2019-12-06 | 2022-07-19 | Micron Technology, Inc. | Memory with TSV health monitor circuitry |

| KR102728552B1 (ko) * | 2019-12-23 | 2024-11-12 | 에스케이하이닉스 주식회사 | 적층형 반도체 장치 및 이의 테스트 방법 |

| US12477751B2 (en) | 2022-04-14 | 2025-11-18 | Samsung Electronics Co., Ltd. | SRAM device and 3D semiconductor integrated circuit thereof |

| JP2025068884A (ja) * | 2023-10-17 | 2025-04-30 | 国立大学法人東京科学大学 | 半導体装置および半導体チップ |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004095799A (ja) * | 2002-08-30 | 2004-03-25 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP4063796B2 (ja) | 2004-06-30 | 2008-03-19 | 日本電気株式会社 | 積層型半導体装置 |

| WO2007032184A1 (ja) * | 2005-08-23 | 2007-03-22 | Nec Corporation | 半導体装置、半導体チップ、チップ間配線のテスト方法、および、チップ間配線切り替え方法 |

| JP4708176B2 (ja) | 2005-12-08 | 2011-06-22 | エルピーダメモリ株式会社 | 半導体装置 |

| US7494846B2 (en) * | 2007-03-09 | 2009-02-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Design techniques for stacking identical memory dies |

| KR100909902B1 (ko) * | 2007-04-27 | 2009-07-30 | 삼성전자주식회사 | 플래쉬 메모리 장치 및 플래쉬 메모리 시스템 |

| KR101519440B1 (ko) | 2007-10-04 | 2015-05-13 | 삼성전자주식회사 | 구성 가능한 수직 입출력 라인을 가지는 적층된 반도체 장치 및 그 방법 |

| US7816934B2 (en) * | 2007-10-16 | 2010-10-19 | Micron Technology, Inc. | Reconfigurable connections for stacked semiconductor devices |

| US8756486B2 (en) * | 2008-07-02 | 2014-06-17 | Micron Technology, Inc. | Method and apparatus for repairing high capacity/high bandwidth memory devices |

| JP5632584B2 (ja) * | 2009-02-05 | 2014-11-26 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体装置 |

| JP5564230B2 (ja) * | 2009-10-09 | 2014-07-30 | ピーエスフォー ルクスコ エスエイアールエル | 積層型半導体装置 |

| US8866303B2 (en) * | 2010-06-17 | 2014-10-21 | Conversant Intellectual Property Management Inc. | Semiconductor device with configurable through-silicon vias |

| KR20130011138A (ko) * | 2011-07-20 | 2013-01-30 | 삼성전자주식회사 | 모노 랭크와 멀티 랭크로 호환 가능한 메모리 장치 |

| JP2014236186A (ja) * | 2013-06-05 | 2014-12-15 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体装置 |

-

2010

- 2010-06-01 KR KR1020100051733A patent/KR101728068B1/ko active Active

-

2011

- 2011-04-13 US US13/085,776 patent/US8654593B2/en active Active

- 2011-05-03 TW TW100115493A patent/TWI532051B/zh active

- 2011-05-30 CN CN201110141841.0A patent/CN102270504B/zh active Active

- 2011-05-31 JP JP2011121586A patent/JP5982097B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| TW201201218A (en) | 2012-01-01 |

| JP2011253607A (ja) | 2011-12-15 |

| KR101728068B1 (ko) | 2017-04-19 |

| CN102270504B (zh) | 2016-08-31 |

| US8654593B2 (en) | 2014-02-18 |

| CN102270504A (zh) | 2011-12-07 |

| TWI532051B (zh) | 2016-05-01 |

| KR20110131976A (ko) | 2011-12-07 |

| US20110292742A1 (en) | 2011-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5982097B2 (ja) | 積層半導体メモリ装置、これを含むメモリシステム及び貫通電極の欠陥リペア方法 | |

| US11894093B2 (en) | Stacked DRAM device and method of manufacture | |

| KR100724653B1 (ko) | 반도체 칩 및 그것을 이용한 반도체 집적 회로 장치 및 반도체 칩 선택 방법 | |

| JP2011253607A5 (enExample) | ||

| CN103985648B (zh) | 半导体的晶圆级封装方法和半导体封装件 | |

| JP2006244689A (ja) | 入出力ビット構造を調節し得る半導体メモリ装置 | |

| JP2008227447A (ja) | 半導体構造の製造方法 | |

| US9287268B2 (en) | Dynamic random access memory (DRAM) and production method, semiconductor packaging component and packaging method | |

| US20090091962A1 (en) | Multi-chip memory device with stacked memory chips, method of stacking memory chips, and method of controlling operation of multi-chip package memory | |

| US20150325521A1 (en) | Semiconductor device and semiconductor chip | |

| JP4399777B2 (ja) | 半導体記憶装置、半導体装置、及び電子機器 | |

| CN106407135B (zh) | 电子装置 | |

| US20110242869A1 (en) | Three-dimensional stacked semiconductor integrated circuit and control method thereof | |

| US9263371B2 (en) | Semiconductor device having through-silicon via | |

| CN110534500A (zh) | 半导体器件和包括半导体器件的存储模块 | |

| KR20150106024A (ko) | 다양한 경로로 신호 입력이 가능한 적층 반도체 장치 및 반도체 시스템 | |

| US20170031653A1 (en) | Buffer, semiconductor apparatus and semiconductor system using the same | |

| US20130314968A1 (en) | Offsetting clock package pins in a clamshell topology to improve signal integrity | |

| CN105826274A (zh) | 半导体封装方法、半导体封装件及动态随机存取存储器的制作方法 | |

| KR20160148344A (ko) | 입출력 회로 및 이를 포함하는 입출력 장치 | |

| JP5473649B2 (ja) | 半導体装置及び半導体モジュール | |

| JP5666030B2 (ja) | 半導体装置及び半導体モジュール | |

| CN120077439A (zh) | 具有多个主管芯的堆叠式动态随机存取存储器(dram)装置 | |

| WO2014115599A1 (ja) | 半導体装置 | |

| JP6201503B2 (ja) | プリント基板、プリント基板製造方法及びプリント基板設計プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140416 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140416 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141119 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20141226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150406 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160704 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160801 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5982097 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |