JP5448604B2 - 薄膜トランジスタ - Google Patents

薄膜トランジスタ Download PDFInfo

- Publication number

- JP5448604B2 JP5448604B2 JP2009152242A JP2009152242A JP5448604B2 JP 5448604 B2 JP5448604 B2 JP 5448604B2 JP 2009152242 A JP2009152242 A JP 2009152242A JP 2009152242 A JP2009152242 A JP 2009152242A JP 5448604 B2 JP5448604 B2 JP 5448604B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor layer

- thin film

- film transistor

- gas

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0312—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes

- H10D30/0316—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes of lateral bottom-gate TFTs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/6737—Thin-film transistors [TFT] characterised by the electrodes characterised by the electrode materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/40—Crystalline structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0231—Manufacture or treatment of multiple TFTs using masks, e.g. half-tone masks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

Description

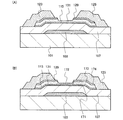

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。

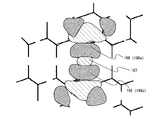

本実施の形態では実施の形態1に示す薄膜トランジスタにおいて、半導体層115に用いることが可能な形態を図7及び図8を用いて示す。図7(A)は薄膜トランジスタの断面図であり、図7(B)はゲート絶縁層107、微結晶半導体118、及びバッファ層131が接する領域の拡大図である。

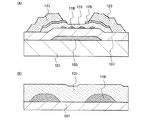

本実施の形態では、実施の形態1と異なる薄膜トランジスタの形態について、図9を参照して説明する。

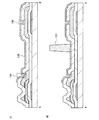

本実施の形態では、薄膜トランジスタ及び表示装置の画素部の作製方法について、以下に示す。ここでは、表示装置として液晶表示装置を用いて説明する。薄膜トランジスタではp型よりもn型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができ、好ましい。そのため、本実施の形態では、n型の薄膜トランジスタの作製方法について説明する。

本実施の形態では、実施の形態4に適用可能なバッファ層の形成工程について説明する。

本実施の形態では、実施の形態4に適用可能なバッファ層の形成工程について説明する。

実施の形態4乃至実施の形態6において、窒素濃度の分布が異なるNH基を有する非晶質半導体層の作製方法について、図18及び図19を用いて示す。

本実施の形態では、実施の形態3に示す薄膜トランジスタの作製方法について、説明する。本実施の形態でも、n型の薄膜トランジスタの作製方法について説明する。

本実施の形態では、コンタクト抵抗を下げることが可能な薄膜トランジスタの構造について示す。具体的には、実施の形態1乃至実施の形態8に示すソース領域及びドレイン領域を、一導電型を付与する不純物元素と、NH基またはNH2基を含有する半導体層(以下、NH基を有する不純物半導体層と示す。)で形成する。

実施の形態1乃至実施の形態3に示す薄膜トランジスタは、発光表示装置や発光装置に用いることができる。発光表示装置や発光装置は、発光素子として代表的には、エレクトロルミネッセンスを利用する発光素子がある。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって大別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

次に、本発明を適用可能な表示装置である表示パネルの構成の一例について、以下に示す。

上記形態の薄膜トランジスタで構成される素子基板、及びそれを用いた表示装置等は、アクティブマトリクス型の表示パネルに適用することができる。すなわち、それらを表示部に組み込んだ電子機器の全てに本発明を実施できる。

Claims (4)

- 絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、

前記ゲート絶縁層に接する第1半導体層と、

前記第1半導体層に積層される第2半導体層と、

前記第2半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、

を有し、

前記第1半導体層は、微結晶半導体層であり、

前記第2半導体層は、NH基、またはNH2基を有する非晶質半導体層で形成され、

前記第1半導体層は、分散された微結晶半導体層または網状の微結晶半導体層であることを特徴とする薄膜トランジスタ。 - 請求項1において、前記NH基は前記第2半導体層に含まれる異なる半導体原子を架橋することを特徴とする薄膜トランジスタ。

- 請求項1において、前記NH2基は前記第2半導体層に含まれる異なる半導体原子のダングリングボンドを終端することを特徴とする薄膜トランジスタ。

- 請求項1乃至請求項3のいずれか一項において、前記第2半導体層は、二次イオン質量分析法によって計測される酸素濃度が、5×10 18 cm −3 以下であることを特徴とする薄膜トランジスタ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009152242A JP5448604B2 (ja) | 2008-06-27 | 2009-06-26 | 薄膜トランジスタ |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008169499 | 2008-06-27 | ||

| JP2008169499 | 2008-06-27 | ||

| JP2008228242 | 2008-09-05 | ||

| JP2008228242 | 2008-09-05 | ||

| JP2009152242A JP5448604B2 (ja) | 2008-06-27 | 2009-06-26 | 薄膜トランジスタ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010087471A JP2010087471A (ja) | 2010-04-15 |

| JP2010087471A5 JP2010087471A5 (ja) | 2012-05-17 |

| JP5448604B2 true JP5448604B2 (ja) | 2014-03-19 |

Family

ID=41444633

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009152242A Expired - Fee Related JP5448604B2 (ja) | 2008-06-27 | 2009-06-26 | 薄膜トランジスタ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8513664B2 (ja) |

| JP (1) | JP5448604B2 (ja) |

| KR (1) | KR101602252B1 (ja) |

| CN (1) | CN102077354B (ja) |

| TW (1) | TWI505472B (ja) |

| WO (1) | WO2009157573A1 (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4294976B2 (ja) * | 2003-02-27 | 2009-07-15 | 東京エレクトロン株式会社 | 基板処理装置 |

| US9524869B2 (en) | 2004-03-11 | 2016-12-20 | Epistar Corporation | Nitride-based semiconductor light-emitting device |

| US20140017840A1 (en) * | 2004-03-11 | 2014-01-16 | Epistar Corporation | Nitride-based light-emitting device |

| JP5436017B2 (ja) | 2008-04-25 | 2014-03-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5518366B2 (ja) * | 2008-05-16 | 2014-06-11 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| EP2291856A4 (en) * | 2008-06-27 | 2015-09-23 | Semiconductor Energy Lab | THIN FILM TRANSISTOR |

| JP5498762B2 (ja) | 2008-11-17 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| US8598586B2 (en) * | 2009-12-21 | 2013-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and manufacturing method thereof |

| JP5602450B2 (ja) * | 2010-02-12 | 2014-10-08 | 三菱電機株式会社 | 薄膜トランジスタ、その製造方法、及び表示装置 |

| TWI538218B (zh) | 2010-09-14 | 2016-06-11 | 半導體能源研究所股份有限公司 | 薄膜電晶體 |

| KR101750430B1 (ko) * | 2010-11-29 | 2017-06-26 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판의 제조 방법 |

| US8741677B2 (en) * | 2010-11-30 | 2014-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method of the same |

| CN102096228B (zh) * | 2010-12-17 | 2012-07-04 | 湖南创图视维科技有限公司 | 一种显示系统和显示方法 |

| US8629445B2 (en) | 2011-02-21 | 2014-01-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, manufacturing method thereof, and electronic appliance |

| CN103038887A (zh) * | 2011-08-09 | 2013-04-10 | 松下电器产业株式会社 | 薄膜半导体器件及薄膜半导体器件的制造方法 |

| CN102646676B (zh) * | 2011-11-03 | 2015-06-10 | 京东方科技集团股份有限公司 | 一种tft阵列基板 |

| KR20230004930A (ko) | 2012-04-13 | 2023-01-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| WO2016009310A1 (en) | 2014-07-15 | 2016-01-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, manufacturing method thereof, and display device including the semiconductor device |

| US9818880B2 (en) | 2015-02-12 | 2017-11-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the semiconductor device |

| JP2016225615A (ja) * | 2015-05-26 | 2016-12-28 | 株式会社半導体エネルギー研究所 | 半導体装置、該半導体装置の作製方法、または該半導体装置を有する表示装置 |

| CN109585303B (zh) * | 2018-11-23 | 2023-03-10 | 合肥鑫晟光电科技有限公司 | 显示面板、阵列基板、薄膜晶体管及其制造方法 |

Family Cites Families (96)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4226898A (en) | 1978-03-16 | 1980-10-07 | Energy Conversion Devices, Inc. | Amorphous semiconductors equivalent to crystalline semiconductors produced by a glow discharge process |

| JPS56122123A (en) | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| US5091334A (en) | 1980-03-03 | 1992-02-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US4460670A (en) | 1981-11-26 | 1984-07-17 | Canon Kabushiki Kaisha | Photoconductive member with α-Si and C, N or O and dopant |

| JPH0658966B2 (ja) | 1982-05-17 | 1994-08-03 | キヤノン株式会社 | 半導体素子 |

| JPS6027122A (ja) * | 1983-07-22 | 1985-02-12 | Semiconductor Energy Lab Co Ltd | 光プラズマ気相反応法 |

| US4727044A (en) | 1984-05-18 | 1988-02-23 | Semiconductor Energy Laboratory Co., Ltd. | Method of making a thin film transistor with laser recrystallized source and drain |

| JPH0228624A (ja) * | 1988-07-18 | 1990-01-30 | Fujitsu Ltd | 薄膜トランジスタ |

| US5221631A (en) | 1989-02-17 | 1993-06-22 | International Business Machines Corporation | Method of fabricating a thin film transistor having a silicon carbide buffer layer |

| JP2839529B2 (ja) | 1989-02-17 | 1998-12-16 | 株式会社東芝 | 薄膜トランジスタ |

| EP0449539B1 (en) * | 1990-03-27 | 1996-07-03 | Kabushiki Kaisha Toshiba | Ohmic contact for thin film transistor |

| JPH03278466A (ja) * | 1990-03-27 | 1991-12-10 | Toshiba Corp | 薄膜トランジスタおよびその製造方法 |

| US5514879A (en) | 1990-11-20 | 1996-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated field effect transistors and method of manufacturing the same |

| US5849601A (en) | 1990-12-25 | 1998-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US7115902B1 (en) | 1990-11-20 | 2006-10-03 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| KR950013784B1 (ko) | 1990-11-20 | 1995-11-16 | 가부시키가이샤 한도오따이 에네루기 겐큐쇼 | 반도체 전계효과 트랜지스터 및 그 제조방법과 박막트랜지스터 |

| US7098479B1 (en) | 1990-12-25 | 2006-08-29 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JPH04266019A (ja) * | 1991-02-20 | 1992-09-22 | Canon Inc | 成膜方法 |

| JP3255942B2 (ja) | 1991-06-19 | 2002-02-12 | 株式会社半導体エネルギー研究所 | 逆スタガ薄膜トランジスタの作製方法 |

| EP0535979A3 (en) | 1991-10-02 | 1993-07-21 | Sharp Kabushiki Kaisha | A thin film transistor and a method for producing the same |

| JPH05129608A (ja) | 1991-10-31 | 1993-05-25 | Sharp Corp | 半導体装置 |

| JPH05175503A (ja) * | 1991-10-23 | 1993-07-13 | Kyocera Corp | 薄膜トランジスタおよびその製造方法 |

| US6835523B1 (en) | 1993-05-09 | 2004-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Apparatus for fabricating coating and method of fabricating the coating |

| JP3157985B2 (ja) | 1993-06-10 | 2001-04-23 | 三菱電機株式会社 | 薄膜トランジスタおよびその製造方法 |

| US6183816B1 (en) | 1993-07-20 | 2001-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating the coating |

| JPH07131030A (ja) | 1993-11-05 | 1995-05-19 | Sony Corp | 表示用薄膜半導体装置及びその製造方法 |

| US6747627B1 (en) | 1994-04-22 | 2004-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Redundancy shift register circuit for driver circuit in active matrix type liquid crystal display device |

| JP3175503B2 (ja) | 1994-11-10 | 2001-06-11 | 株式会社村田製作所 | チップ型圧電共振部品 |

| TW303526B (ja) | 1994-12-27 | 1997-04-21 | Matsushita Electric Industrial Co Ltd | |

| US5677236A (en) | 1995-02-24 | 1997-10-14 | Mitsui Toatsu Chemicals, Inc. | Process for forming a thin microcrystalline silicon semiconductor film |

| JPH10332494A (ja) | 1997-06-03 | 1998-12-18 | Oki Data:Kk | 温度検出回路、駆動装置及びプリンタ |

| US5920772A (en) | 1997-06-27 | 1999-07-06 | Industrial Technology Research Institute | Method of fabricating a hybrid polysilicon/amorphous silicon TFT |

| US6261881B1 (en) | 1998-08-21 | 2001-07-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device provided with semiconductor circuit consisting of semiconductor element and method of manufacturing the same |

| JP2000277439A (ja) | 1999-03-25 | 2000-10-06 | Kanegafuchi Chem Ind Co Ltd | 結晶質シリコン系薄膜のプラズマcvd方法およびシリコン系薄膜光電変換装置の製造方法 |

| JP2001007024A (ja) | 1999-06-18 | 2001-01-12 | Sanyo Electric Co Ltd | 多結晶シリコン膜の形成方法 |

| JP2001053283A (ja) | 1999-08-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| TW507258B (en) | 2000-02-29 | 2002-10-21 | Semiconductor Systems Corp | Display device and method for fabricating the same |

| US7633471B2 (en) | 2000-05-12 | 2009-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and electric appliance |

| GB0017471D0 (en) | 2000-07-18 | 2000-08-30 | Koninkl Philips Electronics Nv | Thin film transistors and their manufacture |

| US6544908B1 (en) | 2000-08-30 | 2003-04-08 | Micron Technology, Inc. | Ammonia gas passivation on nitride encapsulated devices |

| JP4926329B2 (ja) * | 2001-03-27 | 2012-05-09 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法、電気器具 |

| KR100764273B1 (ko) * | 2001-05-31 | 2007-10-05 | 비오이 하이디스 테크놀로지 주식회사 | 박막트랜지스터 제조방법 |

| JP4560245B2 (ja) | 2001-06-29 | 2010-10-13 | キヤノン株式会社 | 光起電力素子 |

| TW519259U (en) * | 2001-08-31 | 2003-01-21 | Asia Vital Components Co Ltd | Improved structure of DC fan bearing fixation device |

| CN1434493A (zh) | 2002-01-23 | 2003-08-06 | 联华电子股份有限公司 | 自生长疏水性纳米分子有机防扩散膜及其制备方法 |

| KR100436181B1 (ko) | 2002-04-16 | 2004-06-12 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| JP2004014958A (ja) | 2002-06-11 | 2004-01-15 | Fuji Electric Holdings Co Ltd | 薄膜多結晶太陽電池とその製造方法 |

| US6838300B2 (en) | 2003-02-04 | 2005-01-04 | Texas Instruments Incorporated | Chemical treatment of low-k dielectric films |

| JP4869601B2 (ja) * | 2003-03-26 | 2012-02-08 | 株式会社半導体エネルギー研究所 | 半導体装置および半導体装置の作製方法 |

| FR2853418B1 (fr) | 2003-04-01 | 2005-08-19 | Commissariat Energie Atomique | Dispositif optique a stabilite mecanique renforcee fonctionnant dans l'extreme ultraviolet et masque de lithographie comportant un tel dispositif |

| US20040198046A1 (en) | 2003-04-01 | 2004-10-07 | Lee Yu-Chou | Method for decreasing contact resistance of source/drain electrodes |

| JP2004335823A (ja) | 2003-05-09 | 2004-11-25 | Canon Inc | 光起電力素子及び光起電力素子の形成方法 |

| TWI222753B (en) * | 2003-05-20 | 2004-10-21 | Au Optronics Corp | Method for forming a thin film transistor of an organic light emitting display |

| US8319219B2 (en) | 2003-07-14 | 2012-11-27 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| JP4748954B2 (ja) | 2003-07-14 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP4480968B2 (ja) | 2003-07-18 | 2010-06-16 | 株式会社半導体エネルギー研究所 | 表示装置 |

| TWI336921B (en) * | 2003-07-18 | 2011-02-01 | Semiconductor Energy Lab | Method for manufacturing semiconductor device |

| JP2005050905A (ja) | 2003-07-30 | 2005-02-24 | Sharp Corp | シリコン薄膜太陽電池の製造方法 |

| JP3887364B2 (ja) | 2003-09-19 | 2007-02-28 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2005123466A (ja) | 2003-10-17 | 2005-05-12 | Sharp Corp | シリコン系薄膜光電変換装置の製造方法およびその方法により製造されたシリコン系薄膜光電変換装置 |

| JP5159021B2 (ja) | 2003-12-02 | 2013-03-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI372463B (en) | 2003-12-02 | 2012-09-11 | Semiconductor Energy Lab | Laser irradiation apparatus, laser irradiation method, and method for manufacturing semiconductor device |

| JP2005167051A (ja) | 2003-12-04 | 2005-06-23 | Sony Corp | 薄膜トランジスタおよび薄膜トランジスタの製造方法 |

| US20060079100A1 (en) | 2004-03-15 | 2006-04-13 | Sharp Laboratories Of America, Inc. | High density plasma grown silicon nitride |

| DE102005013537A1 (de) | 2004-03-24 | 2005-10-20 | Sharp Kk | Fotoelektrischer Wandler und Herstellverfahren für einen solchen |

| US7288284B2 (en) | 2004-03-26 | 2007-10-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Post-cleaning chamber seasoning method |

| US7125758B2 (en) | 2004-04-20 | 2006-10-24 | Applied Materials, Inc. | Controlling the properties and uniformity of a silicon nitride film by controlling the film forming precursors |

| TWI234288B (en) | 2004-07-27 | 2005-06-11 | Au Optronics Corp | Method for fabricating a thin film transistor and related circuits |

| EP1624333B1 (en) | 2004-08-03 | 2017-05-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device, manufacturing method thereof, and television set |

| KR100643493B1 (ko) | 2004-09-23 | 2006-11-10 | 삼성전자주식회사 | 반도체 장치의 실리콘 산질화막을 형성하는 방법 및 장치 |

| TWI505473B (zh) | 2005-01-28 | 2015-10-21 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| KR100722085B1 (ko) * | 2005-09-12 | 2007-05-25 | 삼성전자주식회사 | 전기영동법으로 형성된 탄소나노튜브를 포함하는 태양 전지및 그 제조방법 |

| US20070295399A1 (en) | 2005-12-16 | 2007-12-27 | Bp Corporation North America Inc. | Back-Contact Photovoltaic Cells |

| JP5207598B2 (ja) | 2006-05-24 | 2013-06-12 | パナソニック株式会社 | 窒化物半導体材料、半導体素子およびその製造方法 |

| JP2008091599A (ja) | 2006-10-02 | 2008-04-17 | Sony Corp | 薄膜トランジスタおよびその製造方法ならびに表示装置 |

| JP2008124392A (ja) | 2006-11-15 | 2008-05-29 | Sharp Corp | 半導体装置、その製造方法及び表示装置 |

| JP2008300779A (ja) | 2007-06-04 | 2008-12-11 | Elpida Memory Inc | 半導体装置及びその製造方法 |

| JP5331389B2 (ja) | 2007-06-15 | 2013-10-30 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| JP5311955B2 (ja) | 2007-11-01 | 2013-10-09 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| US7786485B2 (en) | 2008-02-29 | 2010-08-31 | Semicondutor Energy Laboratory Co., Ltd. | Thin-film transistor and display device |

| US7812348B2 (en) | 2008-02-29 | 2010-10-12 | Semiconductor Energy Laboratory Co., Ltd. | Thin-film transistor and display device |

| US7968880B2 (en) | 2008-03-01 | 2011-06-28 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and display device |

| US7821012B2 (en) | 2008-03-18 | 2010-10-26 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| JP5411528B2 (ja) | 2008-03-18 | 2014-02-12 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ及び表示装置 |

| WO2009128522A1 (en) | 2008-04-18 | 2009-10-22 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and method for manufacturing the same |

| US8138032B2 (en) | 2008-04-18 | 2012-03-20 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor having microcrystalline semiconductor film |

| JP5416460B2 (ja) | 2008-04-18 | 2014-02-12 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタおよび薄膜トランジスタの作製方法 |

| US8053294B2 (en) | 2008-04-21 | 2011-11-08 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of thin film transistor by controlling generation of crystal nuclei of microcrystalline semiconductor film |

| JP5436017B2 (ja) | 2008-04-25 | 2014-03-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US8049215B2 (en) | 2008-04-25 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| JP5518366B2 (ja) | 2008-05-16 | 2014-06-11 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| EP2291856A4 (en) | 2008-06-27 | 2015-09-23 | Semiconductor Energy Lab | THIN FILM TRANSISTOR |

| US8283667B2 (en) | 2008-09-05 | 2012-10-09 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| CN102165600B (zh) | 2008-09-26 | 2013-09-25 | 株式会社半导体能源研究所 | 光电转换器件及其制造方法 |

| JP5525224B2 (ja) | 2008-09-30 | 2014-06-18 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2010103906A1 (en) | 2009-03-09 | 2010-09-16 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

-

2009

- 2009-06-22 CN CN200980124788.4A patent/CN102077354B/zh not_active Expired - Fee Related

- 2009-06-22 KR KR1020117001356A patent/KR101602252B1/ko not_active Expired - Fee Related

- 2009-06-22 WO PCT/JP2009/061794 patent/WO2009157573A1/en not_active Ceased

- 2009-06-24 US US12/490,458 patent/US8513664B2/en not_active Expired - Fee Related

- 2009-06-24 TW TW098121203A patent/TWI505472B/zh not_active IP Right Cessation

- 2009-06-26 JP JP2009152242A patent/JP5448604B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010087471A (ja) | 2010-04-15 |

| US20090321743A1 (en) | 2009-12-31 |

| WO2009157573A1 (en) | 2009-12-30 |

| CN102077354B (zh) | 2014-08-20 |

| TWI505472B (zh) | 2015-10-21 |

| KR101602252B1 (ko) | 2016-03-10 |

| US8513664B2 (en) | 2013-08-20 |

| CN102077354A (zh) | 2011-05-25 |

| KR20110023888A (ko) | 2011-03-08 |

| TW201017889A (en) | 2010-05-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5448604B2 (ja) | 薄膜トランジスタ | |

| JP5448603B2 (ja) | 薄膜トランジスタ | |

| JP5464893B2 (ja) | 半導体装置 | |

| JP5464894B2 (ja) | 半導体装置 | |

| JP5361468B2 (ja) | 半導体装置の作製方法 | |

| JP2009278075A (ja) | 薄膜トランジスタおよび薄膜トランジスタの作製方法 | |

| JP5436016B2 (ja) | 半導体装置 | |

| JP5518366B2 (ja) | 薄膜トランジスタ | |

| JP5495775B2 (ja) | 半導体装置 | |

| JP5498711B2 (ja) | 薄膜トランジスタ | |

| JP5602389B2 (ja) | 薄膜トランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120322 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120322 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131008 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131010 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131121 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20131121 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131217 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131224 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5448604 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |