JP5464893B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5464893B2 JP5464893B2 JP2009101238A JP2009101238A JP5464893B2 JP 5464893 B2 JP5464893 B2 JP 5464893B2 JP 2009101238 A JP2009101238 A JP 2009101238A JP 2009101238 A JP2009101238 A JP 2009101238A JP 5464893 B2 JP5464893 B2 JP 5464893B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor layer

- thin film

- film transistor

- insulating layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 231

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 188

- 239000013078 crystal Substances 0.000 claims description 103

- 229910052757 nitrogen Inorganic materials 0.000 claims description 94

- 239000012535 impurity Substances 0.000 claims description 69

- 230000015572 biosynthetic process Effects 0.000 claims description 62

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 46

- 229910052760 oxygen Inorganic materials 0.000 claims description 46

- 239000001301 oxygen Substances 0.000 claims description 46

- 238000001004 secondary ion mass spectrometry Methods 0.000 claims description 3

- 230000003247 decreasing effect Effects 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 549

- 239000010409 thin film Substances 0.000 description 128

- 239000007789 gas Substances 0.000 description 122

- 239000000758 substrate Substances 0.000 description 97

- 238000000034 method Methods 0.000 description 77

- 239000010408 film Substances 0.000 description 76

- 238000012545 processing Methods 0.000 description 73

- 239000000463 material Substances 0.000 description 56

- 229910052581 Si3N4 Inorganic materials 0.000 description 49

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 49

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 41

- 229910052710 silicon Inorganic materials 0.000 description 41

- 239000010703 silicon Substances 0.000 description 41

- 239000004973 liquid crystal related substance Substances 0.000 description 34

- 238000004519 manufacturing process Methods 0.000 description 31

- 230000008569 process Effects 0.000 description 23

- 230000006911 nucleation Effects 0.000 description 15

- 238000010899 nucleation Methods 0.000 description 15

- 238000005530 etching Methods 0.000 description 14

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 14

- 230000006870 function Effects 0.000 description 12

- 238000009832 plasma treatment Methods 0.000 description 12

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 12

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 9

- 239000003990 capacitor Substances 0.000 description 9

- 229910052750 molybdenum Inorganic materials 0.000 description 9

- 239000011733 molybdenum Substances 0.000 description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 230000007423 decrease Effects 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- 230000001965 increasing effect Effects 0.000 description 8

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 8

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 239000001257 hydrogen Substances 0.000 description 6

- 229910052739 hydrogen Inorganic materials 0.000 description 6

- 239000000203 mixture Substances 0.000 description 6

- 239000012495 reaction gas Substances 0.000 description 6

- 230000005236 sound signal Effects 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 5

- 238000002347 injection Methods 0.000 description 5

- 239000007924 injection Substances 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 229910052715 tantalum Inorganic materials 0.000 description 5

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 5

- 238000002834 transmittance Methods 0.000 description 5

- 229910000838 Al alloy Inorganic materials 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- 229910004205 SiNX Inorganic materials 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 230000001413 cellular effect Effects 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 238000007865 diluting Methods 0.000 description 4

- 238000001678 elastic recoil detection analysis Methods 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 150000004767 nitrides Chemical class 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 238000005192 partition Methods 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 230000007261 regionalization Effects 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- 229910000583 Nd alloy Inorganic materials 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- 229910020286 SiOxNy Inorganic materials 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 230000018109 developmental process Effects 0.000 description 3

- 239000000284 extract Substances 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 229910000423 chromium oxide Inorganic materials 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000004040 coloring Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 230000005525 hole transport Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 229910052706 scandium Inorganic materials 0.000 description 2

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910017073 AlLi Inorganic materials 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- 229910019974 CrSi Inorganic materials 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910000676 Si alloy Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910001362 Ta alloys Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000008187 granular material Substances 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- QEHKBHWEUPXBCW-UHFFFAOYSA-N nitrogen trichloride Chemical compound ClN(Cl)Cl QEHKBHWEUPXBCW-UHFFFAOYSA-N 0.000 description 1

- GVGCUCJTUSOZKP-UHFFFAOYSA-N nitrogen trifluoride Chemical compound FN(F)F GVGCUCJTUSOZKP-UHFFFAOYSA-N 0.000 description 1

- 239000005416 organic matter Substances 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229910052990 silicon hydride Inorganic materials 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/02—Pretreatment of the material to be coated

- C23C16/0272—Deposition of sub-layers, e.g. to promote the adhesion of the main coating

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/24—Deposition of silicon only

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/4401—Means for minimising impurities, e.g. dust, moisture or residual gas, in the reaction chamber

- C23C16/4404—Coatings or surface treatment on the inside of the reaction chamber or on parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78663—Amorphous silicon transistors

- H01L29/78669—Amorphous silicon transistors with inverted-type structure, e.g. with bottom gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78678—Polycrystalline or microcrystalline silicon transistor with inverted-type structure, e.g. with bottom gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Inorganic Chemistry (AREA)

- Thin Film Transistor (AREA)

Description

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。

本実施の形態では、図1に示す薄膜トランジスタの作製方法であって、実施の形態1とは異なるものについて説明する。本実施の形態では、実施の形態1と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

本実施の形態では、図1に示す薄膜トランジスタの作製方法であって、実施の形態1及び実施の形態2とは異なるものについて説明する。本実施の形態では、実施の形態1及び実施の形態2と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

本実施の形態では、実施の形態1乃至実施の形態3とは異なる半導体装置の作製方法について説明する。本実施の形態では、実施の形態1と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。本実施の形態では、多階調マスクを用いることなく薄膜トランジスタを形成する。

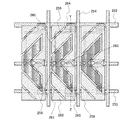

本実施の形態では、表示装置の一形態として、実施の形態5で示す薄膜トランジスタを有する液晶表示装置について説明する。ここでは、VA(Vertical Alignment)型の液晶表示装置について、図17乃至図19を参照して説明する。VA型とは、液晶パネルの液晶分子の配列を制御する方式の一種をいう。VA型の液晶表示装置では、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く。本実施の形態では、特に画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に液晶分子を倒すよう工夫されている。これをマルチドメイン化あるいはマルチドメイン設計という。以下の説明では、マルチドメイン設計が考慮された液晶表示装置について説明する。

本実施の形態では、表示装置の一形態として、実施の形態5で示す薄膜トランジスタを有する発光表示装置について説明する。ここでは、発光表示装置が有する画素の構成の一例について説明する。図20(A)は画素の平面図を示し、図20(B)は図20(A)中の切断線A−Bに対応する断面構造を示す。

次に、表示装置が有する表示パネルの構成の一例について説明する。

上記実施の形態の薄膜トランジスタで構成される素子基板及びこれを用いた表示装置等は、アクティブマトリクス型の表示装置パネルに適用することができる。更には、これらを表示部に組み込んだ電子機器に適用することもできる。

102 ゲート電極層

104 ゲート絶縁層

105 半導体層

106 半導体層

109 ドナーとなる不純物元素を含む半導体層

110 ソース領域及びドレイン領域

111 導電層

112 配線層

114 絶縁層

116 画素電極層

120 第1の領域

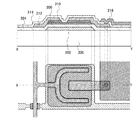

121 結晶粒

122 第2の領域

131 第1のレジストマスク

132 第2のレジストマスク

141 処理室

142 ステージ

143 ガス供給部

144 シャワープレート

145 排気口

146 上部電極

147 下部電極

148 交流電源

149 温度制御部

150 ガス供給手段

151 排気手段

152 シリンダ

153 圧力調整弁

154 ストップバルブ

155 マスフローコントローラ

156 バタフライバルブ

157 コンダクタンスバルブ

158 ターボ分子ポンプ

159 ドライポンプ

160 クライオポンプ

161 プラズマCVD装置

180 グレートーンマスク

181 基板

182 遮光部

183 回折格子部

185 ハーフトーンマスク

186 基板

187 半透光部

188 遮光部

200 基板

202 ゲート電極層

204 ゲート絶縁層

205 半導体層

206 半導体層

209 ドナーとなる不純物元素を含む半導体層

210 ソース領域及びドレイン領域

211 導電層

212 配線層

214 絶縁層

216 画素電極層

231 第1のレジストマスク

232 第2のレジストマスク

250 基板

251 対向基板

252 ゲート電極

253 ゲート電極

254 配線

255 配線

256 配線

257 絶縁層

258 平坦化膜

259 開口部

260 画素電極

261 スリット

262 画素電極

263 開口部

264 薄膜トランジスタ

265 薄膜トランジスタ

266 遮光膜

267 着色膜

268 平坦化膜

269 対向電極

270 スリット

271 配向膜

272 配向膜

273 液晶層

280 容量素子

281a 薄膜トランジスタ

281b 薄膜トランジスタ

282 発光素子

283a 走査線

283b ゲート電極

284a 信号線

284b 配線

285a 電源線

285b 配線

286 絶縁層

287 平坦化膜

288 陰極

289 EL層

290 陽極

291 隔壁

292 保護絶縁膜

301 基板

302 画素部

303 信号線駆動回路

304 走査線駆動回路

305 FPC

306 保護回路

311 基板

312 画素部

313 信号線駆動回路

314 走査線駆動回路

315 FPC

316 保護回路

321 基板

322 画素部

323a アナログスイッチ

323b シフトレジスタ

324 走査線駆動回路

325 FPC

326 保護回路

331 筐体

332 表示パネル

333 主画面

334 モデム

335 受信機

336 リモコン操作機

337 表示部

338 サブ画面

339 スピーカ部

341 携帯電話機

342 表示部

343 操作部

351 本体

352 表示部

361 照明部

362 傘

363 可変アーム

364 支柱

365 台

366 電源

371 画素部

372 信号線駆動回路

373 走査線駆動回路

374 チューナ

375 映像信号増幅回路

376 映像信号処理回路

377 コントロール回路

378 信号分割回路

379 音声信号増幅回路

380 音声信号処理回路

381 制御回路

382 入力部

383 スピーカ

385 筐体

386 表示部

387 スピーカ

388 マイクロフォン

389 操作キー

390 ポインティングディバイス

391 表面カメラ用レンズ

392 外部接続端子ジャック

393 イヤホン端子

394 筐体

395 キーボード

396 外部メモリスロット

397 裏面カメラ

398 ライト

Claims (1)

- ゲート電極と、

前記ゲート電極上のゲート絶縁層と、

前記ゲート絶縁層に接し、非晶質構造の中に複数の結晶領域を含みチャネル形成領域を構成する第1の半導体層と、

一導電型を付与する不純物元素を含み、ソース領域及びドレイン領域を有する第2の半導体層と、を有し、

前記結晶領域は、前記ゲート絶縁層と前記第1の半導体層との界面から離れた位置から、前記第2の半導体層に向かって略放射状に成長した逆錐形状の構造を有し、

前記第1の半導体層は、二次イオン質量分析法によって計測される酸素濃度が、5×10 18 atoms/cm 3 以下であり、窒素濃度が1×10 20 atoms/cm 3 乃至1×10 21 atoms/cm 3 であり、

前記窒素濃度は、前記ゲート絶縁層と前記第1の半導体層との界面近傍において、二次イオン質量分析法によって計測されるピーク濃度が3×10 20 atoms/cm 3 乃至1×10 21 atoms/cm 3 であり、該界面近傍から前記第2の半導体層に向かって減少しており、

前記結晶領域は単結晶を含み、

前記単結晶は双晶を含むことを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009101238A JP5464893B2 (ja) | 2008-04-18 | 2009-04-17 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008109657 | 2008-04-18 | ||

| JP2008109657 | 2008-04-18 | ||

| JP2009101238A JP5464893B2 (ja) | 2008-04-18 | 2009-04-17 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009278081A JP2009278081A (ja) | 2009-11-26 |

| JP2009278081A5 JP2009278081A5 (ja) | 2012-05-31 |

| JP5464893B2 true JP5464893B2 (ja) | 2014-04-09 |

Family

ID=41199209

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009101238A Expired - Fee Related JP5464893B2 (ja) | 2008-04-18 | 2009-04-17 | 半導体装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8119468B2 (ja) |

| JP (1) | JP5464893B2 (ja) |

| KR (1) | KR101455317B1 (ja) |

| CN (1) | CN102007586B (ja) |

| TW (1) | TWI489558B (ja) |

| WO (1) | WO2009128522A1 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7753751B2 (en) | 2004-09-29 | 2010-07-13 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating the display device |

| TWI517378B (zh) | 2005-10-17 | 2016-01-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| CN102007585B (zh) * | 2008-04-18 | 2013-05-29 | 株式会社半导体能源研究所 | 薄膜晶体管及其制造方法 |

| US8053294B2 (en) * | 2008-04-21 | 2011-11-08 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of thin film transistor by controlling generation of crystal nuclei of microcrystalline semiconductor film |

| US8049215B2 (en) * | 2008-04-25 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| JP5436017B2 (ja) * | 2008-04-25 | 2014-03-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5377061B2 (ja) * | 2008-05-09 | 2013-12-25 | 株式会社半導体エネルギー研究所 | 光電変換装置 |

| WO2009157573A1 (en) * | 2008-06-27 | 2009-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, semiconductor device and electronic device |

| EP2291856A4 (en) * | 2008-06-27 | 2015-09-23 | Semiconductor Energy Lab | THIN FILM TRANSISTOR |

| JP5498762B2 (ja) * | 2008-11-17 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| JP5590868B2 (ja) * | 2008-12-11 | 2014-09-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI607670B (zh) * | 2009-01-08 | 2017-12-01 | 半導體能源研究所股份有限公司 | 發光裝置及電子裝置 |

| US8344378B2 (en) | 2009-06-26 | 2013-01-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and method for manufacturing the same |

| DE102009056162B4 (de) * | 2009-11-27 | 2015-12-24 | Helmholtz-Zentrum Berlin Für Materialien Und Energie Gmbh | Verfahren zur Herstellung einer defektarmen kristallinen Siliziumschicht auf einem Substrat mittels chemischer oder physikalischer Gasphasenabscheidung |

| US8299467B2 (en) * | 2009-12-28 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and fabrication method thereof |

| JP5697819B2 (ja) * | 2009-12-28 | 2015-04-08 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ |

| US20120001179A1 (en) * | 2010-07-02 | 2012-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN102096228B (zh) * | 2010-12-17 | 2012-07-04 | 湖南创图视维科技有限公司 | 一种显示系统和显示方法 |

| JP6302186B2 (ja) | 2012-08-01 | 2018-03-28 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP6204012B2 (ja) | 2012-10-17 | 2017-09-27 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP6076683B2 (ja) | 2012-10-17 | 2017-02-08 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP6155020B2 (ja) | 2012-12-21 | 2017-06-28 | 株式会社半導体エネルギー研究所 | 発光装置及びその製造方法 |

| JP6216125B2 (ja) | 2013-02-12 | 2017-10-18 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP6104649B2 (ja) | 2013-03-08 | 2017-03-29 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP6348707B2 (ja) * | 2013-12-11 | 2018-06-27 | 東京エレクトロン株式会社 | アモルファスシリコンの結晶化方法、結晶化シリコン膜の成膜方法、半導体装置の製造方法および成膜装置 |

| US11862668B2 (en) * | 2021-07-02 | 2024-01-02 | Micron Technology, Inc. | Single-crystal transistors for memory devices |

Family Cites Families (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5091334A (en) * | 1980-03-03 | 1992-02-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JPS56122123A (en) * | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| JPS5771126A (en) | 1980-10-21 | 1982-05-01 | Semiconductor Energy Lab Co Ltd | Semiamorhous semiconductor |

| JPS5892217A (ja) | 1981-11-28 | 1983-06-01 | Semiconductor Energy Lab Co Ltd | 半導体装置作製方法 |

| JPS6262073A (ja) | 1985-09-11 | 1987-03-18 | Ishikawajima Harima Heavy Ind Co Ltd | ポペツト弁の温度制御装置 |

| JPH01144682A (ja) | 1987-11-30 | 1989-06-06 | Nec Corp | 薄膜トランジスタの製造方法 |

| JP2650946B2 (ja) * | 1988-03-04 | 1997-09-10 | 株式会社日立製作所 | 薄膜電界効果素子 |

| JPH0253941A (ja) | 1988-08-17 | 1990-02-22 | Tsudakoma Corp | 織機の運転装置 |

| JP2839529B2 (ja) * | 1989-02-17 | 1998-12-16 | 株式会社東芝 | 薄膜トランジスタ |

| US5221631A (en) * | 1989-02-17 | 1993-06-22 | International Business Machines Corporation | Method of fabricating a thin film transistor having a silicon carbide buffer layer |

| EP0449539B1 (en) * | 1990-03-27 | 1996-07-03 | Kabushiki Kaisha Toshiba | Ohmic contact for thin film transistor |

| JPH03278466A (ja) * | 1990-03-27 | 1991-12-10 | Toshiba Corp | 薄膜トランジスタおよびその製造方法 |

| JP2791422B2 (ja) | 1990-12-25 | 1998-08-27 | 株式会社 半導体エネルギー研究所 | 電気光学装置およびその作製方法 |

| US5849601A (en) | 1990-12-25 | 1998-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US5514879A (en) * | 1990-11-20 | 1996-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated field effect transistors and method of manufacturing the same |

| KR950013784B1 (ko) | 1990-11-20 | 1995-11-16 | 가부시키가이샤 한도오따이 에네루기 겐큐쇼 | 반도체 전계효과 트랜지스터 및 그 제조방법과 박막트랜지스터 |

| US7115902B1 (en) | 1990-11-20 | 2006-10-03 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US7098479B1 (en) | 1990-12-25 | 2006-08-29 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JP3255942B2 (ja) | 1991-06-19 | 2002-02-12 | 株式会社半導体エネルギー研究所 | 逆スタガ薄膜トランジスタの作製方法 |

| EP0535979A3 (en) | 1991-10-02 | 1993-07-21 | Sharp Kabushiki Kaisha | A thin film transistor and a method for producing the same |

| JP3123722B2 (ja) | 1991-10-03 | 2001-01-15 | キヤノン株式会社 | 薄膜半導体トランジスターの製造方法及び薄膜トランジスター |

| US6835523B1 (en) | 1993-05-09 | 2004-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Apparatus for fabricating coating and method of fabricating the coating |

| US6171674B1 (en) * | 1993-07-20 | 2001-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Hard carbon coating for magnetic recording medium |

| JPH06326312A (ja) | 1993-05-14 | 1994-11-25 | Toshiba Corp | アクティブマトリクス型表示装置 |

| JPH0794749A (ja) * | 1993-09-22 | 1995-04-07 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JPH07131030A (ja) | 1993-11-05 | 1995-05-19 | Sony Corp | 表示用薄膜半導体装置及びその製造方法 |

| TW303526B (ja) * | 1994-12-27 | 1997-04-21 | Matsushita Electric Ind Co Ltd | |

| US5677236A (en) | 1995-02-24 | 1997-10-14 | Mitsui Toatsu Chemicals, Inc. | Process for forming a thin microcrystalline silicon semiconductor film |

| US5920772A (en) * | 1997-06-27 | 1999-07-06 | Industrial Technology Research Institute | Method of fabricating a hybrid polysilicon/amorphous silicon TFT |

| JP2000277439A (ja) | 1999-03-25 | 2000-10-06 | Kanegafuchi Chem Ind Co Ltd | 結晶質シリコン系薄膜のプラズマcvd方法およびシリコン系薄膜光電変換装置の製造方法 |

| JP2001007024A (ja) | 1999-06-18 | 2001-01-12 | Sanyo Electric Co Ltd | 多結晶シリコン膜の形成方法 |

| JP2001102587A (ja) * | 1999-09-28 | 2001-04-13 | Toshiba Corp | 薄膜トランジスタおよびその製造方法ならびに半導体薄膜の製造方法 |

| GB0017471D0 (en) * | 2000-07-18 | 2000-08-30 | Koninkl Philips Electronics Nv | Thin film transistors and their manufacture |

| KR100436181B1 (ko) | 2002-04-16 | 2004-06-12 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| JP2004014958A (ja) | 2002-06-11 | 2004-01-15 | Fuji Electric Holdings Co Ltd | 薄膜多結晶太陽電池とその製造方法 |

| JP4748954B2 (ja) | 2003-07-14 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP2005050905A (ja) | 2003-07-30 | 2005-02-24 | Sharp Corp | シリコン薄膜太陽電池の製造方法 |

| JP3887364B2 (ja) * | 2003-09-19 | 2007-02-28 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2005123466A (ja) * | 2003-10-17 | 2005-05-12 | Sharp Corp | シリコン系薄膜光電変換装置の製造方法およびその方法により製造されたシリコン系薄膜光電変換装置 |

| JP2005167051A (ja) | 2003-12-04 | 2005-06-23 | Sony Corp | 薄膜トランジスタおよび薄膜トランジスタの製造方法 |

| US20060079100A1 (en) * | 2004-03-15 | 2006-04-13 | Sharp Laboratories Of America, Inc. | High density plasma grown silicon nitride |

| US7288284B2 (en) * | 2004-03-26 | 2007-10-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Post-cleaning chamber seasoning method |

| US7125758B2 (en) * | 2004-04-20 | 2006-10-24 | Applied Materials, Inc. | Controlling the properties and uniformity of a silicon nitride film by controlling the film forming precursors |

| JP2005322845A (ja) | 2004-05-11 | 2005-11-17 | Sekisui Chem Co Ltd | 半導体デバイスと、その製造装置、および製造方法 |

| JP4286741B2 (ja) | 2004-07-26 | 2009-07-01 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| EP1624333B1 (en) * | 2004-08-03 | 2017-05-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device, manufacturing method thereof, and television set |

| KR100643493B1 (ko) * | 2004-09-23 | 2006-11-10 | 삼성전자주식회사 | 반도체 장치의 실리콘 산질화막을 형성하는 방법 및 장치 |

| TWI505473B (zh) * | 2005-01-28 | 2015-10-21 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US20070295399A1 (en) * | 2005-12-16 | 2007-12-27 | Bp Corporation North America Inc. | Back-Contact Photovoltaic Cells |

| JP4283803B2 (ja) * | 2005-12-28 | 2009-06-24 | Tdk株式会社 | Ptc素子 |

| JP5331389B2 (ja) | 2007-06-15 | 2013-10-30 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| CN102007585B (zh) * | 2008-04-18 | 2013-05-29 | 株式会社半导体能源研究所 | 薄膜晶体管及其制造方法 |

-

2009

- 2009-04-10 KR KR1020107023162A patent/KR101455317B1/ko active IP Right Grant

- 2009-04-10 WO PCT/JP2009/057711 patent/WO2009128522A1/en active Application Filing

- 2009-04-10 CN CN2009801138105A patent/CN102007586B/zh not_active Expired - Fee Related

- 2009-04-14 US US12/423,123 patent/US8119468B2/en not_active Expired - Fee Related

- 2009-04-16 TW TW098112647A patent/TWI489558B/zh not_active IP Right Cessation

- 2009-04-17 JP JP2009101238A patent/JP5464893B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8119468B2 (en) | 2012-02-21 |

| KR20100134669A (ko) | 2010-12-23 |

| TW201005836A (en) | 2010-02-01 |

| CN102007586A (zh) | 2011-04-06 |

| TWI489558B (zh) | 2015-06-21 |

| CN102007586B (zh) | 2013-09-25 |

| KR101455317B1 (ko) | 2014-10-27 |

| WO2009128522A1 (en) | 2009-10-22 |

| JP2009278081A (ja) | 2009-11-26 |

| US20090261328A1 (en) | 2009-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5464893B2 (ja) | 半導体装置 | |

| JP5464894B2 (ja) | 半導体装置 | |

| JP5448603B2 (ja) | 薄膜トランジスタ | |

| JP5416460B2 (ja) | 薄膜トランジスタおよび薄膜トランジスタの作製方法 | |

| JP5448604B2 (ja) | 薄膜トランジスタ | |

| JP5436017B2 (ja) | 半導体装置 | |

| JP5517441B2 (ja) | 半導体膜の形成方法、薄膜トランジスタの作製方法及び表示装置の作製方法 | |

| JP5436016B2 (ja) | 半導体装置 | |

| JP5542364B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP5311957B2 (ja) | 表示装置及びその作製方法 | |

| JP2009071285A (ja) | 表示装置の作製方法 | |

| JP2009071284A (ja) | 表示装置 | |

| JP5518366B2 (ja) | 薄膜トランジスタ | |

| JP5602389B2 (ja) | 薄膜トランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120409 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131015 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131022 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140121 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5464893 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |