JP5377061B2 - 光電変換装置 - Google Patents

光電変換装置 Download PDFInfo

- Publication number

- JP5377061B2 JP5377061B2 JP2009108991A JP2009108991A JP5377061B2 JP 5377061 B2 JP5377061 B2 JP 5377061B2 JP 2009108991 A JP2009108991 A JP 2009108991A JP 2009108991 A JP2009108991 A JP 2009108991A JP 5377061 B2 JP5377061 B2 JP 5377061B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- semiconductor

- layer

- crystal

- photoelectric conversion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000006243 chemical reaction Methods 0.000 title claims abstract description 218

- 239000004065 semiconductor Substances 0.000 claims abstract description 579

- 239000013078 crystal Substances 0.000 claims abstract description 287

- 239000012535 impurity Substances 0.000 claims abstract description 140

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 54

- 229910052757 nitrogen Inorganic materials 0.000 claims description 27

- 238000001004 secondary ion mass spectrometry Methods 0.000 claims description 7

- 239000010410 layer Substances 0.000 description 548

- 239000010408 film Substances 0.000 description 132

- 239000007789 gas Substances 0.000 description 106

- 239000000758 substrate Substances 0.000 description 92

- 239000000463 material Substances 0.000 description 55

- 230000015572 biosynthetic process Effects 0.000 description 51

- 238000000034 method Methods 0.000 description 48

- 238000010790 dilution Methods 0.000 description 33

- 239000012895 dilution Substances 0.000 description 33

- 239000012495 reaction gas Substances 0.000 description 31

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 28

- 229910052760 oxygen Inorganic materials 0.000 description 28

- 239000001301 oxygen Substances 0.000 description 28

- 239000004020 conductor Substances 0.000 description 27

- 229920005989 resin Polymers 0.000 description 26

- 239000011347 resin Substances 0.000 description 26

- -1 SiH 2 Cl 2 Chemical compound 0.000 description 24

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 24

- 239000010409 thin film Substances 0.000 description 24

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 23

- 229920001940 conductive polymer Polymers 0.000 description 23

- 229910021417 amorphous silicon Inorganic materials 0.000 description 21

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 20

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 19

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 18

- 239000002131 composite material Substances 0.000 description 18

- 238000004519 manufacturing process Methods 0.000 description 18

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 238000002156 mixing Methods 0.000 description 15

- 229910052710 silicon Inorganic materials 0.000 description 15

- 239000010703 silicon Substances 0.000 description 15

- 239000002904 solvent Substances 0.000 description 15

- 239000011229 interlayer Substances 0.000 description 14

- 229910052751 metal Inorganic materials 0.000 description 14

- 239000002184 metal Substances 0.000 description 14

- 238000010438 heat treatment Methods 0.000 description 13

- 150000002894 organic compounds Chemical class 0.000 description 13

- 229910000077 silane Inorganic materials 0.000 description 13

- 239000012298 atmosphere Substances 0.000 description 11

- 239000000203 mixture Substances 0.000 description 11

- 239000002245 particle Substances 0.000 description 11

- 239000002861 polymer material Substances 0.000 description 11

- 239000010936 titanium Substances 0.000 description 11

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 10

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 239000000969 carrier Substances 0.000 description 10

- 230000012010 growth Effects 0.000 description 10

- 239000001257 hydrogen Substances 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 10

- 229910052709 silver Inorganic materials 0.000 description 10

- 229910052719 titanium Inorganic materials 0.000 description 10

- 238000010521 absorption reaction Methods 0.000 description 9

- 238000001035 drying Methods 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 9

- 239000004332 silver Substances 0.000 description 9

- 239000011787 zinc oxide Substances 0.000 description 9

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 7

- 230000015556 catabolic process Effects 0.000 description 7

- 238000006731 degradation reaction Methods 0.000 description 7

- 238000007865 diluting Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 229910052990 silicon hydride Inorganic materials 0.000 description 7

- 229910052715 tantalum Inorganic materials 0.000 description 7

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 7

- 230000007704 transition Effects 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- 238000000576 coating method Methods 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 238000010304 firing Methods 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- 239000007769 metal material Substances 0.000 description 6

- 238000007639 printing Methods 0.000 description 6

- 239000011241 protective layer Substances 0.000 description 6

- 238000000926 separation method Methods 0.000 description 6

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 230000006872 improvement Effects 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 4

- 239000002253 acid Substances 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000003085 diluting agent Substances 0.000 description 4

- 238000007599 discharging Methods 0.000 description 4

- 239000002270 dispersing agent Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 150000002484 inorganic compounds Chemical class 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 230000031700 light absorption Effects 0.000 description 4

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 4

- 239000002105 nanoparticle Substances 0.000 description 4

- 239000003960 organic solvent Substances 0.000 description 4

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 4

- 238000007650 screen-printing Methods 0.000 description 4

- 238000007789 sealing Methods 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- 229920001187 thermosetting polymer Polymers 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- OKKJLVBELUTLKV-UHFFFAOYSA-N Methanol Chemical compound OC OKKJLVBELUTLKV-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 239000011230 binding agent Substances 0.000 description 3

- 150000001716 carbazoles Chemical class 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 229910052743 krypton Inorganic materials 0.000 description 3

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 229910052754 neon Inorganic materials 0.000 description 3

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 3

- 230000000737 periodic effect Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229920000767 polyaniline Polymers 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 229920000139 polyethylene terephthalate Polymers 0.000 description 3

- 239000005020 polyethylene terephthalate Substances 0.000 description 3

- 229920000128 polypyrrole Polymers 0.000 description 3

- 229920000123 polythiophene Polymers 0.000 description 3

- 238000003672 processing method Methods 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 3

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 3

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 3

- UHXOHPVVEHBKKT-UHFFFAOYSA-N 1-(2,2-diphenylethenyl)-4-[4-(2,2-diphenylethenyl)phenyl]benzene Chemical group C=1C=C(C=2C=CC(C=C(C=3C=CC=CC=3)C=3C=CC=CC=3)=CC=2)C=CC=1C=C(C=1C=CC=CC=1)C1=CC=CC=C1 UHXOHPVVEHBKKT-UHFFFAOYSA-N 0.000 description 2

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 2

- QENGPZGAWFQWCZ-UHFFFAOYSA-N 3-Methylthiophene Chemical compound CC=1C=CSC=1 QENGPZGAWFQWCZ-UHFFFAOYSA-N 0.000 description 2

- VFUDMQLBKNMONU-UHFFFAOYSA-N 9-[4-(4-carbazol-9-ylphenyl)phenyl]carbazole Chemical group C12=CC=CC=C2C2=CC=CC=C2N1C1=CC=C(C=2C=CC(=CC=2)N2C3=CC=CC=C3C3=CC=CC=C32)C=C1 VFUDMQLBKNMONU-UHFFFAOYSA-N 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- LSNNMFCWUKXFEE-UHFFFAOYSA-M Bisulfite Chemical compound OS([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-M 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 239000002841 Lewis acid Substances 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 238000001237 Raman spectrum Methods 0.000 description 2

- 229910001128 Sn alloy Inorganic materials 0.000 description 2

- PPBRXRYQALVLMV-UHFFFAOYSA-N Styrene Chemical compound C=CC1=CC=CC=C1 PPBRXRYQALVLMV-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- MWPLVEDNUUSJAV-UHFFFAOYSA-N anthracene Chemical compound C1=CC=CC2=CC3=CC=CC=C3C=C21 MWPLVEDNUUSJAV-UHFFFAOYSA-N 0.000 description 2

- ILAHWRKJUDSMFH-UHFFFAOYSA-N boron tribromide Chemical compound BrB(Br)Br ILAHWRKJUDSMFH-UHFFFAOYSA-N 0.000 description 2

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 150000001732 carboxylic acid derivatives Chemical class 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 229920001577 copolymer Polymers 0.000 description 2

- VPUGDVKSAQVFFS-UHFFFAOYSA-N coronene Chemical compound C1=C(C2=C34)C=CC3=CC=C(C=C3)C4=C4C3=CC=C(C=C3)C4=C2C3=C1 VPUGDVKSAQVFFS-UHFFFAOYSA-N 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- ZUOUZKKEUPVFJK-UHFFFAOYSA-N diphenyl Chemical compound C1=CC=CC=C1C1=CC=CC=C1 ZUOUZKKEUPVFJK-UHFFFAOYSA-N 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 239000005357 flat glass Substances 0.000 description 2

- 230000004927 fusion Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 150000002366 halogen compounds Chemical class 0.000 description 2

- AMWRITDGCCNYAT-UHFFFAOYSA-L hydroxy(oxo)manganese;manganese Chemical compound [Mn].O[Mn]=O.O[Mn]=O AMWRITDGCCNYAT-UHFFFAOYSA-L 0.000 description 2

- GRPQBOKWXNIQMF-UHFFFAOYSA-N indium(3+) oxygen(2-) tin(4+) Chemical compound [Sn+4].[O-2].[In+3] GRPQBOKWXNIQMF-UHFFFAOYSA-N 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- HJOVHMDZYOCNQW-UHFFFAOYSA-N isophorone Chemical compound CC1=CC(=O)CC(C)(C)C1 HJOVHMDZYOCNQW-UHFFFAOYSA-N 0.000 description 2

- 150000007517 lewis acids Chemical class 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- RNVCVTLRINQCPJ-UHFFFAOYSA-N o-toluidine Chemical compound CC1=CC=CC=C1N RNVCVTLRINQCPJ-UHFFFAOYSA-N 0.000 description 2

- 230000000149 penetrating effect Effects 0.000 description 2

- VLTRZXGMWDSKGL-UHFFFAOYSA-N perchloric acid Chemical compound OCl(=O)(=O)=O VLTRZXGMWDSKGL-UHFFFAOYSA-N 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 238000001782 photodegradation Methods 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 239000009719 polyimide resin Substances 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 238000004151 rapid thermal annealing Methods 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- RTSZQXSYCGBHMO-UHFFFAOYSA-N 1,2,4-trichloro-3-prop-1-ynoxybenzene Chemical compound CC#COC1=C(Cl)C=CC(Cl)=C1Cl RTSZQXSYCGBHMO-UHFFFAOYSA-N 0.000 description 1

- OXHNLMTVIGZXSG-UHFFFAOYSA-N 1-Methylpyrrole Chemical compound CN1C=CC=C1 OXHNLMTVIGZXSG-UHFFFAOYSA-N 0.000 description 1

- XOYZGLGJSAZOAG-UHFFFAOYSA-N 1-n,1-n,4-n-triphenyl-4-n-[4-[4-(n-[4-(n-phenylanilino)phenyl]anilino)phenyl]phenyl]benzene-1,4-diamine Chemical group C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 XOYZGLGJSAZOAG-UHFFFAOYSA-N 0.000 description 1

- FQNVFRPAQRVHKO-UHFFFAOYSA-N 1-n,4-n-bis(4-methylphenyl)-1-n,4-n-diphenylbenzene-1,4-diamine Chemical compound C1=CC(C)=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC(C)=CC=1)C1=CC=CC=C1 FQNVFRPAQRVHKO-UHFFFAOYSA-N 0.000 description 1

- SPDPTFAJSFKAMT-UHFFFAOYSA-N 1-n-[4-[4-(n-[4-(3-methyl-n-(3-methylphenyl)anilino)phenyl]anilino)phenyl]phenyl]-4-n,4-n-bis(3-methylphenyl)-1-n-phenylbenzene-1,4-diamine Chemical compound CC1=CC=CC(N(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=CC(=CC=2)N(C=2C=C(C)C=CC=2)C=2C=C(C)C=CC=2)C=2C=C(C)C=CC=2)=C1 SPDPTFAJSFKAMT-UHFFFAOYSA-N 0.000 description 1

- ZPOROQKDAPEMOL-UHFFFAOYSA-N 1h-pyrrol-3-ol Chemical compound OC=1C=CNC=1 ZPOROQKDAPEMOL-UHFFFAOYSA-N 0.000 description 1

- JEBPFDQAOYARIB-UHFFFAOYSA-N 2,3,6,7-tetramethyl-9,10-dinaphthalen-2-ylanthracene Chemical compound C1=CC=CC2=CC(C=3C4=CC(C)=C(C)C=C4C(C=4C=C5C=CC=CC5=CC=4)=C4C=C(C(=CC4=3)C)C)=CC=C21 JEBPFDQAOYARIB-UHFFFAOYSA-N 0.000 description 1

- BFTIPCRZWILUIY-UHFFFAOYSA-N 2,5,8,11-tetratert-butylperylene Chemical group CC(C)(C)C1=CC(C2=CC(C(C)(C)C)=CC=3C2=C2C=C(C=3)C(C)(C)C)=C3C2=CC(C(C)(C)C)=CC3=C1 BFTIPCRZWILUIY-UHFFFAOYSA-N 0.000 description 1

- UCDCWSBXWOGCKR-UHFFFAOYSA-N 2-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC=C1N UCDCWSBXWOGCKR-UHFFFAOYSA-N 0.000 description 1

- HONWGFNQCPRRFM-UHFFFAOYSA-N 2-n-(3-methylphenyl)-1-n,1-n,2-n-triphenylbenzene-1,2-diamine Chemical compound CC1=CC=CC(N(C=2C=CC=CC=2)C=2C(=CC=CC=2)N(C=2C=CC=CC=2)C=2C=CC=CC=2)=C1 HONWGFNQCPRRFM-UHFFFAOYSA-N 0.000 description 1

- RUUWTSREEUTULQ-UHFFFAOYSA-N 2-octylaniline Chemical compound CCCCCCCCC1=CC=CC=C1N RUUWTSREEUTULQ-UHFFFAOYSA-N 0.000 description 1

- UWRZIZXBOLBCON-UHFFFAOYSA-N 2-phenylethenamine Chemical compound NC=CC1=CC=CC=C1 UWRZIZXBOLBCON-UHFFFAOYSA-N 0.000 description 1

- IBHNCJLKIQIKFU-UHFFFAOYSA-N 2-tert-butyl-9,10-bis(2-naphthalen-1-ylphenyl)anthracene Chemical compound C1=CC=C2C(C3=CC=CC=C3C3=C4C=CC=CC4=C(C=4C(=CC=CC=4)C=4C5=CC=CC=C5C=CC=4)C4=CC=C(C=C43)C(C)(C)C)=CC=CC2=C1 IBHNCJLKIQIKFU-UHFFFAOYSA-N 0.000 description 1

- MNHPNCZSKTUPMB-UHFFFAOYSA-N 2-tert-butyl-9,10-bis(4-phenylphenyl)anthracene Chemical compound C=12C=CC=CC2=C(C=2C=CC(=CC=2)C=2C=CC=CC=2)C2=CC(C(C)(C)C)=CC=C2C=1C(C=C1)=CC=C1C1=CC=CC=C1 MNHPNCZSKTUPMB-UHFFFAOYSA-N 0.000 description 1

- ONMVVYFKZFORGI-UHFFFAOYSA-N 2-tert-butyl-9,10-dinaphthalen-1-ylanthracene Chemical compound C1=CC=C2C(C3=C4C=CC=CC4=C(C=4C5=CC=CC=C5C=CC=4)C4=CC=C(C=C43)C(C)(C)C)=CC=CC2=C1 ONMVVYFKZFORGI-UHFFFAOYSA-N 0.000 description 1

- OBAJPWYDYFEBTF-UHFFFAOYSA-N 2-tert-butyl-9,10-dinaphthalen-2-ylanthracene Chemical compound C1=CC=CC2=CC(C3=C4C=CC=CC4=C(C=4C=C5C=CC=CC5=CC=4)C4=CC=C(C=C43)C(C)(C)C)=CC=C21 OBAJPWYDYFEBTF-UHFFFAOYSA-N 0.000 description 1

- WBPXZSIKOVBSAS-UHFFFAOYSA-N 2-tert-butylanthracene Chemical compound C1=CC=CC2=CC3=CC(C(C)(C)C)=CC=C3C=C21 WBPXZSIKOVBSAS-UHFFFAOYSA-N 0.000 description 1

- LGPVKMIWERPYIJ-UHFFFAOYSA-N 3,4-dibutyl-1h-pyrrole Chemical compound CCCCC1=CNC=C1CCCC LGPVKMIWERPYIJ-UHFFFAOYSA-N 0.000 description 1

- OJFOWGWQOFZNNJ-UHFFFAOYSA-N 3,4-dimethyl-1h-pyrrole Chemical compound CC1=CNC=C1C OJFOWGWQOFZNNJ-UHFFFAOYSA-N 0.000 description 1

- JSOMPMRZESLPSM-UHFFFAOYSA-N 3-(2-methylpropyl)aniline Chemical compound CC(C)CC1=CC=CC(N)=C1 JSOMPMRZESLPSM-UHFFFAOYSA-N 0.000 description 1

- TVMBOHMLKCZFFW-UHFFFAOYSA-N 3-N,6-N,9-triphenyl-3-N,6-N-bis(9-phenylcarbazol-3-yl)carbazole-3,6-diamine Chemical compound C1=CC=CC=C1N(C=1C=C2C3=CC(=CC=C3N(C=3C=CC=CC=3)C2=CC=1)N(C=1C=CC=CC=1)C=1C=C2C3=CC=CC=C3N(C=3C=CC=CC=3)C2=CC=1)C1=CC=C(N(C=2C=CC=CC=2)C=2C3=CC=CC=2)C3=C1 TVMBOHMLKCZFFW-UHFFFAOYSA-N 0.000 description 1

- ZAJAQTYSTDTMCU-UHFFFAOYSA-N 3-aminobenzenesulfonic acid Chemical compound NC1=CC=CC(S(O)(=O)=O)=C1 ZAJAQTYSTDTMCU-UHFFFAOYSA-N 0.000 description 1

- ATWNFFKGYPYZPJ-UHFFFAOYSA-N 3-butyl-1h-pyrrole Chemical compound CCCCC=1C=CNC=1 ATWNFFKGYPYZPJ-UHFFFAOYSA-N 0.000 description 1

- KPOCSQCZXMATFR-UHFFFAOYSA-N 3-butylthiophene Chemical compound CCCCC=1C=CSC=1 KPOCSQCZXMATFR-UHFFFAOYSA-N 0.000 description 1

- FFRZVVFLHHGORC-UHFFFAOYSA-N 3-decyl-1h-pyrrole Chemical compound CCCCCCCCCCC=1C=CNC=1 FFRZVVFLHHGORC-UHFFFAOYSA-N 0.000 description 1

- JAYBIBLZTQMCAY-UHFFFAOYSA-N 3-decylthiophene Chemical compound CCCCCCCCCCC=1C=CSC=1 JAYBIBLZTQMCAY-UHFFFAOYSA-N 0.000 description 1

- RFKWIEFTBMACPZ-UHFFFAOYSA-N 3-dodecylthiophene Chemical compound CCCCCCCCCCCCC=1C=CSC=1 RFKWIEFTBMACPZ-UHFFFAOYSA-N 0.000 description 1

- KEAYXGHOGPUYPB-UHFFFAOYSA-N 3-ethoxy-1h-pyrrole Chemical compound CCOC=1C=CNC=1 KEAYXGHOGPUYPB-UHFFFAOYSA-N 0.000 description 1

- OTODBDQJLMYYKQ-UHFFFAOYSA-N 3-methoxy-1h-pyrrole Chemical compound COC=1C=CNC=1 OTODBDQJLMYYKQ-UHFFFAOYSA-N 0.000 description 1

- FEKWWZCCJDUWLY-UHFFFAOYSA-N 3-methyl-1h-pyrrole Chemical compound CC=1C=CNC=1 FEKWWZCCJDUWLY-UHFFFAOYSA-N 0.000 description 1

- OGGKVJMNFFSDEV-UHFFFAOYSA-N 3-methyl-n-[4-[4-(n-(3-methylphenyl)anilino)phenyl]phenyl]-n-phenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 OGGKVJMNFFSDEV-UHFFFAOYSA-N 0.000 description 1

- YIRWZHZOCIDDAH-UHFFFAOYSA-N 3-octoxy-1h-pyrrole Chemical compound CCCCCCCCOC=1C=CNC=1 YIRWZHZOCIDDAH-UHFFFAOYSA-N 0.000 description 1

- AUVZKIJQGLYISA-UHFFFAOYSA-N 3-octoxythiophene Chemical compound CCCCCCCCOC=1C=CSC=1 AUVZKIJQGLYISA-UHFFFAOYSA-N 0.000 description 1

- WFHVTZRAIPYMMO-UHFFFAOYSA-N 3-octyl-1h-pyrrole Chemical compound CCCCCCCCC=1C=CNC=1 WFHVTZRAIPYMMO-UHFFFAOYSA-N 0.000 description 1

- PRPLKAUMELMCKP-UHFFFAOYSA-N 4-methyl-1h-pyrrol-3-ol Chemical compound CC1=CNC=C1O PRPLKAUMELMCKP-UHFFFAOYSA-N 0.000 description 1

- FXPOCCDGHHTZAO-UHFFFAOYSA-N 4-methyl-1h-pyrrole-3-carboxylic acid Chemical compound CC1=CNC=C1C(O)=O FXPOCCDGHHTZAO-UHFFFAOYSA-N 0.000 description 1

- LRFIHWGUGBXFEC-UHFFFAOYSA-N 4-methylthiophene-3-carboxylic acid Chemical compound CC1=CSC=C1C(O)=O LRFIHWGUGBXFEC-UHFFFAOYSA-N 0.000 description 1

- USIXUMGAHVBSHQ-UHFFFAOYSA-N 9,10-bis(3,5-diphenylphenyl)anthracene Chemical compound C1=CC=CC=C1C1=CC(C=2C=CC=CC=2)=CC(C=2C3=CC=CC=C3C(C=3C=C(C=C(C=3)C=3C=CC=CC=3)C=3C=CC=CC=3)=C3C=CC=CC3=2)=C1 USIXUMGAHVBSHQ-UHFFFAOYSA-N 0.000 description 1

- BITWULPDIGXQDL-UHFFFAOYSA-N 9,10-bis[4-(2,2-diphenylethenyl)phenyl]anthracene Chemical compound C=1C=C(C=2C3=CC=CC=C3C(C=3C=CC(C=C(C=4C=CC=CC=4)C=4C=CC=CC=4)=CC=3)=C3C=CC=CC3=2)C=CC=1C=C(C=1C=CC=CC=1)C1=CC=CC=C1 BITWULPDIGXQDL-UHFFFAOYSA-N 0.000 description 1

- VIZUPBYFLORCRA-UHFFFAOYSA-N 9,10-dinaphthalen-2-ylanthracene Chemical compound C12=CC=CC=C2C(C2=CC3=CC=CC=C3C=C2)=C(C=CC=C2)C2=C1C1=CC=C(C=CC=C2)C2=C1 VIZUPBYFLORCRA-UHFFFAOYSA-N 0.000 description 1

- FCNCGHJSNVOIKE-UHFFFAOYSA-N 9,10-diphenylanthracene Chemical compound C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 FCNCGHJSNVOIKE-UHFFFAOYSA-N 0.000 description 1

- OEYLQYLOSLLBTR-UHFFFAOYSA-N 9-(2-phenylphenyl)-10-[10-(2-phenylphenyl)anthracen-9-yl]anthracene Chemical group C1=CC=CC=C1C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1C1=CC=CC=C1 OEYLQYLOSLLBTR-UHFFFAOYSA-N 0.000 description 1

- DQMMBEPJQZXXGK-UHFFFAOYSA-N 9-(4-phenylphenyl)carbazole Chemical compound C1=CC=CC=C1C1=CC=C(N2C3=CC=CC=C3C3=CC=CC=C32)C=C1 DQMMBEPJQZXXGK-UHFFFAOYSA-N 0.000 description 1

- XCICDYGIJBPNPC-UHFFFAOYSA-N 9-[4-[3,5-bis(4-carbazol-9-ylphenyl)phenyl]phenyl]carbazole Chemical compound C12=CC=CC=C2C2=CC=CC=C2N1C1=CC=C(C=2C=C(C=C(C=2)C=2C=CC(=CC=2)N2C3=CC=CC=C3C3=CC=CC=C32)C=2C=CC(=CC=2)N2C3=CC=CC=C3C3=CC=CC=C32)C=C1 XCICDYGIJBPNPC-UHFFFAOYSA-N 0.000 description 1

- SXGIRTCIFPJUEQ-UHFFFAOYSA-N 9-anthracen-9-ylanthracene Chemical group C1=CC=CC2=CC3=CC=CC=C3C(C=3C4=CC=CC=C4C=C4C=CC=CC4=3)=C21 SXGIRTCIFPJUEQ-UHFFFAOYSA-N 0.000 description 1

- NBYGJKGEGNTQBK-UHFFFAOYSA-N 9-phenyl-10-(10-phenylanthracen-9-yl)anthracene Chemical group C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 NBYGJKGEGNTQBK-UHFFFAOYSA-N 0.000 description 1

- 229910002012 Aerosil® Inorganic materials 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 229910021630 Antimony pentafluoride Inorganic materials 0.000 description 1

- 229910015900 BF3 Inorganic materials 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- ZKHISQHQYQCSJE-UHFFFAOYSA-N C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=C(C=C(C=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=C(C=C(C=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)N(C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 ZKHISQHQYQCSJE-UHFFFAOYSA-N 0.000 description 1

- TXGYLDFMFJXYEO-UHFFFAOYSA-N CC1=CC2=C(C3=CC(=C(C=C3C(=C2C=C1C)C1=CC=CC2=CC=CC=C12)C)C)C1=CC=CC2=CC=CC=C12.C1(=CC=CC2=CC=CC=C12)C1=C(C=CC=C1)C=1C2=CC=CC=C2C(=C2C=CC=CC12)C1=C(C=CC=C1)C1=CC=CC2=CC=CC=C12 Chemical compound CC1=CC2=C(C3=CC(=C(C=C3C(=C2C=C1C)C1=CC=CC2=CC=CC=C12)C)C)C1=CC=CC2=CC=CC=C12.C1(=CC=CC2=CC=CC=C12)C1=C(C=CC=C1)C=1C2=CC=CC=C2C(=C2C=CC=CC12)C1=C(C=CC=C1)C1=CC=CC2=CC=CC=C12 TXGYLDFMFJXYEO-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- QZRGKCOWNLSUDK-UHFFFAOYSA-N Iodochlorine Chemical compound ICl QZRGKCOWNLSUDK-UHFFFAOYSA-N 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- NTIZESTWPVYFNL-UHFFFAOYSA-N Methyl isobutyl ketone Chemical compound CC(C)CC(C)=O NTIZESTWPVYFNL-UHFFFAOYSA-N 0.000 description 1

- UIHCLUNTQKBZGK-UHFFFAOYSA-N Methyl isobutyl ketone Natural products CCC(C)C(C)=O UIHCLUNTQKBZGK-UHFFFAOYSA-N 0.000 description 1

- FXHOOIRPVKKKFG-UHFFFAOYSA-N N,N-Dimethylacetamide Chemical compound CN(C)C(C)=O FXHOOIRPVKKKFG-UHFFFAOYSA-N 0.000 description 1

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229920000571 Nylon 11 Polymers 0.000 description 1

- 229920000299 Nylon 12 Polymers 0.000 description 1

- 229920002292 Nylon 6 Polymers 0.000 description 1

- 229920002302 Nylon 6,6 Polymers 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- 239000002033 PVDF binder Substances 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229920000280 Poly(3-octylthiophene) Polymers 0.000 description 1

- 239000004962 Polyamide-imide Substances 0.000 description 1

- 229920002396 Polyurea Polymers 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- XBDYBAVJXHJMNQ-UHFFFAOYSA-N Tetrahydroanthracene Natural products C1=CC=C2C=C(CCCC3)C3=CC2=C1 XBDYBAVJXHJMNQ-UHFFFAOYSA-N 0.000 description 1

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 1

- 239000007983 Tris buffer Substances 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 1

- RZZQJFHQKOPJFD-UHFFFAOYSA-N [O-2].[Zn+2].[O-2].[In+3].[Sn+4] Chemical compound [O-2].[Zn+2].[O-2].[In+3].[Sn+4] RZZQJFHQKOPJFD-UHFFFAOYSA-N 0.000 description 1

- SORGEQQSQGNZFI-UHFFFAOYSA-N [azido(phenoxy)phosphoryl]oxybenzene Chemical compound C=1C=CC=CC=1OP(=O)(N=[N+]=[N-])OC1=CC=CC=C1 SORGEQQSQGNZFI-UHFFFAOYSA-N 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 150000004703 alkoxides Chemical class 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 125000002490 anilino group Chemical group [H]N(*)C1=C([H])C([H])=C([H])C([H])=C1[H] 0.000 description 1

- 239000002518 antifoaming agent Substances 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- VBVBHWZYQGJZLR-UHFFFAOYSA-I antimony pentafluoride Chemical compound F[Sb](F)(F)(F)F VBVBHWZYQGJZLR-UHFFFAOYSA-I 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 239000003849 aromatic solvent Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- YBGKQGSCGDNZIB-UHFFFAOYSA-N arsenic pentafluoride Chemical compound F[As](F)(F)(F)F YBGKQGSCGDNZIB-UHFFFAOYSA-N 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 235000010290 biphenyl Nutrition 0.000 description 1

- 239000004305 biphenyl Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000009835 boiling Methods 0.000 description 1

- QDWJUBJKEHXSMT-UHFFFAOYSA-N boranylidynenickel Chemical compound [Ni]#B QDWJUBJKEHXSMT-UHFFFAOYSA-N 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- 229910052794 bromium Inorganic materials 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229910000423 chromium oxide Inorganic materials 0.000 description 1

- 238000010549 co-Evaporation Methods 0.000 description 1

- 238000004581 coalescence Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000002178 crystalline material Substances 0.000 description 1

- BHQBDOOJEZXHPS-UHFFFAOYSA-N ctk3i0272 Chemical group C1=CC=CC=C1C(C(=C(C=1C=CC=CC=1)C(=C1C=2C=CC=CC=2)C=2C3=CC=CC=C3C(C=3C4=CC=CC=C4C(C=4C(=C(C=5C=CC=CC=5)C(C=5C=CC=CC=5)=C(C=5C=CC=CC=5)C=4C=4C=CC=CC=4)C=4C=CC=CC=4)=C4C=CC=CC4=3)=C3C=CC=CC3=2)C=2C=CC=CC=2)=C1C1=CC=CC=C1 BHQBDOOJEZXHPS-UHFFFAOYSA-N 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 125000004093 cyano group Chemical group *C#N 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 239000000412 dendrimer Substances 0.000 description 1

- 229920000736 dendritic polymer Polymers 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- JBTWLSYIZRCDFO-UHFFFAOYSA-N ethyl methyl carbonate Chemical compound CCOC(=O)OC JBTWLSYIZRCDFO-UHFFFAOYSA-N 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 239000003205 fragrance Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-N hexanoic acid Chemical compound CCCCCC(O)=O FUZZWVXGSFPDMH-UHFFFAOYSA-N 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 150000002430 hydrocarbons Chemical class 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 1

- CBEQRNSPHCCXSH-UHFFFAOYSA-N iodine monobromide Chemical compound IBr CBEQRNSPHCCXSH-UHFFFAOYSA-N 0.000 description 1

- PDJAZCSYYQODQF-UHFFFAOYSA-N iodine monofluoride Chemical compound IF PDJAZCSYYQODQF-UHFFFAOYSA-N 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 239000005355 lead glass Substances 0.000 description 1

- 125000000040 m-tolyl group Chemical group [H]C1=C([H])C(*)=C([H])C(=C1[H])C([H])([H])[H] 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 239000002923 metal particle Substances 0.000 description 1

- 150000007522 mineralic acids Chemical class 0.000 description 1

- 239000012046 mixed solvent Substances 0.000 description 1

- WOYDRSOIBHFMGB-UHFFFAOYSA-N n,9-diphenyl-n-(9-phenylcarbazol-3-yl)carbazol-3-amine Chemical compound C1=CC=CC=C1N(C=1C=C2C3=CC=CC=C3N(C=3C=CC=CC=3)C2=CC=1)C1=CC=C(N(C=2C=CC=CC=2)C=2C3=CC=CC=2)C3=C1 WOYDRSOIBHFMGB-UHFFFAOYSA-N 0.000 description 1

- UMFJAHHVKNCGLG-UHFFFAOYSA-N n-Nitrosodimethylamine Chemical compound CN(C)N=O UMFJAHHVKNCGLG-UHFFFAOYSA-N 0.000 description 1

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical group C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 1

- 125000001624 naphthyl group Chemical group 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 235000005985 organic acids Nutrition 0.000 description 1

- 150000002902 organometallic compounds Chemical class 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- YWXLYZIZWVOMML-UHFFFAOYSA-N oxirane-2,2,3,3-tetracarbonitrile Chemical compound N#CC1(C#N)OC1(C#N)C#N YWXLYZIZWVOMML-UHFFFAOYSA-N 0.000 description 1

- DYIZHKNUQPHNJY-UHFFFAOYSA-N oxorhenium Chemical compound [Re]=O DYIZHKNUQPHNJY-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- 125000002080 perylenyl group Chemical group C1(=CC=C2C=CC=C3C4=CC=CC5=CC=CC(C1=C23)=C45)* 0.000 description 1

- CSHWQDPOILHKBI-UHFFFAOYSA-N peryrene Natural products C1=CC(C2=CC=CC=3C2=C2C=CC=3)=C3C2=CC=CC3=C1 CSHWQDPOILHKBI-UHFFFAOYSA-N 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N phenol group Chemical group C1(=CC=CC=C1)O ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 239000013034 phenoxy resin Substances 0.000 description 1

- 229920006287 phenoxy resin Polymers 0.000 description 1

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 1

- OBCUTHMOOONNBS-UHFFFAOYSA-N phosphorus pentafluoride Chemical compound FP(F)(F)(F)F OBCUTHMOOONNBS-UHFFFAOYSA-N 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 230000036417 physical growth Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 229920002849 poly(3-ethoxythiophene) polymer Polymers 0.000 description 1

- 229920002850 poly(3-methoxythiophene) polymer Polymers 0.000 description 1

- 229920000078 poly(4-vinyltriphenylamine) Polymers 0.000 description 1

- 229920002493 poly(chlorotrifluoroethylene) Polymers 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920002312 polyamide-imide Polymers 0.000 description 1

- 229920001707 polybutylene terephthalate Polymers 0.000 description 1

- 239000005023 polychlorotrifluoroethylene (PCTFE) polymer Substances 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 229920000570 polyether Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000002952 polymeric resin Substances 0.000 description 1

- 229920005749 polyurethane resin Polymers 0.000 description 1

- 229920002689 polyvinyl acetate Polymers 0.000 description 1

- 239000011118 polyvinyl acetate Substances 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 229920001289 polyvinyl ether Polymers 0.000 description 1

- 229920002620 polyvinyl fluoride Polymers 0.000 description 1

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 125000002924 primary amino group Chemical group [H]N([H])* 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- RUOJZAUFBMNUDX-UHFFFAOYSA-N propylene carbonate Chemical compound CC1COC(=O)O1 RUOJZAUFBMNUDX-UHFFFAOYSA-N 0.000 description 1

- DOYOPBSXEIZLRE-UHFFFAOYSA-N pyrrole-3-carboxylic acid Chemical compound OC(=O)C=1C=CNC=1 DOYOPBSXEIZLRE-UHFFFAOYSA-N 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 239000011342 resin composition Substances 0.000 description 1

- 229910003449 rhenium oxide Inorganic materials 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000004094 surface-active agent Substances 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- IFLREYGFSNHWGE-UHFFFAOYSA-N tetracene Chemical compound C1=CC=CC2=CC3=CC4=CC=CC=C4C=C3C=C21 IFLREYGFSNHWGE-UHFFFAOYSA-N 0.000 description 1

- NLDYACGHTUPAQU-UHFFFAOYSA-N tetracyanoethylene Chemical group N#CC(C#N)=C(C#N)C#N NLDYACGHTUPAQU-UHFFFAOYSA-N 0.000 description 1

- PCCVSPMFGIFTHU-UHFFFAOYSA-N tetracyanoquinodimethane Chemical compound N#CC(C#N)=C1C=CC(=C(C#N)C#N)C=C1 PCCVSPMFGIFTHU-UHFFFAOYSA-N 0.000 description 1

- 229920005992 thermoplastic resin Polymers 0.000 description 1

- YNVOMSDITJMNET-UHFFFAOYSA-N thiophene-3-carboxylic acid Chemical compound OC(=O)C=1C=CSC=1 YNVOMSDITJMNET-UHFFFAOYSA-N 0.000 description 1

- 239000005341 toughened glass Substances 0.000 description 1

- 229910000314 transition metal oxide Inorganic materials 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 229910001930 tungsten oxide Inorganic materials 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 229910001935 vanadium oxide Inorganic materials 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/0248—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies

- H01L31/0352—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies characterised by their shape or by the shapes, relative sizes or disposition of the semiconductor regions

- H01L31/035272—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by their semiconductor bodies characterised by their shape or by the shapes, relative sizes or disposition of the semiconductor regions characterised by at least one potential jump barrier or surface barrier

- H01L31/03529—Shape of the potential jump barrier or surface barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/042—PV modules or arrays of single PV cells

- H01L31/0475—PV cell arrays made by cells in a planar, e.g. repetitive, configuration on a single semiconductor substrate; PV cell microarrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02529—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02587—Structure

- H01L21/0259—Microstructure

- H01L21/02595—Microstructure polycrystalline

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

Description

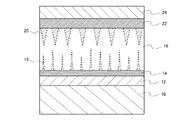

図1は本形態に係る光電変換装置の構成を示す。図1に示す光電変換装置は、基板10上に設けられた第1電極12と、該第1電極12上に設けられた第1の半導体層14と、該第1の半導体層14上に設けられた第2の半導体層16と、該第2の半導体層16上に設けられた第3の半導体層22と、該第3の半導体層22上に設けられた第2電極24と、で構成される。第1の半導体層14と第3の半導体層22は相対する一導電型を付与する不純物元素が添加された不純物半導体層であり、一方がn型半導体層、他方がp型半導体層である。第1の半導体層14と第3の半導体層22との間に設けられる第2の半導体層16は、非晶質構造の中に第1の結晶領域と第2の結晶領域とを含むi型半導体層である。本発明の一態様に係る光電変換装置は、一対の不純物半導体層である第1の半導体層14と第3の半導体層22との間に、被膜の成膜方向に向かって成長する第1の結晶領域と第2の結晶領域とを含む半導体層である第2の半導体層を有することを特徴の一つとする。また、本形態に係る光電変換装置は、このような構成にすることにより少なくとも一つの半導体接合を含む。ここでは、第1の半導体層14はn型半導体、第3の半導体層22はp型半導体、第2の半導体層はi型半導体とする例を示す。

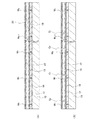

図5は、本形態に係る光電変換装置の構成を示す。この光電変換装置は、n型半導体である第1の半導体層14とp型半導体である第3の半導体層22に挟まれてi型半導体である第2の半導体層16を設けることにより、少なくとも一つの半導体接合を含んでいる。また、第1の半導体層14と第2の半導体層16の間に、低濃度不純物半導体層13を設ける構成を示す。低濃度不純物半導体層13は、第1の半導体層14と同じ導電型を付与する不純物元素を含み、且つ第1の半導体層14よりも不純物濃度が低い半導体層である。本形態では、低濃度不純物半導体層13は、n型半導体の例で説明する。

本形態では、ユニットセルを複数積層した、所謂スタック型(タンデム型を含む)光電変換装置について説明する。本形態では、単結晶半導体層(代表的には単結晶シリコン)を有するユニットセルをボトムセルとし、非単結晶半導体層(代表的には非単結晶シリコン)を有するユニットセルをトップセルとする光電変換装置の例を説明する。

本形態では、同一基板上に複数のユニットセルを形成し、複数のユニットセルを直列接続して光電変換装置を集積化する、所謂集積型光電変換装置の例を説明する。以下、集積型光電変換装置の作製工程および構成の概略について説明する。

本形態では、光電変換装置の他の態様として、光センサ装置の例を示す。

本形態では、上記実施の形態と異なる構成の集積型光電変換装置の例について説明する。以下、本形態に係る集積型光電変換装置の作製工程の概略について説明する。

12 第1電極

13 低濃度不純物半導体層

14 第1の半導体層

16 第2の半導体層

18 第1の結晶領域

20 第2の結晶領域

22 第3の半導体層

24 第2電極

Claims (3)

- 第1電極上に設けられ、微結晶半導体で形成された一導電型を付与する不純物元素を含む第1の半導体層と、

前記第1の半導体層上に設けられた第2の半導体層と、

前記第2の半導体層上に設けられ、前記一導電型とは逆導電型を付与する不純物元素を含む第3の半導体層と、

前記第3の半導体層上に設けられた第2電極と、

を有し、

前記第2の半導体層は、前記第1の半導体層との界面側に、前記第1の半導体層との界面から前記第3の半導体層に向かって幅が狭まっていく立体的形状を有する第1の結晶領域と、

前記第3の半導体層との界面側に、前記第3の半導体層との界面から前記第1の半導体層に向かって幅が狭まっていく立体的形状を有する第2の結晶領域と、

を含み、

前記第1の結晶領域は、前記第1の半導体層から前記第2の半導体層が成膜される方向に向けて上狭まりに成長しており、

前記第2の結晶領域は、前記第1の半導体層との界面とは離れた位置から上拡がりに成長しており、

前記第2の半導体層は、結晶質半導体である前記第1の結晶領域および前記第2の結晶領域が非晶質構造の中に存在し、

前記第2の半導体層は、二次イオン質量分析法によって計測される窒素濃度が2×1020/cm3以上7×1020/cm3以下の第1の領域を有し、

前記第1の領域を起点として、前記第2の結晶領域が前記第3の半導体層に向けて成長していることを特徴とする光電変換装置。 - 請求項1において、

前記第2の結晶領域は、単結晶、または、双晶を含む単結晶であることを特徴とする光電変換装置。 - 請求項1又は請求項2において、

前記第1の半導体層はn型半導体であり、前記第2の半導体層はi型半導体であり、前記第3の半導体層はp型半導体であることを特徴とする光電変換装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009108991A JP5377061B2 (ja) | 2008-05-09 | 2009-04-28 | 光電変換装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008123332 | 2008-05-09 | ||

| JP2008123332 | 2008-05-09 | ||

| JP2009108991A JP5377061B2 (ja) | 2008-05-09 | 2009-04-28 | 光電変換装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009295970A JP2009295970A (ja) | 2009-12-17 |

| JP2009295970A5 JP2009295970A5 (ja) | 2012-05-17 |

| JP5377061B2 true JP5377061B2 (ja) | 2013-12-25 |

Family

ID=41265891

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009108991A Expired - Fee Related JP5377061B2 (ja) | 2008-05-09 | 2009-04-28 | 光電変換装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8410354B2 (ja) |

| JP (1) | JP5377061B2 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7888167B2 (en) * | 2008-04-25 | 2011-02-15 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and method for manufacturing the same |

| US20090293954A1 (en) * | 2008-05-30 | 2009-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric Conversion Device And Method For Manufacturing The Same |

| US8344378B2 (en) * | 2009-06-26 | 2013-01-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and method for manufacturing the same |

| KR101072472B1 (ko) * | 2009-07-03 | 2011-10-11 | 한국철강 주식회사 | 광기전력 장치의 제조 방법 |

| CN101958361A (zh) * | 2009-07-13 | 2011-01-26 | 无锡尚德太阳能电力有限公司 | 透光薄膜太阳电池组件刻蚀方法 |

| US8704083B2 (en) * | 2010-02-11 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and fabrication method thereof |

| US9076909B2 (en) * | 2010-06-18 | 2015-07-07 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and method for manufacturing the same |

| WO2011161901A1 (ja) * | 2010-06-25 | 2011-12-29 | パナソニック株式会社 | 多結晶シリコン薄膜の形成方法、多結晶シリコン薄膜基板、シリコン薄膜太陽電池及びシリコン薄膜トランジスタ装置 |

| JP5666974B2 (ja) * | 2011-04-21 | 2015-02-12 | 株式会社東芝 | 半導体材料を用いた太陽電池 |

| WO2013080766A1 (ja) * | 2011-11-30 | 2013-06-06 | 京セラ株式会社 | 光電変換装置 |

| US9048099B2 (en) * | 2013-05-09 | 2015-06-02 | Applied Materials, Inc. | Multi-layer amorphous silicon structure with improved poly-silicon quality after excimer laser anneal |

| US10854646B2 (en) * | 2018-10-19 | 2020-12-01 | Attollo Engineering, LLC | PIN photodetector |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56122123A (en) | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| JPS6262073A (ja) | 1985-09-11 | 1987-03-18 | Ishikawajima Harima Heavy Ind Co Ltd | ポペツト弁の温度制御装置 |

| JPH0651909B2 (ja) | 1985-12-28 | 1994-07-06 | キヤノン株式会社 | 薄膜多層構造の形成方法 |

| JPH0253941A (ja) | 1988-08-17 | 1990-02-22 | Tsudakoma Corp | 織機の運転装置 |

| US5007971A (en) | 1989-01-21 | 1991-04-16 | Canon Kabushiki Kaisha | Pin heterojunction photovoltaic elements with polycrystal BP(H,F) semiconductor film |

| DE4315959C2 (de) | 1993-05-12 | 1997-09-11 | Max Planck Gesellschaft | Verfahren zur Herstellung einer strukturierten Schicht eines Halbleitermaterials sowie einer Dotierungsstruktur in einem Halbleitermaterial unter Einwirkung von Laserstrahlung |

| US5677236A (en) | 1995-02-24 | 1997-10-14 | Mitsui Toatsu Chemicals, Inc. | Process for forming a thin microcrystalline silicon semiconductor film |

| US6287888B1 (en) | 1997-12-26 | 2001-09-11 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and process for producing photoelectric conversion device |

| JP4293385B2 (ja) | 1998-01-27 | 2009-07-08 | 株式会社半導体エネルギー研究所 | 光電変換装置の作製方法 |

| JPH11274527A (ja) * | 1998-03-24 | 1999-10-08 | Sanyo Electric Co Ltd | 光起電力装置 |

| JP4282797B2 (ja) * | 1998-10-08 | 2009-06-24 | 株式会社半導体エネルギー研究所 | 光電変換装置 |

| EP0994515B1 (en) | 1998-10-12 | 2007-08-22 | Kaneka Corporation | Method of manufacturing silicon-based thin-film photoelectric conversion device |

| JP3672750B2 (ja) | 1998-10-12 | 2005-07-20 | 株式会社カネカ | シリコン系薄膜光電変換装置の製造方法 |

| JP3046965B1 (ja) | 1999-02-26 | 2000-05-29 | 鐘淵化学工業株式会社 | 非晶質シリコン系薄膜光電変換装置の製造方法 |

| JP2000277439A (ja) | 1999-03-25 | 2000-10-06 | Kanegafuchi Chem Ind Co Ltd | 結晶質シリコン系薄膜のプラズマcvd方法およびシリコン系薄膜光電変換装置の製造方法 |

| JP4488550B2 (ja) * | 1999-06-09 | 2010-06-23 | 富士電機システムズ株式会社 | 薄膜太陽電池とその製造方法 |

| JP2005050905A (ja) | 2003-07-30 | 2005-02-24 | Sharp Corp | シリコン薄膜太陽電池の製造方法 |

| EP1643564B1 (en) | 2004-09-29 | 2019-01-16 | Panasonic Intellectual Property Management Co., Ltd. | Photovoltaic device |

| US8207010B2 (en) | 2007-06-05 | 2012-06-26 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing photoelectric conversion device |

| US8138032B2 (en) | 2008-04-18 | 2012-03-20 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor having microcrystalline semiconductor film |

| WO2009128522A1 (en) | 2008-04-18 | 2009-10-22 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and method for manufacturing the same |

| JP5416460B2 (ja) | 2008-04-18 | 2014-02-12 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタおよび薄膜トランジスタの作製方法 |

| US7888167B2 (en) | 2008-04-25 | 2011-02-15 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and method for manufacturing the same |

| US20090293954A1 (en) | 2008-05-30 | 2009-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric Conversion Device And Method For Manufacturing The Same |

-

2009

- 2009-04-28 JP JP2009108991A patent/JP5377061B2/ja not_active Expired - Fee Related

- 2009-05-04 US US12/435,133 patent/US8410354B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009295970A (ja) | 2009-12-17 |

| US20090277504A1 (en) | 2009-11-12 |

| US8410354B2 (en) | 2013-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5377061B2 (ja) | 光電変換装置 | |

| JP5667750B2 (ja) | 光電変換装置および光電変換装置の作製方法 | |

| JP5433286B2 (ja) | 光電変換装置の作製方法 | |

| US8207010B2 (en) | Method for manufacturing photoelectric conversion device | |

| US7736933B2 (en) | Method for manufacturing photoelectric conversion device | |

| JP5289927B2 (ja) | 光電変換装置 | |

| JP5577030B2 (ja) | 光電変換装置及びその製造方法 | |

| KR101512785B1 (ko) | 광전 변환 장치의 제작 방법 | |

| JP5503946B2 (ja) | 光電変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120320 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120320 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130321 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130604 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130917 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130924 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5377061 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |