JP3594894B2 - ビアフィリングめっき方法 - Google Patents

ビアフィリングめっき方法 Download PDFInfo

- Publication number

- JP3594894B2 JP3594894B2 JP2000334044A JP2000334044A JP3594894B2 JP 3594894 B2 JP3594894 B2 JP 3594894B2 JP 2000334044 A JP2000334044 A JP 2000334044A JP 2000334044 A JP2000334044 A JP 2000334044A JP 3594894 B2 JP3594894 B2 JP 3594894B2

- Authority

- JP

- Japan

- Prior art keywords

- plating

- copper

- accelerator

- via hole

- filling

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D7/00—Electroplating characterised by the article coated

- C25D7/12—Semiconductors

- C25D7/123—Semiconductors first coated with a seed layer or a conductive layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/011—Manufacture or treatment of electrodes ohmically coupled to a semiconductor

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/18—Electroplating using modulated, pulsed or reversing current

-

- C—CHEMISTRY; METALLURGY

- C25—ELECTROLYTIC OR ELECTROPHORETIC PROCESSES; APPARATUS THEREFOR

- C25D—PROCESSES FOR THE ELECTROLYTIC OR ELECTROPHORETIC PRODUCTION OF COATINGS; ELECTROFORMING; APPARATUS THEREFOR

- C25D5/00—Electroplating characterised by the process; Pretreatment or after-treatment of workpieces

- C25D5/34—Pretreatment of metallic surfaces to be electroplated

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/423—Plated through-holes or plated via connections characterised by electroplating method

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09563—Metal filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S205/00—Electrolysis: processes, compositions used therein, and methods of preparing the compositions

- Y10S205/917—Treatment of workpiece between coating steps

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Organic Chemistry (AREA)

- Electrochemistry (AREA)

- Materials Engineering (AREA)

- Metallurgy (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Electroplating Methods And Accessories (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Manufacturing Of Printed Wiring (AREA)

Description

【発明の属する技術分野】

本発明はビアフィリングめっき方法に関する。

【0002】

【従来の技術】

半導体チップ等の電子部品を搭載する多層回路基板の製造方法にいわゆるビルドアップ法がある。

ビルドアップ法は、下層の銅などからなる配線パターン10上に絶縁層12を塗布または積層して形成し(図13)、この絶縁層12にビアホール14をレーザー加工もしくはフォトリソグラフィーによって形成し(図14)、底面に配線パターン10が露出するビアホール14内および絶縁層12上に無電解銅めっき、次いで電解銅めっきを施して、絶縁層12上に銅めっき層16を形成し(図15)、この銅めっき層16をエッチング加工して上層の配線パターン18を形成する(図16)ものである。この工程を繰り返すことによって、下層の配線パターン10と上層の配線パターン18とがビアめっき皮膜を介して電気的に接続される多層の回路基板が製造される。

【0003】

ところで、絶縁層12を形成する場合、ビアホール14内を導電ペーストや絶縁樹脂で埋めて、ビアホール14に起因する絶縁層表面の段差を解消するようにしているが、工数が多くなるだけでなく、平坦化にも限界がある。

そこで、昨今、ビアホール内を銅めっきで埋めるビアフィリングめっき方法が提案されている。

このビアフィリングめっき方法では、めっき液の攪拌に工夫をこらし、ビアホール内にもめっき液が良好に回り込むようにするとか、めっき液にめっき促進剤を添加し、ビアホール内のめっきの付きまわりを良好にするとかして、ビアホール内が銅めっきで埋まるようにしている。

【0004】

【発明が解決しようとする課題】

しかしながら、昨今では、配線パターンがますますファイン化し、そのためにビアホールも小径化し、アスペクト比の大きなものとなっていることから、ビアホールを銅めっきで埋めることは困難になっている。

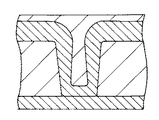

特に、めっき電流はコーナー部に集中しやすいことから、ビアホールの開口縁部にめっきが厚く付き、図17に示すようにビアホールが袋穴状となり、この袋穴内にめっき液が残留するなどの課題が生じている。

【0005】

そこで、本発明は上記課題を解決すべくなされたものであり、その目的とするところは、アスペクト比の大きな小径のビアホール内も良好に銅めっきで埋めることができるビアフィリングめっき方法を提供するにある。

【0006】

【課題を解決するための手段】

本発明は上記目的を達成するため次の構成を備える。

すなわち、導体層が底面に露出するように基板の絶縁層に形成されたビアホール内に、銅めっきを施してビアホール内をめっき金属により充填するビアフィリングめっき方法において、前記基板の絶縁層表面およびビアホールの底面を含む壁面に銅皮膜を形成する銅皮膜形成工程と、めっき促進剤が添加された水溶液中に、前記銅皮膜が形成された基板を浸漬して、前記銅皮膜表面にめっき促進剤を付着させる浸漬工程と、ビアホールの底面を含む内壁面を除く前記銅皮膜表面に付着しためっき促進剤を除去する剥離工程と、前記剥離工程の後、絶縁層表面に形成された銅皮膜およびビアホールの底面を含む壁面に形成された銅皮膜上に電解銅めっきを施して前記ビアホール内にめっき金属を充填する電解銅めっき工程とを含むことを特徴としている。

【0007】

上記方法によれば、ビアホール内に確実にめっき促進剤を付着させて基板の絶縁層表面との間にめっき条件の差異をつけることができ、ビアホール内にも電流を集中させることができ、アスペクト比の大きなビアホールであっても十分に銅めっきで埋めることができる。

【0008】

めっき促進剤として、下記の一般式〔化3〕もしくは〔化4〕で表される1種以上の硫黄化合物を用いることができる。これら硫黄化合物は、濡れ性を向上させるための、ポリエチレングリコールやポリプロピレングリコールなどの非イオン界面活性剤を添加した水溶液として用いる。

【化3】

【化4】

また、〔化3〕のめっき促進剤は、3−メルカプト−1−プロパンスルホン酸ナトリウムもしくは2−メルカプトエタンスルホン酸ナトリウム、〔化4〕のめっき促進剤は、ビス−(3−スルフォプロピル)−ジスルファイドジソディウムを効果的に用いることができる。

【0009】

前記剥離工程は、銅のエッチング液を用いるエッチング処理、シアン電解浴を用いるシアン電解処理、前記銅皮膜表面に紫外線を斜めに照射する紫外線処理、または前記銅皮膜表面を研磨する研磨処理などで行うことができる。

【0010】

前記剥離工程を省き、前記浸漬工程の後、前記電解銅めっき工程の初期の段階において、逆電解処理を行ってもよい。

また、前記剥離工程を省き、前記浸漬工程の後、前記電解銅めっき工程において正負の反転するパルスめっきを行ってもよい。

【0011】

また、前記電解銅めっき工程において、めっき促進剤を含まない電解銅めっき液を用いると好適である。

さらに、前記めっき促進剤に3−メルカプト−1−プロパンスルホン酸ナトリウムもしくは2−メルカプトエタンスルホン酸ナトリウムを用いて前記浸漬工程を行い、前記剥離工程を省き、前記電解銅めっき工程において、めっき促進剤を含まない電解銅めっき液を用いるようにしてもよい。

また、前記浸漬工程の前に、前記銅皮膜表面に銅ストライクめっきを施すようにすると好適である。

【0012】

【発明の実施の形態】

以下、本発明の好適な実施の形態を添付図面に基づいて詳細に説明する。

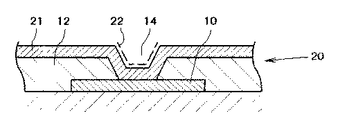

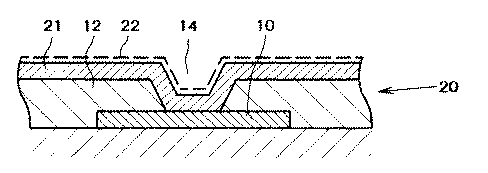

まず、図1に示すように、下層の導体層となる配線パターン10が形成された基板上に、絶縁層12を塗布または積層して形成し、絶縁層12にレーザー加工もしくはフォトリソグラフィーにより底面に配線パターン10が露出するビアホール14を形成する。例えば、基板上に、ポリフェニレンエーテル(PPE)の樹脂シートを加熱加圧して積層することにより絶縁層を形成し、この絶縁層にYAGレーザー、炭酸ガスレーザー等によるレーザー加工によりビアホールを形成するのである。

次に、無電解銅めっきを施して、絶縁層12およびビアホール14内に無電解銅めっき皮膜21を形成する。なお、無電解銅めっきに代えて、スパッタリングや蒸着によって銅皮膜21を形成してもよい。以下では、無電解銅めっき皮膜で説明する。

【0013】

次に上記基板20を、めっき促進剤が添加された水溶液中に浸漬し、無電解銅めっき皮膜21上にめっき促進剤22を付着させる(めっき促進剤層22、図2)。

めっき促進剤としては、3−メルカプト−1−プロパンスルホン酸ナトリウムもしくは2−メルカプトエタンスルホン酸ナトリウム等の、一般式

【化5】

で表される硫黄化合物、もしくはビス−(3−スルフォプロピル)−ジスルファイドジソディウム等の、一般式

【化6】

で表される硫黄化合物を用いることができる。

【0014】

これらめっき促進剤は、ブライトナー(光沢剤)と呼ばれる銅めっき液に添加する添加物の一種でもある。

めっき促進剤が被めっき物表面に付着すると、抵抗値が低下し、電流が集中してめっきが促進されると考えられる。

本発明におけるめっき促進剤とは、銅めっき液に添加した場合に、添加しない場合に比して、めっき液中に設置した参照電極に対する陰極電位が、正側に移動する硫黄化合物と定義する。

上記めっき促進剤を1種、もしくは2種以上を混合して用いる。

このめっき促進剤の水溶液の濃度は特に限定されないが、数ppm〜数%の濃度で用いることができる。

また、水溶液にかびなどが繁殖しないように、硫酸、硫酸銅などの酸性成分を添加するようにしてもよい。

【0015】

めっき促進剤溶液は常温で用い、基板20の浸漬時間はめっき促進剤溶液の濃度にもよるが、概ね5分〜15分程度と比較的長時間浸漬し、ビアホール14内へ十分にめっき促進剤溶液が進入するようにするとよい。まためっき促進剤溶液を攪拌するか、基板20を揺動させるようにするとよい。

なお、めっき促進剤溶液の基板20への濡れ性を向上させるため、基板20をあらかじめ界面活性剤溶液等の前処理液に浸漬するとよい。

浸漬後、基板20を適宜水洗する。水洗してもめっき促進剤が落ちてしまうことはない。

【0016】

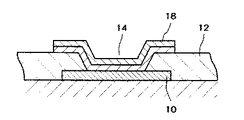

次に、図3に示すように、ビアホール14内を除く絶縁層12表面の無電解銅めっき皮膜21表面に付着しためっき促進剤22を剥離する。

この剥離工程は、塩化第1鉄水溶液等の銅のエッチング液に基板20を浸漬することで行える。基板20をこのエッチング液に浸漬し、直ちに水洗するようにする。銅のエッチング液に基板20を短時間浸漬した場合には、ビアホール14内にまでエッチング液が入り込まないので、ビアホール14内を除く無電解銅めっき皮膜21上のめっき促進剤22を選択的に剥離することができる。

【0017】

上記剥離工程は、シアン電解浴によるシアン電解処理によっても行うことができる。あるいは

無電解銅めっき21表面に対して紫外線を斜めに照射する紫外線処理によってめっき促進剤22を分解させて剥離するようにしてもよい。紫外線を基板20に対して斜めに照射することによって、紫外線がビアホール14内に進入せず、したがって、ビアホール14以外の部分に付着しているめっき促進剤を選択的に剥離可能である。あるいは、絶縁層12表面の無電解銅めっき皮膜21表面を研磨する研磨処理によってもめっき促進剤22を選択的に除去できる。

【0018】

このような剥離工程を行って後、絶縁層12表面およびビアホール14内の無電解銅めっき皮膜21上に電解銅めっきを施してビアフィリングを行う電解銅めっき工程を行う。

銅めっき液の組成の一例を下記に示す。

硫酸銅 120g/l

硫酸 190g/l

塩素イオン 50ppm

添加剤 40ml/l

添加剤の組成の一例を下記に示す。

PEG4000 180g/l

(ポリエチレングリコール)

PPG425 72g/l

(ポリプロピレングリコール)

添加剤としてこのようなポリマー成分を添加するとよい。

【0019】

上記銅めっき液には、めっき促進剤が混入されていない。

銅めっき液の組成は上記に限定されるものではない。

上記のように、めっき促進剤溶液に基板20を浸漬した後、ビアホール14内を除く絶縁層表面に付着しためっき促進剤を剥離して電解銅めっきを行うことによって、図6に示すように、ビアホール14内に電流が集中し、ビアホール14内を電解銅めっきで埋めるビアフィリングが行える(図4)。

次に、絶縁層12上に形成された銅めっき皮膜23および21をエッチングして上層の配線パターン24を形成する(図5)。

上記工程を繰り返すことによって、層間の配線パターンが銅めっきによって導通された多層の回路基板を得ることができる。

【0020】

図12は、めっき促進剤の特性を示すグラフである。

上記銅めっき液に、めっき促進剤を添加しないで銅めっきを行った場合と、5分後にめっき促進剤を銅めっき液に1ppm添加した場合における、銅めっき液中に設置した参照電極に対する陰極電位の変移を調べたものである。めっき促進剤として、3−メルカプト−1−プロパンスルホン酸ナトリウム、2−メルカプトエタンスルホン酸ナトリウム、ビス−(3−スルフォプロピル)−ジスルファイドジソディウムを添加した場合のいずれも、添加前に比して陰極電位が正側にシフトしていることがわかる。

【0021】

なお、電解銅めっき液には、ビアホール14内に効果的に電流が集中するように、めっき促進剤を添加しないものを用いるのが好適であるが、めっき促進剤を添加した電解銅めっき液を用いてもよい。この場合にも、既に上記浸漬工程でビアホール14内にはめっき促進剤が付着しているため、ビアホール14内に電流が集中し、ビアホール14内を銅めっきで埋めることができる。

【0022】

また、前記剥離工程の代わりに、電解銅めっき工程の初期の段階で、逆電解処理を行うようにしてもよい。例えば、電解銅めっき開始後数分後に、30秒毎等に陽極(正)と陰極(負)の極性を反転させて数分間銅めっきを行う。極性を反転した際に、ビアホール14以外の部分に付着しているめっき促進剤の剥離が進行し、ビアホール14内へ電流を集中させることができ、ビアホール14内を銅めっきで埋めることができた。

【0023】

あるいは、前記剥離工程の代わりに、電解銅めっき工程で正負の反転するパルスめっきを行うようにしてもよい。例えば、正電流(めっき電流)を10ms、負電流を1msとするパルスめっき(PPR電解めっき)を行うことにより、ビアホール14以外の部分に付着しているめっき促進剤の剥離作用がなされ、ビアホール14内を銅めっきで埋めることができた。

【0024】

あるいはまた、前記めっき促進剤の剥離工程を省き、電解銅めっきの工程で、めっき促進剤を含まない銅めっき液を用いることだけでもビアホール14内を銅めっきで埋めることができる。

この場合にも既に浸漬処理の段階でビアホール14内にめっき促進剤を付着させてあるので、ビアホール14内に電流を集中できるからである。

【0025】

また、無電解銅めっき工程と浸漬工程との間に、無電解銅めっき皮膜21上に電解によるストライク銅めっき皮膜を形成するめっき工程を行うとさらに好適である。

これにより無電解銅めっき皮膜21上に純粋な銅の皮膜が形成された状態となるので、無電解銅めっき皮膜21の表面の酸化等によるめっき促進剤の未着を防止することができ、この清浄な銅表面にめっき促進剤がムラなく均一に付着するので、確実にビアホール14内を銅めっきで埋めることができるようになる。

【0026】

【実施例】

〔実施例1〕

導体層が底面に露出するように絶縁層にビアホールが形成された基板表面に無電解銅めっきを施し、この基板を、3−メルカプト−1−プロパンスルホン酸ナトリウム(めっき促進剤)の1%水溶液に、15分間揺動させながら浸漬し、無電解銅めっき皮膜の表面にめっき促進剤を付着させた。

水洗後、シアン電解浴(NaCN 20g/l、NaOH 140g/l)で、基板側を陰極にして、常温、1.4V、30秒間電解して、ビアホール内以外の無電解銅めっき皮膜表面のめっき促進剤を剥離した。

水洗後、上記電解銅めっき浴を用いて、常温、1A/dm2の電流密度、100分間のめっき条件で電解銅めっきを施した結果を図7および図8に示す。

図7は開口部の直径46μm、深さ53μm、アスペクト比1.15のビアホールであるが、銅めっきでビアホール−内が完全に埋められている。図8は開口部の直径28μm、深さ53μm、アスペクト比1.89のビアホールであるが、銅めっきでビアホール内が完全に埋められている。

なお、3−メルカプト−1−プロパンスルホン酸ナトリウムの代わりに、2−メルカプトエタンスルホン酸ナトリウムあるいはビス−(3−スルフォプロピル)−ジスルファイドジソディウムを用いた場合にも同様の結果が得られた。また、これら促進剤の1種以上を混合して用いた場合も同様の結果が得られた。

【0027】

〔実施例2〕

導体層が底面に露出するように絶縁層にビアホールが形成された基板表面に無電解銅めっきを施し、この基板を、3−メルカプト−1−プロパンスルホン酸ナトリウム 1.5g/lのめっき促進剤溶液に3分浸漬して、無電解銅めっき皮膜上にめっき促進剤を付着させた。

水洗後、上記電解銅めっきを用いて、常温、1A/dm2の電流密度、100分間のめっき条件で電解銅めっきを施した。その際、めっき開始後2分から9分の間、30秒毎に陽極と陰極の極性を反転させる処理を行った。その結果を図9、図10に示す。

図9は開口部の直径が40μmのビアホールのもの、図10は開口部の直径が60μmのビアホールのものであるが、いずれもビアホール内が十分に銅めっきで埋められている。

なお、3−メルカプト−1−プロパンスルホン酸ナトリウムの代わりに、2−メルカプトエタンスルホン酸ナトリウムあるいはビス−(3−スルフォプロピル)−ジスルファイドジソディウムを用いた場合にも同様の結果が得られた。また、これら促進剤の1種以上を混合して用いた場合も同様の結果が得られた。

【0028】

〔実施例3〕

導体層が底面に露出するように絶縁層にビアホールが形成された基板表面に無電解銅めっきを施し、この基板を、3−メルカプト−1−プロパンスルホン酸ナトリウムの1%水溶液に、10分間揺動させながら浸漬し、無電解銅めっき皮膜の表面にめっき促進剤を付着させた。

水洗後、実施例1の電解銅めっき液を用いて、下記の条件でPPR電解銅めっきを行った。

正電流時間 10ms

負電流時間 0.5ms

正電流密度 1A/dm2

負電流密度 3A/dm2

めっき時間100分

上記電解銅めっきの結果を図11に示す。開口部の直径が100μm、深さ30μmのビアホール内を十分に銅めっきで埋めることができた。

なお、3−メルカプト−1−プロパンスルホン酸ナトリウムの代わりに、2−メルカプトエタンスルホン酸ナトリウムあるいはビス−(3−スルフォプロピル)−ジスルファイドジソディウムを用いた場合にも同様の結果が得られた。また、これら促進剤の1種以上を混合して用いた場合も同様の結果が得られた。

【0029】

以上本発明につき好適な実施例を挙げて種々説明したが、本発明はこの実施例に限定されるものではなく、発明の精神を逸脱しない範囲内で多くの改変を施し得るのはもちろんである。

【0030】

【発明の効果】

以上のように本発明によれば、アスペクト比の大きなビアホールであっても十分にビアフィリングを行えるという著効を奏する。

【図面の簡単な説明】

【図1】銅皮膜を形成した状態の説明図、

【図2】めっき促進剤溶液に浸漬した状態の説明図、

【図3】めっき促進剤を部分剥離した状態の説明図、

【図4】ビアフィリングをした状態の説明図、

【図5】上層の配線パターンを形成した説明図、

【図6】ビアホールに電流が集中した状態を示す説明図、

【図7】実施例1のビアフィリング状態を示す説明図、

【図8】実施例1のビアフィリング状態を示す説明図、

【図9】実施例2のビアフィリング状態を示す説明図、

【図10】実施例2のビアフィリング状態を示す説明図、

【図11】実施例3のビアフィリング状態を示す説明図、

【図12】めっき促進剤の特性を示すグラフである。

【図13】ビルドアップ法の工程を示し、絶縁層を形成した説明図、

【図14】ビアホールを形成した説明図、

【図15】銅めっき皮膜を形成した説明図、

【図16】配線パターンを形成した説明図、

【図17】ビアホールが袋穴状になった状態の説明図である。

【符号の説明】

10 配線パターン

12 絶縁層

14 ビアホール

20 基板

21 無電解銅めっき皮膜

22 めっき促進剤(層)

23 銅めっき皮膜

24 配線パターン

Claims (10)

- 導体層が底面に露出するように基板の絶縁層に形成されたビアホール内に、銅めっきを施してビアホール内をめっき金属により充填するビアフィリングめっき方法において、

前記基板の絶縁層表面およびビアホールの底面を含む壁面に銅皮膜を形成する銅皮膜形成工程と、

めっき促進剤が添加された水溶液中に、前記銅皮膜が形成された基板を浸漬して、前記銅皮膜表面にめっき促進剤を付着させる浸漬工程と、

ビアホールの底面を含む内壁面を除く前記銅皮膜表面に付着しためっき促進剤を除去する剥離工程と、

前記剥離工程の後、絶縁層表面に形成された銅皮膜およびビアホールの底面を含む壁面に形成された銅皮膜上に電解銅めっきを施して前記ビアホール内にめっき金属を充填する電解銅めっき工程とを含むことを特徴とするビアフィリングめっき方法。 - 〔化1〕のめっき促進剤が、3−メルカプト−1−プロパンスルホン酸ナトリウムもしくは2−メルカプトエタンスルホン酸ナトリウムであることを特徴とする請求項2記載のビアフィリングめっき方法。

- 〔化2〕のめっき促進剤が、ビス−(3−スルフォプロピル)−ジスルファイドジソディウムであることを特徴とする請求項2記載のビアフィリングめっき方法。

- 前記剥離工程は、銅のエッチング液を用いるエッチング処理、シアン電解浴を用いるシアン電解処理、前記銅皮膜表面に紫外線を斜めに照射する紫外線処理、または前記銅皮膜表面を研磨する研磨処理を施す工程であることを特徴とする請求項1、2、3または4記載のビアフィリングめっき方法。

- 前記剥離工程を省き、前記浸漬工程の後、前記電解銅めっき工程の初期の段階において、逆電解処理を施すことを特徴とする請求項1、2、3または4記載のビアフィリングめっき方法。

- 前記剥離工程を省き、前記浸漬工程の後、前記電解銅めっき工程で正負の反転するパルスめっきを施すことを特徴とする請求項1、2、3または4記載のビアフィリングめっき方法。

- 前記電解銅めっき工程において、めっき促進剤を含まない電解銅めっき液を用いることを特徴とする請求項1、2、3、4、5、6または7記載のビアフィリングめっき方法。

- 前記めっき促進剤に3−メルカプト−1−プロパンスルホン酸ナトリウムもしくは2−メルカプトエタンスルホン酸ナトリウムを用いて前記浸漬工程を行い、

前記剥離工程を省き、

前記電解銅めっき工程において、めっき促進剤を含まない電解銅めっき液を用いることを特徴とする請求項1記載のビアフィリングめっき方法。 - 前記浸漬工程の前に、前記銅皮膜表面に銅ストライクめっきを施すことを特徴とする1、2、3、4、5、6、7、8または9記載のビアフィリングめっき方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000334044A JP3594894B2 (ja) | 2000-02-01 | 2000-11-01 | ビアフィリングめっき方法 |

| US09/772,457 US6755957B2 (en) | 2000-02-01 | 2001-01-30 | Method of plating for filling via holes |

| EP01300837A EP1122989B1 (en) | 2000-02-01 | 2001-01-31 | Method of plating for filling via holes |

| TW90101961A TW574438B (en) | 2000-02-01 | 2001-01-31 | Method of plating for filling via holes |

| KR20010004601A KR100730326B1 (ko) | 2000-02-01 | 2001-01-31 | 비어 홀을 충전하는 도금 방법 |

| DE60126853T DE60126853T2 (de) | 2000-02-01 | 2001-01-31 | Plattierungsverfahren zum Füllen von Kontaktlöchern |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000023794 | 2000-02-01 | ||

| JP2000-23794 | 2000-02-01 | ||

| JP2000334044A JP3594894B2 (ja) | 2000-02-01 | 2000-11-01 | ビアフィリングめっき方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001291954A JP2001291954A (ja) | 2001-10-19 |

| JP3594894B2 true JP3594894B2 (ja) | 2004-12-02 |

Family

ID=26584623

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000334044A Expired - Fee Related JP3594894B2 (ja) | 2000-02-01 | 2000-11-01 | ビアフィリングめっき方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6755957B2 (ja) |

| EP (1) | EP1122989B1 (ja) |

| JP (1) | JP3594894B2 (ja) |

| KR (1) | KR100730326B1 (ja) |

| DE (1) | DE60126853T2 (ja) |

| TW (1) | TW574438B (ja) |

Families Citing this family (53)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7449098B1 (en) | 1999-10-05 | 2008-11-11 | Novellus Systems, Inc. | Method for planar electroplating |

| US7531079B1 (en) | 1998-10-26 | 2009-05-12 | Novellus Systems, Inc. | Method and apparatus for uniform electropolishing of damascene IC structures by selective agitation |

| US6534116B2 (en) | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US6491806B1 (en) | 2000-04-27 | 2002-12-10 | Intel Corporation | Electroplating bath composition |

| WO2002015245A2 (en) * | 2000-08-10 | 2002-02-21 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| US6921551B2 (en) * | 2000-08-10 | 2005-07-26 | Asm Nutool, Inc. | Plating method and apparatus for controlling deposition on predetermined portions of a workpiece |

| US6858121B2 (en) * | 2000-08-10 | 2005-02-22 | Nutool, Inc. | Method and apparatus for filling low aspect ratio cavities with conductive material at high rate |

| US6863795B2 (en) * | 2001-03-23 | 2005-03-08 | Interuniversitair Microelektronica Centrum (Imec) | Multi-step method for metal deposition |

| JP4000796B2 (ja) * | 2001-08-08 | 2007-10-31 | 株式会社豊田自動織機 | ビアホールの銅メッキ方法 |

| CN1283848C (zh) * | 2001-10-16 | 2006-11-08 | 新光电气工业株式会社 | 小直径孔镀铜的方法 |

| JP2003168860A (ja) * | 2001-11-30 | 2003-06-13 | Cmk Corp | プリント配線板及びその製造方法 |

| JP3976564B2 (ja) * | 2001-12-20 | 2007-09-19 | 日本リーロナール有限会社 | ビアフィリング方法 |

| JP3964263B2 (ja) * | 2002-05-17 | 2007-08-22 | 株式会社デンソー | ブラインドビアホール充填方法及び貫通電極形成方法 |

| US7405163B1 (en) * | 2003-12-17 | 2008-07-29 | Novellus Systems, Inc. | Selectively accelerated plating of metal features |

| US7449099B1 (en) * | 2004-04-13 | 2008-11-11 | Novellus Systems, Inc. | Selectively accelerated plating of metal features |

| US7799200B1 (en) | 2002-07-29 | 2010-09-21 | Novellus Systems, Inc. | Selective electrochemical accelerator removal |

| JP2004342750A (ja) | 2003-05-14 | 2004-12-02 | Toshiba Corp | 電子デバイスの製造方法 |

| US8530359B2 (en) | 2003-10-20 | 2013-09-10 | Novellus Systems, Inc. | Modulated metal removal using localized wet etching |

| US8158532B2 (en) | 2003-10-20 | 2012-04-17 | Novellus Systems, Inc. | Topography reduction and control by selective accelerator removal |

| DE102004005300A1 (de) * | 2004-01-29 | 2005-09-08 | Atotech Deutschland Gmbh | Verfahren zum Behandeln von Trägermaterial zur Herstellung von Schltungsträgern und Anwendung des Verfahrens |

| US20050224358A1 (en) * | 2004-03-30 | 2005-10-13 | Lsi Logic Corporation | Method for improved local planarity control during electropolishing |

| JP4150930B2 (ja) * | 2004-10-21 | 2008-09-17 | 日立電線株式会社 | 半導体装置用両面配線テープキャリアの製造方法 |

| CN101189921A (zh) * | 2005-06-01 | 2008-05-28 | 松下电器产业株式会社 | 电路基板和其制造方法以及使用该电路基板的电子部件 |

| US7550070B2 (en) | 2006-02-03 | 2009-06-23 | Novellus Systems, Inc. | Electrode and pad assembly for processing conductive layers |

| JP4759416B2 (ja) * | 2006-03-20 | 2011-08-31 | 新光電気工業株式会社 | 非シアン無電解金めっき液及び無電解金めっき方法 |

| US7405154B2 (en) * | 2006-03-24 | 2008-07-29 | International Business Machines Corporation | Structure and method of forming electrodeposited contacts |

| US7575666B2 (en) * | 2006-04-05 | 2009-08-18 | James Watkowski | Process for electrolytically plating copper |

| JP4862508B2 (ja) * | 2006-06-12 | 2012-01-25 | 日立電線株式会社 | 導体パターン形成方法 |

| US8500985B2 (en) | 2006-07-21 | 2013-08-06 | Novellus Systems, Inc. | Photoresist-free metal deposition |

| US7732329B2 (en) | 2006-08-30 | 2010-06-08 | Ipgrip, Llc | Method and apparatus for workpiece surface modification for selective material deposition |

| US20080148561A1 (en) * | 2006-12-22 | 2008-06-26 | Motorola, Inc. | Methods for making printed wiring boards |

| KR100832705B1 (ko) * | 2006-12-23 | 2008-05-28 | 동부일렉트로닉스 주식회사 | 시스템 인 패키지의 비아 도금방법 및 그 시스템 |

| KR200454218Y1 (ko) * | 2008-10-08 | 2011-06-23 | 주식회사강산 | 핸드레일 |

| AT506583B9 (de) | 2008-10-23 | 2009-12-15 | Happy Plating Gmbh | Elektrochemisches beschichtungsverfahren |

| US8168540B1 (en) | 2009-12-29 | 2012-05-01 | Novellus Systems, Inc. | Methods and apparatus for depositing copper on tungsten |

| KR101705734B1 (ko) | 2011-02-18 | 2017-02-14 | 삼성전자주식회사 | 구리 도금 용액 및 이것을 이용한 구리 도금 방법 |

| EP2551375A1 (en) * | 2011-07-26 | 2013-01-30 | Atotech Deutschland GmbH | Electroless nickel plating bath composition |

| US20140262801A1 (en) * | 2013-03-14 | 2014-09-18 | Rohm And Haas Electronic Materials Llc | Method of filling through-holes |

| US9598787B2 (en) * | 2013-03-14 | 2017-03-21 | Rohm And Haas Electronic Materials Llc | Method of filling through-holes |

| JP6327463B2 (ja) * | 2013-10-09 | 2018-05-23 | 日立化成株式会社 | 多層配線基板の製造方法 |

| JP6350064B2 (ja) * | 2013-10-09 | 2018-07-04 | 日立化成株式会社 | 多層配線基板の製造方法 |

| JP6350063B2 (ja) * | 2013-10-09 | 2018-07-04 | 日立化成株式会社 | 多層配線基板 |

| US10154598B2 (en) * | 2014-10-13 | 2018-12-11 | Rohm And Haas Electronic Materials Llc | Filling through-holes |

| JP6625872B2 (ja) | 2015-11-25 | 2019-12-25 | 新光電気工業株式会社 | 配線基板及び配線基板の製造方法 |

| US10508357B2 (en) | 2016-02-15 | 2019-12-17 | Rohm And Haas Electronic Materials Llc | Method of filling through-holes to reduce voids and other defects |

| US10512174B2 (en) * | 2016-02-15 | 2019-12-17 | Rohm And Haas Electronic Materials Llc | Method of filling through-holes to reduce voids and other defects |

| JP2017162895A (ja) * | 2016-03-08 | 2017-09-14 | 株式会社ジェイデバイス | 配線構造、プリント基板、半導体装置及び配線構造の製造方法 |

| EP3826439B1 (en) * | 2019-11-19 | 2026-01-07 | AT & S Austria Technologie & Systemtechnik Aktiengesellschaft | Method of manufacturing a laminated component carrier with blind hole having wedges filled with filling medium by sputtering and back-sputtering |

| KR102254649B1 (ko) | 2020-04-14 | 2021-05-24 | 주식회사 디에이피 | 인쇄회로기판의 전기 동도금 방법 |

| CN113747664B (zh) * | 2020-05-29 | 2024-01-05 | 深南电路股份有限公司 | 一种印制线路板及其制作方法 |

| CN113795086B (zh) * | 2021-10-19 | 2023-04-14 | 重庆新固兴科技有限公司 | 双面假贴机 |

| CN115003032B (zh) * | 2022-06-21 | 2023-03-07 | 东莞市国盈电子有限公司 | 一种马达驱动控制线路板及其制造工艺 |

| CN117265530A (zh) * | 2023-09-06 | 2023-12-22 | 九江德福科技股份有限公司 | 一种消除复合铜箔透光点的方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE1075398B (de) * | 1954-03-22 | 1960-02-11 | DEHYDAG Deutsche Hydrierwerke G.m.b.H., Düsseldorf | Bad zur galvanischen Herstellung von Metallüberzügen |

| JPH01143797A (ja) * | 1987-11-30 | 1989-06-06 | Mitsumi Electric Co Ltd | プレス装置 |

| US5174886A (en) | 1991-02-22 | 1992-12-29 | Mcgean-Rohco, Inc. | High-throw acid copper plating using inert electrolyte |

| US5252196A (en) | 1991-12-05 | 1993-10-12 | Shipley Company Inc. | Copper electroplating solutions and processes |

| JPH1143797A (ja) * | 1997-07-25 | 1999-02-16 | Hideo Honma | ビアフィリング方法 |

| JPH11298141A (ja) * | 1998-04-08 | 1999-10-29 | Hitachi Ltd | 電子装置の製造方法 |

| KR100336829B1 (ko) | 1998-04-10 | 2002-05-16 | 모기 쥰이찌 | 다층 배선 기판의 제조 방법 |

| WO1999057342A1 (en) | 1998-04-30 | 1999-11-11 | Ebara Corporation | Method and device for plating substrate |

| US6534116B2 (en) * | 2000-08-10 | 2003-03-18 | Nutool, Inc. | Plating method and apparatus that creates a differential between additive disposed on a top surface and a cavity surface of a workpiece using an external influence |

| JP3124523B2 (ja) | 1999-01-28 | 2001-01-15 | 日本エレクトロプレイテイング・エンジニヤース株式会社 | 銅メッキ方法 |

| US6224737B1 (en) * | 1999-08-19 | 2001-05-01 | Taiwan Semiconductor Manufacturing Company | Method for improvement of gap filling capability of electrochemical deposition of copper |

-

2000

- 2000-11-01 JP JP2000334044A patent/JP3594894B2/ja not_active Expired - Fee Related

-

2001

- 2001-01-30 US US09/772,457 patent/US6755957B2/en not_active Expired - Lifetime

- 2001-01-31 KR KR20010004601A patent/KR100730326B1/ko not_active Expired - Lifetime

- 2001-01-31 DE DE60126853T patent/DE60126853T2/de not_active Expired - Lifetime

- 2001-01-31 TW TW90101961A patent/TW574438B/zh not_active IP Right Cessation

- 2001-01-31 EP EP01300837A patent/EP1122989B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| KR20010078217A (ko) | 2001-08-20 |

| JP2001291954A (ja) | 2001-10-19 |

| DE60126853D1 (de) | 2007-04-12 |

| EP1122989B1 (en) | 2007-02-28 |

| KR100730326B1 (ko) | 2007-06-19 |

| EP1122989A2 (en) | 2001-08-08 |

| US6755957B2 (en) | 2004-06-29 |

| EP1122989A3 (en) | 2002-07-03 |

| TW574438B (en) | 2004-02-01 |

| US20010013472A1 (en) | 2001-08-16 |

| DE60126853T2 (de) | 2007-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3594894B2 (ja) | ビアフィリングめっき方法 | |

| JP4248353B2 (ja) | スルーホールの充填方法 | |

| JP5828333B2 (ja) | ビルドアップ積層基板の製造方法 | |

| JP5078142B2 (ja) | スルーホールに金属を充填するための電気処理、とりわけプリント基板のスルーホールに銅を充填するための電気処理 | |

| JP4195706B2 (ja) | プリント配線板およびその製造方法 | |

| JPH04100294A (ja) | プリント配線板の製造方法 | |

| US11729917B2 (en) | Method for optimized filling hole and manufacturing fine line on printed circuit board | |

| US7063800B2 (en) | Methods of cleaning copper surfaces in the manufacture of printed circuit boards | |

| CN116076159A (zh) | 印刷电路板的制造方法 | |

| JP4000225B2 (ja) | 多層プリント配線板の製造方法 | |

| JPH0362036B2 (ja) | ||

| GB2080630A (en) | Printed circuit panels | |

| US4968398A (en) | Process for the electrolytic removal of polyimide resins | |

| JP2858564B2 (ja) | 印刷配線板の製造方法 | |

| JP2006328476A (ja) | めっき方法 | |

| JPH08148810A (ja) | プリント配線板の製造法 | |

| JP2002368380A (ja) | 両面可撓性回路基板の製造法 | |

| JPS62230996A (ja) | アルミニウム基板にめつきをする方法 | |

| JP2002076617A (ja) | プリント配線板の製造方法及びプリント配線板 | |

| JP2008088521A (ja) | 深さの異なるビアへのめっき充填方法 | |

| JP2004128053A (ja) | 多層プリント配線板の製造方法 | |

| JP3191686B2 (ja) | 印刷配線板の製造方法 | |

| JP2006339483A (ja) | 配線基板の製造方法及び配線基板 | |

| JPH06334337A (ja) | プリント回路板の製造方法 | |

| JPH05175652A (ja) | プリント配線板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040824 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040901 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3594894 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080910 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080910 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090910 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090910 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100910 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110910 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110910 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120910 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120910 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |