CN100468770C - 具有保护层和低损凹槽的氮化物基晶体管及其制造方法 - Google Patents

具有保护层和低损凹槽的氮化物基晶体管及其制造方法 Download PDFInfo

- Publication number

- CN100468770C CN100468770C CNB2004800405318A CN200480040531A CN100468770C CN 100468770 C CN100468770 C CN 100468770C CN B2004800405318 A CNB2004800405318 A CN B2004800405318A CN 200480040531 A CN200480040531 A CN 200480040531A CN 100468770 C CN100468770 C CN 100468770C

- Authority

- CN

- China

- Prior art keywords

- layer

- protective layer

- nitride

- barrier layer

- ohmic contact

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000011241 protective layer Substances 0.000 title claims abstract description 148

- 150000004767 nitrides Chemical class 0.000 title claims abstract description 70

- 238000000034 method Methods 0.000 title claims description 42

- 238000004519 manufacturing process Methods 0.000 title description 15

- 239000010410 layer Substances 0.000 claims abstract description 285

- 230000004888 barrier function Effects 0.000 claims abstract description 119

- 239000004065 semiconductor Substances 0.000 claims abstract description 29

- 229910052751 metal Inorganic materials 0.000 claims abstract description 26

- 239000002184 metal Substances 0.000 claims abstract description 26

- 238000000137 annealing Methods 0.000 claims abstract description 17

- 238000002161 passivation Methods 0.000 claims description 47

- 238000005530 etching Methods 0.000 claims description 36

- 239000000463 material Substances 0.000 claims description 29

- 239000000758 substrate Substances 0.000 claims description 26

- 238000005516 engineering process Methods 0.000 claims description 24

- 230000015572 biosynthetic process Effects 0.000 claims description 17

- 239000011248 coating agent Substances 0.000 claims description 13

- 238000000576 coating method Methods 0.000 claims description 13

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 8

- 239000000203 mixture Substances 0.000 claims description 7

- 239000000377 silicon dioxide Substances 0.000 claims description 4

- 235000012239 silicon dioxide Nutrition 0.000 claims description 4

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 claims description 3

- 238000001039 wet etching Methods 0.000 claims description 3

- 238000011065 in-situ storage Methods 0.000 claims description 2

- 229910002704 AlGaN Inorganic materials 0.000 claims 4

- 238000011049 filling Methods 0.000 claims 1

- 229910002601 GaN Inorganic materials 0.000 description 31

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 27

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 23

- 229910017083 AlN Inorganic materials 0.000 description 19

- 229910010271 silicon carbide Inorganic materials 0.000 description 14

- 229910004298 SiO 2 Inorganic materials 0.000 description 10

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 8

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 6

- 230000007704 transition Effects 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- AJGDITRVXRPLBY-UHFFFAOYSA-N aluminum indium Chemical compound [Al].[In] AJGDITRVXRPLBY-UHFFFAOYSA-N 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 229920002120 photoresistant polymer Polymers 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 229910052594 sapphire Inorganic materials 0.000 description 4

- 239000010980 sapphire Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- PNEYBMLMFCGWSK-UHFFFAOYSA-N Alumina Chemical compound [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- -1 InGaN (InGaN) Chemical compound 0.000 description 3

- 229910004541 SiN Inorganic materials 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 239000004411 aluminium Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 239000011435 rock Substances 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910005883 NiSi Inorganic materials 0.000 description 1

- 229910004205 SiNX Inorganic materials 0.000 description 1

- 229910008807 WSiN Inorganic materials 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910021431 alpha silicon carbide Inorganic materials 0.000 description 1

- 230000003139 buffering effect Effects 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000007850 degeneration Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000017525 heat dissipation Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000002248 hydride vapour-phase epitaxy Methods 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000006911 nucleation Effects 0.000 description 1

- 238000010899 nucleation Methods 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- HYXGAEYDKFCVMU-UHFFFAOYSA-N scandium oxide Chemical compound O=[Sc]O[Sc]=O HYXGAEYDKFCVMU-UHFFFAOYSA-N 0.000 description 1

- 238000004062 sedimentation Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 230000005533 two-dimensional electron gas Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66446—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET]

- H01L29/66462—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET] with a heterojunction interface channel or gate, e.g. HFET, HIGFET, SISFET, HJFET, HEMT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7782—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with confinement of carriers by at least two heterojunctions, e.g. DHHEMT, quantum well HEMT, DHMODFET

- H01L29/7783—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with confinement of carriers by at least two heterojunctions, e.g. DHHEMT, quantum well HEMT, DHMODFET using III-V semiconductor material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Junction Field-Effect Transistors (AREA)

- Electrodes Of Semiconductors (AREA)

- Weting (AREA)

Abstract

一种晶体管制造方法,包括在氮化物基半导体沟道层上形成氮化物基半导体势垒层以及在该氮化物基半导体势垒层的栅极区上形成保护层。在该势垒层上形成图形化欧姆接触金属区,并退火该图形化欧姆接触金属区以提供第一及第二欧姆接触。在保护层位于该栅极区上的情形下进行该退火。也在该势垒层的栅极区上形成栅极接触。还提供了在栅极区内具有保护层的晶体管,该晶体管具有势垒层且该晶体管的薄层电阻基本上和该势垒层的原生薄层电阻相同。

Description

政府利益声明

本发明是在政府支持下进行的。政府对本发明具有特定权利。

技术领域

本发明涉及半导体器件,更为特别地涉及包含氮化物基有源层的晶体管。

背景技术

诸如硅(Si)和砷化镓(GaAs)的材料已经在用于低功率和(在Si的情况下)低频应用的半导体器件中得到广泛应用。然而,由于带隙相对较小(例如室温下Si为1.12eV,GaAs为1.42eV)与/或击穿电压相对较低,这些人们更为熟悉的半导体材料不是很适合用于大功率与/或高频应用。

考虑到Si和GaAs所面临的困难,大功率、高温、与/或高频应用和器件的兴趣已经转到诸如碳化硅(室温下α-SiC的带隙为2.996eV)和III族氮化物(例如室温下GaN的带隙为3.36eV)的宽带隙半导体材料.和砷化镓及硅相比,这些材料通常具有更高的电场击穿强度和更高的电子饱和速度。

大功率与/或高频应用中特别感兴趣的一种器件为高电子迁移率晶体管(HEMT),也称为调制掺杂场效应晶体管(MODFET)。这些器件在许多环境下可具有操作优点,因为在具有不同带隙能量的两种半导体材料的异质结处形成二维电子气(2DEG),且其中带隙能量小的材料具有更高的......

......掺杂的”),带隙较小材料并且可包含非常高的面电子浓度,例如超过1013载流子/cm2。另外,源于带隙更宽的半导体的电子转移到该2DEG,使得能够由于离化杂质散射减小而实现高的电子迁移率。

高载流子浓度和高载流子迁移率的这种组合使HEMT具有非常大的跨导,且其性能在高频应用中与金属半导体场效应晶体管(MESFET)相比具有强大的优势。

由于包含前述高击穿电场、宽带隙、大的导带偏移、与/或高的饱和电子漂移速度的材料特性的组合,氮化镓/铝镓氮化物(GaN/AlGaN)材料体系中制造的高电子迁移率晶体管具有产生大RF功率量的潜力。2DEG中大部分电子是由于AlGaN的极化所致。GaN/AlGaN体系中的HEMT已经得到证明。美国专利5192987和5296395描述了GaN/AlGaN HEMT的结构及其制造方法。被共同转让并在此被引用作为参考的Sheppard等的美国专利6316793描述了一种HEMT器件,该器件包含半绝缘碳化硅衬底、位于该衬底上的氮化铝缓冲层、位于该缓冲层上的绝缘氮化镓层、位于该氮化镓层上的铝镓氮化物势垒层(barrier layer)、以及位于该铝镓氮化物有源结构上的钝化层。

氮化物基晶体管的一个制造步骤为形成该晶体管的欧姆接触。形成欧姆接触通常需要高的退火温度(例如900℃).这种高的退火温度可能损伤材料与/或器件。

例如,在形成欧姆接触时使用高的退火温度的传统器件中,和原生的AlGaN与/或GaN层的薄层电阻相比,AlGaN与/或GaN层栅极区(定义为两个接触之间的有源器件区)的薄层电阻通常增大.薄层电阻的这种增大被认为会对器件产生不利影响。

本发明的实施例提供了晶体管制造方法,包括在氮化物基半导体沟道层上形成氮化物基半导体势垒层以及在该氮化物基半导体势垒层的栅极区上形成保护层。在该势垒层上形成图形化的欧姆接触金属区,并对其进行退火以提供第一及第二欧姆接触.在保护层位于该栅极区上的情形下进行该退火。还在该势垒层的栅极区(例如第一和第二欧姆接触之间的有源器件区)上形成栅极接触.

在本发明另外的实施中,在退火该图形化欧姆接触金属之后除去该保护层。该保护层可以是氮化铝层.可以使用低损伤蚀刻技术除去该保护层。例如,该低损伤蚀刻技术包含使用强碱(例如KOH)的湿法去除。除去该保护层之后,可以在势垒层的暴露部分上形成钝化层。在这些实施例中,形成栅极接触包含:使用低损伤蚀刻技术在该钝化层内蚀刻凹槽从而暴露该势垒层的栅极区的一部分;以及在该钝化层的凹槽内形成栅极接触。

在本发明的附加实施例中,该钝化层形成于该势垒层和该保护层的暴露部分上。在这些实施例中,可以通过形成延伸穿过该钝化层和该保护层从而接触该势垒层的栅极接触,提供栅极接触.

在本发明又一些实施例中,形成保护层包括在该势垒层上形成图形化的保护层。该图形化的保护层覆盖与栅极区相对应的势垒层的第一部分,并暴露与第一及第二欧姆接触相对应的势垒层的相邻第二部分.通过在该势垒层的第二部分上形成图形化的欧姆接触金属区,提供图形化的欧姆接触金属区。所述图形化的欧姆接触金属区与该图形化的保护层相邻并分隔开。

在本发明另外的实施例中,形成图形化的保护层包括:毯状沉积保护层材料在阻挡......

......材料,该掩模具有与第一及第二欧姆接触的位置相对应的窗口;利用低损伤蚀刻技术通过该窗口蚀刻该毯状沉积的保护层;以及除去该掩模。与第一及第二欧姆接触的位置相对应的窗口可以大于第一及第二欧姆接触的面积。该低损伤蚀刻技术可以是下述技术中的一种或多种:RIE、ECR、下游等离子体、与/或使用CF4/O2、NF3/O2或其它氟化物类型的ICP。

形成该栅极接触包括:在该图形化保护层内形成暴露该势垒层第一部分的一部分的凹槽;以及在该凹槽内沉积栅极接触。形成凹槽包括:在该图形化保护层上形成掩模,该掩模具有和该凹槽的位置相对应的窗口;使用低损伤蚀刻技术通过该窗口蚀刻该图形化保护层;以及除去该掩模。用于蚀刻该图形化保护层的低损伤蚀刻技术可包括:RIE、ECR、下游等离子体、与/或使用CF4/O2、NF3/O2或其它氟化物类型的ICP。

在本发明特定实施例中,该保护层包含SiN、AlN、与/或SiO2.该SiN、AlN、与/或SiO2可以是非化学配比的,并可具有压应变或张应变.可采用物理气相沉积(PVD)与/或化学气相沉积(CVD)沉积该保护层。

在本发明另外附加实施例中,在该图形化保护层上形成钝化层,该钝化层基本上填充该图形化保护层与该第一及第二欧姆接触之间的间隙。该图形化保护层和该钝化层可以是相同或不同的材料。例如,该图形化保护层可以是氮化铝,该钝化层可以是氟化硅。或者,该图形化保护层和该钝化层为氮化硅。

在本发明另外其它实施例中,除去该图形化保护层从而暴露该势垒层的第一部分。在除去该图形化保护层之后,可以在该势垒层的暴露部分上形成钝化层。在这些实施例中,该图形化保护层可以是氮化铝,该钝化层可以是氮化硅。

在形成钝化层之后进行......。形成栅极接触包含:在该钝化层内形成暴露该势垒层第一部分的一部分的凹槽;以及在该凹槽内形成栅极接触。形成凹槽可包括在该钝化层上形成掩模。该掩模具有和该凹槽的位置相对应的窗口。使用低损伤蚀刻技术通过该窗口蚀刻该钝化层,随后除去该掩模。

在本发明特定实施例中,氮化物基沟道层和氮化物基半导体势垒层为III族氮化物层。例如,该沟道层的成分为AlxGa1-xN,其中0≤x<1,其中该沟道层的带隙小于该势垒层的带隙.该沟道层还可以是铝镓氮化物(AlGaN)、氮化镓(GaN)、铟镓氮化物(InGaN)、与/或铝铟镓氮化物(AlInGaN),该势垒层可以是氮化铝(AlN)、铝铟氮化物(AlInN)、AlGaN、GaN、InGaN、与/或AlInGaN.该势垒层与/或沟道层可以为多层。还可在衬底上形成缓冲层,在该缓冲层上形成沟道层以提供氮化物基沟道层。该沟道层和该势垒层配置成提供高电子迁移率晶体管(HEMT)。该氮化物基沟道层可以提供于SiC衬底上。

在本发明另外的实施例中,在形成栅极接触之前形成钝化层.栅极接触的形成包括:在该钝化层和该图形化保护层内形成暴露该势垒层第一部分的一部分的凹槽;以及在该凹槽内形成栅极接触.

在本发明特定实施例中,保护层的厚度形成为至少是大约欧姆接触材料的厚度。该保护层的厚度还可以为至少约两个单原子层(monolayer)的厚度。特别地,该保护层厚度为约1nm至约500nm.

在本发明另外其它实施例中,高电子迁移率晶体管包含衬底上的氮化物基沟道层以及该氮化物基沟道层上的氮化物基半导体势垒层。......的沟道......

......与氮化物基HEMT沟道的原生薄层电阻基本相同.......在势垒层上提供欧姆接触和栅极接触。

该高电子迁移率晶体管进一步包含置于势垒层上的保护层,该势垒层与欧姆接触相邻且分隔开,且栅极接触延伸穿过该势垒层。还可在该保护层上提供钝化层,且该钝化层基本上填充欧姆接触与该保护层之间的间隙。该钝化层还可位于该保护层上,且该栅极接触可延伸穿过该保护层和该钝化层。也可直接在该保护层上提供栅极接触。位于该势垒层上的钝化层可以基本上填充欧姆接触与栅极接触之间的间隙。

在本发明特定实施例中,氮化物基沟道层和氮化物基半导体势垒层分别包含III族氮化物层。该沟道层的带隙可小于该势垒层。该沟道层可包含厚度大于约的未掺杂层。该沟道层还可包含III族氮化物层的超晶格与/或组合。该沟道层可包含铝镓氮化物(AlGaN)、氮化镓(GaN)、铟镓氮化物(InGaN)、与/或铝铟镓氮化物(AlInGaN)。该势垒层可包含氮化铝(AlN)、铝铟氮化物(AlInN)、AlGaN、GaN、InGaN、与/或AlInGaN。例如,该势垒层可包含AlxGa1-xN,其中0<x<1.该势垒层可包含多个层。还可以在衬底上提供缓冲层,其中该氮化物基沟道层置于该缓冲层上。

在本发明另外的实施例中,保护层的厚度至少约为欧姆接触的厚度。该欧姆接触还具有小于约1Ω-mm的接触电阻.

在本发明另外的实施例中,高电子迁移率晶体管包含:衬底上的氮化物基沟道层、该氮化物基沟道层上的氮化物基半导体势垒层、该势垒层上的保护层、该势垒层上的欧姆接触(与保护层相邻并分隔开从而在所述欧姆接触与保护层之间提供间隙)、以及位于该势垒层上的栅极接触并延伸穿过......

......基本上填充该欧姆接触与该保护层之间的间隙。

在本发明的又一些实施例中,晶体管的制造包括:在氮化物基半导体沟道层上形成氮化物基半导体势垒层;以及在该氮化物基半导体势垒层的栅极区上形成保护层。在该势垒层上形成图形化的欧姆接触金属区。退火该图形化的欧姆接触金属以提供第一和第二欧姆接触,例如源极接触和漏极接触。使用低损伤蚀刻技术在该势垒层的栅极区内的保护层内蚀刻凹槽,从而暴露该势垒层的栅极区的一部分.在该钝化层中的凹槽内形成栅极接触。

在本发明的特定实施例中,该保护层包含钝化层.该保护层可以是例如氮化铝层、氮化硅层、与/或二氧化硅单层或多层.该低损伤蚀刻技术可以是使用强碱的湿法蚀刻。在本发明某些实施例中,在形成保护层之前,退火图形化的欧姆接触金属以提供第一及第二欧姆接触。在本发明其它实施例中,在形成保护层之后,退火图形化的欧姆接触金属以提供第一及第二欧姆接触。

附图说明

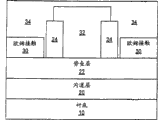

图1A至1F为示出根据本发明实施例的晶体管制造的示意图。

图2A至2B为示出根据本发明另一些实施例的晶体管制造的操作的示意图。

图3为根据本发明实施例的备选制造步骤的示意图。

图4为根据本发明另一些实施例的晶体管的示意图。

图5为根据本发明另一些实施例的晶体管的示意图.

具体实施方式

在下文中参考附图更加全面地描述本发明,其中在附图中示出了本发明的实施例。然而,可以以许多不同形式实施本发明,不应将本发明本发明理解为受限于本说明书中所阐述的实施例;相反,提供这些实施例使得本公开变得彻底和完整,并向本领域技术人员全面地传达本发明的范围。在整个说明书中,相同的数字表示相同的元件。另外,示意性地示出各图中所示的各层和区域.因此,本发明不限于附图中所示的相对尺寸、间距、和排列。本领域技术人员还将会理解,本说明书中提到的形成于衬底或其它层“之上”的层是指,该层直接形成于该衬底或其它层上,或者该层形成于该衬底或其它层上的一个或多个插入层之上。本领域技术人员将会理解,置成与另一个特征相邻的结构或特征可以具有与该相邻特征交叠或位于该相邻特征之下的部分。

本发明的实施例利用保护层与/或低损伤凹槽制造技术减小诸如晶体管的半导体器件中的栅极泄漏与/或提供高质量的肖特基接触.使用保护层可以减小在器件欧姆接触退火过程中可能出现的晶体管栅极区内半导体的损伤。因此可以提供高质量的栅极和欧姆接触,同时减小由形成欧姆接触导致的栅极区的退化。

本发明的实施例尤其适用于诸如III族氮化物基器件的氮化物基HEMT。这里使用的术语“III族氮化物”指氮与元素周期表中III族元素(通常为铝(Al)、镓(Ga)、与/或铟(In))之间形成的半导体化合物。该术语还表示诸如AlGaN和AlInGaN的三元和四元化合物.本领域技术人员将容易理解,III族元素可与氮组合形成二元(例如GaN)、三元(例如AlGaN、AlInN)、以及四元(例如AlInGaN)化合物。这些化合物都具有这样的经验化学式,其中一个氮分子与总共......相结合......,

......0≤x≤1通常用于描述它们。

例如,在共同转让的标题为“ALUMINUM GALLIUM NITRIDE/GALLIUMNITRIDE HIGH ELECTRON MOBILITY TRANSISTORS HAVING A GATE CONTACTON A GALLIUM NITRIDE BASED CAP SEGMENT AND METHODS OF FABRICATINGSAME”的美国专利6316793以及2001年7月12日提交并于2002年6月6日公开的美国专利申请No.2002/0066908A1;标题为“GROUP IIINITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR(HEMT)WITHBARRIER/SPACER LAYER”于2001年5月11日提交的美国临时申请序列号60/290195;标题为“GROUP-III NITRIDE BASED HIGH ELECTRONMOBILITY TRANSISTOR(HEMT)WITH BARRIER/SPACER LAYER”,Smorchkova等2002年11月14日公开的美国专利申请No.2002/0167023A1;以及标题为“NITRIDE-BASED TRANSISTORS ANDMETHODS OF FABRICATION THEREOF USING NON-ETCHED CONTACTRECESSES”的美国专利申请序列号NO.10/617843中描述了可以使用本发明实施例的GaN基HEMT的适合结构,这些专利公开在此被完整引用作为参考。

图1A至1E示意性阐述了本发明的实施例的制造.从图1A可以看出,提供衬底10,可以在该衬底上形成氮化物基器件。在本发明特定实施例中,衬底10可以为半绝缘碳化硅(SiC)衬底,该碳化硅例如可以为4H多型碳化硅。其它碳化硅候选多型包括3C、6H、和15R多型。术语“半绝缘”为描述性的,而非绝对意义上的。在本发明具体实施例中,碳化硅体晶体室温下的电阻率等于或高于约1×105Ω-cm。

可在衬底10上提供可选的缓冲层、成核层、与/或过渡层(未示出)。例如,可以提供AlN缓冲层以在碳化硅衬底和器件其余部分之间提供恰当的晶体结构过渡。另外,也可以提供(多个)应变平衡过渡层,例如如共同转让的并......公开的美国专利公开2003/0102482A1............TRANSISTORS AND METHODS OF FABRI CATING STRAIN BALANCEDNITRIDE HETEROJUNCTION TRANSISTORS,和标题为“STRAIN BALANCEDNITRIDE HETEROJUNCTION TRANSISTOR”的于2001年12月3日提交的美国临时专利申请序列号No.60/337687中所描述的,这些专利公开在此引用作为参考,如同在此阐述了其全文一样。

和III族氮化物器件极为常用的衬底材料蓝宝石(Al2O3)相比,碳化硅与III族氮化物的晶格更匹配。这种更小的晶格失配导致III族氮化物薄膜的质量高于通常蓝宝石上得到的III族氮化物薄膜的质量。碳化硅还具有非常高的导热率,因此碳化硅上的III族氮化物器件的总输出功率不会像在蓝宝石上形成的相同器件那样受到衬底热散逸限制。另外,利用半绝缘碳化硅衬底使得可以实现器件隔离和寄生电容减小。例如由北卡罗来纳州Durham的Cree Inc.,即本发明的受让人制造合适的SiC衬底,制造方法在例如美国专利No.Re.34,861、4,946,547、5,200,022、以及6,218,680中得到描述,这些专利的内容在此被完整引用作为参考。类似地,例如在美国专利No.5,210,051、5,393,993、5,523,589、以及5,292,501中已经描述了III族氮化物的外延生长技术,这些专利的内容在此被完整引用作为参考。

尽管碳化硅可以用作衬底材料,本发明的实施例可以使用任何合适的衬底,例如蓝宝石、氮化铝、铝镓氮化物、氮化镓、硅、GaAs、LGO、ZnO、LAO、InP等。在一些实施例中,还可以形成适当的缓冲层。

返回图1A,在衬底10上提供沟道层20。可使用缓冲层、过渡层、与/或成核层,将沟道层20沉积在衬底10上。沟道层20可受到压应变。另外,可以使用MOCVD或者本技术领域技术人员已知的其它方法(例如MBE或HVPE)沉积该沟道层与/或缓冲成核与/或过渡层.

......III-氮化物,例如AlxGa1-xN,其中0≤x<1,假设在该沟道层和势垒层之间的界面处,沟道层20导带边缘的能量低于势垒层22导带边缘的能量。在在本发明的某些实施例中,x=0,表示沟道层20为GaN。沟道层20还可以为其它III族氮化物,例如InGaN、AlInGaN等.沟道层20可以是未掺杂的(“非故意掺杂”),生长到厚度大于约.沟道层20还可以为多层结构,例如GaN、AlGaN等的超晶格或组合。

在沟道层20上提供势垒层22。沟道层20带隙可小于势垒层22的带隙,且沟道层20的电子亲合势也可大于势垒层22。势垒层22可沉积在沟道层20上。在本发明特定实施例中,势垒层22为AlN、AlInN、AlGaN或AlInGaN,其厚度为约0.1nm至约10nm。在标题为“GROUP-III NITRIDEBASED HIGH ELECTRON MOBILITY TRANSISTOR (HEMT) WITHBARRIER/SPACER LAYER”Smorchkova等的美国专利公开No.2002/0167023A1中描述了根据本发明特定实施例的各层的示例,该专利公开内容在此引用作为参考,如同在此阐述了其全文一样。在本发明特定实施例中,势垒层22足够厚且Al组分和掺杂足够高,使得当势垒层22被掩埋在欧姆接触金属下时通过极化效应在沟道层20和势垒层22之间的界面感生相当高的载流子浓度。同样,势垒层22应该足够厚以减小或最小化由于沉积在势垒层22和第二盖层24之间的界面处离化杂质引起的电子在沟道中的散射(图1B)。

势垒层22可以为III族氮化物,并且带隙大于沟道层20的带隙且电子亲合势小于沟道层20。因此,在本发明的某些实施例中,势垒层22为AlGaN、AlInGaN与/或AlN或者这些层的组合。势垒层22厚度为例如约0.1nm至约10nm,但是并不厚到使得......

......本发明,势垒层22未掺杂或者用n型掺杂剂掺杂到小于约1019cm-3的浓度。在本发明一些实施例中,势垒层22为AlxGa1-xN,其中0<x<1。在特定实施例中,铝浓度约为25%.然而,在本发明的其它实施例中,势垒层22包含铝浓度为约5%至约100%的AlGaN。在本发明特定实施例中,铝组分大于约10%。

图1B示出了在势垒层22上形成保护层24.保护层24为氮化硅(SixNy)、氮化铝(AlN)、与/或其它合适的保护材料,例如二氧化硅(SiO2)与/或氧氮化物(oxynitride)。保护层24还可以使用其它材料,只要能够除去该材料而不损伤下面的势垒层22即可.例如,保护层24也可包含氧化镁、氧化钪、氧化铝与/或氧氮化铝.另外,保护层24可以是组分均匀与/或不均匀的单层或多层.

在本发明特定实施例中,保护层24为SiN.可通过PVD与/或CVD形成SiN,该SiN可以为非化学配比的并处于压应变或张应变.例如,该保护层的应力可以为约-100MPa至约100MPa.在本发明某些实施例中,SiN保护层在633nm波长的折射率为约1.6至约2.2.在特定实施例中,SiN保护层的折射率为1.98±0.05。

在某些实施例中,保护层24可以为AlN。可通过PVD与/或CVD形成该AlN,该AlN可以为非化学配比的并处于压应变或张应变.例如,该保护层的应力可以为约-100MPa至约100MPa。在本发明某些实施例中,AlN保护层在633nm波长的折射率为约1.8至约2.1.在特定实施例中,AlN保护层的折射率为1.85±0.05。

保护层24还可以为SiO2。可通过PVD与/或CVD形成该SiO2,该SiO2可以为非化学配比的并处于压应变或张应变。例如,该保护层的应力可以为约-100MPa至约......

......在633nm波长的折射率为约1.36至约1.56。在特定实施例中,SiO2保护层的折射率为1.46±0.03。

保护层24毯状形成于势垒层22上,可通过沉积形成该保护层24。例如,可通过高质量溅射与/或PECVD形成氮化硅层。通常,保护层24的厚度约为30nm,然而,也可以使用其它厚度的层。例如,保护层应该足够厚,从而在随后欧姆接触退火过程中保护下面的层。厚度仅为两个或三个单原子层的层就足以达到该目的。然而,通常保护层24的厚度为约10nm至约500nm。同样,可与III族氮化物层的MOCVD生长原位地生长高质量的SiN保护层。

如图1C所示,在保护层24内开窗口,用于形成欧姆接触30.可使用图形化掩模以及对势垒层22具有低损伤的蚀刻形成这些窗口,以暴露下面的势垒层22。除了反应离子蚀刻之外,低损伤蚀刻技术的示例还包含例如感应耦合等离子体或电子回旋共振(ECR)或等离子体没有DC成分的下游等离子体蚀刻。对于SiO2,低损伤蚀刻可以为使用缓冲氢氟酸的湿法蚀刻。还可以选择性地将SiN与/或SiO2蚀刻到诸如ITO、SCO、MgO等的蚀刻停止层,随后也可以低损伤地除去该蚀刻停止层.对于SiN,可以使用SiO2作为蚀刻停止层。在这些实施例中,保护层24可包含SiN、AlN、与/或SiO2层以及蚀刻阻止层。因此在本发明某些实施例中,保护层24可包含多个层。

如图1C进一步所示,随后执行光刻步骤和蒸发,图形化欧姆金属以提供欧姆接触30。欧姆接触30被图形化成小于保护层24内的窗口,使得欧姆接触30的边缘与保护层24分隔开。例如,欧姆接触30的边缘可以与保护层24分隔约0.1至约0.2μm的距离.欧姆接触30的边缘与保护层24的间距应为......

......欧姆接触金属的......。如果该欧姆接触金属接触保护层24,则金属可能在随后加热步骤中扩散到保护层24内,这导致栅极接触和(多个)欧姆接触30之间短路。然而,欧姆接触30和保护层24之间的间隙不应太大而达不到保护层24的保护目的并由此大幅降低器件性能,但该间隙不应太小而出现欧姆材料与保护层随机接触的危险。因此,例如在本发明某些实施例中,该间隙为约0.1μm至约0.5μm。

退火该欧姆接触材料以提供欧姆接触30。该退火可以为高温退火。例如,在高于约900℃的温度下进行该退火。通过使用欧姆接触退火,该欧姆接触的电阻可从高电阻减小到小于约1Ω-mm。因此,这里使用的术语“欧姆接触”是指接触电阻小于约1Ω-mm的非整流接触.在高温加工步骤期间存在保护层可防止由于该步骤所致的对势垒层22的损伤。因此,例如,高温欧姆接触退火之后栅极区21的薄层电阻基本上和原生(即在接触退火之前)的栅极区21的薄层电阻相同。

图1D示出了栅极窗口的形成。从图1D可以看出,掩模26形成于欧姆接触以及保护层24上,图形化该掩模以形成暴露该保护层24的一部分的窗口。随后穿过保护层24形成凹槽以暴露势垒层22的一部分。使用掩模26以及前述低损伤蚀刻工艺形成该凹槽。在欧姆接触30提供源极接触和漏极接触的特定实施例中,该凹槽可以在源极接触和漏极接触之间偏移,使得该凹槽以及随后的栅极接触32与源极接触比与漏极接触更靠近。

从图1E可以看出,栅极接触32形成于该凹槽内并接触势垒层22的暴露部分。该栅极接触可以为图1E所示的“T”栅,并且可使用传统制造技术制造。合适的栅极材料可取决于阻挡......的成分......

可以使用与氮化物基半导体材料的肖特基接触,例如Ni、Pt、NiSix、Cu、Pd、Cr、W与/或WSiN。尽管是不理想地,但也可以由于例如该低损伤蚀刻的各向异性而在保护层24和栅极接触32之间形成小的间隙,从而形成保护层24和栅极接触32之间的势垒层22的暴露表面.

图1F示出了钝化层34的形成.该钝化层可毯状沉积在图1E的结构上。在特定实施例中,沉积该钝化层34从而基本上填充保护层24和欧姆接触30之间的间隙,同时也填充保护层24和栅极接触32之间的间隙(如果存在该间隙)。在本发明某些实施例中,钝化层34可以是氮化硅、氮化铝、二氧化硅与/或氧氮化物。另外,钝化层34可以是组分均匀与/或不均匀的单层或多层。

尽管已经参考了形成开口栅极接触窗口以及形成与保护层24之间存在间隙的栅极接触的两个掩模工艺描述了本发明的实施例,图2A和2B示出了使用单个掩模形成欧姆接触窗口和欧姆接触的操作。从图2A可以看出,可在保护层24上形成具有负斜角的诸如光致抗蚀剂的掩模200。掩模200的负斜角对应于随后形成的欧姆接触30和图形化的保护层24之间的间隙。使用前述的低损伤蚀刻工艺各向同性地蚀刻保护层24以提供接触窗口。因此,将由掩模200的底部尺寸定义接触窗口。如果蚀刻是各向同性的且该低损伤蚀刻显著过蚀刻以提供横向底切从而形成期望间距,则也可以使用没有负斜角的掩模层.

从图2B可以看出,欧姆接触金属300被蒸发到所得到的结构上。掩模200的突出部分定义了金属沉积在暴露的势垒层22上的位置。因此,接触金属300与图形化的保护层24分隔开。除去掩模200以及掩模200上的金属300,从而得到图1C的结构.

......本领域技术人员公知的.另外,尽管掩模200被示成具有斜角,但在本发明其它实施例中,该掩模可具有台阶或为该掩模提供两个不同外观窗口尺寸的其它这种配置,用于保护层24的蚀刻以及接触材料的沉积。因此,例如可以获得具有不同曝光灵敏度的多层光致抗蚀剂,使得单次曝光可提供具有突出部分或台阶的掩模,使得靠近保护层24的光致抗蚀剂层所提供的窗口大于由远离保护层24的光致抗蚀剂层所提供的窗口。

图3示出了根据本发明另一些实施例的晶体管制造。从图3可以看出,可以省略欧姆金属沉积之前形成保护层24,且欧姆金属可以沉积在势垒层22上并被图形化,从而在势垒层22上提供欧姆接触材料区30。随后在势垒层22的栅极区上以及该欧姆接触材料上形成保护层40。在本发明特定实施例中,保护层40可以是通过溅射而毯状沉积的氮化铝。保护层40也可以是参考保护层24在上面描述的材料。

当保护层40在适当位置时执行欧姆接触材料区30的退火。随后例如可以使用诸如前述的低损伤蚀刻技术除去保护层40.随后,在形成钝化层34之前或之后形成栅极接触32.例如,可以通过溅射沉积氮化硅层。随后,例如使用前述的低损伤蚀刻工艺在该钝化层内蚀刻形成栅极凹槽,并在该凹槽内形成栅极.这种过程可以使氮化硅钝化层维持其完整厚度直至“T”栅边缘。因此,可以提供具有诸如图4所示的结构的晶体管。

或者,可以使用图1A至1F所示的制造步骤提供图4所示的结构,然而可在形成栅极接触32之前或之后除去该保护层24。这种情况下,应使用诸如前述的低损伤蚀刻技术除去保护层24.

......保护层24形成为至少约和欧姆接触30一样厚。从图5可以看出,在这种实施例中,栅极接触34的侧翼可以直接形成在保护层24上.例如,保护层24可形成厚度为约500至约。可执行穿过保护层24的低损伤蚀刻,并且“T”栅32直接形成在保护层24上并穿过该保护层.随后还可提供例如叠层钝化34以改善器件的环境保护.

尽管这里已经参考具体HEMT结构描述了本发明的实施例,不应理解为本发明局限于这些结构.例如,HEMT器件中可包含另外的层而仍然获益于本发明的教导。这种另外的层可包括GaN盖层,例如Yu等在“Schottky barrier engineering in III-V nitrides via thepiezoelectric effect”Applied Physics Letters,Vol.73,No.13,1998中或者2001年7月12日提交2002年6月6日公开的美国专利公开No.2002/0066908A1“ALUMINUM GALLIUMNITRIDE/GALLIUM NITRIDE HIGH ELECTRON MOBILITY TRANSISTORSHAVING A GATE CONTACT ON A GALLIUM NITRIDE BASED CAP SEGMENTAND METHODS OF FABRICATING SAME”中所公开的,这些公开在此引用作为参考,如同在此阐述了其全文一样。在一些实施例中,可沉积诸如SiNx的绝缘层或者相对高质量的AlN,用于形成MISHEMT与/或钝化表面。所述另外的层也可包含组分渐变的一个或多个过渡层。

另外,势垒层22还可设有多个层,如Smorchkova等标题为“GROUPIII NITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR(HEMT)WITHBARRIER/SPACER LAYER”的美国专利公开No.2002/0167023A1中所描述的,该公开在此引用作为参考,如同在此阐述了其全文一样。因此,不应将本发明的实施例理解为将势垒层局限于单层,而是可以包含例如具有GaN、AlGaN与/或AlN层的组合的势垒层。例如,可利用GaN,AlN结构以减小或防止合金散射。因此,......的实施例......

......层可包含AlGaN基势垒层、AlN基势垒层及其组合.

在附图和说明书中,已经公开了本发明的典型实施例;尽管使用了特定的术语,但使用这些术语是出于普通的描述意义,而非出于限制的目的。

Claims (40)

1.一种制造晶体管的方法,包括:

在氮化物基半导体沟道层上形成氮化物基半导体势垒层;

在该氮化物基半导体势垒层的栅极区上形成保护层;

在该势垒层上形成图形化的欧姆接触金属区;

除去该保护层;

退火该图形化的欧姆接触金属以提供第一和第二欧姆接触,其中在保护层位于栅极区上的情形下进行该退火;以及

直接在该势垒层的栅极区上形成栅极接触。

2.权利要求1的方法,其中该保护层包含氮化铝层、氮化硅层与/或二氧化硅层。

3.权利要求1的方法,其中除去该保护层包括使用低损伤蚀刻技术除去该保护层。

4.权利要求3的方法,其中该低损伤蚀刻技术包括使用强碱的湿法蚀刻。

5.权利要求1的方法,其中在除去该保护层之后,在该势垒层的暴露部分上形成钝化层。

6.权利要求5的方法,其中形成栅极接触包括:

使用低损伤蚀刻技术在该钝化层内蚀刻凹槽,从而暴露该势垒层的栅极区的一部分;以及

在该钝化层的凹槽内形成栅极接触。

7.权利要求5的方法,其中形成栅极接触包括形成延伸穿过该钝化层与该势垒层接触的栅极接触。

8.权利要求1的方法,其中形成保护层包括在该势垒层上形成图形化的保护层,该图形化的保护层覆盖与栅极区相对应的势垒层的第一部分并暴露与第一及第二欧姆接触相对应的势垒层的相邻第二部分;并且

其中形成图形化的欧姆接触金属区包括在势垒层的第二部分上形成图形化的欧姆接触金属区,该图形化的欧姆接触金属区与该图形化的保护层相邻并分隔开。

9.权利要求8的方法,其中形成图形化的保护层包括:

在该势垒层上毯状沉积保护层材料;

在该毯状沉积的保护层材料上形成掩模,该掩模具有与第一及第二欧姆接触的位置相对应的窗口;

利用低损伤蚀刻技术通过所述窗口蚀刻该毯状沉积的保护层;以及

除去该掩模。

10.权利要求9的方法,其中与第一及第二欧姆接触的位置相对应的窗口大于第一及第二欧姆接触的面积。

11.权利要求9的方法,其中在除去该掩模之前,在势垒层的第二部分上形成图形化的欧姆接触金属区,该图形化的欧姆接触金属区与该图形化的保护层相邻且分隔开。

12.权利要求5的方法,其中该钝化层包含氮化硅。

13.权利要求1的方法,进一步包括:

形成III族氮化物层以提供该氮化物基沟道层;以及

其中形成氮化物基半导体势垒层包括形成III族氮化物层。

14.权利要求13的方法,其中该沟道层的成分为AlxGa1-xN,其中0≤x<1,且其中该沟道层的带隙小于该势垒层的带隙。

15.权利要求14的方法:

其中该沟道层包含AlGaN、GaN、InGaN、与/或AlInGaN;并且

其中该势垒层包含AlN、AlInN、AlGaN、GaN、InGaN、与/或AlInGaN。

16.权利要求1的方法,其中该势垒层包含多个层。

17.权利要求1的方法,进一步包括:

在衬底上形成缓冲层;以及

在该缓冲层上形成III族氮化物沟道层以提供该氮化物基沟道层。

18.权利要求1的方法,其中该沟道层和该势垒层配置成提供高电子迁移率晶体管。

19.权利要求1的方法,其中该氮化物基沟道层提供于SiC衬底上。

20.权利要求1的方法,其中该保护层形成的厚度至少为所述欧姆接触材料的厚度。

21.权利要求1的方法,其中该保护层的厚度至少为两个单原子层的厚度。

22.权利要求1的方法,其中该保护层厚度为5.0nm至500nm。

23.权利要求5的方法,其中原位地形成钝化层。

24.权利要求23的方法,其中形成钝化层包括使用MOCVD生长方法生长该钝化层。

25.一种高电子迁移率晶体管,包含:

衬底上的氮化物基沟道层;

该氮化物基沟道层上的氮化物基半导体势垒层,该氮化物基半导体势垒层的薄层电阻基本上和该氮化物基半导体势垒层的原生薄层电阻相同;

该势垒层上的欧姆接触;以及

直接在该势垒层上的栅极接触。

26.权利要求25的高电子迁移率晶体管,进一步包含置于该势垒层上的保护层,该保护层与所述欧姆接触相邻且分隔开,且栅极接触延伸穿过该保护层。

27.权利要求26的高电子迁移率晶体管,进一步包含位于该保护层上且基本填充所述欧姆接触和该保护层之间的间隙的钝化层。

28.权利要求27的高电子迁移率晶体管,其中该钝化层还位于该保护层上,且其中所述栅极接触延伸穿过该保护层和该钝化层。

29.权利要求27的高电子迁移率晶体管,其中该栅极接触的至少一部分直接位于该保护层上,且该栅极接触的一部分直接位于该势垒层上。

30.权利要求25的高电子迁移率晶体管,进一步包含位于该势垒层上并基本上填充所述欧姆接触与该栅极接触之间的间隙的钝化层。

31.权利要求41的高电子迁移率晶体管,

其中该氮化物基沟道层包括III族氮化物层;且

其中该氮化物基半导体势垒层包括III族氮化物层。

32.权利要求25的高电子迁移率晶体管,其中该沟道层的带隙小于该势垒层。

34.权利要求25的高电子迁移率晶体管,其中该沟道层包含III族氮化物层的超晶格与/或组合。

35.权利要求25的高电子迁移率晶体管:

其中该沟道层包含AlGaN、GaN、InGaN、与/或AlInGaN;并且

其中该势垒层包含AlN、AlInN、AlGaN、GaN、InGaN、与/或AlInGaN。

36.权利要求25的高电子迁移率晶体管,其中该势垒层包含AlxGa1-xN,其中0<x<1。

37.权利要求25的高电子迁移率晶体管,其中该势垒层包含多个层。

38.权利要求25的高电子迁移率晶体管,进一步包含衬底上的缓冲层,且其中该氮化物基沟道层置于该缓冲层上。

39.权利要求26的高电子迁移率晶体管,其中该保护层的厚度至少和所述欧姆接触的厚度相同。

40.权利要求25的高电子迁移率晶体管,其中所述欧姆接触的接触电阻小于1Ω-mm。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/758,871 | 2004-01-16 | ||

| US10/758,871 US7045404B2 (en) | 2004-01-16 | 2004-01-16 | Nitride-based transistors with a protective layer and a low-damage recess and methods of fabrication thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1906765A CN1906765A (zh) | 2007-01-31 |

| CN100468770C true CN100468770C (zh) | 2009-03-11 |

Family

ID=34807509

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2004800405318A Expired - Lifetime CN100468770C (zh) | 2004-01-16 | 2004-09-28 | 具有保护层和低损凹槽的氮化物基晶体管及其制造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US7045404B2 (zh) |

| EP (2) | EP2492963B1 (zh) |

| JP (2) | JP5156235B2 (zh) |

| KR (2) | KR101202497B1 (zh) |

| CN (1) | CN100468770C (zh) |

| CA (1) | CA2553669A1 (zh) |

| TW (1) | TW200525760A (zh) |

| WO (1) | WO2005076365A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107230617A (zh) * | 2016-03-25 | 2017-10-03 | 北京大学 | 氮化镓半导体器件的制备方法 |

Families Citing this family (182)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7898047B2 (en) * | 2003-03-03 | 2011-03-01 | Samsung Electronics Co., Ltd. | Integrated nitride and silicon carbide-based devices and methods of fabricating integrated nitride-based devices |

| US7112860B2 (en) | 2003-03-03 | 2006-09-26 | Cree, Inc. | Integrated nitride-based acoustic wave devices and methods of fabricating integrated nitride-based acoustic wave devices |

| US7045404B2 (en) | 2004-01-16 | 2006-05-16 | Cree, Inc. | Nitride-based transistors with a protective layer and a low-damage recess and methods of fabrication thereof |

| US7382001B2 (en) * | 2004-01-23 | 2008-06-03 | International Rectifier Corporation | Enhancement mode III-nitride FET |

| US7612390B2 (en) * | 2004-02-05 | 2009-11-03 | Cree, Inc. | Heterojunction transistors including energy barriers |

| US20050218414A1 (en) * | 2004-03-30 | 2005-10-06 | Tetsuzo Ueda | 4H-polytype gallium nitride-based semiconductor device on a 4H-polytype substrate |

| JP2005317684A (ja) * | 2004-04-27 | 2005-11-10 | Eudyna Devices Inc | ドライエッチング方法および半導体装置 |

| US7332795B2 (en) * | 2004-05-22 | 2008-02-19 | Cree, Inc. | Dielectric passivation for semiconductor devices |

| US7238560B2 (en) * | 2004-07-23 | 2007-07-03 | Cree, Inc. | Methods of fabricating nitride-based transistors with a cap layer and a recessed gate |

| JP4866007B2 (ja) * | 2005-01-14 | 2012-02-01 | 富士通株式会社 | 化合物半導体装置 |

| EP1843390B1 (en) * | 2005-01-25 | 2011-11-09 | Fujitsu Limited | Semiconductor device provided with mis structure and method for manufacturing the same |

| JP4912604B2 (ja) * | 2005-03-30 | 2012-04-11 | 住友電工デバイス・イノベーション株式会社 | 窒化物半導体hemtおよびその製造方法。 |

| US7598576B2 (en) * | 2005-06-29 | 2009-10-06 | Cree, Inc. | Environmentally robust passivation structures for high-voltage silicon carbide semiconductor devices |

| US7855401B2 (en) * | 2005-06-29 | 2010-12-21 | Cree, Inc. | Passivation of wide band-gap based semiconductor devices with hydrogen-free sputtered nitrides |

| US9331192B2 (en) * | 2005-06-29 | 2016-05-03 | Cree, Inc. | Low dislocation density group III nitride layers on silicon carbide substrates and methods of making the same |

| US7525122B2 (en) * | 2005-06-29 | 2009-04-28 | Cree, Inc. | Passivation of wide band-gap based semiconductor devices with hydrogen-free sputtered nitrides |

| US20070018199A1 (en) | 2005-07-20 | 2007-01-25 | Cree, Inc. | Nitride-based transistors and fabrication methods with an etch stop layer |

| US20070018198A1 (en) * | 2005-07-20 | 2007-01-25 | Brandes George R | High electron mobility electronic device structures comprising native substrates and methods for making the same |

| US8183595B2 (en) * | 2005-07-29 | 2012-05-22 | International Rectifier Corporation | Normally off III-nitride semiconductor device having a programmable gate |

| JP4897948B2 (ja) | 2005-09-02 | 2012-03-14 | 古河電気工業株式会社 | 半導体素子 |

| JP4799965B2 (ja) * | 2005-09-06 | 2011-10-26 | 日本電信電話株式会社 | 窒化物半導体を用いたヘテロ構造電界効果トランジスタ |

| WO2008027027A2 (en) * | 2005-09-07 | 2008-03-06 | Cree, Inc | Transistor with fluorine treatment |

| US7399692B2 (en) * | 2005-10-03 | 2008-07-15 | International Rectifier Corporation | III-nitride semiconductor fabrication |

| US7709269B2 (en) * | 2006-01-17 | 2010-05-04 | Cree, Inc. | Methods of fabricating transistors including dielectrically-supported gate electrodes |

| US7592211B2 (en) | 2006-01-17 | 2009-09-22 | Cree, Inc. | Methods of fabricating transistors including supported gate electrodes |

| JP2007234986A (ja) * | 2006-03-02 | 2007-09-13 | National Institute Of Information & Communication Technology | AlN障壁層を有するGaN系電界効果トランジスタ、及びそのような電界効果トランジスタの製造方法 |

| JP5362187B2 (ja) * | 2006-03-30 | 2013-12-11 | 日本碍子株式会社 | 半導体素子 |

| US9040398B2 (en) * | 2006-05-16 | 2015-05-26 | Cree, Inc. | Method of fabricating seminconductor devices including self aligned refractory contacts |

| US7737455B2 (en) * | 2006-05-19 | 2010-06-15 | Bridgelux, Inc. | Electrode structures for LEDs with increased active area |

| JP5207598B2 (ja) * | 2006-05-24 | 2013-06-12 | パナソニック株式会社 | 窒化物半導体材料、半導体素子およびその製造方法 |

| CN100495724C (zh) * | 2006-09-06 | 2009-06-03 | 中国科学院半导体研究所 | 氮化镓基异质结场效应晶体管结构及制作方法 |

| JP5520432B2 (ja) | 2006-10-03 | 2014-06-11 | 古河電気工業株式会社 | 半導体トランジスタの製造方法 |

| US8823057B2 (en) * | 2006-11-06 | 2014-09-02 | Cree, Inc. | Semiconductor devices including implanted regions for providing low-resistance contact to buried layers and related devices |

| WO2008061778A1 (en) * | 2006-11-21 | 2008-05-29 | Interuniversitair Microelektronica Centrum | Surface treatment and passivation of aigan/gan hemt |

| JP5401758B2 (ja) * | 2006-12-12 | 2014-01-29 | サンケン電気株式会社 | 半導体装置及びその製造方法 |

| WO2008086001A2 (en) * | 2007-01-10 | 2008-07-17 | International Rectifier Corporation | Active area shaping for iii-nitride device and process for its manufacture |

| US20080265444A1 (en) * | 2007-04-26 | 2008-10-30 | Heetronix | Thin-film aluminum nitride encapsulant for metallic structures on integrated circuits and method of forming same |

| US9647103B2 (en) * | 2007-05-04 | 2017-05-09 | Sensor Electronic Technology, Inc. | Semiconductor device with modulated field element isolated from gate electrode |

| JP2008288289A (ja) * | 2007-05-16 | 2008-11-27 | Oki Electric Ind Co Ltd | 電界効果トランジスタとその製造方法 |

| US8455920B2 (en) * | 2007-05-23 | 2013-06-04 | International Rectifier Corporation | III-nitride heterojunction device |

| JP2008306026A (ja) * | 2007-06-08 | 2008-12-18 | Eudyna Devices Inc | 半導体装置の製造方法 |

| US20090072269A1 (en) * | 2007-09-17 | 2009-03-19 | Chang Soo Suh | Gallium nitride diodes and integrated components |

| US7800132B2 (en) * | 2007-10-25 | 2010-09-21 | Northrop Grumman Systems Corporation | High electron mobility transistor semiconductor device having field mitigating plate and fabrication method thereof |

| US7935620B2 (en) * | 2007-12-05 | 2011-05-03 | Freescale Semiconductor, Inc. | Method for forming semiconductor devices with low leakage Schottky contacts |

| KR100922575B1 (ko) * | 2007-12-05 | 2009-10-21 | 한국전자통신연구원 | 티형 게이트 전극을 구비한 반도체 소자 및 그의 제조 방법 |

| US7632726B2 (en) * | 2007-12-07 | 2009-12-15 | Northrop Grumman Space & Mission Systems Corp. | Method for fabricating a nitride FET including passivation layers |

| US8431962B2 (en) * | 2007-12-07 | 2013-04-30 | Northrop Grumman Systems Corporation | Composite passivation process for nitride FET |

| US7750370B2 (en) * | 2007-12-20 | 2010-07-06 | Northrop Grumman Space & Mission Systems Corp. | High electron mobility transistor having self-aligned miniature field mitigating plate on a protective dielectric layer |

| US7842587B2 (en) * | 2008-01-30 | 2010-11-30 | Freescale Semiconductor, Inc. | III-V MOSFET fabrication and device |

| US8519438B2 (en) | 2008-04-23 | 2013-08-27 | Transphorm Inc. | Enhancement mode III-N HEMTs |

| US9711633B2 (en) * | 2008-05-09 | 2017-07-18 | Cree, Inc. | Methods of forming group III-nitride semiconductor devices including implanting ions directly into source and drain regions and annealing to activate the implanted ions |

| US7985986B2 (en) | 2008-07-31 | 2011-07-26 | Cree, Inc. | Normally-off semiconductor devices |

| US8384115B2 (en) | 2008-08-01 | 2013-02-26 | Cree, Inc. | Bond pad design for enhancing light extraction from LED chips |

| US8289065B2 (en) | 2008-09-23 | 2012-10-16 | Transphorm Inc. | Inductive load power switching circuits |

| US7898004B2 (en) | 2008-12-10 | 2011-03-01 | Transphorm Inc. | Semiconductor heterostructure diodes |

| JP5472293B2 (ja) * | 2009-04-20 | 2014-04-16 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| US8742459B2 (en) * | 2009-05-14 | 2014-06-03 | Transphorm Inc. | High voltage III-nitride semiconductor devices |

| US8105889B2 (en) | 2009-07-27 | 2012-01-31 | Cree, Inc. | Methods of fabricating transistors including self-aligned gate electrodes and source/drain regions |

| US8390000B2 (en) | 2009-08-28 | 2013-03-05 | Transphorm Inc. | Semiconductor devices with field plates |

| US20110068348A1 (en) | 2009-09-18 | 2011-03-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Thin body mosfet with conducting surface channel extensions and gate-controlled channel sidewalls |

| US8216924B2 (en) * | 2009-10-16 | 2012-07-10 | Cree, Inc. | Methods of fabricating transistors using laser annealing of source/drain regions |

| US8389977B2 (en) | 2009-12-10 | 2013-03-05 | Transphorm Inc. | Reverse side engineered III-nitride devices |

| US20110241020A1 (en) * | 2010-03-31 | 2011-10-06 | Triquint Semiconductor, Inc. | High electron mobility transistor with recessed barrier layer |

| US8907350B2 (en) * | 2010-04-28 | 2014-12-09 | Cree, Inc. | Semiconductor devices having improved adhesion and methods of fabricating the same |

| US8847563B2 (en) | 2010-07-15 | 2014-09-30 | Cree, Inc. | Power converter circuits including high electron mobility transistors for switching and rectifcation |

| US8742460B2 (en) | 2010-12-15 | 2014-06-03 | Transphorm Inc. | Transistors with isolation regions |

| US8643062B2 (en) | 2011-02-02 | 2014-02-04 | Transphorm Inc. | III-N device structures and methods |

| JP5762049B2 (ja) * | 2011-02-28 | 2015-08-12 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8716141B2 (en) | 2011-03-04 | 2014-05-06 | Transphorm Inc. | Electrode configurations for semiconductor devices |

| US8772842B2 (en) | 2011-03-04 | 2014-07-08 | Transphorm, Inc. | Semiconductor diodes with low reverse bias currents |

| KR101781438B1 (ko) * | 2011-06-14 | 2017-09-25 | 삼성전자주식회사 | 반도체 발광소자의 제조방법 |

| US8901604B2 (en) | 2011-09-06 | 2014-12-02 | Transphorm Inc. | Semiconductor devices with guard rings |

| US9257547B2 (en) | 2011-09-13 | 2016-02-09 | Transphorm Inc. | III-N device structures having a non-insulating substrate |

| US8598937B2 (en) | 2011-10-07 | 2013-12-03 | Transphorm Inc. | High power semiconductor electronic components with increased reliability |

| US8530978B1 (en) * | 2011-12-06 | 2013-09-10 | Hrl Laboratories, Llc | High current high voltage GaN field effect transistors and method of fabricating same |

| JP2013131650A (ja) * | 2011-12-21 | 2013-07-04 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| US9165766B2 (en) | 2012-02-03 | 2015-10-20 | Transphorm Inc. | Buffer layer structures suited for III-nitride devices with foreign substrates |

| US8860088B2 (en) | 2012-02-23 | 2014-10-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor structure and method of forming the same |

| WO2013155108A1 (en) | 2012-04-09 | 2013-10-17 | Transphorm Inc. | N-polar iii-nitride transistors |

| CN102709321A (zh) * | 2012-04-20 | 2012-10-03 | 程凯 | 增强型开关器件及其制造方法 |

| US20130299895A1 (en) | 2012-05-09 | 2013-11-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Iii-v compound semiconductor device having dopant layer and method of making the same |

| US8866195B2 (en) | 2012-07-06 | 2014-10-21 | Taiwan Semiconductor Manufacturing Co., Ltd. | III-V compound semiconductor device having metal contacts and method of making the same |

| US9184275B2 (en) | 2012-06-27 | 2015-11-10 | Transphorm Inc. | Semiconductor devices with integrated hole collectors |

| US9076850B2 (en) | 2012-07-30 | 2015-07-07 | Samsung Electronics Co., Ltd. | High electron mobility transistor |

| US9099490B2 (en) * | 2012-09-28 | 2015-08-04 | Intel Corporation | Self-aligned structures and methods for asymmetric GaN transistors and enhancement mode operation |

| US9812338B2 (en) | 2013-03-14 | 2017-11-07 | Cree, Inc. | Encapsulation of advanced devices using novel PECVD and ALD schemes |

| US9991399B2 (en) | 2012-10-04 | 2018-06-05 | Cree, Inc. | Passivation structure for semiconductor devices |

| US8994073B2 (en) | 2012-10-04 | 2015-03-31 | Cree, Inc. | Hydrogen mitigation schemes in the passivation of advanced devices |

| JP6178065B2 (ja) * | 2012-10-09 | 2017-08-09 | 株式会社東芝 | 半導体装置 |

| US9570600B2 (en) | 2012-11-16 | 2017-02-14 | Massachusetts Institute Of Technology | Semiconductor structure and recess formation etch technique |

| US9171730B2 (en) | 2013-02-15 | 2015-10-27 | Transphorm Inc. | Electrodes for semiconductor devices and methods of forming the same |

| US9087718B2 (en) | 2013-03-13 | 2015-07-21 | Transphorm Inc. | Enhancement-mode III-nitride devices |

| US9245993B2 (en) | 2013-03-15 | 2016-01-26 | Transphorm Inc. | Carbon doping semiconductor devices |

| US20140335666A1 (en) | 2013-05-13 | 2014-11-13 | The Government Of The United States Of America, As Represented By The Secretary Of The Navy | Growth of High-Performance III-Nitride Transistor Passivation Layer for GaN Electronics |

| US9755059B2 (en) | 2013-06-09 | 2017-09-05 | Cree, Inc. | Cascode structures with GaN cap layers |

| US9847411B2 (en) | 2013-06-09 | 2017-12-19 | Cree, Inc. | Recessed field plate transistor structures |

| US9679981B2 (en) | 2013-06-09 | 2017-06-13 | Cree, Inc. | Cascode structures for GaN HEMTs |

| WO2015009514A1 (en) | 2013-07-19 | 2015-01-22 | Transphorm Inc. | Iii-nitride transistor including a p-type depleting layer |

| JP6338832B2 (ja) * | 2013-07-31 | 2018-06-06 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR101455283B1 (ko) * | 2013-08-09 | 2014-10-31 | 홍익대학교 산학협력단 | 패시베이션막 형성방법 및 이를 포함하는 AlGaN/GaN HFET의 제조방법 |

| CN103760206B (zh) * | 2014-01-14 | 2016-07-06 | 江苏新广联科技股份有限公司 | 基于氮化镓材料的人体血糖测试芯片 |

| US20150255589A1 (en) * | 2014-03-10 | 2015-09-10 | Toshiba Corporation | Indium-containing contact and barrier layer for iii-nitride high electron mobility transistor devices |

| EP2930754A1 (en) * | 2014-04-11 | 2015-10-14 | Nxp B.V. | Semiconductor device |

| US10276712B2 (en) | 2014-05-29 | 2019-04-30 | Hrl Laboratories, Llc | III-nitride field-effect transistor with dual gates |

| US9318593B2 (en) | 2014-07-21 | 2016-04-19 | Transphorm Inc. | Forming enhancement mode III-nitride devices |

| US9536967B2 (en) | 2014-12-16 | 2017-01-03 | Transphorm Inc. | Recessed ohmic contacts in a III-N device |

| US9536966B2 (en) | 2014-12-16 | 2017-01-03 | Transphorm Inc. | Gate structures for III-N devices |

| CN106373874A (zh) * | 2015-07-21 | 2017-02-01 | 北大方正集团有限公司 | 基于AlGaN/GaN HEMT的欧姆接触电极的制造方法 |

| US9812532B1 (en) | 2015-08-28 | 2017-11-07 | Hrl Laboratories, Llc | III-nitride P-channel transistor |

| CN105226093B (zh) * | 2015-11-11 | 2018-06-26 | 成都海威华芯科技有限公司 | GaN HEMT器件及其制作方法 |

| CN108292678B (zh) | 2015-11-19 | 2021-07-06 | Hrl实验室有限责任公司 | 具有双栅极的iii族氮化物场效应晶体管 |

| CN105448977A (zh) * | 2015-12-31 | 2016-03-30 | 深圳市华讯方舟微电子科技有限公司 | 高电子迁移率晶体管及其制造方法 |

| WO2017123999A1 (en) | 2016-01-15 | 2017-07-20 | Transphorm Inc. | Enhancement mode iii-nitride devices having an al(1-x)sixo gate insulator |

| US9786660B1 (en) | 2016-03-17 | 2017-10-10 | Cree, Inc. | Transistor with bypassed gate structure field |

| US10128365B2 (en) | 2016-03-17 | 2018-11-13 | Cree, Inc. | Bypassed gate transistors having improved stability |

| US9947616B2 (en) | 2016-03-17 | 2018-04-17 | Cree, Inc. | High power MMIC devices having bypassed gate transistors |

| TWI762486B (zh) | 2016-05-31 | 2022-05-01 | 美商創世舫科技有限公司 | 包含漸變空乏層的三族氮化物裝置 |

| US10354879B2 (en) | 2016-06-24 | 2019-07-16 | Cree, Inc. | Depletion mode semiconductor devices including current dependent resistance |

| CN109314135B (zh) * | 2016-07-01 | 2023-03-10 | 英特尔公司 | 用于GaN E模式晶体管性能的栅极堆叠体设计 |

| CN108010840B (zh) * | 2016-11-02 | 2021-04-23 | 株洲中车时代半导体有限公司 | 掺杂半导体器件的制备方法和半导体器件 |

| JP2018170458A (ja) * | 2017-03-30 | 2018-11-01 | 株式会社東芝 | 高出力素子 |

| CN107424919A (zh) * | 2017-05-12 | 2017-12-01 | 中国电子科技集团公司第十三研究所 | 一种低损伤介质栅及其制备方法 |

| US10615273B2 (en) | 2017-06-21 | 2020-04-07 | Cree, Inc. | Semiconductor devices having a plurality of unit cell transistors that have smoothed turn-on behavior and improved linearity |

| US10268789B1 (en) | 2017-10-03 | 2019-04-23 | Cree, Inc. | Transistor amplifiers having node splitting for loop stability and related methods |

| CN111480215B (zh) * | 2017-10-11 | 2023-08-15 | 阿卜杜拉国王科技大学 | 具有氮化铟铝三元合金层和第二iii族氮化物三元合金层的异质结的半导体器件 |

| CN109728086A (zh) * | 2017-10-31 | 2019-05-07 | 中国工程物理研究院电子工程研究所 | 侧墙栅高迁移率晶体管的制备方法 |

| JP7100241B2 (ja) * | 2017-12-20 | 2022-07-13 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| CN108461543B (zh) * | 2018-05-29 | 2022-07-08 | 苏州闻颂智能科技有限公司 | 一种GaN HEMT器件及其制备方法 |

| US10483352B1 (en) * | 2018-07-11 | 2019-11-19 | Cree, Inc. | High power transistor with interior-fed gate fingers |

| US10763334B2 (en) | 2018-07-11 | 2020-09-01 | Cree, Inc. | Drain and/or gate interconnect and finger structure |

| US10600746B2 (en) | 2018-07-19 | 2020-03-24 | Cree, Inc. | Radio frequency transistor amplifiers and other multi-cell transistors having gaps and/or isolation structures between groups of unit cell transistors |

| WO2020106537A1 (en) | 2018-11-19 | 2020-05-28 | Cree, Inc. | Semiconductor devices having a plurality of unit cell transistors that have smoothed turn-on behavior and improved linearity |

| US10741496B2 (en) | 2018-12-04 | 2020-08-11 | Nxp Usa, Inc. | Semiconductor devices with a protection layer and methods of fabrication |

| US10770415B2 (en) | 2018-12-04 | 2020-09-08 | Cree, Inc. | Packaged transistor devices with input-output isolation and methods of forming packaged transistor devices with input-output isolation |

| JP7074045B2 (ja) * | 2018-12-21 | 2022-05-24 | 住友電気工業株式会社 | 窒化物半導体デバイスの製造方法及び窒化物半導体デバイス |

| US10937873B2 (en) | 2019-01-03 | 2021-03-02 | Cree, Inc. | High electron mobility transistors having improved drain current drift and/or leakage current performance |

| JP7163806B2 (ja) * | 2019-02-05 | 2022-11-01 | 富士通株式会社 | 化合物半導体装置、化合物半導体装置の製造方法及び増幅器 |

| CN109841677A (zh) * | 2019-03-28 | 2019-06-04 | 英诺赛科(珠海)科技有限公司 | 高电子迁移率晶体管及其制造方法 |

| US11417746B2 (en) | 2019-04-24 | 2022-08-16 | Wolfspeed, Inc. | High power transistor with interior-fed fingers |

| US10923585B2 (en) | 2019-06-13 | 2021-02-16 | Cree, Inc. | High electron mobility transistors having improved contact spacing and/or improved contact vias |

| US10971612B2 (en) | 2019-06-13 | 2021-04-06 | Cree, Inc. | High electron mobility transistors and power amplifiers including said transistors having improved performance and reliability |

| CN112436056B (zh) * | 2019-08-26 | 2024-03-26 | 联华电子股份有限公司 | 高电子迁移率晶体管 |

| CN112490286B (zh) * | 2019-09-12 | 2023-09-19 | 联华电子股份有限公司 | 半导体装置及其制作方法 |

| US11075271B2 (en) | 2019-10-14 | 2021-07-27 | Cree, Inc. | Stepped field plates with proximity to conduction channel and related fabrication methods |

| US11658233B2 (en) | 2019-11-19 | 2023-05-23 | Wolfspeed, Inc. | Semiconductors with improved thermal budget and process of making semiconductors with improved thermal budget |

| CN111223925A (zh) * | 2019-11-27 | 2020-06-02 | 西安电子科技大学 | 基于AlN/GaN超晶格沟道的双向阻断功率器件及制作方法 |

| JP2021145050A (ja) * | 2020-03-12 | 2021-09-24 | 富士通株式会社 | 半導体装置 |

| CN115699326A (zh) | 2020-04-03 | 2023-02-03 | 沃孚半导体公司 | 具有源极、栅极和/或漏极导电通孔的基于iii族氮化物的射频晶体管放大器 |

| US11670605B2 (en) | 2020-04-03 | 2023-06-06 | Wolfspeed, Inc. | RF amplifier devices including interconnect structures and methods of manufacturing |

| US20210313293A1 (en) | 2020-04-03 | 2021-10-07 | Cree, Inc. | Rf amplifier devices and methods of manufacturing |

| US11837457B2 (en) | 2020-09-11 | 2023-12-05 | Wolfspeed, Inc. | Packaging for RF transistor amplifiers |

| US11356070B2 (en) | 2020-06-01 | 2022-06-07 | Wolfspeed, Inc. | RF amplifiers having shielded transmission line structures |

| JP2023520029A (ja) | 2020-04-03 | 2023-05-15 | ウルフスピード インコーポレイテッド | 裏面ソース端子、ゲート端子及び/又はドレイン端子を有するiii族窒化物ベースの高周波増幅器 |

| US11769768B2 (en) | 2020-06-01 | 2023-09-26 | Wolfspeed, Inc. | Methods for pillar connection on frontside and passive device integration on backside of die |

| US11228287B2 (en) | 2020-06-17 | 2022-01-18 | Cree, Inc. | Multi-stage decoupling networks integrated with on-package impedance matching networks for RF power amplifiers |

| US11533025B2 (en) | 2020-06-18 | 2022-12-20 | Wolfspeed, Inc. | Integrated doherty amplifier with added isolation between the carrier and the peaking transistors |

| US11533024B2 (en) | 2020-06-25 | 2022-12-20 | Wolfspeed, Inc. | Multi-zone radio frequency transistor amplifiers |

| US11581859B2 (en) | 2020-06-26 | 2023-02-14 | Wolfspeed, Inc. | Radio frequency (RF) transistor amplifier packages with improved isolation and lead configurations |

| WO2022006770A1 (en) * | 2020-07-08 | 2022-01-13 | Innoscience (Zhuhai) Technology Co., Ltd. | Electronic device and manufacturing method thereof |

| US11887945B2 (en) | 2020-09-30 | 2024-01-30 | Wolfspeed, Inc. | Semiconductor device with isolation and/or protection structures |

| US11742302B2 (en) | 2020-10-23 | 2023-08-29 | Wolfspeed, Inc. | Electronic device packages with internal moisture barriers |

| US12100630B2 (en) | 2020-11-13 | 2024-09-24 | Macom Technology Solutions Holdings, Inc. | Packaged RF power device with PCB routing outside protective member |

| CN112614898A (zh) * | 2020-12-23 | 2021-04-06 | 宁波铼微半导体有限公司 | 一种横向导通型GaN混合pn肖特基功率二极管及其制备方法 |

| US11791389B2 (en) | 2021-01-08 | 2023-10-17 | Wolfspeed, Inc. | Radio frequency transistor amplifiers having widened and/or asymmetric source/drain regions for improved on-resistance performance |

| CN114975614A (zh) * | 2021-02-24 | 2022-08-30 | 联华电子股份有限公司 | 高电子迁移率晶体管及其制作方法 |

| US11869964B2 (en) | 2021-05-20 | 2024-01-09 | Wolfspeed, Inc. | Field effect transistors with modified access regions |

| US12009417B2 (en) | 2021-05-20 | 2024-06-11 | Macom Technology Solutions Holdings, Inc. | High electron mobility transistors having improved performance |

| US12015075B2 (en) | 2021-05-20 | 2024-06-18 | Macom Technology Solutions Holdings, Inc. | Methods of manufacturing high electron mobility transistors having a modified interface region |

| TWI762346B (zh) * | 2021-06-04 | 2022-04-21 | 瑞礱科技股份有限公司 | 一種iii族氮化物半導體元件之歐姆接觸製造方法 |

| US11842937B2 (en) | 2021-07-30 | 2023-12-12 | Wolfspeed, Inc. | Encapsulation stack for improved humidity performance and related fabrication methods |

| US20230075505A1 (en) | 2021-09-03 | 2023-03-09 | Wolfspeed, Inc. | Metal pillar connection topologies for heterogeneous packaging |

| US20230078017A1 (en) | 2021-09-16 | 2023-03-16 | Wolfspeed, Inc. | Semiconductor device incorporating a substrate recess |

| WO2023056145A1 (en) | 2021-10-01 | 2023-04-06 | Wolfspeed, Inc. | Bypassed gate transistors having improved stability |

| US20230291367A1 (en) | 2022-03-08 | 2023-09-14 | Wolfspeed, Inc. | Group iii nitride-based monolithic microwave integrated circuits having multi-layer metal-insulator-metal capacitors |

| US20240105824A1 (en) | 2022-09-23 | 2024-03-28 | Wolfspeed, Inc. | Barrier Structure for Sub-100 Nanometer Gate Length Devices |

| US20240105823A1 (en) | 2022-09-23 | 2024-03-28 | Wolfspeed, Inc. | Barrier Structure for Dispersion Reduction in Transistor Devices |

| US20240106397A1 (en) | 2022-09-23 | 2024-03-28 | Wolfspeed, Inc. | Transistor amplifier with pcb routing and surface mounted transistor die |

| US20240120202A1 (en) | 2022-10-06 | 2024-04-11 | Wolfspeed, Inc. | Implanted Regions for Semiconductor Structures with Deep Buried Layers |

| US20240266419A1 (en) | 2023-02-03 | 2024-08-08 | Wolfspeed, Inc. | Semiconductor Device Having Semiconductor Structure with Polarity Inverting Layer |

| US20240266426A1 (en) | 2023-02-03 | 2024-08-08 | Wolfspeed, Inc. | Semiconductor Structure for Improved Radio Frequency Thermal Management |

| US20240304702A1 (en) | 2023-03-06 | 2024-09-12 | Wolfspeed, Inc. | Field Reducing Structures for Nitrogen-Polar Group III-Nitride Semiconductor Devices |

| WO2024191770A2 (en) | 2023-03-15 | 2024-09-19 | Macom Technology Solutions Holdings, Inc. | Bypassed gate transistors having improved stability |

Family Cites Families (164)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US34861A (en) * | 1862-04-01 | Improved washing-machine | ||

| FR1487060A (zh) * | 1965-07-30 | 1967-10-11 | ||

| FR2465317A2 (fr) * | 1979-03-28 | 1981-03-20 | Thomson Csf | Transistor a effet de champ a frequence de coupure elevee |

| EP0033037B1 (en) * | 1979-12-28 | 1990-03-21 | Fujitsu Limited | Heterojunction semiconductor devices |

| US4536942A (en) * | 1982-12-09 | 1985-08-27 | Cornell Research Foundation, Inc. | Fabrication of T-shaped metal lines for semiconductor devices |

| US4551905A (en) * | 1982-12-09 | 1985-11-12 | Cornell Research Foundation, Inc. | Fabrication of metal lines for semiconductor devices |

| JPH088350B2 (ja) * | 1985-04-08 | 1996-01-29 | 日本電気株式会社 | 半導体装置 |

| US4987008A (en) | 1985-07-02 | 1991-01-22 | Semiconductor Energy Laboratory Co., Ltd. | Thin film formation method |

| JPS6229175A (ja) * | 1985-07-29 | 1987-02-07 | Nippon Telegr & Teleph Corp <Ntt> | 電界効果型トランジスタの製造方法 |

| US4755867A (en) * | 1986-08-15 | 1988-07-05 | American Telephone And Telegraph Company, At&T Bell Laboratories | Vertical Enhancement-mode Group III-V compound MISFETs |

| US4788156A (en) | 1986-09-24 | 1988-11-29 | Microwave Technology, Inc. | Subchannel doping to reduce short-gate effects in field effect transistors |

| JPS63155671A (ja) * | 1986-12-18 | 1988-06-28 | Nec Corp | 半導体装置の製造方法 |

| US4987462A (en) * | 1987-01-06 | 1991-01-22 | Texas Instruments Incorporated | Power MISFET |

| US5258631A (en) * | 1987-01-30 | 1993-11-02 | Hitachi, Ltd. | Semiconductor device having a two-dimensional electron gas as an active layer |

| US4792531A (en) * | 1987-10-05 | 1988-12-20 | Menlo Industries, Inc. | Self-aligned gate process |

| US4866005A (en) | 1987-10-26 | 1989-09-12 | North Carolina State University | Sublimation of silicon carbide to produce large, device quality single crystals of silicon carbide |

| US5411914A (en) | 1988-02-19 | 1995-05-02 | Massachusetts Institute Of Technology | III-V based integrated circuits having low temperature growth buffer or passivation layers |

| EP0334006A1 (en) | 1988-02-22 | 1989-09-27 | Siemens Aktiengesellschaft | Stacked channel heterojunction fet |

| JP2508818B2 (ja) * | 1988-10-03 | 1996-06-19 | 三菱電機株式会社 | 半導体装置の製造方法 |

| US5231038A (en) * | 1989-04-04 | 1993-07-27 | Mitsubishi Denki Kabushiki Kaisha | Method of producing field effect transistor |

| US4946547A (en) * | 1989-10-13 | 1990-08-07 | Cree Research, Inc. | Method of preparing silicon carbide surfaces for crystal growth |

| US5053348A (en) * | 1989-12-01 | 1991-10-01 | Hughes Aircraft Company | Fabrication of self-aligned, t-gate hemt |

| US5196358A (en) | 1989-12-29 | 1993-03-23 | The United States Of America As Represented By The Secretary Of The Navy | Method of manufacturing InP junction FETS and junction HEMTS using dual implantation and double nitride layers |

| JPH03292744A (ja) * | 1990-01-24 | 1991-12-24 | Toshiba Corp | 化合物半導体装置およびその製造方法 |

| US5210051A (en) * | 1990-03-27 | 1993-05-11 | Cree Research, Inc. | High efficiency light emitting diodes from bipolar gallium nitride |

| US5172197A (en) * | 1990-04-11 | 1992-12-15 | Hughes Aircraft Company | Hemt structure with passivated donor layer |

| US5292501A (en) * | 1990-06-25 | 1994-03-08 | Degenhardt Charles R | Use of a carboxy-substituted polymer to inhibit plaque formation without tooth staining |

| US5200022A (en) * | 1990-10-03 | 1993-04-06 | Cree Research, Inc. | Method of improving mechanically prepared substrate surfaces of alpha silicon carbide for deposition of beta silicon carbide thereon and resulting product |

| JPH04167439A (ja) * | 1990-10-30 | 1992-06-15 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JPH04223342A (ja) * | 1990-12-26 | 1992-08-13 | Mitsubishi Electric Corp | 半導体装置のゲート電極とその製造方法 |

| US5192987A (en) * | 1991-05-17 | 1993-03-09 | Apa Optics, Inc. | High electron mobility transistor with GaN/Alx Ga1-x N heterojunctions |

| JP3135939B2 (ja) | 1991-06-20 | 2001-02-19 | 富士通株式会社 | Hemt型半導体装置 |

| JPH0575139A (ja) * | 1991-09-12 | 1993-03-26 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP2735718B2 (ja) * | 1991-10-29 | 1998-04-02 | 三菱電機株式会社 | 化合物半導体装置及びその製造方法 |

| JP3352712B2 (ja) * | 1991-12-18 | 2002-12-03 | 浩 天野 | 窒化ガリウム系半導体素子及びその製造方法 |

| DE69202554T2 (de) * | 1991-12-25 | 1995-10-19 | Nippon Electric Co | Tunneltransistor und dessen Herstellungsverfahren. |

| JP2978972B2 (ja) * | 1992-03-12 | 1999-11-15 | 富士通株式会社 | 半導体装置の製造方法 |

| JPH05275463A (ja) | 1992-03-30 | 1993-10-22 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| JPH05299441A (ja) * | 1992-04-24 | 1993-11-12 | Matsushita Electric Ind Co Ltd | 電界効果トランジスタの製造方法 |

| JPH05326561A (ja) * | 1992-05-22 | 1993-12-10 | Nec Corp | 電界効果トランジスタの製造方法 |

| JPH0653241A (ja) * | 1992-08-03 | 1994-02-25 | Nec Corp | 電界効果トランジスタの製造方法 |

| EP0592064B1 (en) * | 1992-08-19 | 1998-09-23 | Mitsubishi Denki Kabushiki Kaisha | Method of producing a field effect transistor |

| US5399896A (en) * | 1992-09-29 | 1995-03-21 | Mitsubishi Denki Kabushiki Kaisha | FET with a T-shaped gate of a particular structure |

| JPH06267991A (ja) * | 1993-03-12 | 1994-09-22 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JPH06275655A (ja) * | 1993-03-24 | 1994-09-30 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| DE4326714A1 (de) * | 1993-08-03 | 1995-02-09 | Mantis Ulv Spruehgeraete | Segmentrotationsdüse |

| JP2560993B2 (ja) * | 1993-09-07 | 1996-12-04 | 日本電気株式会社 | 化合物半導体装置の製造方法 |

| JPH0786310A (ja) * | 1993-09-20 | 1995-03-31 | Mitsubishi Electric Corp | 高融点金属ゲート電極の形成方法 |

| US5393993A (en) * | 1993-12-13 | 1995-02-28 | Cree Research, Inc. | Buffer structure between silicon carbide and gallium nitride and resulting semiconductor devices |

| JP3294411B2 (ja) * | 1993-12-28 | 2002-06-24 | 富士通株式会社 | 半導体装置の製造方法 |

| US5484740A (en) * | 1994-06-06 | 1996-01-16 | Motorola, Inc. | Method of manufacturing a III-V semiconductor gate structure |

| US5514605A (en) * | 1994-08-24 | 1996-05-07 | Nec Corporation | Fabrication process for compound semiconductor device |

| US5686737A (en) * | 1994-09-16 | 1997-11-11 | Cree Research, Inc. | Self-aligned field-effect transistor for high frequency applications |

| US5592501A (en) * | 1994-09-20 | 1997-01-07 | Cree Research, Inc. | Low-strain laser structures with group III nitride active layers |

| US5523589A (en) * | 1994-09-20 | 1996-06-04 | Cree Research, Inc. | Vertical geometry light emitting diode with group III nitride active layer and extended lifetime |

| US5773334A (en) * | 1994-09-26 | 1998-06-30 | Toyota Jidosha Kabushiki Kaisha | Method of manufacturing a semiconductor device |

| JP3380344B2 (ja) * | 1994-11-30 | 2003-02-24 | 富士通株式会社 | 半導体装置及びその製造方法 |

| JP3157690B2 (ja) * | 1995-01-19 | 2001-04-16 | 沖電気工業株式会社 | pn接合素子の製造方法 |

| JP2687917B2 (ja) * | 1995-02-20 | 1997-12-08 | 日本電気株式会社 | 半導体装置の製造方法 |

| US5534462A (en) * | 1995-02-24 | 1996-07-09 | Motorola, Inc. | Method for forming a plug and semiconductor device having the same |

| US5670798A (en) * | 1995-03-29 | 1997-09-23 | North Carolina State University | Integrated heterostructures of Group III-V nitride semiconductor materials including epitaxial ohmic contact non-nitride buffer layer and methods of fabricating same |

| SE9501311D0 (sv) * | 1995-04-10 | 1995-04-10 | Abb Research Ltd | Method for producing a semiconductor device having a semiconductor layer of SiC |

| US6002148A (en) * | 1995-06-30 | 1999-12-14 | Motorola, Inc. | Silicon carbide transistor and method |

| US5569943A (en) * | 1995-09-01 | 1996-10-29 | The United States Of America As Represented By The Secretary Of The Army | Field effect real space transistor |

| US5733806A (en) * | 1995-09-05 | 1998-03-31 | Motorola, Inc. | Method for forming a self-aligned semiconductor device |

| US6075262A (en) * | 1995-09-21 | 2000-06-13 | Fujitsu Limited | Semiconductor device having T-shaped gate electrode |

| JPH09129865A (ja) * | 1995-11-06 | 1997-05-16 | Mitsubishi Electric Corp | 半導体装置 |

| JPH09139494A (ja) * | 1995-11-16 | 1997-05-27 | Mitsubishi Electric Corp | 半導体装置の製造方法,及び半導体装置 |

| KR0175030B1 (ko) * | 1995-12-07 | 1999-04-01 | 김광호 | 반도체 소자의 고내열 금속 배선 구조 및 그 형성 방법 |

| KR100195269B1 (ko) * | 1995-12-22 | 1999-06-15 | 윤종용 | 액정표시장치의 제조방법 |

| JPH09186175A (ja) * | 1995-12-28 | 1997-07-15 | Sanyo Electric Co Ltd | 化合物半導体装置の製造方法 |

| US5915164A (en) * | 1995-12-28 | 1999-06-22 | U.S. Philips Corporation | Methods of making high voltage GaN-A1N based semiconductor devices |

| KR0179116B1 (ko) * | 1995-12-30 | 1999-03-20 | 구자홍 | 자가정렬형 티형 게이트 제조방법 |

| DE19600116C2 (de) * | 1996-01-03 | 2001-03-15 | Siemens Ag | Doppelheterostruktur-HEMT |

| US5710449A (en) | 1996-05-22 | 1998-01-20 | Integrated Device Technology, Inc. | Memory cell having active regions without N+ implants |

| JPH1050982A (ja) | 1996-07-31 | 1998-02-20 | Nippon Telegr & Teleph Corp <Ntt> | 半導体装置 |

| JP2891204B2 (ja) * | 1996-09-27 | 1999-05-17 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6936839B2 (en) * | 1996-10-16 | 2005-08-30 | The University Of Connecticut | Monolithic integrated circuit including a waveguide and quantum well inversion channel devices and a method of fabricating same |

| KR100571071B1 (ko) * | 1996-12-04 | 2006-06-21 | 소니 가부시끼 가이샤 | 전계효과트랜지스터및그제조방법 |

| JP2904167B2 (ja) * | 1996-12-18 | 1999-06-14 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6677619B1 (en) * | 1997-01-09 | 2004-01-13 | Nichia Chemical Industries, Ltd. | Nitride semiconductor device |

| JP3156620B2 (ja) * | 1997-02-12 | 2001-04-16 | 日本電気株式会社 | 電界効果トランジスタ及びその製造方法 |

| JP3546634B2 (ja) | 1997-03-19 | 2004-07-28 | ソニー株式会社 | 窒化物系化合物半導体の選択エッチング方法および半導体装置の製造方法 |

| US6448648B1 (en) * | 1997-03-27 | 2002-09-10 | The United States Of America As Represented By The Secretary Of The Navy | Metalization of electronic semiconductor devices |

| JP3670104B2 (ja) | 1997-03-27 | 2005-07-13 | 日世株式会社 | 殺菌済食品の製造方法 |

| JPH10335637A (ja) * | 1997-05-30 | 1998-12-18 | Sony Corp | ヘテロ接合電界効果トランジスタ |

| US6316820B1 (en) * | 1997-07-25 | 2001-11-13 | Hughes Electronics Corporation | Passivation layer and process for semiconductor devices |

| JPH1154527A (ja) * | 1997-07-30 | 1999-02-26 | Fujitsu Ltd | 電界効果トランジスタおよびその製造方法 |

| US6159861A (en) * | 1997-08-28 | 2000-12-12 | Nec Corporation | Method of manufacturing semiconductor device |

| US6242327B1 (en) * | 1997-09-19 | 2001-06-05 | Fujitsu Limited | Compound semiconductor device having a reduced source resistance |

| US6201262B1 (en) * | 1997-10-07 | 2001-03-13 | Cree, Inc. | Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlay structure |

| JP3372470B2 (ja) * | 1998-01-20 | 2003-02-04 | シャープ株式会社 | 窒化物系iii−v族化合物半導体装置 |

| WO1999040618A1 (en) * | 1998-02-09 | 1999-08-12 | Koninklijke Philips Electronics N.V. | Process of manufacturing a semiconductor device including a buried channel field effect transistor |

| US6150680A (en) * | 1998-03-05 | 2000-11-21 | Welch Allyn, Inc. | Field effect semiconductor device having dipole barrier |

| JPH11261053A (ja) | 1998-03-09 | 1999-09-24 | Furukawa Electric Co Ltd:The | 高移動度トランジスタ |

| US6086673A (en) * | 1998-04-02 | 2000-07-11 | Massachusetts Institute Of Technology | Process for producing high-quality III-V nitride substrates |

| JP3534624B2 (ja) * | 1998-05-01 | 2004-06-07 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| KR100262940B1 (ko) * | 1998-05-29 | 2000-09-01 | 이계철 | 절연막 리프트 오프를 이용한 화합물 반도체 소자 제조 방법 |

| JP3385981B2 (ja) | 1998-06-01 | 2003-03-10 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US6316793B1 (en) * | 1998-06-12 | 2001-11-13 | Cree, Inc. | Nitride based transistors on semi-insulating silicon carbide substrates |

| JP3416532B2 (ja) * | 1998-06-15 | 2003-06-16 | 富士通カンタムデバイス株式会社 | 化合物半導体装置及びその製造方法 |

| JP2000196029A (ja) * | 1998-12-28 | 2000-07-14 | Sony Corp | 半導体装置とその製造方法 |

| JP3209270B2 (ja) * | 1999-01-29 | 2001-09-17 | 日本電気株式会社 | ヘテロ接合電界効果トランジスタ |

| JP2000277724A (ja) | 1999-03-26 | 2000-10-06 | Nagoya Kogyo Univ | 電界効果トランジスタとそれを備えた半導体装置及びその製造方法 |

| US6518637B1 (en) * | 1999-04-08 | 2003-02-11 | Wayne State University | Cubic (zinc-blende) aluminum nitride |

| US6218680B1 (en) * | 1999-05-18 | 2001-04-17 | Cree, Inc. | Semi-insulating silicon carbide without vanadium domination |

| JP2000349280A (ja) | 1999-06-03 | 2000-12-15 | Nec Corp | 半導体装置及びその製造方法並びに半導体基板構造 |

| JP4584379B2 (ja) * | 1999-07-16 | 2010-11-17 | 三菱電機株式会社 | 半導体装置の製造方法 |

| US6077733A (en) * | 1999-09-03 | 2000-06-20 | Taiwan Semiconductor Manufacturing Company | Method of manufacturing self-aligned T-shaped gate through dual damascene |

| US6639255B2 (en) * | 1999-12-08 | 2003-10-28 | Matsushita Electric Industrial Co., Ltd. | GaN-based HFET having a surface-leakage reducing cap layer |

| JP4592938B2 (ja) | 1999-12-08 | 2010-12-08 | パナソニック株式会社 | 半導体装置 |

| JP3393602B2 (ja) * | 2000-01-13 | 2003-04-07 | 松下電器産業株式会社 | 半導体装置 |

| JP3362723B2 (ja) * | 2000-01-26 | 2003-01-07 | 日本電気株式会社 | 電界効果型トランジスタの製造方法 |

| US6586781B2 (en) * | 2000-02-04 | 2003-07-01 | Cree Lighting Company | Group III nitride based FETs and HEMTs with reduced trapping and method for producing the same |

| JP4667556B2 (ja) * | 2000-02-18 | 2011-04-13 | 古河電気工業株式会社 | 縦型GaN系電界効果トランジスタ、バイポーラトランジスタと縦型GaN系電界効果トランジスタの製造方法 |

| US6447604B1 (en) | 2000-03-13 | 2002-09-10 | Advanced Technology Materials, Inc. | Method for achieving improved epitaxy quality (surface texture and defect density) on free-standing (aluminum, indium, gallium) nitride ((al,in,ga)n) substrates for opto-electronic and electronic devices |

| US6498111B1 (en) | 2000-08-23 | 2002-12-24 | Cree Lighting Company | Fabrication of semiconductor materials and devices with controlled electrical conductivity |

| JP4751498B2 (ja) * | 2000-03-30 | 2011-08-17 | 富士通株式会社 | 半導体三端子装置 |

| US6475889B1 (en) * | 2000-04-11 | 2002-11-05 | Cree, Inc. | Method of forming vias in silicon carbide and resulting devices and circuits |

| US6521961B1 (en) * | 2000-04-28 | 2003-02-18 | Motorola, Inc. | Semiconductor device using a barrier layer between the gate electrode and substrate and method therefor |

| JP4022708B2 (ja) * | 2000-06-29 | 2007-12-19 | 日本電気株式会社 | 半導体装置 |

| US6515316B1 (en) * | 2000-07-14 | 2003-02-04 | Trw Inc. | Partially relaxed channel HEMT device |

| JP2002076023A (ja) | 2000-09-01 | 2002-03-15 | Nec Corp | 半導体装置 |

| JP2002124663A (ja) * | 2000-10-13 | 2002-04-26 | Murata Mfg Co Ltd | ヘテロ接合電界効果トランジスタ |

| TWI288435B (en) * | 2000-11-21 | 2007-10-11 | Matsushita Electric Ind Co Ltd | Semiconductor device and equipment for communication system |

| JP2002170949A (ja) | 2000-12-01 | 2002-06-14 | Matsushita Electric Ind Co Ltd | 電界効果トランジスタ |

| US6548333B2 (en) * | 2000-12-01 | 2003-04-15 | Cree, Inc. | Aluminum gallium nitride/gallium nitride high electron mobility transistors having a gate contact on a gallium nitride based cap segment |

| JP3428962B2 (ja) * | 2000-12-19 | 2003-07-22 | 古河電気工業株式会社 | GaN系高移動度トランジスタ |

| TW466768B (en) * | 2000-12-30 | 2001-12-01 | Nat Science Council | An In0.34Al0.66As0.85Sb0.15/InP HFET utilizing InP channels |

| US6593193B2 (en) * | 2001-02-27 | 2003-07-15 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device and method for fabricating the same |

| JP3501284B2 (ja) * | 2001-03-30 | 2004-03-02 | 富士通カンタムデバイス株式会社 | 半導体装置の製造方法 |

| US6849882B2 (en) | 2001-05-11 | 2005-02-01 | Cree Inc. | Group-III nitride based high electron mobility transistor (HEMT) with barrier/spacer layer |

| JP2003023015A (ja) | 2001-07-06 | 2003-01-24 | Mitsubishi Electric Corp | GaAs系半導体電界効果トランジスタ |

| US6646293B2 (en) * | 2001-07-18 | 2003-11-11 | Motorola, Inc. | Structure for fabricating high electron mobility transistors utilizing the formation of complaint substrates |

| US6853018B2 (en) * | 2001-07-19 | 2005-02-08 | Sony Corporation | Semiconductor device having a channel layer, first semiconductor layer, second semiconductor layer, and a conductive impurity region |

| JP2005527102A (ja) * | 2001-07-24 | 2005-09-08 | クリー インコーポレイテッド | 高電子移動度トランジスタ及びその製造方法 |

| US6734111B2 (en) | 2001-08-09 | 2004-05-11 | Comlase Ab | Method to GaAs based lasers and a GaAs based laser |

| JP2003086608A (ja) * | 2001-09-14 | 2003-03-20 | Toshiba Corp | 電界効果トランジスタ及びその製造方法 |

| JP2003209124A (ja) * | 2001-11-06 | 2003-07-25 | Sony Corp | 電界効果半導体素子の製造方法及び電界効果半導体素子 |

| US7030428B2 (en) | 2001-12-03 | 2006-04-18 | Cree, Inc. | Strain balanced nitride heterojunction transistors |

| JP2003197646A (ja) * | 2001-12-27 | 2003-07-11 | Shin Etsu Handotai Co Ltd | 電界効果トランジスタ |

| KR100438895B1 (ko) * | 2001-12-28 | 2004-07-02 | 한국전자통신연구원 | 고전자 이동도 트랜지스터 전력 소자 및 그 제조 방법 |

| JP3733420B2 (ja) * | 2002-03-01 | 2006-01-11 | 独立行政法人産業技術総合研究所 | 窒化物半導体材料を用いたヘテロ接合電界効果型トランジスタ |

| JP3705431B2 (ja) * | 2002-03-28 | 2005-10-12 | ユーディナデバイス株式会社 | 半導体装置及びその製造方法 |

| DE10304722A1 (de) * | 2002-05-11 | 2004-08-19 | United Monolithic Semiconductors Gmbh | Verfahren zur Herstellung eines Halbleiterbauelements |

| JP3986887B2 (ja) | 2002-05-17 | 2007-10-03 | 松下電器産業株式会社 | 半導体装置 |

| US6852615B2 (en) * | 2002-06-10 | 2005-02-08 | Hrl Laboratories, Llc | Ohmic contacts for high electron mobility transistors and a method of making the same |

| US6893947B2 (en) * | 2002-06-25 | 2005-05-17 | Freescale Semiconductor, Inc. | Advanced RF enhancement-mode FETs with improved gate properties |

| US6982204B2 (en) | 2002-07-16 | 2006-01-03 | Cree, Inc. | Nitride-based transistors and methods of fabrication thereof using non-etched contact recesses |

| US6740535B2 (en) * | 2002-07-29 | 2004-05-25 | International Business Machines Corporation | Enhanced T-gate structure for modulation doped field effect transistors |

| US20040021152A1 (en) * | 2002-08-05 | 2004-02-05 | Chanh Nguyen | Ga/A1GaN Heterostructure Field Effect Transistor with dielectric recessed gate |

| US6897137B2 (en) * | 2002-08-05 | 2005-05-24 | Hrl Laboratories, Llc | Process for fabricating ultra-low contact resistances in GaN-based devices |

| US6884704B2 (en) * | 2002-08-05 | 2005-04-26 | Hrl Laboratories, Llc | Ohmic metal contact and channel protection in GaN devices using an encapsulation layer |

| JP4385205B2 (ja) * | 2002-12-16 | 2009-12-16 | 日本電気株式会社 | 電界効果トランジスタ |

| US8089097B2 (en) * | 2002-12-27 | 2012-01-03 | Momentive Performance Materials Inc. | Homoepitaxial gallium-nitride-based electronic devices and method for producing same |

| JP4385206B2 (ja) * | 2003-01-07 | 2009-12-16 | 日本電気株式会社 | 電界効果トランジスタ |

| JP4179539B2 (ja) | 2003-01-15 | 2008-11-12 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| JP4746825B2 (ja) | 2003-05-15 | 2011-08-10 | 富士通株式会社 | 化合物半導体装置 |

| US7501669B2 (en) * | 2003-09-09 | 2009-03-10 | Cree, Inc. | Wide bandgap transistor devices with field plates |

| US7052942B1 (en) | 2003-09-19 | 2006-05-30 | Rf Micro Devices, Inc. | Surface passivation of GaN devices in epitaxial growth chamber |

| US6867078B1 (en) * | 2003-11-19 | 2005-03-15 | Freescale Semiconductor, Inc. | Method for forming a microwave field effect transistor with high operating voltage |