JP6190015B2 - 表示装置、表示モジュール及び電子機器 - Google Patents

表示装置、表示モジュール及び電子機器 Download PDFInfo

- Publication number

- JP6190015B2 JP6190015B2 JP2016150972A JP2016150972A JP6190015B2 JP 6190015 B2 JP6190015 B2 JP 6190015B2 JP 2016150972 A JP2016150972 A JP 2016150972A JP 2016150972 A JP2016150972 A JP 2016150972A JP 6190015 B2 JP6190015 B2 JP 6190015B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- source

- drain

- electrically connected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0231—Manufacture or treatment of multiple TFTs using masks, e.g. half-tone masks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/11—OLEDs or polymer light-emitting diodes [PLED] characterised by the electroluminescent [EL] layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/10—Deposition of organic active material

- H10K71/16—Deposition of organic active material using physical vapour deposition [PVD], e.g. vacuum deposition or sputtering

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Geometry (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Optics & Photonics (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

- Control Of El Displays (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

程度の半導体薄膜により構成される薄膜トランジスタが注目されている。薄膜トランジス

タは、IC(Integrated Circuit)及び電気光学装置を始めとした電

子デバイスに広く応用されている。薄膜トランジスタは、特に液晶表示装置又はEL(E

lectro Luminescence)表示装置等に代表される、画像表示装置のス

イッチング素子として開発が急がれている。

一方の電極と、該電極とともにEL層を挟持する他方の電極と、の間に電圧が印加される

ことにより、EL層に電流が流れて発光層が発光する。この発光が表示パターンとして観

察者に認識される。なお、ここで、アクティブマトリクス型EL表示装置とは、マトリク

ス状に配置された画素をスイッチング素子により駆動することによって、画面上に表示パ

ターンが形成される方式を採用したEL表示装置をいう。

高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型EL表示

装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求

められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられ

る。

スタが用いられている。薄膜トランジスタの作製において、フォトリソグラフィに用いる

フォトマスクの枚数を削減することは、工程の簡略化のために重要である。例えばフォト

マスクが一枚増加すると、レジスト塗布、プリベーク、露光、現像、ポストベーク等の工

程と、その前後の工程において、被膜の形成及びエッチング工程、更にはレジスト剥離、

洗浄及び乾燥工程等が必要になる。そのため、作製工程に使用するフォトマスクが一枚増

加するだけで、工程数が大幅に増加する。そのため、作製工程におけるフォトマスクを低

減するために、数多くの技術開発がなされている。

ト型と、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型に大別され

る。ボトムゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数

は、トップゲート型薄膜トランジスタの作製工程において使用されるフォトマスクの枚数

よりも少ないことが知られている。ボトムゲート型薄膜トランジスタは、3枚のフォトマ

スクにより作製されることが一般的である。

はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが

多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、歩留ま

りの低下等が懸念されていた。また、薄膜トランジスタの電気的特性を犠牲にせざるを得

ないことも多い。

段として、多階調マスク(ハーフトーンマスク又はグレートーンマスクと呼ばれるもの)

を用いた技術が広く知られている。多階調マスクを用いて作製工程を低減する技術として

、例えば特許文献1が挙げられる。

合であっても、少なくとも2枚のフォトマスクが必要であり、これ以上フォトマスクの枚

数を低減することは困難である。このうち1枚は、ゲート電極層のパターニングのために

用いられている。

に使用することなく薄膜トランジスタが作製可能な、新しい手法を提供することを課題と

する。すなわち、複雑な技術を用いる必要がなく、かつ1枚のフォトマスクでも作成可能

な、薄膜トランジスタの作製方法が開示される。

も少なくすることができる。

る。本発明の一態様は、EL表示装置の作製において、複雑な技術を用いることなく、フ

ォトリソグラフィ法に用いるフォトマスクの枚数を従来よりも少なくすることを課題とす

る。そして、EL表示装置の作製工程を簡略にすることを本発明の一態様の課題とする。

電膜上に絶縁膜、半導体膜、不純物半導体膜及び第2の導電膜をこの順に積層した薄膜積

層体と、を形成し、第1のエッチングにより前記第1の導電膜を露出させつつ、少なくと

も前記薄膜積層体のパターンを形成し、第2のエッチングにより第1の導電膜のパターン

を形成する。ここで、第2のエッチングは、第1の導電膜がサイドエッチングされる条件

により行う。

いが、異方性の高いエッチング法(物理的エッチング)により行うことが好ましい。第1

のエッチングに異方性の高いエッチング法を用いることで、パターンの加工精度を向上さ

せることができる。なお、第1のエッチングをドライエッチングにより行う場合には、一

の工程にて行うことが可能であるが、第1のエッチングをウエットエッチングにより行う

場合には、複数の工程により第1のエッチングを行う。従って、第1のエッチングには、

ドライエッチングを用いることが好ましい。

が、等方性のエッチングが支配的なエッチング法(化学的エッチング)により行うことが

好ましい。第2のエッチングに等方性のエッチングが支配的なエッチング法(化学的エッ

チング)を用いることで、第1の導電膜をサイドエッチングすることができる。従って、

第2のエッチングには、ウエットエッチングを用いることが好ましい。

め、第1の導電膜は前記パターン形成された薄膜積層体よりも内側に後退する。従って、

第2のエッチング後の第1の導電膜の側面は、パターン形成された薄膜積層体の側面より

も内側に存在する。更には、パターン形成された第1の導電膜の側面とパターン形成され

た薄膜積層体の側面との間隔は概ね等しいものとなる。

形成する金属配線の上面レイアウトをいう。

を有するレジストマスクを用いて前記ゲート電極層より上層に設けられるソース電極及び

ドレイン電極層を形成した薄膜トランジスタを有するEL表示装置の作製方法である。

の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて、前記第1の絶縁膜、前記半導体膜、前記不純物半導

体膜及び前記第2の導電膜に第1のエッチングを行って前記第1の導電膜の少なくとも表

面を露出させ、前記第1の導電膜の一部に第2のエッチングを行って前記第1の絶縁膜の

幅よりも幅が狭くなるようにゲート電極層を形成し、前記第2の導電膜上に第2のレジス

トマスクを形成し、前記第2のレジストマスクを用いて前記第2の導電膜、前記不純物半

導体膜及び前記半導体膜の一部に第3のエッチングを行ってソース電極及びドレイン電極

層、ソース領域及びドレイン領域層並びに半導体層を形成することで薄膜トランジスタを

形成し、前記第2のレジストマスクを除去し、前記薄膜トランジスタを覆って第2の絶縁

膜を形成し、前記ソース電極及びドレイン電極層の一部を露出するように前記第2の絶縁

膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に第1の画素電極を選択的に形

成し、前記第1の画素電極上にEL層を形成し、前記EL層上に第2の画素電極を形成す

ることを特徴とするEL表示装置の作製方法である。

の導電膜を順に積層して形成し、前記第2の導電膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて、前記第1の絶縁膜、前記半導体膜、前記不純物半導

体膜及び前記第2の導電膜に第1のエッチングを行って前記第1の導電膜の少なくとも表

面を露出させ、前記第2の導電膜上に第2のレジストマスクを形成し、前記第2のレジス

トマスクを形成後に前記第1の導電膜の一部に第2のエッチングを行って前記第1の絶縁

膜の幅よりも幅が狭くなるようにゲート電極層を形成し、前記第2のレジストマスクを用

いて前記第2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチング

を行ってソース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層

を形成することで薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記

薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の

一部を露出するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶

縁膜上に第1の画素電極を選択的に形成し、前記第1の画素電極上にEL層を形成し、前

記EL層上に第2の画素電極を形成することを特徴とするEL表示装置の作製方法である

。

の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマス

クを形成し、前記第1のレジストマスクを用いて、前記第1の絶縁膜、前記半導体膜、前

記不純物半導体膜及び前記第2の導電膜に第1のエッチングを行って前記第1の導電膜の

少なくとも表面を露出させ、前記第1の導電膜の一部に第2のエッチングを行って前記第

1の絶縁膜の幅よりも幅が狭くなるようにゲート電極層を形成し、前記第1のレジストマ

スクを後退させることで前記第1のレジストマスクの凹部と重畳する前記第2の導電膜を

露出させつつ第2のレジストマスクを形成し、前記第2のレジストマスクを用いて前記第

2の導電膜、前記不純物半導体膜及び前記半導体膜の一部に第3のエッチングを行ってソ

ース電極及びドレイン電極層、ソース領域及びドレイン領域層並びに半導体層を形成する

ことで薄膜トランジスタを形成し、前記第2のレジストマスクを除去し、前記薄膜トラン

ジスタを覆って第2の絶縁膜を形成し、前記ソース電極及びドレイン電極層の一部を露出

するように前記第2の絶縁膜に開口部を形成し、前記開口部及び前記第2の絶縁膜上に第

1の画素電極を選択的に形成し、前記第1の画素電極上にEL層を形成し、前記EL層上

に第2の画素電極を形成することを特徴とするEL表示装置の作製方法である。

の導電膜を順に積層して形成し、前記第2の導電膜上に凹部を有する第1のレジストマス

クを形成し、前記第1のレジストマスクを用いて、前記第1の絶縁膜、前記半導体膜、前

記不純物半導体膜及び前記第2の導電膜に第1のエッチングを行って前記第1の導電膜の

少なくとも表面を露出させ、前記第1のレジストマスクを後退させることで前記第1のレ

ジストマスクの凹部と重畳する前記第2の導電膜を露出させつつ第2のレジストマスクを

形成し、前記第2のレジストマスクを形成後に前記第1の導電膜の一部に第2のエッチン

グを行って前記第1の絶縁膜の幅よりも幅が狭くなるようにゲート電極層を形成し、前記

第2のレジストマスクを用いて前記第2の導電膜、前記不純物半導体膜及び前記半導体膜

の一部に第3のエッチングを行ってソース電極及びドレイン電極層、ソース領域及びドレ

イン領域層並びに半導体層を形成することで薄膜トランジスタを形成し、前記第2のレジ

ストマスクを除去し、前記薄膜トランジスタを覆って第2の絶縁膜を形成し、前記ソース

電極及びドレイン電極層の一部を露出するように前記第2の絶縁膜に開口部を形成し、前

記開口部及び前記第2の絶縁膜上に第1の画素電極を選択的に形成し、前記第1の画素電

極上にEL層を形成し、前記EL層上に第2の画素電極を形成することを特徴とするEL

表示装置の作製方法である。

記第1のレジストマスクは多階調マスクを用いて形成することが好ましい。多階調マスク

を用いることで、簡略な工程で凹部を有するレジストマスクを形成することができる。

素子領域が形成され、前記第2のエッチングによって前記素子領域の側面から概ね等しい

距離だけ内側にゲート電極層の側面を形成することができる。

いずれかにおいて、前記第1のエッチングはドライエッチングにより行い、前記第2のエ

ッチングはウエットエッチングにより行うことが好ましい。第1のエッチングによる加工

は高精度に行うことが好ましく、第2のエッチングによる加工はサイドエッチングを伴う

必要がある。高精度な加工を行うためにはドライエッチングが好ましく、また、ウエット

エッチングは化学反応を利用するためドライエッチングよりもサイドエッチングが生じや

すいためである。

ッタリング法により形成した絶縁膜と、スピンコート法により形成した絶縁膜と、を積層

して形成することが好ましい。特に好ましくは窒化シリコン膜をCVD法又はスパッタリ

ング法により形成し、有機樹脂膜をスピンコート法により形成する。第2の絶縁膜をこの

ように形成することで、薄膜トランジスタの電気的特性に影響を及ぼしうる不純物元素等

から薄膜トランジスタを保護し、且つ画素電極の被形成面の平坦性を向上させて歩留まり

の低下を防止することができる。

ート電極層を覆うゲート絶縁膜を有し、前記ゲート絶縁膜上に半導体層を有し、前記半導

体層上にソース領域及びドレイン領域を有し、前記ソース領域及びドレイン領域上にソー

ス電極及びドレイン電極を有し、前記ゲート電極層の側面に接して空洞が設けられている

ものである。空洞が設けられることによってゲート電極端部近傍を低誘電率化(low−

k化)できる。

は、レジストマスク等により所望の形状にパターン形成されたものをいう。しかし、積層

膜の各層については、膜と層を特に区別することなく用いることがある。

」が極力生じない条件により行うことが好ましい。

度によって当該膜が膜としての形態を保ち、且つ当該膜に求められる機能及び特性を保つ

ことができることをいう。

ゲート配線は、ゲート電極層により形成される。また、ゲート配線は走査線と呼ばれるこ

とがある。

接続される配線をいう。ソース配線は、ソース電極及びドレイン電極層により形成される

。また、ソース配線は信号線と呼ばれることがある。

製工程数を大幅に削減することができ、該薄膜トランジスタはEL表示装置に適用できる

ため、EL表示装置の作製工程数を大幅に削減することができる。

調マスク)を用いて薄膜トランジスタを作製することも可能である。従って、EL表示装

置の作製工程数を大幅に削減することができる。

ストリフロー及びリフトオフ法等の複雑な工程を経る必要がない。そのため、歩留まりを

低下させずにEL表示装置の作製工程数を大幅に削減することができる。

ざるを得ないことも少なくなかったが、本発明の一態様では、薄膜トランジスタの電気的

特性を維持しつつ、薄膜トランジスタの作製工程数を大幅に削減することができる。その

ため、EL表示装置の表示品質等を犠牲にすることなく、EL表示装置の作製工程数を大

幅に削減することができる。

なお、本発明の一態様である薄膜トランジスタは、ゲート電極層端部に接して空洞を有す

るため、ゲート電極とドレイン電極との間に生じるリーク電流が小さいものとなる。

は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態

および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、

本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図

面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通

して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さ

ない場合がある。また、絶縁膜は上面図には表わさないものとする。

本実施の形態では、薄膜トランジスタの作製方法及び該薄膜トランジスタがマトリクス

状に配置されたEL表示装置の作製方法の一例について、図1乃至図16を参照して説明

する。

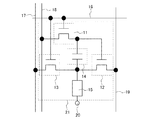

示装置)の画素回路としては、様々なものが検討されている。本実施の形態では、単純な

画素回路の一例を、図1に示し、この画素回路を適用した画素構造の作製方法について説

明する。ただし、本実施の形態において、EL表示装置の画素回路は図1に示す構成に限

定されるものではない。

第2のトランジスタ12、第3のトランジスタ13、容量素子14及び発光素子15を有

する。第1乃至第3のトランジスタはn型トランジスタである。第1のトランジスタ11

のゲート電極は、ゲート配線16に接続され、ソース電極及びドレイン電極の一方(第1

の電極とする。)は、ソース配線18に接続され、ソース電極及びドレイン電極の他方(

第2の電極とする。)は、第2のトランジスタ12のゲート電極、及び容量素子14の一

方の電極(第1の電極とする。)に接続されている。容量素子14の他方の電極(第2の

電極とする。)は、第2のトランジスタ12のソース電極及びドレイン電極の一方(第1

の電極とする。)、第3のトランジスタ13のソース電極及びドレイン電極の一方(第1

の電極とする。)、並びに発光素子15の一方の電極(第1の電極とする。)に接続され

ている。第2のトランジスタ12のソース電極及びドレイン電極の他方(第2の電極とす

る。)は、第2の電源線19に接続されている。第3のトランジスタ13のソース電極及

びドレイン電極の他方(第2の電極とする。)は、第1の電源線17に接続され、ゲート

電極はゲート配線16に接続されている。発光素子15の他方の電極(第2の電極とする

。)は、共通電極20に接続されている。なお、第1の電源線17と第2の電源線19の

電位は異なるものとする。

13がオンすると、第2のトランジスタ12の第1の電極、発光素子15の第1の電極、

及び容量素子14の第2の電極の電位が、第1の電源線17の電位(V17)と等しくな

る。ここで、第1の電源線17の電位(V17)は一定とするため、第2のトランジスタ

12の第1の電極等の電位は一定(V17)である。

ス配線18からの信号の電位(V18)が第1のトランジスタ11を介して第2のトラン

ジスタ12のゲート電極に入力される。このとき、第2の電源線19の電位(V19)が

第1の電源線17の電位(V17)よりも高ければVgs=V18−V17となる。そし

て、Vgsが第2のトランジスタ12のしきい値電圧よりも大きければ、第2のトランジ

スタ12はオンする。

電位(V18)を変化させること(例えば、2値)で、第2のトランジスタ12のオンと

オフとを制御することができる。つまり、発光素子15が有するEL層に、電圧を印加す

るかしないかを制御することができる。

位(V18)を変化させることで、発光素子15に流れる電流量を制御することができる

。

5に電圧を印加するかしないかを制御することができ、発光素子15の発光状態と非発光

状態とを制御することができる。このような駆動方法は、例えば、デジタル時間階調駆動

に用いることができる。デジタル時間階調駆動は、1フレームを複数のサブフレームに分

割し、各サブフレームにおいて発光素子15の発光状態と非発光状態とを制御する駆動方

法である。また、第2のトランジスタ12を飽和領域で動作させる場合、発光素子15に

流れる電流量を制御することができ、発光素子15の輝度を調整することができる。

る。

画素電極まで形成した完成図である。図7乃至図9は、図2乃至図6に示すA−A’にお

ける断面図である。図10乃至図12は、図2乃至図6に示すB−B’における断面図で

ある。図13乃至図15は、図2乃至図6に示すC−C’における断面図である。

純物半導体膜108及び第2の導電膜110を形成する。これらの膜は、単層で形成して

もよいし、複数の膜を積層した積層膜であってもよい。

る。本実施の形態においては、ガラス基板を用いる。

タン、モリブデン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、ニ

オブ若しくはスカンジウム等の金属材料又はこれらを主成分とする合金材料等の導電性材

料を用いて形成することができる。ただし、後の工程(第1の絶縁膜104の形成等)に

耐えうる程度の耐熱性は必要であり、後の工程(第2の導電膜110のエッチング等)で

食刻又は腐食されない材料を選択することを要する。この限りにおいて、第1の導電膜1

02は特定の材料に限定されるものではない。

プラズマCVD法等を含む)等により形成することができる。ただし、特定の方法に限定

されるものではない。

シリコンの酸化膜、窒化膜、酸化窒化膜又は窒化酸化膜等を用いて形成することができる

。ただし、第1の導電膜102と同様に、耐熱性が必要であり、後の工程で食刻又は腐食

されない材料を選択することを要する。この限りにおいて、第1の絶縁膜104は特定の

材料に限定されるものではない。

含む)又はスパッタリング法等により形成することができるが、特定の方法に限定される

ものではない。

スにより形成される非晶質シリコン等を用いて形成することができる。ただし、第1の導

電膜102等と同様に、耐熱性が必要であり、後の工程にて食刻又は腐食されない材料を

選択することを要する。この限りにおいて、半導体膜106は特定の材料に限定されるも

のではない。従って、ゲルマニウム等を用いても良い。

)又はスパッタリング法等により形成することができる。ただし、特定の方法に限定され

るものではない。

しい。結晶性半導体膜としては、多結晶半導体膜又は微結晶半導体膜等が挙げられる。

をいう。多結晶半導体膜は、例えば熱結晶化法又はレーザ結晶化法により形成される。こ

こで、熱結晶化法とは、基板上に非晶質半導体膜を形成し、該基板を加熱することで非晶

質半導体を結晶化する結晶化法をいう。また、レーザ結晶化法とは、基板上に非晶質半導

体膜を形成し、該非晶質半導体膜に対してレーザを照射して非晶質半導体を結晶化する結

晶化法をいう。または、ニッケル等の結晶化促進元素を添加して結晶化する結晶化法を用

いても良い。結晶化促進元素を添加して結晶化する場合には、該半導体膜に対してレーザ

照射を行うことが好ましい。

S(Low Temperature Poly Silicon)と、より高温で結晶

化を行うHTPS(High Temperature Poly Silicon)に

分類される。

いい、膜の全面が結晶粒のみによって構成されるもの、または結晶粒間に非晶質半導体が

介在するものを含む。微結晶半導体膜の形成方法としては、結晶核を形成して該結晶核を

成長させる方法、非晶質半導体膜を形成して該非晶質半導体膜に接して絶縁膜と金属膜と

を形成し、該金属膜に対してレーザを照射することで該金属膜に発生した熱により非晶質

半導体を結晶化させる方法等を用いればよい。ただし、非晶質半導体膜に対して熱結晶化

法又はレーザ結晶化法を用いて形成した結晶性半導体膜は含まないものとする。

た積層膜を用いると、EL表示装置の画素回路が有するトランジスタを高速に動作させる

ことができる。ここで、結晶性半導体膜としては、多結晶半導体(LTPS及びHTPS

を含む)膜を適用しても良いし、微結晶半導体膜を適用しても良い。

化されることを防止することができる。また、耐圧を向上させ、オフ電流を低下させるこ

とができる。

晶性については特に限定されない。

電性を付与する不純物元素が添加された半導体材料ガス等により形成される。本実施の形

態ではn型の薄膜トランジスタを設けるため、例えば、フォスフィン(化学式:PH3)

を含むシランガスにより形成される、リンを含むシリコン膜により設ければよい。ただし

、第1の導電膜102等と同様に、耐熱性が必要であり、後の工程で食刻又は腐食されな

い材料を選択することを要する。この限りにおいて、不純物半導体膜108は、特定の材

料に限定されるものではない。なお、不純物半導体膜108の結晶性についても特に限定

されるものではない。また、半導体膜106により形成される半導体層の一部に、ドーピ

ング等によりオーミック接触可能な領域を設ける場合などには、不純物半導体膜108を

設ける必要がない。

する不純物元素として、ヒ素等を用いてもよく、不純物半導体膜108の形成に用いるシ

ランガスにはアルシン(化学式:AsH3)を所望の濃度で含ませればよい。

D法等を含む)等により行うことができる。ただし、特定の方法に限定されるものではな

い。

って、第1の導電膜102とは異なる材料により形成する。ここで、「異なる材料」とは

、主成分が異なる材料をいう。具体的には、後に説明する第2のエッチングによりエッチ

ングされにくい材料を選択すればよい。また、第1の導電膜102等と同様に、耐熱性が

必要であり、後の工程で食刻又は腐食されない材料を選択することを要する。従って、こ

の限りにおいて、第2の導電膜110は特定の材料に限定されるものではない。

プラズマCVD法等を含む)等により形成することができる。ただし、特定の方法に限定

されるものではない。

物半導体膜108及び第2の導電膜110に対して求められる耐熱性は、第1の導電膜1

02が最も高く、以下前記した順に続き、第2の導電膜110が最も低い。例えば、半導

体膜106が水素を含む非晶質半導体膜である場合には、約300℃以上とすることで半

導体膜中の水素が脱離し、電気的特性が変化する。そのため、例えば半導体膜106を形

成した後の工程では300℃を超えない温度とすることが好ましい。

図10(A)、図13(A)を参照)。ここで、第1のレジストマスク112は凹部又は

凸部を有するレジストマスクであることが好ましい。換言すると、厚さの異なる複数の領

域(ここでは、二の領域)からなるレジストマスクともいうことができる。第1のレジス

トマスク112において、厚い領域を第1のレジストマスク112の凸部と呼び、薄い領

域を第1のレジストマスク112の凹部と呼ぶこととする。ただし、これに限定されず、

凹部又は凸部を有さないレジストマスクを用いてもよい。

域には凸部が形成され、ソース電極及びドレイン電極層を有さず半導体層が露出して形成

される領域には凹部が形成されている。

ここで、多階調マスクについて図16を参照して以下に説明する。

、露光領域、半露光領域及び未露光領域の3段階の光量で露光を行うものをいう。多階調

マスクを用いることで、一度の露光及び現像工程によって、複数(代表的には二種類)の

厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いる

ことで、フォトマスクの枚数を削減することができる。

16(A−1)にはグレートーンマスク140を示し、図16(B−1)にはハーフトー

ンマスク145を示す。

遮光膜により形成された遮光部142、及び遮光膜のパターンにより設けられた回折格子

部143で構成されている。

ドット又はメッシュ等を有することで、光の透過量を制御する。なお、回折格子部143

に設けられるスリット、ドット又はメッシュは周期的なものであってもよいし、非周期的

なものであってもよい。

回折格子部143を構成する遮光膜は、金属膜を用いて形成すればよく、好ましくはクロ

ム又は酸化クロム等により設けられる。

すように、遮光部142に重畳する領域における透光率は0%となり、遮光部142又は

回折格子部143が設けられていない領域における透光率は100%となる。また、回折

格子部143における透光率は、概ね10〜70%の範囲であり、回折格子のスリット、

ドット又はメッシュの間隔等により調整可能である。

半透光膜により形成された半透光部147、及び遮光膜により形成された遮光部148で

構成されている。

膜を用いて形成することができる。遮光部148は、グレートーンマスクの遮光膜と同様

の金属膜を用いて形成すればよく、好ましくはクロム又は酸化クロム等により設けられる

。

すように、遮光部148に重畳する領域における透光率は0%となり、遮光部148又は

半透光部147が設けられていない領域における透光率は100%となる。また、半透光

部147における透光率は、概ね10〜70%の範囲であり、形成する材料の種類又は形

成する膜厚等により、調整可能である。

ジストマスク112を形成することができる。

成してもよい。また、上記したように、第1のレジストマスクが凹部又は凸部を有さない

レジストマスクであってもよい。

の絶縁膜104、半導体膜106、不純物半導体膜108及び第2の導電膜110をエッ

チングによりパターニングし、薄膜積層体114を形成する(図2、図7(B)、図10

(B)、図13(B)を参照)。このとき、少なくとも第1の導電膜102の表面を露出

させることが好ましい。このエッチング工程を第1のエッチングとよぶ。第1のエッチン

グは、ドライエッチング又はウエットエッチングを用いればよい。なお、第1のエッチン

グをドライエッチングにより行う場合には一の工程にて行うことが可能であるが、第1の

エッチングをウエットエッチングにより行う場合には複数の工程により第1のエッチング

を行うと良い。被エッチング膜の種類によってエッチングレートが異なり、一の工程にて

行うことが困難だからである。

2ガスとCF4ガスとO2ガスの混合ガス中でエッチングを行い、次に、Cl2ガスのみ

を用いてエッチングを行い、最後に、CHF3ガスのみを用いてエッチングを行えばよい

。

の導電膜102をエッチングによりパターニングし、ゲート電極層116を形成する(図

3、図7(C)、図10(C)、図13(C)を参照)。このエッチング工程を第2のエ

ッチングとよぶ。

の一方の電極、及び支持部を構成している。ゲート電極層116Aと表記する場合には、

ゲート配線、第1のトランジスタ11のゲート電極、及び第3のトランジスタ13のゲー

ト電極を構成する電極層を指す。ゲート電極層116Bと表記する場合には、第2のトラ

ンジスタ12のゲート電極、及び容量素子14の一方の電極を構成する電極層を指す。ゲ

ート電極層116Cと表記する場合には、支持部を構成する電極層を指す。そして、これ

らを総括してゲート電極層116と呼ぶ。

が、薄膜積層体114の側面より内側に形成されるエッチング条件により行う。換言する

と、ゲート電極層116の側面が、薄膜積層体114の底面に接して形成されるようにエ

ッチングを行う(A−A’断面においてゲート電極層116の幅が薄膜積層体114の幅

より小さくなるようにエッチングを行う)。更には、第2の導電膜110に対するエッチ

ングレートが小さく、且つ第1の導電膜102に対するエッチングレートが大きい条件に

より行う。換言すると、第2の導電膜110に対する第1の導電膜102のエッチング選

択比が大きい条件により行う。このような条件により第2のエッチングを行うことで、ゲ

ート電極層116を形成することができる。

っても良い。ゲート電極層116の側面の形状は、第2のエッチングにおいて用いる薬液

等の条件によって決められるものである。

102に対するエッチングレートが大きい条件」、又は「第2の導電膜110に対する第

1の導電膜102のエッチング選択比が大きい条件」とは、以下の第1の要件及び第2の

要件を満たすものをいう。

116の必要な箇所とは、図3乃至図6に点線で示される領域をいう。すなわち、第2の

エッチング後に、ゲート電極層116がゲート配線、トランジスタが有するゲート電極、

及び容量素子が有する一の電極を構成するように残存することが必要である。ゲート電極

層がゲート配線を構成するためには、これらの配線が断線しないように第2のエッチング

を行う必要がある。図3及び図7に示されるように、薄膜積層体114の側面から間隔d

1だけ内側にゲート電極層116の側面が形成されることが好ましく、間隔d1は実施者

がレイアウトに従って適宜設定すればよい。

ソース電極及びドレイン電極層120により構成されるソース配線及び電源線の最小幅d

2が適切なものとなることである(図6を参照)。第2のエッチングによりソース電極及

びドレイン電極層120がエッチングされるとソース配線及び電源線の最小幅d2が小さ

くなり、ソース配線及び電源線の電流密度が過大となり、電気的特性が低下するためであ

る。そのため、第2のエッチングは、第1の導電膜102のエッチングレートが過大にな

らず、且つ第2の導電膜110のエッチングレートが可能な限り小さい条件で行う。

及び電源線の最小幅d2はソース配線及び電源線と重畳する半導体層の最小幅d4により

決まり、ソース配線及び電源線の最小幅d2を大きくするためには半導体層の最小幅d4

を大きくせねばならず、隣接するゲート配線とを絶縁させることが困難になるためである

。半導体層の最小幅d4は、前記した間隔d1の概ね2倍よりも小さくする。換言すると

、間隔d1は半導体層の最小幅d4の約半分よりも大きくする。

ト電極層を素子毎に分離するために必要な箇所に適宜設ければよい。第2のエッチングに

より、半導体層の幅をd4とした箇所と重畳する部分にはゲート電極層116が残存しな

いパターンを形成することができる。

の電極の幅はソース配線及び電源線の最小幅d2とすることが好ましい。

は非常に重要である。第2のエッチングが第1の導電膜102のサイドエッチングを伴う

ことによって、ゲート電極層116により構成される、隣接するゲート配線間のみならず

、画素回路内の素子の接続を所望のものとするようにパターンの形成をすることができる

ためである。

被エッチング膜の下地膜の面に垂直な方向)のみならず、厚さ方向に対して垂直な方向(

基板面に平行な方向又は被エッチング膜の下地膜の面に平行な方向)にも被エッチング膜

が削られるエッチングをいう。サイドエッチングされた被エッチング膜の端部は、被エッ

チング膜に対するエッチングガス又はエッチングに用いる薬液のエッチングレートによっ

て様々な形状となるように形成されるが、端部が曲面となるように形成されることが多い

。

能する。支持部を有することで、ゲート電極層より上に形成されるゲート絶縁膜等の膜剥

がれを防止することができる。更には支持部を設けることで、第2のエッチングによりゲ

ート電極層116に接して形成される、空洞の領域が必要以上に広くなることを防止でき

る。なお、支持部を設けることで、薄膜積層体114が自重によって破壊され、又は破損

することをも防止することができ、歩留まりが向上するため好ましい。ただし、支持部を

有する形態に限定されず、支持部を設けなくとも良い。

しい。

アルミニウム又はモリブデンを形成し、第2の導電膜110としてチタン又はタングステ

ンを形成し、エッチングには硝酸、酢酸及びリン酸を含む薬液を用いればよい。または、

第1の導電膜102としてモリブデンを形成し、第2の導電膜110としてチタン、アル

ミニウム又はタングステンを形成し、エッチングには過酸化水素水を含む薬液を用いれば

よい。

電膜102としてネオジムを添加したアルミニウム上にモリブデンを形成した積層膜を形

成し、第2の導電膜110としてタングステンを形成し、エッチングには硝酸を2%、酢

酸を10%、リン酸を72%含む薬液を用いる。このような組成の薬液を用いることで、

第2の導電膜110がエッチングされることなく、第1の導電膜102がエッチングされ

る。なお、第1の導電膜102に添加したネオジムは、アルミニウムの低抵抗化とヒロッ

ク防止を目的として添加されたものである。

。これは、ゲート電極層116を形成する第2のエッチングが概略等方的に進行するため

に、ゲート電極層116の側面と薄膜積層体114の側面との間隔d1が概略等しくなる

ようにエッチングされるためである。

、第2のレジストマスク118を形成する。第1のレジストマスク112を後退させて、

第2のレジストマスク118を形成する手段としては、例えば酸素プラズマを用いたアッ

シングが挙げられる。しかし、第1のレジストマスク112を後退させて第2のレジスト

マスク118を形成する手段はこれに限定されるものではない。第2のレジストマスク1

18が形成される領域は、第1のレジストマスク112の凸部の領域と概略一致する。な

お、ここでは第2のエッチングの後に第2のレジストマスク118を形成する場合につい

て説明したが、これに限定されず、第2のレジストマスク118を形成した後に第2のエ

ッチングを行ってもよい。

フォトマスクを用いて第2のレジストマスク118を別途形成すればよい。

110をエッチングし、ソース電極及びドレイン電極層120を形成する(図4、図8(

D)、図11(D)、図14(D)を参照)。ここでエッチング条件は、第2の導電膜1

10以外の膜に対する食刻及び腐食が生じず、又は生じ難い条件を選択する。特に、ゲー

ト電極層116の食刻及び腐食が生じず、又は生じ難い条件により行うことが重要である

。

はドレイン電極、ソース配線、電源線、容量素子の他方の電極、及び薄膜トランジスタと

発光素子の一の電極とを接続する電極を構成している。ソース電極及びドレイン電極層1

20Aと表記する場合には、ソース配線18、及び第1のトランジスタ11のソース電極

及びドレイン電極の一方を構成する電極層を指す。ソース電極及びドレイン電極層120

Bと表記する場合には、第1の電源線17を構成する電極層を指す。ソース電極及びドレ

イン電極層120Cと表記する場合には、第1のトランジスタ11のソース電極及びドレ

イン電極の他方、及び第1のトランジスタ11と画素電極とを接続する電極を構成する電

極層を指す。ソース電極及びドレイン電極層120Dと表記する場合には、第2の電源線

19、及び第2のトランジスタ12のソース電極及びドレイン電極の一方を構成する電極

層を指す。ソース電極及びドレイン電極層120Eと表記する場合には、第3のトランジ

スタ13のソース電極及びドレイン電極の一方を構成する電極層を指す。ソース電極及び

ドレイン電極層120Fと表記する場合には、容量素子14の他方の電極、第2のトラン

ジスタ12のソース電極及びドレイン電極の他方、第3のトランジスタ13のソース電極

及びドレイン電極の他方、並びにこれらから発光素子の一の電極に接続される電極を構成

する電極層を指す。

畳するものを指し、第2のレジストマスク118Bは、ソース電極及びドレイン電極層1

20Bと重畳するものを指し、第2のレジストマスク118Cは、ソース電極及びドレイ

ン電極層120Cと重畳するものを指し、第2のレジストマスク118Dは、ソース電極

及びドレイン電極層120Dと重畳するものを指し、第2のレジストマスク118Eは、

ソース電極及びドレイン電極層120Eと重畳するものを指し、第2のレジストマスク1

18Fは、ソース電極及びドレイン電極層120Fと重畳するものを指す。

ング又はドライエッチングのどちらを用いても良い。

バックチャネル部)をエッチングして、ソース領域及びドレイン領域122、半導体層1

24を形成する(図5、図8(E)、図11(E)、図14(E)を参照)。ここでエッ

チング条件は、不純物半導体膜108及び半導体膜106以外の膜に対する食刻及び腐食

が生じず、又は生じ難い条件を選択する。特に、ゲート電極層116の食刻及び腐食が生

じず、又は生じ難い条件により行うことが重要である。

ックチャネル部)のエッチングはドライエッチング又はウエットエッチングにより行うこ

とができる。

図8(F)、図11(F)、図14(F)を参照)。上記説明したように、薄膜トランジ

スタを一枚のフォトマスク(多階調マスク)により作製することができる。

チングとよぶ。第3のエッチングは、上記説明したように、複数の段階に分けて行っても

良いし、一括して行っても良い。

、第2の絶縁膜は、第1の保護膜126のみで形成しても良いが、ここでは第1の保護膜

126と第2の保護膜128により形成する(図9(G)、図12(G)、図15(G)

を参照)。第1の保護膜126は、第1の絶縁膜104と同様に形成すればよいが、好ま

しくは水素を含有する窒化シリコン又は水素を含有する酸化窒化シリコンにより形成し、

半導体層に金属等の不純物が侵入して拡散し、汚染されることを防止する。

8の表面を概略平坦にすることで、第2の保護膜128上に形成される第1の画素電極層

132の断切れ等を防止することができるためである。従って、ここで「概略平坦」とは

、上記目的を達成しうる程度のものであればよく、高い平坦性が要求されるわけではない

。

等により、スピンコーティング法等により形成することができる。ただし、これらの材料

又は形成方法に限定されるものではない。

と、これを覆って水分の侵入や放出を防止する保護膜を積層して形成したものであること

が好ましい。水分の侵入や放出を防止する保護膜は、具体的には、窒化シリコン、酸化窒

化シリコン、酸化窒化アルミニウム又は窒化アルミニウム等により形成されていることが

好ましい。形成方法としてはスパッタリング法を用いることが好ましい。

H)、図12(H)、図15(H)を参照)。第1の開口部130は、ソース電極及びド

レイン電極層の少なくとも表面に達するように形成する。第2の開口部131は、ゲート

電極層の少なくとも表面に達するように形成する。第1の開口部130及び第2の開口部

131の形成方法は、特定の方法に限定されず、第1の開口部130の径などに応じて実

施者が適宜選択すればよい。例えば、フォトリソグラフィ法によりドライエッチングを行

うことで第1の開口部130及び第2の開口部131を形成することができる。

るものであり、図6に示すように必要な箇所に複数個設ける。第1の開口部130Aはソ

ース電極及びドレイン電極層120C上に設け、第1の開口部130Bはソース電極及び

ドレイン電極層120B上に設け、第1の開口部130Cはソース電極及びドレイン電極

層120E上に設け、第1の開口部130Dはソース電極及びドレイン電極層120F上

に設ける。

なわち、第2の開口部131は第2の絶縁膜のみならず、第1の絶縁膜104、半導体層

124の所望の箇所も除去して設けられるものである。

用することになる。

2(H)、図15(H)を参照)。第1の画素電極層132は、第1の開口部130又は

第2の開口部131を介してソース電極及びドレイン電極層120又はゲート電極層11

6に接続されるように形成する。具体的には、第1の画素電極層132は、第1の開口部

130Aを介してソース電極及びドレイン電極層120Cに接続され、第1の開口部13

0Bを介してソース電極及びドレイン電極層120Bに接続され、第1の開口部130C

を介してソース電極及びドレイン電極層120Eに接続され、第1の開口部130Dを介

してソース電極及びドレイン電極層120Fに接続され、第2の開口部131を介してゲ

ート電極層116Bに接続されるように形成される。また、第1の画素電極層132につ

いても単層で形成しても良いし、複数の膜を積層した積層膜としてもよい。

トマスクを一枚使用することになる。

32は、陰極となる材料により形成することが好ましい。陰極となる材料には、仕事関数

が小さい材料、例えば、Ca、Al、MgAg、AlLi等が挙げられる。

する。隔壁133は開口部を有し、該開口部において第1の画素電極層132が露出され

るように形成する。隔壁133は、有機樹脂膜、無機絶縁膜又は有機ポリシロキサンを用

いて形成する。具体的には、ポリイミド、ポリアミド、ポリイミドアミド、アクリル、ベ

ンゾシクロブテン系樹脂を用いて形成するとよい。特に感光性の材料を用いて、第1の画

素電極層132上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成され

る傾斜面となるように形成することが好ましい。

34を形成する。EL層134は、単数の層で構成されていても、複数の層が積層されて

形成された積層膜により構成されていても良い。EL層134は、少なくとも発光層を有

する。発光層はホール輸送層を介して第2の画素電極層135と接続されることが好まし

い。

形成する。第2の画素電極層135は図1における共通電極20に相当する。第2の画素

電極層135は、透光性を有する導電性材料により形成することができる。ここで、透光

性を有する導電性材料としては、インジウム錫酸化物(以下、ITOという)、酸化タン

グステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化

チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛

酸化物、又は酸化シリコンを添加したインジウム錫酸化物等が挙げられる。透光性を有す

る導電性材料の膜の形成はスパッタリング法又はCVD法等により行えばよいが、特定の

方法に限定されるものではない。また、第2の画素電極層135についても単層で形成し

ても良いし、複数の膜を積層した積層膜としてもよい。

て、第1の画素電極層132とEL層134と第2の画素電極層135が重なり合うこと

で、発光素子136が形成される。発光素子136は、図1における発光素子15に相当

する。この後、発光素子136に酸素、水素、水分、二酸化炭素等が侵入しないように、

第2の画素電極層135及び隔壁133上に第3の保護膜137を形成することが好まし

い(図示しない)。第3の保護膜137は、第2の保護膜128と同様に材料により水分

の侵入や放出を防止する機能を有するものを選択する。窒化シリコン、酸化窒化シリコン

、酸化窒化アルミニウム又は窒化アルミニウム等により形成されていることが好ましい。

更に、第3の保護膜を覆って窒化シリコン膜又はDLC膜等を有することが好ましい。

脂フィルム等)又はカバー材によって、更なるパッケージング(封入)をすることが好ま

しい。保護フィルム及びカバー材は、ガス透過性が低く、脱ガスの少ない材料により設け

ることが好ましい。

まで形成することができる(図9(I)、図12(I)、図15(I)を参照)。しかし

、本実施の形態のEL表示装置は、上記の説明に限定されず、下面射出構造(ボトムエミ

ッション)型EL表示装置、または両面射出構造(デュアルエミッション)型EL表示装

置に適用することも可能である。下面射出構造及び両面射出構造では、第1の画素電極層

132に透光性を有する導電性材料を用いればよい。なお、第1の画素電極層132を陽

極となる材料により形成する場合には、第1の画素電極層132は、例えば、ITOによ

り形成することができる。第1の画素電極層132をこのような構造にすることで、発光

を取り出す効率を向上させることができ、ボトムエミッション型のEL表示装置を作製す

ることができる。そして、EL層134を覆うように、陰極となる材料により第2の画素

電極層135を形成するとよい。第2の画素電極層135は図1における共通電極20に

相当する。陰極となる材料には、仕事関数が小さい材料、例えば、Ca、Al、MgAg

、AlLi等が挙げられる。なお、EL層134及び第2の画素電極層135は、マスク

を介した蒸着により形成することが好ましい。従って、第2の画素電極層135は、蒸着

により形成することが可能な材料により形成するとよい。なお、EL表示装置の画素を図

1に示す回路により構成する場合には、第1の画素電極層132を陽極とし、第2の画素

電極層135を陰極とすることが好ましい。

光を妨げず、劣化等を防止することができる膜であればよい。

画素電極層132Aを形成してもよい。この場合には、まず、第1の画素電極層132B

及び第1の画素電極層132Cに相当する導電層のみを形成し、該導電層上に第1の開口

部130Dを有する絶縁膜を形成し、第1の開口部130Dを介してソース電極及びドレ

イン電極層120Fに接続されるように第1の画素電極層132Aを形成すればよい。画

素回路が形成されている領域をも含むように第1の画素電極層132Aを形成することで

、発光領域を拡大することができ、より高精細な表示が可能となる。

EL素子を用いることも可能である。

17乃至図19を参照して説明する。

ゲート配線側の端子接続部及びソース配線側の端子接続部の上面図及び断面図を示す。

から延伸したゲート配線及びソース配線の上面図を示す。なお、第1の電源線17及び第

2の電源線19についてもソース配線18と同様であってよい。また、隔壁133及び第

2の画素電極層135は、図17には図示していない。

側の端子接続部における断面図を示す。図18では、ゲート電極層116のみが露出され

ている。このゲート電極層116が露出された領域に、端子部が接続される。

配線側の端子接続部における断面図の例を示す。図19のY−Y’において、ゲート電極

層116と、ソース電極及びドレイン電極層120は第1の画素電極層132(少なくと

も、第1の画素電極層132B又は第1の画素電極層132Cと同一の層)を介して接続

されている。図19にはゲート電極層116と、ソース電極及びドレイン電極層120の

様々な接続形態を示している。ここで、EL表示装置の端子接続部には、これらのいずれ

を用いても良いし、図19に示すもの以外の接続形態を用いても良い。ソース電極及びド

レイン電極層120をゲート電極層116に接続させることで、端子の接続部の高さを概

ね等しくすることができる。

の開口部を設けるのみならず、一の端子に対して複数の開口部を設けても良い。一の端子

に対して複数の開口部を設けることで、開口部を形成するエッチング工程が不十分である

等の理由で開口部が良好に形成されなかったとしても、他の開口部により電気的接続を実

現することができる。更には、全ての開口部が問題なく形成された場合であっても、接触

面積を広くすることができるため、コンタクト抵抗を低減することができ、好ましい。

により除去され、ゲート電極層116と、ソース電極及びドレイン電極層120とが露出

され、この露出された領域に第1の画素電極層132(少なくとも、第1の画素電極層1

32B又は第1の画素電極層132Cと同一の層)を形成することで電気的な接続を実現

している。図17に示す上面図は、図19(A)の上面図に相当する。

域の形成は、第1の開口部130及び第2の開口部131の形成と同時に行うことができ

る。

Aが設けられ、第1の保護膜126及び第2の保護膜128の端部がエッチング等により

除去されることで、ゲート電極層116と、ソース電極及びドレイン電極層120とが露

出され、この露出された領域に第1の画素電極層132(少なくとも、第1の画素電極層

132B又は第1の画素電極層132Cと同一の層)を形成することで電気的な接続を実

現している。

は、第1の開口部130及び第2の開口部131の形成と同時に行うことができる。

B及び第4の開口部161が設けられることで、ゲート電極層116と、ソース電極及び

ドレイン電極層120とが露出され、この露出された領域に第1の画素電極層132(少

なくとも、第1の画素電極層132B又は第1の画素電極層132Cと同一の層)を形成

することで電気的な接続を実現している。ここで、図19(A)及び(B)と同様に、第

1の保護膜126及び第2の保護膜128の端部はエッチング等により除去されているが

、この領域は端子の接続部として用いられる。

6が露出された領域の形成は、第1の開口部130及び第2の開口部131の形成と同時

に行うことができる。

極層120に達するように設けられ、第4の開口部161は、第2の開口部131と同様

にゲート電極層116に達するように設けられている。そして、図18及び図19には隔

壁133及び第2の画素電極層135を示しているが、これらは端子接続部には設けられ

ていなくてもよい。

FPC(Flexible Printed Circuit)が接続される。FPCは

ポリイミド等の有機樹脂フィルム上に導電膜により配線が形成されており、異方性導電性

ペースト(Anisotropic Conductive Paste。以下、ACP

という)を介して入力端子と接続される。一般的なACPは、接着剤として機能するペー

ストと、金等がメッキされた数十〜数百μm径の導電性表面を有する粒子と、により構成

されている。ペースト中に混入された粒子が入力端子上の導電層と、FPCに形成された

配線に接続された端子上の導電層と、に接触することで、電気的な接続を実現することが

できる。

L表示装置の作製工程数を大幅に削減することができる。

薄膜トランジスタの作製工程数を大幅に削減することができる。そのため、複雑な工程を

経ることなく、EL表示装置の作製工程数を大幅に削減することができる。

幅に削減することができる。

本実施の形態は、実施の形態1にて説明した方法により作製した表示パネル又は表示装

置を表示部として組み込んだ電子機器について図20乃至図22を参照して説明する。こ

のような電子機器としては、例えば、ビデオカメラ若しくはデジタルカメラ等のカメラ、

ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジ

ェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ

、携帯電話または電子書籍等)が挙げられる。それらの一例を図20に示す。

20(A)に示すテレビジョン装置を完成させることができる。実施の形態1にて説明し

た作製方法を適用した表示パネルにより主画面223が形成され、その他付属設備として

スピーカ部229、操作スイッチ等が備えられている。

た表示用パネル222が組み込まれ、受信機225により一般のテレビ放送の受信をはじ

め、モデム224を介して有線又は無線による通信ネットワークに接続することにより一

方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通

信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別

体のリモコン操作機226により行うことが可能であり、このリモコン操作機226にも

、出力する情報を表示する表示部227が設けられていても良い。

で形成し、チャネルや音量などを表示する構成が付加されていても良い。

画素部251が形成されている。信号線駆動回路252と走査線駆動回路253は、表示

パネルにCOG方式により実装されていても良い。

号のうち、映像信号を増幅する映像信号増幅回路255と、そこから出力される信号を赤

、緑、青の各色に対応した色信号に変換する映像信号処理回路256と、その映像信号を

ドライバICの入力仕様に変換するためのコントロール回路257等を有している。コン

トロール回路257は、走査線側と信号線側にそれぞれ信号を出力する。デジタル駆動す

る場合には、信号線側に信号分割回路258を設け、入力デジタル信号を整数個に分割し

て供給する構成としても良い。

、その出力は音声信号処理回路260を経てスピーカ263に供給される。制御回路26

1は受信局(受信周波数)、音量の制御情報を入力部262から受け、チューナ254及

び音声信号処理回路260に信号を送出する。

ルコンピュータのモニタをはじめ、鉄道の駅や空港等における情報表示盤、又は街頭にお

ける広告表示盤等の大面積の表示媒体にも適用することができる。そのため、本発明の一

態様であるEL表示装置の作製方法を適用することで、これらの表示媒体の生産性を向上

させることができる。

した表示パネル又は表示装置を用いることで、テレビ装置の生産性を高めることができる

。

有する。表示部232に、実施の形態1で説明した表示装置の作製方法を適用した表示パ

ネル又は表示装置を用いることで、コンピュータの生産性を高めることができる。

22(C)が2つの筐体をスライドさせたときの正面図である。携帯電話200は、筐体

201及び筐体202二つの筐体で構成されている。携帯電話200は、携帯電話と携帯

情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデ

ータ処理が可能な所謂スマートフォンである。

は、表示部203、スピーカ204、マイクロフォン205、操作キー206、ポインテ

ィングデバイス207、表面カメラ用レンズ208、外部接続端子ジャック209及びイ

ヤホン端子210等を備え、筐体202においては、キーボード211、外部メモリスロ

ット212、裏面カメラ213、ライト214等により構成されている。また、アンテナ

は筐体201に内蔵されている。

等を内蔵していてもよい。

とが可能であり、スライドさせることで図22(C)のように展開する。表示部203に

は、実施の形態1で説明した表示装置の作製方法を適用した表示パネル又は表示装置を組

み込むことが可能である。表示部203と表面カメラ用レンズ208を同一の面に備えて

いるため、テレビ電話としての使用が可能である。また、表示部203をファインダーと

して用いることで、裏面カメラ213及びライト214で静止画及び動画の撮影が可能で

ある。

録装置(録音装置)又は音声再生装置として使用することができる。また、操作キー20

6により、電話の発着信操作、電子メール等の簡単な情報入力操作、表示部に表示する画

面のスクロール操作、表示部に表示する情報の選択等を行うカーソルの移動操作等が可能

である。

ード211を用いると便利である。更に、重なり合った筐体201と筐体202(図22

(A))をスライドさせることで、図22(C)のように展開させることができる。携帯

情報端末として使用する場合には、キーボード211及びポインティングデバイス207

を用いて、円滑な操作が可能である。外部接続端子ジャック209はACアダプタ及びU

SBケーブル等の各種ケーブルと接続可能であり、充電及びパーソナルコンピュータ等と

のデータ通信が可能である。また、外部メモリスロット212に記録媒体を挿入し、より

大量のデータ保存及び移動が可能になる。

表示部203をファインダーとして静止画及び動画の撮影が可能である。

機能、非接触ICチップ又はイヤホンジャック等を備えたものであってもよい。

タ及び表示装置の作製方法を適用して作製することができるため、これらの電子機器の生

産性を向上させることができる。

12 第2のトランジスタ

13 第3のトランジスタ

14 容量素子

15 発光素子

16 ゲート配線

17 第1の電源線

18 ソース配線

19 第2の電源線

20 共通電極

21 画素

100 基板

102 第1の導電膜

104 第1の絶縁膜

106 半導体膜

108 不純物半導体膜

110 第2の導電膜

112 第1のレジストマスク

114 薄膜積層体

115 エッチングされた第1の導電膜

116 ゲート電極層

116A ゲート電極層

116B ゲート電極層

116C ゲート電極層

116D ゲート電極層

118 第2のレジストマスク

118A 第2のレジストマスク

118B 第2のレジストマスク

118C 第2のレジストマスク

118D 第2のレジストマスク

118E 第2のレジストマスク

118F 第2のレジストマスク

120 ソース電極及びドレイン電極層

120A ソース電極及びドレイン電極層

120B ソース電極及びドレイン電極層

120C ソース電極及びドレイン電極層

120D ソース電極及びドレイン電極層

120E ソース電極及びドレイン電極層

120F ソース電極及びドレイン電極層

122 ソース領域及びドレイン領域

122A ソース領域及びドレイン領域

122B ソース領域及びドレイン領域

122C ソース領域及びドレイン領域

122D ソース領域及びドレイン領域

124 半導体層

126 第1の保護膜

128 第2の保護膜

130 第1の開口部

130A 第1の開口部

130B 第1の開口部

130C 第1の開口部

130D 第1の開口部

131 第2の開口部

132 第1の画素電極層

132A 第1の画素電極層

132B 第1の画素電極層

132C 第1の画素電極層

133 隔壁

134 EL層

135 第2の画素電極層

136 発光素子

137 第3の保護膜

140 グレートーンマスク

141 基板

142 遮光部

143 回折格子部

145 ハーフトーンマスク

146 基板

147 半透光部

148 遮光部

160 第3の開口部

160A 第3の開口部

160B 第3の開口部

161 第4の開口部

170 第1のレジストマスク

171 第2のレジストマスク

200 携帯電話

201 筐体

202 筐体

203 表示部

204 スピーカ

205 マイクロフォン

206 操作キー

207 ポインティングデバイス

208 表面カメラ用レンズ

209 外部接続端子ジャック

210 イヤホン端子

211 キーボード

212 外部メモリスロット

213 裏面カメラ

214 ライト

221 筐体

222 表示用パネル

223 主画面

224 モデム

225 受信機

226 リモコン操作機

227 表示部

228 サブ画面

229 スピーカ部

231 本体

232 表示部

251 画素部

252 信号線駆動回路

253 走査線駆動回路

254 チューナ

255 映像信号増幅回路

256 映像信号処理回路

257 コントロール回路

258 信号分割回路

259 音声信号増幅回路

260 音声信号処理回路

261 制御回路

262 入力部

263 スピーカ

Claims (10)

- 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、画素電極と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有することを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、画素電極と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続されることを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、画素電極と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートとなる領域を有する第2の導電層は、前記第3のトランジスタのゲートとなる領域を有することを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、画素電極と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートとなる領域を有する第2の導電層は、前記第3のトランジスタのゲートとなる領域を有し、

前記第2の導電層は、前記第1の導電層と異なる層であることを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、EL素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記EL素子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有することを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、EL素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記EL素子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続されることを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、EL素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記EL素子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートとなる領域を有する第2の導電層は、前記第3のトランジスタのゲートとなる領域を有することを特徴とする表示装置。 - 画素部を有し、

前記画素部は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、EL素子と、第1の配線と、第2の配線と、第3の配線と、を有し、

前記第1のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第2のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記EL素子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第1の導電層を介して、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1の配線は、第1の方向に沿うように設けられた領域を有し、

前記第2の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第3の配線は、前記第1の方向に沿うように設けられた領域を有し、

前記第1の導電層は、前記第1の配線と交差する領域を有し、

前記第1のトランジスタのゲートとなる領域を有する第2の導電層は、前記第3のトランジスタのゲートとなる領域を有し、

前記第2の導電層は、前記第1の導電層と異なる層であることを特徴とする表示装置。 - 請求項1乃至請求項8のいずれか一項に記載の表示装置と、

FPCと、

を有する表示モジュール。 - 請求項1乃至請求項8のいずれか一項に記載の表示装置と、

スピーカ、筐体、操作キー、又はイヤホン端子、を有する電子機器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008055024 | 2008-03-05 | ||

| JP2008055024 | 2008-03-05 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015200980A Division JP5982550B2 (ja) | 2008-03-05 | 2015-10-09 | 表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017150319A Division JP2018005239A (ja) | 2008-03-05 | 2017-08-03 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016212435A JP2016212435A (ja) | 2016-12-15 |

| JP6190015B2 true JP6190015B2 (ja) | 2017-08-30 |

Family

ID=41052679

Family Applications (11)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009049191A Expired - Fee Related JP5512988B2 (ja) | 2008-03-05 | 2009-03-03 | El表示装置の作製方法 |

| JP2013228991A Active JP5674899B2 (ja) | 2008-03-05 | 2013-11-05 | 表示装置 |

| JP2014141052A Active JP5824557B2 (ja) | 2008-03-05 | 2014-07-09 | 表示装置 |

| JP2015200980A Active JP5982550B2 (ja) | 2008-03-05 | 2015-10-09 | 表示装置 |

| JP2016150972A Active JP6190015B2 (ja) | 2008-03-05 | 2016-08-01 | 表示装置、表示モジュール及び電子機器 |

| JP2017150319A Withdrawn JP2018005239A (ja) | 2008-03-05 | 2017-08-03 | 表示装置 |

| JP2018227458A Active JP6666986B2 (ja) | 2008-03-05 | 2018-12-04 | 表示装置 |

| JP2020027919A Active JP7008095B2 (ja) | 2008-03-05 | 2020-02-21 | 表示装置 |

| JP2022001426A Active JP7225441B2 (ja) | 2008-03-05 | 2022-01-07 | El表示装置の作製方法 |

| JP2023017862A Active JP7609906B2 (ja) | 2008-03-05 | 2023-02-08 | 表示装置 |

| JP2024223728A Pending JP2025032370A (ja) | 2008-03-05 | 2024-12-19 | 表示装置 |

Family Applications Before (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009049191A Expired - Fee Related JP5512988B2 (ja) | 2008-03-05 | 2009-03-03 | El表示装置の作製方法 |

| JP2013228991A Active JP5674899B2 (ja) | 2008-03-05 | 2013-11-05 | 表示装置 |

| JP2014141052A Active JP5824557B2 (ja) | 2008-03-05 | 2014-07-09 | 表示装置 |

| JP2015200980A Active JP5982550B2 (ja) | 2008-03-05 | 2015-10-09 | 表示装置 |

Family Applications After (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017150319A Withdrawn JP2018005239A (ja) | 2008-03-05 | 2017-08-03 | 表示装置 |

| JP2018227458A Active JP6666986B2 (ja) | 2008-03-05 | 2018-12-04 | 表示装置 |

| JP2020027919A Active JP7008095B2 (ja) | 2008-03-05 | 2020-02-21 | 表示装置 |

| JP2022001426A Active JP7225441B2 (ja) | 2008-03-05 | 2022-01-07 | El表示装置の作製方法 |

| JP2023017862A Active JP7609906B2 (ja) | 2008-03-05 | 2023-02-08 | 表示装置 |

| JP2024223728A Pending JP2025032370A (ja) | 2008-03-05 | 2024-12-19 | 表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8101442B2 (ja) |

| JP (11) | JP5512988B2 (ja) |

| KR (1) | KR101519890B1 (ja) |

| CN (2) | CN101527284B (ja) |

| TW (3) | TWI486096B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7749820B2 (en) * | 2008-03-07 | 2010-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, manufacturing method thereof, display device, and manufacturing method thereof |

| US8207026B2 (en) * | 2009-01-28 | 2012-06-26 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of thin film transistor and manufacturing method of display device |

| US7989234B2 (en) | 2009-02-16 | 2011-08-02 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor and method for manufacturing display device |

| US8202769B2 (en) | 2009-03-11 | 2012-06-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5539765B2 (ja) * | 2009-03-26 | 2014-07-02 | 株式会社半導体エネルギー研究所 | トランジスタの作製方法 |

| EP2492780B1 (en) * | 2009-11-26 | 2014-07-02 | Sharp Kabushiki Kaisha | A touch panel manufacturing method, and a method for manufacturing a display device provided with a touch panel |

| KR20130044124A (ko) * | 2010-05-10 | 2013-05-02 | 파나소닉 액정 디스플레이 주식회사 | 결정성 반도체막의 제조 방법, 결정성 반도체막을 갖는 기판, 박막 트랜지스터 |

| US8766253B2 (en) * | 2010-09-10 | 2014-07-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| TWI556317B (zh) | 2010-10-07 | 2016-11-01 | 半導體能源研究所股份有限公司 | 薄膜元件、半導體裝置以及它們的製造方法 |

| US8679986B2 (en) | 2010-10-14 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing display device |

| CN103403849B (zh) * | 2011-02-28 | 2016-08-03 | 夏普株式会社 | 半导体装置及其制造方法以及显示装置 |

| JP6076038B2 (ja) | 2011-11-11 | 2017-02-08 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| JP6033071B2 (ja) * | 2011-12-23 | 2016-11-30 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR101996438B1 (ko) * | 2012-12-13 | 2019-07-05 | 삼성디스플레이 주식회사 | 표시 장치용 기판, 이를 포함한 표시 장치 및 표시 장치의 제조 방법 |

| US9096426B2 (en) * | 2013-04-05 | 2015-08-04 | The United States Of America As Represented By The Secretary Of The Army | Electronic device structure and method of making electronic devices and integrated circuits using grayscale technology and multilayer thin-film composites |

| CN104062843A (zh) | 2014-07-18 | 2014-09-24 | 深圳市华星光电技术有限公司 | 一种掩膜板、阵列基板制作方法及阵列基板 |

| CN105390551B (zh) * | 2015-10-28 | 2018-05-29 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制造方法、阵列基板、显示装置 |

| CN105789327B (zh) * | 2016-05-17 | 2019-05-03 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制备方法、阵列基板、显示装置 |

| WO2021102997A1 (zh) | 2019-11-29 | 2021-06-03 | 京东方科技集团股份有限公司 | 显示基板及其制作方法、显示装置 |

| CN115295563A (zh) * | 2022-08-25 | 2022-11-04 | 昆山国显光电有限公司 | 阵列基板及其制备方法 |

Family Cites Families (97)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56122123A (en) * | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| USRE34658E (en) * | 1980-06-30 | 1994-07-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device of non-single crystal-structure |

| JPS6484669A (en) | 1987-09-26 | 1989-03-29 | Casio Computer Co Ltd | Thin film transistor |

| JPH0311744A (ja) | 1989-06-09 | 1991-01-21 | Citizen Watch Co Ltd | 薄膜トランジスタの製造方法 |

| JPH03161938A (ja) | 1989-11-20 | 1991-07-11 | Seiko Instr Inc | 薄膜トランジスタの製造方法 |

| JPH04188770A (ja) | 1990-11-22 | 1992-07-07 | Casio Comput Co Ltd | 薄膜トランジスタ |

| JPH06194687A (ja) * | 1992-10-30 | 1994-07-15 | Nec Corp | 透過型アクティブマトリクス型液晶素子 |

| JPH07307477A (ja) | 1994-03-15 | 1995-11-21 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP3866783B2 (ja) * | 1995-07-25 | 2007-01-10 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| JP3663261B2 (ja) * | 1995-10-05 | 2005-06-22 | 株式会社東芝 | 表示装置用アレイ基板及びその製造方法 |

| DE69635239T2 (de) * | 1995-11-21 | 2006-07-06 | Samsung Electronics Co., Ltd., Suwon | Verfahren zur Herstellung einer Flüssigkristall-Anzeige |

| JPH09292633A (ja) * | 1996-02-27 | 1997-11-11 | Canon Inc | カラー液晶表示装置の製造方法 |

| JPH10198292A (ja) * | 1996-12-30 | 1998-07-31 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| CN100517424C (zh) * | 1997-08-21 | 2009-07-22 | 精工爱普生株式会社 | 显示装置 |

| JP4131297B2 (ja) * | 1997-10-24 | 2008-08-13 | エルジー ディスプレイ カンパニー リミテッド | 液晶表示装置の製造方法 |

| US6297519B1 (en) * | 1998-08-28 | 2001-10-02 | Fujitsu Limited | TFT substrate with low contact resistance and damage resistant terminals |

| US6493048B1 (en) * | 1998-10-21 | 2002-12-10 | Samsung Electronics Co., Ltd. | Thin film transistor array panel for a liquid crystal display and a method for manufacturing the same |

| US6576924B1 (en) * | 1999-02-12 | 2003-06-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having at least a pixel unit and a driver circuit unit over a same substrate |

| JP2000307118A (ja) | 1999-04-21 | 2000-11-02 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタおよびその製造方法 |

| JP2001109405A (ja) * | 1999-10-01 | 2001-04-20 | Sanyo Electric Co Ltd | El表示装置 |

| KR100669093B1 (ko) * | 1999-11-05 | 2007-01-16 | 엘지.필립스 엘시디 주식회사 | 액정표시소자의 제조방법 |

| JP3761756B2 (ja) * | 1999-12-16 | 2006-03-29 | シャープ株式会社 | 液晶表示装置およびその製造方法 |

| TW578028B (en) * | 1999-12-16 | 2004-03-01 | Sharp Kk | Liquid crystal display and manufacturing method thereof |

| KR100325079B1 (ko) * | 1999-12-22 | 2002-03-02 | 주식회사 현대 디스플레이 테크놀로지 | 고개구율 및 고투과율 액정표시장치의 제조방법 |

| JP2001188240A (ja) * | 1999-12-28 | 2001-07-10 | Sharp Corp | 透明導電膜を有する電子装置 |

| JP2001202035A (ja) * | 2000-01-18 | 2001-07-27 | Sharp Corp | 有機エレクトロルミネッセンス表示装置 |

| US7023021B2 (en) * | 2000-02-22 | 2006-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| TW521256B (en) * | 2000-05-18 | 2003-02-21 | Semiconductor Energy Lab | Electronic device and method of driving the same |

| KR100494683B1 (ko) * | 2000-05-31 | 2005-06-13 | 비오이 하이디스 테크놀로지 주식회사 | 4-마스크를 이용한 박막 트랜지스터 액정표시장치의제조시에 사용하는 할프톤 노광 공정용 포토 마스크 |

| US7223643B2 (en) * | 2000-08-11 | 2007-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| KR100496420B1 (ko) * | 2001-03-02 | 2005-06-17 | 삼성에스디아이 주식회사 | 2층구조의 소오스/드레인 전극을 갖는 박막 트랜지스터 및그의 제조방법과 이를 이용한 액티브 매트릭스형 표시소자및 그의 제조방법 |

| TW488080B (en) * | 2001-06-08 | 2002-05-21 | Au Optronics Corp | Method for producing thin film transistor |

| US6623653B2 (en) * | 2001-06-12 | 2003-09-23 | Sharp Laboratories Of America, Inc. | System and method for etching adjoining layers of silicon and indium tin oxide |

| JP4876341B2 (ja) * | 2001-07-13 | 2012-02-15 | 日本電気株式会社 | アクティブマトリクス基板及びその製造方法 |

| JP3831868B2 (ja) * | 2001-08-13 | 2006-10-11 | 大林精工株式会社 | アクティブマトリックス表示装置とその製造方法 |

| JP4485119B2 (ja) | 2001-11-13 | 2010-06-16 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2003179069A (ja) | 2001-12-12 | 2003-06-27 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ、液晶表示装置、有機エレクトロルミネッセンス素子、ならびに表示装置用基板およびその製造方法 |

| JP2003223119A (ja) * | 2002-01-30 | 2003-08-08 | Toshiba Corp | 表示装置およびその製造方法 |

| KR100789090B1 (ko) * | 2002-12-30 | 2007-12-26 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 제조방법 |

| JP3952979B2 (ja) * | 2003-03-25 | 2007-08-01 | カシオ計算機株式会社 | 表示駆動装置及び表示装置並びにその駆動制御方法 |

| US8319219B2 (en) * | 2003-07-14 | 2012-11-27 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| JP2005128040A (ja) * | 2003-10-21 | 2005-05-19 | Hitachi Displays Ltd | 表示装置 |

| KR101006439B1 (ko) * | 2003-11-12 | 2011-01-06 | 삼성전자주식회사 | 박막 트랜지스터 표시판의 제조 방법 |

| KR101012792B1 (ko) * | 2003-12-08 | 2011-02-08 | 삼성전자주식회사 | 박막 트랜지스터 표시판과 그 제조 방법 |

| KR100698062B1 (ko) * | 2004-04-01 | 2007-03-23 | 엘지.필립스 엘시디 주식회사 | 액정표시소자 및 그 제조방법 |

| TWI239651B (en) * | 2004-04-30 | 2005-09-11 | Quanta Display Inc | Manufacturing method of a thin film transistor-liquid crystal display |

| KR101086478B1 (ko) * | 2004-05-27 | 2011-11-25 | 엘지디스플레이 주식회사 | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 |

| KR101121620B1 (ko) * | 2004-06-05 | 2012-02-28 | 엘지디스플레이 주식회사 | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 |

| CN100533746C (zh) * | 2004-08-03 | 2009-08-26 | 株式会社半导体能源研究所 | 显示器件、其制造方法以及电视机 |

| JP4700317B2 (ja) | 2004-09-30 | 2011-06-15 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| KR100669752B1 (ko) * | 2004-11-10 | 2007-01-16 | 삼성에스디아이 주식회사 | 유기 박막 트랜지스터, 이의 제조 방법 및 이를 구비한평판표시장치 |

| KR20060079040A (ko) * | 2004-12-31 | 2006-07-05 | 엘지.필립스 엘시디 주식회사 | 프린지 필드 스위칭 타입의 박막 트랜지스터 기판 및 그제조 방법 |

| JP2006215275A (ja) * | 2005-02-03 | 2006-08-17 | Sony Corp | 表示装置 |

| KR20060120300A (ko) * | 2005-05-19 | 2006-11-27 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 그 제조 방법 |

| KR101100891B1 (ko) * | 2005-05-23 | 2012-01-02 | 삼성전자주식회사 | 박막트랜지스터 기판 및 이를 포함한 디스플레이장치 |

| US7608490B2 (en) * | 2005-06-02 | 2009-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7588970B2 (en) * | 2005-06-10 | 2009-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101201017B1 (ko) * | 2005-06-27 | 2012-11-13 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| KR101225440B1 (ko) * | 2005-06-30 | 2013-01-25 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| US7807516B2 (en) * | 2005-06-30 | 2010-10-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of the same |

| US7867791B2 (en) * | 2005-07-29 | 2011-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device using multiple mask layers formed through use of an exposure mask that transmits light at a plurality of intensities |

| JP4039446B2 (ja) * | 2005-08-02 | 2008-01-30 | エプソンイメージングデバイス株式会社 | 電気光学装置及び電子機器 |

| KR20070019457A (ko) * | 2005-08-12 | 2007-02-15 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 이를 포함하는 액정표시장치 |

| US7914971B2 (en) * | 2005-08-12 | 2011-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Light exposure mask and method for manufacturing semiconductor device using the same |

| JP5078246B2 (ja) * | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| US8149346B2 (en) * | 2005-10-14 | 2012-04-03 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP5105811B2 (ja) | 2005-10-14 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 表示装置 |

| TWI517378B (zh) * | 2005-10-17 | 2016-01-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TWI289360B (en) * | 2005-10-24 | 2007-11-01 | Chunghwa Picture Tubes Ltd | Thin film transistor array substrate and manufacturing method thereof |

| JP5025242B2 (ja) * | 2005-12-02 | 2012-09-12 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、モジュール、及び電子機器 |

| EP3229066A1 (en) * | 2005-12-05 | 2017-10-11 | Semiconductor Energy Laboratory Co., Ltd. | Transflective liquid crystal display with a horizontal electric field configuration |

| EP2479604B1 (en) * | 2005-12-05 | 2015-07-15 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| US7821613B2 (en) * | 2005-12-28 | 2010-10-26 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| JP2007212699A (ja) | 2006-02-09 | 2007-08-23 | Idemitsu Kosan Co Ltd | 反射型tft基板及び反射型tft基板の製造方法 |

| TWI322288B (en) * | 2006-03-07 | 2010-03-21 | Au Optronics Corp | Manufacture method of pixel array substrate |

| US8053816B2 (en) * | 2006-03-10 | 2011-11-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN100433338C (zh) * | 2006-06-23 | 2008-11-12 | 北京京东方光电科技有限公司 | 一种薄膜晶体管器件阵列基板结构及其制造方法 |

| KR20080001181A (ko) * | 2006-06-29 | 2008-01-03 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이 기판과 그 제조방법 |

| KR101295192B1 (ko) * | 2006-06-29 | 2013-08-09 | 엘지디스플레이 주식회사 | 유기전계 발광소자와 그 제조방법 |

| WO2008099528A1 (ja) | 2007-02-13 | 2008-08-21 | Sharp Kabushiki Kaisha | 表示装置、表示装置の製造方法 |

| US20100182303A1 (en) | 2007-07-30 | 2010-07-22 | Shinji Takasugi | Image display device |

| KR101296653B1 (ko) * | 2007-10-05 | 2013-08-14 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 이의 제조 방법 |

| US7824939B2 (en) * | 2007-10-23 | 2010-11-02 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing display device comprising separated and electrically connected source wiring layers |

| KR101448903B1 (ko) * | 2007-10-23 | 2014-10-13 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제작방법 |

| JP5357493B2 (ja) * | 2007-10-23 | 2013-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5427390B2 (ja) * | 2007-10-23 | 2014-02-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5380037B2 (ja) * | 2007-10-23 | 2014-01-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI355553B (en) * | 2007-10-30 | 2012-01-01 | Au Optronics Corp | Pixel structure and method for manufacturing the s |

| EP2232561A4 (en) * | 2007-12-03 | 2015-05-06 | Semiconductor Energy Lab | METHOD OF MANUFACTURING A THIN FILM TRANSISTOR AND METHOD OF MANUFACTURING A DISPLAY ARRANGEMENT |

| US8035107B2 (en) * | 2008-02-26 | 2011-10-11 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing display device |

| CN101939694B (zh) * | 2008-02-27 | 2014-01-29 | 株式会社半导体能源研究所 | 液晶显示器件及其制造方法以及电子装置 |

| US7749820B2 (en) * | 2008-03-07 | 2010-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, manufacturing method thereof, display device, and manufacturing method thereof |

| US7989275B2 (en) * | 2008-03-10 | 2011-08-02 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, manufacturing method thereof, display device, and manufacturing method thereof |

| US7883943B2 (en) * | 2008-03-11 | 2011-02-08 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor and method for manufacturing display device |

| US7985605B2 (en) * | 2008-04-17 | 2011-07-26 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and manufacturing method thereof |

| US7790483B2 (en) * | 2008-06-17 | 2010-09-07 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and manufacturing method thereof, and display device and manufacturing method thereof |

| KR101243824B1 (ko) * | 2008-09-24 | 2013-03-18 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

-

2009

- 2009-02-20 US US12/390,264 patent/US8101442B2/en not_active Expired - Fee Related

- 2009-02-26 TW TW098106187A patent/TWI486096B/zh not_active IP Right Cessation

- 2009-02-26 TW TW105143921A patent/TWI657716B/zh active

- 2009-02-26 TW TW104107395A patent/TWI622321B/zh active

- 2009-03-03 JP JP2009049191A patent/JP5512988B2/ja not_active Expired - Fee Related

- 2009-03-05 KR KR1020090018828A patent/KR101519890B1/ko not_active Expired - Fee Related

- 2009-03-05 CN CN200910128517.8A patent/CN101527284B/zh not_active Expired - Fee Related

- 2009-03-05 CN CN201410220695.4A patent/CN103987146B/zh active Active

-

2013

- 2013-11-05 JP JP2013228991A patent/JP5674899B2/ja active Active

-

2014

- 2014-07-09 JP JP2014141052A patent/JP5824557B2/ja active Active

-

2015

- 2015-10-09 JP JP2015200980A patent/JP5982550B2/ja active Active

-

2016

- 2016-08-01 JP JP2016150972A patent/JP6190015B2/ja active Active

-

2017

- 2017-08-03 JP JP2017150319A patent/JP2018005239A/ja not_active Withdrawn

-

2018

- 2018-12-04 JP JP2018227458A patent/JP6666986B2/ja active Active

-

2020

- 2020-02-21 JP JP2020027919A patent/JP7008095B2/ja active Active

-

2022

- 2022-01-07 JP JP2022001426A patent/JP7225441B2/ja active Active

-

2023

- 2023-02-08 JP JP2023017862A patent/JP7609906B2/ja active Active

-

2024

- 2024-12-19 JP JP2024223728A patent/JP2025032370A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| JP2022058527A (ja) | 2022-04-12 |

| JP5512988B2 (ja) | 2014-06-04 |

| TW201714489A (zh) | 2017-04-16 |

| JP2025032370A (ja) | 2025-03-11 |

| TW200950583A (en) | 2009-12-01 |

| TWI486096B (zh) | 2015-05-21 |

| TWI657716B (zh) | 2019-04-21 |

| US20090224249A1 (en) | 2009-09-10 |

| JP2014063179A (ja) | 2014-04-10 |

| JP2018005239A (ja) | 2018-01-11 |

| JP5674899B2 (ja) | 2015-02-25 |

| CN103987146B (zh) | 2017-04-19 |

| JP2009239272A (ja) | 2009-10-15 |

| JP2023065419A (ja) | 2023-05-12 |

| US8101442B2 (en) | 2012-01-24 |

| CN103987146A (zh) | 2014-08-13 |

| TW201524264A (zh) | 2015-06-16 |

| JP2014206753A (ja) | 2014-10-30 |

| KR20090095520A (ko) | 2009-09-09 |

| JP5982550B2 (ja) | 2016-08-31 |

| TWI622321B (zh) | 2018-04-21 |

| JP2016048378A (ja) | 2016-04-07 |

| JP7609906B2 (ja) | 2025-01-07 |

| JP5824557B2 (ja) | 2015-11-25 |

| JP7225441B2 (ja) | 2023-02-20 |

| CN101527284B (zh) | 2014-07-02 |

| CN101527284A (zh) | 2009-09-09 |

| JP7008095B2 (ja) | 2022-01-25 |

| KR101519890B1 (ko) | 2015-05-21 |

| JP2016212435A (ja) | 2016-12-15 |

| JP2019040215A (ja) | 2019-03-14 |

| JP2020096193A (ja) | 2020-06-18 |

| JP6666986B2 (ja) | 2020-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7225441B2 (ja) | El表示装置の作製方法 | |

| JP5383256B2 (ja) | 薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法 | |

| JP5371487B2 (ja) | 薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法 | |

| JP5364422B2 (ja) | 発光装置及びその作製方法 | |

| JP5396165B2 (ja) | 薄膜トランジスタの作製方法及び表示装置の作製方法 | |

| JP5530111B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP5997725B2 (ja) | 表示装置 | |

| JP2010230950A (ja) | 表示装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170704 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170803 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6190015 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |