JP5259505B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP5259505B2 JP5259505B2 JP2009152642A JP2009152642A JP5259505B2 JP 5259505 B2 JP5259505 B2 JP 5259505B2 JP 2009152642 A JP2009152642 A JP 2009152642A JP 2009152642 A JP2009152642 A JP 2009152642A JP 5259505 B2 JP5259505 B2 JP 5259505B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- word line

- node

- memory cell

- mos transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

本発明の第1の実施形態に係る半導体装置について、図1を用いて説明する。本実施形態の概要は、読み出し時において種々の電圧を発生させる2つ以上の電圧発生回路の出力端をショートさせることで、メモリセルアレイに接続されるワード線WLに転送される電圧のタイミングを揃えるものである。まず、第1の実施形態に係る半導体装置の構成について説明する。

メモリセルアレイ1は、データ保持可能な複数の不揮発性のメモリセルトランジスタMTを備えている。そしてメモリセルトランジスタMTは、例えば電荷蓄積層と制御ゲートを含む積層ゲートを備えたnチャネルMOSトランジスタである。メモリセルトランジスタMTの制御ゲートはワード線WLとして機能し、ドレインはビット線BLに電気的に接続され、ソースはソース線SLに電気的に接続されている。そして、メモリセルアレイ1は複数の不揮発性のメモリセルトランジスタMTを含んだブロックBLK0乃至BLKsを備える(sは自然数)。

次に図2を用いて、上記構成のブロックBLK0乃至BLKsにおけるメモリセルアレイ1の断面構成について説明する。図2は図1においてビット線BL方向に沿ったNANDストリング11の断面図を示している。

次に上記メモリセルトランジスタMTの閾値分布について図3を用いて説明する。図3は、横軸に閾値分布をとり、縦軸にメモリセルトランジスタMTのセル数を示したグラフである。

次に図1に戻ってロウデコーダ2について説明する。ロウデコーダ2は、ブロックデコーダ20、及びnチャネル型MOSトランジスタ21乃至23を備える。ブロックデコーダ20は、データの書き込み動作時、読み出し動作時、及び消去時において、制御部6から与えられたブロックアドレスをデコードし、その結果に基づいてブロックBLKを選択する。すなわち、ブロックデコーダ20は制御線TGを介して、選択されたメモリセルトランジスタMTが含まれるブロックBLKに対応するMOSトランジスタ21乃至23を選択し、該MOSトランジスタ21乃至23をオン状態とする。このとき、ブロックデコーダ20からは、ブロック選択信号が出力される。ブロック選択信号とは、データの読み出し、書き込み、消去など行う際に、ロウデコーダ2が複数あるメモリブロックBLK0乃至BLKsのうちいずれかを選択する信号である。またこれにより、ロウデコーダ2は、選択されたブロックBLKに対応するメモリセルアレイ1のロウ方向を選択する。つまり、ブロックデコーダ20から与えられる選択信号に基づいて、ロウデコーダ2はセレクトゲート線SGD1、SGS1、及びワード線WL0〜WL63に対し、ワード線制御回路3を介して電圧発生回路4から与えられた電圧をそれぞれ印加する。

次にワード線制御回路3について説明する。ここでは、ワード線制御回路3の構成については触れず、機能的な説明をする。ワード線制御回路3は、電圧発生回路4が生成した種々の電圧を、適切なワード線WLに割り当てた後、ロウデコーダ2を介して転送する。例えば、ワード線制御回路3は読み出し時においてワード線WL31に、該ワード線WLに接続されたメモリセルトランジスタMTの保持する読み出したいデータに応じた電圧を転送する場合、それ以外のワード線WL0乃至30及びワード線WL32乃至63にはメモリセルトランジスタMTがオン状態とされる電圧が転送される制御を行う。なお、このワード線制御回路3により、セレクトゲート線SGD1を介して、信号sgdが選択トランジスタST1のゲートに転送される。また、ワード線制御回路3により、セレクトゲート線SGS1を介して、信号sgsが選択トランジスタST2のゲートに転送される。そして、信号sgd及び信号sgsはそれぞれ‘H’レベルを電圧VDD(例えば、1.8[V])とし、‘L’レベルを0[V]とした信号である。選択トランジスタST1、ST2は、それぞれ電圧VDDによりオン状態とされる。

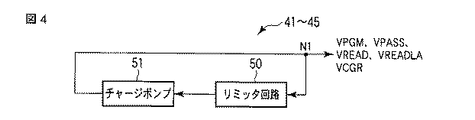

次に電圧発生回路4について説明する。図1に示すように電圧発生回路4は第1電圧発生回路41、第2電圧発生回路42、第3電圧発生回路43、第4電圧発生回路44、及び第5電圧発生回路45を備える。第1電圧発生回路41乃至第5電圧発生回路45について図4を用いて説明する。

センスアンプ5は、データの読み出し時にメモリセルトランジスタMTからビット線BLに読み出されたデータをセンスして増幅する。より具体的には、センスアンプ5は電圧VDDをビット線BLにプリチャージする。そして、センスアンプ5はビット線BLにおける電圧(または電流)をセンスする。また、データの書き込み時には、電圧発生回路4から転送された電圧VDDをビット線BLに転送する。

次に制御部6について説明する。制御部6は、特に読み出し時において、第1電圧発生回路41及び第2電圧発生回路42の出力端からそれぞれ出力される電圧が昇圧される間、該電圧の昇圧速度が揃うように、該出力端同士を短絡させる。また、制御部6はNAND型フラッシュメモリ全体の動作を制御する。すなわち、図示せぬホストから与えられた上記アドレス、及びコマンドに基づいて、データの書き込み動作、読み出し動作、及び消去動作における動作シーケンスを実行する。そして、制御部6は上記アドレス、及び動作シーケンスに基づき、ブロック選択信号/カラム選択信号を生成する。制御部6は、ブロック選択信号をロウデコーダ2に出力する。

次に、図5を用いてショート回路7及び上記説明した第1、第2電圧発生回路41、42の構成例について説明する。図5は、制御部6、ショート回路7、第1電圧発生回路41、及び第2電圧発生回路42のブロック図である。制御部6は制御ユニット60及びローカルポンプ61を備える。ローカルポンプ61は制御ユニット60から与えられるイネーブル信号EN(図中、ENと表記)に応じて、ショート回路7に‘L’または‘H’レベルの信号を出力する。そして、ローカルポンプ61は第2電圧発生回路42の出力端であるノードN3に接続される。つまり、ローカルポンプ6はノードN3の電位をリファレンス電圧として、MOSトランジスタ71に電圧を印加する。すなわち、ローカルポンプ61がMOSトランジスタ71のゲートに与える電圧の値は、ノードN3のリファレンス電圧と該MOSトランジスタ71の閾値電圧との和である。ここで、MOSトランジスタ71の閾値電圧をVth71とすると、ローカルポンプ61が出力する‘H’レベルの信号は、電圧(ノードN3の電位+Vth71)とされる。そしてこの‘H’レベルの信号により、MOSトランジスタ71がオン状態とされる。

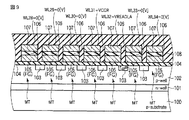

次に、上記NAND型フラッシュメモリにおける読み出し動作について図6(a)、(b)を用いて説明する。図6(a)、(b)は、図2で説明したメモリセルアレイ1の断面図において、特にメモリセルトランジスタMTに着目した図であり、N番目(Nは自然数)のワード線WLに対応するメモリセルトランジスタMTのデータを読み出そうとする様子を示している。すなわち、N番目のワード線WLが選択ワード線WLとされる場合である。

まず、選択ワード線WLNに対応するメモリセルトランジスタMTのデータを読み出す場合、該選択ワード線WLNのドレイン側に隣接するメモリセルトランジスタMTに電圧VCGRを転送する。例えば、N=31とすれば、選択ワード線WL31に隣接するワード線WL32に電圧VCGRを転送する。これにより、ワード線WL32に対応するメモリセルトランジスタMTの閾値分布を把握することが出来る。つまり、メモリセルトランジスタMTの閾値分布が、例え当初予定とする閾値分布からズレていたとしても、この読み出しステップを実行することにより、メモリセルトランジスタMTの閾値分布を把握することが出来る。つまり、電圧VCGRは、メモリセルトランジスタMTから読み出したいデータに応じた電圧とされることから、該メモリセルトランジスタMTがオン状態とされたその電圧VCGRの値によりその閾値分布が確認できる。そして、この電圧VCGRの値を以って、第2電圧発生回路が生成する電圧VREADLAの値が設定される。ここで、電圧VREADLA=電圧(VREAD±α)とすると、メモリセルトランジスタMTの閾値分布が高い場合は、電圧VREADLA=電圧(VREAD+α)であり、閾値分布が低い場合は、VREADLA=電圧(VREAD−α)とされる。

次のステップとして、該選択ワード線WL31に対応するメモリセルトランジスタMTの制御ゲート107に電圧VCGRを転送する。この際、ワード線WL31に隣接するワード線WL32には電圧VREADLAを転送し、それ以外のワード線WL0乃至WL30及びワード線WL33乃至WL63には電圧VREADを転送する。ここで、ワード線WL32に転送される電圧VREADLAは、ステップ1において該ワード線WL32に対応するメモリセルトランジスタMTの閾値分布に応じた電圧とされる。これにより、ワード線WLに接続されたメモリセルトランジスタMTがオン状態とされ、データの読み出しが図示せぬビット線BLを介してセンスアンプ5により実行される。

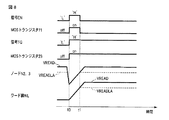

次に第2電圧発生回路42が生成する電圧VREADLAが、電圧VREADよりも大きい値である場合の、上記NAND型フラッシュメモリにおいて読み出し動作時の電圧転送動作について図7を用いて説明する。すなわち、電圧VREADLA=電圧(VREAD+α)である。図7は、ローカルポンプ61に与えられるイネーブル信号EN、MOSトランジスタ71のゲートに与えられる電位、信号TG、MOSトランジスタ23のオン・オフ状態、ノードN2、N3における電位、及びワード線WLにおける電位のタイムチャートである。また、図中におけるノードN2、3について、実線がノードN2を示し、破線がノードN3を示す。これら、電圧転送動作のタイミングは、制御部6により制御される。以下、全ての実施形態においても同様である。

図7に示すように、時刻t0以前では、信号TGが‘L’レベルであることからMOSトランジスタ23がオフ状態とされ、また更にイネーブル信号ENが‘L’レベルであることから、MOSトランジスタ71もオフ状態とされる。これによりノードN2、N3の電位はそれぞれ電圧VREAD及び電圧VREADLAで維持される。

次に時刻t0において、それまで‘L’レベルとされたイネーブル信号ENが制御ユニット60により‘H’レベルとされる。これにより、ローカルポンプ61はMOSトランジスタ71のゲートに‘H’レベルの信号を出力する。この結果、MOSトランジスタ71はオン状態とされる。換言すれば、ノードN2とノードN3とが短絡される。そして、ロウデコーダ2のブロックデコーダ20が出力する信号TGが‘H’レベルとされることによりMOSトランジスタ23がオン状態とされるため、第1電圧発生回路41及び第2電圧発生回路42にワード線WLが有する負荷が掛かる。なお、信号TGは時刻t0以降、‘H’レベルを維持する。このため、ノードN2、N3において第1、第2電圧発生回路41、42が生成する電圧VREAD及び電圧VREADLAから、それぞれ一旦、0[V]とされる。

そして、時刻t1とされると、ノードN2及びN3、並びに非選択ワード線WLの電位が電圧VREADに達する。すると制御部6はイネーブル信号ENを‘L’レベルへと切り替える。すなわち、ローカルポンプ61の出力を‘L’レベルとする。この結果、MOSトランジスタ71はオフ状態とされ、ノードN2とNノードN3とが電気的に分離される。このため、ノードN2の電位は電圧VREADとされ、非選択ワード線WLの電位も該電圧VREADで維持される。

時刻t1以降になると、第2電圧発生回路42が生成する電圧VREADLAにより、ノードN3の電位は該電圧VREADLAにまで上昇する。すなわち、電圧VREADLAが転送される非選択ワード線WLの電位は、時刻t1以降、該電圧VREADLAまで上昇する。

次に、第1電圧発生回路41が生成する電圧VREADが、電圧VREADLAよりも大きい値である場合の、NAND型フラッシュメモリの電圧転送動作について図8を用いて説明する。すなわち、電圧VREADLA=電圧(VREAD−α)である。また、上記説明した読み出し動作(その1)と同一の動作については説明を省略する。

本実施形態に係る半導体装置であると、(1)の効果を奏することができる。

(1)動作信頼性を向上することができる。

以下、本実施形態に係る効果について説明する。本実施形態に係る半導体装置であると、図5に示したように第1電圧発生回路41の出力端(ノードN2)と第2電圧発生回路42の出力端(ノードN3)とを短絡するショート回路7及びそれを時間で制御する機能を備えた制御部6を備える。

次に上記第1の実施形態の変形例に係る半導体装置について図10を用いて説明する。図10は変形例に係るNAND型フラッシュメモリの読み出し動作時における電圧転送動作を示すタイムチャートである。図10は、ローカルポンプ61に与えられるイネーブル信号EN、MOSトランジスタ71のゲートに与えられる電位、信号TG、MOSトランジスタ23のオン・オフ状態、ノードN2、N3における電位、及びワード線WLにおける電位のタイムチャートであり、特に電圧VREAD>電圧VREADLAの場合について示す。すなわち、電圧VREADLA=電圧(VREAD−α)とされる。またこれら、電圧転送動作のタイミングは、制御部6により制御される。なお、上記第1の実施形態で説明した読み出し動作と同一の動作については説明を省略する。またなお、選択ワード線WLをN=31とする。すなわち、非選択ワード線WL32に電圧VREADLAが転送され、それ以外の非選択ワード線WL0乃至WL30及び非選択ワード線WL33乃至WL63には電圧VREADが転送される。

図10に示すように、ノードN2、N3、及びワード線WLの電位が電圧VREADLAに達する前の、時刻t1において制御部6によりMOSトランジスタ71のゲートに与える信号を‘L’レベルとする。すなわち、制御ユニット60によりローカルポンプ61に与えられるイネーブル信号ENを時刻t1において‘L’レベルとする。これにより、MOSトランジスタ71はオフ状態とされ、ノードN2とノードN3とが電気的に分離される。すると、第2電圧発生回路42にとって、負荷は非選択ワード線WL32の1本とされるため、時刻t1において該電圧発生回路42が生成する電圧VREADLAの昇圧速度が上昇する。すなわち、電圧の傾きが急峻とされる。

そして、時刻t2において、ノードN3、及び非選択ワード線WL32の電位が電圧VREADLAに達する。そして、時刻t3において非選択ワード線WL0乃至WL30及び非選択ワード線WL33乃至WL63の電位は電圧VREADに達する。

変形例に係る半導体装置であると、特に電圧VREAD>電圧VREADLAの場合に下記(2)の効果を奏することが出来る。

(2)動作速度の向上が出来る。

変形例に係る半導体装置であると、制御部6はノードN3の電位が電圧VREADLAに達する前の時刻t1で、MOSトランジスタ71をオフ状態とする。これにより、ワード線WLへの円滑な電圧転送が可能となる。つまり、ノードN3の電位が電圧VREADLAに達した直後にMOSトランジスタ71をオフ状態とするものではない。このため、MOSトランジスタ71をオフ状態、すなわちノードN2とノードN3とを電気的に切り離した直後、ノードN3及びワード線WL32の電位が、電圧VREADLAからオーバーシュートしてしまうといったことを防止することが出来る。つまり、本実施形態の変形例に係る半導体装置であると、電圧VREADLAからオーバーシュートした電圧が、該電圧VREADLAに戻るまでの時間が増加してしまうことから防止することが出来る。これにより、本実施形態に係る半導体装置によれば動作速度の向上が出来、チップ全体の動作も速くなる。

次に、本発明の第2の実施形態に係る半導体装置について説明する。本実施形態に係る半導体装置は、上記第1の実施形態において電圧発生回路4が更に電圧VREADKを生成及び出力する構成を備えたものである。なお、上記第1の実施形態と同一の構成については説明を省略する。

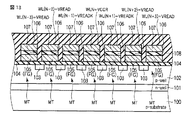

次に、上記NAND型フラッシュメモリにおいて上記電圧VCGR、電圧VREAD、電圧VREADLA、及び電圧VREADKを用いた読み出し動作について図12(a)、(b)及び図13を用いて説明する。電圧VREADKは、選択ワード線WLをN番目とすると(N−1)番目のワード線WLまたは(N−1)番目のワード線WL及び(N+1)番目のワード線WLに転送される。

<ステップ1>

まずステップ1において図12(a)に示すように、ワード線WL(N−3)乃至ワード線WL(N−2)、ワード線WL(N+2)、及びワード線WL(N+3)に電圧VREADを転送する。そして第6電圧発生回路46は、ワード線WL(N−1)に電圧VREADを転送する。

次にステップ2において、ワード線WL(N−1)に電圧VREADKを転送する。電圧VREADKはメモリセルトランジスタMTをオン状態とする電圧であり、電圧VREADLAと同様、メモリセルトランジスタMTの閾値分布に基づいてその大きさを変えることが出来る。つまり、第6電圧発生回路46のチャージポンプ50により電圧VREADKは、電圧(VREAD+β)または電圧(VREAD−β)いずれかの値をとる。なお、αとβとの値は同一でもよいし、α>β、α<βのうちいずれの関係でもよい。これにより、ワード線WL(N−3)乃至WL(N+3)に接続されたメモリセルトランジスタMTがオン状態とされ、データの読み出しが図示せぬビット線BLを介してセンスアンプ5により実行される。また、電圧VREADK−が必要に応じて電圧(VREAD+β)の値をとっても良い。すなわちこの場合、電圧VREADKは常に電圧VREADよりも大きな値とされる。

次に図13を用いて、ワード線WL(N−1)及びワード線WL(N+1)にそれぞれ電圧VREADKを転送する場合について説明する。図13に示すように、ワード線WL(N+1)に上記電圧VREADLAを転送せず、ワード線WL(N−1)及び(N+1)にそれぞれ電圧VREADKを転送する。この場合においても、電圧VREADKは図12で説明した値をとる。すなわち、電圧VREADKは、電圧(VREAD+β)または電圧(VREAD−β)いずれかの値でよく(以下、必要に応じて電圧(VREAD−β)を電圧VREADK−と、電圧(VREAD+β)を電圧VREADK+と呼ぶことがある)、ワード線WL(N−1)及びワード線WL(N+1)には場合の数だけ、これら電圧が転送される。また電圧VREADKによりメモリセルトランジスタMTがオン状態とされる。これにより、ワード線WL(N−3)乃至WL(N+3)に接続されたメモリセルトランジスタMTがオン状態とされ、データの読み出しが図示せぬビット線BLを介してセンスアンプ5により実行される。

次に上記第1電圧発生回路41、第2電圧発生回路42、及び第6電圧発生回路46がそれぞれ生成する電圧の大小関係について説明する。第1電圧発生回路41、第2電圧発生回路42、及び第6電圧発生回路46がそれぞれ生成する電圧の大小関係は次の5つのパターン(I)〜(V)に分けられる。なお、上記図12におけるデータの読み出し時を(I)〜(V)までとし、上記図13におけるデータの読み出しの電圧関係を(VI)及び(VII)とする。

(II)電圧VREADK<電圧VREAD<電圧VREADLA

(III)電圧VREADLA≦電圧VREAD≦電圧VREADK

(IV)電圧VREADK≦電圧VREADLA<電圧VREAD

(V)電圧VREAD≦電圧VREADK≦電圧VREADLA

(VI)電圧VREADK−<電圧VREAD<電圧VREADK+

(VII)電圧VREAD≦電圧VREADK−≦電圧VREADK+

<読み出し動作時の電圧転送動作ついて(その3)>

次に、上記説明したNAND型フラッシュメモリにおいて読み出し動作時の電圧転送動作について図14を用いて説明する。図14は、ローカルポンプ61に与えられるイネーブル信号EN、MOSトランジスタ71のゲートに与えられる電位、ノードN2、N3における電位、及びワード線WLにおける電位のタイムチャートである。これら、電圧転送動作のタイミングは、制御部6により制御される。なお、ここでは、一例として上記(I)の場合におけるノードN2、N3の電位を挙げる。また、上記説明した読み出し動作(その1、その2)と同一の動作については説明を省略する。

図14に示すように、時刻t0以前では、信号TGが‘L’レベルとされ、MOSトランジスタ23がオフ状態とされることにより、ノードN2乃至ノードN4の電位はそれぞれ電圧VREAD、電圧VREADLA、及び電圧VREADKとされる。

時刻t0を経過するとノードN2乃至N4の電位はそれぞれ同一の昇圧速度で上昇する。そして時刻t1になると制御部6はイネーブル信号ENを‘L’レベルへと切り替える。すなわち、ローカルポンプ61の出力を‘L’レベルとする。ここで電圧VREAD≦電圧VREADLA≦電圧VREADKであることから、制御部6は時刻t1においてノードN2乃至N4の電位が電圧VREADとされるように時間を制御する。またこの際、ワード線WLの電位も電圧VREADとされる。

時刻t2において、例えば選択ワード線WLをN=31とすれば、該選択ワード線WL31に隣接するワード線WL32の電位、及びノードN3の電位はそれぞれ電圧VREADLAに達する。また、時刻t3においてワード線WL30の電位、及びノードN4の電位はそれぞれ電圧VREADKに達する。

本実施形態に係る半導体装置であっても上記(1)の効果を奏することができる。すなわち、半導体装置の動作信頼性を向上させることが出来る。本実施形態に係る半導体装置であると、上記第1の実施形態で説明した電圧VREADLAの他、電圧VREADKがワード線WLに転送された場合であっても、該電圧VREADLA、電圧VREADK、及び電圧VREADが転送されるべきワード線WLの電位は同一の昇圧速度で上昇する。このため、上記第1の実施形態で説明した従来例のようにワード線WLの電位の立ち上がりにタイムラグが生じるといった問題がない。つまり、本実施形態に係る半導体装置であっても、GIDL電流を抑圧させることが出来、動作信頼性の向上を図ることが出来る。

Claims (4)

- ワード線と、

前記ワード線に接続されるメモリセルと、

第1負荷として機能し、前記ワード線とは異なる第1ワード線に接続された第1ノードに第1電圧を出力する第1電圧発生回路と、

前記ワード線及び第1ワード線とは異なり、前記第1負荷よりも大きな第2負荷として機能する第2ワード線に接続された第2ノードに第2電圧を出力する第2電圧発生回路と、

前記第1ノードと前記第2ノードとを短絡可能なMOSトランジスタと、

前記メモリセルの保持データの読み出し動作であって、前記第1ワード線及び前記第2ワード線の電位が上昇する際に前記MOSトランジスタをオン状態とさせることで、前記第1ノードと前記第2ノードとを短絡するよう制御する制御部と

を具備し、前記制御部は、前記MOSトランジスタをオン状態で維持させる期間を、時

間で制御することを特徴とする半導体記憶装置。 - 前記第1電圧が前記第2電圧よりも大きい場合、前記制御部は前記第1負荷の電位が前記第2電圧に達する前に、前記MOSトランジスタをオフ状態とする

ことを特徴とする請求項1記載の半導体記憶装置。 - 読み出し時において、前記第2電圧が前記第1電圧よりも大きい場合、制御部は前記第2負荷の電位が前記第1電圧に達する前に、前記MOSトランジスタをオフ状態とする

ことを特徴とする請求項1記載の半導体記憶装置。 - 前記MOSトランジスタはn型高耐圧イントリシックMOSトランジスタである

ことを特徴とする請求項1記載の半導体記憶装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009152642A JP5259505B2 (ja) | 2009-06-26 | 2009-06-26 | 半導体記憶装置 |

| US12/822,587 US8493786B2 (en) | 2009-06-26 | 2010-06-24 | Semiconductor device for short-circuiting output terminals of two or more voltage generator circuits at read time and control method for the same |

| US14/657,249 USRE47017E1 (en) | 2009-06-26 | 2015-03-13 | Semiconductor device for short-circuiting output terminals of two or more voltage generator circuits at read time and control method for the same |

| US16/041,428 USRE49175E1 (en) | 2009-06-26 | 2018-07-20 | Semiconductor device including three voltage generator circuits and two transistors configured to short-circuit respective different combinations of the voltage generator circuits |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009152642A JP5259505B2 (ja) | 2009-06-26 | 2009-06-26 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011008875A JP2011008875A (ja) | 2011-01-13 |

| JP5259505B2 true JP5259505B2 (ja) | 2013-08-07 |

Family

ID=43380547

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009152642A Active JP5259505B2 (ja) | 2009-06-26 | 2009-06-26 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US8493786B2 (ja) |

| JP (1) | JP5259505B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5491741B2 (ja) * | 2009-01-30 | 2014-05-14 | 株式会社東芝 | 半導体記憶装置 |

| JP2013080535A (ja) | 2011-10-03 | 2013-05-02 | Toshiba Corp | 半導体記憶装置 |

| JP2013239215A (ja) * | 2012-05-11 | 2013-11-28 | Toshiba Corp | 半導体記憶装置 |

| JP2014038670A (ja) | 2012-08-13 | 2014-02-27 | Toshiba Corp | 不揮発性半導体記憶装置 |

| KR20160029396A (ko) * | 2014-09-05 | 2016-03-15 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| US10096356B2 (en) * | 2015-12-04 | 2018-10-09 | Toshiba Memory Corporation | Method of operation of non-volatile memory device |

| JP2018147530A (ja) * | 2017-03-03 | 2018-09-20 | 東芝メモリ株式会社 | 半導体記憶装置 |

| KR102743813B1 (ko) * | 2019-06-25 | 2024-12-18 | 에스케이하이닉스 주식회사 | 메모리 장치 및 이의 동작 방법 |

Family Cites Families (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57103522A (en) | 1980-12-19 | 1982-06-28 | Fujitsu Ltd | Power supply device |

| JPS603726A (ja) | 1983-06-22 | 1985-01-10 | Nec Corp | 基準電源 |

| FR2594820B1 (fr) | 1986-02-26 | 1988-06-10 | Onera (Off Nat Aerospatiale) | Procede et generateur pour engendrer de l'iode atomique a l'etat fondamental, et laser chimique a iode en faisant application |

| US4961220A (en) | 1988-12-21 | 1990-10-02 | Spectrum Concepts, Inc. | Power management in a microprocessor-controlled battery-powered telephone device |

| US5235520A (en) | 1989-10-20 | 1993-08-10 | Seiko Epson Corporation | Integrated circuit having a function for generating a constant voltage |

| JPH07105159B2 (ja) | 1989-11-16 | 1995-11-13 | 株式会社東芝 | 半導体記憶装置の冗長回路 |

| US5216558A (en) | 1991-01-30 | 1993-06-01 | Iomega Corporation | Drawer loading removable cartridge disk drive |

| JP3247402B2 (ja) | 1991-07-25 | 2002-01-15 | 株式会社東芝 | 半導体装置及び不揮発性半導体記憶装置 |

| US5216588A (en) | 1992-02-14 | 1993-06-01 | Catalyst Semiconductor, Inc. | Charge pump with high output current |

| US5337284A (en) | 1993-01-11 | 1994-08-09 | United Memories, Inc. | High voltage generator having a self-timed clock circuit and charge pump, and a method therefor |

| US5394077A (en) | 1993-04-30 | 1995-02-28 | Kabushiki Kaisha Toshiba | Internal power supply circuit for use in a semiconductor device |

| EP0627807B1 (en) | 1993-05-27 | 1998-08-12 | Fujitsu Limited | Power line connection circuit and power line switch IC for the same |

| US5553030A (en) | 1993-09-10 | 1996-09-03 | Intel Corporation | Method and apparatus for controlling the output voltage provided by a charge pump circuit |

| US5671179A (en) | 1994-10-19 | 1997-09-23 | Intel Corporation | Low power pulse generator for smart voltage flash eeprom |

| JPH08171796A (ja) | 1994-12-16 | 1996-07-02 | Toshiba Corp | 半導体記憶装置 |

| JP3192344B2 (ja) * | 1995-03-15 | 2001-07-23 | 株式会社東芝 | 半導体記憶装置 |

| JP3497601B2 (ja) | 1995-04-17 | 2004-02-16 | 松下電器産業株式会社 | 半導体集積回路 |

| EP0766256B1 (en) | 1995-09-29 | 1999-12-01 | STMicroelectronics S.r.l. | Voltage regulator for semiconductor non-volatile electrically programmable memory devices |

| US5602794A (en) * | 1995-09-29 | 1997-02-11 | Intel Corporation | Variable stage charge pump |

| KR0172404B1 (ko) | 1995-12-21 | 1999-03-30 | 김광호 | 반도체 메모리장치의 리프레쉬별 내부 승압전원 제어방법 |

| JP3998278B2 (ja) | 1996-02-27 | 2007-10-24 | 株式会社ルネサステクノロジ | 内部電位発生回路 |

| JP2917914B2 (ja) | 1996-05-17 | 1999-07-12 | 日本電気株式会社 | 昇圧回路 |

| JP3805830B2 (ja) * | 1996-05-31 | 2006-08-09 | 株式会社ルネサステクノロジ | 不揮発性メモリ |

| TW423162B (en) | 1997-02-27 | 2001-02-21 | Toshiba Corp | Power voltage supplying circuit and semiconductor memory including the same |

| KR100271840B1 (ko) | 1997-08-27 | 2000-11-15 | 다니구찌 이찌로오 | 회로 면적의 증대를 억제하면서 복수의 전위를 출력할 수 있는내부 전위 발생 회로 |

| JP3935592B2 (ja) * | 1997-08-27 | 2007-06-27 | 株式会社ルネサステクノロジ | 内部電位発生回路 |

| JP4491846B2 (ja) * | 1998-09-21 | 2010-06-30 | ソニー株式会社 | 不揮発性メモリのロウデコーダ |

| JP4149637B2 (ja) * | 2000-05-25 | 2008-09-10 | 株式会社東芝 | 半導体装置 |

| KR100394757B1 (ko) * | 2000-09-21 | 2003-08-14 | 가부시끼가이샤 도시바 | 반도체 장치 |

| FR2838840B1 (fr) * | 2002-04-23 | 2005-04-01 | St Microelectronics Sa | Comparateur de tension d'alimentation |

| FR2838861A1 (fr) * | 2002-04-23 | 2003-10-24 | St Microelectronics Sa | Memoire effacable et programmable electriquement comprenant un dispositif de gestion d'une tension d'alimentation interne |

| KR100645055B1 (ko) * | 2004-10-28 | 2006-11-10 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 프로그램 방법 |

| JP4908064B2 (ja) * | 2005-08-19 | 2012-04-04 | 株式会社東芝 | 半導体集積回路装置 |

| KR100802111B1 (ko) * | 2006-03-28 | 2008-02-11 | 삼성광주전자 주식회사 | 안전회로가 구현된 충전장치 및 그의 충전방법 |

| KR100800479B1 (ko) * | 2006-07-25 | 2008-02-04 | 삼성전자주식회사 | 하이브리드 로컬 부스팅 방식을 이용한 불휘발성 메모리장치의 프로그램 방법 |

| JP4369462B2 (ja) * | 2006-11-22 | 2009-11-18 | Okiセミコンダクタ株式会社 | チャージポンプ型dc/dcコンバータ |

| KR101431758B1 (ko) * | 2008-01-18 | 2014-08-20 | 삼성전자주식회사 | 안정적인 워드라인 전압을 발생할 수 있는 플래시 메모리장치 |

| JP2009266351A (ja) * | 2008-04-28 | 2009-11-12 | Toshiba Corp | 半導体記憶装置、及びその制御方法 |

-

2009

- 2009-06-26 JP JP2009152642A patent/JP5259505B2/ja active Active

-

2010

- 2010-06-24 US US12/822,587 patent/US8493786B2/en not_active Ceased

-

2015

- 2015-03-13 US US14/657,249 patent/USRE47017E1/en active Active

-

2018

- 2018-07-20 US US16/041,428 patent/USRE49175E1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011008875A (ja) | 2011-01-13 |

| US20100329017A1 (en) | 2010-12-30 |

| USRE47017E1 (en) | 2018-08-28 |

| USRE49175E1 (en) | 2022-08-16 |

| US8493786B2 (en) | 2013-07-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12148482B2 (en) | Semiconductor memory device | |

| CN103514952B (zh) | Nand闪存及对其施加偏压的方法 | |

| US8787087B2 (en) | Semiconductor memory device controlling operation timing of the sense circuit | |

| KR101718153B1 (ko) | Nand형 플래시 메모리의 독출 방법 및 nand형 플래시 메모리 | |

| USRE49175E1 (en) | Semiconductor device including three voltage generator circuits and two transistors configured to short-circuit respective different combinations of the voltage generator circuits | |

| US7701784B2 (en) | Semiconductor memory device which includes memory cell having charge accumulation layer and control gate | |

| US8331160B2 (en) | Memory device having improved programming operation | |

| JP4504405B2 (ja) | 半導体記憶装置 | |

| US7898851B2 (en) | Semiconductor memory device which includes memory cell having charge accumulation layer and control gate | |

| US20150287462A1 (en) | Semiconductor memory device | |

| JP4939971B2 (ja) | 不揮発性半導体メモリ | |

| CN115620780A (zh) | 半导体存储装置及在其中执行读出动作的方法 | |

| US9396803B2 (en) | Non-volatile semiconductor memory device | |

| JP2009146556A (ja) | 半導体記憶装置 | |

| JP2009245556A (ja) | 半導体記憶装置 | |

| CN104246894A (zh) | 降低非易失性存储器单元中的编程干扰的方法 | |

| JP2016157494A (ja) | 半導体記憶装置 | |

| US7924620B2 (en) | Nonvolatile semiconductor memory including charge accumulation layer and control gate | |

| US20170148518A1 (en) | Semiconductor memory device | |

| US11443810B2 (en) | Negative level shifters and nonvolatile memory devices including the same | |

| USRE50856E1 (en) | Semiconductor device for short-circuiting nodes connected to a word line control circuit and control method for the same | |

| JP2009266351A (ja) | 半導体記憶装置、及びその制御方法 | |

| CN111341756B (zh) | 半导体存储装置 | |

| JP2006286033A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110830 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5259505 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |