JP4624924B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4624924B2 JP4624924B2 JP2005513609A JP2005513609A JP4624924B2 JP 4624924 B2 JP4624924 B2 JP 4624924B2 JP 2005513609 A JP2005513609 A JP 2005513609A JP 2005513609 A JP2005513609 A JP 2005513609A JP 4624924 B2 JP4624924 B2 JP 4624924B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- drain

- source

- semiconductor device

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0221—Manufacture or treatment of FETs having insulated gates [IGFET] having asymmetry in the channel direction, e.g. lateral high-voltage MISFETs having drain offset region or extended-drain MOSFETs [EDMOS]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

- H10D30/603—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs having asymmetry in the channel direction, e.g. lateral high-voltage MISFETs having drain offset region or extended drain IGFETs [EDMOS]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/013—Manufacturing their source or drain regions, e.g. silicided source or drain regions

- H10D84/0133—Manufacturing common source or drain regions between multiple IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

-

- H10W44/20—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/149—Source or drain regions of field-effect devices

- H10D62/151—Source or drain regions of field-effect devices of IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/149—Source or drain regions of field-effect devices

- H10D62/151—Source or drain regions of field-effect devices of IGFETs

- H10D62/156—Drain regions of DMOS transistors

- H10D62/157—Impurity concentrations or distributions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/254—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes extend entirely through the semiconductor bodies, e.g. via-holes for back side contacts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/257—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are characterised by top-view geometrical layouts, e.g. interdigitated, semi-circular, annular or L-shaped electrodes

-

- H10W40/228—

-

- H10W72/5522—

-

- H10W90/754—

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Amplifiers (AREA)

Description

一般に、この種の移動体通信装置は、電波の放射と受信をするアンテナ、電力変調された高周波信号を増幅してアンテナへ供給する高周波電力増幅器、アンテナで受信した高周波信号を信号処理する受信部、これらの制御を行う制御部、そしてこれらに電源電圧を供給する電池(バッテリー)で構成される。

特開平6−310717号公報(特許文献1)には、ドレイン側に低不純物濃度のオフセットドレイン領域を介して高不純物濃度のドレイン領域を設ける高耐圧用MOSFETにおいて、ゲート電極の側壁にサイドウォールスペーサを形成する前と後に不純物を2回イオン注入することによって、ソース側をLDD(Lightly Doped Drain)構造にする技術が開示されている。

米国特許第602011号公報(特許文献2)には、ドレイン側に低不純物濃度のオフセットドレイン領域を介して高不純物濃度のドレイン領域を設ける高耐圧用MOSFETにおいて、異なるパターンのフォトレジスト膜をマスクに用いた2回のイオン注入によって、低不純物濃度のオフセットドレイン領域と高不純物濃度のドレイン領域との間に第3のドレイン領域を形成する技術が開示されている。

これらの増幅素子のうち、パワーMOSFETは、ドレイン側に低不純物濃度のオフセットドレイン領域を介して高不純物濃度のドレイン領域を設けることによって、高いドレイン耐圧を確保する構造を採用したものであるが、化合物半導体デバイスに比較して電力付加効率は低いものの、バイアス制御が容易で、かつ量産性も高いという利点がある。

しかし、最近の移動体通信装置は、部品点数の増加に伴って電力消費量が増大していることから、各部品は一層の小型化、低電力動作が要求されている。特に、電力増幅回路は、各部品の中でも多くの電力を消費する部品であることから、チップサイズの小型化とそれに伴う低電力動作が強く要求されている。

従って、パワーMOSFETを増幅素子に用いる移動体通信装置用半導体装置の一つの課題は、パワーMOSFETを用いた増幅回路の電力付加効率を向上させることにある。また、パワーMOSFETを増幅素子に用いる移動体通信装置用半導体装置のもう一つの課題は、増幅素子であるパワーMOSFETが形成されるチップサイズの小型化を推進することにある。

増幅回路の電力付加効率を向上させるためには、パワーMOSFETのオン抵抗(Ron)を低減すると共に、帰還容量(Cgd)と呼ばれるドレイン、ゲート間寄生容量を低減する必要がある。ところが、パワーMOSFETのオン抵抗(Ron)と帰還容量(Cgd)とは、互いにトレードオフの関係にある。すなわち、パワーMOSFETのオン抵抗(Ron)を低減するためには、オフセットドレイン領域の不純物濃を高くすることが有効であるが、オフセットドレイン領域の不純物濃度を高くすると、ドレイン、ゲート間寄生容量である帰還容量(Cgd)も大きくなり、増幅回路の電力付加効率が低下してしまうという問題が生じる。従って、パワーMOSFETの電力付加効率を向上させるためには、オン抵抗(Ron)と帰還容量(Cgd)を共に低減する技術を開発することが課題となる。

本発明の一つの目的は、移動体通信装置用半導体装置の電力付加効率を向上させる技術を提供することにある。

本発明の他の目的は、移動体通信装置用半導体装置のチップサイズの小型化を推進する技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下の通りである。

本発明の半導体装置は、第1導電型の半導体基板の主面の一部に、チャネル形成領域を挟んで互いに離間して形成された第2導電型のソースおよびドレインと、前記チャネル形成領域の上部にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側壁に形成されたサイドウォールスペーサと、前記半導体基板の主面の他部に、前記ソースと接するように形成された第1導電型の打抜き層とを備えたMOSFETを有し、

前記MOSFETの前記ドレインは、第2導電型の低濃度領域と、前記低濃度領域に接し、かつ前記チャネル形成領域から離間して形成された第2導電型の高濃度領域とからなり、前記低濃度領域は、さらに前記チャネル形成領域に接する第1低濃度領域と、前記サイドウォールスペーサに対して自己整合で形成され、前記第1低濃度領域よりも不純物濃度が高い第2低濃度領域とからなるものである。

本発明の半導体装置は、第1導電型の半導体基板の主面の一部に、チャネル形成領域を挟んで互いに離間して形成された第2導電型のソースおよびドレインと、前記チャネル形成領域の上部にゲート絶緑膜を介して形成されたゲート電極と、前記半導体基板の主面の他部に、前記ソースと接するように形成された第1導電型の複数の打抜き層とを備えたMOSFETを有しており、

前記ソースおよび前記ドレインは、前記半導体基板の主面の第1方向に沿って互いに平行に延在するフィンガー状の平面パターンを有し、

前記複数の打抜き層は、前記第1方向に沿って配列され、それぞれの打抜き層は、その長辺が前記第1方向と交差する第2方向と平行になるような矩形の平面パターンを有しているものである。

本発明の半導体装置は、第1導電型の半導体基板の主面の第1領域にチャネル形成領域を挟んで互いに離間して形成された第2導電型のソースおよびドレインと、前記チャネル形成領域の上部にゲート絶縁膜を介して形成された多結晶シリコン膜からなるゲート電極と、前記ゲート電極の上部を覆うキャップ絶縁膜と、前記キャップ絶縁膜の上部を覆い、前記キャップ絶縁膜とはエッチングレートが異なるストッパ絶縁膜と、前記ストッパ絶縁膜の上部を覆う層間絶縁膜とを備え、

前記ゲート電極の上部には、前記層間絶縁膜、前記ストッパ絶縁膜および前記キャップ絶縁膜を貫通して前記ゲート電極の表面に達する溝が形成され、前記溝の内部には、前記多結晶シリコン膜よりも電気抵抗が小さい導電膜が埋め込まれているものである。

本発明の半導体装置の製造方法は、第1導電型の半導体基板の主面上にゲート絶縁膜を介してゲート電極を形成した後、前記ゲート電極の両側の前記半導体基板に不純物をイオン注入することによって、ソース、ドレインを形成する際、ドレインを形成する工程が、

(a)前記半導体基板のドレイン形成領域に不純物をイオン注入することによって、一端が前記ゲート電極の側壁下部に延在する第2導電型の第1低濃度領域を形成する工程、

(b)前記(a)工程の後、前記ゲート電極の側壁にサイドウォールスペーサを形成する工程、

(c)前記(b)工程の後、前記半導体基板のドレイン形成領域に不純物をイオン注入することによって、前記第1低濃度領域よりも不純物濃度が高い第2導電型の第2低濃度領域を前記サイドウォールスペーサに対して自己整合で形成する工程、

(d)前記第2低濃度領域の一部に不純物をイオン注入することによって、前記第2低濃度領域よりも不純物濃度が高く、一端が前記ゲート電極の側壁下部から離間する第2導電型の高濃度領域を形成する工程を含むものである。

図2は、本発明の半導体装置の要部を示す断面図である。

図3は、本発明の半導体装置の製造工程中における要部断面図である。

図4は、図3に続く、半導体装置の製造工程中における要部断面図である。

図5は、図4に続く、半導体装置の製造工程中における要部断面図である。

図6は、図5に続く、半導体装置の製造工程中における要部断面図である。

図7は、図6に続く、半導体装置の製造工程中における要部断面図である。

図8は、図7に続く、半導体装置の製造工程中における要部断面図である。

図9は、図8に続く、半導体装置の製造工程中における要部断面図である。

図10は、図9に続く、半導体装置の製造工程中における要部断面図である。

図11は、図10に続く、半導体装置の製造工程中における要部断面図である。

図12は、図11に続く、半導体装置の製造工程中における要部断面図である。

図13は、図12に続く、半導体装置の製造工程中における要部断面図である。

図14は、図13に続く、半導体装置の製造工程中における要部断面図である。

図15は、図14に続く、半導体装置の製造工程中における要部断面図である。

図16は、図15に続く、半導体装置の製造工程中における要部断面図である。

図17は、本発明による構造と従来構造のオン抵抗(Ron)および帰還容量(Cgd)を比較した表である。

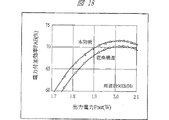

図18は、本発明による構造と従来構造に対し、周波数900MHzの正弦波信号を入力したときの電力付加効率を比較したグラフである。

図19は、本発明を用いた一実施の形態である増幅回路を有するRFパワーモジュールの概略斜視図である。

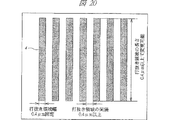

図20は、一辺の幅が一定である長方形の打抜き層の、平面レイアウトを示した平面図である。

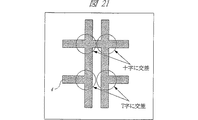

図21は、長方形の打抜き層が十字あるいはT字に交差している打抜き層のレイアウトを示した平面図である。

図22は、長方形の打抜き層の長手方向をフィンガーの長手方向に対して平行に配置したレイアウトを示した平面図である。

図23は、長方形の打抜き層の長手方向をフィンガーの長手方向に対して垂直に配置したレイアウトを示した平面図である。

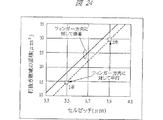

図24は、長方形の打抜き層の長手方向をフィンガーの長手方向に対して平行または垂直に配置したレイアウトでの、打抜き層の面積を比較したグラフである。

図25は、打抜き層をメアンダ(meandering)状に配置したレイアウトを示した平面図である。

図26は、打抜き層をメッシュ状に配置したレイアウトを示した平面図である。

図27は、本発明において、プラグでゲート電極をシャントした半導体装置の要部を示す断面図である。

また、以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

(実施の形態1)

本実施の形態1は、例えばGSM方式のネットワークを利用して情報を伝送するデジタル携帯電話に使用されるRF(Radio Frequency)パワーモジュールに搭載される半導体装置である。

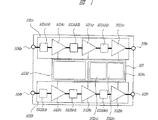

図1は、本実施の形態1のRFパワーモジュールを構成する増幅回路の回路ブロック図を示している。この図には、例えばGSM900とDCS1800との2つの周波数帯が使用可能(デュアルバンド方式)で、それぞれの周波数帯でGMSK(Gaussian filtered Minimum Shift Keying)変調方式とEDGE(Enhanced Data GSM Environment)変調方式との2つの通信方式を使用可能なRFパワーモジュールに使用される増幅回路が示されている。

増幅回路は、GSM900用の電力増幅回路102Aと、DCS1800用の電力増幅回路102Bと、それら電力増幅回路102A、102Bの増幅動作の制御や補佐などを行う周辺回路103とを有している。各電力増幅回路102A、102Bは、それぞれ3つの増幅段102A1〜102A3、102B1〜102B3と、3つの整合回路102AM1〜102AM3、102BM1〜102BM3とを有している。すなわち、入力端子104a、104bは、入力用の整合回路102AM1、102BM1を介して1段目の増幅段102A1、102B1の入力に電気的に接続され、1段目の増幅段102A1、102B1の出力は、段間用の整合回路102AM2、102BM2を介して2段目の増幅段102A2、102B2の入力に電気的に接続され、2段目の増幅段102A2、102B2の出力は、段間用の整合回路102AM3、102BM3を介して最終段の増幅段102A3、102B3の入力に電気的に接続され、最終段の増幅段102A3、102B3の出力は、出力端子105a、105bと電気的に接続されている。

周辺回路103は、制御回路103Aと、上記増幅段102A1〜102A3、102B1〜102B3にバイアス電圧を印加するバイアス回路103Bなどを有している。制御回路103Aは、上記電力増幅回路102A、102Bに印加する所望の電圧を発生する回路であり、電源制御回路103A1およびバイアス電圧生成回路103A2を有している。電源制御回路103A1は、上記増幅段102A1〜102A3、102B1〜102B3の各々の出力用のパワーMOSFETのドレイン端子に印加される第1電源電圧を生成する回路である。また、上記バイアス電圧生成回路103A2は、上記バイアス回路103Bを制御するための第1制御電圧を生成する回路である。ここでは、電源制御回路103A1が外部のベースバンド回路から供給される出力レベル指定信号に基づいて上記第1電源電圧を生成すると、バイアス電圧生成回路103A2が電源制御回路103A1で生成された上記第1電源電圧に基づいて、上記第1制御電圧を生成するようになっている。上記ベースバンド回路は、上記出力レベル指定信号を生成する回路である。この出力レベル指定信号は、電力増幅回路102A、102Bの出力レベルを指定する信号で、携帯電話と基地局との間の距離、すなわち、電波の強弱に応じた出力レベルに基づいて生成されているようになっている。

上記電力増幅回路102A、102Bのそれぞれは、上記3段の増幅段102A1〜102A3、102B1〜102B3として、3個のnチャネル型パワーMOSFETを順次従属接続した回路構成を有している。

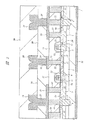

図2は、上記電力増幅回路102A、102Bが形成された半導体基板1の要部を示す断面図である。

例えば比抵抗が5mΩcm程度のp型単結晶シリコンからなる半導体基板(第1導電型の半導体基板、以下、基板という)1の主面には、比抵抗が20Ωcm程度、膜厚が2μm程度のp型単結晶シリコンからなるエピタキシャル層2が形成されている。エピタキシャル層2の主面の一部には、p型ウエル5が形成されている。このp型ウエル5は、パワーMOSFETのドレインからソースへの空乏層の延びを抑えるパンチスルーストッパとしての機能を有している。

p型ウエル5の表面には、酸化シリコンからなるゲート絶縁膜6を介してパワーMOSFETのゲート電極7が形成されている。ゲート電極7は、例えばn型の多結晶シリコン膜とタングステンシリサイド(WSix)膜の積層膜からなる。ゲート電極7の下部のp型ウエル5は、パワーMOSFETのチャネルが形成される領域となる。ゲート電極7の側壁には、酸化シリコンからなるサイドウォールスペーサ12が形成されている。

エピタキシャル層2の内部のチャネル形成領域を挟んで互いに離間する領域には、パワーMOSFETのソース、ドレインが形成されている。ドレインは、チャネル形成領域に接するn−型オフセットドレイン領域(第1低濃度領域)9と、このn−型オフセットドレイン領域9に接し、チャネル形成領域から離間して形成されたn型オフセットドレイン領域(第2低濃度領域)13と、n型オフセットドレイン領域13に接し、チャネル形成領域からさらに離間して形成されたn+型ドレイン領域(高濃度オフセット領域)15とからなる。これらn−型オフセットドレイン領域9、n型オフセットドレイン領域13およびn+型ドレイン領域15のうち、ゲート電極7に最も近いn−型オフセットドレイン領域9は不純物濃度が最も低く、ゲート電極7から最も離間したn+型ドレイン領域15は不純物濃度が最も高い。後述するように、n−型オフセットドレイン領域9は、ゲート電極7に対して自己整合で形成され、n型オフセットドレイン領域13は、ゲート電極7の側壁のサイドウォールスペーサ12に対して自己整合で形成される。

このように、本実施の形態のパワーMOSFETの一つの特徴は、ゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くしたことにある。

この構造により、ゲート電極7とドレインとの間に空乏層が広がるようになる結果、ゲート電極7とその近傍のn−型オフセットドレイン領域9との間に形成される帰還容量(Cgd)は小さくなる。また、n型オフセットドレイン領域13の不純物濃度が高いことから、オン抵抗(Ron)も小さくなる。n型オフセットドレイン領域13は、ゲート電極7から離間した位置に形成されているために、帰還容量(Cgd)に及ぼす影響は僅かである。すなわち、本実施の形態のパワーMOSFETによれば、従来のパワーMOSFETにおいては、互いにトレードオフの関係にあったオン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅回路の電力付加効率を向上させることができる。

一方、パワーMOSFETのソースは、チャネル形成領域に接するn−型ソース領域(低濃度領域)10と、このn−型ソース領域10に接し、チャネル形成領域から離間して形成されたn+型ソース領域(高濃度領域)16とからなる。チャネル形成領域に接するn−型ソース領域10は、チャネル形成領域から離間したn+型ソース領域16に較べて不純物濃度が低く、かつ浅く形成されている。また、n−型ソース領域10の下部には、ソースからチャネル形成領域への不純物の広がりを抑制し、さらに短チャネル効果を抑制するためのp型ハロー領域11が形成されている。後述するように、n−型ソース領域10は、ゲート電極7に対して自己整合で形成され、n+型ソース領域16は、ゲート電極7の側壁のサイドウォールスペーサ12に対して自己整合で形成される。

n+型ソース領域16の端部(n−型ソース領域10と接する側と反対側の端部)には、n+型ソース領域16と接するp型打抜き層4が形成されている。このp型打抜き層4の表面近傍には、p型打抜き層4の表面を低抵抗化するためのp+型半導体領域17が形成されている。p型打抜き層4は、ソースと基板1とを接続するための導電層であるが、本実施の形態のパワーMOSFETの一つの特徴は、エピタキシャル層2に形成した溝3の内部に埋め込んだp型多結晶シリコン膜からなる導電層によってp型打抜き層4を形成したことにある。

従来のパワーMOSFETは、エピタキシャル層2に不純物をイオン注入することによって打抜き層を形成している。イオン注入によって形成したp型打抜き層は、単位面積当たりの寄生抵抗が大きいという欠点があるが、高濃度の不純物をドープしたp型多結晶シリコン膜を溝3の内部に埋め込むことにより、寄生抵抗の小さいp型打抜き層4を形成することができる。

上記パワーMOSFETのp型打抜き層4(p+型半導体領域17)、ソース(n+型ソース領域16)およびドレイン(n+型オフセットドレイン領域15)のそれぞれの上部には、窒化シリコン膜20と酸化シリコン膜21とに形成されたコンタクトホール22内のプラグ23が接続されている。プラグ23は、W膜を主体とする導電膜で構成されている。

p型打抜き層4(p+型半導体領域17)およびソース(n+型ソース領域16)には、プラグ23を介してソース電極25が接続され、ドレイン(n+型オフセットドレイン領域15)には、プラグ23を介してドレイン電極24が接続されている。ソース電極25およびドレイン電極24は、アルミニウム(Al)合金膜を主体とする導電膜で構成されている。

ドレイン電極24およびソース電極25のそれぞれには、ドレイン電極24およびソース電極25を覆う酸化シリコン膜26に形成されたスルーホール27を介して配線28が接続されている。配線28は、アルミニウム(Al)合金膜を主体とする導電膜で構成されている。配線28の上部には、酸化シリコン膜と窒化シリコン膜の積層膜からなる表面保護膜29が形成されている。また、基板1の裏面には、例えばニッケル(Ni)膜、チタン(Ti)膜、Ni膜および金(Au)膜の積層膜からなるソース裏面電極31が形成されている。

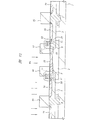

次に、図2に示すパワーMOSFETの製造方法を図3〜図16を用いて工程順に説明する。

まず、図3に示すように、p型単結晶シリコンからなる基板1の主面上に周知のエピタキシャル成長法を用いてp型単結晶シリコンからなるエピタキシャル層2を形成した後、周知のフォトリソグラフィ技術とドライエッチング技術とを用いてエピタキシャル層2の一部(打抜き層形成領域)をエッチングし、基板1に達する深さ2.2μm程度の溝3を形成する。

次に、図4に示すように、溝3の内部を含む基板1上にCVD法でp型多結晶シリコン膜30を堆積した後、溝3の外部の多結晶シリコン膜30をエッチバック法で除去することにより、溝3の内部にp型多結晶シリコン膜30からなるp型打抜き層4を形成する。このように、不純物をドープしたp型多結晶シリコン膜を溝3の内部に埋め込むことにより、寄生抵抗の小さいp型打抜き層4を形成することができる。なお、多結晶シリコン膜に代えて溝3の内部に金属膜を埋め込むことにより、さらに寄生抵抗の小さい打抜き層を形成することができる。

次に、図5に示すように、フォトレジスト膜40をマスクにしてエピタキシャル層2の一部にホウ素(B)をイオン注入することによって、パンチスルーストッパ用のp型ウエル5を形成する。p型ウエル5は、主としてパワーMOSFETのソース形成領域とチャネル形成領域とに形成される。イオン注入条件は、例えば第1回目が加速エネルギー200keV、ドーズ量2.0×1013/cm2、第2回目が加速エネルギー50keV、ドーズ量1.0×1013/cm2である。

続いて、エピタキシャル層2の表面をフッ酸で洗浄した後、図6に示すように、基板1を約800℃で熱処理することによって、エピタキシャル層2の表面に膜厚11nm程度の酸化シリコン膜からなるゲート絶縁膜6を形成する。ゲート絶縁膜6は、熱酸化膜に代えて、窒素を含む酸化シリコン膜、いわゆる酸窒化膜を適用してもよい。この場合は、ゲート絶縁膜6の界面におけるホットエレクトロンのトラップを低減することができる。また、熱酸化膜の上部にCVD法で酸化シリコン膜を堆積し、これら2層の酸化膜でゲート絶縁膜6を構成してもよい。

次に、ゲート絶縁膜6の上部にゲート電極7を形成する。ゲート電極7を形成するには、例えばゲート絶縁膜6の上部にCVD法で膜厚100nm程度のn型多結晶シリコン膜を堆積し、続いてn型多結晶シリコン膜の上部にCVD法で膜厚150nmのWSix膜を堆積し、さらにWSix膜の上部にCVD法で膜厚150nmの酸化シリコン膜からなるキャップ絶縁膜8を堆積した後、フォトレジスト膜をマスクにしてキャップ絶縁膜8、WSix膜およびn型多結晶シリコン膜をドライエッチングする。グート電極7のゲート長は、0.23μm程度である。

次に、図7に示すように、フォトレジスト膜41をマスクにしてエピタキシャル層2の一部にリン(P)をイオン注入することによって、n−型オフセットドレイン領域9を形成する。n−型オフセットドレイン領域9は、その端部がチャネル形成領域と接するように、ゲート電極7の側壁下部で終端する。n−型オフセットドレイン領域9を形成するためのイオン注入条件は、例えば加速エネルギー40keV、ドーズ量8.0×1012/cm2である。このように、n−型オフセットドレイン領域9の不純物濃度を低くすることにより、ゲート電極7とドレインとの間に空乏層が広がるようになるので、両者の間に形成される帰還容量(Cgd)が低減される。

次に、フォトレジスト膜41を除去した後、図8に示すように、フォトレジスト膜42をマスクにしてp型ウエル5の表面にヒ素(As)をイオン注入することによって、n−型ソース領域10を形成する。このときのイオン注入条件は、例えば加速エネルギー15keV、ドーズ量3.0×1015/cm2である。このように、不純物(As)を低加速エネルギーでイオン注入し、n−型ソース領域10を浅く形成することにより、ソースからチャネル形成領域への不純物の広がりを抑制できるので、しきい値電圧の低下を抑制することができる。

次に、上記不純物(As)のイオン注入に引き続いて、図9に示すように、フォトレジスト膜42をマスクにしてp型ウエル5の表面にホウ素(B)をイオン注入することによって、n−型ソース領域10の下部にp型ハロー領域11を形成する。このとき、基板1の主面に対して30度の斜め方向から不純物をイオン注入する斜めイオン注入法を用い、例えば加速エネルギー15keV、ドーズ量7.0×1012/cm2で不純物をイオン注入した後、基板1を90度回転するという操作を4回繰り返す。p型ハロー領域11は、必ずしも形成する必要はないが、これを形成した場合は、ソースからチャネル形成領域への不純物の広がりがさらに抑制され、さらに短チャネル効果が抑制されるので、しきい値電圧の低下をさらに抑制することができる。

次に、フォトレジスト膜42を除去した後、図10に示すように、ゲート電極7の側壁にサイドウォールスペーサ12を形成する。サイドウォールスペーサ12は、基板1上にCVD法で酸化シリコン膜を堆積した後、この酸化シリコン膜を異方性エッチングして形成する。サイドウォールスペーサ12用の酸化シリコン膜は、具体的には有機ソースであるTEOS(tetraethyl orthosilicate)を熱分解して形成するHLD(High Temperature Low Pressure Decomposition)膜が用いられる。HLD膜は、膜厚均一性に優れ、また膜中に不純物が拡散し難いという特徴がある。

次に、図11に示すように、ドレイン形成領域の上部に開口を有するフォトレジスト膜43をマスクにして、n−型オフセットドレイン領域9の一部にリン(P)をイオン注入する。このときのイオン注入条件は、例えば加速エネルギー40keV、ドーズ量8.0×1012/cm2である。これにより、n−型オフセットドレイン領域9の一部には、ゲート電極7のドレイン側の側壁に形成されたサイドウォールスペーサ12に対して自己整合的にn型オフセットドレイン領域13が形成される。

上記イオン注入の加速エネルギーは、n−型オフセットドレイン領域9を形成する際に行うイオン注入の加速エネルギーと同じなので、n型オフセットドレイン領域13の接合深さは、n−型オフセットドレイン領域9の接合深さとほぼ同じになる。また、n型オフセットドレイン領域13に注入された不純物は、n−型オフセットドレイン領域9に注入された不純物と同じ導電型の不純物(P)なので、n型オフセットドレイン領域13の不純物濃度は、n−型オフセットドレイン領域9の不純物濃度よりも高くなる。すなわち、n型オフセットドレイン領域13は、n−型オフセットドレイン領域9よりも低抵抗となるので、オン抵抗(Ron)を低減することができる。

n−型オフセットドレイン領域9は、ゲート電極7に対して自己整合的に形成されるのに対し、n型オフセットドレイン領域13は、ゲート電極7の側壁のサイドウォールスペーサ12に対して自己整合的に形成されることから、n型オフセットドレイン領域13は、ゲート長方向に沿ったサイドウォールスペーサ12の膜厚に相当する分、ゲート電極7から離間して形成される。従って、n型オフセットドレイン領域13の不純物濃度を高くしても、帰還容量(Cgd)に及ぼす影響は僅かである。

次に、フォトレジスト膜43を除去した後、図12に示すように、n型オフセットドレイン領域13の一部とソース形成領域のp型ウエル5のそれぞれの上部に開口を有するフォトレジスト膜44をマスクにして、n型オフセットドレイン領域13とp型ウエル5のそれぞれの一部にヒ素(As)をイオン注入する。このときのイオン注入条件は、例えば加速エネルギー60keV、ドーズ量8.0×1015/cm2である。

上記のイオン注入により、n型オフセットドレイン領域13の一部には、n型オフセットドレイン領域13よりも不純物濃度が高く、かつn型オフセットドレイン領域13よりもさらにチャネル形成領域から離間したn+型ドレイン領域15が形成される。なお、このとき、高不純物濃度のn+型ドレイン領域15を低不純物濃度のn型オフセットドレイン領域13やn−型オフセットドレイン領域9に比べて浅く形成することにより、ソース、ドレイン間の寄生容量(ドレイン容量)を低減することができる。

また、上記のイオン注入により、p型ウエル5には、n−型ソース領域10よりも不純物濃度が高く、かつn−型ソース領域10よりも底部の位置が深いn+型ソース領域16が形成される。n+型ソース領域16は、ゲート電極7の側壁のサイドウォールスペーサ12に対して自己整合的に形成されるので、ゲート長方向に沿ったサイドウォールスペーサ12の膜厚に相当する分、チャネル形成領域から離間して形成される。

このように、n+型ソース領域16をサイドウォールスペーサ12に対して自己整合的に形成することにより、n+型ソース領域16とチャネル形成領域との距離を高精度に規定することができる。他方、ゲート電極7の側壁にサイドウォールスペーサ12を形成せず、フォトレジスト膜をマスクにしたイオン注入によってチャネル形成領域から離間したn+型ソース領域16を形成しようとすると、フォトマスクの合わせずれによってn+型ソース領域16とチャネル形成領域との距離がばらついてしまう。この場合、n+型ソース領域16の端部がチャネル形成領域に近づき過ぎると、n+型ソース領域16の不純物がチャネル形成領域に拡散し、しきい値電圧がばらついてしまう。他方、n+型ソース領域16の端部がチャネル形成領域から離れ過ぎると、ソース抵抗が増加してしまう。

従って、n+型ソース領域16をサイドウォールスペーサ12に対して自己整合で形成する本実施の形態によれば、パワーMOSFETを微細化した場合でも上記のような問題を回避できるので、パワーMOSFETの微細化を推進することができる。

ここまでの工程により、n−型オフセットドレイン領域9とn型オフセットドレイン領域13とn+型ドレイン領域15とからなるドレイン、およびn−型ソース領域10とn+型ソース領域16とからなるソースを有するパワーMOSFETが完成する。

次に、フォトレジスト膜44を除去した後、図13に示すように、p型打抜き層4の上部を開口したフォトレジスト膜45をマスクにしてp型打抜き層4の表面にフッ化ホウ素(BF2)をイオン注入することにより、p+型半導体領域17を形成し、p型打抜き層4の表面を低抵抗化する。イオン注入条件は、例えば加速エネルギー50keV、ドーズ量2.0×1015/cm2である。

次に、フォトレジスト膜45を除去した後、図14に示すように、基板1上にCVD法で膜厚50nm程度の窒化シリコン膜20と膜厚800nm程度の酸化シリコン膜21とを堆積した後、化学的機械研磨(Chemical Mechanical Polishing)法を用いて酸化シリコン膜21の表面を平坦化し、続いてフォトレジスト膜をマスクにして酸化シリコン膜21と窒化シリコン膜20とをドライエッチングすることにより、p型打抜き層4(p+型半導体領域17)、ソース(n+型ソース領域17)およびドレイン(n+型ドレイン領域15)のそれぞれの上部にコンタクトホール22を形成する。

次に、図15に示すように、コンタクトホール22の内部にW膜を主体とするプラグ23を埋め込んだ後、酸化シリコン膜21の上部にアルミニウム(Al)合金膜を主体とするドレイン電極24とソース電極25とを形成する。

次に、図16に示すように、ドレイン電極24およびソース電極25の上部にCVD法で膜厚900nm程度の酸化シリコン膜26を堆積し、続いて酸化シリコン膜26の一部をエッチングしてスルーホール27を形成した後、酸化シリコン膜26の上部にアルミニウム(Al)合金膜を主体とする配線28を形成し、配線28とドレイン電極24および配線28とソース電極25をそれぞれ接続する。次に、配線28の上部にCVD法で堆積した膜厚300nm程度の酸化シリコン膜と膜厚500nm程度の窒化シリコン膜とからなる表面保護膜29を形成する。

その後、表面保護膜29の一部を選択的に除去して配線28の一部(図示しないパッド部)を露出した後、基板1の裏面を280nm程度研磨し、続いて基板1の裏面にソース裏面電極31を形成する。ここまでの工程により、前記図2に示す電力増幅回路が略完成する。ソース裏面電極31は、例えば膜厚0.1μm程度のニッケル(Ni)膜、膜厚0.15μm程度のチタン(Ti)膜、膜厚0.1μm程度のNi膜および膜厚1.3μm程度の金(Au)膜をスパッタリング法で順次堆積することによって形成する。基板1は、半導体チップに個片化された後、ソース裏面電極31を介してモジュール基板に半田付けされる。

図17は、ゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くした本実施の形態のパワーMOSFETの帰還容量(Cgd)およびオン抵抗(Ron)と、このような二重オフセット構造を有しない従来のパワーMOSFETの帰還容量(Cgd)およびオン抵抗(Ron)とを比較したものである。図示のように、本実施の形態のパワーMOSFETは、従来のパワーMOSFETに較べて帰還容量(Cgd)およびオン抵抗(Ron)が共に低減されている。

この結果、図18に示すように、本実施の形態のパワーMOSFETを用いた増幅回路は、従来のパワーMOSFETを用いた増幅回路に較べて電力付加効率(PAE)が2%程度向上することが本発明者の実測によって判明した。

図19は、本実施の形態のパワーMOSFETを用いた増幅回路を有する半導体チップ1Aが搭載されたRFパワーモジュールの概略斜視図である。

半導体チップ1Aは、基板1の裏面をモジュール基板50の主面と対向させた状態でキャビティ内に搭載されている。半導体チップ1Aは、Auワイヤ51を介して伝送線路52と電気的に接続されている。伝送線路52には、半導体チップ1Aの他、インピーダンス整合用のコンデンサ53などが接続されている。Auワイヤ51は、インダクタとしての機能を有し、伝送線路52は、インピーダンス整合用のインダクタとしての機能を有している。基板1の裏面に形成されたソース裏面電極31は、チップ搭載用の電極54に半田付けされている。電極54は、モジュール基板50内のサーマルビア55を通じてモジュール基板50の裏面のGND電極56と電気的かつ熱的に接合されている。モジュール基板50の主面はモールド樹脂57で覆われ、半導体チップ1Aやコンデンサ53などが封止されている。

(実施の形態2)

前記実施の形態1のパワーMOSFETは、高濃度の不純物をドープしたp型多結晶シリコン膜を溝3の内部に埋め込むことによって、p型打抜き層4を形成している。このような方法で形成したp型打抜き層4は、不純物のイオン注入によって形成した打抜き層よりも寄生抵抗を小さくできる利点がある。

しかし、導電膜を溝の内部に埋め込んで打抜き層を形成する方法は、基板1に深い溝を掘るためにプロセス的な制約が多く、自由に打抜き層を配置することが困難である。すなわち、多結晶シリコン膜や金属膜などの導電膜を溝に埋め込んで打抜き層を形成するためには、まずアスペクト比の高い溝を掘り、その内部に隙間なく導電膜を埋め込まなければならない。溝の内部の導電膜中にボイド(空隙)が生じると基板の表面は平坦化されないため、後に続く各種の膜堆積工程において、打抜き層の段差が原因で膜のはがれ等の不良を起こす可能性が高い。従って、溝の深さや導電膜堆積装置などによって、溝の幅に制限が生じる。

打抜き層の平面レイアウトは、図20に示すような一辺の幅が一定の長方形が最も不良を起こしにくい。これは、このような形状の場合、溝の幅が変化している領域が存在していないため、導電膜が均一に埋め込まれるからである。

他方、図21に示すように、長方形の溝が十字あるいはT字に交差するレイアウトにおいては、交差している部分で溝の幅が他の部分より広くなる。このため、溝の幅が広くなった部分で導電膜が均一に埋め込まれない可能性が生じ、前述したような膜のはがれ等の不良を起こす可能性がある。溝の幅が広くなった部分にも導電膜を均一に埋め込むことのできる導電膜堆積装置があれば、このような十字やT字のレイアウトも許容されるが、通常の場合は装置が対応できないケースが多い。また、このような打抜き層は溝が深いために、溝の幅とその間隔を打抜き層に接続されるコンタクトホールの幅よりも広くしなければならない。

フィンガー形状のパワーMOSFETにおいて、図22のように打抜き層4の長手方向をフィンガーの長手方向に対して平行に配置する場合を考える。この場合、打抜き層4とそれに接続されるコンタクトホール22aは、マスク合わせのマージンを考慮してフィンガーに対して垂直方向に複数個配置し、両側の端部を合わせ精度分だけ、長手方向を広げる必要がある。

一方、図23のように、打抜き層4の長手方向をフィンガーの長手方向に対して垂直に配置した場合は、マスク合わせのマージン分広げるのは、打抜き層4とコンタクトホール22aではなく、打抜き層4そのものとなる。従って、図22のレイアウトと比較して打抜き層4の面積が広がる結果、打抜き層4の寄生抵抗を低減することができる。図24は、打抜き層4の一辺の幅を0.4μm、打抜き層4同士の間隔を0.4μmとした時、図22の平行に配置するレイアウトと図23の垂直に配置するレイアウトで、各種セルピッチに対する打抜き層4の面積を比較したものである。図に示すように、垂直に配置するレイアウト(実線)の方が平行に配置するレイアウト(破線)に較べて打抜き層4の面積が大きくなるので、寄生抵抗を低減することができる。

また、図22に示すような打抜き層4のレイアウトでは、最適なセルピッチは離散的な数値となり、打抜き層4の一辺の幅が0.4μm、打抜き層4同士の間隔が0.4μmというような配置の制限が生じる。例えば、ソースと隣接した位置にフィンガーの長手方向と平行に打抜き層4を1つ配置するとセルピッチは3.5μmとなるとする。この場合、打抜き層を2つに増やすとセルピッチは3.9μmとなる。

一方、図23に示すような打抜き層4のレイアウトでは、セルピッチの変更に対応して打抜き層4の長手方向の長さを変えればよい。従って、周囲の条件に合わせて比較的自由にセルピッチを変更することが可能である。

図25は、打抜き層4の平面レイアウトをメアンダ(meandering)型とし、図26は、メッシュ型にした例である。これらのレイアウトは、打抜き層4の一部で幅が変化しているので、図23のレイアウトに較べると導電膜の埋め込みが困難となるが、図23のレイアウトよりも打抜き層4の面積が大きいので、寄生抵抗をさらに低減することができる。また、比較的自由にセルピッチを変更することが可能である。

(実施の形態3)

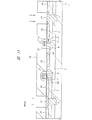

図27は、本実施の形態のパワーMOSFETを示す基板1の要部断面図である。本実施の形態のnチャネル型パワーMOSFETは、ゲート電極7をn型の多結晶シリコン膜のみで構成すると共に、ゲート電極7の上部の絶縁膜に長溝32を設け、この長溝32の内部に埋め込んだプラグ23でゲート電極7をシャントしている。プラグ23は、コンタクトホール22の内部に埋め込まれたプラグ23と同じく、W膜を主体とする金属膜からなる。長溝32は、ゲート電極7とほぼ同程度の長さを有し、ゲート電極7と平行して延在している。

ゲート電極7の上部に長溝32を形成するには、パワーMOSFETの上部に酸化シリコン膜21を堆積した後、フォトレジスト膜をマスクにして酸化シリコン膜21をドライエッチングし、ゲート電極7の上部を覆う窒化シリコン膜21の表面でエッチングを一旦停止する。次に、窒化シリコン膜21をドライエッチングした後、窒化シリコン膜21の下層の酸化シリコン膜(キャップ絶縁膜8)をエッチングすることにより、ゲート電極7の表面に達する長溝32が形成される。このように、ゲート電極7の上部を覆う窒化シリコン膜21の表面でエッチングを一旦停止し、次にキャップ絶縁膜8をエッチングすることにより、長溝32の幅をゲート電極7のゲート長より広くした場合でも、長溝32の底部が基板1に突き抜ける不具合を防止できる。これにより、長溝32の幅をゲート電極7のゲート長より広くし、長溝32に埋め込まれるプラグ23とゲート電極7とのコンタクト抵抗を低減することができる。また、長溝32の内部のプラグ23は、ソース、ドレインの上部のコンタクトホール22にプラグ23を埋め込む工程で同時に埋め込むことができる。

このように、ゲート電極7の上部の長溝32に埋め込んだ金属膜からなる低抵抗のプラグ23でゲート電極7をシャントしてそのシート抵抗を低減することにより、ゲート電極7をシャントするための1層目あるいは2層目のAl合金配線が不要となる。これにより、シャント用Al合金配線の引き回し領域が不要となるので、パワーMOSFETが形成される半導体チップ1Aのサイズを縮小することができ、RFパワーモジュールの小型化を推進することができる。

また、ゲート電極7を多結晶シリコンの単層膜で構成することにより、pチャネル型パワーMOSFETのゲート電極をp型の多結晶シリコン膜で構成することができる。これにより、pチャネル型パワーMOSFETを短チャネル効果が生じにくい表面チャネル型とすることができるので、pチャネル型パワーMOSFETの微細化による性能の向上を推進することができる。

また、ゲート電極7を多結晶シリコンの単層膜で構成することにより、この多結晶シリコンの単層膜を使って同一半導体チップ1A内に抵抗素子33を作ることができる。また、多結晶シリコンの単層膜で構成されたゲート電極7をMIM(Metal Insulator Metal)型容量素子の一方の電極として利用することも可能である。このように、ゲート電極7を多結晶シリコンの単層膜で構成し、ゲート電極7の上部の長溝32に埋め込んだプラグ23でシャントすることにより、同一半導体チップ1A内に抵抗素子33や容量素子を容易に作製することができるので、RFパワーモジュールの1チップ化を推進することができる。また、これにより、半導体チップ1Aが搭載されるモジュール基板50の配線レイアウトが容易となるので、RFパワーモジュールの電力付加効率の向上および小型化を推進することができる。

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

パワーMOSFETのオン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、移動体通信装置用半導体装置の電力付加効率を向上させることができる。

パワーMOSFETのケート電極上の溝に埋め込んだ金属膜からなる低抵抗のプラグでゲート電極をシャントしてシート抵抗を低減することにより、シャント用Al合金配線の引き回し領域が不要となるので、パワーMOSFETが形成される半導体チップのサイズを縮小することができる。

Claims (14)

- 第1導電型の半導体基板の主面の一部に、チャネル形成領域を挟んで互いに離間して形成された第2導電型のソースおよびドレインと、

前記チャネル形成領域の上部にゲート絶縁膜を介して形成されたゲート電極と、

前記ゲート電極の側壁に形成されたサイドウォールスペーサとを備えたMOSFETを有する半導体装置であって、

前記ドレインは、第2導電型のドレイン低濃度領域と、

前記ドレイン低濃度領域に接し、かつ前記チャネル形成領域から離間して形成され、前記ドレイン低濃度領域よりも不純物濃度が高い、第2導電型のドレイン高濃度領域とからなり、

前記ドレイン低濃度領域は、さらに前記チャネル形成領域に接する第1ドレイン低濃度領域と、

前記サイドウォールスペーサに対して自己整合で形成され、前記第1ドレイン低濃度領域よりも不純物濃度が高い第2ドレイン低濃度領域とからなり、

前記ソースは、前記チャネル形成領域に接する第2導電型のソース低濃度領域と、前記サイドウォールスペーサに対して自己整合で形成され、前記ソース低濃度領域よりも不純物濃度が高い第2導電型のソース高濃度領域とからなり、

前記ソース低濃度領域は、前記ソース高濃度領域よりも、前記半導体基板の主面の浅い領域に形成され、

前記ドレイン高濃度領域は、前記第1ドレイン低濃度領域および前記第2ドレイン低濃度領域よりも、前記半導体基板の主面の浅い領域に形成され、

前記ソース高濃度領域の接合深さは、前記ドレイン高濃度領域の接合深さとほぼ同じに構成され、

前記MOSFETによって、高周波信号を増幅する電力増幅回路が構成されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、前記第1ドレイン低濃度領域の接合深さは、前記第2ドレイン低濃度領域の接合深さとほぼ同じに構成されていることを特徴とする半導体装置。

- 請求項2記載の半導体装置において、前記ソース高濃度領域は、前記ドレイン高濃度領域を形成する工程と同一の工程で形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記ソース高濃度領域は、前記ドレイン高濃度領域を形成する工程と同一の工程で形成されていることを特徴とする半導体装置。

- 請求項3記載の半導体装置において、前記ソース低濃度領域は、前記第1ドレイン低濃度領域を形成する工程および前記第2ドレイン低濃度領域を形成する工程とは別の工程で形成されていることを特徴とする半導体装置。

- 請求項4記載の半導体装置において、前記ソース低濃度領域は、前記第1ドレイン低濃度領域を形成する工程および前記第2ドレイン低濃度領域を形成する工程とは別の工程で形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記ソース低濃度領域は、前記第1ドレイン低濃度領域を形成する工程および前記第2ドレイン低濃度領域を形成する工程とは別の工程で形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記ソースの下部の前記半導体基板に第1導電型のパンチスルーストッパ層が形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記半導体基板の裏面にソース電極が形成され、前記MOSFETの前記ソースと前記ソース電極とは、第1導電型の打抜き層によって電気的に接続されていることを特徴とする半導体装置。

- 請求項3記載の半導体装置において、前記半導体基板の裏面にソース電極が形成され、前記MOSFETの前記ソースと前記ソース電極とは、第1導電型の打抜き層によって電気的に接続されていることを特徴とする半導体装置。

- 請求項8記載の半導体装置において、前記ゲート電極と同層の膜によって抵抗素子が形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記ゲート電極と同層の膜によって抵抗素子が形成されていることを特徴とする半導体装置。

- 請求項8記載の半導体装置において、前記ゲート電極と同層の膜によって容量素子の一方の電極が形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記ゲート電極と同層の膜によって容量素子の一方の電極が形成されていることを特徴とする半導体装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003313971 | 2003-09-05 | ||

| JP2003313971 | 2003-09-05 | ||

| PCT/JP2004/011317 WO2005024931A1 (ja) | 2003-09-05 | 2004-07-30 | 半導体装置およびその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010020255A Division JP4891415B2 (ja) | 2003-09-05 | 2010-02-01 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2005024931A1 JPWO2005024931A1 (ja) | 2006-11-16 |

| JP4624924B2 true JP4624924B2 (ja) | 2011-02-02 |

Family

ID=34225153

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005513609A Expired - Lifetime JP4624924B2 (ja) | 2003-09-05 | 2004-07-30 | 半導体装置 |

| JP2010020255A Expired - Lifetime JP4891415B2 (ja) | 2003-09-05 | 2010-02-01 | 半導体装置 |

| JP2011240057A Pending JP2012089851A (ja) | 2003-09-05 | 2011-11-01 | 半導体装置 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010020255A Expired - Lifetime JP4891415B2 (ja) | 2003-09-05 | 2010-02-01 | 半導体装置 |

| JP2011240057A Pending JP2012089851A (ja) | 2003-09-05 | 2011-11-01 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US7176520B2 (ja) |

| JP (3) | JP4624924B2 (ja) |

| TW (1) | TWI361490B (ja) |

| WO (1) | WO2005024931A1 (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100493025B1 (ko) * | 2002-08-07 | 2005-06-07 | 삼성전자주식회사 | 반도체 메모리 장치의 제조 방법 |

| KR100560470B1 (ko) * | 2003-11-24 | 2006-03-13 | 삼성에스디아이 주식회사 | 다이오드 접속된 트랜지스터의 제조 방법 및 이를 이용한화상 표시 장치 |

| JP2005235825A (ja) * | 2004-02-17 | 2005-09-02 | Renesas Technology Corp | 電子回路モジュール |

| DE102004026100B4 (de) * | 2004-05-25 | 2007-10-25 | Infineon Technologies Ag | ESD-Schutzstrukturen für Halbleiterbauelemente |

| US7180132B2 (en) * | 2004-09-16 | 2007-02-20 | Fairchild Semiconductor Corporation | Enhanced RESURF HVPMOS device with stacked hetero-doping RIM and gradual drift region |

| US7250348B1 (en) * | 2004-11-12 | 2007-07-31 | National Semiconductor Corporation | Apparatus and method for packaging semiconductor devices using a patterned photo sensitive film to reduce stress buffering |

| US7615426B2 (en) * | 2005-02-22 | 2009-11-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | PMOS transistor with discontinuous CESL and method of fabrication |

| JP2006339343A (ja) | 2005-06-01 | 2006-12-14 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2007258568A (ja) * | 2006-03-24 | 2007-10-04 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP5073992B2 (ja) * | 2006-08-28 | 2012-11-14 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置 |

| JP2008166361A (ja) * | 2006-12-27 | 2008-07-17 | Sony Corp | 半導体素子及び固体撮像装置並びに撮像装置 |

| JP5280716B2 (ja) * | 2007-06-11 | 2013-09-04 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US8072035B2 (en) | 2007-06-11 | 2011-12-06 | Renesas Electronics Corporation | Semiconductor device and method of manufacturing the same |

| JP5302522B2 (ja) * | 2007-07-02 | 2013-10-02 | スパンション エルエルシー | 半導体装置及びその製造方法 |

| US20090026619A1 (en) * | 2007-07-24 | 2009-01-29 | Northrop Grumman Space & Mission Systems Corp. | Method for Backside Metallization for Semiconductor Substrate |

| JP5203669B2 (ja) * | 2007-10-22 | 2013-06-05 | 株式会社東芝 | 半導体装置およびその製造方法 |

| JP5381989B2 (ja) * | 2008-08-26 | 2014-01-08 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| JP4911158B2 (ja) * | 2008-10-30 | 2012-04-04 | ソニー株式会社 | 半導体装置および固体撮像装置 |

| KR20110123544A (ko) * | 2010-05-07 | 2011-11-15 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| US8138558B2 (en) * | 2010-08-20 | 2012-03-20 | Great Wall Semiconductor Corporation | Semiconductor device and method of forming low voltage MOSFET for portable electronic devices and data processing centers |

| JP5701684B2 (ja) | 2011-05-23 | 2015-04-15 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 半導体装置 |

| US8569129B2 (en) * | 2011-05-31 | 2013-10-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Device-manufacturing scheme for increasing the density of metal patterns in inter-layer dielectrics |

| US8803225B2 (en) * | 2012-01-12 | 2014-08-12 | Tsinghua University | Tunneling field effect transistor having a lightly doped buried layer |

| JP2012124506A (ja) * | 2012-01-20 | 2012-06-28 | Renesas Electronics Corp | 半導体装置 |

| JP2014036082A (ja) * | 2012-08-08 | 2014-02-24 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| US9153642B2 (en) * | 2013-03-05 | 2015-10-06 | Qualcomm Incorporated | Metal-oxide-metal (MOM) capacitor with enhanced capacitance |

| US9655265B2 (en) * | 2014-05-26 | 2017-05-16 | Infineon Technologies Ag | Electronic module |

| US9698248B2 (en) | 2014-07-25 | 2017-07-04 | Su Zhou Oriental Semiconductor Co., Ltd | Power MOS transistor and manufacturing method therefor |

| US9559097B2 (en) * | 2014-10-06 | 2017-01-31 | Nxp Usa, Inc. | Semiconductor device with non-isolated power transistor with integrated diode protection |

| CN107924874B (zh) | 2015-08-07 | 2021-11-26 | 罗姆股份有限公司 | 复合型半导体装置 |

| KR101876237B1 (ko) * | 2015-12-15 | 2018-07-10 | 현대오트론 주식회사 | 파워 모듈 및 그 제조 방법 |

| TWI621273B (zh) * | 2017-04-27 | 2018-04-11 | Richtek Technology Corporation | 具有可調整臨界電壓之高壓空乏型mos元件及其製造方法 |

| US11437313B2 (en) * | 2020-02-19 | 2022-09-06 | Taiwan Semiconductor Manufacturing Co., Ltd. | Structure and method of forming a semiconductor device with resistive elements |

| US11437466B2 (en) * | 2020-08-11 | 2022-09-06 | Taiwan Semiconductor Manufacturing Company Limited | Avalanche-protected transistors using a bottom breakdown current path and methods of forming the same |

| CN115188713B (zh) * | 2022-07-08 | 2025-09-16 | 弘大芯源(深圳)半导体有限公司 | 一种用于制造功率集成电路的方法 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58219766A (ja) * | 1982-06-14 | 1983-12-21 | Matsushita Electric Ind Co Ltd | Mos型半導体装置の製造方法 |

| JPS6312861U (ja) * | 1986-07-10 | 1988-01-27 | ||

| JPH06232153A (ja) * | 1993-02-03 | 1994-08-19 | Sony Corp | 半導体装置及びその製造方法 |

| JPH0730107A (ja) * | 1993-07-13 | 1995-01-31 | Sony Corp | 高耐圧トランジスタ及びその製造方法 |

| JPH07130898A (ja) * | 1993-11-05 | 1995-05-19 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JPH1154509A (ja) * | 1997-07-31 | 1999-02-26 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2001094094A (ja) * | 1999-09-21 | 2001-04-06 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2001127169A (ja) * | 1999-10-27 | 2001-05-11 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2002343960A (ja) * | 2001-05-11 | 2002-11-29 | Hitachi Ltd | 半導体装置 |

| JP2002368121A (ja) * | 2001-06-04 | 2002-12-20 | Hitachi Ltd | 電力用半導体装置 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4600933A (en) * | 1976-12-14 | 1986-07-15 | Standard Microsystems Corporation | Semiconductor integrated circuit structure with selectively modified insulation layer |

| JP2515300B2 (ja) | 1986-07-02 | 1996-07-10 | 日産自動車株式会社 | 内燃機関の点火時期制御装置 |

| JPS6355960A (ja) * | 1986-08-27 | 1988-03-10 | Hitachi Ltd | 半導体装置 |

| JPH03171740A (ja) | 1989-11-30 | 1991-07-25 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| US5155563A (en) | 1991-03-18 | 1992-10-13 | Motorola, Inc. | Semiconductor device having low source inductance |

| KR100274555B1 (ko) * | 1991-06-26 | 2000-12-15 | 윌리엄 비. 켐플러 | 절연 게이트 전계 효과 트랜지스터 구조물 및 이의 제조 방법 |

| JPH05218321A (ja) | 1992-01-30 | 1993-08-27 | Nec Corp | 電界効果型トランジスタおよびその製造方法 |

| JP3216258B2 (ja) | 1992-09-11 | 2001-10-09 | 株式会社日立製作所 | 絶縁ゲート半導体装置 |

| JP3221766B2 (ja) * | 1993-04-23 | 2001-10-22 | 三菱電機株式会社 | 電界効果トランジスタの製造方法 |

| JPH07283414A (ja) | 1994-04-05 | 1995-10-27 | Toshiba Corp | Mos型半導体装置 |

| ATE423853T1 (de) * | 1994-06-24 | 2009-03-15 | Innogenetics Nv | Gleichzeitiger nachweis, identifizierung und differenzierung von mykobakterium spezies unter verwendung eines hybridisierungs-assays |

| TW370719B (en) * | 1997-10-23 | 1999-09-21 | Winbond Electronics Corp | Manufacturing method of anti-electrostatic discharge element |

| JPH11204799A (ja) * | 1998-01-20 | 1999-07-30 | Mitsubishi Electric Corp | 高周波mosfet装置とその製造方法 |

| JP3120389B2 (ja) * | 1998-04-16 | 2000-12-25 | 日本電気株式会社 | 半導体装置 |

| US6020611A (en) * | 1998-06-10 | 2000-02-01 | Motorola, Inc. | Semiconductor component and method of manufacture |

| US6225181B1 (en) * | 1999-04-19 | 2001-05-01 | National Semiconductor Corp. | Trench isolated bipolar transistor structure integrated with CMOS technology |

| US6191460B1 (en) * | 1999-09-07 | 2001-02-20 | Integrated Device Technology, Inc. | Identical gate conductivity type static random access memory cell |

| JP4581179B2 (ja) * | 2000-04-26 | 2010-11-17 | 富士電機システムズ株式会社 | 絶縁ゲート型半導体装置 |

| JP2002076337A (ja) | 2000-09-01 | 2002-03-15 | Hitachi Ltd | 半導体装置及び半導体装置の製造方法 |

| EP1187220A3 (en) * | 2000-09-11 | 2007-10-10 | Kabushiki Kaisha Toshiba | MOS field effect transistor with reduced on-resistance |

| JP4488660B2 (ja) * | 2000-09-11 | 2010-06-23 | 株式会社東芝 | Mos電界効果トランジスタ |

| JP2003007844A (ja) * | 2001-04-09 | 2003-01-10 | Seiko Instruments Inc | 半導体装置 |

| JP4070485B2 (ja) * | 2001-05-09 | 2008-04-02 | 株式会社東芝 | 半導体装置 |

| JP2004039657A (ja) * | 2002-06-28 | 2004-02-05 | Renesas Technology Corp | 半導体装置 |

-

2004

- 2004-06-02 TW TW093115837A patent/TWI361490B/zh not_active IP Right Cessation

- 2004-07-30 WO PCT/JP2004/011317 patent/WO2005024931A1/ja not_active Ceased

- 2004-07-30 US US10/902,130 patent/US7176520B2/en not_active Expired - Lifetime

- 2004-07-30 JP JP2005513609A patent/JP4624924B2/ja not_active Expired - Lifetime

-

2006

- 2006-12-27 US US11/645,577 patent/US7791131B2/en not_active Expired - Lifetime

-

2010

- 2010-02-01 JP JP2010020255A patent/JP4891415B2/ja not_active Expired - Lifetime

- 2010-06-25 US US12/823,453 patent/US7994567B2/en not_active Expired - Lifetime

-

2011

- 2011-06-24 US US13/167,850 patent/US20110254087A1/en not_active Abandoned

- 2011-11-01 JP JP2011240057A patent/JP2012089851A/ja active Pending

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58219766A (ja) * | 1982-06-14 | 1983-12-21 | Matsushita Electric Ind Co Ltd | Mos型半導体装置の製造方法 |

| JPS6312861U (ja) * | 1986-07-10 | 1988-01-27 | ||

| JPH06232153A (ja) * | 1993-02-03 | 1994-08-19 | Sony Corp | 半導体装置及びその製造方法 |

| JPH0730107A (ja) * | 1993-07-13 | 1995-01-31 | Sony Corp | 高耐圧トランジスタ及びその製造方法 |

| JPH07130898A (ja) * | 1993-11-05 | 1995-05-19 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JPH1154509A (ja) * | 1997-07-31 | 1999-02-26 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP2001094094A (ja) * | 1999-09-21 | 2001-04-06 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2001127169A (ja) * | 1999-10-27 | 2001-05-11 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2002343960A (ja) * | 2001-05-11 | 2002-11-29 | Hitachi Ltd | 半導体装置 |

| JP2002368121A (ja) * | 2001-06-04 | 2002-12-20 | Hitachi Ltd | 電力用半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4891415B2 (ja) | 2012-03-07 |

| US7176520B2 (en) | 2007-02-13 |

| TW200511580A (en) | 2005-03-16 |

| US20100258876A1 (en) | 2010-10-14 |

| US20110254087A1 (en) | 2011-10-20 |

| US20070102757A1 (en) | 2007-05-10 |

| JP2010171433A (ja) | 2010-08-05 |

| US7994567B2 (en) | 2011-08-09 |

| JPWO2005024931A1 (ja) | 2006-11-16 |

| US7791131B2 (en) | 2010-09-07 |

| US20050051814A1 (en) | 2005-03-10 |

| WO2005024931A1 (ja) | 2005-03-17 |

| TWI361490B (en) | 2012-04-01 |

| JP2012089851A (ja) | 2012-05-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4624924B2 (ja) | 半導体装置 | |

| JP4907070B2 (ja) | 半導体装置およびその製造方法 | |

| US9640654B2 (en) | Semiconductor device | |

| JP2001094094A (ja) | 半導体装置およびその製造方法 | |

| JP5042492B2 (ja) | 半導体装置 | |

| JP2008258369A (ja) | 半導体装置およびその製造方法 | |

| JP4801323B2 (ja) | 半導体装置の製造方法 | |

| JP2006013070A (ja) | 半導体装置およびその製造方法 | |

| US8138550B2 (en) | Method of manufacturing a semiconductor device and a semiconductor device | |

| JP2005327827A (ja) | 半導体装置およびその製造方法 | |

| JP2012124506A (ja) | 半導体装置 | |

| JP2006019612A (ja) | 半導体装置およびその製造方法 | |

| JP5374553B2 (ja) | 半導体装置 | |

| JP2013258344A (ja) | 半導体装置 | |

| JP2008252113A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100201 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101019 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101104 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4624924 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131112 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |