JP4503677B2 - 上側および下側の基板表面を露出させた半導体パッケージ - Google Patents

上側および下側の基板表面を露出させた半導体パッケージ Download PDFInfo

- Publication number

- JP4503677B2 JP4503677B2 JP2008509150A JP2008509150A JP4503677B2 JP 4503677 B2 JP4503677 B2 JP 4503677B2 JP 2008509150 A JP2008509150 A JP 2008509150A JP 2008509150 A JP2008509150 A JP 2008509150A JP 4503677 B2 JP4503677 B2 JP 4503677B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- package

- die

- assembly

- land

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 528

- 239000004065 semiconductor Substances 0.000 title claims abstract description 65

- 125000006850 spacer group Chemical group 0.000 claims abstract description 61

- 229910000679 solder Inorganic materials 0.000 claims description 63

- 238000007789 sealing Methods 0.000 claims description 12

- 239000002184 metal Substances 0.000 description 95

- 239000000853 adhesive Substances 0.000 description 43

- 230000001070 adhesive effect Effects 0.000 description 43

- 238000000034 method Methods 0.000 description 40

- 238000010586 diagram Methods 0.000 description 28

- 238000000465 moulding Methods 0.000 description 26

- 230000015654 memory Effects 0.000 description 17

- 230000000712 assembly Effects 0.000 description 13

- 238000000429 assembly Methods 0.000 description 13

- 238000007689 inspection Methods 0.000 description 12

- 239000000047 product Substances 0.000 description 11

- 239000012467 final product Substances 0.000 description 10

- 238000013461 design Methods 0.000 description 8

- 238000004140 cleaning Methods 0.000 description 7

- 238000009434 installation Methods 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 230000001413 cellular effect Effects 0.000 description 6

- 230000010354 integration Effects 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 3

- 239000011324 bead Substances 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000002844 melting Methods 0.000 description 3

- 230000008018 melting Effects 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000002452 interceptive effect Effects 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 235000008409 marco Nutrition 0.000 description 2

- 244000078446 marco Species 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000000523 sample Substances 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000013100 final test Methods 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- -1 tapes Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0652—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0651—Wire or wire-like electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0652—Bump or bump-like direct electrical connections from substrate to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06551—Conductive connections on the side of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

- H01L2225/06558—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking the devices having passive surfaces facing each other, i.e. in a back-to-back arrangement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

- H01L2225/06568—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking the devices decreasing in size, e.g. pyramidical stack

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06572—Auxiliary carrier between devices, the carrier having an electrical connection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06575—Auxiliary carrier between devices, the carrier having no electrical connection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06582—Housing for the assembly, e.g. chip scale package [CSP]

- H01L2225/06586—Housing with external bump or bump-like connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06596—Structural arrangements for testing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1017—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support

- H01L2225/1023—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support the support being an insulating substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1041—Special adaptations for top connections of the lowermost container, e.g. redistribution layer, integral interposer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1058—Bump or bump-like electrical connections, e.g. balls, pillars, posts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/552—Protection against radiation, e.g. light or electromagnetic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01015—Phosphorus [P]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01027—Cobalt [Co]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01051—Antimony [Sb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01075—Rhenium [Re]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/143—Digital devices

- H01L2924/1433—Application-specific integrated circuit [ASIC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1532—Connection portion the connection portion being formed on the die mounting surface of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

- H01L2924/1815—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30105—Capacitance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Wire Bonding (AREA)

- Combinations Of Printed Boards (AREA)

Description

この出願は、「積層半導体パッケージシステム(Stacked semiconductor package system)」と題される、2005年4月29日に出願された米国仮出願番号第60/594,711号の優先権を主張し、この出願はまた、2005年6月20日に出願された米国仮出願番号第60/692,842号および2006年3月31日に出願された米国出願番号第11/394,635号の優先権を主張し、これらは両方とも「第2の基板を含み、上側および下側の基板表面を露出させた半導体パッケージ(Semiconductor package including second substrate and having exposed substrate surfaces on upper and lower sides)」と題され、これらは両方ともスタッツ・チップパック・リミテッド(STATS ChipPAC Ltd.)に譲渡された。

この発明は半導体のパッケージングに関する。

置を含む。

に業界で利用される表面実装アセンブリ方法を使用して、アセンブリにおける他のパッケージの上にたとえばメモリ(フラッシュ、SRAM、DRAM)などの既製のパッケージングされたチップを積層できることも望ましい。特に、ある製品用のメモリのタイプは、機能性が異なるごとに異なっている可能性がある。たとえば、画像取込の機能性がセルラー電話において望まれる場合には、高速メモリ(DRAM)が必要であろう。

300μmよりも大きなz相互接続はんだボールを利用しなければならない。ボールの直径が大きくなることは、ボールのピッチが大きくなることを決定づける(たとえば、典型的には300μmのボールでは約.65mmのピッチ)。それはひいては、底部パッケージ基板の周辺の利用可能な空間に収められることができるボールの数を制限する。さらに、はんだボールの周辺の構成によって、底部BGAは標準的なBGAのモールドキャップよりも大幅に大きくならざるを得ない。そして、はんだボールの周辺の構成によって、パッケージ全体の大きさが大きくなる(ボールの列の数およびボールピッチに応じて大きさが大きくなる)。標準的なBGAでは、本体の大きさはモールドキャップよりも約2〜3mmも大きい可能性がある。さらに、PoP構成における上部パッケージは、たとえはるかに少ない相互接続部を有する小さなチップを含んでいるとしても、底部パッケージに匹敵する大きさにされなければならない。ボールの取付(たとえば追加のボールの列)用により大きなエリアを与えるためにパッケージの設置面積を増大させることは、特定の適用例では大きさの限界を超える可能性があり、いずれにしてもより長いワイヤボンドの全長およびより大きな基板面積を必然的に伴い、これらは両方ともこれらの構成要素のコストを増大させる。パッケージ間の相互接続部の数が増大することによって、基板の電気的な接続部内でのルーティングを容易にするために上部パッケージ基板が少なくとも2つ(および多くの場合3つ以上)の金属層を有することが必要になる可能性がある。いくつかの適用例では、底部パッケージに2つのダイを積層させることがPoP構成において実用的でない場合がある。なぜなら、これによって、底部モールドキャップがさらに厚くなるためであり、上述の問題を悪化させるためである。

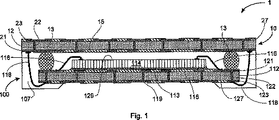

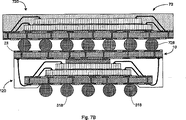

この発明は、第1のパッケージ基板のダイ取付側の上に実装され、第1のパッケージ基板のダイ取付側に電気的に接続された少なくとも1つのダイを有し、かつ、ダイの上に実装された第2の基板を有する半導体パッケージに向けられる。ダイ取付側に対向する第1のパッケージ基板の側は、基板の「ランド」側と称されることができる。第2の基板は、第1のパッケージ基板のダイ取付側に面している第1の側と、第1のパッケージ基板のダイ取付側から離れる方に向いている、(第2の基板の「ランド」側と称されることができる)第2の側とを有する。したがって、基板の「ランド」側は互いに離れる方に向いている。第1のパッケージ基板および第2の基板のz相互接続は、第1のパッケージ基板および第2の基板を接続するワイヤボンドによるものである。

接着剤を備えるスペーサのようなもしくは第1のパッケージ基板の上に実装される接着性スペーサのようなスペーサまたはスペーサアセンブリをパッケージサブアセンブリの上に実装するステップと、スペーサ上の接着剤の上または接着性スペーサの上に第2の基板を実装するステップと、接着剤または接着性スペーサを硬化させるステップと、プラズマ洗浄を行なうステップと、ワイヤボンディングを行なって、第2の基板の第1の側と第1のパッケージ基板のランド側との間にz相互接続部を形成するステップと、プラズマ洗浄を行なうステップと、モールディング操作を行なって、基板の第1の側、z相互接続ワイヤボンドおよびワイヤループ、第1のパッケージ基板の端縁、ならびに第1のパッケージ基板のランド側の縁のエリアを密閉し、第2の基板の第2の(「ランド」)側および縁のエリア内に位置する第1のパッケージ基板のランド側のエリアを露出したままにするステップと、第2のレベルの相互接続はんだボールを第1のパッケージ基板の露出したエリア上の箇所に取付けるステップと、(第2の基板がストリップまたはアレイ状に設けられた場合には)鋸で切り分けて、パッケージを完成させるステップとを含む。

ここで、この発明の代替的な実施例を示す図面を参照することによってさらに詳細にこの発明について記載する。この発明の特徴ならびに他の特徴および構造との関係を示す図面は概略的なものであり、一定の比例に応じているわけではない。説明の明確さを向上させるために、この発明の実施例を示す図面では、他の図に示されている要素に対応する要素はすべてが特に名称を変更されるわけではないが、すべての図面においてすべて容易に識別可能である。

に向いている。

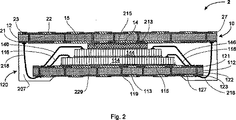

スペーサ14は、ダイ144の上向きに向いている面229と基板10の下向きに向いている面19との間に所望の分離をもたらすのに十分な直径を有するポリマー球で充填された硬化可能な接着剤からなる接着性スペーサであってもよい。

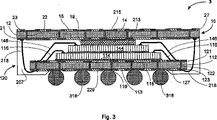

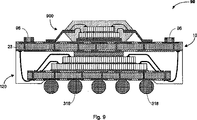

部分は、パッケージ、ダイまたは受動素子などの追加の構成要素の積層に利用可能である。しかしながら、第1のパッケージ基板の露出した部分は第2のパッケージ基板よりもエリアが限られており、第1のパッケージ側に作られることができる相互接続部の数を制限する。さらに、第1のパッケージ基板のランド側の縁のエリアを覆うアセンブリモールディング207の一部は、ワイヤボンド218のループの高さ(および許容差)を収容するのに十分に厚くなければならない。典型的には、ワイヤループにおけるモールディングの厚さは約50μmから約200μmの範囲にある。ワイヤループの端部が第1のパッケージのランド側のパッドの上にステッチングされるように逆方向のワイヤボンディングが利用される場合には、ワイヤループの高さは実際にはわずか約35μmであってもよく、したがって、このような実施例ではわずか約100μmという縁のエリアの上のモールディングの厚さを達成できる。順方向のワイヤボンディングが利用される場合には、より大きなモールドの高さが必要になる。なぜなら、厚さが約1ミルのワイヤを形成する、現在利用可能なワイヤボンディング技術を使用するボール(またはバンプ)上のワイヤループの高さは、通常約100μm以上であるためである。

でなされる、たとえば図3に示す実施例によって、たとえば図7Bおよび図8Bに示すようにアセンブリの上にはるかに大きな追加の構成要素を積層することが可能になる。

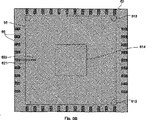

ダイが取付けられた状態の第1のパッケージ基板のダイ取付側を図5Bに示す。第1のダイ114は、基板のダイ取付側の上に、活性側を上に向けて付着される。この例では、ダイは正方形を規定する4つの端縁を有する。ワイヤボンドパッド51は、ダイの4つの端縁の近くに列をなして配置される。基板のランド側と同様に、ダイ取付側の表面の大半は、特にボンドフィンガ(たとえば54)の列(この例では、ダイの各端縁に沿った1列)を含む、金属層上の箇所がはんだマスクの開口によって露呈している場合を除いて、はんだマスクによって覆われている。ワイヤ116は、ダイパッド51をボンドフィンガ5

4と接続する。はんだマスクが覆い隠しているのは、ボンドフィンガ54をビア(たとえば522)に接続する金属層におけるトレース(たとえば521)であり、ビアは、基板のダイ取付側のパターニングされた金属層におけるトレースを、ランド側のパターニングされた金属層におけるトレースと電気的に接続する。したがって、第1のパッケージダイは、ワイヤを介して第1のパッケージ基板のダイ取付側の金属層におけるトレースに接続され、ビアを介してランド側の金属層におけるz相互接続ワイヤボンドフィンガに接続される。z相互接続ワイヤは、第1のパッケージ基板のランド側のボンドフィンガを第2のパッケージ基板のダイ取付側のボンドフィンガに接続する。第2のダイ144の設置面積は破線544によって図5Bに示されている。スペーサ14の設置面積は図5Bに破線514によって示されている。代替的には、第2のダイの上に実装されたスペーサ14ではなく第1の基板上のスペーサ13が利用される場合、その位置はたとえば破線513によって一例として示されている。第2のダイおよびワイヤボンド146ならびにスペーサ14、または代替的にスペーサ13は、簡略化するために図5Bからは省略されている。

ジュールを構築するためのプラットホームの役割を果たし得る。はんだボールとの相互接続(パッド上のはんだの相互接続)を容易にするために、はんだペースト(図には図示せず)が、第1のパッケージ基板および/または第2の基板の露出した側のボンディングパッドの上に、たとえば焼付によって分配または塗布されてもよい。

たとえばモジュール82を与える図8Bにおける820)のいずれかを選択できる。したがって、図7A、図7B、図8A、図8Bと同様の実施例では、製造業者は、機能(メモリの容量および速度、メモリタイプ)に応じておよびさまざまな供給業者からのコストに応じて、選択されたメモリBGAまたはLGAとプラットホームを組合せることができる。

のアセンブリ封止部にキャビティが形成され、第2の基板のランド側の内側エリア249を露出した(封止しない)ままにし、そこでは、以下にさらに詳細に記載するように、パッケージまたはダイなどの追加の素子を第2のパッケージ基板のランド側の上に実装でき、第2のパッケージ基板のランド側と電気的に接続させることができる。

ワイヤループおよびワイヤボンドが接続されるワイヤボンドパッドを含む第2の基板の上向きに向いている側の縁のエリアとを覆う。これによって、積層パッケージアセンブリの上のキャビティに積層されるべき1つ以上の素子と相互接続するために、第2の(「上部」)基板のランド側のエリアが露出したままになる。別の言い方をすれば、アセンブリの第2の基板側のアセンブリ封止部にキャビティが形成され、第2の基板のランド側の内側エリア269を露出した(封止しない)ままにし、そこでは、パッケージまたはダイなどの追加の素子を第2のパッケージ基板のランド側の上に実装でき、第2のパッケージ基板のランド側と電気的に接続させることができる。

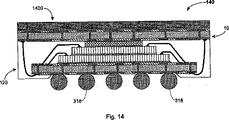

1のダイ取付側の上に実装される。ダイ273は、第1のアセンブリ基板241のダイ取付側のダイ取付側の金属層におけるパッドの上に裏面を下向きに付着され、第1のアセンブリ基板241のダイ取付側の金属層におけるパッドと電気的に接続される。第1のパッケージモールディングはダイの活性側およびワイヤボンドを密閉し、第2の基板244はモールディングの上向きに向いている面の接着剤を使用してモールディングの上に付着される。したがって、第2の基板の下向きに向いている面は第1のパッケージモールディング上の接着剤の上に載っている。モールディングは、ダイ273を第1のパッケージアセンブリ基板241と接続するワイヤボンドのループの高さを収容するのに十分に厚い。

ィングパッドの上にリフローされて、たとえばコンピュータなどの最終製品のマザーボード(図には図示せず)の下にある回路への相互接続をもたらす。

る金属層上のパッドと電気的に接続される。ダイと基板との間のアンダーフィルは、電気的な相互接続部を保護する働きをし、相互接続部に構造的および機械的な整合性および頑強性を与える働きをする。この例では、第2のダイ303′は第1のダイ303の上に裏面を下向きに実装され、ワイヤボンドによって基板のダイ取付側における金属層上のパッドと電気的に接続される。第1のパッケージモールディングはダイの活性側およびワイヤボンドを密閉し、第2の基板244はモールディングの上向きに向いている面の接着剤を使用してモールディングの上に付着される。したがって、第2の基板の下向きに向いている面は第1のパッケージモールディング上の接着剤の上に載っている。モールディングは、ダイ303′を第1のパッケージアセンブリ基板241と接続するワイヤボンドのループの高さを収容するのに十分に厚い。

得る。または、コア基板/インターポーザはたとえば金属リードフレームであってもよい。受動素子または電気シールドなどの追加の特徴がコア基板/インターポーザの表面上に設けられる場合もあれば、コア基板/インターポーザに埋込まれる場合もある。このような追加の特徴は、さらにまたは代替的に、第1のパッケージ基板の表面上に取付けられてもよい。

ンド」)側および縁のエリア内に位置する第1のパッケージ基板のランド側のエリアを露出したままにするステップと、第1のパッケージ基板の露出したエリア上の箇所に第2のレベルの相互接続はんだボールを取付けるステップと、(第2の基板がストリップまたはアレイ状に設けられた場合には)鋸で切り分けてパッケージを完成させるステップとを含む。

Claims (13)

- 半導体パッケージアセンブリであって、第1のパッケージ基板のダイ取付側の上に実装され、第1のパッケージ基板のダイ取付側に電気的に接続された少なくとも1つのダイを備え、前記半導体パッケージアセンブリはさらに、前記ダイの上に実装された第2の基板を備え、ダイ取付側に対向する第1のパッケージ基板の側は基板のランド側であり、前記第2の基板は、前記第1のパッケージ基板のダイ取付側に面している第1の側と、前記第1のパッケージ基板のダイ取付側から離れる方に向いている、ランド側である第2の側とを有し、その結果、基板のランド側は互いに離れる方に向いており、前記第1のパッケージ基板および前記第2の基板の間のz相互接続は、前記第1のパッケージ基板の前記ランド側の縁のエリアにおけるワイヤボンド箇所と、前記第2の基板の前記第1の側の縁のエリアにおける、周辺に位置するワイヤボンド箇所との間であって、かつ前記第1のパッケージ基板および前記第2の基板を接続するワイヤボンドによるものであり、前記第2の基板の前記第2の側の少なくとも一部および前記第1のパッケージ基板の前記ランド側の少なくとも一部の両方が露出するように前記第1のパッケージ基板および前記第2の基板はアセンブリ封止部により封止され、

前記ダイは、ワイヤボンドによって前記第1のパッケージ基板と電気的に接続される、半導体パッケージアセンブリ。 - 前記第2の基板は前記第1のパッケージ基板よりも大きい、請求項1に記載の半導体パッケージアセンブリ。

- 前記アセンブリ封止部は、前記第1のパッケージ基板と前記第2の基板との間のスペースを保つためのスペーサが接触していない前記第2の基板の第1の側のエリアを覆い、z相互接続ワイヤボンドおよびワイヤループ、前記第1のパッケージ基板の端縁、ならびに前記第1のパッケージ基板のランド側の縁のエリアを密閉し、その結果、前記第2の基板のランド側および前記縁のエリアの内側に位置する第1のパッケージ基板のランド側のエリアの両方を露出したままにし、

前記スペーサは前記第2の基板の前記第1の側と前記ダイの上面との間または前記第2の基板の前記第1の側と前記第1のパッケージ基板の前記ダイ取付側との間に配置されている、請求項2に記載の半導体パッケージアセンブリ。 - 前記第1のパッケージ基板は前記第2の基板よりも大きい、請求項1に記載の半導体パッケージアセンブリ。

- 前記アセンブリ封止部は、前記スペーサが接触していない前記第2の基板の第1の側のエリアを覆い、前記z相互接続ワイヤボンドおよびワイヤループ、前記第2の基板の端縁、ならびに前記第2の基板のランド側の縁のエリアを密閉し、その結果、前記第1のパッケージ基板のランド側および前記縁のエリアの内側に位置する前記第2の基板のランド側のエリアの両方を露出したままにする、請求項3に記載の半導体パッケージアセンブリ。

- 前記第2の基板はスペーサによって前記ダイの上に支持され、前記スペーサはワイヤループの高さを収容するために前記第2の基板の前記第1の側と前記ダイの上部との間に十分な空間を与える、請求項1に記載の半導体パッケージアセンブリ。

- 前記第2の基板はスペーサによって前記第1のパッケージ基板の上に支持され、ワイヤループの高さを収容するために前記第2の基板の前記第1の側と前記ダイの上部との間に十分な空間を与える、請求項1に記載の半導体パッケージアセンブリ。

- 前記第2の基板は、前記ダイの上に実装されたスペーサによって前記ダイの上に支持される、請求項1に記載の半導体パッケージアセンブリ。

- 前記第2の基板は、前記第1のパッケージ基板の上に実装されたスペーサによって前記ダイの上に支持される、請求項1に記載の半導体パッケージアセンブリ。

- 前記ダイおよび前記第1のパッケージ基板は、前記第1のパッケージ基板との前記ダイの電気的な相互接続部とともに、パッケージサブアセンブリを構成する、請求項1に記載の半導体パッケージアセンブリ。

- 前記第1のパッケージ基板および前記第2の基板のいずれかはボールグリッドアレイ基板であり、下にある回路との前記第1のパッケージ基板の第2のレベルの相互接続は、前記第1のパッケージ基板のランド側の露出した部分における相互接続によってなされる、請求項10に記載の半導体パッケージアセンブリ。

- 前記第1のパッケージ基板および前記第2の基板のいずれかはボールグリッドアレイ基板であり、下にある回路との前記第2の基板の第2のレベルの相互接続は、前記第2の基板の露出したランド側における相互接続によってなされる、請求項10に記載の半導体パッケージアセンブリ。

- 前記第1のパッケージ基板は前記第2の基板よりも大きく、下にある回路との前記第1のパッケージ基板の第2のレベルの相互接続は、第1のパッケージ基板のランド側におけるはんだボール相互接続によってなされる、請求項10に記載の半導体パッケージアセンブリ。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US59471105P | 2005-04-29 | 2005-04-29 | |

| US69284205P | 2005-06-20 | 2005-06-20 | |

| US11/394,635 US7429786B2 (en) | 2005-04-29 | 2006-03-31 | Semiconductor package including second substrate and having exposed substrate surfaces on upper and lower sides |

| PCT/US2006/016143 WO2006118982A2 (en) | 2005-04-29 | 2006-04-27 | Semiconductor substrate with exposed upper and lower sides |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008539599A JP2008539599A (ja) | 2008-11-13 |

| JP2008539599A5 JP2008539599A5 (ja) | 2009-07-02 |

| JP4503677B2 true JP4503677B2 (ja) | 2010-07-14 |

Family

ID=37233660

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008509150A Active JP4503677B2 (ja) | 2005-04-29 | 2006-04-27 | 上側および下側の基板表面を露出させた半導体パッケージ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7429786B2 (ja) |

| JP (1) | JP4503677B2 (ja) |

| KR (1) | KR101120122B1 (ja) |

| TW (1) | TWI322489B (ja) |

| WO (1) | WO2006118982A2 (ja) |

Families Citing this family (113)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6930256B1 (en) | 2002-05-01 | 2005-08-16 | Amkor Technology, Inc. | Integrated circuit substrate having laser-embedded conductive patterns and method therefor |

| US9691635B1 (en) | 2002-05-01 | 2017-06-27 | Amkor Technology, Inc. | Buildup dielectric layer having metallization pattern semiconductor package fabrication method |

| US7548430B1 (en) | 2002-05-01 | 2009-06-16 | Amkor Technology, Inc. | Buildup dielectric and metallization process and semiconductor package |

| US7633765B1 (en) | 2004-03-23 | 2009-12-15 | Amkor Technology, Inc. | Semiconductor package including a top-surface metal layer for implementing circuit features |

| TWI322448B (en) * | 2002-10-08 | 2010-03-21 | Chippac Inc | Semiconductor stacked multi-package module having inverted second package |

| US10811277B2 (en) | 2004-03-23 | 2020-10-20 | Amkor Technology, Inc. | Encapsulated semiconductor package |

| US11081370B2 (en) | 2004-03-23 | 2021-08-03 | Amkor Technology Singapore Holding Pte. Ltd. | Methods of manufacturing an encapsulated semiconductor device |

| SG130055A1 (en) * | 2005-08-19 | 2007-03-20 | Micron Technology Inc | Microelectronic devices, stacked microelectronic devices, and methods for manufacturing microelectronic devices |

| SG130066A1 (en) | 2005-08-26 | 2007-03-20 | Micron Technology Inc | Microelectronic device packages, stacked microelectronic device packages, and methods for manufacturing microelectronic devices |

| US8012867B2 (en) * | 2006-01-31 | 2011-09-06 | Stats Chippac Ltd | Wafer level chip scale package system |

| US20070187818A1 (en) * | 2006-02-15 | 2007-08-16 | Texas Instruments Incorporated | Package on package design a combination of laminate and tape substrate |

| US7986043B2 (en) * | 2006-03-08 | 2011-07-26 | Stats Chippac Ltd. | Integrated circuit package on package system |

| US7981702B2 (en) * | 2006-03-08 | 2011-07-19 | Stats Chippac Ltd. | Integrated circuit package in package system |

| DE102006016345A1 (de) * | 2006-04-05 | 2007-10-18 | Infineon Technologies Ag | Halbleitermodul mit diskreten Bauelementen und Verfahren zur Herstellung desselben |

| KR100885419B1 (ko) * | 2006-04-26 | 2009-02-24 | 삼성전자주식회사 | 적층형 패키지 구조체 |

| KR100792352B1 (ko) * | 2006-07-06 | 2008-01-08 | 삼성전기주식회사 | 패키지 온 패키지의 바텀기판 및 그 제조방법 |

| US20080029884A1 (en) * | 2006-08-03 | 2008-02-07 | Juergen Grafe | Multichip device and method for producing a multichip device |

| US20080054496A1 (en) * | 2006-08-30 | 2008-03-06 | Neill Thornton | High temperature operating package and circuit design |

| TWM308495U (en) * | 2006-09-08 | 2007-03-21 | Lingsen Precision Ind Ltd | Microelectromechanical module package structure |

| US8154881B2 (en) * | 2006-11-13 | 2012-04-10 | Telecommunication Systems, Inc. | Radiation-shielded semiconductor assembly |

| US7550857B1 (en) | 2006-11-16 | 2009-06-23 | Amkor Technology, Inc. | Stacked redistribution layer (RDL) die assembly package |

| US7608921B2 (en) * | 2006-12-07 | 2009-10-27 | Stats Chippac, Inc. | Multi-layer semiconductor package |

| US7566962B2 (en) * | 2006-12-26 | 2009-07-28 | Advanced Semiconductor Engineering Inc. | Semiconductor package structure and method for manufacturing the same |

| TWI341576B (en) * | 2007-01-24 | 2011-05-01 | Chipmos Technologies Inc | Chip package reducing wiring layers on substrate and its carrier |

| US8063481B2 (en) * | 2007-02-21 | 2011-11-22 | Rambus Inc. | High-speed memory package |

| TWI335070B (en) * | 2007-03-23 | 2010-12-21 | Advanced Semiconductor Eng | Semiconductor package and the method of making the same |

| US7777354B2 (en) * | 2007-06-05 | 2010-08-17 | Stats Chippac Ltd. | Integrated circuit package system with leaded package |

| US9330945B2 (en) * | 2007-09-18 | 2016-05-03 | Stats Chippac Ltd. | Integrated circuit package system with multi-chip module |

| US7888184B2 (en) * | 2008-06-20 | 2011-02-15 | Stats Chippac Ltd. | Integrated circuit packaging system with embedded circuitry and post, and method of manufacture thereof |

| JP2010010437A (ja) * | 2008-06-27 | 2010-01-14 | Stanley Electric Co Ltd | 光半導体装置 |

| TWI473553B (zh) * | 2008-07-03 | 2015-02-11 | Advanced Semiconductor Eng | 晶片封裝結構 |

| KR101297192B1 (ko) * | 2008-11-10 | 2013-08-19 | 삼성전자주식회사 | 화상형성장치, 칩, 및, 칩 패키지 |

| US20100171206A1 (en) * | 2009-01-07 | 2010-07-08 | Chi-Chih Chu | Package-on-Package Device, Semiconductor Package, and Method for Manufacturing The Same |

| TWI499024B (zh) * | 2009-01-07 | 2015-09-01 | Advanced Semiconductor Eng | 堆疊式多封裝構造裝置、半導體封裝構造及其製造方法 |

| US8012797B2 (en) * | 2009-01-07 | 2011-09-06 | Advanced Semiconductor Engineering, Inc. | Method for forming stackable semiconductor device packages including openings with conductive bumps of specified geometries |

| US20100244223A1 (en) * | 2009-03-25 | 2010-09-30 | Cho Namju | Integrated circuit packaging system with an integral-interposer-structure and method of manufacture thereof |

| US8710634B2 (en) * | 2009-03-25 | 2014-04-29 | Stats Chippac Ltd. | Integrated circuit packaging system with an integral-interposer-structure and method of manufacture thereof |

| US8003445B2 (en) * | 2009-03-26 | 2011-08-23 | Stats Chippac Ltd. | Integrated circuit packaging system with z-interconnects having traces and method of manufacture thereof |

| US7960827B1 (en) | 2009-04-09 | 2011-06-14 | Amkor Technology, Inc. | Thermal via heat spreader package and method |

| US8623753B1 (en) * | 2009-05-28 | 2014-01-07 | Amkor Technology, Inc. | Stackable protruding via package and method |

| US8222538B1 (en) | 2009-06-12 | 2012-07-17 | Amkor Technology, Inc. | Stackable via package and method |

| US8533853B2 (en) | 2009-06-12 | 2013-09-10 | Telecommunication Systems, Inc. | Location sensitive solid state drive |

| US8106499B2 (en) * | 2009-06-20 | 2012-01-31 | Stats Chippac Ltd. | Integrated circuit packaging system with a dual substrate package and method of manufacture thereof |

| US20100327419A1 (en) | 2009-06-26 | 2010-12-30 | Sriram Muthukumar | Stacked-chip packages in package-on-package apparatus, methods of assembling same, and systems containing same |

| US8471154B1 (en) | 2009-08-06 | 2013-06-25 | Amkor Technology, Inc. | Stackable variable height via package and method |

| US8743561B2 (en) * | 2009-08-26 | 2014-06-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Wafer-level molded structure for package assembly |

| TWI469283B (zh) * | 2009-08-31 | 2015-01-11 | Advanced Semiconductor Eng | 封裝結構以及封裝製程 |

| US8796561B1 (en) | 2009-10-05 | 2014-08-05 | Amkor Technology, Inc. | Fan out build up substrate stackable package and method |

| EP2309535A1 (en) | 2009-10-09 | 2011-04-13 | Telefonaktiebolaget L M Ericsson (Publ) | Chip package with a chip embedded in a wiring body |

| US8304921B2 (en) * | 2009-11-13 | 2012-11-06 | Stats Chippac Ltd. | Integrated circuit packaging system with interconnect and method of manufacture thereof |

| US8198131B2 (en) | 2009-11-18 | 2012-06-12 | Advanced Semiconductor Engineering, Inc. | Stackable semiconductor device packages |

| JP2011128140A (ja) * | 2009-11-19 | 2011-06-30 | Dainippon Printing Co Ltd | センサデバイス及びその製造方法 |

| TWI411051B (zh) * | 2009-12-02 | 2013-10-01 | Mstar Semiconductor Inc | 封裝層疊方法與結構及其電路板系統 |

| US8937381B1 (en) | 2009-12-03 | 2015-01-20 | Amkor Technology, Inc. | Thin stackable package and method |

| US9691734B1 (en) | 2009-12-07 | 2017-06-27 | Amkor Technology, Inc. | Method of forming a plurality of electronic component packages |

| TWI408785B (zh) | 2009-12-31 | 2013-09-11 | Advanced Semiconductor Eng | 半導體封裝結構 |

| US8569894B2 (en) | 2010-01-13 | 2013-10-29 | Advanced Semiconductor Engineering, Inc. | Semiconductor package with single sided substrate design and manufacturing methods thereof |

| US8536462B1 (en) | 2010-01-22 | 2013-09-17 | Amkor Technology, Inc. | Flex circuit package and method |

| TWI419283B (zh) | 2010-02-10 | 2013-12-11 | Advanced Semiconductor Eng | 封裝結構 |

| TWI411075B (zh) | 2010-03-22 | 2013-10-01 | Advanced Semiconductor Eng | 半導體封裝件及其製造方法 |

| US8981577B2 (en) * | 2010-03-24 | 2015-03-17 | Stats Chippac Ltd. | Integrated circuit packaging system with interconnect and method of manufacture thereof |

| US8278746B2 (en) | 2010-04-02 | 2012-10-02 | Advanced Semiconductor Engineering, Inc. | Semiconductor device packages including connecting elements |

| US8624374B2 (en) | 2010-04-02 | 2014-01-07 | Advanced Semiconductor Engineering, Inc. | Semiconductor device packages with fan-out and with connecting elements for stacking and manufacturing methods thereof |

| US8300423B1 (en) | 2010-05-25 | 2012-10-30 | Amkor Technology, Inc. | Stackable treated via package and method |

| US8294276B1 (en) | 2010-05-27 | 2012-10-23 | Amkor Technology, Inc. | Semiconductor device and fabricating method thereof |

| US8338229B1 (en) | 2010-07-30 | 2012-12-25 | Amkor Technology, Inc. | Stackable plasma cleaned via package and method |

| US8717775B1 (en) | 2010-08-02 | 2014-05-06 | Amkor Technology, Inc. | Fingerprint sensor package and method |

| US9059187B2 (en) * | 2010-09-30 | 2015-06-16 | Ibiden Co., Ltd. | Electronic component having encapsulated wiring board and method for manufacturing the same |

| US8337657B1 (en) | 2010-10-27 | 2012-12-25 | Amkor Technology, Inc. | Mechanical tape separation package and method |

| TWI451546B (zh) | 2010-10-29 | 2014-09-01 | Advanced Semiconductor Eng | 堆疊式封裝結構、其封裝結構及封裝結構之製造方法 |

| TWI455265B (zh) * | 2010-11-01 | 2014-10-01 | 矽品精密工業股份有限公司 | 具微機電元件之封裝結構及其製法 |

| US8482134B1 (en) | 2010-11-01 | 2013-07-09 | Amkor Technology, Inc. | Stackable package and method |

| US9748154B1 (en) | 2010-11-04 | 2017-08-29 | Amkor Technology, Inc. | Wafer level fan out semiconductor device and manufacturing method thereof |

| US8525318B1 (en) | 2010-11-10 | 2013-09-03 | Amkor Technology, Inc. | Semiconductor device and fabricating method thereof |

| US8557629B1 (en) | 2010-12-03 | 2013-10-15 | Amkor Technology, Inc. | Semiconductor device having overlapped via apertures |

| US8535961B1 (en) | 2010-12-09 | 2013-09-17 | Amkor Technology, Inc. | Light emitting diode (LED) package and method |

| TWI445155B (zh) | 2011-01-06 | 2014-07-11 | Advanced Semiconductor Eng | 堆疊式封裝結構及其製造方法 |

| US8171800B1 (en) * | 2011-01-25 | 2012-05-08 | Continental Automotive Systems, Inc. | Differential pressure sensor using dual backside absolute pressure sensing |

| KR101828386B1 (ko) * | 2011-02-15 | 2018-02-13 | 삼성전자주식회사 | 스택 패키지 및 그의 제조 방법 |

| US9721872B1 (en) | 2011-02-18 | 2017-08-01 | Amkor Technology, Inc. | Methods and structures for increasing the allowable die size in TMV packages |

| US9171792B2 (en) | 2011-02-28 | 2015-10-27 | Advanced Semiconductor Engineering, Inc. | Semiconductor device packages having a side-by-side device arrangement and stacking functionality |

| US9013011B1 (en) | 2011-03-11 | 2015-04-21 | Amkor Technology, Inc. | Stacked and staggered die MEMS package and method |

| KR101140113B1 (ko) | 2011-04-26 | 2012-04-30 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스 |

| US8765497B2 (en) * | 2011-09-02 | 2014-07-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Packaging and function tests for package-on-package and system-in-package structures |

| US8653674B1 (en) | 2011-09-15 | 2014-02-18 | Amkor Technology, Inc. | Electronic component package fabrication method and structure |

| US8633598B1 (en) | 2011-09-20 | 2014-01-21 | Amkor Technology, Inc. | Underfill contacting stacking balls package fabrication method and structure |

| US9029962B1 (en) | 2011-10-12 | 2015-05-12 | Amkor Technology, Inc. | Molded cavity substrate MEMS package fabrication method and structure |

| TWI449152B (zh) | 2011-12-21 | 2014-08-11 | Ind Tech Res Inst | 半導體元件堆疊結構 |

| KR20130105175A (ko) * | 2012-03-16 | 2013-09-25 | 삼성전자주식회사 | 보호 층을 갖는 반도체 패키지 및 그 형성 방법 |

| US9385006B2 (en) * | 2012-06-21 | 2016-07-05 | STATS ChipPAC Pte. Ltd. | Semiconductor device and method of forming an embedded SOP fan-out package |

| US9799592B2 (en) | 2013-11-19 | 2017-10-24 | Amkor Technology, Inc. | Semicondutor device with through-silicon via-less deep wells |

| KR101366461B1 (ko) | 2012-11-20 | 2014-02-26 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스 및 그 제조 방법 |

| US10115661B2 (en) | 2013-02-08 | 2018-10-30 | Qualcomm Incorporated | Substrate-less discrete coupled inductor structure |

| AT513747B1 (de) * | 2013-02-28 | 2014-07-15 | Mikroelektronik Ges Mit Beschränkter Haftung Ab | Bestückungsverfahren für Schaltungsträger und Schaltungsträger |

| CN104051411B (zh) | 2013-03-15 | 2018-08-28 | 台湾积体电路制造股份有限公司 | 叠层封装结构 |

| US9768048B2 (en) * | 2013-03-15 | 2017-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Package on-package structure |

| KR101488590B1 (ko) | 2013-03-29 | 2015-01-30 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스 및 그 제조 방법 |

| US20150014852A1 (en) * | 2013-07-12 | 2015-01-15 | Yueli Liu | Package assembly configurations for multiple dies and associated techniques |

| US9478498B2 (en) | 2013-08-05 | 2016-10-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Through package via (TPV) |

| US9524948B2 (en) * | 2013-09-30 | 2016-12-20 | Mediatek Inc. | Package structure |

| KR101607981B1 (ko) | 2013-11-04 | 2016-03-31 | 앰코 테크놀로지 코리아 주식회사 | 반도체 패키지용 인터포저 및 이의 제조 방법, 제조된 인터포저를 이용한 반도체 패키지 |

| KR102190390B1 (ko) | 2013-11-07 | 2020-12-11 | 삼성전자주식회사 | 반도체 패키지 및 이의 제조 방법 |

| CN104760920B (zh) | 2014-01-02 | 2017-01-04 | 意法半导体研发(深圳)有限公司 | 具有mems ic的紧凑电子封装体和相关方法 |

| CN105097680B (zh) * | 2014-05-16 | 2019-06-07 | 恩智浦美国有限公司 | 用于集成电路器件的保护性封装 |

| JP6235423B2 (ja) * | 2014-06-30 | 2017-11-22 | 東芝メモリ株式会社 | 半導体装置 |

| US20170053858A1 (en) * | 2015-08-20 | 2017-02-23 | Intel Corporation | Substrate on substrate package |

| US10229859B2 (en) | 2016-08-17 | 2019-03-12 | Advanced Semiconductor Engineering, Inc. | Semiconductor device package and a method of manufacturing the same |

| US9960328B2 (en) | 2016-09-06 | 2018-05-01 | Amkor Technology, Inc. | Semiconductor device and manufacturing method thereof |

| US9859255B1 (en) * | 2016-10-01 | 2018-01-02 | Intel Corporation | Electronic device package |

| KR102359904B1 (ko) | 2019-09-16 | 2022-02-08 | 삼성전자주식회사 | 반도체 패키지 |

| US20230065615A1 (en) * | 2021-08-27 | 2023-03-02 | Advanced Semiconductor Engineering, Inc. | Electronic device |

| TWI808835B (zh) * | 2022-07-20 | 2023-07-11 | 強茂股份有限公司 | 晶圓級晶片尺寸封裝件及方法 |

| TWI843347B (zh) * | 2022-12-20 | 2024-05-21 | 矽品精密工業股份有限公司 | 電子封裝件及其製法 |

Family Cites Families (109)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5446620A (en) * | 1990-08-01 | 1995-08-29 | Staktek Corporation | Ultra high density integrated circuit packages |

| FR2670322B1 (fr) * | 1990-12-05 | 1997-07-04 | Matra Espace | Modules de memoire a l'etat solide et dispositifs de memoire comportant de tels modules |

| US5222014A (en) * | 1992-03-02 | 1993-06-22 | Motorola, Inc. | Three-dimensional multi-chip pad array carrier |

| US5422435A (en) * | 1992-05-22 | 1995-06-06 | National Semiconductor Corporation | Stacked multi-chip modules and method of manufacturing |

| FR2694840B1 (fr) | 1992-08-13 | 1994-09-09 | Commissariat Energie Atomique | Module multi-puces à trois dimensions. |

| US5340771A (en) * | 1993-03-18 | 1994-08-23 | Lsi Logic Corporation | Techniques for providing high I/O count connections to semiconductor dies |

| US5444296A (en) * | 1993-11-22 | 1995-08-22 | Sun Microsystems, Inc. | Ball grid array packages for high speed applications |

| US5436203A (en) * | 1994-07-05 | 1995-07-25 | Motorola, Inc. | Shielded liquid encapsulated semiconductor device and method for making the same |

| MY112145A (en) * | 1994-07-11 | 2001-04-30 | Ibm | Direct attachment of heat sink attached directly to flip chip using flexible epoxy |

| US5652185A (en) | 1995-04-07 | 1997-07-29 | National Semiconductor Corporation | Maximized substrate design for grid array based assemblies |

| US5719440A (en) * | 1995-12-19 | 1998-02-17 | Micron Technology, Inc. | Flip chip adaptor package for bare die |

| US5952725A (en) * | 1996-02-20 | 1999-09-14 | Micron Technology, Inc. | Stacked semiconductor devices |

| US7166495B2 (en) * | 1996-02-20 | 2007-01-23 | Micron Technology, Inc. | Method of fabricating a multi-die semiconductor package assembly |

| US6075289A (en) * | 1996-10-24 | 2000-06-13 | Tessera, Inc. | Thermally enhanced packaged semiconductor assemblies |

| US5994166A (en) * | 1997-03-10 | 1999-11-30 | Micron Technology, Inc. | Method of constructing stacked packages |

| US5898219A (en) * | 1997-04-02 | 1999-04-27 | Intel Corporation | Custom corner attach heat sink design for a plastic ball grid array integrated circuit package |

| JPH10294423A (ja) * | 1997-04-17 | 1998-11-04 | Nec Corp | 半導体装置 |

| US5982633A (en) * | 1997-08-20 | 1999-11-09 | Compaq Computer Corporation | Opposed ball grid array mounting |

| JP3834426B2 (ja) * | 1997-09-02 | 2006-10-18 | 沖電気工業株式会社 | 半導体装置 |

| CA2218307C (en) * | 1997-10-10 | 2006-01-03 | Gennum Corporation | Three dimensional packaging configuration for multi-chip module assembly |

| JP3644662B2 (ja) * | 1997-10-29 | 2005-05-11 | 株式会社ルネサステクノロジ | 半導体モジュール |

| JPH11219984A (ja) | 1997-11-06 | 1999-08-10 | Sharp Corp | 半導体装置パッケージおよびその製造方法ならびにそのための回路基板 |

| US5899705A (en) * | 1997-11-20 | 1999-05-04 | Akram; Salman | Stacked leads-over chip multi-chip module |

| JP2000208698A (ja) * | 1999-01-18 | 2000-07-28 | Toshiba Corp | 半導体装置 |

| TW432550B (en) * | 1998-02-07 | 2001-05-01 | Siliconware Precision Industries Co Ltd | Method of encapsulating a chip |

| SG75958A1 (en) * | 1998-06-01 | 2000-10-24 | Hitachi Ulsi Sys Co Ltd | Semiconductor device and a method of producing semiconductor device |

| US6451624B1 (en) | 1998-06-05 | 2002-09-17 | Micron Technology, Inc. | Stackable semiconductor package having conductive layer and insulating layers and method of fabrication |

| US6034875A (en) * | 1998-06-17 | 2000-03-07 | International Business Machines Corporation | Cooling structure for electronic components |

| US5977640A (en) * | 1998-06-26 | 1999-11-02 | International Business Machines Corporation | Highly integrated chip-on-chip packaging |

| JP2000058691A (ja) | 1998-08-07 | 2000-02-25 | Sharp Corp | ミリ波半導体装置 |

| US6201302B1 (en) * | 1998-12-31 | 2001-03-13 | Sampo Semiconductor Corporation | Semiconductor package having multi-dies |

| JP2000228468A (ja) * | 1999-02-05 | 2000-08-15 | Mitsubishi Electric Corp | 半導体チップ及び半導体装置 |

| JP3685947B2 (ja) * | 1999-03-15 | 2005-08-24 | 新光電気工業株式会社 | 半導体装置及びその製造方法 |