JP3998373B2 - 半導体集積回路装置の製造方法 - Google Patents

半導体集積回路装置の製造方法 Download PDFInfo

- Publication number

- JP3998373B2 JP3998373B2 JP18745099A JP18745099A JP3998373B2 JP 3998373 B2 JP3998373 B2 JP 3998373B2 JP 18745099 A JP18745099 A JP 18745099A JP 18745099 A JP18745099 A JP 18745099A JP 3998373 B2 JP3998373 B2 JP 3998373B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- groove

- conductive film

- forming

- photoresist

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 247

- 238000004519 manufacturing process Methods 0.000 title claims description 118

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 199

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 136

- 229910052814 silicon oxide Inorganic materials 0.000 claims abstract description 136

- 239000000758 substrate Substances 0.000 claims description 97

- 238000000034 method Methods 0.000 claims description 81

- 238000005530 etching Methods 0.000 claims description 70

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 67

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 67

- 239000010949 copper Substances 0.000 claims description 30

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 29

- 229910052802 copper Inorganic materials 0.000 claims description 29

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 25

- 229910052721 tungsten Inorganic materials 0.000 claims description 24

- 239000010937 tungsten Substances 0.000 claims description 24

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 23

- 239000000126 substance Substances 0.000 claims description 20

- 238000005498 polishing Methods 0.000 claims description 17

- 230000001678 irradiating effect Effects 0.000 claims description 11

- 238000000059 patterning Methods 0.000 claims description 4

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 3

- 229910000838 Al alloy Inorganic materials 0.000 claims description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 abstract description 44

- 238000001312 dry etching Methods 0.000 abstract description 28

- 238000004528 spin coating Methods 0.000 abstract 1

- 239000010408 film Substances 0.000 description 768

- 239000010410 layer Substances 0.000 description 56

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 45

- 238000003860 storage Methods 0.000 description 34

- 238000005229 chemical vapour deposition Methods 0.000 description 26

- 239000003990 capacitor Substances 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 22

- 239000002184 metal Substances 0.000 description 22

- 230000004888 barrier function Effects 0.000 description 21

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 18

- 229910001936 tantalum oxide Inorganic materials 0.000 description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 229910052710 silicon Inorganic materials 0.000 description 17

- 239000010703 silicon Substances 0.000 description 17

- 238000002955 isolation Methods 0.000 description 16

- 238000004380 ashing Methods 0.000 description 15

- 239000012535 impurity Substances 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 13

- 238000004544 sputter deposition Methods 0.000 description 12

- 230000008569 process Effects 0.000 description 11

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 10

- 229910052698 phosphorus Inorganic materials 0.000 description 10

- 239000011574 phosphorus Substances 0.000 description 10

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 7

- 238000000151 deposition Methods 0.000 description 6

- 230000009977 dual effect Effects 0.000 description 6

- 239000000463 material Substances 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 239000012790 adhesive layer Substances 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 3

- 239000012141 concentrate Substances 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000007517 polishing process Methods 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- -1 PLZT Chemical class 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000007772 electrode material Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 1

- 229910002113 barium titanate Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000007788 roughening Methods 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- HSXKFDGTKKAEHL-UHFFFAOYSA-N tantalum(v) ethoxide Chemical compound [Ta+5].CC[O-].CC[O-].CC[O-].CC[O-].CC[O-] HSXKFDGTKKAEHL-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/7684—Smoothing; Planarisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76865—Selective removal of parts of the layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

- H01L21/76879—Filling of holes, grooves or trenches, e.g. vias, with conductive material by selective deposition of conductive material in the vias, e.g. selective C.V.D. on semiconductor material, plating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/82—Electrodes with an enlarged surface, e.g. formed by texturisation

- H01L28/90—Electrodes with an enlarged surface, e.g. formed by texturisation having vertical extensions

- H01L28/91—Electrodes with an enlarged surface, e.g. formed by texturisation having vertical extensions made by depositing layers, e.g. by depositing alternating conductive and insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/318—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor the storage electrode having multiple segments

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

- H01L28/82—Electrodes with an enlarged surface, e.g. formed by texturisation

- H01L28/84—Electrodes with an enlarged surface, e.g. formed by texturisation being a rough surface, e.g. using hemispherical grains

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、半導体集積回路装置の製造技術に関し、特に、絶縁膜に形成した溝またはスルーホールの内部に導電層を形成するプロセスに適用して有効な技術に関する。

【0002】

【従来の技術】

DRAM(Dynamic Random Access Memory)のメモリセルは、半導体基板の主面上にマトリクス状に配置された複数のワード線と複数のビット線との交点に配置され、1個のメモリセル選択用MISFET(Metal Insulator Semiconductor Field Effect Transistor) とこれに直列に接続された1個の情報蓄積用容量素子(キャパシタ)とで構成されている。

【0003】

上記メモリセル選択用MISFETは、周囲を素子分離領域で囲まれた活性領域に形成され、主としてゲート酸化膜、ワード線と一体に構成されたゲート電極およびソース、ドレインを構成する一対の半導体領域で構成されている。ビット線は、メモリセル選択用MISFETの上部に配置され、その延在方向に隣接する2個のメモリセル選択用MISFETによって共有されるソース、ドレインの一方と電気的に接続されている。情報蓄積用容量素子は、同じくメモリセル選択用MISFETの上部に配置され、上記ソース、ドレインの他方と電気的に接続されている。

【0004】

特開平7−7084号公報は、メモリセル選択用MISFETの上部に情報蓄積用容量素子を配置するスタックド・キャパシタ(Stacked Capacitor) 構造のDRAMを開示している。この公報に記載されたDRAMは、メモリセルの微細化に伴う情報蓄積用容量素子の蓄積電荷量の減少を補うために、ビット線の上部に配置した情報蓄積用容量素子の下部電極(蓄積電極)を円筒状に加工することによってその表面積を増やし、その上部に容量絶縁膜と上部電極(プレート電極)とを形成している。

【0005】

また、特開平11−17144号公報は、上記した円筒状の下部電極の内側底部に絶縁膜からなる補強部材を形成することによって、下部電極の機械的強度を向上させ、製造工程の途中で円筒状の下部電極が倒れたりする不良を防止している。特開平5−129550号公報の[0025]〜[0028]および図5(a)〜図5(c)には、溝の内部および外部のホトレジストを塗布後に露光量を制御して全面露光して溝内部にホトレジストを残して溝の上部を加工する開示がある。特開平7−66284号公報の[0015]〜[0016]および図1(c)、(d)、(e)には、SOIの酸化膜分離溝の形成において分離溝内を含むホトレジストを塗布後全面露光して溝内部のみにホトレジストを残してマスク材のエッチング除去時に埋め込み酸化膜のエッチングを防止して、その後ホトレジストを除去後溝内部に絶縁膜を埋め込む開示がある。特開平8−335634号公報の[0012]および図1(e)、(f)には、デュアルダマシン配線の形成においてコンタクトホール内に有機膜を埋め込んだ状態で配線溝を形成するために絶縁膜をエッチングしたのち有機膜を除去してデュアルダマシン配線溝を形成する開示がある。

【0006】

【発明が解決しようとする課題】

本発明者は、ビット線の上部に堆積した厚い酸化シリコン膜に溝を形成し、この溝の内部に情報蓄積用容量素子の下部電極(蓄積電極)を形成する技術を開発している。

【0007】

上記情報蓄積用容量素子を形成するには、一例としてビット線の上部に厚い酸化シリコン膜を形成した後、フォトレジスト膜をマスクにしたドライエッチングで上記酸化シリコン膜に溝を形成する。次に、溝の内部および酸化シリコン膜の上部に多結晶シリコン膜を堆積した後、溝の内部の多結晶シリコン膜をSOG(Spin On Glass) などの塗布膜で保護し、酸化シリコン膜の上部の多結晶シリコン膜をドライエッチングで除去することによって、溝の内部に情報蓄積用容量素子の下部電極として使用される多結晶シリコン膜を形成する。

【0008】

次に、溝の内部の多結晶シリコン膜を覆っているSOG膜を除去する。SOG膜の除去は、酸化シリコン膜とSOG膜とのエッチング選択比の差を利用したドライエッチングまたはウェットエッチングによって行う。

【0009】

次に、多結晶シリコン膜の上部に酸化タンタル( Ta2 O5)膜などの誘電体膜を堆積した後、酸化タンタル膜の上部に窒化チタンなどの導電膜を堆積することによって、多結晶シリコン膜で構成された下部電極、酸化タンタル膜で構成された容量絶縁膜および窒化チタンなどの導電膜で構成された上部電極からなる情報蓄積用容量素子を形成する。

【0010】

上記情報蓄積用容量素子は、酸化シリコン膜に形成した溝の内部に下部電極を形成するので、従来の円筒状の下部電極のように、製造工程の途中で下部電極が倒れたりする不具合が生じないという利点がある。その反面、上記情報蓄積用容量素子の下部電極は、円筒の内壁および外壁を蓄積電荷量確保のための有効領域として利用する従来の下部電極に比べて表面積が少ないので、蓄積電荷量を確保するためには、下部電極が形成される溝を深くしたり、下部電極の表面に凹凸を形成したりすることによって表面積を増やす工夫が必要となる。

【0011】

しかし、酸化シリコン膜とSOG膜とのエッチング選択比の差を利用してSOG膜を選択的に除去する前記下部電極の製造方法は、酸化シリコン膜とSOG膜とのエッチング選択比が十分に大きくないために、溝の内部の多結晶シリコン膜を覆っているSOG膜をエッチングで除去する際、溝の外部の酸化シリコン膜もある程度エッチングされてその上面が下方に後退してしまう。特に、多結晶シリコン膜の表面に凹凸を形成したような場合は、凹凸の隙間に残ったSOG膜を除去するためのオーバーエッチングが必要となるため、上記した酸化シリコン膜の後退量が大きくなる。

【0012】

上記のような酸化シリコン膜の後退が生じると、溝の内部に形成された多結晶シリコン膜の上端部が溝の開孔端よりも上方に突き出てしまうために、情報蓄積用容量素子の表面の平坦性が低下したり、多結晶シリコン膜の上端部に電界が集中して情報蓄積用容量素子のリーク電流が増加したりするといった不具合を引き起こす。

【0013】

本発明の目的は、絶縁膜に形成された溝の内部に下部電極を形成する情報蓄積用容量素子を備えたDRAMの製造歩留まりを向上させる技術を提供することにある。

【0014】

本発明の他の目的は、絶縁膜に形成した溝またはスルーホールの内部に導電層を形成する技術を提供することにある。

【0015】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0016】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0017】

(1)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0018】

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜に溝またはスルーホールを形成する工程、

(b)前記溝またはスルーホールの内部および前記第1絶縁膜の上部に、前記溝またはスルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(c)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトレジスト膜を露光する工程、

(d)前記フォトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトレジスト膜の未露光部を残す工程、

(e)前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝またはスルーホールの内部に前記第2導電膜を残す工程。

【0019】

(2)本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程における前記第2導電膜の除去を、前記フォトレジスト膜をマスクにしたエッチングによって行う。

【0020】

(3)本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程における前記第2導電膜の除去を化学機械研磨法によって行う。

【0021】

(4)本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(d)工程における前記フォトレジスト膜の除去を、前記フォトレジスト膜を現像することによって行う。

【0022】

(5)本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程の後、

(f)前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部に露出した前記第2導電膜の表面に第3導電膜を選択成長させることによって、前記溝またはスルーホールの内部に前記第3導電膜を埋め込む工程をさらに含む。

【0023】

(6)本発明の半導体集積回路装置の製造方法は、前記(5)において、前記第2導電膜が窒化チタンまたはタングステンからなる。

【0024】

(7)本発明の半導体集積回路装置の製造方法は、前記(5)において、前記第3導電膜がタングステンまたはアルミニウム合金からなる。

【0025】

(8)本発明の半導体集積回路装置の製造方法は、前記(5)において、前記(f)工程の後、

(h)前記第1絶縁膜の上部に第4導電膜を形成し、前記溝またはスルーホールの内部の前記第3導電膜を介して前記第4導電膜と前記第1導電膜とを電気的に接続する工程をさらに含む。

【0026】

(9)本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程の後、

(f)前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部および前記第1絶縁膜の上部に第5導電膜を形成する工程、

(g)前記第5導電膜の表面に第6導電膜を選択成長させた後、前記溝またはスルーホールの外部の前記第6導電膜および前記第5導電膜を除去し、前記溝またはスルーホールの内部に前記第6導電膜および前記第5導電膜を残す工程をさらに含む。

【0027】

(10)本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第2導電膜が窒化チタンまたは窒化タンタルからなる。

【0028】

(11)本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第5導電膜および前記第6導電膜が銅からなる。

【0029】

(12)本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第6導電膜および前記第5導電膜の除去を、化学機械研磨法によって行う。

【0030】

(13)本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

【0031】

(a)半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方に電気的に接続される第1導電膜を形成する工程、

(b)前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

(c)前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(d)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

(e)前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(f)前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

(g)前記溝の内部の前記フォトレジスト膜を除去した後、前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

【0032】

(14)本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

【0033】

(a)半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方に電気的に接続される第1導電膜を形成する工程、

(b)前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

(c)前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続されるアモルファスシリコンからなる第2導電膜を形成する工程、

(d)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

(e)前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(f)前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

(g)前記溝の内部の前記フォトレジスト膜を除去した後、前記溝の内部に露出した前記第2導電膜の表面に凹凸を形成する工程、

(h)前記第2導電膜を熱処理することによって多結晶化する工程、

(i)前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

【0034】

(15)本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

【0035】

(a)半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方に電気的に接続される第1導電膜を形成する工程、

(b)前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

(c)前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続されるアモルファスシリコンからなる第2導電膜を形成する工程、

(d)前記第2導電膜の表面に凹凸を形成する工程、

(e)前記第2導電膜を熱処理することによって多結晶化する工程、

(f)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

(g)前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(h)前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

(i)前記溝の内部の前記フォトレジスト膜を除去した後、前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

【0036】

(16)本発明の半導体集積回路装置の製造方法は、前記(14)または(15)において、前記フォトレジスト膜で覆われていない領域の前記第2導電膜の除去を、前記フォトレジスト膜をマスクにしたエッチングによって行う。

【0037】

(17)本発明の半導体集積回路装置の製造方法は、前記(14)、(15)または(16)において、前記第2導電膜の表面の前記凹凸を、前記アモルファスシリコンの表面にシリコン粒を成長させることによって形成する。

【0038】

(18)本発明の半導体集積回路装置の製造方法は、前記(1)〜(17)のいずれか一項において、前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去する際、前記溝の内部の前記第2導電膜の上端部を、前記溝の開孔端よりも下方に後退させる。

【0039】

(19)本発明の半導体集積回路装置の製造方法は、前記(18)において、前記第2導電膜の上端部の後退量が、前記第2導電膜の表面に形成された前記凹凸の径とほぼ等しい。

【0040】

(20)本発明の半導体集積回路装置の製造方法は、前記(13)〜(19)のいずれか一項において、前記第2絶縁膜が酸化シリコン膜である。

【0041】

(21)本発明の半導体集積回路装置の製造方法は、前記(13)〜(20)のいずれか一項において、前記第3絶縁膜が高誘電率膜または強誘電体膜である。

【0042】

(22)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0043】

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜にスルーホールを形成する工程、

(b)前記スルーホールの内部および前記第1絶縁膜の上部にフォトレジスト膜を形成した後、前記スルーホールの内部の前記フォトレジスト膜の一部および配線溝形成領域の前記フォトレジスト膜を選択的に露光する工程、

(c)前記フォトレジスト膜の露光部を除去し、前記第1絶縁膜の上部の一部および前記スルーホールの内部の一部に前記フォトレジスト膜の未露光部を残す工程、

(d)前記フォトレジスト膜をマスクにして前記第1絶縁膜をエッチングすることにより、前記第1絶縁膜に配線溝を形成する工程、

(e)前記フォトレジスト膜を除去した後、前記第1絶縁膜の上部、前記配線溝の内部および前記スルーホールの内部に、前記スルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(f)前記第1絶縁膜の上部の前記第2導電膜を化学機械研磨法で除去することによって、前記配線溝の内部および前記スルーホールの内部に前記第2導電膜からなる埋込み配線を形成する工程。

【0044】

(23)本発明の半導体集積回路装置の製造方法は、前記(22)において、前記第2導電膜が銅からなる。

【0045】

(24)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0046】

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜および前記第1導電膜をパターニングすることによって、その上部が前記第1絶縁膜で覆われた前記第1導電膜からなるゲート電極を形成する工程、

(b)前記ゲート電極の両側の前記半導体基板に半導体領域を形成する工程、

(c)前記ゲート電極が形成された前記半導体基板上に第2絶縁膜を形成した後、前記第2絶縁膜の上部に、前記第1絶縁膜および前記第2絶縁膜とはエッチングの選択比が異なる第3絶縁膜を形成する工程、

(d)第1フォトレジスト膜をマスクにして前記第3絶縁膜をエッチングすることにより、前記半導体領域の上部の前記第2絶縁膜に達する第1溝および前記ゲート電極の上部の前記第2絶縁膜に達する第2溝を形成する工程、

(e)前記第1フォトレジスト膜を除去した後、前記第1、第2溝の内部および前記第3絶縁膜の上部に第2フォトレジスト膜を形成する工程、

(f)前記第2フォトレジスト膜に露光光を照射することによって、前記第2溝の内部および前記第3絶縁膜の上部の前記第2フォトレジスト膜を露光した後、前記第2フォトレジスト膜の露光部を除去することによって、前記第1溝の内部に前記第2フォトレジスト膜の未露光部を残す工程、

(g)前記第1溝の内部の前記第2フォトレジスト膜をマスクにしたエッチングで前記第2溝の底部の前記第2絶縁膜およびその下部の前記第1絶縁膜の一部をエッチングする工程、

(h)前記第2フォトレジスト膜を除去した後、前記第1溝の下部の前記第2絶縁膜および前記第2溝の下部の前記第1絶縁膜をエッチングすることによって、前記半導体領域の上部に第1コンタクトホールを形成し、前記ゲート電極の上部に第2コンタクトホールを形成する工程。

【0047】

(25)本発明の半導体集積回路装置の製造方法は、前記(25)において、前記第1絶縁膜および前記第2絶縁膜が窒化シリコンからなり、前記第3絶縁膜が酸化シリコン膜からなる。

【0048】

(26)本発明の半導体集積回路装置の製造方法は、前記(24)において、前記(h)工程の後、

(i)前記第1、第2コンタクトホールの内部および前記第3絶縁膜の上部に第2導電膜を形成する工程、

(j)前記第2導電膜をパターニングすることによって、前記第1コンタクトホールを通じて前記半導体領域に電気的に接続される第1配線および前記第2コンタクトホールを通じて前記ゲート電極に電気的に接続される第2配線を形成する工程をさらに含む。

【0049】

(27)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0050】

(a)半導体基板の主面上に形成した第1絶縁膜に溝を形成した後、前記溝の内部および前記第1絶縁膜の上部にシリコン層を形成する工程、

(b)前記溝の内部の前記シリコン層の上部に選択的に第2絶縁膜を形成し、前記溝の外部の前記シリコン層を選択的に除去する工程、

(c)前記溝の内部の前記第2絶縁膜を除去した後、前記シリコン層に凹凸を形成する工程、

(d)前記凹凸が形成された前記シリコン層の上部に誘電体膜を形成し、前記誘電体膜の上部に導電膜を形成する工程。

【0051】

(28)本発明の半導体集積回路装置の製造方法は、前記(27)において、前記シリコン層がアモルファスシリコンからなる。

【0052】

(29)本発明の半導体集積回路装置の製造方法は、前記(27)において、前記第1絶縁膜が酸化シリコンからなり、前記第2絶縁膜がフォトレジストからなる。

【0053】

(30)本発明の半導体集積回路装置の製造方法は、前記(27)において、前記シリコン層の前記凹凸を、前記シリコン層の表面にシリコン粒を成長させることによって形成する。

【0054】

(31)本発明の半導体集積回路装置の製造方法は、前記(29)において、前記(b)工程が、

(b−1)前記溝の内部および前記第1絶縁膜の上部にフォトレジスト膜を形成した後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を選択的に露光する工程、

(b−2)前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(b−3)前記フォトレジスト膜をマスクにしたエッチングで前記溝の外部の前記シリコン層を除去する工程を含む。

【0055】

(32)本発明の半導体集積回路装置の製造方法は、(27)〜(31)のいずれか一項において、前記凹凸が形成された前記シリコン層が容量素子の第1電極を構成し、前記誘電体膜が前記容量素子の容量絶縁膜を構成し、前記導電膜が前記容量素子の第2電極を構成する。

【0056】

(33)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0057】

(a)半導体基板の主面上に形成した第1絶縁膜に溝を形成した後、前記溝の内部および前記第1絶縁膜の上部に導電層を形成する工程、

(b)前記導電層の上部にフォトレジスト膜を形成した後、前記フォトレジスト膜に露光光を照射することによって、前記第1絶縁膜の上部の前記フォトレジスト膜を完全に露光し、前記溝の内部の前記フォトレジスト膜の一部を露光する工程、

(c)前記フォトレジスト膜を現像することによって、完全に露光された領域の前記フォトレジスト膜を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(d)前記フォトレジスト膜で覆われていない領域の前記導電層を選択的に除去する工程。

【0058】

(34)本発明の半導体集積回路装置の製造方法は、前記(33)において、前記導電層の選択的な除去を、前記フォトレジスト膜をマスクにしたエッチングによって行う。

【0059】

(35)本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0060】

(a)半導体基板の主面上に酸化シリコン膜を形成した後、前記酸化シリコン膜に溝を形成する工程、

(b)前記溝の内部および前記酸化シリコン膜の上部に第1導電膜を形成する工程、

(c)前記第1導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

(d)前記フォトレジスト膜の露光部を現像により除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(e)前記フォトレジスト膜をマスクにしたエッチングで前記酸化シリコン膜の上部の前記第1導電膜を除去する工程、

(f)前記溝の内部の前記フォトレジスト膜を除去することによって、前記溝の内部に前記第1導電膜を選択的に形成する工程。

【0061】

(36)本発明の半導体集積回路装置の製造方法は、前記(35)において、前記(f)工程における前記フォトレジスト膜の除去を、アッシングによって行う。

【0062】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。

【0063】

(実施の形態1)

本発明の実施形態1であるDRAM(Dynamic Random Access Memory)の製造方法を図1〜図21を用いて工程順に説明する。

【0064】

まず、図1に示すように、例えばp型の単結晶シリコンからなる半導体基板(以下、単に基板という)1の主面に素子分離溝2を形成した後、基板1にp型不純物(ホウ素(B))をイオン注入してp型ウエル3を形成する。素子分離溝2を形成するには、例えば基板1の素子分離領域をエッチングして溝を形成した後、溝の内部および基板1上にCVD(Chemical Vapor Deposition )法で酸化シリコン膜5を堆積し、続いて溝の外部の酸化シリコン膜5を化学機械研磨(Chemical Mechanical Polishing; CMP) 法で除去して溝の内部のみに酸化シリコン膜5を残す。

【0065】

次に、基板1をスチーム酸化してp型ウエル3の表面にゲート酸化膜6を形成した後、ゲート酸化膜6上にゲート電極7(ワード線WL)を形成する。ゲート電極7(ワード線WL)を形成するには、例えば基板1上にリン(P)などのn型不純物をドープした多結晶シリコン膜をCVD法で堆積し、続いてその上部にスパッタリング法で窒化タングステン(WN)膜およびタングステン(W)膜を堆積し、さらにその上部にCVD法で窒化シリコン膜8を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでこれらの膜をパターニングする。

【0066】

次に、図2に示すように、ゲート電極7の両側のp型ウエル3にリン(P)などのn型不純物をイオン注入してn- 型半導体領域9を形成し、続いてゲート電極7(ワード線WL)の上部にCVD法で窒化シリコン膜10および酸化シリコン膜11を堆積した後、酸化シリコン膜11の表面を化学機械研磨法で平坦化する。

【0067】

次に、図3に示すように、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜11および窒化シリコン膜10をドライエッチングすることにより、n- 型半導体領域9の上部にコンタクトホール12、13を形成する。酸化シリコン膜11のエッチングは、窒化シリコン膜10に対する酸化シリコン膜11のエッチング選択比が十分に大きくなる条件で行い、下層の窒化シリコン膜10が除去されないようにする。また、窒化シリコン膜10のエッチングは、基板1に対する窒化シリコン膜10のエッチング選択比が十分に大きくなる条件で行い、基板1が深く削れないようにする。さらに、窒化シリコン膜10のエッチングは、窒化シリコン膜10を異方的にエッチングする条件で行い、ゲート電極7(ワード線WL)の側壁に窒化シリコン膜10を残す。これにより、コンタクトホール12、13がゲート電極7(ワード線WL)に対して自己整合(セルフアライン)で形成されるので、コンタクトホール12、13とゲート電極7(ワード線WL)との合わせ余裕が不要となり、DRAMのメモリセルサイズを縮小することができる。

【0068】

次に、コンタクトホール12、13を通じてp型ウエル3にリンまたはヒ素(As)などのn型不純物をイオン打ち込みすることによって、n+ 型半導体領域14(ソース、ドレイン)を形成する。ここまでの工程で、ゲート酸化膜6、ゲート電極7およびn+ 型半導体領域14(ソース、ドレイン)を有するnチャネル型のメモリセル選択用MISFETQsが形成される。

【0069】

次に、コンタクトホール12、13の内部にプラグ15を形成する。プラグ15を形成するには、例えばコンタクトホール12、13の内部および酸化シリコン膜11の上部にリンなどのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積した後、酸化シリコン膜11の上部の多結晶シリコン膜をドライエッチング(または化学機械研磨法)で除去し、多結晶シリコン膜をコンタクトホール12、13の内部のみに残す。

【0070】

次に、図4に示すように、酸化シリコン膜11の上部にCVD法で酸化シリコン膜16を堆積し、続いてフォトレジスト膜(図示せず)をマスクにしたドライエッチングでコンタクトホール12の上部の酸化シリコン膜16にスルーホール17を形成した後、スルーホール17の内部にプラグ18を形成し、さらにプラグ18の上部にビット線BLを形成する。

【0071】

プラグ18を形成するには、例えばスルーホール17の内部および酸化シリコン膜16の上部にスパッタリング法で窒化チタン膜およびタングステン膜を堆積した後、酸化シリコン膜16の上部の窒化チタン膜およびタングステン膜を化学機械研磨法で除去し、これらの膜をスルーホール17の内部のみに残す。また、ビット線BLを形成するには、例えば酸化シリコン膜16の上部にスパッタリング法でタングステン膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングでタングステン膜をパターニングする。ビット線BLは、スルーホール17内のプラグ18およびコンタクトホール12内のプラグ15を介してメモリセル選択用MISFETQsのソース、ドレインの一方(n+ 型半導体領域14)と電気的に接続される。

【0072】

次に、酸化シリコン膜16の上部にCVD法で酸化シリコン膜19を堆積し、続いてフォトレジスト膜(図示せず)をマスクにしたドライエッチングでコンタクトホール13の上部の酸化シリコン膜19、16にスルーホール21を形成した後、スルーホール21の内部にプラグ22を形成する。プラグ22を形成するには、例えばスルーホール21の内部および酸化シリコン膜19の上部にリンなどのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積した後、酸化シリコン膜19の上部の多結晶シリコン膜をドライエッチング(または化学機械研磨法)で除去し、多結晶シリコン膜をスルーホール21の内部のみに残す。

【0073】

次に、図5に示すように、酸化シリコン膜19の上部にCVD法で窒化シリコン膜23を堆積し、続いて窒化シリコン膜23の上部にCVD法で酸化シリコン膜24を堆積した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜24および窒化シリコン膜23をドライエッチングすることにより、スルーホール21の上部に溝25を形成する。後述する情報蓄積用容量素子Cの下部電極は、この溝25の内壁に沿って形成されるので、下部電極の表面積を大きくして蓄積電荷量を増やすためには、酸化シリコン膜24を厚い膜厚(例えば1μm 以上)で堆積する必要がある。

【0074】

酸化シリコン膜24のエッチングは、窒化シリコン膜23に対する酸化シリコン膜24のエッチング選択比が大きくなる条件で行い、下層の窒化シリコン膜23が除去されないようにする。また、窒化シリコン膜23のエッチングは、酸化シリコン膜19に対する窒化シリコン膜23のエッチング選択比が大きくなる条件で行い、下層の酸化シリコン膜19が深く削れないようにする。このように、厚い膜厚の酸化シリコン膜24の下層にエッチングストッパとなる窒化シリコン膜23を設けることにより、酸化シリコン膜24をエッチングして溝25を形成する際に下層の酸化シリコン膜19が過剰にエッチングされる不具合が防止されるので、深い溝25を高い寸法精度で形成することができる。

【0075】

次に、図6に示すように、溝25の内部および酸化シリコン膜24の上部にリンなどのn型不純物をドープしたアモルファスシリコン膜26AをCVD法で堆積する。アモルファスシリコン膜26Aは、溝25の内壁に沿って堆積される程度の薄い膜厚(例えば50〜60nm程度)で形成する。

【0076】

次に、図7に示すように、アモルファスシリコン膜26Aの上部にフォトレジスト膜30をスピン塗布する。フォトレジスト膜30は、露光部が現像液に可溶となるポジ型フォトレジスト(例えばノボラック樹脂系フォトレジスト)を使用する。

【0077】

次に、図8に示すように、フォトレジスト膜30の全面に露光光を照射する。このとき、溝25の外部や溝25の開孔端近傍のフォトレジスト膜30は露光されるが、深い溝25の内部のフォトレジスト膜2は露光量が不足するために露光されない。

【0078】

次に、図9に示すように、アルカリ水溶液などを使ってフォトレジスト膜30を現像する。このとき、露光部である溝25の外部や溝25の開孔端近傍のフォトレジスト膜30は現像液に可溶となるために除去されるが、未露光部である溝25の内部のフォトレジスト膜30は除去されない。この結果、溝25の外部の酸化シリコン膜24上にはアモルファスシリコン膜26Aが露出するが、溝25の内部のアモルファスシリコン膜26Aは、溝25の開孔端近傍を除き、フォトレジスト膜30で覆われたままとなる。

【0079】

次に、図10に示すように、フォトレジスト膜30で覆われていない領域、すなわち溝25の外部および溝25の開孔端近傍のアモルファスシリコン膜26Aをドライエッチングで除去する。アモルファスシリコン膜26Aのエッチングは、フォトレジスト膜30に対するアモルファスシリコン膜26Aのエッチング選択比が十分に大きくなる条件で行い、溝25の内部のフォトレジスト膜30で覆われたアモルファスシリコン膜26Aが露出して削られないようにする。

【0080】

また、このエッチングは、アモルファスシリコン膜26Aを異方的にエッチングする条件で行い、溝25の開孔端近傍においてアモルファスシリコン膜26の上端部を溝25の開孔端よりも僅かに下方に後退させることが望ましい。これにより、溝25の内部に形成される下部電極の先端部(上端部)に電界が集中し難くなるため、情報蓄積用容量素子のリーク電流を低減することができる。なお、アモルファスシリコン膜26の後退量は、次の工程でアモルファスシリコン膜26Aの表面に成長させるシリコン粒の直径とほぼ同程度(約50nm)とするのがよい。後退量が少なすぎるとアモルファスシリコン膜26の上端部に成長したシリコン粒が溝25の開孔端よりも上方に突出するために、そこに電界が集中し易くなる。他方、後退量が多すぎると下部電極の表面積が小さくなるので、蓄積電荷量が減少する。

【0081】

次に、図11に示すように、溝25の内部に残ったフォトレジスト膜30を除去する。フォトレジスト膜30の除去は、例えばオゾンを熱分解したときに発生する酸素ラジカルによってフォトレジストを酸化分解するオゾンアッシング法を用いて行う。このアッシングは、酸素ラジカルが多量、かつ長時間にわたって発生する条件で行い、深い溝25の内部のアモルファスシリコン膜26Aを覆っているフォトレジスト膜30を完全に分解・除去する。

【0082】

このように、本実施の形態では、溝25の外部のアモルファスシリコン膜26Aをドライエッチングで除去する際、溝25の内部のアモルファスシリコン膜26Aをフォトレジスト膜30で保護し、その後、不要となったフォトレジスト膜30をアッシングで除去する。この方法によれば、フォトレジスト膜30に対するアモルファスシリコン膜26Aのエッチング選択比が大きいため、溝25の外部のアモルファスシリコン膜26Aをドライエッチングで除去する際、溝25の内部のアモルファスシリコン膜26Aの削れを最小限に抑えることができる。また、溝25の内部のフォトレジスト膜30の除去をアッシングで行うことにより、溝25の外部の酸化シリコン膜24の削れを最小限に抑えることもできる。

【0083】

次に、図12に示すように、溝25の内部のアモルファスシリコン膜26Aを加工して表面が粗面化された多結晶シリコン膜26を形成する。多結晶シリコン膜26を形成するには、例えばフッ酸系の洗浄液を使ってアモルファスシリコン膜26Aの表面を清浄化し、続いて減圧雰囲気中、アモルファスシリコン膜26Aにモノシラン(SiH4 )またはジシラン(Si2 H6 )を供給してその表面に平均粒径50nm程度のシリコン粒を成長させた後、基板1を熱処理してアモルファスシリコン膜26Aを多結晶化する。表面が粗面化された多結晶シリコン膜26はその表面積が大きいので、情報蓄積用容量素子の蓄積電荷量を増やすことができる。

【0084】

また、本実施の形態では、溝25の内部のアモルファスシリコン膜26Aを保護するフォトレジスト膜30をアッシングで除去した後、アモルファスシリコン膜26Aの表面を粗面化するので、溝25の内部のフォトレジスト膜30を容易に除去することができる。これに対し、アモルファスシリコン膜26Aの表面を粗面化してからその表面を保護膜で覆い、溝25の外部のアモルファスシリコン膜26Aをエッチングで除去した後に保護膜を除去する方法では、アモルファスシリコン膜26Aの表面の細かい凹凸の隙間に保護膜が残り易い。

【0085】

次に、図13に示すように、溝25の外部の酸化シリコン膜24の上部および溝25の内部の多結晶シリコン膜26の上部に高誘電率膜の一種である酸化タンタル(Ta2 O5 )膜28を堆積する。酸化タンタル膜28は、例えばペンタエトキシタンタルと酸素とをソースガスに用いた熱CVD法で形成し、その膜厚は20nm程度とする。また、酸化タンタル膜28の成膜に先立って多結晶シリコン膜26を窒化処理し、その表面に薄い窒化シリコン膜を形成することによって、酸化タンタル膜28のリーク電流を低減してもよい。その後、約800℃の酸素雰囲気中で酸化タンタル膜28を改質・結晶化することにより、高誘電率でリーク電流の少ない良質の酸化タンタル膜28が得られる。

【0086】

次に、図14に示すように、酸化タンタル膜28の上部にCVD法とスパッタリング法とを併用して窒化チタン(TiN)膜29を堆積することにより、多結晶シリコン膜26からなる下部電極、酸化タンタル膜28からなる容量絶縁膜および窒化チタン膜29からなる上部電極によって構成される情報蓄積用容量素子Cを形成する。情報蓄積用容量素子Cの下部電極(多結晶シリコン膜26)は、スルーホール21内のプラグ22およびコンタクトホール13内のプラグ15を介してメモリセル選択用MISFETQsのソース、ドレインの他方(n+ 型半導体領域14)と電気的に接続される。ここまでの工程により、メモリセル選択用MISFETQsと、これに直列に接続された情報蓄積用容量素子Cとによって構成されるDRAMのメモリセルが完成する。

【0087】

その後、情報蓄積用容量素子Cの上部に2層程度のアルミニウム(Al)配線を形成し、さらにその上部に酸化シリコン膜と窒化シリコン膜との積層膜などによって構成されるパッシベーション膜を形成するが、その図示および説明は省略する。

【0088】

なお、本実施の形態では、酸化シリコン膜24に形成した溝25の内部に多結晶シリコン膜26からなる下部電極を形成したが、下部電極材料は多結晶シリコンに限定されるものではない。また、容量絶縁膜材料や上部電極材料も酸化タンタルや窒化チタンに限定されるものではない。下部電極や上部電極は、例えばタングステン膜、白金、ルテニウム、イリジウムなどで構成することもできる。また、容量絶縁膜は、例えばBST、STO、BaTiO3 (チタン酸バリウム)、PbTiO3 (チタン酸鉛)、PZT(PbZrX Ti1-X O3 )、PLT(PbLaX Ti1-X O3 )、PLZTなどの金属酸化物からなる高誘電率膜や強誘電体膜などで構成することもできる。

【0089】

(実施の形態2)

前記情報蓄積用容量素子Cの下部電極(多結晶シリコン膜26)は、次のような方法で形成することもできる。

【0090】

まず、図15に示すように、ビット線BLを覆う酸化シリコン膜19の上方に窒化シリコン膜23と厚い膜厚の酸化シリコン膜24とを堆積し、続いて酸化シリコン膜24および窒化シリコン膜23に深い溝25を形成した後、溝25の内部および酸化シリコン膜24の上部にアモルファスシリコン膜26Aを堆積する。ここまでは、前記実施の形態1の図1〜図6に示す工程と同じである。

【0091】

次に、図16に示すように、アモルファスシリコン膜26Aの表面にシリコン粒を成長させた後、基板1を熱処理してアモルファスシリコン膜26Aを多結晶化することにより、溝25の内部および酸化シリコン膜24の上部に表面が粗面化された多結晶シリコン膜26を形成する。アモルファスシリコン膜26Aの粗面化処理は、前記実施の形態1と同じ方法で行う。

【0092】

次に、図17に示すように、多結晶シリコン膜26の上部にポジ型のフォトレジスト膜30をスピン塗布し、続いてフォトレジスト膜30の全面に露光光を照射した後、図18に示すように、フォトレジスト膜30を現像して露光部を除去することにより、溝25の内部に未露光のフォトレジスト膜30を残す。

【0093】

次に、図19に示すように、フォトレジスト膜30で覆われていない溝25の外部および溝25の開孔端近傍の多結晶シリコン膜26をドライエッチングで除去する。多結晶シリコン膜26のエッチングは、前記実施の形態1で行ったアモルファスシリコン膜26Aのエッチングと同様、フォトレジスト膜30に対する多結晶シリコン膜26のエッチング選択比が十分に大きくなる条件で行い、溝25の内部のフォトレジスト膜30で覆われたアモルファスシリコン膜26Aが露出して削られないようにする。また、このエッチングは、多結晶シリコン膜26を異方的にエッチングする条件で行い、溝25の開孔端近傍においてアモルファスシリコン膜26の上端部を溝25の開孔端よりも僅かに下方に後退させることが望ましい。

【0094】

なお、表面に粗面化処理が施された多結晶シリコン膜26をエッチングする場合は、膜の表面形状に沿ってエッチングが進行するために、溝25の外部の酸化シリコン膜24の上部に多結晶シリコン膜26のエッチング残りが生じ易い。このエッチング残りは、隣接する溝25の間で下部電極同士が短絡する原因となるため、上記多結晶シリコン膜26をエッチングする際は、この点に配慮したエッチング条件を選定する必要がある。

【0095】

次に、図20に示すように、前述したオゾンアッシング法などを用いて溝25の内部に残ったフォトレジスト膜30を除去し、多結晶シリコン膜26を露出させる。このとき、多結晶シリコン膜26の表面に形成されたシリコン粒の隙間などにフォトレジスト膜30のアッシング残りが生じると、情報蓄積用容量素子Cの蓄積電荷量の減少を引き起こす。従って、溝25の内部のフォトレジスト膜30を除去する際は、この点に配慮したアッシング条件を選定する必要がある。

【0096】

その後、図21に示すように、溝25の外部の酸化シリコン膜24の上部および溝25の内部の多結晶シリコン膜26の上部に酸化タンタル膜28を堆積し、続いて酸化タンタル膜28を改質・結晶化するための熱処理を行った後、酸化タンタル膜28の上部に窒化チタン膜29を堆積することにより、多結晶シリコン膜26からなる下部電極、酸化タンタル膜28からなる容量絶縁膜および窒化チタン膜29からなる上部電極によって構成される情報蓄積用容量素子Cを形成する。酸化タンタル膜28および窒化チタン膜29は、前記実施の形態1と同様の方法で形成する。

【0097】

このように、本実施の形態では、溝25の外部の多結晶シリコン膜26をドライエッチングで除去する際、溝25の内部の多結晶シリコン膜26をフォトレジスト膜30で保護し、その後、不要となったフォトレジスト膜30をアッシングで除去する。この方法によれば、フォトレジスト膜30に対する多結晶シリコン膜26のエッチング選択比が大きいため、溝25の外部のアモルファスシリコン膜26をドライエッチングで除去する際、溝25の内部の多結晶シリコン膜26の削れを最小限に抑えることができる。また、溝25の内部のフォトレジスト膜30の除去をアッシングで行うことにより、溝25の外部の酸化シリコン膜24の削れを最小限に抑えることもできる。

【0098】

(実施の形態3)

本発明の実施形態3であるプラグの形成方法を図22〜図33を用いて工程順に説明する。

【0099】

まず、図22に示すように、例えばp型の単結晶シリコンからなる基板1の主面に素子分離溝2を形成した後、基板1の一部にp型不純物(ホウ素)をイオン注入してp型ウエル3を形成し、他の一部にn型不純物(リンまたはヒ素)をイオン注入してn型ウエル4を形成する。

【0100】

次に、周知のCMOSプロセスに従ってp型ウエル3にnチャネル型MISFETQnを形成し、n型ウエル4にpチャネル型MISFETQpを形成する。nチャネル型MISFETQnは、主としてゲート酸化膜6、ゲート電極7およびn+ 型半導体領域(ソース、ドレイン)31で構成され、pチャネル型MISFETQpは、主としてゲート酸化膜6、ゲート電極7およびp+ 型半導体領域(ソース、ドレイン)32で構成される。

【0101】

次に、図23に示すように、nチャネル型MISFETQnおよびpチャネル型MISFETQpの上部にCVD法で酸化シリコン膜33を堆積し、続いて酸化シリコン膜33の表面を化学機械研磨法で平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜33をドライエッチングすることにより、n+ 型半導体領域(ソース、ドレイン)31の上部にコンタクトホール34、35を形成し、p+ 型半導体領域(ソース、ドレイン)32の上部にコンタクトホール36、37を形成する。またこのとき同時に、ゲート電極7の上部にコンタクトホール38を形成する。

【0102】

次に、酸化シリコン膜33の上部に第1層目の配線41〜47を形成する。配線41〜47を形成するには、例えばコンタクトホール34〜38の内部および酸化シリコン膜33の上部にスパッタリング法またはCVD法で窒化チタン膜を堆積し、続いて窒化チタン膜の上部にCVD法でタングステン膜を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでタングステン膜および窒化チタン膜をパターニングする。

【0103】

上記コンタクトホール34〜38の内部にはプラグを形成してもよい。この場合は、まず、コンタクトホール34〜38の内部および酸化シリコン膜33の上部にスパッタリング法またはCVD法で窒化チタン膜を堆積し、続いて窒化チタン膜の上部にCVD法でタングステン膜を堆積した後、化学機械研磨法で酸化シリコン膜33の上部のタングステン膜および窒化チタン膜を除去することによって、コンタクトホール34〜38の内部にプラグを形成する。次に、酸化シリコン膜33の上部にスパッタリング法でタングステン膜を堆積し、フォトレジスト膜をマスクにしたドライエッチングでタングステン膜をパターニングすることによって、第1層目の配線41〜47を形成する。

【0104】

次に、図24に示すように、酸化シリコン膜33の上部にCVD法で酸化シリコン膜48を堆積し、続いて酸化シリコン膜48の表面を化学機械研磨法で平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜48をドライエッチングすることにより、第1層目の配線41、43、44、46、47の上部にスルーホール51〜55を形成する。

【0105】

次に、図25に示すように、スルーホール51〜55の内部および酸化シリコン膜48の上部にバリアメタル膜56を形成する。このバリアメタル膜56は、次の工程でスルーホール51〜55の内部に形成されるプラグと酸化シリコン膜48との接着力を向上させるための接着層であり、例えばスパッタリング法またはCVD法で堆積した窒化チタン膜からなる。

【0106】

次に、図26に示すように、バリアメタル膜56の上部にポジ型のフォトレジスト膜40をスピン塗布した後、図27に示すように、フォトレジスト膜40の全面に露光光を照射する。このとき、スルーホール51〜55の外部やスルーホール51〜55の開孔端近傍のフォトレジスト膜40は露光されるが、スルーホール51〜55の内部のフォトレジスト膜40は露光量が不足するので露光されない。

【0107】

次に、図28に示すように、フォトレジスト膜40を現像して露光部を除去し、スルーホール51〜55の内部に未露光のフォトレジスト膜40を残した後、図29に示すように、スルーホール51〜55の外部のバリアメタル膜56をドライエッチングで除去する。このとき、スルーホール51〜55の内部のバリアメタル膜56は、その表面がフォトレジスト膜40で覆われているので、除去されずに残る。バリアメタル膜56のエッチングは、フォトレジスト膜40に対するバリアメタル膜56のエッチング選択比が十分に大きくなる条件で行い、スルーホール51〜55の内部のフォトレジスト膜40で覆われたバリアメタル膜56が露出して削られないようにする。

【0108】

次に、図30に示すように、スルーホール51〜55の内部に残ったフォトレジスト膜40をオゾンアッシング法などを用いて除去した後、図31に示すように、スルーホール51〜55の内部に露出したバリアメタル膜56の表面に選択CVD法などを用いてタングステン膜57を成長させる。このタングステン膜57は、前記第1層目の配線41、43、44、46、47と次の工程で酸化シリコン膜48の上部に形成される第2層目の配線とを電気的に接続するプラグ材料として使用される。

【0109】

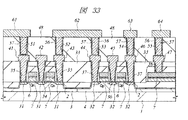

次に、図32に示すように、スルーホール51〜55の外部に露出したタングステン膜57をドライエッチング(または化学機械研磨法で研磨)してその表面の高さを酸化シリコン膜48の表面の高さとほぼ同じにした後、図33に示すように、酸化シリコン膜48の上部に第2層目の配線61〜64を形成する。配線61〜64を形成するには、例えば酸化シリコン膜48の上部にスパッタリング法でタングステン膜を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでタングステン膜をパターニングする。

【0110】

(実施の形態4)

本発明の実施形態4であるプラグの形成方法を図34〜図39を用いて工程順に説明する。

【0111】

まず、図34に示すように、前記実施の形態3と同様の方法でnチャネル型MISFETQnおよびpチャネル型MISFETQpの上部に第1層目の配線41〜47を形成し、続いて第1層目の配線41〜47の上部に堆積した酸化シリコン膜48をドライエッチングしてスルーホール51〜55を形成する。

【0112】

次に、図35に示すように、スルーホール51〜55の内部および酸化シリコン膜48の上部に接着層となるバリアメタル膜56を形成した後、バリアメタル膜56の上部にスピン塗布したポジ型のフォトレジスト膜40を全面露光する。このとき、酸化シリコン膜48の上部およびスルーホール51〜55の上部のフォトレジスト膜40は露光されるが、露光量が不足するスルーホール51〜55の内部のフォトレジスト膜40は露光されない。

【0113】

次に、フォトレジスト膜40を現像して露光部を除去し、スルーホール51〜55の内部に未露光のフォトレジスト膜40を残した後、図36に示すように、フォトレジスト膜40で覆われていない酸化シリコン膜48の上部のバリアメタル膜56をドライエッチングで除去し、さらにスルーホール51〜55の内部に残ったフォトレジスト膜40をオゾンアッシング法などを用いて除去する。

【0114】

次に、図37に示すように、スルーホール51〜55の内部および酸化シリコン膜48の上部にシード層65を形成する。このシード層65は、次の工程でスルーホール51〜55の内部に形成されるプラグの下地層となるもので、例えばスパッタリング法で堆積した銅(Cu)膜からなる。

【0115】

次に、図38に示すように、シード層65の表面に無電解メッキ法または蒸着法を用いて銅膜66を堆積した後、図39に示すように、スルーホール51〜55の外部の銅膜66およびシード層65を化学機械研磨法で除去することにより、スルーホール51〜55の内部に銅膜66およびシード層65からなるプラグ66A〜66Eを形成する。

【0116】

一般に、銅は酸化シリコン膜中に拡散し易いという性質や、酸化シリコン膜に対する接着力が弱いという性質がある。そのため、酸化シリコン膜に形成した溝やスルーホールの内部に銅のプラグや配線を形成する場合は、銅膜と酸化シリコン膜との間に銅の拡散を抑制し、かつ酸化シリコンに対する接着力が大きい窒化チタン膜などのバリアメタル膜を設ける必要がある。

【0117】

このような理由から、化学機械研磨法を使った銅プラグや銅配線の形成工程では、溝やスルーホールの外部の酸化シリコン膜上に形成された銅膜や銅のシード層を研磨・除去した後、さらにその下層の銅とは材質が異なるバリアメタル膜を研磨・除去しなければならないので、化学機械研磨工程が煩雑になる。

【0118】

これに対し、上記した本実施の形態の銅プラグ形成方法によれば、化学機械研磨工程に先立ってスルーホール51〜55の外部のバリアメタル膜56をドライエッチングで除去し、その後、銅膜66およびこれと同じ材質からなるシード層65を研磨・除去するので、化学機械研磨工程が簡略になる。なお、銅の拡散を防ぐバリアメタル膜は、窒化チタン膜の他、窒化タンタル(TaN)膜、窒化タングステン(WN)膜などで構成することもできる。

【0119】

(実施の形態5)

本発明の実施形態5であるデュアルダマシン方式を用いた埋込み銅配線の形成方法を図40〜図49を用いて工程順に説明する。

【0120】

まず、図40に示すように、前記実施の形態3、4と同様の方法でnチャネル型MISFETQnおよびpチャネル型MISFETQpを形成し、続いてそれらの上部に第1層目の配線41〜47を形成した後、図41に示すように、第1層目の配線41〜47の上部にCVD法で酸化シリコン膜68を堆積する。

【0121】

次に、図42に示すように、フォトレジスト膜(図示せず)をマスクにしたドライエッチングで配線41、43、44、46、47の上部の酸化シリコン膜68にスルーホール71〜75を形成した後、図43に示すように、スルーホール71〜75の内部および酸化シリコン膜68の上部にポジ型のフォトレジスト膜50をスピン塗布する。

【0122】

次に、図44に示すように、フォトマスク49を通して配線形成領域のフォトレジスト膜50に選択的に露光光を照射する。このとき、スルーホール71〜75の内部のフォトレジスト膜50は、スルーホール71〜75の途中までは露光されるが、途中よりも下方は露光量が不足するために露光されない。

【0123】

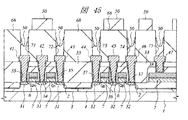

次に、図45に示すように、フォトレジスト膜50を現像して露光部を除去し、未露光のフォトレジスト膜50を残す。このとき、スルーホール71〜75の内部は、途中よりも上のフォトレジスト膜50のみが除去されるので、途中よりも下方にフォトレジスト膜50が残った状態となる。

【0124】

次に、図46に示すように、フォトレジスト膜50をマスクにして配線形成領域の酸化シリコン膜68をドライエッチングすることによって、配線溝76〜79を形成する。酸化シリコン膜68のエッチングは、フォトレジスト膜50に対する比べて酸化シリコン膜68のエッチング選択比が十分に大きくなる条件で行い、スルーホール71〜75の内部のフォトレジスト膜50が配線溝76〜79の底部に露出した時点でエッチングを停止する。

【0125】

次に、図47に示すように、スルーホール71〜75の内部に残ったフォトレジスト膜50をオゾンアッシング法などを用いて除去した後、図48に示すように、配線溝76〜79およびその下部のスルーホール71〜75の内部に接着層となるバリアメタル膜56を形成した後、バリアメタル膜56の上部に銅膜86を堆積する。バリアメタル膜56は、例えばCVD法で堆積した窒化チタン膜からなる。また、銅膜86は、スパッタリング法などを用いて堆積する。

【0126】

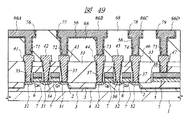

次に、図49に示すように、配線溝76〜79の外部の銅膜86およびバリアメタル膜56を化学機械研磨法で除去することによって、配線溝76〜79の内部およびその下部のスルーホール71〜75の内部に埋込み銅配線86A〜86Dを形成する。

【0127】

通常、配線溝およびその下部のスルーホールに同時に埋込み配線を形成するデュアルダマシン・プロセスでは、酸化シリコン膜に配線溝とスルーホールとを形成する際、配線溝とスルーホールとの境界部にエッチングストッパとなる絶縁膜(例えば窒化シリコン膜)を形成することによって配線溝の深さを規定する。すなわち、第1酸化シリコン膜の上部に窒化シリコン膜を挟んで第2酸化シリコン膜を堆積し、続いて第2酸化シリコン膜、窒化シリコン膜および第1酸化シリコン膜をドライエッチングしてスルーホールを形成した後、窒化シリコン膜をエッチングストッパにしてその上部の第2酸化シリコン膜をドライエッチングする。これにより、第2酸化シリコン膜に配線溝が形成され、その下部の窒化シリコン膜および第1酸化シリコン膜にスルーホールが残る。しかし、このようなデュアルダマシン・プロセスは、1層の埋込み配線を形成するのに3層の絶縁膜(第1酸化シリコン膜、窒化シリコン膜および第2酸化シリコン膜)を必要とするので、工程が増加するという問題がある。また、酸化シリコン膜よりも誘電率が高い窒化シリコン膜を含んだ絶縁膜に埋込み銅配線を形成すると、その寄生容量が増加するという問題もある。

【0128】

これに対し、スルーホール71〜75の内部に埋め込んだフォトレジスト膜50をエッチングストッパにして配線溝76〜79を形成する本実施の形態によれば、一層の酸化シリコン膜68にスルーホール71〜75および配線溝76〜79を形成するので、デュアルダマシン・プロセスの工程を短縮することができる。また、誘電率が高い絶縁膜(窒化シリコン膜)をエッチングストッパに使用しないので、埋込み銅配線86A〜86Eの寄生容量を低減することもできる。

【0129】

(実施の形態6)

本発明の実施形態6であるセルフアライン・コンタクトホールの形成方法を図50〜図58を用いて工程順に説明する。

【0130】

まず、図50に示すように、基板1の主面に酸化シリコン膜5を埋め込んだ素子分離2、p型ウエル3およびn型ウエル4を形成し、続いてp型ウエル3およびn型ウエル4の表面にゲート酸化膜6を形成した後、ゲート酸化膜6の上部にゲート電極7を形成する。ゲート電極7を形成するには、例えば基板1上にリンなどのn型不純物をドープした多結晶シリコン膜をCVD法で堆積し、続いてその上部にスパッタリング法で窒化タングステン膜およびタングステン膜を堆積し、さらにその上部にCVD法で窒化シリコン膜8を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでこれらの膜をパターニングする。ゲート電極7の上部の窒化シリコン膜8は、後述するコンタクトホールをゲート電極7に対して自己整合(セルフアライン)で形成するために必要な絶縁膜である。

【0131】

次に、図51に示すように、p型ウエル3にリンなどのn型不純物をイオン注入してn- 型半導体領域9を形成し、n型ウエル4にp型不純物(ホウ素)をイオン注入してp- 型半導体領域20を形成した後、ゲート電極7の上部にCVD法で窒化シリコン膜27および酸化シリコン膜11を堆積し、続いて酸化シリコン膜11の表面を化学機械研磨法で平坦化する。窒化シリコン膜27は、後述するコンタクトホールを素子分離溝2に対して自己整合で形成するために必要な絶縁膜である。

【0132】

コンタクトホールをゲート電極7および素子分離溝2に対してそれぞれ自己整合で形成する場合は、上記のようにゲート電極7の上部に窒化シリコン膜8を形成し、さらに素子分離溝2の上部に窒化シリコン膜27を形成する。そのため、ここまでの工程で拡散層(n- 型半導体領域9、p- 型半導体領域20)および素子分離溝2は1層の窒化シリコン膜27で覆われ、ゲート電極7は2層の窒化シリコン膜8、27で覆われる。

【0133】

次に、図52に示すように、フォトレジスト膜(図示せず)をマスクにして拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部の酸化シリコン膜11をドライエッチングする。またこのとき同時に、ゲート電極7の上部の酸化シリコン膜11をドライエッチングする。酸化シリコン膜11のエッチングは、窒化シリコン膜27に対する酸化シリコン膜11のエッチング選択比が大きくなる条件で行い、下層の窒化シリコン膜27が除去されないようにする。

【0134】

窒化シリコン膜27をエッチングストッパにしてその上部の酸化シリコン膜11をドライエッチングすると、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部には1層の窒化シリコン膜27が残り、ゲート電極7の上部には2層の窒化シリコン膜8、27が残る。そのため、次の工程で拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部の1層の窒化シリコン膜27をドライエッチングしてそれらの上部にコンタクトホールを形成する際、同時にゲート電極7の上部の2層の窒化シリコン膜8、27をドライエッチングしてその上部にコンタクトホールを形成しようとすると、基板1および素子分離溝2内の酸化シリコン膜5が深く削れてしまい、リーク電流の増加といった素子特性の劣化を引き起こす。従って、基板1や酸化シリコン膜5の過剰な削れを防ぐためには、ゲート電極7の上部の窒化シリコン膜8、27のエッチングと、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部の窒化シリコン膜27のエッチングとを別工程で行う必要があり、フォトマスクが2枚必要となる。

【0135】

そこで本実施の形態では、窒化シリコン膜27をエッチングストッパにしてその上部の酸化シリコン膜11をドライエッチングした後、図53に示すように、酸化シリコン膜11の上部にポジ型のフォトレジスト膜60をスピン塗布し、続いてフォトレジスト膜60の全面に露光光を照射する。このとき、ゲート電極7の上方のフォトレジスト膜60は、その膜厚が薄いために露光されるが、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上方のフォトレジスト膜60は、その膜厚が厚いために途中までしか露光されない。

【0136】

次に、図54に示すように、フォトレジスト膜60を現像して露光部を除去する。このとき、ゲート電極7の上部(図の矢印で示す箇所)は、フォトレジスト膜60が除去されて窒化シリコン膜27が露出するが、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部は、未露光のフォトレジスト膜60が残るので窒化シリコン膜27は露出しない。

【0137】

次に、図55に示すように、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部のフォトレジスト膜60をマスクにしてゲート電極7の上部の窒化シリコン膜27、8をドライエッチングする。このエッチングは、酸化シリコン膜11に対する窒化シリコン膜27、8のエッチング選択比が十分に大きくなる条件で行い、ゲート電極7を覆う窒化シリコン膜8の膜厚が拡散層(n- 型半導体領域9、p- 型半導体領域20)を覆う窒化シリコン膜27の膜厚とほぼ同じになった時点でエッチングを停止する。

【0138】

次に、図56に示すように、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部に残ったフォトレジスト膜60をオゾンアッシング法で除去した後、図57に示すように、拡散層(n- 型半導体領域9、p- 型半導体領域20)を覆う窒化シリコン膜27とゲート電極7を覆う窒化シリコン膜8とをドライエッチングで除去することにより、n- 型半導体領域9の上部にコンタクトホール91、92を形成し、p- 型半導体領域20の上部にコンタクトホール93、94を形成し、ゲート電極7の上部にコンタクトホール95を形成する。窒化シリコン膜8、27のエッチングは、それらを異方的にエッチングする条件で行い、ゲート電極7の側壁に窒化シリコン膜27を残すようにする。

【0139】

上記した窒化シリコン膜8、27のエッチングは、拡散層(n- 型半導体領域9、p- 型半導体領域20)の上部の窒化シリコン膜27とゲート電極7の上部の窒化シリコン膜8とをほぼ同じ膜厚にしてから行うため、それらを同時にエッチングしても素子分離溝2内の酸化シリコン膜5や基板1が深く削られることはない。

【0140】

このように、本実施形態6によれば、コンタクトホール91〜94をゲート電極7および素子分離溝2に対して自己整合で形成する際、ゲート電極7の上部のコンタクトホール95を同時に形成することができるので、コンタクトホール91〜95を形成するためのフォトマスクが1枚で済む。

【0141】

次に、図58に示すように、コンタクトホール91、92を通じてp型ウエル3にn型不純物(リンまたはヒ素)をイオン注入してn+ 型半導体領域(ソース、ドレイン)31を形成することにより、nチャネル型MISFETQnを形成する。また、コンタクトホール93、94を通じてn型ウエル4にp型不純物(ホウ素)をイオン注入してp+ 型半導体領域(ソース、ドレイン)32を形成することにより、pチャネル型MISFETQpを形成する。その後、前記実施の形態3〜5と同様の方法で酸化シリコン膜11の上部に第1層目の配線41〜47を形成する。

【0142】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0143】

【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

【0144】

(1)本発明によれば、絶縁膜に形成された溝の内部に下部電極を形成する情報蓄積用容量素子を備えたDRAMの信頼性、製造歩留まりを向上させることができる。

【0145】

(2)本発明によれば、絶縁膜に形成した溝またはスルーホールの内部に歩留まりよく導電層を形成することができる。

【0146】

(3)本発明によれば、絶縁膜に形成した溝またはスルーホールの内部に少ない工程で導電層を形成することができる。

【図面の簡単な説明】

【図1】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図2】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図3】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図4】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図5】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図6】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図7】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図8】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図9】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図10】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図11】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図12】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図13】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図14】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図15】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図16】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図17】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図18】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図19】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図20】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図21】本発明の実施の形態2である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図22】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図23】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図24】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図25】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図26】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図27】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図28】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図29】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図30】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図31】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図32】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図33】本発明の実施の形態3である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図34】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図35】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図36】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図37】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図38】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図39】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図40】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図41】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図42】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図43】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図44】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図45】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図46】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図47】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図48】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図49】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図50】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図51】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図52】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図53】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図54】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図55】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図56】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図57】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図58】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【符号の説明】

1 半導体基板

2 素子分離溝

3 p型ウエル

4 n型ウエル

5 酸化シリコン膜

6 ゲート酸化膜

7 ゲート電極

8 窒化シリコン膜

9 n- 型半導体領域

10 窒化シリコン膜

11 酸化シリコン膜

12、13 コンタクトホール

14 n+ 型半導体領域

15 プラグ

16 酸化シリコン膜

17 スルーホール

18 プラグ

19 酸化シリコン膜

20 p- 型半導体領域

21 スルーホール

22 プラグ

23 窒化シリコン膜

24 酸化シリコン膜

25 溝

26A アモルファスシリコン膜

26 多結晶シリコン膜

27 窒化シリコン膜

28 酸化タンタル膜

29 窒化チタン膜

30 フォトレジスト膜

31 n+ 型半導体領域(ソース、ドレイン)

32 p+ 型半導体領域(ソース、ドレイン)

33 酸化シリコン膜

34〜38 コンタクトホール

40 フォトレジスト膜

41〜47 配線

48 酸化シリコン膜

49 フォトマスク

50 フォトレジスト膜

51〜55 スルーホール

56 バリアメタル膜

57 タングステン膜

60 フォトレジスト膜

61〜64 配線

65 シード層

66 銅膜

66A〜66E プラグ

68 酸化シリコン膜

71〜75 スルーホール

76〜79 配線溝

86 銅膜

86A〜86D 埋込み銅配線

91〜95 コンタクトホール

BL ビット線

C 情報蓄積用容量素子

Qn nチャネル型MISFET

Qp pチャネル型MISFET

Qs メモリセル選択用MISFET

WL ワード線

Claims (11)

- 以下の工程を含む半導体集積回路装置の製造方法;

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜に溝またはスルーホールを形成して前記第1導電膜を露出する工程、

(b)前記溝またはスルーホールの内部および前記第1絶縁膜の上部に、前記溝またはスルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(c)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトレジスト膜および前記溝またはスルーホールに埋め込まれた上部のフォトレジスト膜を露光する工程、

(d)前記フォトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトレジスト膜の未露光部を残す工程、

(e)前記未露光部のフォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝またはスルーホールの内部に前記第2導電膜を残す工程、

(f)前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部に露出した前記第2導電膜の表面に第3導電膜を選択成長させることによって、前記溝またはスルーホールの内部に前記第3導電膜を埋め込む工程。 - 請求項1記載の半導体集積回路装置の製造方法において、前記第2導電膜は窒化チタンまたはタングステンからなることを特徴とする半導体集積回路装置の製造方法。

- 請求項1記載の半導体集積回路装置の製造方法において、前記第3導電膜はタングステンまたはアルミニウム合金からなることを特徴とする半導体集積回路装置の製造方法。

- 請求項1記載の半導体集積回路装置の製造方法において、前記(f)工程の後、

(g)前記第1絶縁膜の上部に第4導電膜を形成し、前記溝またはスルーホールの内部の前記第3導電膜を介して前記第4導電膜と前記第1導電膜とを電気的に接続する工程、

をさらに含むことを特徴とする半導体集積回路装置の製造方法。 - 以下の工程を含む半導体集積回路装置の製造方法;

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜に溝またはスルーホールを形成して前記第1導電膜を露出する工程、

(b)前記溝またはスルーホールの内部および前記第1絶縁膜の上部に、前記溝またはスルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(c)前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトレジスト膜および前記溝またはスルーホールに埋め込まれた上部のフォトレジスト膜を露光する工程、

(d)前記フォトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトレジスト膜の未露光部を残す工程、

(e)前記未露光部のフォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝またはスルーホールの内部に前記第2導電膜を残す工程、

(f)前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部および前記第1絶縁膜の上部に第5導電膜を形成する工程、

(g)前記第5導電膜の表面に第6導電膜を選択成長させた後、前記溝またはスルーホールの外部の前記第6導電膜および前記第5導電膜を除去し、前記溝またはスルーホールの内部に前記第6導電膜および前記第5導電膜を残す工程。 - 請求項5記載の半導体集積回路装置の製造方法において、前記第2導電膜は窒化チタンまたは窒化タンタルからなることを特徴とする半導体集積回路装置の製造方法。

- 請求項5記載の半導体集積回路装置の製造方法において、前記第5導電膜および前記第6導電膜は銅からなることを特徴とする半導体集積回路装置の製造方法。

- 請求項5記載の半導体集積回路装置の製造方法において、前記第6導電膜および前記第5導電膜の除去は、化学機械研磨法によって行うことを特徴とする半導体集積回路装置の製造方法。

- 以下の工程を含む半導体集積回路装置の製造方法;

(a)半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜および前記第1導電膜をパターニングすることによって、その上部が前記第1絶縁膜で覆われた前記第1導電膜からなるゲート電極を形成する工程、

(b)前記ゲート電極の両側の前記半導体基板に半導体領域を形成する工程、

(c)前記ゲート電極が形成された前記半導体基板上に第2絶縁膜を形成した後、前記第2絶縁膜の上部に、前記第1絶縁膜および前記第2絶縁膜とはエッチングの選択比が異なる第3絶縁膜を形成する工程、

(d)第1フォトレジスト膜をマスクにして前記第3絶縁膜をエッチングすることにより、前記半導体領域の上部の前記第2絶縁膜に達する第1溝および前記ゲート電極の上部の前記第2絶縁膜に達する第2溝を形成する工程、

(e)前記第1フォトレジスト膜を除去した後、前記第1、第2溝の内部および前記第3絶縁膜の上部に第2フォトレジスト膜を形成する工程、

(f)前記第2フォトレジスト膜に露光光を照射することによって、前記第2溝の内部および前記第3絶縁膜の上部の前記第2フォトレジスト膜を露光した後、前記第2フォトレジスト膜の露光部を除去することによって、前記第1溝の内部に前記第2フォトレジスト膜の未露光部を残す工程、

(g)前記第1溝の内部の前記未露光部の第2フォトレジスト膜をマスクにしたエッチングで前記第2溝の底部の前記第2絶縁膜およびその下部の前記第1絶縁膜の一部をエッチングする工程、

(h)前記未露光部の第2フォトレジスト膜を除去した後、前記第1溝の下部の前記第2絶縁膜および前記第2溝の下部の前記第1絶縁膜をエッチングすることによって、前記半導体領域の上部に第1コンタクトホールを形成し、前記ゲート電極の上部に第2コンタクトホールを形成する工程。 - 請求項9記載の半導体集積回路装置の製造方法において、前記第1絶縁膜および前記第2絶縁膜は窒化シリコンからなり、前記第3絶縁膜は酸化シリコン膜からなることを特徴とする半導体集積回路装置の製造方法。

- 請求項9記載の半導体集積回路装置の製造方法において、前記(h)工程の後、

(i)前記第1、第2コンタクトホールの内部および前記第3絶縁膜の上部に第2導電膜を形成する工程、

(j)前記第2導電膜をパターニングすることによって、前記第1コンタクトホールを通じて前記半導体領域に電気的に接続される第1配線および前記第2コンタクトホールを通じて前記ゲート電極に電気的に接続される第2配線を形成する工程、をさらに含むことを特徴とする半導体集積回路装置の製造方法。

Priority Applications (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18745099A JP3998373B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体集積回路装置の製造方法 |

| TW089111652A TW466749B (en) | 1999-07-01 | 2000-06-14 | Manufacturing method of semiconductor integrated circuit device |

| KR1020000034824A KR100770468B1 (ko) | 1999-07-01 | 2000-06-23 | 반도체 집적회로장치의 제조방법 |

| US09/610,114 US6444405B1 (en) | 1999-07-01 | 2000-06-30 | Method of forming conductive layers in the trenches or through holes made in an insulating film on a semiconductors substrate |

| US10/112,945 US20020098678A1 (en) | 1999-07-01 | 2002-04-02 | Method of forming conductive layers in the trenches or through holes made in an insulating film on a semiconductor substrate |

| US10/367,737 US6770528B2 (en) | 1999-07-01 | 2003-02-19 | Method of forming a data-storing capacitive element made in an insulating film on a semiconductor substrate |

| US10/846,571 US20040214428A1 (en) | 1999-07-01 | 2004-05-17 | Method of forming conductive layers in the trenches or through holes made in an insulating film on a semiconductor substrate |

| KR1020060103766A KR100757888B1 (ko) | 1999-07-01 | 2006-10-25 | 반도체 집적회로장치의 제조방법 |

| KR1020070020994A KR100802698B1 (ko) | 1999-07-01 | 2007-03-02 | 반도체 집적회로장치의 제조방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP18745099A JP3998373B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体集積回路装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006046189A Division JP2006191137A (ja) | 2006-02-23 | 2006-02-23 | 半導体集積回路装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001015712A JP2001015712A (ja) | 2001-01-19 |

| JP2001015712A5 JP2001015712A5 (ja) | 2006-04-13 |

| JP3998373B2 true JP3998373B2 (ja) | 2007-10-24 |

Family

ID=16206298

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP18745099A Expired - Fee Related JP3998373B2 (ja) | 1999-07-01 | 1999-07-01 | 半導体集積回路装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US6444405B1 (ja) |

| JP (1) | JP3998373B2 (ja) |

| KR (3) | KR100770468B1 (ja) |

| TW (1) | TW466749B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3998373B2 (ja) * | 1999-07-01 | 2007-10-24 | 株式会社ルネサステクノロジ | 半導体集積回路装置の製造方法 |

| JP2001223345A (ja) * | 1999-11-30 | 2001-08-17 | Hitachi Ltd | 半導体装置とその製造方法 |

| KR100476399B1 (ko) * | 2002-06-29 | 2005-03-16 | 주식회사 하이닉스반도체 | 반도체 장치의 캐패시터 제조방법 |

| US20040084400A1 (en) | 2002-10-30 | 2004-05-06 | Gregory Costrini | Patterning metal stack layers of magnetic switching device, utilizing a bilayer metal hardmask |

| KR100526869B1 (ko) * | 2003-06-19 | 2005-11-09 | 삼성전자주식회사 | 반도체 메모리에서의 커패시터 하부 전극 형성방법 |

| US7199045B2 (en) * | 2004-05-26 | 2007-04-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal-filled openings for submicron devices and methods of manufacture thereof |

| KR100668833B1 (ko) * | 2004-12-17 | 2007-01-16 | 주식회사 하이닉스반도체 | 반도체소자의 캐패시터 제조방법 |

| KR100666380B1 (ko) * | 2005-05-30 | 2007-01-09 | 삼성전자주식회사 | 포토레지스트 제거방법 및 이를 이용한 반도체 소자의 제조방법. |

| US9220301B2 (en) | 2006-03-16 | 2015-12-29 | R.J. Reynolds Tobacco Company | Smoking article |

| JP2007311560A (ja) * | 2006-05-18 | 2007-11-29 | Toshiba Corp | 半導体装置 |

| US8669597B2 (en) | 2008-05-06 | 2014-03-11 | Spansion Llc | Memory device interconnects and method of manufacturing |

| US8513119B2 (en) | 2008-12-10 | 2013-08-20 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming bump structure having tapered sidewalls for stacked dies |

| KR200452291Y1 (ko) * | 2008-12-31 | 2011-02-15 | 엘에스산전 주식회사 | 배선용 차단기의 보조커버 고정장치 |

| US20100171197A1 (en) * | 2009-01-05 | 2010-07-08 | Hung-Pin Chang | Isolation Structure for Stacked Dies |

| US8791549B2 (en) | 2009-09-22 | 2014-07-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Wafer backside interconnect structure connected to TSVs |

| US8466059B2 (en) | 2010-03-30 | 2013-06-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Multi-layer interconnect structure for stacked dies |

| US8900994B2 (en) | 2011-06-09 | 2014-12-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for producing a protective structure |

| KR101883380B1 (ko) * | 2011-12-26 | 2018-07-31 | 삼성전자주식회사 | 커패시터를 포함하는 반도체 소자 |

| US9633847B2 (en) * | 2015-04-10 | 2017-04-25 | Tokyo Electron Limited | Using sub-resolution openings to aid in image reversal, directed self-assembly, and selective deposition |

| US9576788B2 (en) * | 2015-04-24 | 2017-02-21 | Applied Materials, Inc. | Cleaning high aspect ratio vias |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR960003864B1 (ko) | 1992-01-06 | 1996-03-23 | 삼성전자주식회사 | 반도체 메모리장치 및 그 제조방법 |

| JP3222188B2 (ja) * | 1992-04-14 | 2001-10-22 | 株式会社日立製作所 | 半導体装置及びその製造方法 |

| US5270265A (en) * | 1992-09-01 | 1993-12-14 | Harris Corporation | Stress relief technique of removing oxide from surface of trench-patterned semiconductor-on-insulator structure |

| US5670425A (en) * | 1995-11-09 | 1997-09-23 | Lsi Logic Corporation | Process for making integrated circuit structure comprising local area interconnects formed over semiconductor substrate by selective deposition on seed layer in patterned trench |

| US5900668A (en) * | 1995-11-30 | 1999-05-04 | Advanced Micro Devices, Inc. | Low capacitance interconnection |

| US5914202A (en) * | 1996-06-10 | 1999-06-22 | Sharp Microeletronics Technology, Inc. | Method for forming a multi-level reticle |

| US6051858A (en) * | 1996-07-26 | 2000-04-18 | Symetrix Corporation | Ferroelectric/high dielectric constant integrated circuit and method of fabricating same |

| US5691215A (en) * | 1996-08-26 | 1997-11-25 | Industrial Technology Research Institute | Method for fabricating a sub-half micron MOSFET device with insulator filled shallow trenches planarized via use of negative photoresist and de-focus exposure |

| US5716883A (en) * | 1996-11-06 | 1998-02-10 | Vanguard International Semiconductor Corporation | Method of making increased surface area, storage node electrode, with narrow spaces between polysilicon columns |

| JPH10173157A (ja) * | 1996-12-06 | 1998-06-26 | Toshiba Corp | 半導体装置 |

| US6150211A (en) * | 1996-12-11 | 2000-11-21 | Micron Technology, Inc. | Methods of forming storage capacitors in integrated circuitry memory cells and integrated circuitry |

| JPH10189898A (ja) * | 1996-12-24 | 1998-07-21 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| US5905280A (en) * | 1997-02-11 | 1999-05-18 | Micron Technology, Inc. | Capacitor structures, DRAM cell structures, methods of forming capacitors, methods of forming DRAM cells, and integrated circuits incorporating capacitor structures and DRAM cell structures |

| US5981333A (en) * | 1997-02-11 | 1999-11-09 | Micron Technology, Inc. | Methods of forming capacitors and DRAM arrays |

| JPH1117140A (ja) * | 1997-06-25 | 1999-01-22 | Sony Corp | 半導体装置及びその製造方法 |

| JPH1117144A (ja) | 1997-06-26 | 1999-01-22 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JPH11214646A (ja) * | 1998-01-28 | 1999-08-06 | Mitsubishi Electric Corp | 半導体記憶装置およびその製造方法 |

| US6380096B2 (en) * | 1998-07-09 | 2002-04-30 | Applied Materials, Inc. | In-situ integrated oxide etch process particularly useful for copper dual damascene |

| JP2000156480A (ja) * | 1998-09-03 | 2000-06-06 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP3337067B2 (ja) | 1999-05-07 | 2002-10-21 | 日本電気株式会社 | 円筒形キャパシタ下部電極の製造方法 |

| US6146517A (en) * | 1999-05-19 | 2000-11-14 | Infineon Technologies North America Corp. | Integrated circuits with copper metallization for interconnections |

| JP3998373B2 (ja) * | 1999-07-01 | 2007-10-24 | 株式会社ルネサステクノロジ | 半導体集積回路装置の製造方法 |

| US6403442B1 (en) * | 1999-09-02 | 2002-06-11 | Micron Technology, Inc. | Methods of forming capacitors and resultant capacitor structures |

-

1999

- 1999-07-01 JP JP18745099A patent/JP3998373B2/ja not_active Expired - Fee Related

-

2000

- 2000-06-14 TW TW089111652A patent/TW466749B/zh not_active IP Right Cessation

- 2000-06-23 KR KR1020000034824A patent/KR100770468B1/ko not_active IP Right Cessation

- 2000-06-30 US US09/610,114 patent/US6444405B1/en not_active Expired - Lifetime

-

2002

- 2002-04-02 US US10/112,945 patent/US20020098678A1/en not_active Abandoned

-

2003

- 2003-02-19 US US10/367,737 patent/US6770528B2/en not_active Expired - Fee Related

-

2004

- 2004-05-17 US US10/846,571 patent/US20040214428A1/en not_active Abandoned

-

2006

- 2006-10-25 KR KR1020060103766A patent/KR100757888B1/ko not_active IP Right Cessation

-

2007

- 2007-03-02 KR KR1020070020994A patent/KR100802698B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR100802698B1 (ko) | 2008-02-12 |

| US20020098678A1 (en) | 2002-07-25 |

| KR20070034028A (ko) | 2007-03-27 |

| US6444405B1 (en) | 2002-09-03 |

| TW466749B (en) | 2001-12-01 |

| US6770528B2 (en) | 2004-08-03 |

| KR100770468B1 (ko) | 2007-10-26 |

| US20030148600A1 (en) | 2003-08-07 |

| KR20010029834A (ko) | 2001-04-16 |

| KR100757888B1 (ko) | 2007-09-11 |

| US20040214428A1 (en) | 2004-10-28 |

| JP2001015712A (ja) | 2001-01-19 |

| KR20060128763A (ko) | 2006-12-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100802698B1 (ko) | 반도체 집적회로장치의 제조방법 | |

| KR100699335B1 (ko) | 반도체 집적회로 장치 및 그 제조방법 | |

| US6900492B2 (en) | Integrated circuit device with P-type gate memory cell having pedestal contact plug and peripheral circuit | |

| JP2992516B1 (ja) | 半導体装置の製造方法 | |

| JP2000156480A (ja) | 半導体集積回路装置およびその製造方法 | |

| JPH10200075A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP3614267B2 (ja) | 半導体集積回路装置の製造方法 | |

| JP3752795B2 (ja) | 半導体記憶装置の製造方法 | |

| US6426255B1 (en) | Process for making a semiconductor integrated circuit device having a dynamic random access memory | |

| JP4290921B2 (ja) | 半導体集積回路装置 | |

| US20080251824A1 (en) | Semiconductor memory device and manufacturing method thereof | |

| WO2002075812A1 (fr) | Procede de production de circuit integre semi-conducteur et dispositif de circuit integre semi-conducteur | |

| JPH1187651A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2006191137A (ja) | 半導体集積回路装置の製造方法 | |

| JP2001217406A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2000058776A (ja) | 半導体装置およびその製造方法 | |

| JPH11297951A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP4133039B2 (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JP2000323480A (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JP2003133436A (ja) | 半導体装置の製造方法 | |

| JPH11186522A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2002217388A (ja) | 半導体装置の製造方法 | |

| JP2001217407A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2003142602A (ja) | 半導体集積回路装置およびその製造方法 | |

| JPH1187263A (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20050315 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060223 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070621 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070717 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070807 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100817 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110817 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110817 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110817 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120817 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120817 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130817 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |