JP3866460B2 - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP3866460B2 JP3866460B2 JP26617699A JP26617699A JP3866460B2 JP 3866460 B2 JP3866460 B2 JP 3866460B2 JP 26617699 A JP26617699 A JP 26617699A JP 26617699 A JP26617699 A JP 26617699A JP 3866460 B2 JP3866460 B2 JP 3866460B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- block

- nand

- signal line

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G11C16/16—Circuits for erasing electrically, e.g. erase voltage switching circuits for erasing blocks, e.g. arrays, words, groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/14—Word line organisation; Word line lay-out

Description

【発明の属する技術分野】

この発明は、電気的書き換え可能な複数のメモリセルを直列接続してNANDセル(メモリセルストリング)を構成してなる不揮発性半導体記憶装置(EEPROM)に関する。

【0002】

【従来の技術】

電気的書き換えを可能としたEEPROMとして、従来より、NANDセル型EEPROMが知られている。NANDセル型EEPROMの1つのメモリセルは、半導体基板上に絶縁膜を介して浮遊ゲート(電荷蓄積層)と制御ゲートが積層されたスタック構造のトランジスタを有する。複数個のメモリセルは、隣接するもの同士でソース・ドレインを共有する形で直列接続されてNANDセルを構成する。このようなNANDセルがマトリクス配列されてメモリセルアレイが構成される。

【0003】

メモリセルアレイの列方向に並ぶNANDセルの一端側のドレインは、選択トランジスタを介してビット線に共通接続され、他端側ソースはやはり選択トランジスタを介して共通ソース線に接続される。メモリセルトランジスタのワード線及び選択トランジスタのゲート電極は、メモリセルアレイの行方向にそれぞれワード線(制御ゲート線)、選択ゲート線として共通接続される。

【0004】

このようなNANDセル型EEPROMは、例えば次のような文献▲1▼,▲2▼により知られている。

【0005】

▲1▼ K. -D. Suh et al., "A 3.3V 32Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme," IEEE J. Solid-State Circuits, Vol.30, pp.1149-1156, Nov.1995

▲2▼ Y. Iwata et al., "A 35ns Cycle Time 3.3V Only 32Mb NAND Flash EEPROM," IEEE J. Solid-State Circuits, Vol.30, pp.1157-1164, Nov.1995.

図18は、NANDセル型EEPROMのメモリセルアレイのひとつのNANDセルブロックの構成を示している。複数個のメモリセルMは、それらのソース、ドレインを隣接するもの同士で共有する形で直列接続されてNANDセルが構成される。NANDセルの一端は選択トランジスタS1を介してビット線BLに、他端はやはり選択トランジスタS2を介して共通接地線に接続される。図18の横方向に並ぶメモリセルMの制御ゲートは、共通にワード線WLに接続される。選択トランジスタS1,S2のゲートも同様に選択ゲート線SSL,GSLに共通接続される。一つのワード線により駆動されるNANDセルの範囲がNANDセルブロックを構成している。

【0006】

通常、この様なNANDセルブロックがビット線方向に複数個配置されてメモリセルアレイが構成される。各NANDセルブロックはデータ消去の単位となっていわゆる一括消去が行われる。またNANDセルブロック内のひとつの選択されたワード線に沿うメモリセル列は1ページと呼ばれ、1ページがデータ読み出し及び書き込みの単位となる。

【0007】

メモリセルMは、例えばnチャネルの場合、浮遊ゲートに電子が注入されたしきい値が正の状態(Eタイプ状態)と、浮遊ゲートの電子が放出されたしきい値が負の状態(Dタイプ状態)とを二値に対応させることにより、データ記憶を行う。例えば、Dタイプ状態が“1”データの保持状態(消去状態)、Eタイプ状態が“0”データ保持状態(書き込み状態)というように定義される。また、“1”データを保持しているメモリセルのしきい値を正方向にシフトさせて“0”データを保持した状態に移行させる動作が「書き込み動作」、“0”データを保持しているメモリセルのしきい値を負方向にシフトさせて“1”データを保持した状態に移行させる動作が「消去動作」というように定義される。この明細書では、以下の説明をこの定義に従って行う。

【0008】

図19は、メモリセルアレイの選択されたNANDセルブロックでのデータ消去、読み出し及び書き込み動作の各部電位関係を示している。消去動作では、選択されたNANDセルブロックの全ワード線を0V、選択ゲート線SSL,GSL及びビット線BLをフローティング(F)とし、メモリセルのP型ウェルに高い正の消去電圧Vera(例えば、3ms、21Vの消去パルス)を与える。その結果、選択ブロックでは、ウェルとワード線の間に消去電圧がかかり、浮遊ゲートの電子がFN(Fowler-Nordheim )トンネル電流によりウェルに放出される。これにより、そのNANDセルブロック内のメモリセルは“1”の消去状態になる。

【0009】

このとき、非選択のNANDセルブロックでは、フローティング状態のワード線とウェルとの容量カップリングにより、消去パルスの影響を受けない。カップリング比は、フローティング状態のワード線に接続される容量から計算される。実際には、ポリシリコンのワード線とセル領域のPウェルとの容量が全容量に対して支配的であり、実測結果から求めたカップリング比は約0.9と大きく、これがFNトンネル電流が流れるのを妨げる。消去ベリファイ(検証)は選択ブロック内の全てのメモリセルのしきい値電圧が例えば−1V以下になったかどうかによって判定される。

【0010】

データ読み出し動作は、選択ワード線に0V、非選択ワード線及び選択ゲート線に一定の読み出し電圧Vread(しきい値によらず、チャネルを導通させるに必要な電圧)を与え、選択されたメモリセルの導通の有無によるビット線BLの電位変化を読むことにより行われる。

【0011】

データ書き込み動作は、選択ワード線に正の高い書き込み電圧Vpgm、非選択ワード線にはパス電圧Vpass、ビット線側の選択ゲート線SSLにVcc、共通ソース線側の選択ゲート線GSLにVss=0Vを与え、“0”を書き込むべきビット線BLにVss、書き込み禁止(即ち“1”の消去状態に保つべき)ビット線BLにVccを与えることにより行われる。このとき、Vssが与えられたビット線につながる選択メモリセルでは、チャネル電位がVssに保持され、制御ゲートとチャネル間の大きな電界がかかって、チャネルから浮遊ゲートにトンネル電流による電子注入が生じる。同じビット線につながるVpassが与えられた他の非選択メモリセルでは、書き込みに十分に電界がかからず、書き込みは行われない。

【0012】

Vccが与えられたビット線に沿うメモリセルでは、NANDセルのチャネルはVcc又はVcc−Vth(Vthは選択トランジスタのしきい値電圧)に予備充電されて選択トランジスタがカットオフする。そして制御ゲートに書き込み電圧Vpgm及びパス電圧Vpassが与えられると、フローティングとなっているNANDセルのチャネルと、Vpgm又はVpassが与えられた制御ゲートとの容量結合によりチャネル電位は上昇して、電子注入が起こらない。

【0013】

以上のようにして、Vssが与えられたビット線とVpgmが与えられた選択ワード線の交差部のメモリセルでのみ、電子注入が行われて“0”書き込みがなされる。選択ブロック内の書き込み禁止のメモリセルにおいては、上述のようにチャネル電位がワード線とチャネルとの容量結合によって決定されるから、書き込み禁止電位を十分に高くするためには、チャネルの初期充電を十分に行うことおよびワード線とチャネル間の容量カップリング比を大きくすることが重要となる。

【0014】

ワード線とチャネル間のカップリング比Bは、B=Cox/(Cox+Cj)により算出される。ここで、Coxはワード線とチャネルとの間のゲート容量の総和、Cjはメモリセルトランジスタのソースおよびドレインの接合容量の総和である。また、NANDセルのチャネル容量とは、これらゲート容量の総和Coxと接合容量の総和Cjの合計となる。さらに、その他の容量である選択ゲート線とソースのオーバラップ容量や、ビット線とソースおよびドレインとの容量等は全チャネル容量に比べて非常に小さいため、ここでは無視している。

【0015】

【発明が解決しようとする課題】

以上に説明したNAND型EEPROMにおいては、従来より平面方向(デザイン・ルール)のスケーリングは行われているが、これに対応した深さ方向(酸化膜厚)のスケーリングは行われていない。具体的に、トンネル酸化膜の膜厚は、16M、32M、64M、256MビットNAND型EEPROMで10nmとほぼ一定である。そしてトンネル酸化膜の膜厚が一定であれば、トンネル酸化膜にかかる電界を一定にするために、メモリセルの書き換え電圧も一定電圧を維持しなければならず、低電圧化できない。トンネル酸化膜の膜厚について、プロセス技術者によりさらに薄膜化することが試みられてはいるが、例えば、5nmの酸化膜は実現していない。また、書き換え電圧を低電圧化させるには、制御ゲートと浮遊ゲート間の容量を増大させ、カップリング比を大きくすれば良い。しかし、これも、制御ゲートと浮遊ゲート間の酸化膜を薄膜化させる必要があったり、制御ゲートと浮遊ゲートの間のキャパシタ面積を増やすなどの工夫が必要であり、容易には成し遂げ得ない。

【0016】

結局、NAND型EEPROMでは、16Mから256Mビットまで書き換え電圧として20V程度の高電圧が必要となっている。このため、その高電圧をワード線に駆動するロウデコーダのトランジスタを高耐圧トランジスタで設計しなくてはならない。高耐圧トランジスタは、周辺回路の通常のトランジスタよりもデザイン・ルールを緩くして、トランジスタ内の各部の寸法を長くすることにより、加わる電界を弱める工夫が成されている。例えば、0.25μmルールで設計した256MビットNAND型EEPROMの場合、この高耐圧トランジスタは、周辺回路の通常のトランジスタよりもデザイン・ルールを数倍大きくしている。そして、256MビットNAND型EEPROMの16個のメモリセルと2個の選択トランジスタから成る1つのNANDストリングのピッチ(長さ)は、8.5μmであり、そのピッチに2個以上の高耐圧トランジスタは配置できず、1個の高耐圧トランジスタを配置するのが限界となっている。

【0017】

例えば、次世代1GビットNAND型EEPROMでは、0.15μmのデザイン・ルールが適用された場合、この1つのNANDストリングのピッチは、約5um程度になる。また、縦方向のスケーリングがやはり困難であったとすると、上述した理由により書き換え電圧を低くすることができない。従って、現在の16個のメモリセルトランジスタと2個の選択トランジスタから成る1つのNANDストリングのピッチには、サイズの大きいワード線駆動用の高耐圧トランジスタを配置できない。このため、例えば、1つのNANDストリングの直列接続のメモリセルトランジスタの数を増やし、例えば、32個のメモリセル構成とか、64個のメモリセル構成とかして、1つのNANDストリングのピッチを大きくしなければならなくなる。

【0018】

しかし、単に1つのNANDストリング内のメモリセルトランジスタの個数を増やすと、同時に消去ブロックサイズが増えてしまう。それは、従来のNAND型EEPROMでは、NANDストリング(NANDセル)を1ブロックとし、ブロック単位での消去しか許されなかったためである。NANDセルブロック単位での消去しか許されない理由は、次の通りである。例えば、16個のメモリセルからなるNANDストリングを8個ずつのメモリセルを書き換えの単位である1ブロックとし、下部ブロックを何度も選択して書き換えたとする。そうすると、上部ブロックのワード線にはパス電圧Vpassのストレスが加わり、書き換えが多数回に及ぶと、非選択ブロックのしきい値電圧も変化してしまう。

【0019】

この消去ブロックのサイズは、16MビットNAND型EEPROMでは、4Kバイト、32MビットNAND型EEPROMでは、8Kバイト、256MビットNAND型EEPROMでは、16Kバイトと大容量化に伴い、徐々に大きくはなっている。しかし、例えば、デジタルカメラのフィルム媒体にNAND型EEPROMを使用した場合、コンパティビリティを保つために急激なブロックサイズの増大はしたくないという要請もある。したがって、大容量の1GビットNAND型EEPROMでも、256MビットNAND型EEPROMと同様に消去ブロックサイズを16Kバイトとする必要が出てくる。

【0020】

この発明は、上記事情を考慮してなされたもので、1つのNANDセルブロック内に複数の消去単位を設定可能としたNAND型EEPROMを提供することを目的としている。

【0021】

【課題を解決するための手段】

この発明による不揮発性半導体記憶装置の第1の態様は、第1の信号線と、第2の信号線と、これら第1の信号線と第2の信号線の間に電気的書き換え可能なメモリセルを複数個直列接続して構成されたNANDセルと、このNANDセルを複数ブロックに分割するためにNANDセル内の所定の隣接メモリセルの間に介在させたブロック分離選択トランジスタと、を有することを特徴とする。

【0022】

なお、この発明においては、複数ブロック間の少なくとも2つ以上のブロック分離選択トランジスタのゲートが共通接続されていても良い。

【0023】

また、この発明による不揮発性半導体記憶装置の第2の態様は、ワード線により選択される電気的書き換え可能なメモリセルが第1の信号線と第2の信号線の間にそれぞれ選択トランジスタを介して複数個直列接続されてNANDセルを構成して、複数のNANDセルが配列されたメモリセルアレイと、アドレスにより前記メモリセルアレイのメモリセル選択を行うアドレスデコーダと、前記メモリセルアレイからの読み出しデータをセンスし、前記メモリセルアレイへの書き込みデータをラッチする機能を有するセンスアンプ回路と、前記メモリセルアレイへのデータ書き込み、消去及び読み出しの制御を行う制御回路とを備え、前記メモリセルアレイは、各NANDセル内の所定の隣接メモリセルの間に介在させたブロック分離選択トランジスタにより複数のメモリセルユニットに分割されていることを特徴とする。

【0024】

なお、この発明において、具体的には、前記メモリセルアレイのデータ書き換え時、前記複数のメモリセルユニットの一つを消去単位として選択してデータ消去がなされ、1本のワード線に沿った複数のメモリセルの所定範囲を1ページとしてデータ書き込みがなされる。

【0025】

なおこの発明において、データ消去は、選択されたメモリセルユニットの全ワード線に接地電位を与え、非選択のメモリセルユニットの全ワード線、前記第1の信号線側及び第2の信号線側の選択トランジスタ及び前記ブロック分離選択トランジスタのゲートにそれぞれつながる選択ゲート線をフローティングとし、且つ前記メモリセルアレイが形成された基板領域に消去電圧を与えることにより行われる。

【0026】

なおこの発明において、データ書き込みは、書き込むべきデータ“0”,“1”に応じて第1の信号線に接地電位、電源電位を与え、選択されたメモリセルユニット内の非選択ワード線にメモリセルを導通させるパス電圧を与え、非選択のメモリセルユニットの全ワード線、及び非選択のメモリセルユニットと前記選択されたメモリセルユニットの間の前記ブロック分離選択トランジスタのゲートにつながる選択ゲート線にメモリセルを導通させる前記パス電圧より低い読み出し電圧を与え、前記選択されたメモリセルユニットの選択ワード線に前記パス電圧より高い書き込み電圧を与えることにより行われる。

【0027】

なおこの発明において、具体的には、前記メモリセルアレイは、各NANDセル内の所定の隣接メモリセルの間に介在させた2n −1(n:正の整数)個のブロック分離選択トランジスタにより、2n 個のメモリセルユニットに分割される。この場合、各メモリセルユニットが同数のメモリセルを含むようにしてもよいし、或いは異なる数のメモリセルを含むようにしてもよい。

【0028】

なおこの発明において好ましくは、前記アドレスデコーダのなかのワード線駆動回路は、前記メモリセルアレイのワード線方向の両端部に、1乃至2メモリセルユニット毎に振り分けて配置される。

【0029】

また、この発明による不揮発性半導体記憶装置の第3の態様は、それぞれ異なるワード線により選択される電気的書き換え可能な複数のメモリセルがビット線に直列接続されてNANDセルを構成し、ワード線方向に並ぶ複数のNANDセルがNANDセルブロックを構成し、且つ各NANDセルの所定の隣接メモリセルの間に介在させたブロック分離選択トランジスタにより前記NANDセルブロックが複数のメモリセルユニットに分割されたメモリセルアレイと、アドレスにより前記メモリセルアレイのメモリセル選択を行うアドレスデコーダと、前記メモリセルアレイからの読み出しデータをセンスし、前記メモリセルアレイへの書き込みデータをラッチする機能を有するセンスアンプ回路と、前記複数のメモリセルユニットの一つを消去単位として選択してそのメモリセルユニット内のデータを一括消去し、1本のワード線に沿った複数のメモリセルの所定範囲を1ページとしてデータ書き込みを行うデータ書き換え手段と、を備えたことを特徴とする。

【0030】

この発明によると、NANDセル内のブロック分離選択トランジスタを介在させることによって、1NANDセルブロック内に複数の消去ブロックを設定することが可能であり、消去ブロックサイズを増やすことなく、1NANDストリング内のメモリセルの個数を増やすことを可能となる。

【0031】

また、この発明による不揮発性半導体記憶装置の第4の態様は、第1および第2の信号線と、第1および第2の選択トランジスタと、各々が、電気的に書き換え可能なメモリセルを複数個直列接続して構成された第1乃至第n(n≦3)のNANDセルブロックと、第1乃至第(n−1)のブロック分離選択トランジスタと、を備え、前記第1の信号線に前記第1の選択トランジスタが接続され、前記第1の選択トランジスタに前記第1のNANDセルブロックが接続され、第i(1≦i≦n−1)のNANDセルブロックに第iのブロック分離選択トランジスタが接続され、第i(1≦i≦n−1)のブロック分離選択トランジスタに第(i+1)のNANDセルブロックが接続され、第nのNANDセルブロックに第2の選択トランジスタが接続され、第2の選択トランジスタに第2の信号線が接続され、前記第1乃至第nのブロック分離選択トランジスタのうち、少なくとも2つのブロック分離選択トランジスタのゲートが共通接続されていることを特徴とする。

【0032】

また、この発明による不揮発性半導体記憶装置の第5の態様は第1および第2の信号線と、第1および第2の選択トランジスタと、各々が電気的に書き換え可能な第1乃至第nのメモリセルと、第1乃至第(n−1)のブロック分離選択トランジスタと、を備え、前記第1の信号線に前記第1の選択トランジスタが接続され、前記第1の選択トランジスタに前記第1のメモリセルが接続され、第i(1≦i≦n−1)のメモリセルに第iのブロック分離選択トランジスタが接続され、第i(1≦i≦n−1)のブロック分離選択トランジスタに第(i+1)のメモリセルが接続され、第nのメモリセルに第2の選択トランジスタが接続され、第2の選択トランジスタに第2の信号線が接続され、前記第1乃至第nのブロック分離選択トランジスタのうち、少なくとも2つのブロック分離選択トランジスタのゲートが共通接続されていることを特徴とする。

【0033】

なお、第4および第5の態様において前記第1および第2の選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは金属電極から構成され、前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートは多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは金属電極から構成されていても良い。

【0034】

なお、第4および第5の態様において、前記第1および第2の選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは、金属電極から構成され、前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは、金属電極から構成されるように構成しても良い。

【0035】

なお、データ書き込み時に、前記第1の選択トランジスタおよび前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートには、電源電圧Vcc若しくはそれ以上の読み出し電圧Vreadが印加され、前記第2の選択トランジスタのゲートには、接地電圧Vssが印加されるように構成しても良い。

【0036】

なお、前記第1の信号線はビット線で、前記第2の信号線はセルソース線であることが好ましい。

【0037】

なお、前記メモリセルは浮遊ゲートと、前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートと、を有する二層のスタック構造からなる電気的書き換え可能なメモリセルであることが好ましい。

【0038】

【発明の実施の形態】

第1の実施の形態

図1は、この発明の第1の実施の形態によるNAND型EEPROMのメモリセルアレイの1つのNANDセルブロック1のメモリセルアレイの等価回路を示している。この例では、ビット線BLの本数として528バイト((512+16)×8=4224本)を例にとり、示している。この実施の形態では、1つのNANDセルは32個のメモリセルトランジスタMC0〜MC31により構成されている。メモリセルトランジスタMC0〜MC31はビット線BLとソース線SLの間に直列接続される。ビット線BLとメモリトランジスタMC0の間には選択トランジスタSSTが設けられ、ソース線SLとメモリセルトランジスタMC31の間にも同様に選択トランジスタGSTが設けられている。

【0039】

この実施の形態においては、上述した二つの選択トランジスタSST,GSTの他に、1つのNANDセルを2分割する形でブロック分離のための選択トランジスタSTが設けられている。即ち、隣接するメモリセルトランジスタMC15とMC16の間にブロック分離選択トランジスタSTを介在させることにより、NANDブロック1が二つのメモリユニットMU0,MU1に分割されている。この2分割されたメモリユニットMU0,MU1がそれぞれデータ消去の単位ブロックサイズとなる。

【0040】

図2は、NANDセルブロック1のレイアウトであり、図3及び図4はそれぞれ、図2のA−A′、B−B′断面を示している。p型シリコン基板10のメモリセルアレイ領域にはn型ウェル11が形成され、このn型ウェル11内にはp型ウェル12が形成され、このp型ウェル12には素子分離絶縁膜13により素子領域が区画されている。素子領域にトンネル酸化膜14を介して浮遊ゲート15が各メモリセルトランジスタ毎に形成され、この上に層間ゲート絶縁膜16を介して制御ゲート17が形成されている。

【0041】

制御ゲート17は、図2に示すように行方向に連続的に配設されて、これがワード線WLとなる。制御ゲート17をマスクとしてイオン注入を行うことにより、ソース、ドレイン拡散層21が形成されている。図3では、選択トランジスタSST,STは、メモリセルトランジスタMCと同様の構造として示しているが、図4の断面に対応する断面では、浮遊ゲート15に対応する層と制御ゲート17に対応する層とが、所定箇所で共通接続されて連続的に配設されて、選択ゲート線SSL,STLとなる。ソース側の選択トランジスタGSTも同様であり、そのゲートは連続的に配設されて、選択ゲート線GSLとなる。ここで、選択トランジスタSST,STとメモリセルトランジスタMCとはゲート酸化膜厚を異ならせてもよい。

【0042】

ページ書き込み/読み出し機能を持つNAND型EEPROMとしての全体ブロック構成は、図5のようになる。図示のように、メモリセルアレイ51と、外部から入力されたアドレスに基いてメモリセルアレイ51のワード線を選択駆動するロウデコーダ52と、メモリセルアレイ51のビット線BLに接続される、入出力データのラッチ機能を持つセンスアンプ回路53とを有する。センスアンプ回路53にはカラムゲート55が接続され、カラムデコーダ54により外部から入力されたアドレスに基いてカラムゲート55を制御することで、対応するビット線およびセンスアンプ回路が選択される。

【0043】

センスアンプ回路53は、カラムゲート55を介してデータ入出力(I/O)バッファ58に接続される。書き込み動作や消去動作に必要な高電圧を供給するために昇圧回路56が設けられ、またメモリセルアレイ51へのデータ書き込み、消去及び読み出しの制御信号を生成してチップ内部を制御するとともに外部とのインターフェースをとるための制御回路57が設けられている。

【0044】

ロウデコーダ52は、データの書き込み時、消去時およびデータの読み出し時にそれぞれアドレス信号に基づいて複数のワード線WLを選択駆動するものであり、そのワード線ドライバには、所要の電圧が供給される。センスアンプ回路53は、読み出し時にビット線データをセンスする機能、書き込み時に外部からロードされるデータを保持するデータラッチ機能、書き込み及び消去の際にビット線BLに対して所要の電圧をそれぞれ選択的に供給する機能を有する。

【0045】

制御回路57には、NANDセルに対する消去/消去ベリファイ、書き込み/書き込みベリファイ、及び読み出し動作を制御するためのシーケンス制御手段(例えばプログラマブルロジックアレイ)が含まれている。

【0046】

図6は、センスアンプ回路53のなかの一つのセンスアンプの構成を示している。センスアンプは、入出力が交差接続されたインバータI1,I2により構成されたデータラッチ回路61を主体とする。このラッチ回路61の一方のノードQbはセンス用NMOSトランジスタM12と活性化用NMOSトランジスタM13を介して接地される。センス用NMOSトランジスタM12のゲートがセンスノードNsenseである。センスノードNsenseは、トランスファゲートNMOSトランジスタM1を介してビット線BLiに接続されている。

【0047】

ラッチ回路61の他方のノードQは、リセット用NMOSトランジスタM4を介してセンスノードNsenseに接続され、またカラム選択NMOSトランジスタM11を介して入出力バッファに接続されている。センスノードNsenseにはまた、センスノードNsenseをプリチャージするためのNMOSトランジスタM2、及びディスチャージするためのNMOSトランジスタM3が設けられている。

【0048】

次に、この実施の形態によるNAND型EEPROMのデータ消去、書き込み、及び読み出しの動作を順次説明する。

【0049】

図7は、データ消去動作での各部のバイアス電位関係を示している。前述のように、従来のNAND型EEPROMでは1つのNANDセルブロックが消去単位となるのに対し、この実施の形態では、図1に示すメモリユニットMU0,MU1がそれぞれ消去単位となる。図7では、下部メモリユニットMU1を選択ブロック、上部メモリユニットMU0を非選択ブロックとしたデータ消去動作の例を示している。

【0050】

即ち、図1において、ワード線WL0〜WL15の範囲を非選択ブロック、WL16〜WL31の範囲を選択ブロックとする。消去動作が開始されると、消去する選択ブロックのワード線WL16〜WL31には、Vss(0V)が印加され、非選択ブロックのワード線WL0〜WL15および選択ゲート線SSL,GSL,STLはフローティング状態にされる。この状態で、メモリセルアレイのpウェル(p−well)に消去電圧Vera(20V)が印加される。

【0051】

このとき、非選択ブロックのワード線WL0〜WL15および選択ゲート線SSL、STL、GSLはpウェルとの容量結合により、α×Veraに昇圧される。αは約0.9であるから、18V程度まで上がる。また、ビット線BL0、BL1、およびソース線SLはpウェルとビット線コンタクト部のn+ 型拡散層およびソース線SL部のn+ 型拡散層とのPN接合が順バイアス状態となり、Vera−Vfまで上昇する。VfはPN接合のビルトイン・ポテンシャルであり、約0.7Vであるから、ビット線BL0、BL1及びソース線SLは約19.3V程度となる。従って、非選択ブロックのワード線WL0〜WL15に沿ったメモリセルトランジスタでは、消去動作は起こらない。

【0052】

選択ブロックのワード線WL16〜WL31に沿ったメモリセルトランジスタでは、基板領域にVera、制御ゲートにVssが印加されているため、浮遊ゲートの電子はトンネル電流により基板領域(pウェル)へと放出され、メモリセルトランジスタの記憶データは一括消去される。

【0053】

図8は、データ書き込み動作での各部のバイアス電位関係を示している。図8では、上の説明で一括消去された選択ブロック(即ちメモリユニットMU1)内のワード線WL17について書き込みを行う場合を示している。また、ビット線BL0では“0”データ書き込みを行い、ビット線BL1では“1”データ書き込み(即ち、“1”データの消去状態を保つ書き込み禁止)を行う場合を想定している。

【0054】

この場合、図9は、図1に示すビット線中二つのビット線BL0,BL1のみ取り出して、電位関係を示したものである。

【0055】

このデータ書き込みでは、まずビット線BL0,BL1にそれぞれ書き込み用の接地電位Vss、書き込み禁止用の電源電位Vccが与えられる。その後ソース線側の選択ゲート線GSLはVssに保ったまま、他のワード線及び選択ゲート線に、Vccよりわずかに高い読み出し電圧Vread(約3.5V程度)が与えられる。これにより、ビット線BL0につながるNANDセルチャネルには書き込みのための電位Vssが伝達される。ビット線BL1につながるNANDセルチャネルには、書き込み禁止のためのVccが伝達されるが、そのチャネル電位がVread−Vth(選択トランジスタ、若しくは、メモリセルトランジスタのしきい値電圧の内、高いしきい値電圧)だけ低下した値まで上昇すると、選択トランジスタSSTはオフになり、チャネルはフローティングになる。

【0056】

この状態で次に、選択ブロックのワード線の内、書き込みを行わない非選択ワード線WL16およびWL18〜WL31には、読み出し電圧Vreadより高いパス電圧Vpass(約8V)が、書き込みを行う選択ワード線WL17には更に高い書き込み電圧Vpgm(約16V)が、それぞれ印加される。非選択ブロックのワード線WL0〜WL15、ドレイン側選択ゲート線SSL、及びブロック分離選択ゲート線STLは、電位を値Vreadのまま保つ。

【0057】

この時、選択ブロック内のビット線BL1側のチャネル領域は、初期状態の電位Vcc−Vthから電位VpassおよびVpgmに上昇するワードとの容量結合により、β×(Vpass−Vread)+(Vcc−Vth)まで上昇する。電位Vpgmが与えられるワード線1本に対して、電位Vpassが与えられるワード線数は15本であるから、ほぼ値Vpassにより決まる上述のチャネル電位になる。ここで、βは、ワード線とチャネル領域の容量カップリング比であり、約0.5である。

【0058】

この時、書き込み禁止のビット線BL1側のブロック分離選択トランジスタST1は、ゲート電圧がVreadであり、チャネル電圧が上述のように昇圧される結果、ゲート・ソース間電圧が負になりカットオフする。即ち、書き込み禁止のビット線BL1側では、メモリセルトランジスタMC171を含む選択ブロック内のチャネル領域は、非選択ブロックであるメモリセルユニットMU0側のチャネル領域とは切り離されたフローティング状態で昇圧される。

【0059】

一方、電位Vssが与えられたビット線BL0側では、ビット線BL0から伝達される電位Vssによりブロック分離選択トランジスタST0がオン状態を保つ。従って、選択されたメモリセルトランジスタMC170のチャネルまで電位Vssが伝わっている。この結果、書き込み電圧Vpgmが与えられた選択ワード線WL17で駆動されるメモリセルトランジスタMC170では、トンネル注入による書き込み動作が起こる。同じビット線BL0に沿った他のメモリセルでは、大きな電界がかからず、書き込みは生じない。

【0060】

なお、実際のデータ書き込み動作は、図5に示す制御回路57によるシーケンス制御により、書き込み電圧パルス印加と書き込み後のしきい値をチェックするベリファイ(検証)動作を繰り返して、1ページ分のデータを所定しきい値範囲に追い込むという制御が行われる。1ページは例えば、1ワード線の範囲のビット線数であるが、ページバッファ等との関係で1ワード線の範囲を2ページとする場合もある。

【0061】

この様なページ単位のデータ書き込みサイクルを説明すると、まず、図5のセンスアンプ回路53のデータラッチに連続的に書き込みデータがロードされる。このとき、“0”が書き込み動作を行うセルデータであり、“1”は書き込み禁止のセルデータである。書き込みサイクルは、次のステップで構成される。

(1)ビット線のレベルを、センスアンプにラッチされているデータに従って、Vss又はVccに設定する。

(2)選択ワード線に書き込み電圧パルスを印加する。

(3)選択ワード線を放電する。

(4)書き込みベリファイ読み出しを行う。

【0062】

ベリファイ動作では、十分な書き込みが行われたセルに対応するデータラッチのデータが“0”から“1”に変わり、それ以上の書き込み動作が行われないようにする。ベリファイ動作のバイアス条件は、基本的に通常のデータ読み出しの場合と同様であるが、しきい値の判定を行うために、選択ワード線に与えられる電圧は通常の読み出しの場合の0Vより高く設定される。このベリファイ動作で書き込みが不十分と判定されたセルについてのみ、次のサイクルで再度書き込み動作を繰り返される。

【0063】

図10は、データ読み出し動作での各部の電位関係を示している。読み出しが開始されると、ビット線は初期状態の電位Vb1(約1.5V)に予備充電される。そして、選択ブロックの選択ワード線(図10では、WL19)の電位をVssにする以外は、選択NANDセル内の全ての選択ゲート線およびワード線の電位を読み出し電圧Vreadとする。これにより、“0”データ(書き込み状態のメモリセル)を読み出すビット線の電位はVb1を保ち、“1”データ(消去状態のメモリセル)を読み出すビット線の電位はVBb1からVssになる。このビット線電位の変化を、従来と同様にセンスアンプにより“0”,“1”として判別する。

【0064】

以上のようにこの実施の形態によると、NANDセルブロック内をブロック分離選択トランジスタにより二つのメモリセルユニットに分けて、一つのメモリセルユニットを消去単位とするデータ書き換えを可能としている。これにより次のような効果が得られる。即ち、現在より微細なデザイン・ルールでNAND型EEPROMを作った場合に、メモリセルアレイを駆動する高耐圧トランジスタを配置するためには一つのNANDセル内のメモリセル数をより多くすることが必要になる。従来の方式では、NANDセルブロックがそのまま消去ブロックサイズであるから、NANDセルのメモリセル数が増えると、消去ブロックサイズも大きくなってしまうが、この実施の形態によれば、消去ブロックサイズを大きくすることなく、NANDセルのメモリセル数を多くすることができる。これにより高耐圧トランジスタの配置が容易になる。また、EEPROM容量が増大した場合にも消去ブロックサイズの変更をしたくないという要請にも、応えることが可能となる。

【0065】

また、データ消去後の書き込み動作時、メモリセルユニットの間に挿入されたブロック分離選択トランジスタと非選択ブロック(メモリセルユニット)のワード線には、パス電圧Vpassより低い読み出し電圧Vreadを与えた状態で非選択ブロックのチャネル領域が選択ブロックのチャネル領域と分離されるようにしている。従って、従来の構成でNANDセルブロック内に消去単位を設定して繰り返しデータ書き換えを行った場合のように、非選択ブロックのワード線にパス電圧Vpassが与えられることがなく、ストレスが低減され、信頼性が向上する。

【0066】

第1の実施の形態では、一つのブロック分離選択トランジスタSTを挿入することにより、NANDセルブロックを二つのメモリユニットに分割したが、一般的には、2n −1(n:正の整数)個のブロック分離選択トランジスタを挿入することにより、2n 個のメモリセルユニットに分割することができる。またこの場合、各メモリセルユニットが2m (m:正の整数)個ずつ同数のメモリセルを含むようにすることもできるし、或いは各メモリセルユニットのメモリセル数2m が異なるように設定することもできる。

【0067】

第2の実施の形態

図11は、32個のメモリセルトランジスタからなる1NANDストリングを4個のメモリセルユニットMU0〜MU3に分割した第2の実施の形態の構成を示している。4個のメモリセルユニットMU0〜MU3はそれぞれビット線BL側の選択トランジスタSST、ブロック分離選択トランジスタST0〜ST2、および、ソース線SL側の選択トランジスタGSTを介してビット線BLとソース線SLとの間に直列接続されている。各メモリセルユニットは、等しく8個のメモリセルトランジスタを含む。

【0068】

図12は、この実施の形態において、メモリセルユニットMU2が選択されて消去される場合のバイアス状態を示している。このとき選択ブロック(即ちメモリセルユニットMU2)内のワード線WL16WL23には電位Vssが与えられ、その他の非選択ワード線及び選択ゲート線はフローティングとして、Pウェルに消去電圧Veraが与えられる。これにより、第1の実施の形態と同様に、選択ブロックの一括消去がなされる。

【0069】

図13はこの実施の形態において、ワード線WL19に関してデータ書き込みを行う場合のバイアス状態を示している。この場合も選択NANDセル内の非選択ブロックであるメモリセルユニットMU0,MU1,MU3のワード線の電位は全て読み出し電圧Vreadとする。選択されたメモリセルユニットMU2では、選択ワード線WL19に書き込み電圧Vpgmが、その他の非選択ワード線にはパス電圧Vpassが与えられる。これにより、ワード線WL19に沿って、ビット線BLに与えられたデータ電位に応じて、書き込み及び書き込み禁止のバイアス状態が得られる。

【0070】

この実施の形態によっても、消去ブロックサイズを大きくすることなく、NANDセルのメモリセル数を多くすることができ、これにより高耐圧トランジスタの配置が容易になる。また、EEPROM容量が増大した場合にも消去ブロックサイズの変更をしたくないという要請にも、応えることが可能となる。

【0071】

また、データ消去後の書き込み動作時、メモリセルユニットの間に挿入されたブロック分離選択トランジスタと非選択ブロック(メモリセルユニット)のワード線には、パス電圧Vpassより低い読み出し電圧Vreadを与えた状態で非選択ブロックのチャネル領域が選択ブロックのチャネル領域と分離されるようにしている。従って、非選択ブロックのワード線にパス電圧Vpassが与えられることがなく、ストレスが低減され、信頼性が向上する。

【0072】

更にこの実施の形態では、書き込み動作において、選択されたメモリセルユニットMU2の書き込み禁止のチャネル領域のリーク電流を低減化させるため、ソース線SLの電位はVccにしている。これにより、メモリセルユニットMU3のチャネル領域はVcc−Vthまで充電される。この様にすると、ブロック分離選択トランジスタST2にバックバイアス効果が働き、リーク電流が低減される。同時にブロック分離選択トランジスタST2に加わるドレイン・ソース間電圧も低減化でき、トランジスタST2のパンチスルーも抑えられる。

【0073】

第3の実施の形態

図14は、メモリセルユニット内のメモリセルトランジスタの個数を変えた第3の実施の形態の構成を示す図である。この実施の形態では、メモリセルユニットMU0とMU1はそれぞれ2個直列接続されたメモリセルトランジスタから構成され、MU2は4個、MU3は8個のメモリセルトランジスタで構成されている。

【0074】

この実施の形態によっても、消去ブロックサイズを大きくすることなく、NANDセルのメモリセル数を多くすることができ、その結果高耐圧トランジスタの配置が容易になる。また、EEPROM容量が増大した場合にも消去ブロックサイズの変更をしたくないという要請にも、応えることが可能となる。

【0075】

また、データ消去後の書き込み動作時、メモリセルユニットの間に挿入されたブロック分離選択トランジスタと非選択ブロック(メモリセルユニット)のワード線には、パス電圧Vpassより低い読み出し電圧Vreadを与えた状態で非選択ブロックのチャネル領域が選択ブロックのチャネル領域と分離されるようにしている。従って、非選択ブロックのワード線にパス電圧Vpassが与えられることがなく、ストレスが低減され、信頼性が向上する。

【0076】

更にこの実施の形態におけるようにメモリセル数の異なる複数種のメモリセルユニットを設けると、データ書き換えのサイズを適宜選択することができる。従って、多様な用途に好適である。

【0077】

第4の実施の形態

図15は更に、各メモリセルユニットをメモリセルトランジスタ1個により構成し、ブロック分離選択トランジスタとメモリセルトランジスタとを交互に直列接続した第4の実施の形態の構成を示す図である。

【0078】

この実施の形態によっても、消去ブロックサイズを大きくすることなく、NANDセルのメモリセル数を多くすることができ、その結果高耐圧トランジスタの配置が容易になる。また、EEPROM容量が増大した場合にも消去ブロックサイズの変更をしたくないという要請にも、応えることが可能となる。

【0079】

また、データ消去後の書き込み動作時、ブロック分離選択トランジスタと非選択ブロック(メモリセルユニット)のワード線に、パス電圧Vpassより低い読み出し電圧Vreadを与えた状態で非選択ブロックのチャネル領域が選択ブロックのチャネル領域と分離されるようにすることで、NANDセルブロック内に消去単位を設定して繰り返しデータ書き換えを行った場合のストレスが低減され、信頼性が向上する。

【0080】

更にこの実施の形態の場合、消去ブロックサイズが書き込みページのサイズと同じになるため、ページ単位でのデータ書き換えが可能となる。

【0081】

第5の実施の形態

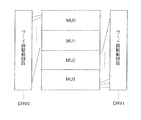

図16は、第1の実施の形態のメモリセルアレイ構成の場合に、ロウデコーダのなかのメモリセルユニットMU0に対するワード線駆動回路DRV0と、メモリセルユニットMU1に対するワード線駆動回路DRV1とを、メモリセルアレイのワード線方向の両端部に振り分けて配置した第5の実施の形態の構成を示す図である。メモリセルユニット数が4個以上と多い場合には、同様の手法で、隣接する二つのメモリセルユニットでそれらのワード線駆動回路を左右に振り分けるようにして、メモリセルアレイの両側にワード線駆動回路を配置する。

【0082】

NANDセルブロック毎にワード線駆動回路を左右に振り分ける手法は、既に特願平6−198840号明細書(平成6年8月23日出願)や、米国特許第5,517,457号明細書、米国特許第5,615,163号明細書等に開示されている。この発明では、NANDストリング内をメモリセルユニットとしてブロック化しているから、そのブロック毎に、図示のようにワード線駆動回路を振り分けて配置することにより、NANDストリング毎にワード線駆動回路を振り分けた場合に比べて、レイアウト上のフレキシビリティがより向上し、コンパクトな設計が可能となる。特にデザイン・ルールが小さくなり、一つのメモリセルユニットの幅内にワード線駆動回路の高耐圧トランジスタを配置できない場合に、有効である。

【0083】

第6の実施の形態

図17は更に、メモリセルユニットの2個ずつについて、ワード線駆動回路DRV0,DRV1を左右に振り分け配置した第6の実施の形態の構成を示す図である。図16に示す第5の実施の形態の場合に比べて更にデザイン・ルールが小さくなり、二つのメモリセルユニットの範囲内に高耐圧トランジスタを配置できない場合には、この様なワード線駆動回路の配置とすればよい。

【0084】

本発明の更に他の実施の形態を説明する前に、図15に示す第4の実施の形態において、ブロック分離選択トランジスタST0〜ST6をメモリセルMC0〜MC7と同様な構造にした場合の例を考え、そのレイアウトを図20に示し、この図20のA−A′断面を図21に示す。

【0085】

この場合のメモリセルサイズのブロック分離選択トランジスタ間のメモリセル数依存性を図22に示す。ここでFはFeature size、すなわちデザイン・ルールを示してい。また、この例においては、メモリサイズは1つのメモリセルユニットが16個のメモリセルで構成されている場合を示している。

【0086】

この例においては、ブロック分離選択トランジスタを利用して、ブロック分割することにより、従来のNANDセルのストリングにおいて、選択トランジスタ間のメモリセル数を少なくしていく場合に比べて、はるかに小さな面積のメモリセルが実現できる。例えば、選択トランジスタ若しくはブロック分離選択トランジスタ間のメモリセル数を1個の場合、従来のNANDセルのストリングの約半分のセルサイズが実現できる。

【0087】

しかし、選択トランジスタ間のメモリセル数が16個の場合のセルサイズを100とすると、ブロック分離選択トランジスタ間のメモリセル数が1個となると、セルサイズが219と約2倍に増大してしまう(図22参照)。

【0088】

図23(a),(b),(c)を用いてこの理由を説明する。従来型でしかも選択トランジスタ間のメモリセル数が多い場合、メモリセル1個のサイズは素子分離にSTI(Shallow Trench Isolation)を用いると、ビット線ピッチ2F×ワード線ピッチ2F=4F2 のセルサイズがほぼ実現できる(図23(a)参照)。しかし、本発明のNANDストリングはビット線ピッチ2F×ワード線ピッチ4F=8F2 にほぼ等しくなってしまう(図23(b)参照)。これは、図23(c)で示しAND型EEPROMのビット線ピッチ4F×ワード線ピッチ2F=8F2 とほぼ同じメモリサイズとなる。なおこのAND型EEPROMの断面図を図24に示す。

【0089】

そこで、ブロック分離選択トランジスタ間のメモリセル数を減らしてもメモリセルサイズが増加しない例を本発明の第7および第8実施の形態として以下に説明する。

【0090】

第7の実施の形態

この第7の実施の形態のNAND型EEPROMは、図11に示す第2の実施の形態のNAND型EEPROMにおいて、読み出し、消去、書き込みを図25、図26、図27に示すように制御するようにした構成となっている。読み出し、書き込みに関しては、ワード線WL19が選択された場合を考える。基本的な特徴は、常にブロック分離選択トランジスタのゲート電圧はそれぞれの場合、等しい電圧に制御することである。

【0091】

すなわち、読み出し時は、選択ゲート線STL0,STL1,STL2は全て、電圧Vreadにする(図25参照)。

【0092】

また、消去時は選択ゲート線STL0,STL1,STL2は全てα×Veraフローティングにする(図25)。さらに、書き込み時は選択ゲート線STL0,STL1,STL2は全て電圧Vreadとし、選択ゲート線GSLをVssとする。選択ゲート線STL2がVreadでも、非選択ブロックのワード線WL24〜WL31がVreadとなるため、書き込み禁止のNANDストリング内のブロック分離選択トランジスタST2はカットオフする。

【0093】

したがって、この第7の実施の形態のNAND型EEPROMは、図28に示すように、ブロック分離選択ゲート線STLを共通にできる。

【0094】

第8の実施の形態

本発明の第8の実施の形態は、図15に示す第4の実施の形態において、読み出し、消去、書き込みの電圧条件を図29、図30、図31に示すように構成したものである。読み出し、書き込みに関しては、ワード線WL3が選択された場合を示している。

【0095】

したがって、第7の実施と同様に、この第8の実施の形態の構成も図32に示すようにブロック分離選択ゲート線STLを共通にできる。また、ビット線側の選択ゲートSSLも共通にした場合、第7の実施の形態、第8の実施の形態は各々図33、図34に示すように構成しても有効である。ただし、セルソース線側の選択ゲートGSLは、書き込み時にVssにする必要があり、これは、共通化できない。

【0096】

なお第7および第8の実施の形態においては、ブロック分選択ゲート線を全て共通にしたが、少なくとも2つのブロック分離選択ゲート線を共通に接続しても良い。

【0097】

次に本発明のNAND型EEPROMの製造方法およびプロセスの構成を説明する。ブースタプレート技術が最近提案されているが、これと同様なプロセスを本発明の製造方法に利用すれば良い。

【0098】

まず、提案されたブースタプレートなる導電体を用いて非書き込みNAND列のチャネル電位を高くし、かつ、書き込み/消去/読み出しの電圧を低下させるNAND型EEPROMについて説明する。

【0099】

このNAND型EEPROMについては文献(J.D.Choi et al., "A Novel Booster Plate Technology in High Density NAND Flash Memories for Voltage Scaling-Down and Zero Program Disturbance," in Symp. VLSI Technology Dig. Tech. Papers, June 1996, pp.238-239)に記載されている。

【0100】

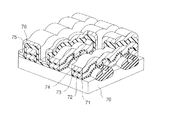

図35は、ブースタプレートを有するNAND型EEPROMの構成を示す斜視図であり、このNAND型EEPROMは次のように構成されている。図35に示すように、基板70はゲート絶縁膜71を介して浮遊ゲート72が形成され、この浮遊ゲート72上にONO膜73を介して制御ゲート74が形成されている。そして、さらに前記制御ゲート74上にはプレート酸化膜75を介してブースタプレート76が形成されている。

【0101】

すなわち、上記文献のNAND型EEPROMは、従来のNAND型EEPROMを作製した後に、プレート酸化膜75であるCVD酸化膜(SiO2 )とタングステン・ポリサイド(poly−SiとWSiX )を堆積し、その後、ポリサイド層をパターニングし、各ブロックの全メモリセル・トランジスタを覆うブースタプレート76を形成したものである。

【0102】

メモリセルの動作は、基本的には従来のNAND型EEPROMとほぼ同様であるが、ブースタプレート76には、書き込み時に書き込み電圧が、また消去時に0Vがそれぞれ印加される。

【0103】

ところで、前記ブースタプレートには2つの利点がある。一つは、書き込みの際の容量カップリングγが大きくなることである。ブースタプレートがない従来のNAND型EEPROMにおいて、容量カップリングγは、

γ=Ccf/(Cfs+Ccf)

と表わされる。ここで、Ccfは制御ゲート(ワード線)74と浮遊ゲート72間の容量であり、Cfsは浮遊ゲート72と基板70間の容量である。一方、ブースタプレート76を付加した場合の容量カップリング比γbは、

γb=(Ccf+Cbf)/(Cfs+Ccf+Cbf)

と表わされ、従来のブースタプレートがない場合のγよりも大きくなる。したがって、書き込み時の書き込み電圧を低下できる。ここで、Cbfはブースタプレート76と浮遊ゲート72間の容量である。

【0104】

また、消去時の容量カップリング比は、(1−γb)で表わされるため、基板70と浮遊ゲート72間の電位差を大きくでき、従来よりも高速な消去、あるいは、消去電圧を低下することが可能となる。また、γbが大きくなることによって、読み出し時におけるパス・トランジスタへの印加電圧も低下できる。

【0105】

もう一つの利点は、制御ゲート(ワード線)74とチャネル間の容量カップリング比が大きくなることである。ブースタプレート76がある場合の容量カップリング比Bbは、

Bb=(Cox+Cboot)/(Cox+Cboot+Cj)

と表わされる。ここで、Coxは制御ゲート(ワード線)74とチャネルとの間のゲート容量の総和、Cbootはブースタプレート76とチャネルとの間のゲート容量の総和、Cjはセルトランジスタのソースおよびドレインの接合容量の総和である。したがって、書き込み時にパス・トランジスタの電圧を過度に高めなくても、書き込み禁止のNAND列のチャネル電位を高くすることができ、誤書き込みに対するマージンが向上できる。

【0106】

このブースタプレートをブロック分離選択ゲート線に利用すれば良い。

【0107】

次に本発明のNAND型EEPROMの製造方法について説明する。図36〜図50は、本発明のNAND型EEPROMの製造工程を示す図である。図36,39,42,45,48は、本発明のNAND型EEPROMの製造工程における平面図であり、図37,40,43,46,49はそれぞれの製造工程における平面図中のX−X′に沿った断面図、図38,41,44,47,50はそれぞれの製造工程における平面図中のY−Y′に沿った断面図である。

【0108】

図36〜図38に示すように、p形シリコン基板81上にメモリセルnウェル82を形成し、このメモリセルnウェル82内にメモリセルpウェル83を形成する。このメモリセルpウェル83上に、フィールド酸化膜(素子分離絶縁膜)84を形成する。以下に上記フィールド酸化膜84で囲まれた領域への、NANDセル、ここでは4個のメモリセルトランジスタとそれを挟む2つの選択ゲートトランジスタからなるNANDセルの製造方法を示していく。

【0109】

前記メモリセルpウェル83上にフィールド酸化膜84を形成後、図39〜図41に示すように、膜厚が5nm〜20nmの熱酸化膜からなる第1のゲート絶縁膜85を成膜する。さらに、この第1のゲート絶縁膜85上に、膜厚が1000nm以上の第1の多結晶シリコン膜あるいはシリサイド膜と多結晶シリコン膜との積層膜あるいは金属膜からなるブースタプレート86を成膜する。

【0110】

続いて、図40に示すように、マスク材とするシリコン窒化膜(SiN)87をリソグラフィ法により形成し、さらにこのシリコン窒化膜87の側面に側壁88を形成する。そして、このシリコン窒化膜87および側壁88をマスクとして、図43に示すように、前記第1のゲート絶縁膜85およびブースタプレート86を制御ゲート線方向に沿った線状にエッチング加工する。

【0111】

次に、図42〜図44に示すように、膜厚が5nm〜10nmの熱酸化膜からなる第2のゲート絶縁膜89を成膜する。この第2のゲート絶縁膜89上に、膜厚が1000nm以上の第2の多結晶シリコン膜あるいはシリサイド膜と多結晶シリコン膜との積層膜あるいは金属膜からなる浮遊ゲート90を成膜する。さらに、図44に示すように、制御ゲート線方向の隣接するフィールド酸化膜84上で浮遊ゲート90間の分離溝91を形成する。

【0112】

その後、前記浮遊ゲート90上に、膜厚が15nm〜40nmの第3のゲート絶縁膜92を形成する。さらに、この第3のゲート絶縁膜92上に、膜厚が100nm〜400nmの第3の多結晶シリコンあるいはシリサイド膜と多結晶シリコン膜との積層体あるいは金属からなる膜93を堆積する。

【0113】

次に、図45〜図47に示すように、上記膜93と浮遊ゲート90を、互いに隣接するブースタプレート86間及びブースタプレート86の上面の一部上で残存するように、セルフアラインでエッチング加工する。これにより、ワード線(制御ゲート)93、選択ゲート線93a及び浮遊ゲート90を形成する。

【0114】

その後、NANDセルのドレイン部とソース部に、イオン注入によりN+ 層184を、セルフアラインで形成する。この際、NANDセルのメモリセルトランジスタ間のドレイン/ソース領域はブースタプレート86で覆われているため、N+ 層が形成されない。

【0115】

次に、図48〜図50に示すように、第4の絶縁膜95を全面に堆積し、この第4の絶縁膜95にコンタクト孔96を開ける。さらに、このコンタクト孔96にタングステンプラグ97を埋め込み、このタングステンプラグ97に接続されるアルミニウム(Al)からなるビット線98を配設する。そして、パシベーション膜99で全面を覆う。以上により、本発明のNAND型EEPROMは完成する。最後に、図46、図48のA,B,Cで示したブロック分離選択ゲート線をメモリアレイ端、若しくは、サブアレイ端で電気的に共通になるように、その他の配線若しくは、同一の配線で結線する。

【0116】

【発明の効果】

以上のようにこの発明によれば、1つのNANDセルブロック内に複数の消去ブロックを設定することが可能であり、消去ブロックサイズを増やすことなく、1つのNANDストリング内のメモリセルの個数を増やすことを可能としたNAND型EEPROMが得られる。

【図面の簡単な説明】

【図1】この発明の第1の実施の形態によるNAND型EEPROMのメモリセルアレイの等価回路。

【図2】第1の実施の形態にかかるメモリセルアレイのレイアウト。

【図3】図2に示す切断線A−A′に沿った断面図。

【図4】図2に示す切断線B−B′に沿った断面図。

【図5】第1の実施の形態のNAND型EEPROMのブロック構成を示す図。

【図6】第1の実施の形態のNAND型EEPROMのセンスアンプ構成を示す図。

【図7】第1の実施の形態のNAND型EEPROMのデータ消去動作のバイアス関係を示す図。

【図8】第1の実施の形態のNAND型EEPROMのデータ書き込み動作のバイアス関係を示す図。

【図9】図8のバイアス関係をメモリセルアレイ上で示す図。

【図10】第1の実施の形態のNAND型EEPROMのデータ読み出し動作のバイアス関係を示す図。

【図11】第2の実施の形態にかかるメモリセルアレイの構成を示す図。

【図12】第2の実施の形態でのデータ消去動作のバイアス関係を示す図。

【図13】第2の実施の形態でのデータ書き込み動作のバイアス関係を示す図。

【図14】第3の実施の形態にかかるメモリセルアレイの構成を示す図。

【図15】第4の実施の形態にかかるメモリセルアレイの構成を示す図。

【図16】第5の実施の形態にかかるワード線駆動回路の配置を示す図。

【図17】第6の実施の形態にかかるワード線駆動回路の配置を示す図。

【図18】従来のNAND型EEPROMのメモリセルアレイ構成を示す図。

【図19】従来のNAND型EEPROMのデータ消去、読み出し及び書き込みのバイアス関係を示す図。

【図20】第4の実施の形態によるメモリセルアレイのレイアウト図。

【図21】第4の実施の形態によるメモリセルアレイの断面図。

【図22】選択トランジス間のメモリセル数とセルサイズとの関係を示すグラフ。

【図23】各メモリセルのサイズを説明する図。

【図24】AND型EEPROMの断面図。

【図25】第7の実施の形態のデータ読出し動作のバイアス関係を示す図。

【図26】第7の実施の形態のデータ消去動作のバイアス関係を示す図。

【図27】第7の実施の形態のデータ書込み動作のバイアス関係を示す図。

【図28】第7の実施の形態にかかるメモリセルアレイの構成を示す図。

【図29】第8の実施の形態のデータ読出し動作のバイアス関係を示す図。

【図30】第8の実施の形態のデータ消去動作のバイアス関係を示す図。

【図31】第8の実施の形態のデータ書込み動作のバイアス関係を示す図。

【図32】第8の実施の形態にかかるメモリセルアレイの構成を示す図。

【図33】第7の実施の形態の変形例にかかるメモリセルアレイの構成を示す図。

【図34】第8の実施の形態の変形例にかかるメモリセルアレイの構成を示す図。

【図35】ブースタプレートを有するNAND型EEPROMの構成を示す斜視図。

【図36】本発明によるNAND型EEPROMの製造工程における平面図。

【図37】図36に示す切断線X−X’に沿った断面図。

【図38】図36に示す切断線Y−Y’に沿った断面図。

【図39】本発明によるNAND型EEPROMの製造工程における平面図。

【図40】図39に示す切断線X−X’に沿った断面図。

【図41】図39に示す切断線Y−Y’に沿った断面図。

【図42】本発明によるNAND型EEPROMの製造工程における平面図。

【図43】図42に示す切断線X−X’に沿った断面図。

【図44】図42に示す切断線Y−Y’に沿った断面図。

【図45】本発明によるNAND型EEPROMの製造工程における平面図。

【図46】図45に示す切断線X−X’に沿った断面図。

【図47】図45に示す切断線Y−Y’に沿った断面図。

【図48】本発明によるNAND型EEPROMの製造工程における平面図。

【図49】図48に示す切断線X−X’に沿った断面図。

【図50】図48に示す切断線Y−Y’に沿った断面図。

【符号の説明】

1 NANDセルブロック

MC メモリセルトランジスタ

SST,GST 選択トランジスタ

ST ブロック分離選択トランジスタ

WL ワード線

BL ビット線

SL ソース線

SSL,GSL,STL 選択ゲート線

MU0〜MU3 メモリセルユニット

51 メモリセルアレイ

52 ロウデコーダ

53 センスアンプ回路

54 カラムデコーダ

55 カラムゲート

56 昇圧回路

57 制御回路

DRV0,DRV1 ワード線駆動回路

Claims (22)

- 第1の信号線と、

第2の信号線と、

これら第1の信号線と第2の信号線の間に電気的書き換え可能なメモリセルを複数個直列接続して構成されたNANDセルと、

このNANDセルを複数ブロックに分割するためにNANDセル内の所定の隣接メモリセルの間に電流経路が直列に接続されたブロック分離選択トランジスタと、

を有することを特徴とする不揮発性半導体記憶装置。 - ワード線により選択される電気的書き換え可能なメモリセルが第1の信号線と第2の信号線の間にそれぞれ選択トランジスタを介して複数個直列接続されてNANDセルを構成して、複数のNANDセルが配列されたメモリセルアレイと、

アドレスにより前記メモリセルアレイのメモリセル選択を行うアドレスデコーダと、

前記メモリセルアレイからの読み出しデータをセンスし、前記メモリセルアレイへの書き込みデータをラッチする機能を有するセンスアンプ回路と、

前記メモリセルアレイへのデータ書き込み、消去及び読み出しの制御を行う制御回路とを備え、

前記メモリセルアレイは、各NANDセル内の所定の隣接メモリセルの間に電流経路が直列に接続されたブロック分離選択トランジスタにより複数のメモリセルユニットに分割されている

ことを特徴とする不揮発性半導体記憶装置。 - 前記メモリセルアレイのデータ書き換え時、前記複数のメモリセルユニットの一つを消去単位として選択してデータ消去がなされ、1本のワード線に沿った複数のメモリセルの所定範囲を1ページとしてデータ書き込みがなされる

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。 - 前記データ消去は、

選択されたメモリセルユニットの全ワード線に接地電位を与え、

非選択のメモリセルユニットの全ワード線、前記第1の信号線側及び第2の信号線側の選択トランジスタ及び前記ブロック分離選択トランジスタのゲートにそれぞれつながる選択ゲート線をフローティングとし、且つ

前記メモリセルアレイが形成された基板領域に消去電圧を与える、

ことにより行われる請求項3記載の不揮発性半導体記憶装置。 - 前記データ書き込みは、

書き込むべきデータ“0”,“1”に応じて第1の信号線に接地電位、電源電位を与え、

選択されたメモリセルユニット内の非選択ワード線にメモリセルを導通させるパス電圧を与え、

非選択のメモリセルユニットの全ワード線、及び非選択のメモリセルユニットと前記選択されたメモリセルユニットの間の前記ブロック分離選択トランジスタのゲートにつながる選択ゲート線にメモリセルを導通させる前記パス電圧より低い読み出し電圧を与え、

前記選択されたメモリセルユニットの選択ワード線に前記パス電圧より高い書き込み電圧を与える、

ことにより行われる請求項3記載の不揮発性半導体記憶装置。 - 前記メモリセルアレイは、各NANDセル内の所定の隣接メモリセルの間に介在させた2n −1(n:正の整数)個のブロック分離選択トランジスタにより、2n 個のメモリセルユニットに分割されている

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。 - 各メモリセルユニットが同数のメモリセルを含む

ことを特徴とする請求項6記載の不揮発性半導体記憶装置。 - 各メモリセルユニットが異なる数のメモリセルを含む

ことを特徴とする請求項6記載の不揮発性半導体記憶装置。 - 前記アドレスデコーダのなかのワード線駆動回路は、前記メモリセルアレイのワード線方向の両端部に、1乃至2メモリセルユニット毎に振り分けて配置されている

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。 - それぞれ異なるワード線により選択される電気的書き換え可能な複数のメモリセルがビット線に直列接続されてNANDセルを構成し、ワード線方向に並ぶ複数のNANDセルがNANDセルブロックを構成し、且つ各NANDセルの所定の隣接メモリセルの間に介在させたブロック分離選択トランジスタにより前記NANDセルブロックが複数のメモリセルユニットに分割されたメモリセルアレイと、

アドレスにより前記メモリセルアレイのメモリセル選択を行うアドレスデコーダと、

前記メモリセルアレイからの読み出しデータをセンスし、前記メモリセルアレイへの書き込みデータをラッチする機能を有するセンスアンプ回路と、

前記複数のメモリセルユニットの一つを消去単位として選択してそのメモリセルユニット内のデータを一括消去し、1本のワード線に沿った複数のメモリセルの所定範囲を1ページとしてデータ書き込みを行うデータ書き換え手段と、

を備えたことを特徴とする不揮発性半導体記憶装置。 - 前記複数ブロック間の少なくとも2つ以上の前記ブロック分離選択トランジスタのゲートが共通接続されていることを特徴とする請求項1記載の不揮発性半導体記憶装置。

- 第1および第2の信号線と、

第1および第2の選択トランジスタと、

各々が、電気的に書き換え可能なメモリセルを複数個直列接続して構成された第1乃至第n(n≦3)のNANDセルブロックと、

第1乃至第(n−1)のブロック分離選択トランジスタと、

を備え、

前記第1の信号線に前記第1の選択トランジスタが接続され、

前記第1の選択トランジスタに前記第1のNANDセルブロックが接続され、

第i(1≦i≦n−1)のNANDセルブロックに第iのブロック分離選択トランジスタが接続され、

第i(1≦i≦n−1)のブロック分離選択トランジスタに第(i+1)のNANDセルブロックが接続され、

第nのNANDセルブロックに第2の選択トランジスタが接続され、

第2の選択トランジスタに第2の信号線が接続され、

前記第1乃至第nのブロック分離選択トランジスタのうち、少なくとも2つのブロック分離選択トランジスタのゲートが共通接続されていることを特徴とする不揮発性半導体記憶装置。 - 前記第1および第2の選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは金属電極から構成され、

前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートは多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは金属電極から構成されていることを特徴とする請求項12記載の不揮発性半導体記憶装置。 - 第1および第2の信号線と、

第1および第2の選択トランジスタと、

各々が電気的に書き換え可能な第1乃至第nのメモリセルと、

第1乃至第(n−1)のブロック分離選択トランジスタと、

を備え、

前記第1の信号線に前記第1の選択トランジスタが接続され、

前記第1の選択トランジスタに前記第1のメモリセルが接続され、第i(1≦i≦n−1)のメモリセルに第iのブロック分離選択トランジスタが接続され、

第i(1≦i≦n−1)のブロック分離選択トランジスタに第(i+1)のメモリセルが接続され、

第nのメモリセルに第2の選択トランジスタが接続され、

第2の選択トランジスタに第2の信号線が接続され、

前記第1乃至第nのブロック分離選択トランジスタのうち、少なくとも2つのブロック分離選択トランジスタのゲートが共通接続されていることを特徴とする不揮発性半導体記憶装置。 - 前記第1および第2の選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは、金属電極から構成され、

前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートは、多結晶シリコン、多結晶シリコンとシリサイドとの積層体、若しくは、金属電極から構成されていることを特徴とする請求項14記載の不揮発性半導体記憶装置。 - 前記第1乃至第(n−1)のブロック分離選択トランジスタのゲート電圧はそれぞれが常に等しい電圧に制御されることを特徴とする請求項12または13記載の不揮発性半導体記憶装置。

- 前記第1乃至第(n−1)のブロック分離選択トランジスタのゲート電圧はそれぞれが常に等しい電圧に制御されることを特徴とする請求項14または15記載の不揮発性半導体記憶装置。

- データ書き込み時に、

前記第1の選択トランジスタおよび前記第1乃至第(n−1)のブロック分離選択トランジスタのゲートには、電源電圧Vcc若しくはそれ以上の読み出し電圧Vreadが印加され、

前記第2の選択トランジスタのゲートには、接地電圧Vssが印加されることを特徴とする請求項16または17記載の不揮発性半導体記憶装置。 - 前記第1の信号線はビット線で、

前記第2の信号線はセルソース線であることを特徴とする請求項11乃至18のいずれかに記載の不揮発性半導体記憶装置。 - 前記メモリセルは浮遊ゲートと、

前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートと、

を有する二層のスタック構造からなる電気的書き換え可能なメモリセルであることを特徴とする請求項11乃至19のいずれかに記載の不揮発性半導体記憶装置。 - 第1の信号線と、

第2の信号線と、

これら第1の信号線と第2の信号線の間に電気的書き換え可能なメモリセルを複数個直列接続して構成されたNANDセルと、

このNANDセルを複数ブロックに分割するためにNANDセル内の所定の隣接メモリセルの間に電流経路が直列に接続されたブロック分離選択トランジスタと、

を有し、

前記複数のブロックの少なくとも1つが前記ブロック分離選択トランジスタと前記第1の信号線との間に設けられ、少なくとも他の1つが前記ブロック分離選択トランジスタと前記第2の信号線との間に設けられていることを特徴とする不揮発性半導体記憶装置。 - ワード線により選択される電気的書き換え可能なメモリセルが第1の信号線と第2の信号線の間にそれぞれ選択トランジスタを介して複数個直列接続されてNANDセルを構成して、複数のNANDセルが配列されたメモリセルアレイと、

アドレスにより前記メモリセルアレイのメモリセル選択を行うアドレスデコーダと、

前記メモリセルアレイからの読み出しデータをセンスし、前記メモリセルアレイへの書き込みデータをラッチする機能を有するセンスアンプ回路と、

前記メモリセルアレイへのデータ書き込み、消去及び読み出しの制御を行う制御回路とを備え、

前記メモリセルアレイは、各NANDセル内の所定の隣接メモリセルの間に電流経路が直列に接続されたブロック分離選択トランジスタにより複数のメモリセルユニットに分割され、

前記複数のメモリセルユニットの少なくとも1つが前記ブロック分離選択トランジスタと前記第1の信号線との間に設けられ、少なくとも他の1つが前記ブロック分離選択トランジスタと前記第2の信号線との間に設けられていることを特徴とする不揮発性半導体記憶装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP26617699A JP3866460B2 (ja) | 1998-11-26 | 1999-09-20 | 不揮発性半導体記憶装置 |

| US09/449,932 US6295227B1 (en) | 1998-11-26 | 1999-11-24 | Non-volatile semiconductor memory device |

| KR10-1999-0052598A KR100488380B1 (ko) | 1998-11-26 | 1999-11-25 | 불휘발성 반도체 기억 장치 |

| TW088120608A TW471155B (en) | 1998-11-26 | 1999-11-25 | Non-volatile semiconductor memory device |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP10-336162 | 1998-11-26 | ||

| JP33616298 | 1998-11-26 | ||

| JP26617699A JP3866460B2 (ja) | 1998-11-26 | 1999-09-20 | 不揮発性半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000222895A JP2000222895A (ja) | 2000-08-11 |

| JP2000222895A5 JP2000222895A5 (ja) | 2004-09-02 |

| JP3866460B2 true JP3866460B2 (ja) | 2007-01-10 |

Family

ID=26547337

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP26617699A Expired - Lifetime JP3866460B2 (ja) | 1998-11-26 | 1999-09-20 | 不揮発性半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6295227B1 (ja) |

| JP (1) | JP3866460B2 (ja) |

| KR (1) | KR100488380B1 (ja) |

| TW (1) | TW471155B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020112296A1 (en) * | 2018-11-30 | 2020-06-04 | Micron Technology, Inc. | Vertical decoder |

Families Citing this family (101)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001028427A (ja) * | 1999-07-14 | 2001-01-30 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JP3957985B2 (ja) * | 2001-03-06 | 2007-08-15 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR100387529B1 (ko) * | 2001-06-11 | 2003-06-18 | 삼성전자주식회사 | 랜덤 억세스 가능한 메모리 셀 어레이를 갖는 불휘발성반도체 메모리 장치 |

| JP2003030994A (ja) * | 2001-07-18 | 2003-01-31 | Fujitsu Ltd | 半導体記憶装置および半導体記憶装置の駆動方法 |

| US6762092B2 (en) * | 2001-08-08 | 2004-07-13 | Sandisk Corporation | Scalable self-aligned dual floating gate memory cell array and methods of forming the array |

| US6504763B1 (en) * | 2002-02-21 | 2003-01-07 | Ememory Technology Inc. | Nonvolatile semiconductor memory capable of random programming |

| US6587383B1 (en) * | 2002-03-19 | 2003-07-01 | Micron Technology, Inc. | Erase block architecture for non-volatile memory |

| US6760245B2 (en) | 2002-05-01 | 2004-07-06 | Hewlett-Packard Development Company, L.P. | Molecular wire crossbar flash memory |

| EP1514309B1 (en) * | 2002-06-19 | 2013-11-27 | SanDisk Technologies Inc. | Deep wordline trench to shield cross coupling between adjacent cells of nand memory |

| US6894930B2 (en) | 2002-06-19 | 2005-05-17 | Sandisk Corporation | Deep wordline trench to shield cross coupling between adjacent cells for scaled NAND |

| US6908817B2 (en) * | 2002-10-09 | 2005-06-21 | Sandisk Corporation | Flash memory array with increased coupling between floating and control gates |

| US7233522B2 (en) * | 2002-12-31 | 2007-06-19 | Sandisk 3D Llc | NAND memory array incorporating capacitance boosting of channel regions in unselected memory cells and method for operation of same |

| US7505321B2 (en) * | 2002-12-31 | 2009-03-17 | Sandisk 3D Llc | Programmable memory array structure incorporating series-connected transistor strings and methods for fabrication and operation of same |

| US7105406B2 (en) * | 2003-06-20 | 2006-09-12 | Sandisk Corporation | Self aligned non-volatile memory cell and process for fabrication |

| JP4537680B2 (ja) | 2003-08-04 | 2010-09-01 | 株式会社東芝 | 不揮発性半導体記憶装置及びその動作方法、製造方法、半導体集積回路及びシステム |

| JP2005100548A (ja) * | 2003-09-26 | 2005-04-14 | Toshiba Corp | 不揮発性半導体記憶装置及び電子カード |

| JP2005116119A (ja) * | 2003-10-10 | 2005-04-28 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US20050128807A1 (en) * | 2003-12-05 | 2005-06-16 | En-Hsing Chen | Nand memory array incorporating multiple series selection devices and method for operation of same |

| US7221588B2 (en) * | 2003-12-05 | 2007-05-22 | Sandisk 3D Llc | Memory array incorporating memory cells arranged in NAND strings |

| US7023739B2 (en) * | 2003-12-05 | 2006-04-04 | Matrix Semiconductor, Inc. | NAND memory array incorporating multiple write pulse programming of individual memory cells and method for operation of same |

| US7161833B2 (en) * | 2004-02-06 | 2007-01-09 | Sandisk Corporation | Self-boosting system for flash memory cells |

| US7466590B2 (en) * | 2004-02-06 | 2008-12-16 | Sandisk Corporation | Self-boosting method for flash memory cells |

| US7183153B2 (en) * | 2004-03-12 | 2007-02-27 | Sandisk Corporation | Method of manufacturing self aligned non-volatile memory cells |

| JP4817617B2 (ja) * | 2004-06-14 | 2011-11-16 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7482223B2 (en) * | 2004-12-22 | 2009-01-27 | Sandisk Corporation | Multi-thickness dielectric for semiconductor memory |

| KR100671625B1 (ko) | 2004-12-28 | 2007-01-19 | 주식회사 하이닉스반도체 | 블록 사이즈를 변경할 수 있는 난드 플래시 메모리 장치 |

| US7177191B2 (en) * | 2004-12-30 | 2007-02-13 | Sandisk 3D Llc | Integrated circuit including memory array incorporating multiple types of NAND string structures |

| KR100672121B1 (ko) | 2005-01-12 | 2007-01-19 | 주식회사 하이닉스반도체 | 불휘발성 메모리 장치 및 그것의 프로그램/판독 방법 |

| US8824205B2 (en) | 2005-04-11 | 2014-09-02 | Micron Technology, Inc. | Non-volatile electronic memory device with NAND structure being monolithically integrated on semiconductor |

| JP4683995B2 (ja) * | 2005-04-28 | 2011-05-18 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| KR100602320B1 (ko) | 2005-05-03 | 2006-07-18 | 주식회사 하이닉스반도체 | 프로그램 속도가 균일한 비휘발성 메모리 소자 |

| US20060256623A1 (en) * | 2005-05-12 | 2006-11-16 | Micron Technology, Inc. | Partial string erase scheme in a flash memory device |

| US7247907B2 (en) * | 2005-05-20 | 2007-07-24 | Silicon Storage Technology, Inc. | Bidirectional split gate NAND flash memory structure and array, method of programming, erasing and reading thereof, and method of manufacturing |

| JP4545056B2 (ja) * | 2005-06-30 | 2010-09-15 | シャープ株式会社 | 不揮発性半導体記憶装置 |

| KR100630537B1 (ko) * | 2005-08-09 | 2006-10-02 | 주식회사 하이닉스반도체 | 듀얼 페이지 프로그램 기능을 가지는 플래시 메모리 장치의페이지 버퍼 회로 및 그 프로그램 동작 방법 |

| KR100687424B1 (ko) | 2005-08-29 | 2007-02-26 | 주식회사 하이닉스반도체 | 비휘발성 메모리 장치 |

| US7751242B2 (en) * | 2005-08-30 | 2010-07-06 | Micron Technology, Inc. | NAND memory device and programming methods |

| US7541240B2 (en) * | 2005-10-18 | 2009-06-02 | Sandisk Corporation | Integration process flow for flash devices with low gap fill aspect ratio |

| JP5250182B2 (ja) * | 2005-10-28 | 2013-07-31 | シャープ株式会社 | 不揮発性メモリ装置およびその駆動方法 |

| US7489546B2 (en) * | 2005-12-20 | 2009-02-10 | Micron Technology, Inc. | NAND architecture memory devices and operation |

| US7362615B2 (en) * | 2005-12-27 | 2008-04-22 | Sandisk Corporation | Methods for active boosting to minimize capacitive coupling effect between adjacent gates of flash memory devices |

| US7436703B2 (en) * | 2005-12-27 | 2008-10-14 | Sandisk Corporation | Active boosting to minimize capacitive coupling effect between adjacent gates of flash memory devices |

| US7428165B2 (en) * | 2006-03-30 | 2008-09-23 | Sandisk Corporation | Self-boosting method with suppression of high lateral electric fields |

| US7511995B2 (en) * | 2006-03-30 | 2009-03-31 | Sandisk Corporation | Self-boosting system with suppression of high lateral electric fields |

| US20070247910A1 (en) * | 2006-04-20 | 2007-10-25 | Micron Technology, Inc. | NAND erase block size trimming apparatus and method |

| US7718491B2 (en) * | 2006-06-16 | 2010-05-18 | Macronix International Co., Ltd. | Method for making a NAND Memory device with inversion bit lines |

| KR100813618B1 (ko) * | 2006-07-25 | 2008-03-17 | 삼성전자주식회사 | 3차원 어레이 구조를 갖는 반도체 메모리 장치 |

| KR100910042B1 (ko) * | 2006-09-20 | 2009-07-30 | 삼성전자주식회사 | 이중 패터닝 기술을 이용한 플래시 메모리 소자 및 그 제조방법 |

| JP4908149B2 (ja) * | 2006-10-18 | 2012-04-04 | 株式会社東芝 | Nand型フラッシュメモリ |

| KR100810414B1 (ko) * | 2006-10-31 | 2008-03-04 | 주식회사 하이닉스반도체 | 플래시 메모리 소자 및 그 제조 방법 |

| US7639540B2 (en) | 2007-02-16 | 2009-12-29 | Mosaid Technologies Incorporated | Non-volatile semiconductor memory having multiple external power supplies |

| US7745285B2 (en) | 2007-03-30 | 2010-06-29 | Sandisk Corporation | Methods of forming and operating NAND memory with side-tunneling |

| US7460404B1 (en) * | 2007-05-07 | 2008-12-02 | Sandisk Corporation | Boosting for non-volatile storage using channel isolation switching |

| US7463522B2 (en) * | 2007-05-07 | 2008-12-09 | Sandisk Corporation | Non-volatile storage with boosting using channel isolation switching |

| US7626869B2 (en) * | 2007-05-07 | 2009-12-01 | Spansion Llc | Multi-phase wordline erasing for flash memory |

| US7577026B2 (en) * | 2007-05-07 | 2009-08-18 | Sandisk Corporation | Source and drain side early boosting using local self boosting for non-volatile storage |

| KR20090001368A (ko) * | 2007-06-29 | 2009-01-08 | 삼성전자주식회사 | 불휘발성 반도체 장치 |

| KR20090010481A (ko) * | 2007-07-23 | 2009-01-30 | 삼성전자주식회사 | 선택 트랜지스터를 프로그램하는 낸드 플래시 메모리 장치및 그것의 프로그램 방법 |

| JP4510060B2 (ja) * | 2007-09-14 | 2010-07-21 | 株式会社東芝 | 不揮発性半導体記憶装置の読み出し/書き込み制御方法 |

| JP5376789B2 (ja) | 2007-10-03 | 2013-12-25 | 株式会社東芝 | 不揮発性半導体記憶装置及び不揮発性半導体記憶装置の制御方法 |

| JP5283960B2 (ja) * | 2008-04-23 | 2013-09-04 | 株式会社東芝 | 三次元積層不揮発性半導体メモリ |

| JP2010118580A (ja) * | 2008-11-14 | 2010-05-27 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5193830B2 (ja) * | 2008-12-03 | 2013-05-08 | 株式会社東芝 | 不揮発性半導体メモリ |

| KR101071858B1 (ko) * | 2009-01-22 | 2011-10-11 | 주식회사 하이닉스반도체 | 플래시 메모리 소자 |

| JP5052575B2 (ja) | 2009-09-01 | 2012-10-17 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR101691092B1 (ko) | 2010-08-26 | 2016-12-30 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US9378831B2 (en) | 2010-02-09 | 2016-06-28 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| KR101691088B1 (ko) | 2010-02-17 | 2016-12-29 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| KR101658479B1 (ko) | 2010-02-09 | 2016-09-21 | 삼성전자주식회사 | 불휘발성 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US9324440B2 (en) | 2010-02-09 | 2016-04-26 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, operating methods thereof and memory systems including the same |

| KR101636015B1 (ko) | 2010-02-11 | 2016-07-05 | 삼성전자주식회사 | 불휘발성 데이터 저장 장치, 그것의 프로그램 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US8923060B2 (en) | 2010-02-17 | 2014-12-30 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices and operating methods thereof |

| JP5788183B2 (ja) * | 2010-02-17 | 2015-09-30 | 三星電子株式会社Samsung Electronics Co.,Ltd. | 不揮発性メモリ装置、それの動作方法、そしてそれを含むメモリシステム |

| US8908431B2 (en) | 2010-02-17 | 2014-12-09 | Samsung Electronics Co., Ltd. | Control method of nonvolatile memory device |

| JP2011170956A (ja) | 2010-02-18 | 2011-09-01 | Samsung Electronics Co Ltd | 不揮発性メモリ装置およびそのプログラム方法と、それを含むメモリシステム |

| US8792282B2 (en) | 2010-03-04 | 2014-07-29 | Samsung Electronics Co., Ltd. | Nonvolatile memory devices, memory systems and computing systems |

| US8553466B2 (en) | 2010-03-04 | 2013-10-08 | Samsung Electronics Co., Ltd. | Non-volatile memory device, erasing method thereof, and memory system including the same |

| KR101085724B1 (ko) * | 2010-05-10 | 2011-11-21 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 및 그 동작 방법 |

| US10671529B2 (en) | 2010-08-20 | 2020-06-02 | Samsung Electronics Co., Ltd. | Address scheduling methods for non-volatile memory devices with three-dimensional memory cell arrays |

| JP5646369B2 (ja) | 2011-03-01 | 2014-12-24 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2012195478A (ja) * | 2011-03-17 | 2012-10-11 | Toshiba Corp | 半導体記憶装置 |

| KR101811035B1 (ko) | 2011-09-30 | 2017-12-21 | 삼성전자주식회사 | 불휘발성 메모리 및 그것의 소거 방법 |

| JP5619812B2 (ja) | 2012-04-24 | 2014-11-05 | ウィンボンドエレクトロニクス コーポレーション | 半導体記憶装置 |

| KR20130129638A (ko) * | 2012-05-21 | 2013-11-29 | 에스케이하이닉스 주식회사 | 불휘발성 반도체 메모리 장치 및 그의 리드 방법 |

| JP2015050332A (ja) * | 2013-09-02 | 2015-03-16 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR102242022B1 (ko) | 2013-09-16 | 2021-04-21 | 삼성전자주식회사 | 불휘발성 메모리 및 그것의 프로그램 방법 |

| KR102293136B1 (ko) * | 2014-10-22 | 2021-08-26 | 삼성전자주식회사 | 비휘발성 메모리 장치, 그것을 포함하는 저장 장치 및 그것의 동작 방법 |

| KR102222594B1 (ko) * | 2014-11-13 | 2021-03-08 | 삼성전자주식회사 | 비휘발성 메모리 장치, 그것의 소거 방법, 및 그것을 포함하는 메모리 시스템 |

| US9786375B2 (en) * | 2015-09-11 | 2017-10-10 | Intel Corporation | Multiple blocks per string in 3D NAND memory |

| WO2017083584A1 (en) | 2015-11-11 | 2017-05-18 | Fu-Chang Hsu | 3d nand array with divided string architecture |

| US9865656B2 (en) * | 2016-02-12 | 2018-01-09 | Toshiba Memory Corporation | Semiconductor memory device |

| KR102468995B1 (ko) * | 2016-03-29 | 2022-11-22 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 동작 방법 |

| US9953717B2 (en) * | 2016-03-31 | 2018-04-24 | Sandisk Technologies Llc | NAND structure with tier select gate transistors |

| TWI648825B (zh) * | 2017-03-16 | 2019-01-21 | 日商東芝記憶體股份有限公司 | 半導體記憶體 |

| CN109754837A (zh) * | 2017-11-07 | 2019-05-14 | 三星电子株式会社 | 具有三维存储单元阵列的非易失存储器件的地址调度方法 |

| US10325665B2 (en) | 2017-12-08 | 2019-06-18 | Intel Corporation | Block by deck operations for NAND memory |

| KR102434922B1 (ko) * | 2018-03-05 | 2022-08-23 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 동작 방법 |

| US10878907B1 (en) * | 2019-06-05 | 2020-12-29 | Sandisk Technologies Llc | Sub-block size reduction for 3D non-volatile memory |

| JP2021093230A (ja) * | 2019-12-10 | 2021-06-17 | キオクシア株式会社 | 半導体記憶装置 |

| US11126548B1 (en) * | 2020-03-19 | 2021-09-21 | Micron Technology, Inc. | Accelerated in-memory cache with memory array sections having different configurations |

| KR20210119084A (ko) * | 2020-03-24 | 2021-10-05 | 에스케이하이닉스 주식회사 | 반도체 장치 및 반도체 장치의 동작 방법 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR970005644B1 (ko) * | 1994-09-03 | 1997-04-18 | 삼성전자 주식회사 | 불휘발성 반도체 메모리장치의 멀티블럭 소거 및 검증장치 및 그 방법 |

| JP3489958B2 (ja) * | 1997-03-19 | 2004-01-26 | 富士通株式会社 | 不揮発性半導体記憶装置 |

-

1999

- 1999-09-20 JP JP26617699A patent/JP3866460B2/ja not_active Expired - Lifetime

- 1999-11-24 US US09/449,932 patent/US6295227B1/en not_active Expired - Lifetime

- 1999-11-25 KR KR10-1999-0052598A patent/KR100488380B1/ko active IP Right Grant

- 1999-11-25 TW TW088120608A patent/TW471155B/zh not_active IP Right Cessation

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020112296A1 (en) * | 2018-11-30 | 2020-06-04 | Micron Technology, Inc. | Vertical decoder |

| US10950284B2 (en) | 2018-11-30 | 2021-03-16 | Micron Technology, Inc. | Vertical decoder |

| US11468930B2 (en) | 2018-11-30 | 2022-10-11 | Micron Technology, Inc. | Vertical decoder |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20000035673A (ko) | 2000-06-26 |

| KR100488380B1 (ko) | 2005-05-11 |

| US6295227B1 (en) | 2001-09-25 |

| JP2000222895A (ja) | 2000-08-11 |

| TW471155B (en) | 2002-01-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3866460B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3679970B2 (ja) | 不揮発性半導体記憶装置及びその製造方法 | |

| JP3653186B2 (ja) | 不揮発性メモリ装置のプログラミング方法 | |

| JP4537680B2 (ja) | 不揮発性半導体記憶装置及びその動作方法、製造方法、半導体集積回路及びシステム | |

| US8513726B2 (en) | EEPROM with increased reading speed | |

| US7672164B2 (en) | Semiconductor integrated circuit device with a stacked gate including a floating gate and a control gate | |

| US6330189B1 (en) | Nonvolatile semiconductor memory device | |

| JP3540579B2 (ja) | 半導体記憶装置及びその製造方法 | |

| US7263000B2 (en) | NAND type memory with dummy cells adjacent to select transistors being biased at different voltage during data erase | |

| US6049494A (en) | Semiconductor memory device | |

| US7164608B2 (en) | NVRAM memory cell architecture that integrates conventional SRAM and flash cells | |

| US7184309B2 (en) | Non-volatile semiconductor memory device | |

| KR100190089B1 (ko) | 플래쉬 메모리장치 및 그 구동방법 | |

| JP3730508B2 (ja) | 半導体記憶装置およびその動作方法 | |

| US6798683B2 (en) | Pattern layout of transfer transistors employed in row decoder | |

| JP7297977B1 (ja) | フラッシュメモリ | |

| KR19980016850A (ko) | 플레쉬 메모리 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060526 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060602 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060721 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060929 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061005 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 3866460 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101013 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111013 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111013 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121013 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131013 Year of fee payment: 7 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |