JP3623804B2 - イオンが注入された構造体および形成方法 - Google Patents

イオンが注入された構造体および形成方法 Download PDFInfo

- Publication number

- JP3623804B2 JP3623804B2 JP53986698A JP53986698A JP3623804B2 JP 3623804 B2 JP3623804 B2 JP 3623804B2 JP 53986698 A JP53986698 A JP 53986698A JP 53986698 A JP53986698 A JP 53986698A JP 3623804 B2 JP3623804 B2 JP 3623804B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon

- semiconductor substrate

- ions

- implanted

- containing material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 1076

- 230000015572 biosynthetic process Effects 0.000 title description 64

- 150000002500 ions Chemical class 0.000 claims description 616

- 229910052710 silicon Inorganic materials 0.000 claims description 583

- 239000010703 silicon Substances 0.000 claims description 583

- 239000000463 material Substances 0.000 claims description 578

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 577

- 230000008569 process Effects 0.000 claims description 454

- 238000005468 ion implantation Methods 0.000 claims description 411

- 239000000758 substrate Substances 0.000 claims description 391

- 239000004065 semiconductor Substances 0.000 claims description 377

- 238000005530 etching Methods 0.000 claims description 291

- 239000003990 capacitor Substances 0.000 claims description 167

- 238000003860 storage Methods 0.000 claims description 120

- 125000006850 spacer group Chemical group 0.000 claims description 78

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 claims description 55

- 238000000151 deposition Methods 0.000 claims description 38

- 239000007943 implant Substances 0.000 claims description 37

- 239000002019 doping agent Substances 0.000 claims description 35

- 239000011810 insulating material Substances 0.000 claims description 25

- 239000004020 conductor Substances 0.000 claims description 21

- 238000001039 wet etching Methods 0.000 claims description 16

- 230000008859 change Effects 0.000 claims description 14

- 238000002955 isolation Methods 0.000 claims description 13

- 238000011049 filling Methods 0.000 claims description 11

- 230000000873 masking effect Effects 0.000 claims description 9

- 239000012535 impurity Substances 0.000 claims description 7

- 238000009413 insulation Methods 0.000 claims description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 4

- 239000007788 liquid Substances 0.000 claims 3

- 239000011368 organic material Substances 0.000 claims 1

- 238000009271 trench method Methods 0.000 claims 1

- 239000002023 wood Substances 0.000 claims 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 725

- 229920005591 polysilicon Polymers 0.000 description 725

- 235000012431 wafers Nutrition 0.000 description 163

- 229920002120 photoresistant polymer Polymers 0.000 description 140

- 229910052581 Si3N4 Inorganic materials 0.000 description 74

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 69

- 238000004519 manufacturing process Methods 0.000 description 48

- 238000002513 implantation Methods 0.000 description 40

- 238000001312 dry etching Methods 0.000 description 30

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 28

- 229910052782 aluminium Inorganic materials 0.000 description 28

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 28

- 230000008021 deposition Effects 0.000 description 24

- 238000000206 photolithography Methods 0.000 description 24

- 239000005380 borophosphosilicate glass Substances 0.000 description 21

- 238000012545 processing Methods 0.000 description 20

- 238000010438 heat treatment Methods 0.000 description 17

- 230000002829 reductive effect Effects 0.000 description 17

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 15

- -1 silicon ion Chemical class 0.000 description 13

- 239000011248 coating agent Substances 0.000 description 12

- 238000000576 coating method Methods 0.000 description 12

- 238000000059 patterning Methods 0.000 description 12

- 239000000377 silicon dioxide Substances 0.000 description 12

- 235000012239 silicon dioxide Nutrition 0.000 description 12

- 239000002585 base Substances 0.000 description 11

- 230000008901 benefit Effects 0.000 description 11

- 239000010936 titanium Substances 0.000 description 11

- 229910052719 titanium Inorganic materials 0.000 description 11

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 239000000243 solution Substances 0.000 description 9

- 229910021341 titanium silicide Inorganic materials 0.000 description 9

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 239000011574 phosphorus Substances 0.000 description 8

- 239000003870 refractory metal Substances 0.000 description 8

- 150000004770 chalcogenides Chemical class 0.000 description 7

- 238000007796 conventional method Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 229910021332 silicide Inorganic materials 0.000 description 7

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 7

- 230000004888 barrier function Effects 0.000 description 6

- 239000007789 gas Substances 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N argon Substances [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 230000035515 penetration Effects 0.000 description 5

- 235000011118 potassium hydroxide Nutrition 0.000 description 5

- 229910052786 argon Inorganic materials 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 125000001475 halogen functional group Chemical group 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 238000011946 reduction process Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000011065 in-situ storage Methods 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 2

- GNKTZDSRQHMHLZ-UHFFFAOYSA-N [Si].[Si].[Si].[Ti].[Ti].[Ti].[Ti].[Ti] Chemical compound [Si].[Si].[Si].[Ti].[Ti].[Ti].[Ti].[Ti] GNKTZDSRQHMHLZ-UHFFFAOYSA-N 0.000 description 2

- 230000001154 acute effect Effects 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000012864 cross contamination Methods 0.000 description 2

- 239000008367 deionised water Substances 0.000 description 2

- 229910021641 deionized water Inorganic materials 0.000 description 2

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 230000013011 mating Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910017604 nitric acid Inorganic materials 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 230000007261 regionalization Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910008484 TiSi Inorganic materials 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000002378 acidificating effect Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- HAYXDMNJJFVXCI-UHFFFAOYSA-N arsenic(5+) Chemical group [As+5] HAYXDMNJJFVXCI-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 238000007630 basic procedure Methods 0.000 description 1

- 239000003637 basic solution Substances 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 229910001423 beryllium ion Inorganic materials 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 150000008282 halocarbons Chemical class 0.000 description 1

- 150000002366 halogen compounds Chemical class 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000003112 inhibitor Substances 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 229910052914 metal silicate Inorganic materials 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 238000005979 thermal decomposition reaction Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28123—Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects

- H01L21/2815—Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects part or whole of the electrode is a sidewall spacer or made by a similar technique, e.g. transformation under mask, plating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28525—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising semiconducting material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

- H01L21/30608—Anisotropic liquid etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32134—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by liquid etching only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H01L21/76232—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials of trenches having a shape other than rectangular or V-shape, e.g. rounded corners, oblique or rounded trench walls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H01L21/76237—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials introducing impurities in trench side or bottom walls, e.g. for forming channel stoppers or alter isolation behavior

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/60—Electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66492—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a pocket or a lightly doped drain selectively formed at the side of the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/318—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor the storage electrode having multiple segments

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Ceramic Engineering (AREA)

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

- Weting (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

1.発明の分野

本発明は、半導体基板上に、ある量のシリコンを含む材料をパターン形成する方法に関し、特にイオン注入、およびイオンが注入されたシリコンを含む材料、またはイオンが注入されていないシリコンを含む材料に対して選択的なエッチング・プロセスを使用することにより、半導体基板上に、ある量のシリコンを含む材料から成形済みの構造体を形成する方法に関する。本発明は、効率的に、成形済みの構造体の結果として得られるプロファイルを高度に制御しながら、ポリシリコン・プラグ、相互接続ライン、トランジスタ・ゲート、トレンチ、およびコンデンサの電荷貯蔵ノードのような、シリコンを含む材料の成形済みの構造体を形成する際に役に立つ。

2.関連技術

本明細書の場合、「半導体基板」という用語は、半導体ウエハ単体、またはその上に他の材料を含む組立体、および半導体材料層単体または他の材料を含む組立体のようなバルク半導体材料を含むが、それに限定されない半導体材料を含むすべての構造物を意味する。「基板」という用語は、上記半導体基板を含むが、それに限定されないすべての支持構造体を意味する。

電子チップ上の集積回路は、コンピュータの論理およびメモリ、および他のインテリジェント電子装置を供給する。これら集積回路は、コンピュータおよび他のインテリジェント電子装置の役に立つ、高度な機能レベルに進歩してきている。集積回路の膨大な機能は、また安い価格で供給され、それにより、消費者は、手ごろな値段でコンピュータおよびインテリジェント電子装置を入手することができる。集積回路は、現在、半導体装置、絶縁フィルム、およびパターン形成されたフィルムが、半導体基板上に予め定めた配置で順次設置される複雑なプロセスで製造される。半導体ウエハ上に形成される従来の半導体装置は、コンデンサ、抵抗、トランジスタ、ダイオード等を含む。進歩した集積回路の製造の場合には、非常に多くのこれらの半導体装置が、一つの半導体ウエハ上に形成される。

市場は、コンピュータおよびエレクトロニクス業界に対して、絶えず集積回路の速度および機能を向上するように、またそのコストを下げるように要求している。この要求を満たす一つの方法は、半導体ウエハ上の所与の表面積上における、半導体装置の形成密度を増大する方法である。そうするためには、小型化と呼ばれるプロセスにより、半導体装置の大きさを小さくしなければならない。集積回路の小型化の際に難しいのは、集積回路の製造プロセスのコストを大きく上げないで、半導体装置の大きさを小さくすることである。

従って、集積回路製造の際に改善しなければならない一つの問題は、集積回路製造プロセスが複雑であることである。集積回路がますます複雑になるにつれて、集積回路を形成するための処理ステップの数が増えてきている。製造プロセスの数も、集積回路がますます複雑になるにつれ、それに比例して増大してきている。集積回路製造プロセスが複雑になると、それに対応して集積回路の製造コストも増大するのは極めて当然なことである。従って、改良型およびもっと機能的なコンピュータ、および他のインテリジェント電子装置の製造コストを手ごろな値段に維持するためには、より簡単でより効率的で、小型化プロセスを助け、集積回路の品質または性能を劣化させない集積回路の新しい製造方法が必要になる。

従来の集積回路製造プロセスにとって必要な一つのステージは、半導体装置またはMOSトランジスタ・ゲート領域およびコンデンサの電荷貯蔵ノードのような半導体装置の個々の機能を形成するために使用される、成形済み構造体を形成するステージである。これら成形済みの構造体は、通常、半導体ウエハ上に構造体の層をパターン形成することにより形成される。構造体の層は、通常、構造体の層の形成、ホトレジスト・マスクによる構造体の層のカバー、ホトレジスト・マスクでカバーされていない構造体の層の一部のエッチングによる除去を含むプロセスによりパターン形成される。ホトレジスト・マスクによりカバーされている構造体の層のある一部または数カ所が、成形済みの構造体を形成する。そこを通して、構造体の層がエッチングされるホトレジスト・マスクは、従来は、写真製版と呼ばれるプロセスにより形成された。写真製版は、通常、あるパターンを、映像レンズを通して、写真製版テンプレートから、パターン形成中の構造体の層に塗布されたホトレジスト・コーティングに転写するために、紫外線(UV)のような光線を使用する。写真製版テンプレートのパターンは、ホトレジスト・コーティング内に形成するための、対応する開口部および無傷の部分と整合する選択した形を持つ半透明および透明な領域を含む。写真製版テンプレートは、従来計算機助成製図により設計され、その上でホトレジスト・コーティングの露出が行われる半導体ウエハの断面より遥かに大きい。光は、ホトレジスト・テンプレートを通過し、写真製版テンプレートのパターンをウエハ上で必要な大きさに縮小する方法で、ホトレジスト・コーティング上に焦点を結ぶ。ポジのホトレジストの場合、マスクされていないホトレジスト・コーティングの一部が、現像により除去される。

パターンを、ホトレジスト・テンプレートからホトレジスト・コーティングに転写することができる解像度により、生成することができる主要部分の大きさが制限される。ホトレジスト・マスクの開口部および無傷の領域の大きさ、従ってホトレジスト・マスクにより形成される成形済みの構造体の大きさは、それに応じて制限される。それ故、写真製版解像度の限界は、集積回路をさらに小型化する場合の障害になっている。従って、0.2ミクロン以下の主要部分の大きさを持つ、成形済みの構造体を形成するための改良型の方法が求められている。

縮小した大きさで形成する必要がある、上記の一つの成形済みの構造体の一例としては、プログラマブル抵抗のオボニック・セルがある。オボニック・セルは、このセルを通過した電荷によりプログラムすることができる抵抗を持つカルコゲニドの領域である。通常、オボニック・セルは、ある量の材料から開口部をエッチングにより形成し、その後で、この開口部内にカルコゲニドを注入することにより形成される。オボニック・セルをプログラムするには、高い密度の電荷が最も適しているので、断面の小さな開口部を形成することが望ましい。このような開口部はそこに掛けられた電荷の密度を増大する働きをする。開口部は、従来、写真製版により形成されてきた。約0.2ミクロンより細い幅を持つ開口部を形成するための、商業的に実行可能な方法を開発することが望ましい。

写真製版により可能な解像度より高い解像度を持つ半導体装置の成形済みの構造体を形成するための、写真製版以外のいくつかの方法が現在使用されている。しかし、これらの別の方法は、いくつかの欠点および制限を持っているので普及していない。例えば、そのような方法の中の一つは、使い捨てスペーサ流れプロセスと呼ばれる。この使い捨てスペーサ流れプロセスは、材料の仮設ブロックを形成する最初のステップと、その後で、材料の仮設ブロックの縁部にスペーサを形成するステップを含む。材料の仮設ブロックは、結果としての高い解像度の成形済みの構造体が位置する場所に、スペーサが形成されるような位置に設置される。スペーサが形成されると、材料の仮設ブロックが除去され、スペーサが残って成形済みの構造体を形成する。スペーサを形成する際に写真製版を使用しないので、スペーサは現在の写真製版の解像度の限界により制限を受けずに、0.2ミクロンまたはそれ以下の大きさに形成することができる。

しかし、使い捨てスペーサ流れプロセスの一つの問題は、それにより形成することができる、成形済みの構造体のタイプが制限されることである。通常、上記成形済みの構造体は、ある幅を持つものでなければならない。すなわち、写真製版の解像度以下の相互接続ラインのような主要な部分が、使い捨てスペーサ流れプロセスより、写真製版の解像度より高い解像度の幅で形成される場合、相互接続ライン全体は、写真製版の解像度の幅より狭くなくてはならない。そこにもっと幅の広い構造体を接続することができる、相互接続ラインのもっと幅の広い部分を形成するための、別の位置およびマスク・ステップを使用しないで、もっと大きい構造体へ相互接続ラインを接続することはできない。

それにより、半導体装置の主要部分のような成形済みの構造体を、現在のプロセスの流れよりもっと簡単で、もっと効率的な方法で形成することができる方法が、現在この業界で求められている。上記説明らから、使い捨てスペーサ流れプロセスのような写真製版に変わる方法よりももっと柔軟であり、従来の写真製版よりも小さい成形済みの構造体を形成するのに、このような方法が使用できるなら、上記方法がさらに役に立つことは明らかであろう。

絶縁面を効率的にまた選択的にエッチングするエッチング・プロセスが、現在通常使用されている。成形済みの構造体を形成する際によく使用される構造体の層、および導電性の特殊な成形済みの構造体の一つのタイプは、ポリシリコンである。ポリシリコンは、集積回路でよく使用されるもので、ある意味では好適なものである。何故なら、容易に蒸着することができるからである。ポリシリコンの蒸着は、シラン、ジシランまたはジクロロシランのよな前駆物質の熱分解を含む化学反応により、蒸着チャンバ内で通常行われる化学蒸着法(CVD)により行われる。

ポリシリコンから成形済みの構造体を形成するために、ポリシリコンが構造体の層として蒸着され、その後で、パターン形成される。従来、ポリシリコンのパターン形成は、ホトレジスト・パターン形成を含むプロセスで行われてきたので、それに付随する上記欠点も持っている。ポリシリコンをパターン形成する従来のプロセスは、また通常、プラズマ・エッチング・プロセスによる乾式エッチングを含む。このプロセスも以下に説明するいくつかの欠点を含む。

通常、成形済みの構造体を形成するためにエッチングを行う場合、エッチングが行われる材料に、直角にエッチングすることができることが望ましい。このようなエッチング・プロセスは、異方性エッチング・プロセスと呼ばれる。異方性乾式エッチングは、半導体ウエハに、一つまたはそれ以上のエッチング・ガスの流れの中で形成されるプラズマにより発生するイオンが衝突するエッチングの一つのタイプである。通常、エッチング・ガスとしては、一つまたはそれ以上のハロカーボンおよび/または一つまたはそれ以上のハロゲン化合物が使用される。従来、エッチング・ガスとしては、例えば、CF4、CHF3(フレオン23)、SF6、NF3およびその他のガスが使用された。さらに、O2、Ar、N2およびその他がガスの流れの中に追加される。例えば、エッチングされる材料の特性、処理のステージ、使用されるエッチング・システムのタイプ、およびエッチング速度および異方性の度合のような必要なエッチング特性により、特定のガス混合物が使用される。

乾式エッチングの異方性の性質は望ましいものであるが、この方法は異なるタイプの層に対して高度に選択的でないという欠点がある。この欠点のために、ハッキリとしたプロファイルを持つ成形済みの構造体を形成するために、必要な深さにおいて、エッチング・プロセスを正確に終了させることは困難である。また、一回のホトレジスト・マスク処理、および乾式エッチング・ステップで形成することができるパターンは、一つの深さおよびホトレジストで形成することができるパターンに限定される。従って、複雑なプロファイルを持つ成形済みの構造体を形成するには、マスク処理および乾式エッチング・ステップを何回も反復して行う必要があり、そのためコストが高くなる。それ故、主要部分の大きさおよびプロファイルをもっと高度に制御することができ、また低いコストで、ポリシリコンのような構造体の層を、異方性に従ってパターン形成することができる、より高度に制御することができるエッチング・プロセスを設計することが望ましい。

上記のような改良型の方法は、上記の利点の他に、多くの付帯的な利点を持つ。例えば、集積回路の性能を向上させるために、それにより形成することができる、成形済みの構造体の種々のタイプのプロファイルに、柔軟性を与える改良型の方法を開発することができれば、それは望ましいことである。上記改良型の方法が、上記安いコストの要求を満たすために、ある半導体装置の形成プロセスのプロセスの流れを簡単にすることができれば、それも望ましくいことである。集積回路製造プロセスの、上記およびその他のニーズをさらに説明するために、いくつかの従来の代表的なプロセスの流れおよびその限界について以下に説明する。

改良の必要があるプロセスの流れの第一の代表的な例について以下に説明する。もっと詳細に説明すると、材料の絶縁層に開口部を形成するために、集積回路の製造プロセス中にはいくつかの段階が必要になる。下に位置する半導体装置または半導体装置の個々の主要部分と電気的接続を行うために、導電性材料が開口部内に蒸着される。通常、能動領域を露出している絶縁層を貫通している開口部は、接点開口部と呼ばれ、いくつかのレベル間誘電層を貫通する開口部は、バイヤ開口部と呼ばれる。本明細書においては、相互接続構造体開口部という用語は、絶縁層を貫通している上記開口部を、集合的に呼ぶために使用される。接点またはバイアを形成するために、接点開口部およびバイア開口部は、導電性材料で満たされる。ポリシリコンで満たされた接点開口部およびバイア開口部は、ポリシリコン・プラグと呼ばれる。本明細書で使用するように、相互接続構造体という用語は、半導体ウエハの異なるレベル上に位置する個々の半導体装置の主要部分を電気的に接続する接点、バイアおよびプラグのような導電性構造体を、集合的に呼ぶために使用される。

従来の一連のプロセスにより、相互接続構造体の開口部、または絶縁層を貫通している他の開口部を形成するために、ホトレジスト・マスクが絶縁層上に置かれ、相互接続構造体の開口部を形成しようとする絶縁層の位置の上の領域を、露出した状態のままにしておくために、パターン形成が行われる。その後、現在の従来からの一連のプロセス場合には、通常は、上記乾式エッチング・プロセスである、エッチング・プロセスにより開口部を形成するために、材料が絶縁層から除去される。

乾式エッチング・プロセスは、すでに説明したとおり、異なるタイプの材料に対して選択性を持っていないために、問題があることが分かっている。高い密度を持つ相互接続構造体を形成する際には、高いアスペクト比の相互接続構造体の開口部が必要になる。本明細書で使用する場合、開口部のアスペクト比は、開口部の垂直方向の主要な長さを、開口部の水平方向の長さで割った比である。高いアスペクト比を持つ相互接続構造体は、下に位置するシリコン基板に過度のエッチングが行われないように、エッチング・プロセスの高い選択性を必要とする。選択性の一つの目安は、窒化シリコン・エッチング・バリア層を使用することにより達成される。しかし、アスペクト比が増大すると、従来の乾式エッチング・プロセスにより、高いアスペクト比を持つ相互接続構造体の開口部を同じようにエッチングするのがますます困難になる。

また、従来の乾式エッチング・プロセスは、均一性が低い。何故なら、従来の乾式エッチング・プロセスを使用すると、全ウエハ面を均一にエッチングするのが難しいからである。乾式エッチングに関連する別のもう一つの問題は、平滑でなく、均一でない、凹凸を持つ表面を乾式エッチングするのが困難なことである。上記相互接続構造体の開口部を乾式エッチングする場合には、凹んだ面よりも凸状の面の方が速くエッチングされ、乾式エッチング・プロセスの選択性が、エッチングされれいる主要部分の深さにより変化するという問題が発生する。それ故、均一でない凹凸を持つ表面で、高い選択性を維持するのは困難である。

相互接続構造体の開口部を形成する際のもう一つの制限要因は、相互接続構造体の開口部をエッチングする前に、マスク処理をするのが困難であることである。マスクは、高い密度の接点開口部を形成する際に、非常に小さい相互接続構造体用の開口部と一緒に形成され、そのため、マスクの開口部を、半導体基板上の正しい位置に正しく整合するのが困難になる。

相互接続構造体を一度完成するために、相互接続構造体の開口部が形成される。相互接続構造体の開口部は、アルミニウムまたはタングステンのような金属により充填される。しかし、相互接続構造体の開口部を金属で充填すると、アルミニウムおよびタングステンが、能動領域の下に位置するエピタキシャル・シリコンに対して、導電性の高いインターフェースを形成しないという別の問題が起こる。アルミニウムは能動領域に拡散し、能動領域をショートする、導電性のスパイクを形成する恐れがある。タングステンは能動領域のところで化学反応を起こし、空隙を形成し、それにより相互接続構造体の導電性が低下する。従って、充填物質としてアルミニウムまたはタングステンを使用すると、ライナー層を形成するために、面倒なステップを行わなければならない。しかし、ライナー層が形成されると、また問題が起こる。何故なら、ライナー層の蒸着により接点開口部が狭くなる傾向があり、充填物質を効率的に蒸着するのが難しくなるからである。

相互接続構造体の開口部の、充填に関連する問題を克服するために使用する、相互接続構造体の一つのタイプに、ポリシリコン・プラグがある。ポリシリコン・プラグを形成するには、最初、ポリシリコン・プラグにより電気的に連絡している、半導体装置の主要部分上に絶縁層が形成される。半導体装置の主要部分は、通常、トランジスタの能動領域を含む。能動領域が形成されると、次に、ボロホスホシリケート・ガラス(BPSG)のような絶縁層が形成され、その後で逆流が起こる。その後、写真製版および乾式エッチングにより、絶縁層を貫通して接点開口部が形成される。その後、接点開口部は、ポリシリコンにより充填される。ポリシリコンは、通常、化学蒸着法により、全絶縁層上にポリシリコンのブランケット層として蒸着される。絶縁層上を延びる上記ブランケット・ポリシリコン層の一部は、その後、CMPまたは乾式エッチングのような平面化プロセスにより除去される。別の方法としては、ポリシリコンをマスク処理し、ポリシリコン層の残りの部分をエッチングすることにより、ポリシリコン・プラグ上に位置する、ポリシリコン層の一部を除去することができる。

ポリシリコン・プラグは、能動領域の下に位置する結晶性シリコンに対して、導電性の高いインターフェースを形成し、それにより導電性を持つ充填物質用に金属を使用する、相互接続構造体形成プロセスの、拡散問題を解決することができるという利点を持つ。一方、ポリシリコン・プラグは、その内部にポリシリコン・プラグが形成される、相互接続構造体の開口部を形成する際に、上記の乾式エッチング・プロセスを依然として使用しなければならないという問題がある。従来のポリシリコン・プラグ形成プロセスは複雑なものであった。そのような複雑なプロセスなので、処理能力が制限され、エラーが発生する機会が増え、それにより集積回路の製造コストが高くなる。従って、それにより、高いアスペクト比の相互接続構造体の開口部を形成するために、乾式エッチングを使用しなくても、相互接続構造体および特に高いアスペクト比の相互接続開口部用の、ポリシリコン・プラグを、効率的にまた簡単に形成することができる方法が求められている。

集積回路の製造の際に頻繁に形成される、もう一つの成形済みの構造体はコンデンサである。コンデンサは、電荷貯蔵ノード、セル・プレート、および介在誘電層と一緒に形成される。電荷貯蔵ノードのポリシリコンおよびセル・プレートは、従来の写真製版および乾式エッチングにより、通常、別々に蒸着され、パターン形成される。介在誘電層は、通常、酸素に露出させて二酸化シリコンを成長させることにより、電荷貯蔵ノードとセル・プレートの形成の間に形成される。

集積回路にコンデンサを形成する際の重要な考慮事項は表面積である。電荷貯蔵ノード、および上部コンデンサ・セル・プレートの、表面積が大きいので静電容量が増大する。コンデンサが、半導体ウエハのシリコン基板上を占有するスペースは最小でなければならないという競合する要件と、このニーズとを満足させなければならない。従来技術がコンデンサ形成の際に、シリコン基板上に占めるスペースを増大しないで、より広い表面積を得るためにとった一つの方法は、シリコン基板の上のある距離のところに、コンデンサを形成するという方法であった。この方法の場合、電荷貯蔵ノードおよびセル・プレートの一方は、通常、狭い領域内で他方を周囲を囲み、いわゆる積層型コンデンサを形成する。積層型コンデンサの種々のコンフィギュレーション、およびその形成方法に関連する共通の一つの問題は、プロセスが通常、複雑であり、長い時間が掛かり、欠陥を生じる機会が増え、コストが高くなることである。従って、大きな表面積を持っていながら、シリコン基板上での占有スペースが最も小さい、積層型コンデンサを簡単に効率的に形成する方法が求められている。また、積層型コンデンサの電荷貯蔵ノードおよびその下に位置する相互接続構造体を、一体に形成することにより、より大きい電荷貯蔵領域を形成することも望ましいことである。

積層型コンデンサの形成に付随するもう一つの問題は、コンデンサの電荷貯蔵ノードの下に位置する、積層型コンデンサ上の能動領域に、積層型コンデンサを電気的にリンクしなければならないという問題である。積層型コンデンサが高速の電荷保持を維持することは、集積回路の高速を維持するのに極めて重要なことである。動的にリフレッシュ可能なランダム・アクセス・メモリ(DRAM)集積回路のような、メモリ機能を持つ集積回路を形成する際には、上記のことは特に重要である。電荷貯蔵ノードにおいて大量の電荷保持を維持するために、積層型コンデンサは、通常、シリコン基板から分離されている。

しかし、シリコン基板上の能動領域から、積層型コンデンサへ相互接続構造体を形成すると、いくつかの問題が起こる。例えば、電荷貯蔵ノードを、その下に位置する能動領域に電気的接続している、相互接続構造体を形成するための従来の方法は、通常、深さがもっと深い相互接続構造体の開口部の形成と、通常はポリシリコンによる、相互接続構造体の開口部の充填を含む。しかし、このようなプロセスは、実行するのが難しい。何故なら、これらは、欠陥が起こらないように、すべてのプロセス・パラメータを正しく制御するための、小さなプロセス・ウインドウを持っているからである。例えば、標準乾式エッチング・プロセスにより、2:1以上のアスペクト比を持つ、相互接続構造体の開口部を形成するのは難しい。

改良型製造プロセスを必要とするもう一つの半導体装置は、MOSトランジスタである。このトランジスタは、現代集積回路製造の最も重要なものであり、マイクロプロセッサのような集積回路は、多くの場合、一つのチップで数百万のトランジスタを使用する。現在、MOSトランジスタは、集積回路形成の際の最も普通のトランジスタである。集積回路上の同じ大きさのスペースにより多くのトランジスタを形成することができれば、集積回路はより多くの機能を持つことができる。それ故、半導体ウエハのシリコン基板上で、より少ない面積しか占有しない、トランジスタを形成するための方法が求められている。

また、トランジスタが、より低い電圧レベルで動作することも望ましいことである。より低い電圧レベルで動作する、MOSトランジスタを形成する際の一つの障害は、MOSトランジスタのチャネルの長さである。チャネルの長さは、通常、形成中のMOSトランジスタのゲート領域の幅により決まる。ゲート領域の幅は、従来の製造プロセスの場合には、すでに説明したように、写真製版の解像度の限界により制限される。ゲート領域の大きさは、またある程度まで、トランジスタが占有する表面積の大きさを決める。従って、集積回路上で、ゲートの長さが短く、動作電圧レベルの低い、トランジスタを製造することができる改良型プロセスが求められている。

トランジスタの形成も複雑なプロセスであり、多数のステップを必要とする。必要なステップの数が多いので、集積回路の製造プロセス・コストが高くなり、処理能力が低下し、エラーが発生する機会が増える。それ故、トランジスタの形成プロセスを合理化する方法を求められている。

改良型形成方法を必要とするもう一つの成形済み構造体は、多くの場合、シリコン基板のレベルまでエッチングが行われ、トレンチ絶縁領域およびトレンチ・コンデンサのような、半導体装置を形成するために使用される浅いトレンチである。トレンチ・コンデンサの大きな静電容量を供給するために、適当な容積を持ちながら、シリコン基板上で大きな表面積を占有しない、トレンチ・コンデンサを形成する方法が求められている。適当な容積を持つトレンチ・コンデンサを形成する方法は、またトレンチ絶縁領域を改善し、通常、トレンチ絶縁領域のどちらかの側面上に形成される、MOSトランジスタのソース/ドレイン領域の間の、クロストーク電流漏洩の防止を助ける。

集積回路の製造の際によく使用されるもう一つの成形済みの構造体は、相互接続ラインである。本明細書においては、相互接続ラインという用語は、半導体装置または同じレベル上に位置する半導体装置の主要部分を、電気的に接続する成形済みの構造体、または半導体ウエハの一つのレベル上に形成された、相互接続構造体の間を電気的に接続し、物理的に相互が分離している半導体装置を意味する。半導体ウエハの一番上の面に形成された場合、この構造体は、単に表面相互接続ラインと呼ばれる。半導体ウエハの上記面の下に形成された場合には、その相互接続ラインは、ローカル相互接続と呼ばれる。

集積回路を小型化する一つの方法は、集積回路において、相互接続ラインの間隔をもっと狭くする方法である。相互接続ラインの間隔を狭くする一つの方法は、相互接続ラインの幅を狭くすることである。相互接続ラインの幅は、従来の写真製版プロセスの解像度の限界により制限される。この制限を克服するために従来技術がとった一つの方法は、上記の使い捨てスペーサ流れプロセスである。すでに説明したとおり、使い捨てスペーサ流れプロセスにより形成された導電ラインの太さは変えることができない。従って、導電性スペーサをもっと幅の広い相互接続ライン、またはその主要部分の大きさがもっと大きい装置に接続しなければならなくなった場合には、そうするために余分の材料は供給されない。それ故、狭い相互接続ラインを形成するための、もっと柔軟なプロセスが求められている。

集積回路を形成する際には、他の成形済みの構造体もよく使用され、改良型のエッチング・プロセスを使用しているために有利であり、そのため、成形済みの構造体を、もっと柔軟で、もっと簡単で、もっと効率的なプロセスにより形成することができる。上記成形済みの構造体の一つの用途は、ミニアチュア・センサおよびミニアチュア・アクチュエータで通常使用されるような、マイクロマシン部品の製造である。最小限度の材料の蒸着ステップと、マスク処理ステップ、およびエッチング・ステップで、上記構造体を形成する方法が求められている。

集積回路形の際に使用されるもう一つの成形済みの構造体は、コンデンサの電荷貯蔵ノード、および他の導電装置を形成するために使用される自立壁部である。結果として得られる自立壁部の厚さ、およびそれにより自立壁部を形成することができる形を、柔軟に得られる方法が求められている。上記自立壁部を効率的にに形成することができ、写真製版の解像度以上の解像度を持つ上記方法も求められている。

発明の概要

この技術に関する上記問題を解決するために、また好適な実施形態で実行され、本明細書に概略記載した本発明は、18の関連する方法を使用する。各方法の場合、成形済みの構造体を形成するために、ある量のシリコンを含む材料の選択した一部が除去される。通常、除去された部分と除去されなかった部分との間の違いは、原子粒子の注入が行われる前に、除去された部分と除去されなかった部分の、ドーパントの濃度のそれぞれのレベルとは無関係な、それぞれの部分の原子粒子のそれぞれの注入レベルである。

第一の方法の場合、半導体基板上に位置するシリコンを含む材料の容積の選択した一部が、シリコンを含む材料の層に成形済みの開口部が残るような方法で除去される。ある実施形態の場合には、最初に、ポリシリコン層を含むシリコンを含む材料の層が、半導体基板上に形成される。シリコンを含む材料の層の上にはマスク被覆基板が形成されるが、このマスク被覆基板は、シリコンを含む材料の層の少なくとも一つの領域をマスクし、シリコンを含む材料の層の第二の領域を、マスクされていない状態のままに維持する。

その後、選択したイオンが、シリコンを含む材料のマスクされていない部分に注入される。上記イオンは、以下に説明する方法で、イオン注入が行われたシリコンを含む材料に対して選択的なエッチング・プロセスにより選択されたタイプのものである。マスク被覆基板の大きさよりも、成形済みの開口部の大きさを小さくするために、半導体基板に対して直角以外の角度で、イオンを注入し、イオンをマスク被覆基板の縁部の下の注入することができる。半導体基板に対して直角以外の注入角度でイオンを注入した場合には、成形済みの開口部の大きさが、マスク被覆基板の大きさよりも小さくなり、一方、半導体基板の表面に直角な注入角度でイオンを注入すると、大きさはほとんど変わらない。

注入領域の大きさをさらに修正し、それにより最終的な成形済みの開口部が得られるように、イオンのタイプ、注入量、および注入エネルギーのような他のイオン注入パラメータを、適当に選択することができる。選択したマスク被覆基板のイオンに対して不浸透性も、結果として得られる成形済みの構造体のエッチングに影響を持つ。イオン注入の後で、熱処理によりイオンを拡散させると、ポリシリコン層へさら深くイオンが浸透し、結果として得られる成形済みの主要部分のプロファイルがさらに調整される。しかし、シリコンを含む材料の層に注入したイオンのプロファイルを、よりハッキリした状態に維持するためには、通常、熱処理を行わない方が望ましい。

さらに、大きさを均一に変化させるために、複数の各イオン注入ステージに対して一つのイオン注入パラメータを変化させながら、イオン注入作業を、複数のイオン注入ステージにより行うことができる。複数の各イオン注入ステージに対する、イオン注入角度を変化させることにより、例えば、ほぼ異方性の側壁を持つ、深い成形済みの開口部を形成することができる。

以降の手順において、マスク被覆基板は、シリコンを含む材料の層から除去され、その後、シリコンを含む材料の層が、エッチング・プロセスによりエッチングされる。このエッチング・プロセスにより、エッチング・プロセスが、イオンによりしきい値濃度までイオン注入されている、シリコンを含む材料の容積の一部をエッチングするより速い速度で、しきい値濃度までイオン注入されていない、シリコンを含む材料の容積の一部がエッチングされる。本明細書においては、このようなエッチング・プロセスを、イオン注入したシリコンを含む材料に対して選択的なエッチング・プロセスと呼ぶ。しきい値濃度の正確な数値は、特定のエッチング・プロセスおよびエッチング・プロセス・パラメータにより変化する。しかし、上記すべてのエッチング・プロセスの場合、しきい値濃度以上にイオン注入されたシリコンを含む材料は、イオン注入されたシリコンを含む材料に対して選択的なエッチングプロセスによっては、実質的に除去されないで、しきい値濃度以下の濃度にイオン注入されたシリコンを含む材料だけが、実質的に除去される。

イオンが注入されたシリコンを含む材料に対して選択的なエッチング・プロセスの一例としては、水酸化テトラメチル・アンモニウム(TMAH)による湿式エッチングがある。TMAH湿式エッチングは、通常、エッチング溶液として管理され、その中に半導体ウエハが浸漬される。好適には、上記エッチング溶液は、脱イオン水に約1:10重量パーセントのTMAHを含んでいることが好ましい。上記エッチング溶液が、脱イオン水に約2.5重量パーセントのTMAHを含んでいれば、さらに好適である。

TMAH湿式エッチングは、この方法が、しきい値濃度までイオン注入されている、シリコンを含む材料をエッチングする速度の、少なくとも二倍の速度で、しきい値濃度以下にイオンが注入されている、シリコンを含む材料をエッチングすることが分かっている。20倍および40倍の速いエッチング速度を容易に達成することができる。TMAHの濃度により、また他のイオン注入の選択により、また他のエッチング・プロセス・パラメータの選択により、60倍までのエッチング速度を達成することができる。

ポリシリコンに対してTMAH湿式エッチングを行う場合、好適には、少なくともポリシリコンに対する注入イオンのしきい値濃度が、シリコンを含む材料の1立方センチあたり、約1X1015から1X1022の範囲になるようにイオンを注入することが好ましい。最も好適なのは、しきい値濃度が、シリコンを含む材料の1立方センチ当り約5X1018から約1X1019である場合である。最も好適なのは、シリコンを含む材料の1立方センチ当りのしきい値濃度が1x1019の場合である。

注入イオンとしては、ホウ素および燐のような普通のドーパンドが適しているが、さらに、他の普通のドーパント・イオン、および通常ドーパント・イオンは見なされないイオンでも、満足する結果が得られる。例えば、シリコンを含む材料の電気的特性を、電気的に活動させるか、または変化させるイオンでも、TMAH湿式エッチングにより使用することができる。このようなイオンの例としては、シリコンを・イオンおよびアルゴン・イオンがある。

イオンを注入したシリコンを含む材料に対して選択的なエッチング・プロセスを使用した場合には、イオンのしきい値濃度までイオン注入されていないポリシリコン層の選択した一部が、エッチングにより除去されて、成形済みの開口部が形成される。エッチングの実行時間のようなエッチング・プロセス・パラメータも、成形済みの開口部をさらに調整するために変化させることができる。成形済みの開口部の使用の一実施形態の場合には、プログラマブル抵抗のオボニック・セルは、成形済みの開口部に、カルコゲニド材料を充填することにより形成される。

関連実施形態の場合には、その内部に成形済みの開口部を含むポリシリコンが、下に位置する層をパターン形成するために、ハードマスクとして使用される。それ故、例えば、窒化シリコンのような、シリコンを含む材料以外の材料の層が、最初にシリコンを含む材料の層の下に形成され、シリコンを含む材料に成形済みの開口部を形成するために、第一の方法が実行される。その後、窒化シリコンの層に成形済みの開口部を形成するために、成形済みの開口部を通して、窒化シリコンの層をエッチングするために、エッチング・プロセスが行われる。

それ故、簡単で効率的な成形済みの開口部を形成するための方法が供給される。この方法は、従来の写真製版プロセスで、形成することができるものよりも小さい、成形済みの開口部を形成するために使用される。結果として得られる成形済みの開口部の可能なプロファイルがより柔軟になるので、それにより形成することができる半導体装置のタイプが増大し、そのため、第一の方法で形成された集積回路の潜在的な機能が増大する。

本発明の第二の方法の場合、成形済みの構造体は、第一の方法のエッチング・プロセスとは反対に、しきい値濃度までイオンの注入を受けていない、シリコンを含む材料をエッチングするよりかなり速い速度で、しきい値濃度までイオン注入されている、シリコンを含む材料をエッチングする、あるエッチング・プロセスで半導体ウエハ上の、シリコンを含む材料の層から形成される。第二の方法は、最初に、半導体基板上に、ポリシリコン層のようなシリコンを含む材料の層を形成する。その後、シリコンを含む材料の層の上に、マスク被覆基板が設置される。マスク被覆基板は、シリコンを含む材料の層の少なくとも一部をカバーするように、またシリコンを含む材料の一部がマスクされないように設置される。

従って、イオンは、シリコンを含む材料の層のマスクされていない部分に注入される。イオンは、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスに従って選択された、選択されたタイプのものである。ある実施形態の場合には、イオンは、燐またはホウ素イオンのようなドーパント・イオンを含む。第一の方法の場合のように、イオン注入作業は、しきい値濃度までイオン注入されている材料の層の一部のプロファイルを、それにより結果として得られる成形済みの構造体のプロファイルを調整するために選択したイオン注入パラメータに従って実行される。イオン注入作業は、第一の方法のところで説明した複数の各イオン注入ステージに対してイオン注入パラメータを変化させ、それに従って、複数のイオン注入ステージにより行うことができる。

イオン注入作業が終了した後で、シリコンを含む材料の層の、マスクされていない部分の高さを部分的に低くするために、シリコンを含む材料をほぼ異方性に従ってエッチングする、最初のエッチング・プロセスが行われる。

最初のエッチング・プロセスが行われると、しきい値濃度までイオン注入を受けていない、シリコンを含む材料の層の一部をエッチングするよりも、かなり速い速度でしきい値濃度までイオン注入されている、シリコンを含む材料の層の一部をエッチングするエッチング・プロセスにより、シリコンを含む材料がエッチングされる。本明細書においては、このようなエッチング・プロセスを、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスと呼ぶ。しきい値濃度であるイオンの濃度は、使用するイオン注入を受けていないシリコンを含む材料に対して選択的な特定のエッチング・プロセスにより、また本明細書を読めば当業者なら容易に理解することができるような方法で、イオン注入パラメータおよびエッチング・パラメータを選択することにより決定される。

例示としてのある実施形態の場合には、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスは、市販のフツ酸のような酸性のエッチング液を使用するが、硝酸のエッチング溶液を使用することもできる。また、KOHエッチング薬品を、ポリシリコン層のドーピング抑制剤と一緒に使用することができる。

イオン注入を受けていない材料に対して選択的なエッチング・プロセスを行うと、その結果、マスクされていて、そのためイオンしきい値濃度以下にイオンが注入されている、シリコンを含む材料の層の一部のところに、隆起した成形済みの構造体が形成される。半導体基板の面に対して直角以外の角度でイオン注入が行われる実施形態の場合には、成形済みの構造体は、シリコンを含む材料層のマスクした部分の大きさより小さくなる。

隆起した成形済みの構造体は、また下に位置する層をエッチングするための、仮設ハードマスクとして使用することができる。隆起した成形済みの構造体を、仮設ハードマスクとして使用する場合には、材料の層の蒸着を行う前に下の層が形成される。隆起した成形済みの構造体は、その後、上記の方法で形成され、下の層をエッチングするとき、ハードマスクとしての働きをする。下の層は、通常、乾式エッチングのようなエッチング・プロセスで、異方性に従ってエッチングされる。隆起した成形済みの構造体は、下の層のエッチングを行った後で除去され、下の層の一部はほぼ同じ位置に残るが、その場合、大きさは隆起した成形済みの構造体の大きさとほぼ同じである。ここでもまた、これらの大きさは、従来の写真製版で形成できるものより小さい。

本発明の第三の方法は、相互接続構造体を形成するために使用される。第三の方法の場合、能動領域のような電荷伝導領域が、最初に半導体基板上に形成される。ある実施形態の場合にはポリシリコン層である、シリコンを含む材料の層が、その後、電荷伝導領域上に形成される。その後、シリコンを含む材料の層は、能動領域上に位置する、シリコンを含む材料の層の、マスクされていない部分を、そのまま残すためにパターン形成されるマスク被覆基板によりマスクされる。

マスク被覆基板が設置された後で、イオンが、シリコンを含む材料の層のマスクされていない部分に注入される。すでに説明したとおり、これらのイオンは、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスに従って選択される。イオン注入プロセス・パラメータは、結果として得られる相互接続構造体の形を決めるために、変化させることができる。また、イオン注入作業を、すでに説明したとおり、複数のイオン注入ステージに分けて行うことができる。

イオン注入作業が終了した後で、マスク被覆基板は除去され、シリコンを含む材料の層が、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスによりエッチングされる。その結果、マスク被覆基板の下の、シリコンを含む材料の層の一部が除去され、マスクされていて、そのためイオン注入を受けていない能動領域の上に位置する、シリコンを含む材料の層の一部が残り、能動領域に電気的に接続している相互接続構造体を形成する。

本発明の方法により、相互接続構造体が、上記の従来の方法により作られた相互接続構造体より、簡単で効率的な方法で作られる。従って、集積回路製造処理能力が増大し、集積回路製造コストが安くなる。すでに説明したとおり、乾式エッチング・プロセスを使用する必要もないし、それに関連する問題も解決する。

本発明の第四の方法は、積層型コンデンサの電荷貯蔵ノードを形成するために使用される。第四の方法の場合、最初に、電荷伝導領域が、半導体基板の上に形成され、その上に積層型コンデンサの電荷貯蔵ノードが形成される。ある実施形態の場合には、電荷伝導領域は、半導体ウエハのシリコン基板に形成された能動領域を含む。能動領域が形成されると、その後で、シリコンを含む材料の層が能動領域上に形成される。これから説明しようとする実施形態の場合には、シリコンを含む材料の層はポリシリコン層を含む。

ポリシリコンの層は、マスク被覆基板によりマスクされ、上記マスク被覆基板は、能動領域上に位置するポリシリコン層の一部を、マスクされていない状態のままに維持するために、パターン形成される。マスク被覆基板は、二つの縁部を持つアイランドの形をした部分により形成されるが、上記二つの縁部は、それぞれ、能動領域の上の一方の側面に位置する。

マスク被覆基板が設置され、パターン形成された後で、シリコンを含む材料のスペーサが、ポリシリコン層上に形成されるが、一方はマスク被覆基板の二つの各縁部に隣接する。スペーサは、従来のスペーサ形成プロセスにより形成され、その形および高さは、形成される積層型コンデンサの電荷貯蔵ノードに従って選択される。

その後で、第一の方法のところで説明した方法とほぼ同じ方法で、ポリシリコンの層のマスクされていない部分に、イオンが注入される。また、上記の複数のステージにより、イオン注入作業を行うことができる。

イオン注入作業が終了した後で、マスク被覆基板は除去され、ポリシリコン層が、第一の方法のところで説明した方法で、イオン注入が行われたシリコンを含む材料に対して選択的なエッチング・プロセスによりエッチングされる。イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより、マスク被覆基板の下に位置するポリシリコン層の一部が除去され、マスクされていない能動領域の上に位置するポリシリコン層の一部はそのまま残留する。スペーサも残留し、そこから上に延びて、積層型コンデンサの電荷貯蔵ノードを形成する。

第四の方法の他の実施形態の場合には、積層型コンデンサの電荷貯蔵ノードと同時に、相互接続構造体が形成される。この手順は、相互接続構造体が形成される場所において、相互接続構造体が位置するポリシリコン層の一部の上に、スペーサが形成されないという点を除けば、積層型コンデンサの電荷貯蔵ノードだけが形成される、第一の実施形態の手順とほぼ同じである。結果として得られる相互接続構造体を形成するために、イオン注入プロセスのパラメータを変更することができる。

第四の方法は、内蔵電荷貯蔵ノードおよびコンデンサ・ベースと一緒に、積層型コンデンサの電荷貯蔵ノードを形成する。積層型コンデンサの電荷貯蔵ノードは、コンデンサ・ベースと同時に形成することができ、それにより、個々の相互接続構造体の形成ステップを行う必要がなくなる。従って、マスク処理ステップおよびエッチング・ステップの数が少なくなり、それにより、処理能力が増大し、コストが下がり、集積回路製造プロセス中にエラーが起らなくなる。第四の方法は、また積層型コンデンサの電荷貯蔵ノード形成プロセスを、より柔軟なものにする。何故なら、積層型コンデンサの電荷貯蔵ノードの形成と同時に、能動領域上にシリコン・プラグを形成することができるからである。

本発明の第五の方法は、MOSプロセスの流れの中で、相互接続構造体を形成するのに使用される。第五の方法の場合、トランジスタ・ゲート領域を形成するところまでは、従来のCMOS集積回路の形成プロセスと同じである。この形成プロセス中、シリコン基板が、PMOS部分およびNMOS部分と一緒に形成される。少なくとも一つのゲート領域が、PMOS部分およびNMOS部分それぞれの上に形成される。絶縁スペーサも、NMOS部分のゲート領域の周囲に形成される。その後で、PMOS部分が、第一のマスク被覆基板によりマスクされる。

その後で、その内部に少なくとも一つの能動領域を形成するために、適当なタイプのドーパント・イオンが、NMOS部分に注入される。その後で、PMOS部分から第一のマスク被覆基板が除去され、シリコンを含む材料の層が、PMOS部分およびNMOS部分上に蒸着される。上記実施形態の場合には、シリコンを含む材料の層はポリシリコン層である。

蒸着が行われると、ポリシリコン層が、第二のマスク被覆基板によりマスクされる。第二のマスク被覆基板は、NMOS部分の選択した能動領域の上に位置する、ポリシリコン層の一部をマスクされていない状態に維持するために、パターン形成される。

その後で、ポリシリコン層のマスクされていない部分にイオンが注入される。このプロセス中、第二のマスク被覆基板が、このマスク被覆基板の下に位置するポリシリコン層の一部にイオンが実質的に衝突し、注入されるのを防止する。イオン注入作業は、上記の第一の方法とほぼ同じ方法で行われる。その後、第二のマスク被覆基板が除去され、ポリシリコン層が、イオン注入を受けたシリコンを含む材料に対して選択的な、エッチング・プロセスによりエッチングされ、それにより、マスク被覆基板の下に位置するポリシリコン層の一部が除去される。NMOS部分の選択した能動領域の上の、ポリシリコン層のマスクされていない部分が残り、ポリシリコンの相互接続構造体を形成する。

上記第一の方法のところで説明した方法により、イオン注入およびエッチング・プロセス・パラメータを適当に選択することができる。ここでもまた、シリコン基板に対して直角以外の角度でイオン注入作業を行うことができ、また複数のステージにより行うことができる。マスク被覆基板のタイプも変化させることができ、結果として得られる相互接続構造体の形をさらに調整するために、熱処理により、注入したイオンを自由に拡散させることができる。

相互接続構造体が形成されると、NMOS部分がマスク被覆基板によりカバーされ、その内部に少なくとも一つの能動領域を形成するために、PMOS部分にイオンが注入される。

それ故、第五の方法の場合、CMOSプロセス中に、相互接続構造体が形成され、そのため従来技術の方法の際には必要であった、いくつかのステップを実行しなくてすむ。また、イオン注入プロセスまたはエッチング・プロセスによる相互汚染を起こさないで、NMOS領域およびPMOS領域のソース/ドレイン領域がドーピングされる。マスク処理作業およびエッチング作業の回数が、従来のCMOSプロセスよりも少なくなり、そのため、集積回路製造プロセスの処理能力が増大し、最終的には、それにより形成される集積回路のコストが下がる。第五の方法も、簡単で効率的なものであり、接点エッチングおよびコンデンサの形成を効率的に行う。

本発明の第六の方法は、自立壁部を形成するために使用される。自立壁部は、積層型コンデンサの電荷貯蔵ノードを形成する際に使用するのに適している。第六の方法の場合、この実施形態の場合にはポリシリコン層である、シリコンを含む材料の層が、最初、半導体基板の上に蒸着される。ポリシリコン層は、好適には、真性ポリシリコンから形成することが好ましい。

ポリシリコン層が形成された後で、マスク被覆基板が、ポリシリコン層の上に置かれ、マスク・アイランドを形成するためにパターン形成される。その後、ポリシリコン層の露出した部分を異方性に従って除去するために、乾式エッチング・プロセスが使用される。乾式エッチング・プロセスは、マスク被覆基板のアイランドの表面の、大きさに対応する表面の大きさを持つポリシリコン層から、ポリシリコン・ブロックを形成する。

乾式エッチング・プロセスが終了した後で、ポリシリコン・ブロックの一つまたはそれ以上の横方向に延びる表面に、マスク被覆基板を、正しい位置に置いたままの状態でイオンが注入されている。イオン注入作業の後で、マスク被覆基板が除去され、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスが行われる。ポリシリコン・ブロックの形、およびイオンが注入されるポリシリコン・ブロックの、横方向に伸びる面の大きさにより、種々の異なる形の自立壁部を形成することができる。適当な形のポリシリコン・ブロックを形成することにより、例えば、薄く、横方向に延びるポリシリコンのコラムを形成することができるが、このコラムの一組は、コンテナ・コンデンサを形成するのに適している。比較的細いコラムを特徴とする細いポストも形成することができる。

ポリシリコン・ブロックの周囲全体にイオン注入が行われた場合には、連続して延びる自立壁部が形成される。ポリシリコン・ブロックが円形である場合には、環状の自立壁部が形成される。結果として得られる自立壁部の厚さは、注入されらイオンの注入角度および注入エネルギーにより決まる。従って、自立壁部は、写真製版の解像度より優れた解像度を持つことができる。

第六の方法の自立壁部は、従来の写真製版およびエネルギー法では不可能であった、高いアスペクト比で形成することができる。種々の形の自立壁部を形成することができるので、集積回路形成プロセスがさらに柔軟になる。さらに、最も少ない処理作業で、自立壁部が効率的に形成されるので、集積回路製造プロセスの処理能力を高く、またコストを低く維持することができる。

本発明の第七の方法は、第六の方法に類似していて、積層型コンデンサの電荷貯蔵ノードを形成するのに適している、自立壁部を形成するのに使用することができる。第七の方法の場合も、第六の方法と同じように、最初に、ポリシリコン層の蒸着が行われ、その後で、ポリシリコン層上にマスク被覆基板が置かれ、パターン形成が行われる。マスク被覆基板は第七の方法の場合も同じものであるが、ポリシリコン層に対応するパターン形成された開口部を形成するために、マスク被覆基板は開口部と一緒にパターン形成される。マスク被覆基板を正しい位置に設置した状態で、ポリシリコン層の開口部の横方向に延びる表面に、イオンを注入するために方向性イオン注入が行われる。イオン注入作業は、第一の方法のところで説明した方法とほぼ同じ方法で行われ、ポリシリコン層の開口部の横方向に延びる面にイオンを注入するために、半導体基板の面に対して直角以外の注入角度で行われる。その後で、マスク被覆基板が除去され、第一の方法のところで説明した方法とほぼ同じ方法で、イオン注入を受けたシリコンを含む材料に対して選択的な、エッチング・プロセスが行われる。

マスク被覆基板の開口部の形、およびポリシリコン層の成形済みの開口部の、横方向に延びる面へのイオン注入の程度により、種々の構成の自立壁部を形成することができる。例えば、マスク被覆基板の開口部を円形に形成し、ポリシリコン層の開口部の横方向に延びる面全体にイオンを注入することにより、積層型コンデンサの電荷貯蔵ノード、またはサラウンド・ゲート・トランジスタ領域を形成するのに適している、環状自立壁部を形成することができる。それ故、第七の方法の自立壁部は、第六の方法の利点に類似の利点を持ち、集積回路製造プロセスをさらに柔軟なものにする。

本発明の第八の方法は、サラウンド・ゲートMOSトランジスタを、形成するのに使用される。第八の方法の場合には、最初に、好適には、第六のまたは第七の方法のところで説明した方法で、自立壁部を形成することが好ましい。好適には、自立壁部は、連続していて、その内部にチャンバを形成し、長方形または六角形を含む任意の適当な形にすることができる。好適な形は環状である。自立壁部は、ゲート酸化層上の半導体基板上に形成され、その後で、連続している絶縁スペーサが自立壁部のどちらかの側面上に形成される。ドーパントが、自立壁部の内部および自立壁部の外部の周囲のところの、シリコン基板に注入される。ドーパントとしては、形成中のトランジスタが、Nチャネル・トランジスタか、またはPチャネル・トランジスタかにより、Nタイプのドーパント、またはPタイプのドーパントが選ばれる。自立壁部領域のイオン注入を受けた内部および外部は、サラウンド・ゲート・トランジスタのソース/ドレイン領域を形成する。

これにより、サラウンド・ゲート・トランジスタが形成されるが、この場合、ゲート領域は、自立壁部から形成され、ソース/ドレイン領域は、ゲート領域の内部に形成され、もう一つのソース/ドレイン領域は、ゲート領域の外部に形成され、ゲート領域を囲む。MOSトランジスタのチャネルは、ゲート領域の下を延びていて、自立壁部の厚さにより決まる短いチャネルを持つ。自立壁部の厚さは、従来の写真製版の解像度のレベルに依存しないので、MOSトランジスタ・チャネルを、対応して非常に短くすることができる。好適には、チャネルの長さは、約0.25ミクロン以下であることが好ましい。

DRAMメモリ・セルも、第八の方法により形成することができる。この形成プロセス中、サラウンド・ゲート・トランジスタが、上記のように形成され、語線がサラウンド・ゲート・トランジスタのゲートに接続される。その後、もっと下の絶縁層がサラウンド・ゲート・トランジスタ上に形成される。相互接続構造体の開口部は、サラウンド・ゲート・トランジスタのソース/ドレイン領域まで、もっと下の絶縁層を貫通して開いている。相互接続構造体の開口部は、導電性材料により充填され、接点が形成される。第一の接点は、ゲート領域の内部のソース/ドレイン領域まで延びていて、第二の接点は、ゲート領域の外部のソース/ドレイン領域まで延びる。

DRAMメモリ・セルを形成する他の手順の場合には、電荷貯蔵ノードは、もっと下の絶縁層上に形成され、ゲート領域の内部のソース/ドレイン領域まで延びる接点と接続する。誘電層は、電荷貯蔵ノードの上に形成され、上部コンデンサ・プレートは、誘電層の上に形成される。その後で、上部絶縁層がコンデンサ上に形成され、デジット線が、ゲート領域の外部のソース/ドレイン領域まで延びる接点に接続している、その頂部のところに形成される。

MOSサラウンド・ゲート・トランジスタは、半導体基板上の最少のスペースしか占有しないで、従来技術のサラウンド・ゲート・トランジスタより、簡単で効率的方法で形成される。MOSサラウンド・ゲート・トランジスタは、約0.2ミクロン以下の長さでもよい、短いMOSトランジスタ・チャネルと、一緒に形成することができる。MOSサラウンド・ゲート・トランジスタは、DRAMメモリ・セルに容易に内蔵させることができる。上記DRAMメモリ・セルは、MOSサラウンド・ゲート・トランジスタと同様に、半導体基板上の最少の表面積しか占有しない。DRAMメモリ・セルは、またMOSサラウンド・ゲート・トランジスタの中心上に、コンデンサが位置しているので、少量の漏洩を起こす。

本発明の第九の方法は、積層型コンデンサの電荷貯蔵ノードとして使用するのに適している、円錐形の自立壁部を形成するのに使用される。第九の方法の場合には、この実施形態の場合にはポリシリコン層である、シリコンを含む材料の層が、最初、半導体基板の上に蒸着される。この実施形態の場合には、半導体基板は、その上に形成された能動領域の側面に、同様にその上に形成されたゲート領域を持つシリコン基板である。ポリシリコン層は、好適には、真性にドーピングされたポリシリコンから形成することが好ましい。ポリシリコン層の蒸着が行われた後で、絶縁層がポリシリコン層の上に形成される。

絶縁層が形成されると、マスク被覆基板が絶縁層上に蒸着され、パターン形成される。マスク被覆基板は、円錐形の積層型コンデンサの電荷貯蔵ノードが形成される位置の、開口部によりパターン形成される。その後で、傾斜面になるように、ポリシリコン層の露出した領域をエッチングするために、乾式エッチング・プロセスTが使用される。それにより、円錐形の開口部が、シリコン基板の能動領域の方向にテーパ状に延びている、ポリシリコン層に形成される。乾式エッチング・プロセスが終了してから、マスク被覆基板が除去され、第二のポリシリコン層が第一のポリシリコン層の上に蒸着され、第二のポリシリコン層が第一のポリシリコン層および絶縁層上に蒸着される。その後で、その内部のイオン注入を受けた領域を形成するために、第一の方法のところで説明した方法で、第二のポリシリコン層にイオンが注入される。

その後で、平面化プロセスにより、第二のポリシリコン層の一番上の部分、および絶縁層が除去される。平面化プロセスの後で、イオン注入を受けたシリコンを含む材料の層に対して選択的な上記エッチング・プロセスが行われる。第一の方法のところで説明した方法とほぼ同じ方法で、高いアスペクト比と、下に位置する能動領域に対して小さな接触面を持つ自立壁部が形成され、それによりシリコン基板上の最少のスペースを占有する。

第九の方法は、従来技術の積層型コンデンサの、電荷貯蔵ノードの形成プロセスと比較すると、マスク処理作業および材料蒸着作業を行う必要がなく、それにより集積回路製造プロセスの処理能力が増大するので有利である。そのため、集積回路製造プロセスが簡単になり、歩留まりが改善され、コストが下がる。第九の方法は、また比較的大きな整合プロセス・ウインドウを持ち、さらに歩留まりが改善し、製造中の集積回路の大きさを容易にさらに小さくすることができる。

本発明の第10の方法は、相互接続構造体を形成するために、第二の方法のイオン注入を受けていないシリコンを含む材料のに対して選択的な、エッチング・プロセスを使用する。この実施形態の場合、シリコン導電材料の層は、ポリシリコン層を含む。このポリシリコン層は、好適には、真性のポリシリコンから作ることが好ましい。第10の方法の場合、最初に、半導体基板上に能動領域およびゲート構造体が形成される。その後で、軽度にドーピングされたポリシリコン層、または全然ドーピングされていないポリシリコン層が、ゲート構造体上に形成される。

ポリシリコン層が形成されると、ポリシリコン・プラグに電気的に接続される、導電性領域上に位置するポリシリコン層の一部をカバーするために、マスク被覆基板がポリシリコン層上に置かれ、パターン形成される。この実施形態の場合には、導電性領域は能動領域である。除去されるポリシリコン層の一部が、露出した状態に維持される。マスク被覆基板のパターン形成が行われた後で、マスク被覆基板の開口部を通して、異方性エッチング・プロセスが行われる。異方性エッチング・プロセスは、マスク被覆基板によりカバーされている、ポリシリコンの一部の高さを一部低くする。その後で、ポリシリコン層の露出した部分は、そのもとの高さより低くなる。

その後で、第二の方法のところで説明した方法とほぼ同じ方法で、イオン注入作業が行われる。このイオン注入作業により注入されるイオンのタイプとしては、砒素イオンがある。上記第二の方法のところで説明したように、イオン注入の後で、イオン注入を受けていないシリコンを含む材料に対して選択的なエッチング・プロセスが行われる。ここでもまた、イオン注入が行われる、ポリシリコン層の一部のプロファイルを調整するために、選択的エッチング・プロセスおよびイオン注入作業のパラメータを、適当に選択することができる。それにより、従来技術の上記方法より効率的で、合理化された方法で形成されるポリシリコン・プラグのような、相互接続構造体が形成される。

本発明の第11の方法の場合、相互接続構造体を形成するために、第一の方法のイオン注入を受けたシリコンを含む材料の層に対して選択的なエッチング・プロセス、および高さを低くする作業が行われる。第11の方法の場合には、複数の隆起した絶縁面が、最初に、半導体基板上に形成される。この実施形態の場合、隆起した絶縁面は、複数のゲート領域を含む。好適には、窒化シリコンのキャップは、複数のゲート領域の頂部に形成することが好ましい。好適には、少なくとも一つの電荷導電領域を、ゲート領域とその底部との間に形成することが好ましい。その後で、ポリシリコン層が、能動領域上およびゲート領域の間に位置する介在開放領域を充填するゲート領域の上に形成される。

第11の方法の以降の手順の場合、ポリシリコン層の高さは、好適には、平面化プロセスにより、ゲート領域の頂部の高さまで低くすることが好ましい。より好適なには、平面化プロセスが、ゲート領域上に形成された窒化シリコンのキャップの上で停止する、化学機械平面化プロセス(CMP)を含むことが好ましい。

以降の手順においては、マスク被覆基板が、ポリシリコン層およびゲート領域上に設置され、その上に相互接続構造体が形成される、能動領域を覆うポリシリコン層の一部上の開口部で、パターン形成される。マスク被覆基板内の開口部も、ゲート領域の頂部と少し重畳している。それにより、上記開口部は、マスク被覆基板の整合が少しずれても欠陥とはならない状態に自己整合する。

第一の方法のところで説明したように、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスに従って選択したタイプのイオンが、能動領域を覆うポリシリコン層の選択した部分に注入される。窒化シリコンのスペーサが、ゲート領域内へイオンが注入されるのを防止し、また自己整合を助ける。

その後で、マスク被覆基板が除去され、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスが、第一の方法のところで説明した方法とほぼ同じ方法で行われる。イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより、イオン注入を受けた能動領域を覆う選択した部分を除いて、ポリシリコン層が除去される。エッチングにより除去されない残りの選択した部分が、相互接続構造体を形成する。上記実施形態の場合には、相互接続構造体は、能動領域からゲート領域の頂部のところまで延びるポリシリコン・プラグである。

第11の方法は、従来技術のBPSGの蒸着ステップ、逆流ステップおよびエッチング・ステップ、ポリシリコン・プラグ形成プロセスを除去することにより、相互接続構造体の形成プロセスを簡単にしている。この合理化したプロセスにより、集積回路製造プロセスの処理能力が向上し、コストが安くなる。従来技術の乾式エッチング・プロセス、および高いアスペクト比の相互接続構造体の、開口部の形成に関連する問題も回避することができる。

本発明の第12の方法は、仮設相互接続構造体を形成するために、本発明のイオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセス、および窒化シリコン上で停止する平面化プロセスを使用する。さらに、第12の方法は、さらに、もっと深い相互接続構造体の開口部を形成するために、後で自己整合した相互接続構造体を除去する。

第12の方法の場合、最初に、好適には、第11の方法のところで説明した方法で、仮設相互接続構造体が形成され、もっと深い相互接続構造体の開口部を形成するために、除去することができる「ダミー」として使用される。第12の方法の場合、半導体基板面上に薄い絶縁層が形成される。もっと深い相互接続構造体の開口部を通して、電気的接触を行う電荷導電領域が、複数の隆起絶縁面の中央の薄い絶縁層の下に位置する。それ故、介在開放領域が、複数の隆起絶縁面の間の電荷導電領域の上に形成される。

その後で、仮設相互接続構造体が、電荷導電領域から隆起絶縁面の頂部へ延びる介在開放領域内に形成される。仮設相互接続構造体は、好適には、第11の方法のところで説明した方法で形成されるのが好ましい。仮設相互接続構造体が形成されると、絶縁材のブランケット層が、相互接続構造体上に形成される。

以下に説明するある実施形態の場合には、半導体基板はシリコン基板であり、電荷導電領域はソース/ドレイン領域であり、仮設相互接続構造体はポリシリコン・プラグであり、隆起絶縁面はゲート領域である。ゲート領域は、好適には、その頂部に窒化シリコンのキャップを備えることが好ましい。ソース/ドレイン領域上にポリシリコン・プラグが形成されると、絶縁材のブランケット層が、ポリシリコン・プラグの上を、ある距離離れて延びるポリシリコン・プラグ上に形成される。

その後で、相互接続構造体の開口部が、ポリシリコン・プラグの頂部まで延びる絶縁材のブランケット層を貫通して形成される。この開口部を形成する一つの方法の場合、マスク被覆基板が設置され、またパターン形成され、ポリシリコンに対して選択的な絶縁材のブランケット層の材料をエッチングする、エッチング・プロセスが実行される。自己整合によりポリシリコン・プラグを形成するために、好適には、エッチング・プロセスが、ゲート領域の頂部のところの窒化シリコンに対して選択的であることが好ましい。相互接続構造体の開口部は、ゲート領域の頂部のところの窒化シリコンのキャップが、エッチング・プロセスがゲート領域にまで及ぶのを防止するように、ポリシリコン・プラグの幅より広く形成することができる。従って、相互接続構造体の開口部の整合のズレを考慮して、、ゲート構造体のほぼ半分の公差が見込まれる。

その後で、下に位置するソース/ドレイン領域を露出させるために、ポリシリコン・プラグが除去される。好適には、ポリシリコンを選択的にエッチングし、絶縁材の層またはゲート領域のキャップの材料を、エッチングしないエッチング・プロセスにより、ポリシリコン・プラグを除去することが好ましい。エッチング・プロセスはまた、好適には、薄い絶縁層がエッチング・バリアとして機能することができ、下に位置するソース/ドレイン領域を過度にエッチングしないように、薄い絶縁層の材料に対して選択的なものであることが好ましい。上記エッチング・プロセスのあるものは、TMAH湿式エッチングを含むエッチング液を使用する。TMAH湿式エッチング液は、絶縁材のブランケット層およびゲート領域の頂部のところの、窒化シリコン・キャップに対して選択的にポリシリコン・プラグを除去する。

ポリシリコン・プラグが除去されると、もっと深い自己整合相互接続構造体の開口部が、ポリシリコン・プラグの位置に形成され、ソース/ドレイン領域から絶縁材のブランケット層の頂部に延びる。ある実施形態の場合には、アルミニウムの接点を形成するために、もっと深い相互接続構造体の開口部は、アルミニウムにより充填される。もっと深い相互接続構造体は、積層型コンデンサを形成する際には特に役に立つ。その場合には、積層型コンデンサのベースを、積層型コンデンサの電荷貯蔵ノードと、一体にすることが好ましい。積層型コンデンサを電荷貯蔵ノードと一体に形成した場合、従来技術のポリシリコン・プラグが一体になっていない積層型コンデンサのと比較すると、セルの静電容量が大きくなる。

本発明の第13の方法は、大きな表面積を持つ積層型コンデンサの、電荷貯蔵ノードを形成するために、第一の方法のイオン注入を受けた、シリコンを含む材料に対して選択的な、エッチング・プロセスを使用する。第13の方法の場合、最初に、平面化された下部絶縁層を貫通して、半導体基板上の電荷導電領域に延びる、相互接続構造体が形成される。相互接続構造体は、好適には、第11の方法のところで説明した方法で形成することが好ましい。その場合、半導体ウエハのシリコン基板上の一組のゲート領域の間の、能動領域まで延びるポリシリコン・プラグが形成される。

ポリシリコン・プラグが形成されると、上部絶縁層が、ポリシリコン・プラグおよびゲート領域上に蒸着される。その後で、上部絶縁層が平面化され、開口部が、ゲート領域の頂部上に位置する窒化シリコンのスペーサの頂部まで延びる、上部絶縁層に形成される。上記開口部は、窒化シリコンのスペーサに重畳し、開口部はゲート領域の間に位置するポリシリコン・プラグと自己整合することができる。上記開口部は、またポリシリコン・プラグの頂部を露出する。開口部は、好適には、円形であって、水平な底部と垂直な側面とを持つことが好ましい。

開口部が形成された後、下部のシリコンを含む層が、下部のシリコンを含む層をエッチングする、エッチング・プロセスを遅くする不純物で真性にドーピングされる。その場合、エッチングは、第一の方法のところで説明した、イオン注入を受けたシリコンを含む材料に対して選択的なものである。その後で、軽度にドーピングされた、または全然ドーピングされていない、中間のシリコンを含む層が下部のポリシリコン層上に形成される。その後で、上部のシリコンを含む層は、下部の絶縁層のドーピングと類似の方法でドーピングされる。下部、中間および上部の各シリコン層は、好適には、水平方向に延びる底部と、底部の縁部から上に延びる垂直方向の側面を持つことが好ましい。下部、中間および上部の各シリコンを含む層は、好適には、ポリシリコンを含むことが好ましい。

その後で、中間のシリコンを含む層の底部にイオンが注入される。このイオンの注入中に、悪影響を与えないで、下部および上部のシリコンを含む層に、イオンを注入することができる。イオン注入作業の際に使用するイオンは、好適には、基板の面に対して直角の注入角度で、選択した注入エネルギーの範囲で注入することが好ましい。選択した注入エネルギーの範囲は、開口部の面上を延びる下部側面および上部側面が、注入したイオンの中間のシリコンを含む層の側面に、注入するのを阻止するように選択される。上部シリコンを含む層の側面も、注入したイオンの上部ポリシリコン層の、側面の下に位置する中間のシリコンを含む層の底面の外縁部へのイオン注入を阻止する。従って、中間のシリコンを含む層の底部の中央部だけにイオンが注入される。

上部絶縁層の頂部上に形成された、下部、中間および上部の各シリコンを含む層の一部は、その後、平面化プロセスのような高さを低くするプロセスにより除去される。別の方法としては、イオン注入により影響を受けた中間層をさらに除去するために、過度の研摩を行うことができる。その後で、中間のポリシリコン層の、比較的イオン注入を受けていない部分を除去するために、イオン注入を受けたシリコンを含む材料に対して選択的な、エッチング・プロセスが行われる。イオン注入を受けていない、中間のシリコンを含む層の底部の中央部分は残り、一方、イオン注入を受けていない中間のシリコンを含む層の底部および側壁部の外側の縁部がエッチングにより除去される。それ故、下部および上部のポリシリコン層の側壁部全体および底部の一部は露出され、電荷貯蔵ノードの表面積が増大する。それにより、大きな表面積を持つ成形済みの構造体が形成され、積層型コンデンサの電荷貯蔵ノードとして非常に適したものになる。積層型コンデンサが完全に形成された場合、薄い誘電層が、電荷貯蔵ノード上に形成され、セル・プレートが、薄い誘電層上に形成される。

電荷貯蔵ノードが、簡単な湿式エッチング液による一回のエッチング・プロセスだけで、合理化された効率的な方法で形成される。電荷貯蔵ノードは、大きな表面積を持つが、半導体基板上において最も小さいスペースしか占有しない。

本発明の第14の方法は、第一の方法のイオン注入を受けた、シリコンを含む材料に対して選択的なエッチング・プロセスを使用し、イオン注入作業の、一組のイオン注入パラメータの選択により決定した厚さを持つ、自立壁部を含む積層型コンデンサの電荷貯蔵ノードを形成する。積層型コンデンサの電荷貯蔵ノードも形成されるが、その際表面積を増大するために、表面がざらざらに処理される。第14の方法の場合には、最初に、積層型コンデンサの電荷貯蔵ノードが接続される、半導体基板および電荷導電領域が形成される。ある実施形態の場合には、半導体基板は、半導体ウエハのシリコン基板を含み、電荷導電領域は、能動領域上に位置する能動領域を含む。好適には、一組のゲート領域を、能動領域の両側に一つずつ、シリコン基板上に形成することが好ましい。その後で、絶縁材の層が、電荷貯蔵ノードのゲート領域上でに必要な高さに対応する深さで、ゲート領域および能動領域上に形成される。

上記絶縁材料の層が形成されると、その後で、絶縁層が平面化され、電荷導電領域まで延びる開口部が絶縁層に形成される。開口部は、好適には、第13の方法で、一組のゲート領域に自己整合することが好ましい。

その後で、ポリシリコン層が開口部に形成される。ポリシリコン層は、好適には、ブランケット層であり、開口部を部分的に充填するだけの厚さに蒸着することが好ましい。ポリシリコン層の厚さは、形成される積層型コンデンサの電荷貯蔵ノードの側壁部の厚さ、およびイオン注入を受けたシリコンを含む材料の層に対して選択的なエッチング・プロセスに従って選択される。

その後で、第一の方法のところで説明した上記方法で、イオン注入プロセスが行われる。イオンは、ポリシリコン層の外側の部分に注入されるが、内側には注入されない。このような注入を行うために、イオンは、好適には、半導体ウエハの面に対して直角以外の角度で、注入することが好ましい。イオンは、またポリシリコン層を、必要な深さに注入するための、注入角度に従って選択した注入エネルギーで注入される。上記の必要な深さは、ポリシリコン層から形成される積層型コンデンサの電荷貯蔵ノードの、結果として得られる自立壁部の厚さに対応する。イオンは、第一の方法のところで説明したように、イオン注入を受けた部分の形を調整するために、各ステージ毎にイオン注入パラメータを変化させて、いくつかのステージに分けて注入することができる。

その後、開口部の残りの部分は、高さ低減プロセスを行うために、ホトレジストまたは他の適当な材料で充填される。ホトレジストまたは他の適当な材料は、開口部のポリシリコンが、高さ低減プロセスにより汚染されるのを防止する。その後で、絶縁層の頂部上を延びるポリシリコン層の一部を除去するために、高さ低減プロセスが実行される。高さ低減プロセスは、好適には、平面化プロセスであることが好ましく、さらに好適なのは、CMPプロセスを使用することである。

積層型コンデンサの電荷貯蔵ノードの表面積を増大するために、第14の方法は、このステージまたはこの後のステージで、ポリシリコン層を粗面にする。そうするためには、好適には、半球形または円筒形の粒子状のポリシリコンを、開口部のポリシリコン層上に化学蒸着法(CVD)により蒸着のが好ましい。

もう一つの手順の場合、イオン注入を受けたシリコンを含む材料の層に対して選択的なエッチング・プロセスが実行され、ポリシリコン層のイオン注入を受けていない内部が除去される。ポリシリコン層の、イオン注入を受けた外側の部分は正しい位置に残り、開口部の底部を除いて、開口部に物理的に接触しない状態で、開口部の周囲に自立壁部を形成する。この場合、自立壁部はゲート領域に接触することができ、下に位置する電荷導電領域と電気的に連絡している。好適には、開口部は円形であり、そのため自立壁部が環状になっていることが好ましい。

第14の方法において、前のステージで、自立壁部の内部が粗面に処理されていなかった場合には、この時点で、粗面にすることができる。ポリシリコン層の内面および外面の両方とも露出しているので、半球形または円筒形の粒子状のポリシリコンが、自立壁部の内面および外面の両方の上に形成される。前のステージにおいて、自立壁部面の面がを粗面になっている場合には、内面だけが粗面に処理される。従って、これ以前のステージで粗面を形成するより、後のこのステージで粗面を形成するほうが望ましい。

積層型コンデンサの電荷貯蔵ノードが形成されると、積層型コンデンサを完成するために、続いて一連の従来のプロセスが行われる。簡単に説明すると、積層型コンデンサを完成するプロセスは、電荷貯蔵ノード上での誘電層の形成、および誘電層上でのポリシリコンまたは他の電荷導電材料の層の形成を含む。

第14の方法は、それにより形成された積層型コンデンサが、より大きな表面積を持っている上に、半導体ウエハのシリコン基板上において、最少のスペースしか必要としないという利点を持つ。この方法は、簡単であり、集積回路製造プロセスの処理能力を高め、コストが安くなるような方法で実行することができる。

本発明の第15の方法は、成形済みのポリシリコンの構造体を形成するために、異なる範囲の深さ、または異なるパターンで複数回イオンを注入するとともに、第一の方法のイオン注入を受けたシリコンを含む材料の層に対して選択的なエッチング・プロセスを使用する。第15の方法の基本的な実施形態を修正した方法により形成した、いくつかの代表的な成形済みの構造体の形成方法について以下に説明する。

第15の方法の基本的な実施形態の場合には、最初に、ある量のシリコンを含む材料が供給される。この実施形態の場合には、ある量のシリコンを含む材料はシリコン層を含む。シリコン層が形成されると、イオンがポリシリコン層の第一の選択した領域に、第一の範囲の深さまで注入される。その後で、ポリシリコン層の第二の選択した領域に、第二の範囲の深さまでイオンが注入される。第二の範囲の深さへのイオン注入は、好適には、低い注入エネルギーで行い、ポリシリコン層に第一の範囲の深さより浅い深さに、注入することが好ましい。イオン注入を行った後で、イオン注入を受けていないポリシリコンを除去するために、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより、ポリシリコン層がエッチングされる。エッチング・プロセスは、第一の方法のところで説明したように行われる。

第一および第二の選択した領域は残り、成形済みの構造体を形成する。隣接する深さまでイオンが注入される他の選択した領域、または異なるプロファイルでパターン形成される他の選択した領域は、種々の形の成形済みの構造体を形成するために、第一および第二の領域に追加することができる。

ある実施形態の場合には、二つの直立部およびその間を延びる介在クロスバーを形成するために、ポリシリコン層の領域を注入することにより、自立壁部のブリッジが形成される。自立ブリッジは、異なる高さの複数のクロスバーで形成することができる。複数のクロスバー自立壁部ブリッジは、溶断可能なヒューズとして使用するのに適していて、プログラマブル読出し専用メモリ(PROM)を形成する際に使用することができる。

一本の直立部、およびこの直立部に一体に取り付けられている、クロスバーを形成することにより、マイクロマシンを形成する際に使用するのに適している、レバーを形成することができる。電気的に相互に接触していない、重畳しいているクロスバーも、形成することができる。

他の実施形態の場合には、その底部の全長を貫通している、一体に形成されたトンネルを含むポリシリコン・ブロックが形成される。ポリシリコン・ブロックは、乾式エッチング・プロセスにより成形され、形成される。トンネルは、残るポリシリコン・ブロックの一部を注入することにより形成され、比較的軽度なイオン注入が行われた部分が、エッチングにより選択的に除去される。

他の実施形態の場合には、ポリシリコン層の面から、ポリシリコン層の面の下まで延びるトンネルが形成される。トンネルの周囲に位置するポリシリコン層の一部は酸化され、トンネル内に金属が蒸着され、その結果、導電性相互接続ラインが、いま酸化したポリシリコン層の面の下を延びることになる。

第15の方法を使用すれば、効率的な方法で、種々様々の導電性の成形済みの構造体を形成することができる。それにより、結果として得られる集積回路の機能を増大することができる。第15の方法による成形済みの構造体は、最も少ない回数の材料蒸着、マスク処理およびエッチング作業により形成される。その後で、最短の集積回路製造プロセス時間で、成形済みの構造体が効率的に形成される。

本発明の第16の方法は、半導体基板にボトルの形のトレンチを形成するために、第一の方法のイオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスを使用する。ボトルの形のトレンチは、トレンチ・コンデンサを形成する際に、またトレンチ絶縁領域を形成する際に役に立つ。

第16の方法の場合には、最初に、半導体基板上のある量のシリコンを含む材料に、実質的に異方性のトレンチが形成される。下記のある実施形態の場合には、シリコンを含む材料の量はシリコン基板であり、シリコン基板は半導体ウエハである。それ故、この実施形態の場合には、シリコン基板が供給され、シリコン基板上にマスク被覆基板が設置される。ある実施形態の場合には、マスク被覆基板はホトレジスト・マスクであり、トレンチのとちらかの側面上に形成されたゲート領域に自己整合する。その後で、イオンがトレンチ内に注入される。好適には、イオンは、シリコン基板の面に対して直角以外の角度で、注入することが好ましい。注入角度は、イオンがトレンチの頂部ではなく、主としてトレンチの底部の方向に向くように選択される。従って、トレンチの頂部より、トレンチの底部に多くのイオンが注入される。

選択したタイプのイオンが注入されないシリコンを含む材料に対して選択的なエッチング・プロセスが、第二の方法のところで説明した方法とほぼ同じ方法で実行される。それにより、トレンチのイオン注入を受けた部分から材料が除去され、トレンチの底部がトレンチの頂部より広がり、トレンチのボトルの形になる。ボトルの形のトレンチは、トレンチ・コンデンサおよびトレンチ絶縁領域の形成を含む、種々の用途に使用することができる。

トレンチ・コンデンサを形成する場合には、トレンチ・コンデンサを完成するために、電荷貯蔵ノードがトレンチ内に蒸着され、その後で誘電層および上部コンデンサ・プレートが蒸着される。トレンチ絶縁領域を形成する場合には、ボトルの形のトレンチが、絶縁材料により充填される。絶縁材料は、最初、トレンチの側壁部上に酸化シリコンの層を成長させ、その後で、トレンチの残りの部分に絶縁材料を、蒸着させることにより形成することができる。

それ故、従来の形のトレンチを形成した場合には、より広い表面積を持つトレンチ・コンデンサが形成される。シリコン基板の占有面積はいままでと同じで、表面積をより広くすることができる。このより広い表面積は、簡単で効率的な方法で達成することができる。同様に、容積の大きいトレンチ絶縁領域が形成され、そのためシリコン基板の表面積を広く占有しないでも、高い絶縁性能が得られる。容積が大きいために、半導体装置の密度および小型化を犠牲にしないで、クロストーク電流漏洩に対する抵抗が高くなる。

本発明の第17の方法は、第一の方法のイオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスを使用する。この第17の方法は、半導体基板の一つまたはそれ以上の露出した各水平面上に、シリコンを含む材料の領域を形成する。一方、露出した垂直面上のどちらにも、シリコンを含む材料の領域は形成しない。

第17の方法の場合は、最初に、その上に露出した水平面および露出した垂直面を持つ、突出構造体が位置する半導体基板が供給される。突出構造体は、例えば、半導体ウエハのシリコン基板上のゲート領域であってもよい。

シリコンを含む材料の層が、露出した水平面および露出した垂直面上に形成される。以下に説明するある実施形態の場合には、シリコンを含む材料の層は、ポリシリコン層である。好適には、ポリシリコン層は真性ポリシリコンであることが好ましい。

イオンは、第一の方法のところで説明したように、イオン注入を受けたポリシリコンに対して選択的な、エッチング・プロセスにより選択したタイプのものである。イオンは、第一の実施形態のところで説明したように、イオンが注入されたポリシリコンに対して選択的なエッチング・プロセスにより選択したタイプのイオンである。イオンは、好適には、露出した水平面に対して直角な注入角度で注入することが好ましい。

直角にイオンを注入すると、露出した水平面上に位置するポリシリコン層の一部が、イオンと一緒に注入されるが、露出した垂直面上に位置するポリシリコン層の一部には、イオンは実質的に注入されない。

以降の手順において、第一の方法のところで説明した、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスが行われる。それ故、露出した垂直面上に位置していて、イオンが注入されなかったポリシリコン層の一部が、エッチングにより除去される。露出した水平面上に位置していて、そのためイオンの注入を受けなかったポリシリコン層の一部は残留する。

第17の方法は、いくつかの用途に使用することができる。ある用途の場合には、垂直に突出している主要部分は、MOSトランジスタのゲート領域であり、ポリシリコン領域が、突き抜け保護を行うために、ハロ注入のための注入マスクとして使用するために、ゲート領域の水平面上に形成される。

他の実施形態の場合には、相互接続ラインとして使用するために、ポリシリコン領域が水平面の上に形成される。相互接続ラインを形成する場合には、相互接続ラインの突出主要部分を絶縁材から形成することができる。従って、それと電気的に接続していない、突出主要部分の頂部の両側に形成されたポリシリコン領域は、個々の相互接続ラインを形成するために使用することができる。上記の突出主要部分は、既存の相互接続ライン、またはゲート領域であってもよいし、その上に突出主要部分の頂部上に位置する、ポリシリコンの領域から、突出主要部分を電気的に絶縁するための絶縁層を持つことができる。それ故、突出主要部分上に位置するポリシリコンの領域および突出主要部分は、それぞれ、別々の相互接続ラインを形成することができる。

相互接続ライン、または他の上記導電性の成形済みの構造体を形成する場合には、水平面上に形成されたポリシリコン領域を、その導電率を増大させるために、耐火性のケイ化金属に変換することができる。この変換を行っている間に、チタンのような耐火性の金属が、通常ブランケット層として、ポリシリコンの領域上に蒸着される。その後で、ポリシリコンの露出した領域を耐火性の金属と反応させるために、熱処理が行われる。その後で、反応していない耐火性の金属の一部は、耐火性の金属のケイ化物に対して選択的な、耐火性の金属をエッチングする適当なエッチング・プロセスにより、除去することができる。耐火性のケイ化金属が、露出した水平面上のポリシリコン領域の場所に残留する。

相互接続ラインおよびハロ・マスク注入が、現在のプロセスの流れと互換性を持つ簡単で効率的な方法で、それぞれ形成される。相互接続ラインは、高い密度で近接した状態で、形成することができ、ハロ注入マスクは、正確に、また非常に小型のトランジスタで役に立つ、適当な大きさの開口部とともに形成することができる。

本発明の第18の方法は、第一の方法の、イオン注入を受けたシリコンを含む材料に対して選択的な、エッチング・プロセスを使用する。第18の方法は、相互接続ラインを、もっと大きな構造体に電気的に接続するための、もっと幅の広い領域に一体に接続している、狭い相互接続ラインを形成する。狭い相互接続ラインは、写真製版の解像度より高い解像度の幅で形成することができる。

第18の方法の場合は、最初に、例えば、以下に説明する実施形態の場合には、半導体基板上のポリシリコン層である、シリコンを含む材料の層が形成される。ポリシリコン層は、好適には、真性ポリシリコンから形成することが好ましい。ポリシリコン層が蒸着されると、マスク被覆基板が設置され、そこを通して、ポリシリコン層の選択した領域が、イオンと一緒に注入される、開口部によりパターン形成される。選択した領域は、形成された相互接続ラインを、相互接続ラインより幅の広い構造体に接続するために使用される。

マスク被覆基板が設置された後で、第一のイオン注入プロセスが実行され、このプロセス中に、選択した領域が、第一の方法のところで説明したように、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより選択した、選択したタイプのイオンと一緒に注入される。その後で、マスク被覆基板が除去され、第二のマスク被覆基板が、ポリシリコン層の上に置かれ、選択した表面の形を持つようにパターン形成される。その外周部は、相互接続ラインの必要な位置と一致する。その後で、ポリシリコン層を、異方性に従ってエッチングした側壁部および選択した面の形の周囲を持つ、ポリシリコンのブロックにするために、乾式エッチング・プロセスまたは同等の材料除去プロセスが行われる。選択した領域は、好適には、ポリシリコンのブロックの近くに位置することが好ましい。

第二のマスク被覆基板が正しい位置に置かれている間に、第二のイオン注入プロセスにより、ポリシリコンのブロックの一つまたはそれ以上の横方向に延びる面に、イオンが注入される。このイオンは、第一の方法のところで説明したように、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより選択したタイプのものである。第二のイオン注入プロセスのイオンは、第一のイオンプロセスのイオンと同じタイプのものでもよいし、異なるタイプのものでもよい。第二のイオン注入プロセスのイオンは、その注入イオンに対して選択した角度およびエネルギーで、ポリシリコンのブロックの横方向に延びる面に、選択した深さまで注入される。上記の選択した深さは、完成した相互接続ラインの太さに対応する。イオン注入角度は、本質的には、第一の方法および第六の方法のところで説明した注入角度である。

イオン注入が行われた後で、第一の方法のところで説明した方法とほぼ同じ方法で、イオン注入を受けたシリコンを含む材料に対して選択的な、エッチング・プロセスが行われる。その結果、ポリシリコンのブロックの、イオン注入を受けていないポリシリコンが、エッチングにより除去され、イオン注入を受けたポリシリコンが残留する。それ故、一つまたはそれ以上の側壁部のイオン注入を受けた領域が、選択した領域のように残留する。ポリシリコン層の選択した領域は、接触パッドを形成し、相互接続ラインに一体に接続される。もちろん、相互接続ライン上に一つ以上の接触パッドを形成することができ、一つ以上の相互接続ラインを形成することができる。

ポリシリコンのブロックを、相互接続ラインに形成されたギャップにより分離されている、二つまたはそれ以上の個々の相互接続ラインに分割するため、ポリシリコンのブロックの全周囲にイオンを注入することができる。ある実施形態の場合には、上記ギャップは、ポリシリコンのブロックの外側の周囲に近接している、仮設スペーサ・ブロックにより形成される。犠牲スペーサ・ブロックは、第二のイオン注入動作の前に形成されるが、好適には、ポリシリコンのブロックのパターン形成の時および形成の前に形成するのが好ましい。仮設スペーサ・ブロックは、注入されたイオンを吸収し、注入されたイオンが、ポリシリコン・ブロックの側壁部のセグメントに、注入されるのを防止する。従って、開口部が、イオン注入を受けていなかったセグメントの位置に形成され、結果として得られる相互接続ラインにギャップができる。別の方法としては、相互接続ラインが形成されてから行われる、別々のマスク処理手順およびエッチング手順により開口部を形成することができる。

第18の方法により形成された相互接続ラインは、写真製版によってではなく、イオン注入角度およびイオン注入エネルギーにより決まる形を持ち、従って、従来の写真製版プロセスによる幅よりも狭い幅を持つことができる。第18の方法による相互接続ラインは、また、相互接続ラインをもっと大きい構造体に接続するための、相互接続ラインより幅の広い一体た型構造体により形成される。従って、半導体装置または半導体装置の主要部分に容易に接続することができるという柔軟性を保持しながら、相互接続ラインを非常に狭くすることができる。さらに、もっと細い相互接続ラインを、ゲート領域として使用することができ、そのように使用した場合、チャネルの長さが短くなる。チャネルの長さが短くなると、MOSトランジスタのしきい値電圧をもっと低くすることができ、その結果、速度がもっと速くなる。

本発明のこれらおよび他の特徴は、以下に説明および添付の請求の範囲を読めば、さらによりよく理解することができるだろうし、以下の本発明の実施形態により理解することができるだろう。

【図面の簡単な説明】

本発明の上記および他の利点が得られる方法を理解してもらうために、上記の簡単な本発明のもっと詳細な説明を、添付の図面に示す特定の実施形態を参照しながら行う。これらの図面は、本発明の通常の実施形態を説明するためのものであって、それ故、本発明の範囲を制限するものでないことを理解してほしい。本発明を、添付の図面を使用してさらに明確に詳細に記述し、説明する。

図1は、本発明の第一の方法の最初の手順における、マスク被覆基板によりパターン形成される、その上に形成されたポリシリコン層を持つ半導体ウエハの横断面図である。

図2は、図1のポリシリコン層の、マスクされていない部分にイオンが注入される、本発明の第一の方法のもう一つの手順を示す、図1の半導体ウエハの横断面図である。

図3は、図2のポリシリコン層のマスクされた部分の、縁部の下の濃度が変化する、複数のイオン注入ステージにおいて注入されたイオンの貫通パターンの深さを示すグラフである。

図4は、図3のポリシリコン層から除去されるマスク被覆基板の、本発明の第一の方法のある手順を示す、図3の半導体ウエハの横断面図である。

図5は、任意のユニットの注入イオン濃度の関数としての、本発明のイオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスのエッチング速度の関係を示すグラフである。

図6は、その内部に成形済みの開口部を形成するために、ポリシリコン層の比較的イオン注入を受けていない部分が除去される、本発明の第一の方法の他の手順を示す図4の半導体ウエハの横断面図である。

図7は、下に位置する層に、類似の大きさの成形済みの開口部を形成するために、図6の成形済みの開口部を含むポリシリコン層が使用される、図1−図6の方法の他の実施形態で使用される手順を示す、図1−図5の半導体ウエハの横断面図である。

図8は、図7の下に位置する層が、図7の成形済みの開口部により、ハードマスクとしてエッチングされる、図7の実施形態の他の手順を示す、図7の半導体ウエハの横断面図である。

図9は、図8の成形済みの開口部に形成されたプログラマブル抵抗のカルコゲニド材料を示す、図8の半導体ウエハの横断面図である。

図10は、半導体基板上にポリシリコン層が形成される、本発明の第二の方法のある手順を示す、半導体ウエハの横断面図である。

図11は、図10のポリシリコン層の上にマスク被覆基板が形成される、本発明の第二の方法の他の手順を示す、図10の半導体ウエハの横断面図である。

図12は、図11のポリシリコン層にイオンが注入される、本発明の第二の方法のもう一つの手順を示す、図11の半導体ウエハの横断面図である。

図13は、図12のポリシリコン層を異方性に従ってエッチングする、第一のエッチング・プロセスが行われる、本発明の第二の方法の他の手順を示す、図12の半導体ウエハの横断面図である。

図14は、成形済みの構造体を形成するために、イオン注入を受けていないシリコンを含む材料に、ポリシリコン層を異方性に従って、また選択的にエッチングする、第二のエッチング・プロセスを行う、本発明の第二の方法の他の手順を示す、図13の半導体ウエハの横断面図である。

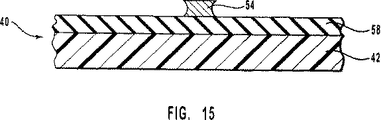

図15は、下に位置する層が形成され、その上に図14の成形済みの構造体が形成される、本発明の第二の方法の一実施形態のある手順を示す、図14の半導体ウエハの横断面図である。

図16は、図15の下に位置する層をエッチングするために、図15の成形済みの構造体が、ハードマスクとして使用される、第二の方法の他の手順を示す、図15の半導体ウエハの横断面図である。

図17は、酸化物の層が、図14の成形済みの構造体上に形成される、第二の方法の他の手順を示す、図14の半導体ウエハの横断面図である。

図18は、酸化物の層に成形済みの主要部分を残して、図17の酸化物の層が平面化される第二の方法の他の手順を示す、図17の半導体ウエハの横断面図である。

図19は、酸化物の層にパターン形成された開口部を残して、図18の成形済みの主要部分がエッチングにより除去される、図18の実施形態の他の手順を示す、図18の半導体ウエハの横断面図である。

図20は、複数のゲート領域の間に複数の能動領域が形成される、本発明の第三の方法の手順を示す、半導体ウエハの横断面図である。

図21は、ポリシリコン層が図20の能動領域上に形成される、本発明の第三の方法の他の手順を示す、図20の半導体ウエハの横断面図である。

図22は、図21のポリシリコン層上にハードマスクが形成され、また図21のポリシリコン層の露出した部分にイオンが注入される、第三の方法の他の手順を示す、図21の半導体ウエハの横断面図である。

図23は、イオンが注入されたリコンを含む材料に対して選択的であり、その結果図22の能動領域上に複数のポリシリコン・プラグが形成される、第三の方法の他の手順を示す、図22の半導体ウエハの横断面図である。

図24は、スペーサが、図22の能動領域上の、図22のハードマスクの開口部の内縁部上に形成され、その場合、図22のポリシリコン層にイオンが注入される、本発明の第四の方法の最初の手順を示す、半導体ウエハの横断面図である。

図25は、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスが行われ、その結果、電荷貯蔵ノードおよびポリシリコン・プラグが形成される、第四の方法の他の手順を示す半導体ウエハの横断面図である。

図26は、複数のゲート領域を形成するために、一連のCMOSプロセスが行われ、複数のゲート領域上に絶縁層が形成される、本発明の第五の方法の最初の手順を示す半導体ウエハの横断面図である。

図27は、半導体ウエハのPMOS部分がマスクされ、半導体ウエハのNMOS部分にイオンが注入される、本発明の第五の方法の他の手順を示す、図26の半導体ウエハの横断面図である。

図28は、図27の構造体上にポリシリコン層が形成され、その上でハードマスク層が形成およびパターン形成され、ポリシリコン層の露出した部分にイオンが注入される、本発明の第五の方法の他の手順を示す、図27の半導体ウエハの横断面図である。

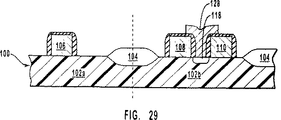

図29は、ポリシリコン・プラグを形成するために、図28のハードマスクが除去され、図28のポリシリコン層が、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスにより除去される、本発明の第五の方法の他の手順を示す、図28の半導体ウエハの横断面図である。

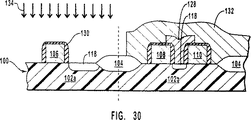

図30は、半導体ウエハのNMOS部分がマスクされ、半導体ウエハのPMOS部分にイオンが注入される、本発明の第五の方法の他の手順を示す、図29の半導体ウエハの横断面図である。

図31は、ポリシリコン層が、マスク被覆基板のアイランドによりパターン形成される、本発明の第六の方法の最初の手順を示す半導体ウエハの横断面図である。

図32は、ポリシリコン・ブロックを形成するために、ポリシリコン層が異方性に従ってエッチングされ、ポリシリコン・ブロックの側壁部にイオンが注入される第六の方法の他の手順を示す、図31の半導体ウエハの横断面図である。

図33は、図32のイオン注入作業により形成されたイオン濃度のプロファイルを示す、図32のポリシリコン・ブロックの拡大横断面図である。

図34は、複数の自立壁部を形成するために、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスを行う第六の方法の他の手順を示す、図31の半導体ウエハの横断面図である。

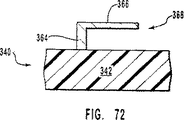

図35は、マスク被覆基板が、ポリシリコン層上に形成され、極細線で示す円形開口部と一緒にパターン形成される、本発明の第七の方法の最初の手順を示す半導体ウエハの斜視図である。

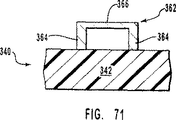

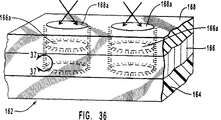

図36は、ポリシリコン層に一組の円形の開口部を形成するために、図35のポリシリコン層が異方性に従ってエッチングされ、極細線で示す円い開口部の側壁部にイオンが注入される第七の方法の他の手順を示す、図35の半導体ウエハの斜視図である。

図37は、図35のイオン注入作業により形成された、イオン濃度プロファイルを示す、図36のポリシリコン・ブロックの拡大横断面図である。

図38は、一組の環状自立壁部を形成するために、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスが行われる第七の方法の他の手順を示す、図36の半導体ウエハの斜視図である。

図39は、円錐形の側壁部を持つ、MOSサラウンド・ゲート・トランジスタが形成し、MOSサラウンド・ゲート・トランジスタの、ドーピングされたソース/ドレイン領域を形成するためにイオンが注入される、本発明の第八の方法の最初の手順を示す半導体ウエハの横断面図である。

図40は、その上の完成したMOSサラウンド・ゲート・トランジスタを示す、図39の半導体ウエハの横断面図である。

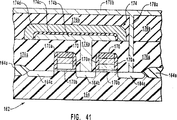

図41は、図40のMOSサラウンド・ゲート・トランジスタを内蔵するメモリ・セルを形成する際に使用される、図40の半導体ウエハの横断面図である。

図42は、一連のゲート構造体が半導体ウエハ上に形成され、ポリシリコン層および窒化シリコン層で覆われる、本発明の第九の方法の最初の手順を示す半導体ウエハの横断面図である。

図43は、図42の窒化シリコンおよびポリシリコン層を貫通して、円錐形の開口部がエッチングにより形成される、本発明の第九の方法の他の手順を示す、図42の半導体ウエハの横断面図である。

図44は、第二のポリシリコン層が蒸着され、その中にイオンが注入される、本発明の第九の方法の他の手順を示す、図43の半導体ウエハの横断面図である。

図45は、一組の小さな表面積のポリシリコン・コンデンサの電荷貯蔵ノードを形成するために、イオン注入を受けたシリコンを含む材料に対して選択的なエッチング・プロセスを行う、本発明の第九の方法の他の手順を示す、図44の半導体ウエハの横断面図である。

図46は、半導体ウエハ上に、一組のゲート領域および介在能動領域が形成され、その場合、ポリシリコン層がその上に形成される、本発明の第10の方法の最初の手順を示す半導体ウエハの横断面図である。

図47は、図46の能動領域上に、マスク被覆基板が形成され、パターン形成される、本発明の第10の方法の他の手順を示す、図46の半導体ウエハの横断面図である。

図48は、ポリシリコン層の露出した領域が、部分的にエッチングされ、その場合、ポリシリコン層の部分的にエッチングされた露出領域にイオンが注入される、本発明の第10の方法の他の手順を示す、図47の半導体ウエハの横断面図である。

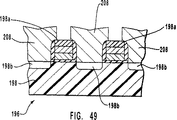

図49は、ポリシリコン・プラグを形成するために、イオンが注入されていないポリシリコンに対して選択的なエッチング・プロセスが行われる、本発明の第10の方法の他の手順を示す半導体ウエハの横断面図である。

図50は、複数のゲート領域および介在能動領域が半導体ウエハ上に形成され、ポリシリコン層がその上に形成される、本発明の第11の方法の最初の手順を示す半導体ウエハの横断面図である。

図51は、図50のポリシリコン層が、図50のゲート領域のレベルまで平面化される、本発明の第11の方法の他の手順を示す、図50の半導体ウエハの断面図である。

図52は、図51のポリシリコン層上に絶縁層が形成され、絶縁層に開口部が形成され、絶縁層の開口部の下の図51のゲート領域の間のポリシリコン領域にイオンが注入される第11の方法の他の手順を示す、図51の半導体ウエハの横断面図である。

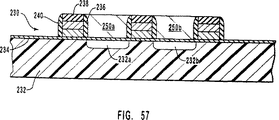

図53は、一組のポリシリコン・プラグを形成するために、イオンが注入されたシリコンを含む材料に対して選択的なエッチング・プロセスにより、絶縁層が除去され、ポリシリコン層がエッチングされる、本発明の第11の方法の他の手順を示す、図52の半導体ウエハの横断面図である。

図54は、半導体ウエハ上に、一組のゲート領域および介在能動領域が形成され、その上にポリシリコン層が形成される、本発明の第12の方法の最初の手順を示す半導体ウエハの横断面図である。

図55は、図54のポリシリコン層が、図54のゲート領域の頂部のレベルまで平面化される、本発明の第12の方法の他の手順を示す、図54の半導体ウエハの横断面図である。

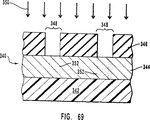

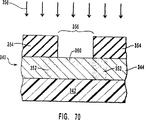

図56は、図55のポリシリコン層の上に絶縁層が形成され、絶縁層に開口部が形成され、絶縁層の開口部の下のゲート領域の間のポリシリコン領域にイオンが注入される、本発明の第12の方法の他の手順を示す、図55の半導体ウエハの横断面図である。