CN100409087C - Tft矩阵基底以及有源矩阵寻址液晶显示器件 - Google Patents

Tft矩阵基底以及有源矩阵寻址液晶显示器件 Download PDFInfo

- Publication number

- CN100409087C CN100409087C CNB021277796A CN02127779A CN100409087C CN 100409087 C CN100409087 C CN 100409087C CN B021277796 A CNB021277796 A CN B021277796A CN 02127779 A CN02127779 A CN 02127779A CN 100409087 C CN100409087 C CN 100409087C

- Authority

- CN

- China

- Prior art keywords

- tft

- light shield

- layer

- shield layer

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 150

- 239000011159 matrix material Substances 0.000 claims abstract description 193

- 230000008033 biological extinction Effects 0.000 claims description 17

- 239000012535 impurity Substances 0.000 claims description 14

- 239000000463 material Substances 0.000 claims description 13

- 229910052710 silicon Inorganic materials 0.000 claims description 13

- 239000010703 silicon Substances 0.000 claims description 13

- 239000004973 liquid crystal related substance Substances 0.000 claims description 7

- 239000010410 layer Substances 0.000 description 538

- 239000011229 interlayer Substances 0.000 description 46

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 40

- 229920005591 polysilicon Polymers 0.000 description 39

- 230000008901 benefit Effects 0.000 description 35

- 229910021417 amorphous silicon Inorganic materials 0.000 description 32

- 229910004298 SiO 2 Inorganic materials 0.000 description 26

- 238000000034 method Methods 0.000 description 26

- 230000000694 effects Effects 0.000 description 21

- 239000012212 insulator Substances 0.000 description 17

- 238000005516 engineering process Methods 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- 238000001259 photo etching Methods 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 238000005286 illumination Methods 0.000 description 6

- 230000001902 propagating effect Effects 0.000 description 6

- 239000011651 chromium Substances 0.000 description 5

- 238000002425 crystallisation Methods 0.000 description 5

- 230000008025 crystallization Effects 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 238000005224 laser annealing Methods 0.000 description 5

- 229910021332 silicide Inorganic materials 0.000 description 5

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 239000003550 marker Substances 0.000 description 4

- 230000005855 radiation Effects 0.000 description 4

- 230000003595 spectral effect Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 230000006872 improvement Effects 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 238000010521 absorption reaction Methods 0.000 description 2

- 239000004411 aluminium Substances 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000033228 biological regulation Effects 0.000 description 2

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 230000001105 regulatory effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000002210 silicon-based material Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 230000009897 systematic effect Effects 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000003760 hair shine Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012774 insulation material Substances 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000005389 semiconductor device fabrication Methods 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78633—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device with a light shield

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136209—Light shielding layers, e.g. black matrix, incorporated in the active matrix substrate, e.g. structurally associated with the switching element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

Abstract

提供了一种TFT矩阵基底,它有效地阻挡了朝向TFT的有源层传播的光。具有图案的第一遮光层以这样一种方式形成于一个透明板和TFT之间,以便与TFT的有源层相重叠。形成具有图案的第三遮光层,以便覆盖相对于TFT来说是位于所述板的对侧上的TFT。第三遮光层具有沿着所述矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分。具有图案的第二遮光层形成于所述第一遮光层和TFT之间。第二遮光层具有吸光特性,它会吸收进入所述基底内侧的光。可以在TFT和第三遮光层之间,额外提供一个形成图案的、具有吸光特性第四遮光层。

Description

技术领域

本发明一般涉及液晶显示(LCD)器件。特别是,本发明涉及薄膜晶体管(TET)以矩阵阵列的形式排列于其上的一种基底,即TFT矩阵基底,以及装配有该基底的一种有源矩阵寻址LCD器件。最好将这种基底和设备用于投影型显示器件的照明灯泡。

背景技术

近年来,开发了适用于壁挂式电视(TV)、投影型TV或办公自动化(OA)设备的各种的显示器件。为实现用于OA设备或高清晰度电视(HDTV)等高等级显示器件,日益希望在传统的显示器件中,使用将TFT用作其开关元件的有源矩阵寻址LCD器件。这是因为有源矩阵LCD器件具有一个优点:即便扫描线的数目增加,其对比度以及响应速度也不会降低。此外,有源矩阵LCD器件还具有另一个优点:如果将它们用作投影型显示器件的照明灯泡,则很容易实现大尺寸显示屏。

对于专用于照明灯泡的LCD器件,一般来说,高亮度光从光源输入LCD器件中,之后,依据图象信息,对这样输入的光进行控制,同时,光穿过同一设备。换言之,在驱动TFT的同时,通过将电场施加到各个像素上来改变各个像素的透射率,从而调节穿透该设备的光的强度。之后,利用包含专用透镜的投影光系统,将穿过该器件的光放大,并投射到大屏幕上。

光源位于LCD器件对置基底侧上,而投影光系统位于TFT矩阵基底一侧。这样,不仅仅是从光源发射出的光,而且由投影光系统反射回的光也将进入该器件。

对于有源矩阵寻址LCD器件来说,象非晶硅或多晶硅这样的一个半导体层(即一个半导体层)被用于每一个TFT的有源层。如果光照射到有源层上,则由于光学激励而会引起电流泄漏。另一方面,如前所述,高亮度光被输LCD器件,用于照明灯泡,这样,电流泄漏将变大。由于除了来自光源的光之外,由投影光系统反射回的光也照射到有源层上,电流泄漏很可能变大。

近年来,有一种趋势,即投影型LCD器件被设计得越来越紧凑,并具有较高的亮度。这样,输入到器件内的光的亮度变得越来越高。从这一点来看,有关电流泄漏的上述问题将变得更加严重。为解决这一问题,利用已有的有源矩阵寻址LCD器件,用作照明灯泡,需要提供遮光层,以防止光照射到TFT的有源层上。

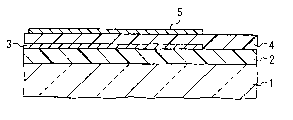

图1和图2A和2B示出了这种类型的已有LCD器件的TFT矩阵基底100的示意性结构,其中,为简便起见,仅仅示出了一个像素。图1是基底100的部分平面图,图2A是沿着图1中的线IIA-IIA的剖面图,图2B是沿着图1中的线IIB-IIB的剖面图。由于所有像素都具有相同的结构,所以,这些图仅仅示出了这些像素中的一个。

已有的TFT矩阵基底100包括一个透明板101,其上以矩阵阵列的形式排列有TFT 131。由硅化钨(WSi2)构成的底部的遮光层103,借助于二氧化硅(SiO2)层102形成于板101之上。底部遮光层103的平面形状类似于格子(lattice),它是由沿着TFT 131的矩阵的行(图1中的X方向)延伸的横向条、以及沿着其列(图1中的Y方向)延伸并与横向条相交的垂直条构成的。完整的层103被覆盖在其上的一个SiO2层104所覆盖。

用作TFT 131的有源层的、形成图案的多晶硅层107,形成于SiO2层104上。每个层107都具有一个形状类似于L的平面。

每一个多晶硅有源层107都包含一个无掺杂的沟道区107c、两个轻微掺杂的LDD(轻微掺杂的漏极)区107b和107d,一个重掺杂源极区107a以及一个重掺杂漏极区107e。源极和漏极区107a和107e位于沟道107c的每一侧。LDD区107b位于源极区107a和沟道区107c之间。LDD区107d位于沟道区107c和漏极区107e之间。

源极区107a、LDD区107b、沟道区107c、LDD区107d以及漏极区107e以这样一种方式沿着Y方向排列,以便与底部折光层103相重叠。漏极区107e的一部分沿着X方向延伸。

栅极绝缘层108形成于SiO2层104上,以覆盖位于下部的有源层107。

由掺杂有杂质的多晶硅或硅化物构成的栅极线109,形成于栅极绝缘层108上。这些线109彼此平行,并沿着X方向延伸。对线109中的每一条进行放置,使其能覆盖属于矩阵同一行的TFT 131的沟道区107C。部分线109刚好位于作为相应的TFT 131的栅极的区107c的上面。线109完全由第一夹层绝缘层110所覆盖。

由铝(AL)制成的数据线111,形成于第一夹层绝缘层110上。这些线111彼此平行,并沿着Y方向延伸。对线111的每一条进行放置,使其与属于矩阵同一列的TFT 131的有源层107重叠。线111完全覆盖了相应的TFT 131的源极区107a、沟道区107c以及LDD区107b和107d。线111覆盖了相应的TFT 131的部分漏极区107e。通过贯通第一夹层绝缘层110和栅极绝缘层108的接触孔121,线111与属于矩阵同一行的TFT 131的源极区107a进行机械连接以及电气连接。线111完全由第二夹层绝缘层112所覆盖。

由铬(Cr)构成的形成有图案的黑底层113,形成于第二夹层绝缘层112上。层113的平面形状类似于格子,它是由沿着矩阵的行(图1中的X方向)延伸的横向条、以及沿着其列(图1中的Y方向)延伸且与横向条相交的垂直条构成的。层113形成图案,以便与栅极线109以及数据线111重叠,从而覆盖TFT 131。层113用作顶部遮光层。层113完全由第三夹层绝缘层114所覆盖。

具有一个大约为矩形平面形状的像素电极115,形成于第三夹层绝缘层114上。电极115位于由栅极线109和数据线111所确定的相应的像素区120内。通过穿透第三夹层绝缘层114、第二夹层绝缘层112、第一夹层绝缘层110以及栅极绝缘层108的接触孔122,电极115与相应的TFT 131的漏极区107e进行机械连接以及电气连接。

利用包含具有上述结构的已有TFT矩阵基底100的已有的LCD器件,一个对置基底(未示出)与基底100相耦合,以便在这两个基底之间,形成一个液晶层。从对置基底的一侧进入LCD器件的光,被黑底层(即顶部遮光层)113阻挡。从TFT矩阵基底100一侧进入的光被底部遮光层103阻挡。但是,这里有一个问题,即不能充分地防止从基底100一侧进入的光照射到TFT 131的LDD区107b和107b以及/或沟道区107c。以下,将参见图3,对这种情况进行详细说明。

如图3所示,从对置基底一侧进入LCD器件的光L101,被黑底层(即顶部遮光层)113阻挡。另一种方案是:光L101穿过基底100,而没有被底部遮光层103反射。这是由于可以为此目的,要很好地调节层113和层103的宽度以及层113和层103之间的间隔。从基底100的一侧进入LCD器件的光L102被底部遮光层103阻挡。

但是,正如可以从图3中看到的那样,从TFT矩阵基底100一侧进入LCD器件的、朝向黑底层113的光L103,被层113所反射,而转到底部遮光层103上。之后,光L103通过多次反射而穿行在层103和数据线111之间的空间中,最后,到达LDD区107b。但是,从基底100一侧进入LCD器件的、朝向数据线111的光L104,通过多次反射而穿行在层103和数据线111之间的空间中,最后,到达LDD区107b。与此相似,在经过多次反射后,光照射到LDD区107d。实际上,包含光L103和L104的各种光从基底100的一侧进入,该光照射到沟道区107c。

为避免这种问题,已经开发和公开了各种改进方案。

例如,日本未经审查的、于2000年6月公开的专利公开No.2000-180899中公开了一种LCD器件,其中底部遮光层的端部逐渐变细,从而形成一个梯形截面。在这个器件中,如果能很好地调节底部遮光层的宽度和数据线的宽度,就可以用底部遮光层来阻挡从TFT矩阵基底一侧进入LCD器件的光,这样,就防止了光线照射到沟道区。

在日本未经审查的、于2000年12月公开的专利公开No.2000-356787中公开了一种LCD器件,其中,在覆盖底部遮光层的介电层中,在靠近沟道区的位置形成空的接触孔。空接触孔中填满了引线材料。在这个器件中,填入空接触孔中的引线材料阻挡了从TFT矩阵基底一侧进入LCD器件的光,这样,就防止了光照射到沟道区。

另外,众所周知,可将黑底层放置于TFT矩阵基底上或是对置基底上。如果黑底层位于对置基底上,在TFT矩阵基底和对置基底的耦合过程中,需要事先考虑大约10μm的对齐误差(即容差),同时,还要考虑这两个基底之间的覆盖精度。结果,黑底层必须非常宽。这导致了不能增大孔径比的缺陷。

与此不同,如果黑底层位于TFT矩阵基底上,则可利用已知的半导体器件制造工艺,提高黑底层和TFT之间的对齐精度。因此,如图1、2A和2B所示,这种结构正日益成为主流。

如上所述,使用具有图1和2A到2B的已有TFT矩阵基底100的已有的LCD器件,从基底100一侧进入LCD器件的光的一部分很可能会到达LDD区107b和107d以及/或沟道区107c。这样,由光而引起的电流的泄漏增大,结果,出现了对比度下降以及图象质量不均匀的问题。

利用专利公开No.2000-180899中所公开的LCD器件,则需要形成底部遮光层的锥形端的工艺步骤。因此,存在制造工艺复杂的问题。

利用公开号No.2000-356787中所公开的LCD器件,则需要在靠近覆盖底部遮光层的绝缘层中的沟道区处,形成空的接触孔的工艺步骤,以及用引线材料填充空的接触孔的工艺步骤。因此,存在制造工艺复杂的问题,这与公开号No.200-180899中的问题相同。

此外,利用公开号No.2000-180899和2000-356787所公开的LCD器件,如果将这些器件用在用于高亮度投影型显示器件的照明灯泡上,很难有效及充分地对朝向TFT的有源层传播的光进行阻挡。

发明内容

因此,本发明的一个目的是提供一种TFT矩阵基底以及一种LCD器件,它能有效阻挡朝向TFT的有源层传播的光。

本发明的另一个目的是提供一种TFT矩阵基底以及一种LCD器件,它能抑制TFT内的由光而引起的电流的泄漏。

本发明的另一个目的是提供一个TFT矩阵基底以及一种LCD器件,它能改善图象质量的对比度以及均匀性。

本发明的另一个目的是提供不使用复杂的工艺步骤就能很容易地制造出来的一种TFT矩阵基底以及一种LCD器件。

通过以下说明,可以使本领域人员清楚了解上述目的,同时还有其它未特别指出的目的。

依据本发明的第一个方面,提供了一种TFT矩阵基底,它包括:

(a)一个透明板;

(b)以成行成列的矩阵阵列排列于所述板上的TFT;

每一个TFT都具有一个第一源极/漏极区、一个第二源极/漏极区,以及一个有源层;

(c)以沿着所述阵列的行延伸的方式,形成于所述板上的栅极线;

(d)以沿着所述阵列的列延伸的方式,形成于所述板上的数据线;

每一条数据线都与相应的一个TFT的第一源极/漏极区电连接;

(e)像素电极,形成于所述板上的像素区域内;

每一个像素电极都与相应的一个TFT的第二源极/漏极区电连接;

(f)具有图案的第一遮光层,以这样一种方式形成于所述板和TFT之间,以便与所述TFT的有源层相重叠;

(g)具有图案的第二遮光层,形成于所述第一遮光层和所述TFT之间;

所述第二遮光层具有吸光特性;

(h)具有图案的第三遮光层,形成它以便覆盖相对于TFT来说是位于所述板的对侧上的TFT;

所述第三遮光层具有沿着所述矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分。

依据本发明第一方面的TFT矩阵基底,具有图案的第一遮光层以这样一种方式形成于所述板和所述TFT之间,以便与TFT的有源层相重叠。形成具有图案的第三遮光层,以覆盖相对于TFT来说是位于与所述板相对一侧上的TFT。第三遮光层具有延矩阵的行延伸的第一部分,以及延其列延伸的第二部分。此外,具有图案的第二遮光层形成于第一遮光层和TFT之间。第二遮光层具有吸光特性。

因此,既便是从所述板的一侧进入到TFT矩阵基底内部的光,被具有图案的第三遮光层以及/或数据线所反射,之后又由具有图案的第一遮光层所反射,所有反射光也都将到达具有图案的第二遮光层。由于第二遮光层具有吸光特性,因此反射光也将被第二遮光层所吸收。这样,可以有效地阻挡朝向TFT矩阵基底内的TFT的有源层传播的任何光。这意味着有源层不会暴露于光中。结果,抑制了TFT内的由光而引起的电流的泄漏,因此改善了图象质量的对比度以及均匀性。

此外,还不需要如日本待审的专利公开号No.2000-180899和2000-356787中所公开的那种复杂的制造工艺。这样,可以不使用复杂的工艺就能很容易地制造出TFT矩阵基底。

在依据本发明第一方面的基底的最佳实施例中,每一个TFT都具有一个沟道区以及一个LDD区。第二遮光层具有覆盖TFT的沟道区的第一部分,以及覆盖其LDD区的第二部分。在这个实施例中,还有另外一个优点,即朝向沟道区和LDD区传播的光可以得到一定的阻挡。一般而言,光照射到沟道区或LDD区,将会引起电流泄漏。这样,通过阻挡或抑制光,就可以有效地减小电流泄漏。

在依据本发明第一方面的基底的另一个最佳实施例中,第二遮光层是由包含硅的材料制成的。特别是,第二遮光层是由硅制成的。在这个实施例中,还存在另外一个优点,即能更有效地抑制电流的泄漏。

在依据本发明第一方面的基底的另外一个最佳实施例中,第二遮光层具有导电性。第二遮光层具有这样一种结构,它允许使用恒定的电压。在这个实施例中,存在一种附加的优点,即可将第二遮光层的偏置在所需的电位下,并能控制TFT的特性。

在依据本发明第一方面的基底的另一个最佳实施例中,第二遮光层具有导电性,并与栅极线电连接。在这个例子中,存在一种附加的优点,即TFT具有一种双栅极结构,该结构具有改善的开/关特性。

在依据本发明第一方面的基底的另外一个最佳实施例中,第二遮光层是由掺杂有杂质的硅构成的。在这个实施例中,存在一种附加的优点,即可以很容易地向第二遮光层提供所需的导电率。

最好是,栅极线以这样一种方式排列,以便与相应的TFT的沟道区相重叠。栅极线在与TFT重叠的部分,具有TFT的栅极的功能。

最好是,分别为与栅极线分离的各个TFT形成栅极。栅极线与相应的栅极电连接。

在依据本发明第一方面的基底的另一个最佳实施例中,夹在TFT的所述第二遮光层和有源层之间的电介质具有从100nm到500nm的范围厚度。在这个实施例中,确保了发明的遮光作用。更好的是,电介质的厚度从150nm到300nm。在这种情况下,提高了本发明的遮光作用。

在依据本发明第一方面的另一个基底的最佳实施例中,除了提供一个像素矩阵部分之外,还提供了一个包含TFT的驱动电路部分,其中TFT是以矩阵形式排列的。所述第二遮光层是为像素矩阵部分内的TFT提供的,所述第二遮光层不是为驱动电路部分中的TFT提供的。在这个实施例中,所述第二遮光层是为像素矩阵部分中的TFT提供的,所述第二遮光层不是为驱动电路部分内的TFT提供的。因此,如果在激光退火(annealing)工艺中,激光照射到设计为像素矩阵部分以及驱动电路部分内的TFT的有源层的非晶硅层,则激光引起的热将会借助于像素矩阵部分内的第二遮光层,以比在驱动电路部分内更快地传播到非晶硅层的周围。结果,在像素矩阵部分中的非晶硅层转变为具有低结晶度的多晶硅层。这意味着光致电流泄漏进一步得以抑制。与此同时,驱动电路部分内的非晶硅层变为具有高迁移率(mobility)的多晶硅层。

依据本发明的第二方面,提供了一种有源矩阵寻址LCD器件,它包括:

(a)依据第一方面的TFT矩阵基底;

(b)与所述TFT矩阵基底相对放置的一个对置基底;以及

(c)形成于所述TFT矩阵基底和所述对置基底之间的一个液晶层。

利用依据本发明第二方面的有源矩阵寻址LCD器件,则由于上述同一原因,能得到依据本发明第一方面的TFT矩阵基底内所显示的那些优点。

依据本发明的第三方面,提供了另一种TFT矩阵基底,它包括:

(a)透明板;

(b)以成行成列的矩阵阵列形式排列于所述板板之上的若干TFT;

每一个TFT都具有第一源极/漏极区,第二源极/漏极区;以及有源层;

(c)以这样一种方式形成于所述板板之上的若干栅极线,以便沿着所述矩阵的行延伸;

(d)以这样一种方式形成于所述板板之上的若干数据线,以便沿着所述矩阵的列延伸;

每一条数据线都与相应一个TFT的第一源极/漏极区电连接;

(e)形成于所述板板上的像素区内的像素电极;

每一个像素电极都与相应的一个TFT的第二源极/漏极区电连接;

(f)以这样一种方式形成于所述板和所述TFT之间的形成图案的第一遮光层,以便与所述TFT的有源层相重叠;

(g)形成具有图案的第三遮光层,以便覆盖相对于所述TFT来说位于所述板的对侧上的TFT;

第三遮光层,具有沿着所述矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分;以及

(h)形成图案的第四遮光层,它形成于所述TFT和所述第三遮光层之间;

所述第四遮光层具有吸光特性。

利用依据本发明第三方面的TFT矩阵基底,具有图案的第一遮光层以这样一种方式形成于所述板和所述TFT之间,以便与所述TFT的有源层相重叠。形成具有图案的第三遮光层,以便覆盖相对于所述TFT来说是位于所述板的对侧上的TFT。第三遮光层具有沿着矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分。而且,具有图案的第四遮光层形成于所述TFT和第三遮光层之间。第四遮光层具有吸光特性。

因此,即便是从所述板一侧进入到TFT矩阵基底内部的光,被具有图案的第三遮光层以及/或数据线反射,之后又由具有图案的第一遮光层反射的情况下,全部反射光也会到达具有图案的第四遮光层。由于第四遮光层具有吸光特性,因此反射光将被第四遮光层所吸收。这样,可有效阻挡朝向TFT矩阵基底中TFT的有源层传播的任何光。这意味着有源层不会暴露于光之中。结果,TFT内光致电流泄漏得以抑制,由此改善的图象质量的对比度以及均匀性。

而且,不再需要日本待审专利公开No.2000-180899和2000-356787中所公开的复杂的制造工序。这样,可以不使用复杂工艺而很容易地制造出TFT矩阵基底。

在依据本发明第三方面基底的最佳实施例中,每一个TFT都具有沟道区和LDD区。第二遮光层具有覆盖TFT的沟道区的第一部分,以及覆盖其LDD区的第二部分。在这个实施例中,存在另一个优点,即确实阻挡了朝向沟道区和LDD区传播的光。一般而言,对沟道区或LDD区的光照射将会引起电流泄漏。这样,通过阻挡或抑制光,可以有效地减少电流泄漏。

在依据本发明第三实施例的基底的另一个实施例中,第四遮光层是由包含硅的材料制成的。优选的是,第四遮光层是由硅制成的。在这个实施例中,存在另外一个优点,即电流泄漏得到更有效的抑制。

在依据本发明第三方面的基底的另一个最佳实施例中,第四遮光层具有导电性。第四遮光层具有允许施加恒定电压的一种结构。在这个实施例中,存在另一个优点,即第四遮光层可以偏置于所需的电势之下,且可以控制TFT的特性。

在依据本发明第三方面的基底的另一个最佳实施例中,第四遮光层具有导电性,并电连接至所述栅极线。

在依据本发明第三方面的基底的另外一个实施例中,第四遮光层是由掺杂的硅构成的。在这个实施例中,存在一个附加优点,即可以很容易地给予第四遮光层以所需的导电率。

最好是,以这样一种方式设置栅极线,以便与相应的TFT的沟道区相重叠。在它们的重叠部分,栅极线具有TFT的栅极功能。

最好是,分别为与栅极线分离的各个TFT形成栅极。栅极线与相应的栅极电连接。

在依据本发明第三方面的基底的另一个最佳实施例中,在第一遮光层和TFT之间还额外形成了具有图案的第二遮光层。第二遮光层具有吸光特性。在这个实施例中,在TFT的每一侧上的光被阻挡,因此,可以获得非常好的遮光效果。

在依据本发明第三方面的另一个最佳实施例中,夹在第二遮光层和TFT的有源层之间的电介质具有从100nm到500nm的厚度范围。在这个实施例中,确保了本发明的遮光作用。更优选的是,电介质的厚度从150nm到300nm。在这种情况下,增强了本发明的遮光效果。

在依据本发明第三方面的基底的另一个实施例中,除了像素矩阵部分之外,还提供了包含TFT的驱动电路部分,其中TFT是以矩阵阵列的形式排列的。第二遮光层是为像素矩阵部分内的TFT而设的,第二遮光层不是为驱动电路部分内的TFT而设的。在这个实施例中,第二遮光层是为像素矩阵部分内的TFT而设的,第二遮光层不是为驱动电路部分内的TFT而设的。因此,在激光退火工序中,如果激光照射到用作像素矩阵部分以及驱动电路部分内的TFT的有源层的非晶硅层时,激光引起的热将会通过像素矩阵部分中的第二遮光层,以比驱动电路部分内的速度更快地传播到非晶硅层的周围。结果,像素矩阵部分内的非晶硅层转变为具有较低结晶度的多晶硅层。这意味着由光引起的电流泄漏进一步得到抑制。与此同时,驱动电路部分内的非晶硅层被转变为具有高迁移率的多晶硅层。

依据本发明的第四方面,提供了另一种有源矩阵寻址LCD器件,它包括:

(a)依据第三方面的TFT矩阵基底;

(b)与所述TFT矩阵基底相对放置的对置基底;以及

(c)形成于所述TFT矩阵基底和对置基底之间的液晶层。

由于上述相同的原因,利用依据本发明第四方面的有源矩阵寻址LCD器件,可以得到与依据本发明第三方面的TFT矩阵基底中所示的那些优点相同的优点。

附图说明

为了容易实现本发明,以下,将参照附图,对其进行说明。

图1是示出了已有技术的TFT矩阵基底的布局的一张部分平面图。

图2A是沿着图1中的线IIA-IIA的局部剖面图,它示出了图1中的已有基底的结构。

图2B是沿着图1中的线IIB-IIB的局部剖面图,它示出了图1中的已有基底的结构。

图3是一张示意性的剖面图,它示出了阻挡进入到图1的已有基底内部的光的效果,它是沿着图1中的线IIA-IIA看进去的。

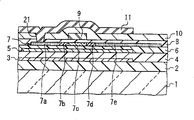

图4是一张局部平面图,它示出了依据本发明第一实施例的TFT矩阵基底的布局。

图5A是一张沿着图4中的线VA-VA的局部剖面图,它示出了图4的基底结构。

图5B是一张沿着图4中的线VB-VB的局部剖面图,它示出了图4的基底结构。

图6是一张示意性的剖面图,它示出了对进入到图4的基底内部的光进行阻挡的效果,它是沿着图4中的线VA-VA看进去的。

图7A到11A是局部剖面图,它们是分别沿着图4的线VA-VA看进去的,它们示出了制造图4的基底的工艺步骤。

图7B到1iB是局部剖面图,它们是分别沿着图4中的线VB-VB看进去的,它们示出了制造图4的基底的工艺步骤。

图12是一张局部平面图,它示出了依据本发明的第二实施例的一个TFT矩阵基底的布局。

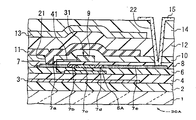

图13A是一张沿着图12内的线XIIIA-XIIIA的局部剖面图,它示出了图12的基底的结构。

图13B是一张沿着图12内的线XIIIB-XIIIB的局部剖面图,它示出了图12的基底的结构。

图14是一张局部平面图,它示出了依据本发明第三实施例的一个TFT矩阵基底的布局。

图15是一张局部平面图,它示出了依据本发明第四实施例的一个TFT矩阵基底的布局。

图16A是一张沿着图15内的线XVIA-XVIA的局部剖面图,它示出了图15的基底结构。

图16B是一张沿着图15内的线XVIB-XVIB的局部剖面图,它示出了图15的基底结构。

图17是一张示意性的剖面图,它示出了对进入到图15的基底内部的光进行阻挡的效果,它是沿着图15内的线XVIA-XVIA看进去的。

图18是一张局部平面图,它示出了依据本发明第五实施例的一个TFT矩阵基底的布局。

图19是一张局部平面图,它示出了依据本发明第六实施例的一个TFT矩阵基底的布局。

图20是一张示意性的剖面图,它示出了使用依据本发明的TFT矩阵基底的有源阵列寻址LCD器件的结构。

图21A是沿图4线VA-VA的局部剖面图,它示出了依据本发明第七实施例的TFT矩阵基底的结构。

图21B是沿图4线VB-VB的局部剖面图,它示出了图21A的基底结构。

图22A是沿图4线VA-VA的局部剖面图,它示出了依据本发明第八实施例的TFT矩阵基底的结构。

图22B是沿图4线VB-VB的局部剖面图,它示出了图22A的基底结构。

图23A是沿图15线XVIA-XVIA的局部剖面图,它示出了依据本发明第九实施例的TFT矩阵基底的结构。

图23B是沿图15线XVIB-XVIB的局部剖面图,它示出了图23A的基底结构。

图24A是沿图15线XVIA-XVIA的局部剖面图,它示出了依据本发明第十实施例的TFT矩阵基底的结构。

图24B是沿图15线XVIB-XVIB的局部剖面图,它示出了图24A的基底结构。

图25示出了一张曲线图,它示出了在像素矩阵部分内提供的TFT中光致电流泄漏与有源层和第二遮光层之间的介电层的厚度之间的关系,这张曲线图是在投射光的特定照射条件下得到的。

图26是依据本发明第十一实施例的TFT矩阵基底的平面示意图。

具体实施方式

以下,将参照附图,对本发明的最佳实施例进行详细说明。

第一实施例

图4和图5A以及5B示出了依据本发明第一实施例的一个TFT矩阵基底30的示意性结构,其中,为简便起见,仅仅示出了一个像素。这种情况也适用于稍后将要说明的任何其它实施例。

TFT矩阵基底30包括一个透明板1,其上以矩阵阵列的形式排列有TFT 31。板1是由象玻璃这样透明且绝缘的材料制成。

一个SiO2层2形成于板1上,以覆盖其整个表面。层2用于防止包含于板1内的重金属扩散到基底30内部。

一个具有图案的第一遮光层3形成于SiO2层2上。层3的平面形状类似于格子,它是由沿着TFT 31的矩阵的行(图4中的X方向)延伸的横向条3a,以及沿其列(图4中的Y方向)延伸的、且与横向条相交的垂直条3b构成的。层3是由具有足够低的光穿透率的材料(例如是WSi2)制成的。层3的厚度设定为足够大,用于阻挡从基底30的后侧即从板1的一侧直接进入的光。整个层3由位于其上的SiO2层4所覆盖。

在SiO2层4上,形成了一个具有图案的第二遮光层5。层5是由具有吸光特性的非晶硅构成的。层5包括沿着TFT 31的矩阵的行(图4中的X方向)延伸的横向条形部分5a,以及沿着其列(图4中的Y方向)延伸并与横向部分5a相交的垂直矩形部分5b。条形部分5a是等间距垂直(沿着Y方向)放置的,它们彼此平行。矩形部分5b是等间距水平(沿着X方向)放置的,它们彼此平行。使层5形成一种图案,以便能完全与位于其下面的第一遮光层3重叠。层5由形成于SiO2层4上的一个SiO2层6所覆盖。

在SiO2层6上,形成了多晶硅层7。使每一个层7形成图案,以便具有大约为L字符的一个平面形状。每一个层7都刚好位于栅极线9与数据线11相交的位置下面,这将在后面进行说明。层7用作每个TFT 31的有源层。

每一个多晶硅的有源层7都包括一个未掺杂的沟道区7c、两个轻度掺杂的LDD区7b和7d、一个重掺杂源极区7a以及一个重掺杂漏极区7e。源极和漏极区7a和7e都位于沟道区7c的每一侧。LDD区7b位于源极区7a和沟道区7c之间。LDD区7d位于沟道区7c以及漏极区7e之间。

源极区7a、LDD区7b、沟道区7c、LDD区7d以及漏极区7e以这样一种方式沿着Y方向排列,以便与所述第一和第二遮光层3和5相重叠。部分漏极区7e沿着X方向延伸。

栅极绝缘层8形成于SiO2层6上,以便覆盖位于其下面的有源层7。

由掺杂有杂质的多晶硅或硅化物构成的栅极线9,形成于栅极绝缘层8上。这些线9彼此平行,并沿着X方向延伸。对每一条线9进行定位,使其能与属于所述矩阵的同一行的TFT的沟道区7c相重叠。线9的一些部分刚好位于用作相应的TFT 31的栅极的区7c之上。线9整个由形成于层8上的第一夹层绝缘层10所覆盖。

由A1制成的数据线11,形成于第一夹层绝缘层10上。这些线彼此平行,且沿着Y方向延伸。每一条线11都被放置在能与属于所述矩阵的同一列的TFT 31的有源层7相重叠的位置上。线11完全覆盖了相应的TFT 31的源极区7a、沟道区7c以及LDD区7b 及7d。线11覆盖了相应的TFT 31的部分漏极区7e。线11通过接触孔21与属于矩阵同一行的TFT 31的源极区域7a机械接触并电气连接,其中,所述接触孔21穿透了第一夹层绝缘层10以及栅极绝缘层8。线11完全由第二夹层绝缘层12所覆盖。

由Cr构成的具有图案的黑底层13形成于第二夹层绝缘层12上。层13的平面形状类似于格子,它是由沿着矩阵的行(图4中的X方向)延伸的横向条、以及沿着其列(图4中的Y方向)延伸并与所述横向条相交的垂直条形成的。使层13形成图案,以便与栅极线9以及数据线11相重叠,从而覆盖TFT 31。层13用作第三遮光层。层13完全被形成于层12上的一个第三夹层绝缘层14所覆盖。

具有大约呈矩形的平面形状的像素电极15,形成于第三夹层绝缘层14上。电极15位于由栅极线9以及数据线11所定义的相应的像素区20内。电极15通过接触孔22,与相应的TFT 31的漏极区7e进行机械接触以及电气连接,其中所述接触孔22穿透了第三夹层绝缘层14、第二夹层绝缘层12、第一夹层绝缘层10以及栅极绝缘层8。

图20示出了一种有源矩阵寻址LCD器件50的结构,它包括具有依据第一实施例的结构的TFT矩阵基底51。利用密封部分53,将一个对置基底52与基底51结合在一起,以便在它们之间形成一个液晶层54。在层54中,一个定向层55形成于基底51上,定向层56形成于基底52上。偏振片57位于基底52上。背光元件58靠近基底51。

利用有源矩阵寻址LCD器件50,如图6所示,从对置基底52一侧进入器件50的光L1被黑底层(即第三遮光层)13所阻挡。或者也可以是,光L1穿透基底30,而未被第一遮光层3反射。这是由于很容易为此目的而对层13和3的宽度、以及层13和3之间的间距进行调整。

另一方面,从TFT矩阵基底30(51)一侧进入器件50的光L2,被第一遮光层3所阻挡。从基底30一侧进入器件50的、朝向黑底13的光L3被层13所反射,而转向第一遮光层3。之后,光L3到达位于层13和TFT 31之间的第二遮光层5。或者也可以采取:光L3由层13和3所反射,之后,光L3到达第二遮光层5。此外,从基底30一侧进入器件50的、朝向数据线11的光L4被线11所反射,最终,到达层5。

如上所述,第二遮光层5是由具有吸光特性的非晶硅构成的。这样,光L1到L4就被层5吸收。

这样,即便从板1一侧传播来的光直接输入到第一遮光层3和数据线11之间的内部空间,或是通过由具有图案的第三遮光层(即黑底层)13反射而间接输入到上述内部空间中时,光也会被第二遮光层5所吸收。这样,能有效、确实地阻挡朝向每个TFT 31的沟道区7c和LDD区7b和7d传播的任何光。

另外,每个TFT 31的沟道区7c被相应的一条栅极线9所覆盖,因此,增强了阻挡朝向区域7c传播的光的效果。

一般而言,硅层具有一种光谱吸收特性,它对于绿光和蓝光波段,具有相对较高的光吸收率,对于红光波段,具有相对较低的光吸收率。可以将这种特性应用于非晶硅,用于形成第二遮光层5,还可以将这种特性应用于多晶硅,用于形成有源层7。众所周知,通过在多晶硅的有源层7内吸收光,可以引起TFT 31的电流泄漏,因此,电流泄漏的大小或量依据所要照射的光的波长而变化。结果,通过制作其光谱吸收特性与多晶硅相似的非晶硅的第二遮光层5,可以有效抑制或减少电流泄漏。

当高亮度光输入到TFT矩阵基底30上时,TFT 31附近的温度将会升高,这是由于在第二遮光层5内吸收光所产生的热而引起的。如上所述,层5的吸收率对于红光波段相对较低。因此,存在一个附加的优点,即能更多地抑制TFT 31附近发生的温度的升高。

出于同一目的,除了非晶硅,还可以使用微晶硅或多晶硅,或是包含硅的硅化物。可以得到与非晶硅的优点基本相同的优点。

接下来,将参照附图7A到11A,以及7B到11B,来说明制造依据图4和5A到5B的第一实施例的TFT矩阵基底30的一种方法。

首先,如图7A和7B所示,通过一个流行的CVD(化学蒸汽沉积)工艺,在透明板1上形成一个SiO2层2。之后,在SiO2层2上形成一个硅化钨(WSi2)层(未示出)。利用流行的光刻以及刻蚀技术,使如此形成的WSi2层形成一种图案,以形成第一遮光层3。此后,利用CVD工艺,在SiO2层2上形成SiO2层4,以覆盖整个层3。

接下来,通过低压CVD(LPCVD)或等离子增强型CVD(PECVD)工艺,在SiO2层4上沉积一层非晶硅层(未示出)。利用通用的光刻以及刻蚀技术,使如此形成的SiO2层形成图案,因而,在层4上形成了第二遮光层5。

此后,如图8A和8B所示。利用CVD工艺,在SiO2层4上沉积了SiO2层6,以便覆盖第二遮光层5。利用LPCVD或PECVD工艺,在层6上沉积一个非晶硅层(未示出)。利用激光退火方法,使如此沉积而形成的非晶硅层结晶。利用通用的光刻以及刻蚀技术,使如此结晶形成的Si层形成图案,因此,在层6上形成了TFT 31的多晶硅的有源层7。

随后,如图9A和9B所示,利用CVD工艺,在SiO2层6上沉积一个SiO2层(即栅极绝缘层)8,以便覆盖多晶硅有源层7。掺杂杂质的多晶硅层(未示出)以及硅化物层(未示出)先后沉积到栅极绝缘层8上,之后,利用通用的光刻以及刻蚀技术,使其形成图案,因而形成了栅极线9。

将如此形成的栅极线9用作掩模,以低掺杂浓度,有选择地将杂质掺杂到多晶硅有源层7上。之后,利用具有图案的光刻胶掩模(未示出),以高掺杂浓度,有选择地将杂质掺杂到多晶硅有源层7上。这样,在层7上,就形成了源极区7a、LDD区7b和7d,沟道区7c以及漏极区7e。

此后,如图10A和10B所示,利用CVD工艺,在栅极绝缘层8上沉积了一个SiO2层,作为第一夹层绝缘层10,以便覆盖栅极线9。之后,利用通用的光刻以及刻蚀技术,有选择地除去第一夹层绝缘层10以及栅极绝缘层8,因此,形成了接触孔21,该孔使源极区7a露出。

利用溅射工艺沉积了一个A1层(未示出),并利用通用的光刻以及刻蚀技术形成图案,因而形成数据线11。线11通过孔21与源极区7a相接触。这样,线11就与区7a电连接。

如图11A和11B所示,利用CVD工艺,将用作第二夹层绝缘层12的一个SiO2层沉积在第一夹层绝缘层10上,以便覆盖数据线11。之后,利用溅射工艺在层12上沉积一个Cr层(未示出),之后,利用通用的光刻以及刻蚀技术,使其形成图案,从而,形成黑底层13,用作第三遮光层。

此后,利用CVD工艺,在第二夹层绝缘层12上沉积一个SiO2层,用作第三夹层绝缘层14,以便覆盖黑底层14。

利用通用的光刻以及刻蚀技术,有选择地除去第三夹层绝缘层14、第二夹层绝缘层12、第一夹层绝缘层10以及栅极绝缘层8,从而形成使漏极区7e露出的接触孔22。之后,将一个ITO(氧化铟锡)层(未示出)沉积在层14上,之后,利用通用的光刻以及刻蚀技术使其形成图案,从而,形成了像素电极15。通过孔22,电极15与漏极区7e相接触。这样,电极15与区7e电连接。

通过上述工艺步骤,就形成了图1和2A到2B所示的TFT矩阵基底。能很容易地从中看到,基底30的制造工艺步骤简单,它不包括复杂的工艺步骤。结果,能很容易地制造基底30。

利用依据本发明第一实施例的TFT矩阵基底30,具有图案的第一遮光层3以这样一种方式形成于板1和TFT 31之间,以便与TFT 31的有源层7相重叠。形成有具有图案的第三遮光(即黑底)层13,以便覆盖相对于TFT 31来说是位于板1对侧上的TFT 31。第三遮光层13具有沿着矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分。此外,具有图案的第二遮光层5形成于所述第一遮光层3和TFT 31之间。层5具有吸光特性。

因此,即便是从板1一侧进入到TFT矩阵基底30内的光被具有图案的第三遮光层13以及/或数据线11反射,之后,又由具有图案的第一遮光层3反射,全部反射光将会到达具有图案的第二遮光层5。由于第二遮光层5具有吸光特性,所以反射光将被层5吸收。这样,就有效阻挡了朝向基底30内的TFT的有源层7传播的任何光。这意味着,有源层7不会暴露于光中。结果,TFT 31内光致电流泄漏得以抑制,因此,提高了图象质量的对比度以及均匀性。

此外,也不需要如日本待审专利公开号No.2000-180899和2000-356787中所公开的复杂的制造工艺。这样,可以不使用复杂工艺步骤,就能很容易地制造基底30。

对于本发明来说,在第一遮光层3和第二遮光层5之间的介电层厚度,以及在第二遮光层5和有源层7之间的介电层的厚度,都是重要参数。特别是,第二遮光层5和有源层7之间的介电层的厚度更加重要。第二遮光层5和有源层7之间的介电层的厚度越小,则遮光效果越好。根据本发明人的测试,发现当将层5和层7之间的介电层的厚度设定为500nm或更小的情况下,遮光效果显著。

此外,发明人还发现,如果第二遮光层5和有源层7之间的介电层的厚度很小,TFT 31的晶体管特性会受到影响,同时,还影响了使用作有源层7的非晶硅层结晶的激光退火工艺。因此,为得到本发明的遮光效应,他们发现层5和7之间的介电层的厚度最好设定在从500nm到100nm的范围内,更好的是从300nm到150nm的范围内。这一点适用于以下将要说明的本发明的其他实施例。

第二实施例

图12和13A以及13B示出了依据本发明第二实施例的TFT矩阵基底30A的结构,其中,为简便起见,仅仅示出了一个像素。

除了第二遮光层5A具有导电性、并与相应的栅极线9电连接之外,第二实施例的基底30A具有与第一实施例的基底30相同的结构。因此,这里为了简便起见,省略了对相同结构的说明,对图12和13A以及13B的第二实施例中的、与图4和5A到5B的第一实施例中所用的相同的或相应的元件,赋予相同的参考标记。

在基底30A中,由掺杂了杂质的多晶硅构成的第二遮光层5A,形成于SiO2层4上。层5A具有沿矩阵的行(即X方向)延伸的条形的第一部分5Aa,以及沿矩阵的列(即Y方向)延伸的矩形的第二部分5Ab。第一部分5Aa彼此平行。层5A是以这样一种方式形成的,以便与所述第一遮光层3相重叠。第二部分5Ab与各个多晶硅的有源层7相重叠。

利用内部引线41,将第二遮光层5A电连接到相应的栅极线9上。因此,栅极线9的一些部分用作TFT 31的第一栅极,与此同时,层5A用作其公共的第二栅极。这意味着TFT 31用作双栅极场效应管(FET)。

这样,对于第二实施例的基底30A,第二遮光层5A被用作公共的第二栅极,因此,TFT 31的内部电极电容增大。为抑制内部电极电容的增加,与第一实施例相比,Y方向上的第二部分5Ab的长度L减小。

具体地,第二遮光层5A的第二部分5Ab与TFT 31的沟道区7c、以及LDD区7b和7d相重叠,同时,几乎不与源极和漏极区7a和7e相重叠。由于这种结构,所以,可以将TFT 31的内部电极的电容量的增大抑制到实际上不会出现问题、且同时还能保持阻挡朝向沟道和LDD区7c、7b和7d传播的光的效果的水平。

可以使用与第一实施例所用的方法几乎相同的方法来制造基底30A。

对于依据第二实施例的TFT矩阵基底30A,可以获得与第一实施例中的优点相同的优点。具体而论,能有效阻挡朝向基底30A内的TFT 31的有源层7传播的任何光。这意味着有源层7不会暴露于光之中。结果,TFT 31内的光致电流泄漏得以抑制,因此改善了图象质量的对比度以及均匀性。此外,可以不使用复杂的工艺步骤,就能很容易地制造出基底30A。

基底30A具有一个附加的优点,即可以获得TFT 31的改善了的开/关特性,这是因为TFT 31用作双栅极FET的缘故。

第三实施例

图14示出了依据本发明第三实施例的一个TFT矩阵基底30B,其中为了简便起见,仅仅示出了一个像素。

除了第二遮光层5B具有导电性、并被施加了一个恒定电压Vc之外,第三实施例的基底30B具有与第一实施例的基底30相同的结构。因此,为了简便起见,在这里我们就省略了对相同结构的说明,而是将与图4和5A到5B的第一实施例中所用的同一参考标记,赋予图12和13A以及13B的第二实施例内的相同或相应的元件。

在基底30B上,由掺杂有杂质的多晶硅构成的第二遮光层5B,形成于SiO2层4上。层5B具有沿矩阵的行(即X方向)延伸的条形的第一部分5Ba,以及沿矩阵的列(即Y方向)延伸的条形的第二部分5Bb。第一部分5Bb彼此平行,同时,第二部分5Bb彼此平行。第一和第二部分5Ba和5Bb彼此相交,从而形成格子形的平面形状。层5B以这样一种方式形成,以便与第一遮光层3相重叠。第二部分5Bb与相应的多晶硅有源层7相重叠。

第二遮光层5B电连接至一个外部端子51,通过该端子向层5B提供一个恒定电压Vc。于是,将层5B偏置在电压Vc。通过调节电压Vc的值,可以根据需要对TFT 31的性能进行控制。

可以使用与第一实施例中所用的方法基本相同的方法来制造基底30B。

利用依据第三实施例的TFT矩阵基底30B,可以得到与第一实施例中的优点相同的优点。具体地,有效地阻挡了朝向基底30B内的TFT31的有源层7(特别是沟道区7c以及LDD区7b和7d)传播的任何光。这意味着有源层7不会暴露于光之中。结果,TFT 31内光致电流泄漏得以抑制,因此改善了图象质量的对比度以及均匀性。此外,还能不使用复杂工艺步骤,容易地制造出基底30B。

基底30B具有一个附加的优点,即可通过调节加到第二遮光层5B上的电压VC的值,来控制TFT 31的性能。

第四实施例

图15和16A到16B示出了依据本发明第四实施例的TFT矩阵基底30C的结构,其中,为了简便起见,仅仅示出了一个像素。

在TFT 31没有被数据线11所覆盖的情况下,通过将本发明应用于TFT矩阵基底的结构或形状,就可以获得第四实施例的基底30C。

具体说,TFT 31的多晶硅有源层7’是沿着矩阵的行延伸的。具有图案的第一遮光层3’、具有图案的第二遮光层5C,以及具有图案的第三遮光层(即黑底层)13’是以这样一种方式形成的,以便与有源层7’相重叠。这些TFT 31各自具有分别电连接至栅极线9的栅极9a。

在基底30C中,由SiO2层2构成的第一遮光层3’,具有沿矩阵的行(即X方向)延伸的条形的第一部分3a’、沿矩阵的列(即Y方向)延伸的条形的第二部分3b’,以及横向突出以覆盖相应的像素区20的矩形的第三部分3c’。第一和第二部分3a’和3b’彼此相交,从而构成了类似于格子的平面形状。第三部分3c’分别位于部分3a’和3b’的各个交叉点上。层3’是由具有足够低的光学透射率的材料(例如是WSi2)制成的。层3’的厚度被设置为足够大,以用于阻挡直接从基底30C的后侧,即从板1一侧,直接进入的光。整个层3’都被贴在其上的SiO2层4所覆盖。

在SiO2层4上,形成具有图案的第二遮光层5C。层5C是由具有吸光特性的非晶硅制成的。层5C包括沿TFT31的矩阵的行(即图4中的X方向)延伸的横向条形部分5Ca和沿TFT31的矩阵的列(即图4中的Y方向)的延伸的、并与横向部分5Ca交叉的垂直矩形部分5Cb。条形部分5Ca是以等间距垂直(在Y方向上)放置的,它们彼此平行。矩形部分5Cb是以等间距水平(在X方向上)放置的,它们彼此平行。使层5C形成图案,以便与位于其下的第一遮光层3’完全重叠。层5C被形成于SiO2层4上的一个SiO2层6所覆盖。

在SiO2层6上,形成了多晶硅的有源层7’。使每一个层7’形成图案,使其具有近似细长的平面形状。每一个层7’都位于靠近相应的栅极线9和相应的栅极数据线11的交叉点的位置上。

每一个多晶硅的有源层7’都包括一个未掺杂的沟道区7c’、两个轻度掺杂的LDD区7b’和7d’、一个重掺杂的源极区7a’、以及一个重掺杂的漏极区7e’。源极和漏极区7a’和7e’都位于沟道区7c’的每一侧。LDD区7b’位于源极区7a’和沟道区7c’之间。LDD区7d’位于沟道区7c’和漏极区7e’之间。

源极区7a’、LDD区7b’、沟道区7c’、LDD区7d’、以及沟道区7e’以这样一种方式沿X方向排列,以便与第一和第二遮光层3’和5C相重叠。

一个栅极绝缘层8形成于SiO2层6上,以覆盖位于其下的有源层7’。

由掺杂有杂质的多晶硅或硅化物构成的栅极线9和栅极9a,形成于栅极绝缘层8上。栅极线9彼此平行,且以这样一种方式沿X方向延伸,从而不与TFT 31的有源层7’相重叠。作为替代的方法,还可以形成栅极9a,使其与各个TFT 31的相应的沟道区7c’相重叠。栅极9a机械以及电气连接至相应的栅极线9。栅极线9以及栅极9a被形成于层8上的第一夹层绝缘层10完全覆盖。

由A1制成的数据线11,形成于第一夹层绝缘层10上。这些线11彼此平行,并沿Y方向延伸。每一条线11都位于一个位置上,在该位置处,它能与属于矩阵同一列的TFT 31的有源层7’相重叠。线11完全覆盖了相应的TFT 31的有源区7a’。通过接触孔21,线11机械接触并电气连接至属于矩阵同一行的TFT 31的源极区7a’,其中,所述接触孔21穿透了第一夹层绝缘层10以及栅极绝缘层8。线11完全由第二夹层绝缘层12所覆盖。

由Cr制成的具有图案的黑底层13’,形成于第二夹层绝缘层12上。层13’的平面形状类似于格子,它是由沿矩阵的行(即图4中的X方向)延伸的横向的条、沿其列(即图4中的Y方向)延伸并与横向条相交的垂直条形成的。使层13’形成图案,从而能与栅极线9、栅极9a、以及数据线11相重叠。横向突出从而与像素电极20相重叠的、层13’的矩形部分,覆盖了相应的TFT 31。层13’用作第三遮光层。层13’完全由形成于层12上的第三夹层绝缘层14所覆盖。

具有近似为矩形的平面形状的像素电极15,形成于第三夹层绝缘层14上。电极15位于由栅极线9和数据线11所确定的相应的像素区20中。通过接触孔22,电极15机械接触并电气连接至相应的TFT31的漏极区7e’,其中,所述接触孔22穿透了第三夹层绝缘层14、第二夹层绝缘层12、第一夹层绝缘层10以及栅极绝缘层8。

利用依据本发明第四实施例的TFT矩阵基底30C,可以得到与第一实施例中的那些优点相同的优点。具体地,如图17所示,从对置基底52一侧进入LCD器件的光,被黑底层(即第三遮光层)13’所阻挡。或者也可以采用:光L1穿透基底30,而不被第一遮光层3’所反射。这是由于可以为此目的而很好地调节层13’和3’的宽度,以及层13’和3’之间的间隔。

另一方面,从TFT矩阵基底30C(51)一侧进入LCD设备的光L2,被第一遮光层3’所阻挡。从基底30C一侧进入的、朝向黑底层13’的光L3,被层13’所反射,而到达第一遮光层3’。之后,光L3到达位于层3’和TFT 31之间的第二遮光层5C。或者也可以采用:光L3被层13’和3’所反射,之后,光L3到达第二遮光层5C。由于第二遮光层5C是由具有吸光特性的非晶硅制成的,因此光L1到Le被层5C所吸收。

这样,既便从板1一侧传播来的光被具有图案的第三遮光层(即黑底层)13’所反射,之后,又被第一遮光层3’反射,光也会被第二遮光层5C所吸收。这样,能有效并确定地阻挡朝向每个TFT 31的沟道区7c’以及LDD区7b’和7d’传播的光。

另外,每个TFT 31的沟道区7c’都被相应的一个栅极9a所覆盖,从而,可以增强阻挡朝向区7c’传播的光的效果。

利用与第一实施例中所用的方法基本相同的方法,来制造基板30C。

利用依据本发明第四实施例的TFT矩阵基底30C,可以得到与第一实施例中的那些优点相同的优点。具体说,可以有效阻挡朝向基底30C内的TFT 31的沟道区7c’以及LDD区7b’和7d’传播的光。这意味着这些区7c’、7b’和7d’不会暴露于光之中。结果,光致电流泄漏得以抑制,从而改善了图象质量的对比度以及均匀性。此外,可以不使用复杂的工艺步骤,就能很容易地制造出基底30C。

第五实施例

图18示出了依据本发明第五实施例的TFT矩阵基底30D的结构,其中为简便起见,仅仅示出了一个像素。

第五实施例的基底30D具有与第四实施例的基底30C相同的结构,除了第二遮光层5D具有导电性、并电连接至相应的栅极线9之外。因此,为了简单起见,省略了对相同结构的说明,而将图15和16A到16B的第四实施例中使用的同一个参考标记,赋予图18的第五实施例中的相应元件。

在基底30D中,第二遮光层5D是由掺杂有杂质的多晶硅构成的。层5D具有沿矩阵的行(即X方向)延伸的条形的第一部分5Da,以及沿矩阵的列(即Y方向)延伸的矩形的第二部分5Db。第一部分5Da彼此平行。横向突出到像素电极20之上的第二部分5Db,与各个多晶硅的有源层7’相重叠。层5D以这样一种方式形成,以便与第一遮光层3’相重叠。

正象第二实施例那样,通过内部引线41,第二遮光层5D电连接至相应的栅极线9。因此,栅极9a用作TFT 31的第一栅极,与此同时,层5D用作其公共的第二栅极。这意味着TFT 31可以用作双栅极FET。

这样,对于第五实施例的基底30D,第二遮光层5D用作公共的第二栅极,从而,TFT 31的内部电极的电容增大了。为抑制内部电极的电容增加,与第四实施例相比,减小了第二部分5Db在X方向上的宽度W。

具体而论,第二遮光层5D的第二部分5Db与TFT 31的沟道区7c’、以及LDD区7b’和7d’相重叠,同时,几乎不与源极和漏极区7a’和7e’相重叠。由于这种结构,因而,可以将TFT 31的内部电极的电容增加抑制到一个水平,在该水平之下,实际上不会出现问题,同时还能保持阻挡朝向沟道和LDD区7c’、7b’和7d’传播的光的效果。

可以用与第一实施例中所用的基本相同的方法来制造基底30d。

利用依据本发明第五实施例的TFT矩阵基底30D,可以得到与第一实施例中的那些优点相同的优点。具体地,可以有效地阻挡朝向基底30D内的TFT 31的沟道区7c’和LDD区7b’以及7d’的任何光。结果,TFT 31内光致电流泄漏得以抑制,从而,改善了图象质量的对比度以及均匀性。此外,还可以不使用复杂的工艺步骤,就能很容易地制造出基底30D。

基底30D具有附加的优点,即可以得到改善了的TFT 31的开/关特性。这一点与第二实施例相同。

第六实施例

图19示出了依据本发明第六实施例的TFT矩阵基底30E的结构,其中为了简便起见,仅仅示出了一个像素。

第六实施例的基底30E具有与第四实施例的基底30C相同的结构,除了第二遮光层5E具有导电性、并加有恒定电压Vc之外。因此,这里,为了简单起见,省略了有关相同结构的说明,对图19的第六实施例中的相同的或相应的元件,赋予与图15和16A到16B的第四实施例中所用的相同的参考标记。

在基底30E中,由掺杂杂质的多晶硅构成的第二遮光层5E,形成于SiO2层4上。第二遮光层5E具有沿矩阵的行(即X方向)延伸的条形的第一部分5Ea、矩形的第二部分5Eb、以及沿矩阵的列(即Y方向)延伸的条形的第三部分5Ec。第一和第三部分5Ea和5Ec彼此交叉,从而构成了类似于格子的平面形状。第二部分5Eb位于部分5Ea和5Ec的各个交叉点上,并突出到像素区20之上。层5E以这样一种方式形成,以便与第一遮光层3’相重叠。第二部分5Eb与多晶硅的有源层7’相重叠。

第二遮光层5E电连接至外部端子51,通过该外部端子,能向层5E提供一个恒定的电压Vc,这一点与第三实施例中的基底30B的情况相似。这样,将层5E偏置在电压Vc之下。通过调节电压Vc的值,可以根据需要控制TFT 31的特性。

可以使用与第一实施例中所用的基本相同的方法来制造基底30E。

利用依据本发明第六实施例的TFT矩阵基底30E,可以得到与第一实施例中的优点相同的优点。具体是,能够有效地阻挡朝向基底30E内的TFT 31的有源层7(尤其是沟道区7c’和LDD区7b’和7d’)传播的任何光。结果,在TFT 31内的光致电流泄漏得以抑制,因而,改善了图象的对比度以及均匀性。此外,可以不使用复杂的工艺步骤,就能很容易地制造出基底30E。

基底30E具有附加的优点,即通过调节加到第二遮光层5B上的电压VC的值,来控制TFT 31的特性,这一点与第三实施例的基底30B相同。

第七实施例

在上述第一到第六实施例中,除了第一遮光层3和第三遮光层(即黑底层)13之外,还有一个位于第一遮光层3和TFT 31之间的第二遮光层5,因此增强了遮光效果。

在以下本发明的第七到第十实施例中,第四遮光层16或16’位于TFT 31和第三遮光层(黑底层)13之间,以便增强遮光效果。正如可以从这些实施例中看到的那样,既便是在第四遮光层16或16’相对于TFT31来说,处于与所述板1相对的一侧上,也可以有效地阻档或抑制朝向TFT 31的有源层7传播的光,这一点与第二遮光层5的情况相似。

图21A和21B示出了依据本发明第七实施例的TFT矩阵基底30F的结构,它们分别是沿着图4中的线VA-VA和VB-VB剖开的。

通过除去图4、5A和5B的第一实施例的TFT矩阵基底30中的第二遮光层5,并向其中添加第四遮光层16,就可以得到第七实施例的基底30F。基底30F的其他结构与基底30相同。由于消除了第二遮光层5,因此在TFT矩阵基底30内,可以消除掉SiO2层4或6。

第四遮光层16的图案或平面形状与图4所示的第二遮光层5相同,它覆盖了每个TFT 31的几乎所有的多晶硅有源层7。层16没有覆盖靠近接触孔22的层7的部分。

第四遮光层16被埋在第一夹层介电层10内。如果层10具有双层结构,则上述这一点非常容易实现。特别是,当形成层10的底面部分之后,用于层16的非晶硅层形成于其底面部分上。随后,使非晶硅层形成图案,从而形成层16。最后,形成层10的顶面部分。

但是,本发明并不仅仅限于图21A和21B所示的结构。例如,第四遮光层16可以形成于第一夹层介电层10上,之后,还可以另外形成第二夹层介电层,以覆盖层16。最终,所形成的第二夹层介电层12可以覆盖附加的介电层。

第八实施例

图22A和22B示出了依据本发明第八实施例的TFT矩阵基底30G的结构,它们分别是沿图4中的线VA-VA和VB-VB剖开的。

通过将第四遮光层16添加到图4、5A和5B的TFT矩阵基底30上,从而可以得到第八实施例的基底30G。基底30G的其他结构与基底30相同。可以说,通过将第二遮光层5添加到图21A和21B的第七实施例的结构30F,从而可以得到基底结构30G。

由于在TFT 31的每一侧(即在顶侧和底侧)都设置了第四和第二遮光层16和5,因此可以在TFT 31的每一侧都获得遮光效果。这样,就存在一个附加的优点,即能得到比第一和第七实施例还要好的遮光效果。

第九实施例

图23A和23B示出了依据本发明第九实施例的TFT矩阵基底30H的结构,它们分别是沿图15中的线XVIA-XVIA和XVIB-XVIB剖开的。

通过从图16A和16B的第四实施例的TFT矩阵基底30C中,去除第二遮光层5C,并通过向其中添加第四遮光层16’,可以得到第九实施例的基底30H。基底30H的其他结构与基底30C相同。由于去除了第二遮光层5C,因此,在TFT矩阵基底30C内,可以去除SiO2层4或6。

第四遮光层16’的图案或平面结构与图15所示的第二遮光层5C的相同,它覆盖了每一个TFT 31的几乎所有的多晶硅有源层7。层16’没有覆盖靠近接触孔22的层7的部分。

第四遮光层16’埋于第二夹层介电层12中。如果层12具有两层结构,则这一点非常容易实现。特别是,当形成层12的底面部分之后,就在该底面部分上形成用于层16’的非晶硅层。之后,在非晶硅层上形成图案,以形成层16’。最后,形成层12的顶面部分。

但是,本发明并不仅仅限制于图23A和23B所示的结构。例如,第四遮光层16’可以形成与第二夹层介电层12之上,之后,可以形成一个附加的介电层,以覆盖层16’。最后,可以形成第三夹层介电层14,以覆盖附加的介电层。

第十实施例

图24A和24B示出了依据本发明第十实施例的TFT矩阵基底30I,它们分别是沿图4中的线VA-VA和VB-VB剖开的。

可以通过将第四遮光层16’添加到图15、16A和16B的TFT矩阵基底30C上,得到第十实施例的基底30I。基底30I的其他结构与基底30C相同。可以说是通过将第二遮光层5C添加到图23A和23B的基底30H,而得到基底30I的。

由于在TFT 31的每一侧(即在顶侧和底侧)都提供了第四和第二遮光层16’和5C,因此可以在TFT 31的每一侧都获得遮光效果。这样,存在一个附加的优点,即能得到比第一和第七实施例还要好的遮光效果。

图25示出了像素矩阵部分内所提供的TFT 31的光致电流泄漏,与在有源层和第二遮光层之间的介电层厚度之间的关系,这种关系是在投影光的特定照射条件下得到的。

正如可以从图25中看到的那样,利用仅仅具有第一和第三遮光层的先有技术的TFT矩阵基底100(参见图1、2A和2B),则光致电流泄漏为4pA。另一方面,依据本发明第四实施例,使用具有第二遮光层,同时还有第一和第三遮光层的TFT矩阵基底30C(参见图15、16A和16B),则随着有源层和第二遮光层之间的介电层厚度从500nm开始逐渐减小,光致电流泄漏也逐渐减小。泄漏值的最大值减小到先有技术基底100的泄漏值的大约1/3。

此外,正如可以从图25中看到的那样,电流泄漏的降低效果,与有源层和第二遮光层之间的介电层的厚度有关。随着这一厚度从500nm开始降低,这一效果增加。但是尽管没有示于图25中,但是一般将这一厚度值设定为小于100nm,TFT 31的导通特性以及在激光退火工艺中的有源层7的结晶度受到很大影响,结果由于TFT 31的导通特性恶化,而使TFT 31不能正常工作。依据这一测试结果,我们发现,最好将我们所讨论的介电层厚度设定为从500nm到100nm的范围内的一个值。

依据本发明的第十实施例,利用具有第二和第四遮光层,同时还有第一和第三遮光层的TFT矩阵基底30I(参见图24A和24B),光致电流泄漏值减小到依据第四实施例的基底30C的大约1/2。这样,通过添加第四遮光层,同时还有第二遮光层,能够保证可以获得抑制泄漏的更好效果。

第十一实施例

一般而言,当激光照射到非晶硅层上,以形成多晶硅有源层时(换言之,当利用激光退火工艺而从非晶硅层获得多晶硅有源层时),如果具有高热传导性的基底直接位于非晶硅层之下,则由激光照射而进行的加热和冷却工艺,将会从其所需要的一个开始改变。结果,产生了一个问题,即严重影响了对非晶硅层的结晶处理。为避免这一问题,一般来说,在非晶硅层和热传导基底之间设置一个具有足够厚度的介电层,从而使它们充分隔离开。

另一方面,我们了解,像素矩阵部分61和驱动电路部分62可以形成于同一基底上,例如象图26所示的TFT矩阵基底60上。在这种情况下,驱动电路部分62内的TFT必须具有晶体管特性中的高迁移率。与此不同,像素矩阵部分61中的TFT不需要高迁移率;它们需要在晶体管特性内的低电流泄漏。为减小光致电流泄漏,最好是用包含相对较多的用作再组合中心的许多陷阱(trap)的硅材料。考虑到这一点,对于像素矩阵部分61内的TFT,多晶硅材料最好具有低结晶度。

因此,利用依据本发明第十一实施例的TFT矩阵基底60,具有依据第一到第十实施例的第二和/或第四遮光层的TFT 31,用作像素矩阵部分61。与此同时,对于驱动电路部分62,使用不具有第二和/或第四遮光层的TFT。这样,对于61部分内的TFT,可以利用第二和/或第四遮光层而快速传播由激光产生的热。结果,形成具有低结晶度的多晶硅层,使其仅仅用于像素矩阵部分61内的TFT的有源层。这意味着可以进一步地抑制光致电流泄漏,这不仅仅是因为存在第二和/或第四遮光层,而且还由于多晶硅层的结晶水平。

等同变换

毋庸置疑,本发明并不仅仅被限制为上述第一到第十一实施例,这是因为这些实施例是本发明的优选的几个实施例。在不脱离本发明主旨的情况下,可以对它们进行改变或修改。

例如,在第一到第六实施例中,第一遮光层3是通过SiO2层2形成于所述透明板1之上的。但是,也可以使第一遮光层3直接形成于透明板1之上,而不需要SiO2层2,这取决于板1的材料。在第三和第六实施例中,第二遮光层5B和5E可以由非晶硅制成,同时,也可以不将恒压Vc加到层5B和5E上。在第一和第四实施例中,第二遮光层5和5C可以由多晶硅构成。在第二、第三、第五以及第六实施例中,第二遮光层5A、5B、5D以及5E可以由掺杂杂质的非晶硅构成。这些情况也适用于第七到第十一实施例。

第二和第四遮光层可以由上述材料之外的任何其它材料构成,只要这种材料吸光,可以加到TFT矩阵基底上就成。

尽管已经说明了本发明的最佳形式,但应当理解,任何不脱离本发明主旨的修改对本领域技术人员来说都是显而易见的。因此,本发明的范围完全由权利要求书所确定。

Claims (25)

1. 一种TFT矩阵基底,包括:

(a)一个透明板;

(b)以成行成列的矩阵阵列形式排列于所述板上的TFT;

每一个TFT都具有第一源极/漏极区、第二源极/漏极区,以及有源层;

(c)以这样一种方式形成于所述板上的栅极线,以便能沿着所述矩阵的行方向延伸;

(d)以这样一种方式形成于所述板上的数据线,以便能沿着所述矩阵的列方向延伸;

每一条数据线都电连接到相应的一个TFT的第一源极/漏极区;

(e)形成于所述板上的像素区内的像素电极;

每一个像素电极都电连接到相应一个TFT的第二源极/漏极区;

(f)具有图案的第一遮光层,以这样一种方式形成于所述板和TFT之间,以便与TFT的所述有源层相重叠;

(g)形成于所述第一遮光层和所述TFT之间的具有图案的第二遮光层;

所述第二遮光层具有吸光特性;

(h)具有图案的第三遮光层,形成它以便覆盖相对于所述TFT来说是位于所述板的对侧上的TFT;

所述第三遮光层具有沿着所述矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分。

2. 依据权利要求1所述的基底,其中所述每一个TFT都具有一个沟道区和一个LDD区;

所述第二遮光层具有覆盖TFT的所述沟道区的第一部分,以及覆盖TFT的所述LDD区的第二部分。

3. 依据权利要求1的基底,其中所述第二遮光层是由含有硅的材料制成的。

4. 依据权利要求1的基底,其中所述第二遮光层具有导电性;

所述第二遮光层具有允许施加恒定电压的结构。

5. 依据权利要求1的基底,其中所述第二遮光层具有导电性,并电连接至所述栅极线。

6. 依据权利要求1的基底,其中所述第二遮光层是由掺杂有杂质的硅制成的。

7. 依据权利要求1的基底,其中所述栅极线以这样一种方式排列,从而能与相应的TFT的沟道区相重叠;

其中所述栅极线在与TFT的重叠区,具有TFT的栅极的功能。

8. 依据权利要求1的基底,还包括是与栅极线分开的、为各个TFT单独形成的若干栅极;

其中,所述栅极线电连接至相应的栅极。

9. 依据权利要求1的基底,其中夹在所述第二遮光层和TFT的所述有源层之间的介电层,具有从100nm到500nm的厚度范围。

10. 依据权利要求1的基底,其中夹在所述第二遮光层和TFT的所述有源层之间的介电层,具有从150nm到300nm的厚度范围。

11. 依据权利要求1的基底,其中除了提供像素矩阵部分之外,还提供了包含TFT的驱动器电路部分,而TFT以矩阵阵列形式排列;

其中,所述第二遮光层是为所述像素矩阵部分中的TFT所设置的,所述第二遮光层不是为所述驱动器电路部分内的TFT而设置的。

12. 一种有源矩阵寻址LCD设备,包括:

(a)依据权利要求1的一种TFT矩阵基底;

(b)与所述TFT矩阵基底相对设置的一个对置基底;以及

(c)在所述TFT矩阵基底和所述对置基底之间形成的一个液晶层。

13. 一种TFT矩阵基底,包括:

(a)透明板;

(b)以成行成列的矩阵形式排列于所述板之上的若干TFT;

每一个TFT都具有第一源极/漏极区、第二源极/漏极区,以及有源层;

(c)以这样一种方式形成于所述板上的若干栅极线,以便能沿着所述阵列的行延伸;

(d)以这样一种方式形成于所述板上的若干数据线,以便能沿着所述阵列的列延伸;

每一条数据线都与相应的一个TFT的第一源极/漏极区电连接;

(e)每一条像素电极都与相应的一个TFT的第二源极/漏极区电连接;

(f)具有图案的第一遮光层以这样一种方式形成于所述板和所述TFT之间,以便与所述TFT的有源层相重叠;

(g)形成具有图案的第三遮光层,以便覆盖相对于所述TFT来说位于所述板的对侧上的TFT;

所述第三遮光层具有沿着所述矩阵的行延伸的第一部分,以及沿着其列延伸的第二部分;以及

(h)具有图案的第四遮光层形成于所述TFT和所述第三遮光层之间;

所述第四遮光层具有吸光特性。

14. 依据权利要求13的基底,其中所述每一个TFT都具有沟道区和LDD区;

其中所述第四遮光层具有覆盖所述TFT的沟道区的第一部分,以及覆盖其LDD区的第二部分。

15. 依据权利要求13的基底,其中所述第四遮光层是由包含硅的材料制成的。

16. 依据权利要求13的基底,其中所述第四遮光层具有导电性;所述第四遮光层具有允许施加恒定电压的结构。

17. 依据权利要求13的基底,其中所述第四遮光层具有导电性,并与所述栅极线电连接。

18. 依据权利要求13的基底,其中所述第四遮光层是由掺杂有杂质的硅构成的。

19. 依据权利要求13的基底,其中所述栅极线以与相应的TFT的沟道区相重叠的方式排列;

而其中的栅极线在它们的重叠部分具有TFT的栅极的功能。

20. 依据权利要求13的基底,其中分别为与栅极线分开的各个TFT形成各栅极;

其中所述栅极线电连接至相应的所述各栅极。

21. 依据权利要求13的基底,还包括形成于所述第一遮光层和TFT之间的具有图案的第二遮光层;

其中所述第二遮光层具有吸光特性。

22. 依据权利要求21的基底,其中夹在所述第二遮光层和所述TFT的有源层之间的电介质具有从100nm到500nm的厚度范围。

23. 依据权利要求21的基底,其中夹在所述第二遮光层和所述TFT的有源层之间的电介质具有从150nm到300nm的厚度范围。

24. 依据权利要求21的基底,其中除了提供像素矩阵部分之外,还提供了包括TFT的驱动器电路部分,其中所述TFT以矩阵形式排列;

其中所述第二遮光层是为所述像素矩阵部分中的TFT提供的,所述第二遮光层不是为所述驱动电路部分内的TFT提供的。

25. 一种有源矩阵寻址LCD驱动器,包括:

(a)依据权利要求13的TFT矩阵基底;

(b)与所述TFT矩阵基底相对放置的对置基底;以及

(c)形成于所述TFT矩阵基底和所述对置基底之间的液晶层。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001235699 | 2001-08-03 | ||

| JP235699/2001 | 2001-08-03 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1402538A CN1402538A (zh) | 2003-03-12 |

| CN100409087C true CN100409087C (zh) | 2008-08-06 |

Family

ID=19067099

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB021277796A Expired - Lifetime CN100409087C (zh) | 2001-08-03 | 2002-08-05 | Tft矩阵基底以及有源矩阵寻址液晶显示器件 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7027109B2 (zh) |

| EP (1) | EP1282001A3 (zh) |

| CN (1) | CN100409087C (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107256872A (zh) * | 2017-07-10 | 2017-10-17 | 厦门天马微电子有限公司 | 一种阵列基板及其制作方法、显示面板、显示装置 |

Families Citing this family (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4423659B2 (ja) * | 2003-01-31 | 2010-03-03 | 日本電気株式会社 | 薄膜トランジスタ、tft基板、及び、液晶表示装置 |

| KR20060001662A (ko) * | 2004-06-30 | 2006-01-06 | 엘지.필립스 엘시디 주식회사 | 수평전계방식 액정표시소자 및 그 제조방법 |

| US20070171379A1 (en) * | 2006-01-26 | 2007-07-26 | Chunghwa Picture Tubes, Ltd | Projection system of changing environment influence on display |

| US8036653B2 (en) * | 2006-05-23 | 2011-10-11 | The Boeing Company | Establishing and conducting communications within a network |

| US7583641B2 (en) | 2006-05-23 | 2009-09-01 | The Boeing Company | Methods and apparatus for network joining using a multiple message per TDMA control slot methodology |

| TWI358832B (en) * | 2007-02-26 | 2012-02-21 | Au Optronics Corp | Semiconductor device and manufacturing method ther |

| WO2011074338A1 (ja) | 2009-12-17 | 2011-06-23 | シャープ株式会社 | 半導体装置、アクティブマトリクス基板、及び表示装置 |

| JP5692699B2 (ja) * | 2010-02-15 | 2015-04-01 | Nltテクノロジー株式会社 | 薄膜トランジスタ、その製造方法、及び表示装置並びに電子機器 |

| JP2011253921A (ja) | 2010-06-02 | 2011-12-15 | Mitsubishi Electric Corp | アクティブマトリックス基板及び液晶装置 |

| CN102338956A (zh) * | 2011-08-31 | 2012-02-01 | 深圳市华星光电技术有限公司 | 薄膜晶体管阵列基板 |

| CN102368499B (zh) * | 2011-10-27 | 2014-04-16 | 深圳市华星光电技术有限公司 | Tft阵列基板及液晶面板 |

| WO2013119215A1 (en) | 2012-02-08 | 2013-08-15 | Empire Technology Development Llc | Coating a substance with graphene |

| CN103543565A (zh) * | 2012-07-13 | 2014-01-29 | 群康科技(深圳)有限公司 | 显示器 |

| US20140070225A1 (en) * | 2012-09-07 | 2014-03-13 | Apple Inc. | Hydrogenation and Crystallization of Polycrystalline Silicon |

| KR102155051B1 (ko) * | 2014-04-29 | 2020-09-11 | 엘지디스플레이 주식회사 | 액정 디스플레이 장치와 이의 제조 방법 |

| CN104409512A (zh) * | 2014-11-11 | 2015-03-11 | 深圳市华星光电技术有限公司 | 基于双栅极结构的低温多晶硅薄膜晶体管及其制备方法 |

| CN104503132A (zh) * | 2015-01-08 | 2015-04-08 | 京东方科技集团股份有限公司 | 一种阵列基板及显示装置 |

| CN104656333A (zh) * | 2015-03-18 | 2015-05-27 | 深圳市华星光电技术有限公司 | Coa型液晶面板的制作方法及coa型液晶面板 |

| CN110571227B (zh) * | 2015-04-15 | 2021-12-07 | 群创光电股份有限公司 | 显示面板 |

| CN105097831B (zh) * | 2015-06-23 | 2019-03-29 | 京东方科技集团股份有限公司 | 低温多晶硅背板及其制造方法和发光器件 |

| CN104914615A (zh) | 2015-06-29 | 2015-09-16 | 京东方科技集团股份有限公司 | 一种显示装置及其制造方法 |

| CN104979405B (zh) * | 2015-07-22 | 2019-05-21 | 京东方科技集团股份有限公司 | 一种薄膜晶体管、阵列基板及显示装置 |

| TWI578509B (zh) * | 2015-07-23 | 2017-04-11 | 友達光電股份有限公司 | 畫素結構 |

| KR102374537B1 (ko) * | 2015-08-21 | 2022-03-15 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102558900B1 (ko) * | 2015-10-23 | 2023-07-25 | 엘지디스플레이 주식회사 | 표시장치와 이의 제조방법 |

| US10088727B2 (en) * | 2015-10-29 | 2018-10-02 | Seiko Epson Corporation | Liquid crystal device and electronic apparatus |

| CN105425489B (zh) * | 2016-01-04 | 2018-11-02 | 京东方科技集团股份有限公司 | 阵列基板及其制作方法、显示装置 |

| CN105700745A (zh) | 2016-01-08 | 2016-06-22 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法、驱动方式、触摸屏、显示装置 |

| CN108701720B (zh) * | 2016-02-24 | 2021-09-21 | 夏普株式会社 | 薄膜晶体管基板和显示面板 |

| CN105652548A (zh) * | 2016-04-05 | 2016-06-08 | 深圳市华星光电技术有限公司 | 一种阵列基板及液晶显示面板 |

| US10185190B2 (en) * | 2016-05-11 | 2019-01-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device, module, and electronic device |

| CN106444197B (zh) * | 2016-11-30 | 2020-06-19 | 厦门天马微电子有限公司 | 一种阵列基板、显示面板以及显示装置 |

| JP6999272B2 (ja) | 2017-01-20 | 2022-01-18 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN108807418A (zh) * | 2017-04-28 | 2018-11-13 | 京东方科技集团股份有限公司 | 显示基板及其制造方法和显示装置 |

| JP6597768B2 (ja) | 2017-12-27 | 2019-10-30 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP6690671B2 (ja) * | 2018-06-20 | 2020-04-28 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP6702387B2 (ja) | 2018-10-08 | 2020-06-03 | セイコーエプソン株式会社 | 電気光学装置、電子機器 |

| TWI714266B (zh) * | 2019-09-18 | 2020-12-21 | 力晶積成電子製造股份有限公司 | 影像感測器 |

| US11682681B2 (en) | 2019-10-17 | 2023-06-20 | Sharp Kabushiki Kaisha | Active matrix substrate and method for manufacturing same |

| CN111128878B (zh) * | 2019-12-25 | 2022-07-12 | Tcl华星光电技术有限公司 | 薄膜晶体管的图案制作方法、薄膜晶体管以及光罩 |

| CN111190306B (zh) * | 2020-02-27 | 2022-07-15 | 京东方科技集团股份有限公司 | 显示装置 |

| US11631704B2 (en) * | 2020-04-21 | 2023-04-18 | Sharp Kabushiki Kaisha | Active matrix substrate and display device |

| CN111812882B (zh) * | 2020-07-03 | 2023-06-02 | Tcl华星光电技术有限公司 | 显示面板及显示装置 |

| CN112002703B (zh) * | 2020-08-07 | 2022-07-12 | 武汉华星光电技术有限公司 | 阵列基板以及液晶显示面板 |

| JP2022139567A (ja) * | 2021-03-12 | 2022-09-26 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| CN114023764A (zh) * | 2021-10-20 | 2022-02-08 | 武汉华星光电半导体显示技术有限公司 | 显示面板及显示装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08313933A (ja) * | 1995-05-19 | 1996-11-29 | Sanyo Electric Co Ltd | 液晶表示装置 |

| CN1205087A (zh) * | 1996-10-16 | 1999-01-13 | 精工爱普生株式会社 | 液晶装置用的基板、液晶装置和投射型显示装置 |

| US6067140A (en) * | 1997-03-03 | 2000-05-23 | Lg Electronics Inc. | Liquid crystal display device and method of manufacturing same |

| CN1258357A (zh) * | 1998-03-19 | 2000-06-28 | 精工爱普生株式会社 | 液晶装置以及投射型显示装置 |

| US6184963B1 (en) * | 1987-06-10 | 2001-02-06 | Hitachi, Ltd. | TFT active matrix LCD devices employing two superposed conductive films having different dimensions for the scanning signal lines |

| JP2001075504A (ja) * | 1999-08-31 | 2001-03-23 | Seiko Epson Corp | 電気光学装置、電気光学装置の製造方法及び電子機器 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0824193B2 (ja) | 1990-10-16 | 1996-03-06 | 工業技術院長 | 平板型光弁駆動用半導体装置の製造方法 |

| JP3112361B2 (ja) | 1992-11-19 | 2000-11-27 | シャープ株式会社 | 表示装置用薄膜トランジスタ基板およびそれを用いた液晶表示装置 |

| KR980003739A (ko) * | 1996-06-14 | 1998-03-30 | 구자홍 | 박막트랜지스터 어레이 기판 및 그 제조방법 |

| JP4021014B2 (ja) | 1997-09-11 | 2007-12-12 | セイコーエプソン株式会社 | 液晶表示パネル及び薄膜トランジスタアレイ基板 |

| JP3736122B2 (ja) | 1998-06-23 | 2006-01-18 | セイコーエプソン株式会社 | 液晶装置及び電子機器 |

| JP3141860B2 (ja) | 1998-10-28 | 2001-03-07 | ソニー株式会社 | 液晶表示装置の製造方法 |

| JP3107075B2 (ja) | 1998-12-14 | 2000-11-06 | 日本電気株式会社 | 液晶表示装置 |

| JP3332083B2 (ja) | 1999-04-16 | 2002-10-07 | 日本電気株式会社 | 液晶表示装置 |

| JP3501125B2 (ja) | 2000-03-17 | 2004-03-02 | セイコーエプソン株式会社 | 電気光学装置 |

| JP2002108248A (ja) | 2000-07-26 | 2002-04-10 | Seiko Epson Corp | 電気光学装置、電気光学装置用基板及び投射型表示装置 |

| JP3608531B2 (ja) | 2000-08-31 | 2005-01-12 | セイコーエプソン株式会社 | 電気光学装置及び投射型表示装置 |

-

2002

- 2002-08-02 US US10/209,870 patent/US7027109B2/en not_active Expired - Lifetime

- 2002-08-03 EP EP02090286A patent/EP1282001A3/en not_active Withdrawn

- 2002-08-05 CN CNB021277796A patent/CN100409087C/zh not_active Expired - Lifetime

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6184963B1 (en) * | 1987-06-10 | 2001-02-06 | Hitachi, Ltd. | TFT active matrix LCD devices employing two superposed conductive films having different dimensions for the scanning signal lines |

| JPH08313933A (ja) * | 1995-05-19 | 1996-11-29 | Sanyo Electric Co Ltd | 液晶表示装置 |

| CN1205087A (zh) * | 1996-10-16 | 1999-01-13 | 精工爱普生株式会社 | 液晶装置用的基板、液晶装置和投射型显示装置 |

| US6067140A (en) * | 1997-03-03 | 2000-05-23 | Lg Electronics Inc. | Liquid crystal display device and method of manufacturing same |

| CN1258357A (zh) * | 1998-03-19 | 2000-06-28 | 精工爱普生株式会社 | 液晶装置以及投射型显示装置 |

| JP2001075504A (ja) * | 1999-08-31 | 2001-03-23 | Seiko Epson Corp | 電気光学装置、電気光学装置の製造方法及び電子機器 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107256872A (zh) * | 2017-07-10 | 2017-10-17 | 厦门天马微电子有限公司 | 一种阵列基板及其制作方法、显示面板、显示装置 |

| CN107256872B (zh) * | 2017-07-10 | 2019-11-26 | 厦门天马微电子有限公司 | 一种阵列基板及其制作方法、显示面板、显示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20030025848A1 (en) | 2003-02-06 |

| US7027109B2 (en) | 2006-04-11 |

| CN1402538A (zh) | 2003-03-12 |

| EP1282001A2 (en) | 2003-02-05 |

| EP1282001A3 (en) | 2004-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100409087C (zh) | Tft矩阵基底以及有源矩阵寻址液晶显示器件 | |

| EP1132765B1 (en) | Liquid crystal device | |

| US6573955B2 (en) | Capacitance substrate for a liquid crystal device and a projection type display device | |

| JP3605823B2 (ja) | 薄膜トランジスタ・アレイ基板およびアクティブマトリックス型液晶表示装置 | |

| JP3386017B2 (ja) | 液晶表示装置用の薄膜トランジスタの製造方法 | |

| US6567136B1 (en) | Liquid crystal display device | |

| KR100249710B1 (ko) | 액정표시장치 | |

| KR100375518B1 (ko) | 액정디스플레이 | |

| US7494851B2 (en) | Thin film transistor array substrate and method for manufacturing the same | |

| KR100429369B1 (ko) | 박막트랜지스터로 향하는 광선을 차광막으로 차단하는 투과액정패널, 이 투과액정패널을 구비한 화상표시장치, 및 이 투과액정패널의 제조방법 | |

| JP3914753B2 (ja) | アクティブマトリクス型液晶表示装置およびスイッチング素子 | |

| JP3767696B2 (ja) | 薄膜トランジスタ・アレイ基板およびアクティブマトリックス型液晶表示装置 | |

| KR100247269B1 (ko) | 액정 표시 장치 | |

| JP2000196094A (ja) | 薄膜トランジスタ基板および液晶表示装置 | |

| JP2001209067A (ja) | 液晶表示装置 | |

| JPH11121755A (ja) | 薄膜半導体装置 | |

| JP2007094433A (ja) | アクティブマトリクス型液晶表示装置およびスイッチング素子 | |

| KR20000014536A (ko) | 다결정 규소 액정 표시 장치 | |

| JP2002134753A (ja) | 薄膜トランジスタ及びそれを用いた液晶表示装置 | |

| JP2004258671A (ja) | 液晶装置及び投写型表示装置 | |

| JP2000114528A (ja) | 薄膜トランジスタの製造方法および電気光学装置の製造方法 | |

| JP2003179235A (ja) | 液晶表示装置用の薄膜トランジスタ及びアクテイブマトリクス型液晶表示装置 | |

| JP2008244050A (ja) | 電気光学装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: JINZHEN CO., LTD. Free format text: FORMER OWNER: NEC CORP. Effective date: 20130409 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20130409 Address after: Samoa Apia hiSoft Center No. 217 mailbox Patentee after: Jinzhen Co.,Ltd. Address before: Tokyo, Japan Patentee before: NEC Corp. |

|

| CX01 | Expiry of patent term |

Granted publication date: 20080806 |

|

| CX01 | Expiry of patent term |