JP7013119B2 - 固体撮像素子、固体撮像素子の製造方法、及び撮像システム - Google Patents

固体撮像素子、固体撮像素子の製造方法、及び撮像システム Download PDFInfo

- Publication number

- JP7013119B2 JP7013119B2 JP2016143096A JP2016143096A JP7013119B2 JP 7013119 B2 JP7013119 B2 JP 7013119B2 JP 2016143096 A JP2016143096 A JP 2016143096A JP 2016143096 A JP2016143096 A JP 2016143096A JP 7013119 B2 JP7013119 B2 JP 7013119B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- photoelectric conversion

- conversion unit

- transfer transistor

- conductive type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 9

- 238000012546 transfer Methods 0.000 claims description 146

- 238000006243 chemical reaction Methods 0.000 claims description 141

- 238000000926 separation method Methods 0.000 claims description 90

- 239000004065 semiconductor Substances 0.000 claims description 61

- 238000009792 diffusion process Methods 0.000 claims description 57

- 239000012535 impurity Substances 0.000 claims description 55

- 230000003321 amplification Effects 0.000 claims description 23

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 23

- 238000003384 imaging method Methods 0.000 claims description 11

- 238000000034 method Methods 0.000 claims description 7

- 238000010586 diagram Methods 0.000 description 16

- 230000000694 effects Effects 0.000 description 9

- 238000001514 detection method Methods 0.000 description 6

- 238000009826 distribution Methods 0.000 description 6

- 230000004888 barrier function Effects 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 238000005036 potential barrier Methods 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 230000001629 suppression Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000010884 ion-beam technique Methods 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/148—Charge coupled imagers

- H01L27/14806—Structural or functional details thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

- H01L27/14605—Structural or functional details relating to the position of the pixel elements, e.g. smaller pixel elements in the center of the imager compared to pixel elements at the periphery

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

分離領域を形成する際には、注入する不純物がレジストの側壁等に衝突してエネルギーを失い、分離領域の上方の半導体領域において不純物濃度が高くなってしまういわゆるレジスト近接効果が発生することが知られている(例えば、特許文献2参照)。特に、固体撮像素子の微細化に伴って隣接する画素間の距離が短くなると、トランジスタ等が配される半導体領域の面積も小さくなるため、レジスト近接効果による影響が無視できなくなる。

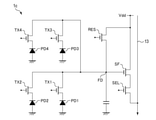

図1~図5を参照しながら、第1実施形態に係る固体撮像素子について説明する。図1は、第1実施形態に係る固体撮像素子における画素1の等価回路を示す概略図である。

次に、図6~図8を参照しながら、第2実施形態に係る固体撮像素子について説明する。第1実施形態では、1つの画素1が1つの光電変換部PDを有する構成について説明した。これに対し本実施形態では、1つの画素1が2つの光電変換部を有する構成について説明する。以下、第1実施形態と異なる構成を中心に説明する。

次に、図9~図11を参照しながら、第3実施形態に係る固体撮像素子について説明する。本実施形態では、複数の光電変換部が、共通のドレイン領域dTXを通る対称軸に対して互いに線対称に配置される。以下、第2実施形態と異なる構成を中心に説明する。

次に、図12を参照しながら、第4実施形態に係る撮像システム1200について説明する。本実施形態の撮像システム1200は、第1~第3実施形態の固体撮像素子を備えるものであり、例えば、デジタルスチルカメラ、デジタルカムコーダー、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、撮像システム1200には、レンズなどの光学系と固体撮像素子とを備えるカメラモジュールも含まれる。図12には、撮像システム1200の一例としてデジタルスチルカメラのブロック図を示す。図12に示す撮像システム1200は、レンズ保護バリア1206、レンズ1202、絞り1204、固体撮像素子1201、信号処理部1208を備える。また、タイミング発生部1210、全体制御・演算部1212、メモリ部1214、記録媒体制御I/F部1216、記録媒体1220、外部I/F部1218を備える。

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。例えば、上述の実施形態では、トランジスタの多数キャリアの導電型(第1導電型)がn型であり、少数キャリアの導電型(第2導電型)がp型であることを想定したが、多数キャリアの導電型と少数キャリアの導電型とが逆であってもよい。また、上述の各実施形態は、組み合わせて適用することも可能である。

11 :第1半導体領域

12 :第2半導体領域

13 :列信号線

100 :ウェル領域

101 :n型領域

102 :p型領域

104 :画素分離部

105 :コンタクト

106 :延長部

111 :第1分離領域

112 :第3分離領域

121 :第2分離領域

122 :第4分離領域

113 :カウンタードープ領域

PD :光電変換部

FD :浮遊拡散部

RES :リセットトランジスタ

SEL :選択トランジスタ

SF :増幅トランジスタ

TX :転送トランジスタ

Claims (12)

- 入射光を光電変換して生じた電荷を蓄積する光電変換部と、前記光電変換部から浮遊拡散部へ前記電荷を転送するMOS型の転送トランジスタと、前記浮遊拡散部に転送された前記電荷の量に応じた信号を出力する出力部とを、第2導電型のウェル領域に配した画素を備える固体撮像素子であって、

前記ウェル領域の第1半導体領域において、

前記転送トランジスタの第1導電型のドレイン領域の下方の深い領域に形成され、第2導電型の不純物濃度が前記ウェル領域よりも高い第2導電型の第1分離領域と、

前記第1半導体領域の上面から前記光電変換部の第1導電型の不純物濃度がピークとなる深さ位置までの領域に、前記ドレイン領域を囲むように形成され、第1導電型の不純物濃度が前記ドレイン領域よりも低い第1導電型のカウンタードープ領域とを有し、

平面視において前記第1半導体領域と直交する方向に延びる第2半導体領域において、

前記出力部が有する複数のトランジスタのチャネル領域に形成された第1導電型の埋め込みチャネル領域と、

前記埋め込みチャネル領域の下方の深い領域に形成され、第2導電型の不純物濃度が前記ウェル領域よりも高い第2導電型の第2分離領域と

を有し、

前記カウンタードープ領域の下面の深さ位置が、前記埋め込みチャネル領域の下面の深さ位置よりも深く、

前記第1半導体領域の前記第1分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第3分離領域を更に有し、

前記第2半導体領域の前記第2分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第4の分離領域を更に有し、

前記光電変換部は、第1光電変換部及び第2光電変換部を含み、

前記転送トランジスタは、前記ドレイン領域を共用する第1転送トランジスタ及び第2転送トランジスタを含み、前記第1転送トランジスタは前記第1光電変換部から前記浮遊拡散部へ前記電荷を転送し、前記第2転送トランジスタは前記第2光電変換部から前記浮遊拡散部へ前記電荷を転送し、

前記第1転送トランジスタ及び前記第2転送トランジスタは、前記光電変換部と前記ドレイン領域の間のチャネル領域の上方に、絶縁膜を介して形成された第1ゲート電極及び第2ゲート電極をそれぞれ有し、

前記ドレイン領域は、平面視における前記第1ゲート電極と前記第2ゲート電極との間に延長部を有し、

前記延長部の下面の深さ位置が、前記ドレイン領域の下面の深さ位置よりも浅いことを特徴とする固体撮像素子。 - 前記転送トランジスタは、前記光電変換部と前記ドレイン領域の間のチャネル領域の上方に、絶縁膜を介して形成されたゲート電極を更に有し、

前記カウンタードープ領域が、平面視において前記ゲート電極と一部重なっている

ことを特徴とする請求項1に記載の固体撮像素子。 - 前記複数のトランジスタは、

前記浮遊拡散部に転送された前記電荷の量に応じた信号を出力する増幅トランジスタと、

前記浮遊拡散部に転送された前記電荷をリセットするリセットトランジスタと、

前記増幅トランジスタが出力する信号を列信号線に出力する選択トランジスタと、

を含む

ことを特徴とする請求項1または2に記載の固体撮像素子。 - 前記光電変換部は、前記第1光電変換部及び第3光電変換部を含み、

前記転送トランジスタは、前記ドレイン領域を共用する前記第1転送トランジスタ及び第3転送トランジスタを含み、前記第1転送トランジスタは前記第1光電変換部から前記浮遊拡散部へ前記電荷を転送し、前記第3転送トランジスタは前記第3光電変換部から前記浮遊拡散部へ前記電荷を転送し、

前記第1光電変換部と前記第3光電変換部とは、平面視において、前記ドレイン領域を通る線を対称軸として互いに線対称に配置されている

ことを特徴とする請求項1または2に記載の固体撮像素子。 - 隣接する画素との境界部に形成された画素分離部を更に有し、前記画素分離部が、前記ドレイン領域及び前記カウンタードープ領域と接していない

ことを特徴とする請求項4に記載の固体撮像素子。 - 光電変換部と、前記光電変換部から浮遊拡散部へ電荷を転送する転送トランジスタと、前記浮遊拡散部に転送された前記電荷の量に応じた信号を出力する出力部とを、第2導電型のウェル領域に配した画素と、

第1の方向に延びる第1半導体領域と、

平面視において前記第1の方向に直交する第2の方向に延びる第2半導体領域と

を備える固体撮像素子であって、

前記第1半導体領域が、

第1導電型の前記浮遊拡散部の下方に形成された前記第2導電型の第1分離領域と、

前記浮遊拡散部を囲い、前記浮遊拡散部の前記第1導電型の不純物濃度よりも低い前記第1導電型の不純物濃度を有する、第1導電型の第1カウンタードープ領域と、

を有し、

前記第2半導体領域が、

前記出力部が有する複数のトランジスタのチャネル領域に形成された第1導電型の第2カウンタードープ領域と、

前記第2カウンタードープ領域の下方に形成された第2導電型の第2分離領域と

を有し、

前記第1カウンタードープ領域の下面の深さ位置が、前記第2カウンタードープ領域の下面の深さ位置よりも深く、

前記第1半導体領域の前記第1分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第3分離領域を更に有し、

前記第2半導体領域の前記第2分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第4の分離領域を更に有し、

前記光電変換部は、第1光電変換部及び第2光電変換部を含み、

前記転送トランジスタは、ドレイン領域を共用する第1転送トランジスタ及び第2転送トランジスタを含み、前記第1転送トランジスタは前記第1光電変換部から前記浮遊拡散部へ前記電荷を転送し、前記第2転送トランジスタは前記第2光電変換部から前記浮遊拡散部へ前記電荷を転送し、

前記第1転送トランジスタ及び前記第2転送トランジスタは、前記光電変換部と前記ドレイン領域の間のチャネル領域の上方に、絶縁膜を介して形成された第1ゲート電極及び第2ゲート電極をそれぞれ有し、

前記ドレイン領域は、平面視における前記第1ゲート電極と前記第2ゲート電極との間に延長部を有し、

前記延長部の下面の深さ位置が、前記ドレイン領域の下面の深さ位置よりも浅いことを特徴とする固体撮像素子。 - 前記転送トランジスタは、前記光電変換部と前記浮遊拡散部の間のチャネル領域の上方に、絶縁膜を介して形成されたゲート電極を更に有し、

前記第1カウンタードープ領域が、平面視において前記ゲート電極と一部重なっている

ことを特徴とする請求項6に記載の固体撮像素子。 - 前記出力部の前記複数のトランジスタは、

前記浮遊拡散部に転送された前記電荷の量に応じた信号を出力する増幅トランジスタと、

前記浮遊拡散部に転送された前記電荷をリセットするリセットトランジスタと、

前記増幅トランジスタが出力する信号を列信号線に出力する選択トランジスタと、

を含む

ことを特徴とする請求項6または7に記載の固体撮像素子。 - 前記延長部の下面の深さ位置が、前記第1カウンタードープ領域の下面の深さ位置よりも浅い

ことを特徴とする請求項8に記載の固体撮像素子。 - 前記光電変換部は、前記第1光電変換部及び第3光電変換部を含み、

前記転送トランジスタは、前記浮遊拡散部を共用する前記第1転送トランジスタ及び第3転送トランジスタを含み、前記第1転送トランジスタは前記第1光電変換部から前記浮遊拡散部へ前記電荷を転送し、前記第3転送トランジスタは前記第3光電変換部から前記浮遊拡散部へ前記電荷を転送し、

前記第1光電変換部と前記第3光電変換部とは、平面視において、前記浮遊拡散部を通る線を対称軸として互いに線対称に配置されている

ことを特徴とする請求項6から9のいずれか1項に記載の固体撮像素子。 - 隣接する画素との境界部に形成された画素分離部を更に有し、前記画素分離部が、前記浮遊拡散部及び前記第1カウンタードープ領域と接していない

ことを特徴とする請求項10に記載の固体撮像素子。 - 入射光を光電変換して生じた電荷を蓄積する光電変換部と、前記光電変換部から浮遊拡散部へ前記電荷を転送するMOS型の転送トランジスタと、前記浮遊拡散部に転送された前記電荷の量に応じた信号を出力する出力部とを、第2導電型のウェル領域に配した画素を備える固体撮像素子の製造方法であって、

前記ウェル領域の第1半導体領域の深い領域に、第2導電型の不純物濃度が前記ウェル領域よりも高い第2導電型の第1分離領域を形成するステップと、

前記第1半導体領域の上面から前記光電変換部の第1導電型の不純物濃度がピークとなる深さ位置までの前記第1半導体領域に、第1導電型の不純物を注入し、第1導電型のカウンタードープ領域を形成するステップと、

前記カウンタードープ領域に、第1導電型の不純物濃度が前記カウンタードープ領域よりも高い第1導電型のドレイン領域を形成するステップと、

平面視において前記第1半導体領域と直交する方向に延びる第2半導体領域の深い領域に、第2導電型の不純物濃度が前記ウェル領域よりも高い第2導電型の第2分離領域を形成するステップと、

前記第2分離領域の上方に、複数のトランジスタを形成するとともに、前記複数のトランジスタのチャネル領域に、第1導電型の埋め込みチャネル領域を形成するステップと、

前記第1半導体領域の前記第1分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第3分離領域を形成するステップと、

前記第2半導体領域の前記第2分離領域の上方において、深さが浅くなるほど第2導電型の不純物濃度が高くなっている第4の分離領域を形成するステップと、

を有し、

前記カウンタードープ領域を形成するステップと、前記埋め込みチャネル領域を形成するステップとが、異なるフォトマスクを用いて行われ、

前記光電変換部は、第1光電変換部及び第2光電変換部を含み、

前記転送トランジスタは、前記ドレイン領域を共用する第1転送トランジスタ及び第2転送トランジスタを含み、前記第1転送トランジスタは前記第1光電変換部から前記浮遊拡散部へ前記電荷を転送し、前記第2転送トランジスタは前記第2光電変換部から前記浮遊拡散部へ前記電荷を転送し、

前記第1転送トランジスタ及び前記第2転送トランジスタは、前記光電変換部と前記ドレイン領域の間のチャネル領域の上方に、絶縁膜を介して形成された第1ゲート電極及び第2ゲート電極をそれぞれ有し、

前記ドレイン領域は、平面視における前記第1ゲート電極と前記第2ゲート電極との間に延長部を有し、

前記延長部の下面の深さ位置が、前記ドレイン領域の下面の深さ位置よりも浅いことを特徴とする固体撮像素子の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016143096A JP7013119B2 (ja) | 2016-07-21 | 2016-07-21 | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム |

| US15/631,391 US10424613B2 (en) | 2016-07-21 | 2017-06-23 | Solid-state imaging device, manufacturing method of solid-state imaging device, and imaging system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016143096A JP7013119B2 (ja) | 2016-07-21 | 2016-07-21 | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018014409A JP2018014409A (ja) | 2018-01-25 |

| JP2018014409A5 JP2018014409A5 (ja) | 2019-09-05 |

| JP7013119B2 true JP7013119B2 (ja) | 2022-01-31 |

Family

ID=60988148

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016143096A Active JP7013119B2 (ja) | 2016-07-21 | 2016-07-21 | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10424613B2 (ja) |

| JP (1) | JP7013119B2 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6789653B2 (ja) * | 2016-03-31 | 2020-11-25 | キヤノン株式会社 | 光電変換装置およびカメラ |

| JP6957157B2 (ja) | 2017-01-26 | 2021-11-02 | キヤノン株式会社 | 固体撮像装置、撮像システム、および固体撮像装置の製造方法 |

| JP6701108B2 (ja) | 2017-03-21 | 2020-05-27 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP6929114B2 (ja) | 2017-04-24 | 2021-09-01 | キヤノン株式会社 | 光電変換装置及び撮像システム |

| US10818715B2 (en) | 2017-06-26 | 2020-10-27 | Canon Kabushiki Kaisha | Solid state imaging device and manufacturing method thereof |

| JP6987562B2 (ja) | 2017-07-28 | 2022-01-05 | キヤノン株式会社 | 固体撮像素子 |

| JP7091080B2 (ja) | 2018-02-05 | 2022-06-27 | キヤノン株式会社 | 装置、システム、および移動体 |

| US11916095B2 (en) * | 2018-04-16 | 2024-02-27 | Sony Semiconductor Solutions Corporation | Imaging device and method of manufacturing imaging device |

| JP7161317B2 (ja) | 2018-06-14 | 2022-10-26 | キヤノン株式会社 | 撮像装置、撮像システム及び移動体 |

| JP7150504B2 (ja) | 2018-07-18 | 2022-10-11 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| JPWO2020090403A1 (ja) * | 2018-10-30 | 2021-09-24 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子および撮像装置 |

| US11393870B2 (en) | 2018-12-18 | 2022-07-19 | Canon Kabushiki Kaisha | Photoelectric conversion device, imaging system, and mobile apparatus |

| JP7292868B2 (ja) | 2018-12-18 | 2023-06-19 | キヤノン株式会社 | 検出器 |

| US11056519B2 (en) | 2019-02-25 | 2021-07-06 | Canon Kabushiki Kaisha | Photoelectric conversion device, imaging system, and mobile apparatus |

| JP2020194912A (ja) * | 2019-05-29 | 2020-12-03 | ソニーセミコンダクタソリューションズ株式会社 | 撮像装置および電子機器 |

| JP7345301B2 (ja) | 2019-07-18 | 2023-09-15 | キヤノン株式会社 | 光電変換装置および機器 |

| CN112449129B (zh) * | 2019-08-28 | 2023-02-10 | 天津大学青岛海洋技术研究院 | 一种具有环绕驱动的网状像素结构 |

| KR20210133739A (ko) * | 2020-04-29 | 2021-11-08 | 에스케이하이닉스 주식회사 | 이미지 센서 |

| KR20220045476A (ko) | 2020-10-05 | 2022-04-12 | 삼성전자주식회사 | 이미지 센서 및 이를 포함하는 전자 시스템 |

| DE102021103062A1 (de) * | 2021-02-10 | 2022-08-11 | Dr. Ing. H.C. F. Porsche Aktiengesellschaft | Stator |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004023107A (ja) | 2002-06-20 | 2004-01-22 | Samsung Electronics Co Ltd | イメージセンサ及びその製造方法 |

| JP2005197674A (ja) | 2003-12-12 | 2005-07-21 | Canon Inc | 光電変換装置とその製造方法、及び撮像システム |

| JP2006294871A (ja) | 2005-04-11 | 2006-10-26 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP2007027714A (ja) | 2005-07-13 | 2007-02-01 | Samsung Electronics Co Ltd | イメージセンサ及びその製造方法 |

| JP2010045292A (ja) | 2008-08-18 | 2010-02-25 | Canon Inc | 光電変換装置及びその製造方法 |

| JP2010205951A (ja) | 2009-03-04 | 2010-09-16 | Sony Corp | 固体撮像装置およびその製造方法、および撮像装置 |

| JP2011082329A (ja) | 2009-10-07 | 2011-04-21 | Sony Corp | 固体撮像装置、撮像装置および固体撮像装置の製造方法 |

| JP2011249461A (ja) | 2010-05-25 | 2011-12-08 | Toshiba Corp | 固体撮像装置 |

| JP2012164943A (ja) | 2011-02-09 | 2012-08-30 | Canon Inc | 固体撮像装置 |

| JP2015188049A (ja) | 2014-03-14 | 2015-10-29 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP2016058635A (ja) | 2014-09-11 | 2016-04-21 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2016025331A5 (ja) | 2014-07-24 | 2017-08-31 |

Family Cites Families (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11274461A (ja) * | 1998-03-23 | 1999-10-08 | Sony Corp | 固体撮像装置とその製造方法 |

| JP3833125B2 (ja) | 2002-03-01 | 2006-10-11 | キヤノン株式会社 | 撮像装置 |

| JP4455435B2 (ja) | 2004-08-04 | 2010-04-21 | キヤノン株式会社 | 固体撮像装置及び同固体撮像装置を用いたカメラ |

| EP1788797B1 (en) | 2005-11-18 | 2013-06-26 | Canon Kabushiki Kaisha | Solid-state image pickup device |

| JP5132102B2 (ja) | 2006-08-01 | 2013-01-30 | キヤノン株式会社 | 光電変換装置および光電変換装置を用いた撮像システム |

| JP4818018B2 (ja) | 2006-08-01 | 2011-11-16 | キヤノン株式会社 | 光電変換装置及びそれを用いた撮像システム |

| JP5127536B2 (ja) | 2008-03-31 | 2013-01-23 | キヤノン株式会社 | 固体撮像装置の駆動方法及び撮像システム |

| JP4494492B2 (ja) | 2008-04-09 | 2010-06-30 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置の駆動方法 |

| JP5213501B2 (ja) | 2008-04-09 | 2013-06-19 | キヤノン株式会社 | 固体撮像装置 |

| JP4759590B2 (ja) | 2008-05-09 | 2011-08-31 | キヤノン株式会社 | 光電変換装置及びそれを用いた撮像システム |

| JP2009278241A (ja) | 2008-05-13 | 2009-11-26 | Canon Inc | 固体撮像装置の駆動方法および固体撮像装置 |

| JP5279352B2 (ja) | 2008-06-06 | 2013-09-04 | キヤノン株式会社 | 固体撮像装置 |

| JP2010268080A (ja) | 2009-05-12 | 2010-11-25 | Canon Inc | 固体撮像装置 |

| JP4977181B2 (ja) | 2009-08-10 | 2012-07-18 | 株式会社東芝 | 固体撮像装置およびその製造方法 |

| JP5539104B2 (ja) | 2009-09-24 | 2014-07-02 | キヤノン株式会社 | 光電変換装置およびそれを用いた撮像システム |

| JP5960961B2 (ja) | 2010-11-16 | 2016-08-02 | キヤノン株式会社 | 固体撮像素子及び撮像システム |

| JP2013093553A (ja) | 2011-10-04 | 2013-05-16 | Canon Inc | 光電変換装置及びその製造方法、並びに光電変換システム |

| JP6053505B2 (ja) | 2012-01-18 | 2016-12-27 | キヤノン株式会社 | 固体撮像装置 |

| JP5967944B2 (ja) | 2012-01-18 | 2016-08-10 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| JP2014049727A (ja) | 2012-09-04 | 2014-03-17 | Canon Inc | 固体撮像装置 |

| JP6148580B2 (ja) | 2013-09-03 | 2017-06-14 | キヤノン株式会社 | 撮像装置及びカメラ |

| JP6261361B2 (ja) | 2014-02-04 | 2018-01-17 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| JP6274567B2 (ja) | 2014-03-14 | 2018-02-07 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP6541347B2 (ja) | 2014-03-27 | 2019-07-10 | キヤノン株式会社 | 固体撮像装置および撮像システム |

| JP6408372B2 (ja) | 2014-03-31 | 2018-10-17 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置及びその駆動制御方法、並びに、電子機器 |

| JP6406911B2 (ja) | 2014-07-24 | 2018-10-17 | キヤノン株式会社 | 撮像装置及び撮像装置の製造方法 |

| JP2016058538A (ja) | 2014-09-09 | 2016-04-21 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| JP6417197B2 (ja) | 2014-11-27 | 2018-10-31 | キヤノン株式会社 | 固体撮像装置 |

| JP6555890B2 (ja) * | 2015-01-23 | 2019-08-07 | キヤノン株式会社 | 撮像装置、撮像システム、および撮像装置の駆動方法 |

| JP2016218115A (ja) | 2015-05-14 | 2016-12-22 | キヤノン株式会社 | 光学素子の設計方法、光学素子アレイ、センサアレイおよび撮像装置 |

| JP6506614B2 (ja) | 2015-05-14 | 2019-04-24 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| US9768213B2 (en) * | 2015-06-03 | 2017-09-19 | Canon Kabushiki Kaisha | Solid-state image sensor and camera |

| US10205894B2 (en) | 2015-09-11 | 2019-02-12 | Canon Kabushiki Kaisha | Imaging device and imaging system |

| JP6570384B2 (ja) | 2015-09-11 | 2019-09-04 | キヤノン株式会社 | 撮像装置及び撮像システム |

| JP6541523B2 (ja) | 2015-09-11 | 2019-07-10 | キヤノン株式会社 | 撮像装置、撮像システム、および、撮像装置の制御方法 |

| JP2017059589A (ja) | 2015-09-14 | 2017-03-23 | キヤノン株式会社 | 固体撮像素子及び撮像装置 |

| JP2017195215A (ja) * | 2016-04-18 | 2017-10-26 | キヤノン株式会社 | 撮像素子及びその製造方法 |

-

2016

- 2016-07-21 JP JP2016143096A patent/JP7013119B2/ja active Active

-

2017

- 2017-06-23 US US15/631,391 patent/US10424613B2/en active Active

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004023107A (ja) | 2002-06-20 | 2004-01-22 | Samsung Electronics Co Ltd | イメージセンサ及びその製造方法 |

| JP2005197674A (ja) | 2003-12-12 | 2005-07-21 | Canon Inc | 光電変換装置とその製造方法、及び撮像システム |

| JP2006294871A (ja) | 2005-04-11 | 2006-10-26 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP2007027714A (ja) | 2005-07-13 | 2007-02-01 | Samsung Electronics Co Ltd | イメージセンサ及びその製造方法 |

| JP2010045292A (ja) | 2008-08-18 | 2010-02-25 | Canon Inc | 光電変換装置及びその製造方法 |

| JP2010205951A (ja) | 2009-03-04 | 2010-09-16 | Sony Corp | 固体撮像装置およびその製造方法、および撮像装置 |

| JP2011082329A (ja) | 2009-10-07 | 2011-04-21 | Sony Corp | 固体撮像装置、撮像装置および固体撮像装置の製造方法 |

| JP2011249461A (ja) | 2010-05-25 | 2011-12-08 | Toshiba Corp | 固体撮像装置 |

| JP2012164943A (ja) | 2011-02-09 | 2012-08-30 | Canon Inc | 固体撮像装置 |

| JP2015188049A (ja) | 2014-03-14 | 2015-10-29 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP2016025331A5 (ja) | 2014-07-24 | 2017-08-31 | ||

| JP2016058635A (ja) | 2014-09-11 | 2016-04-21 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20180026073A1 (en) | 2018-01-25 |

| US10424613B2 (en) | 2019-09-24 |

| JP2018014409A (ja) | 2018-01-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7013119B2 (ja) | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム | |

| US11729530B2 (en) | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus | |

| KR100758321B1 (ko) | 포토다이오드 영역을 매립한 이미지 센서 및 그 제조 방법 | |

| US9209215B2 (en) | Photoelectric conversion apparatus and imaging system using the photoelectric conversion apparatus | |

| JP5539104B2 (ja) | 光電変換装置およびそれを用いた撮像システム | |

| CN1812112B (zh) | 具有非平面晶体管的固态图像传感器设备及其制造方法 | |

| KR101683307B1 (ko) | 고체 촬상 장치, 고체 촬상 장치의 제조 방법, 및 전자 기기 | |

| JP5812692B2 (ja) | 固体撮像装置の製造方法 | |

| JP6406585B2 (ja) | 撮像装置 | |

| US20120119272A1 (en) | Solid-state image sensor, method of manufacturing the same, and imaging system | |

| US20210020676A1 (en) | Image sensor and method of fabricating the same | |

| US12087781B2 (en) | Image sensor having P-type isolation structure | |

| JP2006294871A (ja) | 固体撮像装置 | |

| KR20130043716A (ko) | 블랙 레벨 안정화를 위한 이미지 센서 | |

| KR20170051304A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2017195215A (ja) | 撮像素子及びその製造方法 | |

| US8338868B2 (en) | Shared photodiode image sensor | |

| JP6727897B2 (ja) | 固体撮像装置、固体撮像装置の製造方法、および撮像システム | |

| KR101016552B1 (ko) | 이미지 센서 및 이미지 센서의 제조 방법 | |

| US7763909B2 (en) | Image sensor and method for manufacturing the same | |

| JP6039773B2 (ja) | 固体撮像装置の製造方法 | |

| KR20050093061A (ko) | Cmos 이미지 센서 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20171214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20180126 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190722 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190725 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200630 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200728 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200924 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210325 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20211014 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211221 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220119 |