JP6148580B2 - 撮像装置及びカメラ - Google Patents

撮像装置及びカメラ Download PDFInfo

- Publication number

- JP6148580B2 JP6148580B2 JP2013182475A JP2013182475A JP6148580B2 JP 6148580 B2 JP6148580 B2 JP 6148580B2 JP 2013182475 A JP2013182475 A JP 2013182475A JP 2013182475 A JP2013182475 A JP 2013182475A JP 6148580 B2 JP6148580 B2 JP 6148580B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- supply wiring

- wiring pattern

- pixel array

- image pickup

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003384 imaging method Methods 0.000 title claims description 56

- 230000003287 optical effect Effects 0.000 claims description 12

- 239000004065 semiconductor Substances 0.000 claims description 12

- 238000012937 correction Methods 0.000 claims description 3

- 230000006870 function Effects 0.000 claims description 3

- 239000000463 material Substances 0.000 claims description 3

- 230000000903 blocking effect Effects 0.000 claims 1

- 238000012545 processing Methods 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 10

- 238000003705 background correction Methods 0.000 description 8

- 238000000034 method Methods 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 4

- 238000012546 transfer Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 238000005375 photometry Methods 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/67—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/61—Noise processing, e.g. detecting, correcting, reducing or removing noise the noise originating only from the lens unit, e.g. flare, shading, vignetting or "cos4"

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

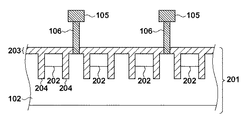

図1〜図5を参照しながら、第1実施形態の撮像装置I1を説明する。撮像装置I1は、図1に例示されるように、画素アレイPAと、ボンディングパッド103と、複数の第1電源配線パターン105と、第2電源配線パターン104と、複数のコンタクト106とを備える。

図6を参照しながら、第2実施形態の撮像装置I2を説明する。前述の第1実施形態では、4本の電源配線パターン105が2画素ごとに配された構成を例示したが、本発明はこの構成に限られるものではなく、各電源配線パターン105の電圧供給の負荷が等しくなるように構成されればよい。

図7を参照しながら、第3実施形態の撮像装置I3を説明する。本実施形態は、画素アレイPAの外側にオプティカルブラック画素部OBが設けられている点で第1実施形態と異なる。電源配線パターン104は、オプティカルブラック画素部OBの上方に配置されている。これにより、オプティカルブラック画素部OBの各画素101OBへの入射光が遮断され、各画素101OBからはノイズ成分に相当するダーク信号が得られる。

図8を参照しながら、第4実施形態の撮像装置I4を説明する。前述の各実施形態では、基準電圧を受けるためのパッド部として、対向する2辺のそれぞれにボンディングパッド103が1つずつ設けられた構成を例示したが、本発明はこの構成に限られるものではない。例えば、本実施形態のように、対向する2辺のそれぞれに複数のボンディングパッド103が設けられてもよい。複数のボンディングパッド103のそれぞれは、b方向に沿って配されており、電源配線パターン104に電気的に接続されている。この構成によると、電源配線パターン104のb方向における電圧降下が低減され、即ち、電源配線パターン104のb方向における各位置での電圧が略等しくなる。

以上では、カメラ等に代表される撮像システムに含まれる撮像装置について述べた。撮像システムの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置(例えば、パーソナルコンピュータ、携帯端末)も含まれる。撮像システムは、上記の実施形態として例示された本発明に係る撮像装置と、この撮像装置から出力される信号を処理する処理部とを含みうる。この処理部は、例えば、A/D変換器、および、このA/D変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

Claims (12)

- 半導体領域に複数の画素が配列された画素アレイと、

基準電圧を受けるためのパッド部と、

それぞれが前記画素アレイの行方向および列方向のうちの一方である第1方向に沿って延在し、前記画素アレイの上に前記画素アレイの行方向および列方向のうちの他方である第2方向に沿って並ぶ複数の第1電源配線パターンと、

前記画素アレイの外側の領域の上に配され、前記第2方向に沿って延在し、前記複数の第1電源配線パターンと前記パッド部とを電気的に接続する第2電源配線パターンと、

前記複数の第1電源配線パターンと前記半導体領域とを電気的に接続する複数のコンタクトと、を備え、

前記第2電源配線パターンの前記第2方向における抵抗値は、前記複数の第1電源配線パターンのそれぞれの前記第1方向における抵抗値よりも小さい、

ことを特徴とする撮像装置。 - 前記画素アレイの外側に配されたオプティカルブラック画素部をさらに備え、

前記第2電源配線パターンの少なくとも一部である第1部分は、前記オプティカルブラック画素部の上に配されている、

ことを特徴とする請求項1に記載の撮像装置。 - 前記第1部分は、入射する光を遮光する遮光部として機能する、

ことを特徴とする請求項2に記載の撮像装置。 - 前記画素アレイから信号を読み出す信号読出部をさらに備え、

前記第2電源配線パターンの少なくとも一部である第2部分は、前記信号読出部の上に配されている、

ことを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。 - 前記画素アレイを駆動する駆動部をさらに備え、

前記第2電源配線パターンの少なくとも一部である第3部分は、前記駆動部の上に配されている、

ことを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。 - 前記パッド部は複数のパッドを含み、前記複数のパッドは、前記第2方向に沿って配され、前記第2電源配線パターンに電気的に接続されている、

ことを特徴とする請求項1乃至5のいずれか1項に記載の撮像装置。 - 前記第1方向に沿って配され、前記画素アレイから信号を読み出すための複数の信号線をさらに備え、

前記複数の第1電源配線パターンのそれぞれは、前記複数の信号線のうちの互いに隣接する2つの信号線の間に配されている、

ことを特徴とする請求項1乃至6のいずれか1項に記載の撮像装置。 - 前記第2電源配線パターンは、互いに平行に配された複数のラインパターンを含む、

ことを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。 - 前記複数のラインパターンは、前記第1方向に沿って配された他のラインパターンを用いて互いに接続されている、

ことを特徴とする請求項8に記載の撮像装置。 - 前記第1電源配線パターンの前記第1方向における抵抗値は、前記第1電源配線パターンの前記第1方向に沿った全長に対しての抵抗値であり、

前記第2電源配線パターンの前記第2方向における抵抗値は、前記第1電源配線パターンの前記第2方向に沿った全長に対しての抵抗値である、

ことを特徴とする請求項1乃至請求項9のいずれか一項に記載の撮像装置。 - 半導体領域に複数の画素が配列された画素アレイと、

基準電圧を受けるためのパッド部と、

それぞれが前記画素アレイの行方向および列方向のうちの一方である第1方向に沿って延在し、前記画素アレイの上に前記画素アレイの行方向および列方向のうちの他方である第2方向に沿って並ぶ複数の第1電源配線パターンと、

前記画素アレイの外側の領域の上に配され、前記第2方向に沿って延在し、前記複数の第1電源配線パターンと前記パッド部とを電気的に接続する第2電源配線パターンと、

前記複数の第1電源配線パターンと前記半導体領域とを電気的に接続する複数のコンタクトと、を備え、

前記複数の第1電源配線パターンと前記第2電源配線パターンとは、同じ材料で構成され、かつ、同じ配線層に配されており、

前記第2電源配線パターンの幅は、前記複数の第1電源配線パターンのそれぞれの幅よりも大きい、

ことを特徴とする撮像装置。 - 請求項1乃至11のいずれか1項に記載の撮像装置と、

前記撮像装置の前記画素アレイからの画像信号について、前記第1方向に対応する方向で生じうるシェーディングの補正を行う補正部と、を具備する、

ことを特徴とするカメラ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013182475A JP6148580B2 (ja) | 2013-09-03 | 2013-09-03 | 撮像装置及びカメラ |

| US14/456,063 US20150062367A1 (en) | 2013-09-03 | 2014-08-11 | Image capturing apparatus and camera |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013182475A JP6148580B2 (ja) | 2013-09-03 | 2013-09-03 | 撮像装置及びカメラ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015050706A JP2015050706A (ja) | 2015-03-16 |

| JP2015050706A5 JP2015050706A5 (ja) | 2016-08-04 |

| JP6148580B2 true JP6148580B2 (ja) | 2017-06-14 |

Family

ID=52582695

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013182475A Active JP6148580B2 (ja) | 2013-09-03 | 2013-09-03 | 撮像装置及びカメラ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20150062367A1 (ja) |

| JP (1) | JP6148580B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6738200B2 (ja) | 2016-05-26 | 2020-08-12 | キヤノン株式会社 | 撮像装置 |

| JP6688165B2 (ja) | 2016-06-10 | 2020-04-28 | キヤノン株式会社 | 撮像装置及び撮像システム |

| JP7013119B2 (ja) | 2016-07-21 | 2022-01-31 | キヤノン株式会社 | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム |

| JP7150504B2 (ja) | 2018-07-18 | 2022-10-11 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| US11393870B2 (en) | 2018-12-18 | 2022-07-19 | Canon Kabushiki Kaisha | Photoelectric conversion device, imaging system, and mobile apparatus |

| US11056519B2 (en) | 2019-02-25 | 2021-07-06 | Canon Kabushiki Kaisha | Photoelectric conversion device, imaging system, and mobile apparatus |

| JP6986046B2 (ja) | 2019-05-30 | 2021-12-22 | キヤノン株式会社 | 光電変換装置および機器 |

| JP7345301B2 (ja) | 2019-07-18 | 2023-09-15 | キヤノン株式会社 | 光電変換装置および機器 |

| JP7171649B2 (ja) | 2020-05-15 | 2022-11-15 | キヤノン株式会社 | 撮像装置および撮像システム |

| JP7474123B2 (ja) * | 2020-06-15 | 2024-04-24 | キヤノン株式会社 | 光電変換装置、光電変換システム及び移動体 |

| JP2023053806A (ja) | 2021-10-01 | 2023-04-13 | キヤノン株式会社 | 撮像装置及び電子機器 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3467013B2 (ja) * | 1999-12-06 | 2003-11-17 | キヤノン株式会社 | 固体撮像装置 |

| JP2004153678A (ja) * | 2002-10-31 | 2004-05-27 | Canon Inc | 固体撮像装置 |

| JP4329409B2 (ja) * | 2003-05-23 | 2009-09-09 | 株式会社ニコン | 電子カメラのシェーディング補正回路 |

| US7432491B2 (en) * | 2005-05-06 | 2008-10-07 | Micron Technology, Inc. | Pixel with spatially varying sensor positions |

| KR20070093335A (ko) * | 2006-03-13 | 2007-09-18 | 마쯔시다덴기산교 가부시키가이샤 | 고체 촬상장치 및 그 구동방법 |

| JP4144892B2 (ja) * | 2006-08-28 | 2008-09-03 | キヤノン株式会社 | 光電変換装置及び撮像装置 |

| JP2008282961A (ja) * | 2007-05-10 | 2008-11-20 | Matsushita Electric Ind Co Ltd | 固体撮像装置 |

| JP5130946B2 (ja) * | 2008-02-15 | 2013-01-30 | ソニー株式会社 | 固体撮像装置、カメラ及び電子機器 |

| JP2010212635A (ja) * | 2009-03-12 | 2010-09-24 | Canon Inc | 固体撮像装置 |

| TW201129087A (en) * | 2010-02-09 | 2011-08-16 | Novatek Microelectronics Corp | Image sensor |

| JP2011216865A (ja) * | 2010-03-17 | 2011-10-27 | Canon Inc | 固体撮像装置 |

| JP2014209696A (ja) * | 2012-07-23 | 2014-11-06 | ソニー株式会社 | 固体撮像装置、信号読み出し方法、および電子機器 |

| JP2014086465A (ja) * | 2012-10-19 | 2014-05-12 | Toshiba Corp | 固体撮像装置 |

| JP2014135326A (ja) * | 2013-01-08 | 2014-07-24 | Toshiba Corp | 固体撮像装置 |

-

2013

- 2013-09-03 JP JP2013182475A patent/JP6148580B2/ja active Active

-

2014

- 2014-08-11 US US14/456,063 patent/US20150062367A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20150062367A1 (en) | 2015-03-05 |

| JP2015050706A (ja) | 2015-03-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6148580B2 (ja) | 撮像装置及びカメラ | |

| US10015426B2 (en) | Solid-state imaging element and driving method therefor, and electronic apparatus | |

| US9653498B2 (en) | Imaging device having electrode overlying photoelectric conversion layer and having electrical contact to electrode | |

| JP6018376B2 (ja) | 固体撮像装置およびカメラ | |

| JP5358136B2 (ja) | 固体撮像装置 | |

| US9053996B2 (en) | Solid-state imaging apparatus with a plurality of processing portions | |

| JP6174902B2 (ja) | 固体撮像装置及びカメラ | |

| KR102389417B1 (ko) | 고체 촬상 소자 및 촬상 장치 | |

| JP4952601B2 (ja) | 固体撮像装置 | |

| US20130250137A1 (en) | Solid-state image sensor and image sensing apparatus | |

| JP2010268440A (ja) | 光電変換装置及び撮像システム | |

| JP2008042239A (ja) | 光電変換装置及びそれを用いた撮像システム | |

| JP6929833B2 (ja) | 撮像素子および撮像装置 | |

| TW201316503A (zh) | 固體攝像元件及電子機器 | |

| JP2016034068A (ja) | 撮像装置及び撮像システム | |

| JP6526159B2 (ja) | 固体撮像装置およびカメラ | |

| JP6257726B2 (ja) | 固体撮像装置およびカメラ | |

| JP6195728B2 (ja) | 固体撮像素子および撮像装置 | |

| JP6355401B2 (ja) | 固体撮像装置及びカメラ | |

| JP2020058066A (ja) | 撮像素子 | |

| JP2023072018A (ja) | 撮像素子、及び電子カメラ | |

| JP6813971B2 (ja) | 光電変換装置及び撮像システム | |

| CN114503266A (zh) | 拍摄元件及拍摄装置 | |

| JP2010135840A (ja) | 撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160620 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160620 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170313 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170421 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170519 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6148580 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |