JP6996461B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6996461B2 JP6996461B2 JP2018169878A JP2018169878A JP6996461B2 JP 6996461 B2 JP6996461 B2 JP 6996461B2 JP 2018169878 A JP2018169878 A JP 2018169878A JP 2018169878 A JP2018169878 A JP 2018169878A JP 6996461 B2 JP6996461 B2 JP 6996461B2

- Authority

- JP

- Japan

- Prior art keywords

- trench

- igbt

- fwd

- region

- pitch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

- H10D8/422—PN diodes having the PN junctions in mesas

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/411—Insulated-gate bipolar transistors [IGBT]

- H10D12/441—Vertical IGBTs

- H10D12/461—Vertical IGBTs having non-planar surfaces, e.g. having trenches, recesses or pillars in the surfaces of the emitter, base or collector regions

- H10D12/481—Vertical IGBTs having non-planar surfaces, e.g. having trenches, recesses or pillars in the surfaces of the emitter, base or collector regions having gate structures on slanted surfaces, on vertical surfaces, or in grooves, e.g. trench gate IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/126—Top-view geometrical layouts of the regions or the junctions

- H10D62/127—Top-view geometrical layouts of the regions or the junctions of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/129—Cathode regions of diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/141—Anode or cathode regions of thyristors; Collector or emitter regions of gated bipolar-mode devices, e.g. of IGBTs

- H10D62/142—Anode regions of thyristors or collector regions of gated bipolar-mode devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/111—Field plates

- H10D64/117—Recessed field plates, e.g. trench field plates or buried field plates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

- H10D8/60—Schottky-barrier diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

- H10W10/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/106—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE] having supplementary regions doped oppositely to or in rectifying contact with regions of the semiconductor bodies, e.g. guard rings with PN or Schottky junctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/106—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE] having supplementary regions doped oppositely to or in rectifying contact with regions of the semiconductor bodies, e.g. guard rings with PN or Schottky junctions

- H10D62/107—Buried supplementary regions, e.g. buried guard rings

Landscapes

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

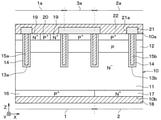

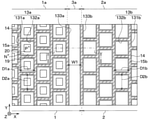

第1実施形態について説明する。なお、本実施形態の半導体装置は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

第2実施形態について説明する。本実施形態は、第1実施形態に対し、分離セル領域3aにダミートレンチを形成したものである。その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

上記第2実施形態の変形例について説明する。上記第2実施形態において、図5に示されるように、分離セル領域3aには、複数のダミートレンチ23がX軸方向に沿って配列されるように形成されていてもよい。この場合、IGBT用端部トレンチ133aの中心と、IGBT用端部トレンチ133aと隣合うダミートレンチ23の中心との間の距離を分離用第1トレンチピッチL1とする。また、FWD用端部トレンチ133bの中心と、FWD用端部トレンチ133bと隣合うダミートレンチ23の中心との間の距離を分離用第2トレンチピッチL2とする。そして、隣合うダミートレンチ23同士の中心間の距離を分離用第3トレンチピッチL3とする。この場合、分離用第1~第3トレンチピッチL1~L3は、各トレンチピッチD1a、D2a、D1b、D2bより狭くなる。

第3実施形態について説明する。第3実施形態は、第2実施形態に対し、分離セルピッチW1と、各トレンチピッチD1a、D2a、D1b、D2bとの関係を変更したものである。その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

第4実施形態について説明する。第4実施形態は、第1実施形態に対し、分離セル領域3aのベース層12の構成を変更したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

上記第4実施形態の変形例について説明する。上記第4実施形態において、分離セル領域3aにおけるベース層12は、IGBTセル領域1aおよびFWDセル領域2aにおけるベース層12よりも高不純物濃度とされていてもよい。これによれば、さらに等電位線がベース層12側に入り込み難くなり、分離セル領域3で電界集中が発生することを抑制できる。なお、このような構成では、分離セル領域3aにおけるベース層12は、IGBTセル領域1aおよびFWDセル領域1bにおけるベース層12と同じ深さとされていてもよい。

第5実施形態について説明する。第5実施形態は、第1実施形態に対し、分離セル領域3aに連通トレンチを形成したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

上記第5実施形態の変形例について説明する。上記第5実施形態において、分離セルピッチW1は、各トレンチピッチD1a、D2a、D1b、D2b以上とされていてもよい。このような半導体装置としても、分離セル領域3aに連通トレンチ134を形成することにより、連通トレンチ134が形成されていない場合と比較して電界集中が発生することを抑制できるため、耐圧の向上を図ることができる。

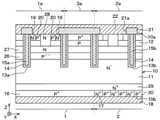

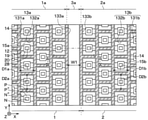

第6実施形態について説明する。第6実施形態は、第1実施形態に対し、ピラー領域、バリア領域、電界緩和領域を形成したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

2 FWD領域

3a 分離セル領域

10 半導体基板

11 ドリフト層

12 ベース層

13a IGBT用トレンチ

13b FWD用トレンチ

14 ゲート絶縁膜

15a 第1ゲート電極

15b 第2ゲート電極

16 コレクタ層

17 カソード層

18 下部電極(第2電極)

22 上部電極(第1電極)

131a IGBT用第1トレンチ

131b FWD用第1トレンチ

132a IGBT用第2トレンチ

132b FWD用第2トレンチ

Claims (11)

- IGBT領域(1)とFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層を貫通するトレンチ(13a、13b)の壁面に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極(15a、15b)と、を有する複数のトレンチゲート構造と、

前記ベース層の表層部であって、前記IGBT領域に形成された前記トレンチと接するように形成された第1導電型のエミッタ領域(19)と、

前記ドリフト層を挟んで前記ベース層側と反対側に形成された第2導電型のコレクタ層(16)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成されると共に前記コレクタ層と隣接する第1導電型のカソード層(17)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(22)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(18)と、を備え、

前記コレクタ層上の領域が前記IGBT領域とされ、前記カソード層上の領域が前記FWD領域とされており、

前記トレンチは、前記IGBT領域に形成される前記ゲート電極としての第1ゲート電極(14a)が配置されるIGBT用トレンチ(13a)と、前記FWD領域に形成され、前記第1ゲート電極とは別に制御される前記ゲート電極としての第2ゲート電極(14b)が配置されるFWD用トレンチ(13b)であり、

前記IGBT用トレンチは、前記半導体基板の面方向における一方向に沿った第1方向に延設されたIGBT用第1トレンチ(131a)と、前記半導体基板の面方向における前記第1方向と交差する第2方向に延設されたIGBT用第2トレンチ(132a)とが連通された格子状とされており、

前記FWD用トレンチは、前記第1方向に延設されたFWD用第1トレンチ(131b)と、前記第2方向に延設されたFWD用第2トレンチ(132b)とが連通された格子状とされ、

前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチ(133a)の中心と、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチ(133b)の中心との間を分離セル領域(3a)とすると共に前記分離セル領域における前記第2方向の距離を分離セルピッチ(W1)とし、隣合う前記IGBT用第1トレンチ同士の中心間の最小距離をIGBT用第1トレンチピッチ(D1a)とし、隣合う前記IGBT用第2トレンチ同士の中心間の最小距離をIGBT用第2トレンチピッチ(D2a)とし、隣合う前記FWD用第1トレンチ同士の中心間の最小距離をFWD用第1トレンチピッチ(D1b)とし、隣合う前記FWD用第2トレンチ同士の中心間の最小距離をFWD用第2トレンチピッチ(D2b)とすると、

前記分離セルピッチは、前記IGBT用第1トレンチピッチ、前記IGBT用第2トレンチピッチ、前記FWD用第1トレンチピッチ、前記FWD用第2トレンチピッチよりも狭くされている半導体装置。 - 前記分離セル領域には、前記第1方向に沿って延設されたダミートレンチ(23)が形成され、

前記ダミートレンチ(23)には、ダミー絶縁膜(24)とダミー電極(25)とが配置されている請求項1に記載の半導体装置。 - IGBT領域(1)とFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層を貫通するトレンチ(13a、13b)の壁面に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極(15a、15b)と、を有する複数のトレンチゲート構造と、

前記ベース層の表層部であって、前記IGBT領域に形成された前記トレンチと接するように形成された第1導電型のエミッタ領域(19)と、

前記ドリフト層を挟んで前記ベース層側と反対側に形成された第2導電型のコレクタ層(16)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成されると共に前記コレクタ層と隣接する第1導電型のカソード層(17)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(22)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(18)と、を備え、

前記コレクタ層上の領域が前記IGBT領域とされ、前記カソード層上の領域が前記FWD領域とされており、

前記トレンチは、前記IGBT領域に形成される前記ゲート電極としての第1ゲート電極(14a)が配置されるIGBT用トレンチ(13a)と、前記FWD領域に形成され、前記第1ゲート電極とは別に制御される前記ゲート電極としての第2ゲート電極(14b)が配置されるFWD用トレンチ(13b)であり、

前記IGBT用トレンチは、前記半導体基板の面方向における一方向に沿った第1方向に延設されたIGBT用第1トレンチ(131a)と、前記半導体基板の面方向における前記第1方向と交差する第2方向に延設されたIGBT用第2トレンチ(132a)とが連通された格子状とされており、

前記FWD用トレンチは、前記第1方向に延設されたFWD用第1トレンチ(131b)と、前記第2方向に延設されたFWD用第2トレンチ(132b)とが連通された格子状とされ、

前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチ(133a)の中心と、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチ(133b)の中心との間を分離セル領域(3a)とすると共に前記分離セル領域における前記第2方向の距離を分離セルピッチ(W1)とし、

前記分離セル領域には、前記第1方向に沿って延設された1つのダミートレンチ(23)が形成され、

前記ダミートレンチ(23)には、ダミー絶縁膜(24)とダミー電極(25)とが配置されており、

隣合う前記IGBT用第1トレンチ同士の中心間の最小距離をIGBT用第1トレンチピッチ(D1a)とし、隣合う前記IGBT用第2トレンチ同士の中心間の最小距離をIGBT用第2トレンチピッチ(D2a)とし、隣合う前記FWD用第1トレンチ同士の中心間の最小距離をFWD用第1トレンチピッチ(D1b)とし、隣合う前記FWD用第2トレンチ同士の中心間の最小距離をFWD用第2トレンチピッチ(D2b)とし、前記ダミートレンチの中心と、当該ダミートレンチと隣合う前記IGBT用第1トレンチの中心との間の距離を分離用第1トレンチピッチ(L1)とし、前記ダミートレンチの中心と、当該ダミートレンチと隣合う前記FWD用第1トレンチの中心との間の距離を分離用第2トレンチピッチ(L2)とすると、

前記分離セルピッチは、前記IGBT用第1トレンチピッチ、前記IGBT用第2トレンチピッチ、前記FWD用第1トレンチピッチ、前記FWD用第2トレンチピッチの少なくとも1つより大きくされ、

前記分離用第1トレンチピッチおよび前記分離用第2トレンチピッチは、前記IGBT用第1トレンチピッチ、前記IGBT用第2トレンチピッチ、前記FWD用第1トレンチピッチ、前記FWD用第2トレンチピッチよりも狭くされている半導体装置。 - IGBT領域(1)とFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層を貫通するトレンチ(13a、13b)の壁面に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極(15a、15b)と、を有する複数のトレンチゲート構造と、

前記ベース層の表層部であって、前記IGBT領域に形成された前記トレンチと接するように形成された第1導電型のエミッタ領域(19)と、

前記ドリフト層を挟んで前記ベース層側と反対側に形成された第2導電型のコレクタ層(16)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成されると共に前記コレクタ層と隣接する第1導電型のカソード層(17)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(22)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(18)と、を備え、

前記コレクタ層上の領域が前記IGBT領域とされ、前記カソード層上の領域が前記FWD領域とされており、

前記トレンチは、前記IGBT領域に形成される前記ゲート電極としての第1ゲート電極(14a)が配置されるIGBT用トレンチ(13a)と、前記FWD領域に形成され、前記第1ゲート電極とは別に制御される前記ゲート電極としての第2ゲート電極(14b)が配置されるFWD用トレンチ(13b)であり、

前記IGBT用トレンチは、前記半導体基板の面方向における一方向に沿った第1方向に延設されたIGBT用第1トレンチ(131a)と、前記半導体基板の面方向における前記第1方向と交差する第2方向に延設されたIGBT用第2トレンチ(132a)とが連通された格子状とされており、

前記FWD用トレンチは、前記第1方向に延設されたFWD用第1トレンチ(131b)と、前記第2方向に延設されたFWD用第2トレンチ(132b)とが連通された格子状とされ、

前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチ(133a)の中心と、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチ(133b)の中心との間を分離セル領域(3a)とすると共に前記分離セル領域における前記第2方向の距離を分離セルピッチ(W1)とし、

前記分離セル領域には、前記第1方向に沿って延設された複数のダミートレンチ(23)が形成され、

前記ダミートレンチ(23)には、ダミー絶縁膜(24)とダミー電極(25)とが配置されており、

隣合う前記IGBT用第1トレンチ同士の中心間の最小距離をIGBT用第1トレンチピッチ(D1a)とし、隣合う前記IGBT用第2トレンチ同士の中心間の最小距離をIGBT用第2トレンチピッチ(D2a)とし、隣合う前記FWD用第1トレンチ同士の中心間の最小距離をFWD用第1トレンチピッチ(D1b)とし、隣合う前記FWD用第2トレンチ同士の中心間の最小距離をFWD用第2トレンチピッチ(D2b)とし、前記ダミートレンチの中心と、当該ダミートレンチと隣合う前記IGBT用第1トレンチの中心との間の距離を分離用第1トレンチピッチ(L1)とし、前記ダミートレンチの中心と、当該ダミートレンチと隣合う前記FWD用第1トレンチの中心との間の距離を分離用第2トレンチピッチ(L2)とし、隣合う前記ダミートレンチ同士の中心間の最大距離を分離用第3トレンチピッチ(L3)とすると、

前記分離セルピッチは、前記IGBT用第1トレンチピッチ、前記IGBT用第2トレンチピッチ、前記FWD用第1トレンチピッチ、前記FWD用第2トレンチピッチの少なくとも1つより大きくされ、

前記分離用第1トレンチピッチ、前記分離用第2トレンチピッチおよび前記分離用第3トレンチピッチは、前記IGBT用第1トレンチピッチ、前記IGBT用第2トレンチピッチ、前記FWD用第1トレンチピッチ、前記FWD用第2トレンチピッチよりも狭くされている半導体装置。 - 前記IGBT領域のうちの前記分離セル領域と異なる領域をIGBTセル領域(1a)とし、前記FWD領域のうちの前記分離セル領域と異なる領域をFWDセル領域(2a)とすると、

前記分離セル領域のベース層は、前記IGBTセル領域および前記FWDセル領域のベース層よりも単位体積当たりの不純物量が高くされている請求項1ないし4のいずれか1つに記載の半導体装置。 - 前記分離セル領域には、前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチと、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチとを連通させる連通トレンチ(134)が形成されており、

前記連通トレンチには、前記第1ゲート電極と前記第2ゲート電極とを絶縁する絶縁膜(135)が配置されている請求項1ないし5のいずれか1つに記載の半導体装置。 - IGBT領域(1)とFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層を貫通するトレンチ(13a、13b)の壁面に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極(15a、15b)と、を有する複数のトレンチゲート構造と、

前記ベース層の表層部であって、前記IGBT領域に形成された前記トレンチと接するように形成された第1導電型のエミッタ領域(19)と、

前記ドリフト層を挟んで前記ベース層側と反対側に形成された第2導電型のコレクタ層(16)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成されると共に前記コレクタ層と隣接する第1導電型のカソード層(17)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(22)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(18)と、を備え、

前記コレクタ層上の領域が前記IGBT領域とされ、前記カソード層上の領域が前記FWD領域とされており、

前記トレンチは、前記IGBT領域に形成される前記ゲート電極としての第1ゲート電極(14a)が配置されるIGBT用トレンチ(13a)と、前記FWD領域に形成され、前記第1ゲート電極とは別に制御される前記ゲート電極としての第2ゲート電極(14b)が配置されるFWD用トレンチ(13b)であり、

前記IGBT用トレンチは、前記半導体基板の面方向における一方向に沿った第1方向に延設されたIGBT用第1トレンチ(131a)と、前記半導体基板の面方向における前記第1方向と交差する第2方向に延設されたIGBT用第2トレンチ(132a)とが連通された格子状とされており、

前記FWD用トレンチは、前記第1方向に延設されたFWD用第1トレンチ(131b)と、前記第2方向に延設されたFWD用第2トレンチ(132b)とが連通された格子状とされ、

前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチ(133a)の中心と、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチ(133b)の中心との間を分離セル領域(3a)とし、前記IGBT領域のうちの前記分離セル領域と異なる領域をIGBTセル領域(1a)とし、前記FWD領域のうちの前記分離セル領域と異なる領域をFWDセル領域(2a)とすると、

前記分離セル領域のベース層は、前記IGBTセル領域および前記FWDセル領域のベース層よりも単位体積当たりの不純物量が高くされており、

前記分離セル領域には、前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチと、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチとを連通させる連通トレンチ(134)が形成されており、

前記連通トレンチには、前記第1ゲート電極と前記第2ゲート電極とを絶縁する絶縁膜(135)が配置されている半導体装置。 - 前記分離セル領域のベース層は、前記IGBTセル領域および前記FWDセル領域のベース層よりも深くまで形成されている請求項5ないし7のいずれか1つに記載の半導体装置。

- 前記分離セル領域のベース層は、前記IGBTセル領域および前記FWDセル領域のベース層よりも不純物濃度が高くされている請求項5ないし8のいずれか1つに記載の半導体装置。

- IGBT領域(1)とFWD領域(2)とが共通の半導体基板(10)に形成されている半導体装置であって、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層を貫通するトレンチ(13a、13b)の壁面に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極(15a、15b)と、を有する複数のトレンチゲート構造と、

前記ベース層の表層部であって、前記IGBT領域に形成された前記トレンチと接するように形成された第1導電型のエミッタ領域(19)と、

前記ドリフト層を挟んで前記ベース層側と反対側に形成された第2導電型のコレクタ層(16)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成されると共に前記コレクタ層と隣接する第1導電型のカソード層(17)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(22)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(18)と、を備え、

前記コレクタ層上の領域が前記IGBT領域とされ、前記カソード層上の領域が前記FWD領域とされており、

前記トレンチは、前記IGBT領域に形成される前記ゲート電極としての第1ゲート電極(14a)が配置されるIGBT用トレンチ(13a)と、前記FWD領域に形成され、前記第1ゲート電極とは別に制御される前記ゲート電極としての第2ゲート電極(14b)が配置されるFWD用トレンチ(13b)であり、

前記IGBT用トレンチは、前記半導体基板の面方向における一方向に沿った第1方向に延設されたIGBT用第1トレンチ(131a)と、前記半導体基板の面方向における前記第1方向と交差する第2方向に延設されたIGBT用第2トレンチ(132a)とが連通された格子状とされており、

前記FWD用トレンチは、前記第1方向に延設されたFWD用第1トレンチ(131b)と、前記第2方向に延設されたFWD用第2トレンチ(132b)とが連通された格子状とされ、

前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチ(133a)の中心と、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチ(133b)の中心との間を分離セル領域(3a)とすると、

前記分離セル領域には、前記IGBT用第1トレンチのうちの最も前記FWD用トレンチ側に位置するトレンチと、前記FWD用第1トレンチのうちの最も前記IGBT用トレンチ側に位置するトレンチとを連通させる連通トレンチ(134)が形成されており、

前記連通トレンチには、前記第1ゲート電極と前記第2ゲート電極とを絶縁する絶縁膜(135)が配置されている半導体装置。 - 前記ドリフト層と前記ベース層との間には、第2導電型の電界緩和領域(26)が形成され、

前記電界緩和領域と前記ベース層との間には、第1導電型のバリア領域(27)が形成され、

前記ベース層の表層部には、前記第1電極と接続されると共に前記バリア領域と接続される第1導電型のピラー領域(28)が形成されている請求項1ないし10のいずれか1つに記載の半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018169878A JP6996461B2 (ja) | 2018-09-11 | 2018-09-11 | 半導体装置 |

| PCT/JP2019/033935 WO2020054447A1 (ja) | 2018-09-11 | 2019-08-29 | 半導体装置 |

| CN201980058845.7A CN112673466B (zh) | 2018-09-11 | 2019-08-29 | 半导体装置 |

| US17/197,308 US11476355B2 (en) | 2018-09-11 | 2021-03-10 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018169878A JP6996461B2 (ja) | 2018-09-11 | 2018-09-11 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020043237A JP2020043237A (ja) | 2020-03-19 |

| JP2020043237A5 JP2020043237A5 (ja) | 2021-03-25 |

| JP6996461B2 true JP6996461B2 (ja) | 2022-01-17 |

Family

ID=69778271

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018169878A Active JP6996461B2 (ja) | 2018-09-11 | 2018-09-11 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US11476355B2 (ja) |

| JP (1) | JP6996461B2 (ja) |

| CN (1) | CN112673466B (ja) |

| WO (1) | WO2020054447A1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7319601B2 (ja) * | 2019-11-01 | 2023-08-02 | 株式会社東芝 | 半導体装置 |

| JP7459666B2 (ja) * | 2020-06-04 | 2024-04-02 | 三菱電機株式会社 | 半導体装置 |

| CN114600252A (zh) * | 2020-06-18 | 2022-06-07 | 丹尼克斯半导体有限公司 | 具有受控阳极注入的逆导型igbt |

| JP7456902B2 (ja) | 2020-09-17 | 2024-03-27 | 株式会社東芝 | 半導体装置 |

| JP7528743B2 (ja) * | 2020-11-27 | 2024-08-06 | 三菱電機株式会社 | 半導体装置 |

| JP7486407B2 (ja) * | 2020-11-27 | 2024-05-17 | 三菱電機株式会社 | 半導体装置および半導体装置の製造方法 |

| EP4139965A1 (en) * | 2021-03-31 | 2023-03-01 | Dynex Semiconductor Limited | Power semiconductor device |

| JP2024067299A (ja) * | 2022-11-04 | 2024-05-17 | 株式会社デンソー | 半導体装置とその製造方法 |

| CN121040233A (zh) * | 2023-11-29 | 2025-11-28 | 富士电机株式会社 | 半导体装置 |

| EP4583165A1 (en) * | 2024-01-04 | 2025-07-09 | Nio Technology (Anhui) Co., Ltd | Reverse conducting insulated-gate bipolar transistor and method of manufacturing |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009021557A (ja) | 2007-06-14 | 2009-01-29 | Denso Corp | 半導体装置 |

| JP2012151470A (ja) | 2011-01-17 | 2012-08-09 | Infineon Technologies Austria Ag | 半導体素子および逆導通igbt |

| JP2016197678A (ja) | 2015-04-06 | 2016-11-24 | 三菱電機株式会社 | 半導体装置 |

| JP2016225560A (ja) | 2015-06-03 | 2016-12-28 | トヨタ自動車株式会社 | 半導体装置 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4799829B2 (ja) | 2003-08-27 | 2011-10-26 | 三菱電機株式会社 | 絶縁ゲート型トランジスタ及びインバータ回路 |

| JP4830360B2 (ja) * | 2005-06-17 | 2011-12-07 | 株式会社デンソー | 半導体装置およびその製造方法 |

| JP5470826B2 (ja) * | 2008-12-08 | 2014-04-16 | 株式会社デンソー | 半導体装置 |

| JP2010263149A (ja) * | 2009-05-11 | 2010-11-18 | Toyota Motor Corp | 半導体装置 |

| JP5768395B2 (ja) * | 2010-07-27 | 2015-08-26 | 株式会社デンソー | 半導体装置およびその制御方法 |

| US8716746B2 (en) | 2010-08-17 | 2014-05-06 | Denso Corporation | Semiconductor device |

| JP5321669B2 (ja) * | 2010-11-25 | 2013-10-23 | 株式会社デンソー | 半導体装置 |

| JP5874210B2 (ja) | 2011-06-23 | 2016-03-02 | トヨタ自動車株式会社 | ダイオード |

| EP2725623B1 (en) * | 2011-09-08 | 2019-10-30 | Fuji Electric Co., Ltd. | Semiconductor device |

| US9159786B2 (en) * | 2012-02-20 | 2015-10-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dual gate lateral MOSFET |

| JP5825201B2 (ja) * | 2012-03-05 | 2015-12-02 | 株式会社デンソー | 半導体装置およびその製造方法 |

| US9136158B2 (en) * | 2012-03-09 | 2015-09-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Lateral MOSFET with dielectric isolation trench |

| JP5942737B2 (ja) * | 2012-09-24 | 2016-06-29 | 株式会社デンソー | 半導体装置 |

| JP6135636B2 (ja) | 2014-10-17 | 2017-05-31 | トヨタ自動車株式会社 | 半導体装置 |

| JP6260515B2 (ja) | 2014-11-13 | 2018-01-17 | 三菱電機株式会社 | 半導体装置 |

| JP6344483B2 (ja) * | 2014-11-17 | 2018-06-20 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP6261494B2 (ja) * | 2014-12-03 | 2018-01-17 | 三菱電機株式会社 | 電力用半導体装置 |

| US20170309704A1 (en) * | 2015-01-14 | 2017-10-26 | Mitsubishi Electric Corporation | Semiconductor device and manufacturing method therefor |

| JP6641983B2 (ja) * | 2015-01-16 | 2020-02-05 | 株式会社デンソー | 半導体装置 |

| WO2016114131A1 (ja) * | 2015-01-16 | 2016-07-21 | 株式会社デンソー | 半導体装置 |

| JP6334465B2 (ja) * | 2015-06-17 | 2018-05-30 | 富士電機株式会社 | 半導体装置 |

| JP6428503B2 (ja) * | 2015-06-24 | 2018-11-28 | 株式会社デンソー | 半導体装置 |

| US10559663B2 (en) * | 2016-10-14 | 2020-02-11 | Fuji Electric Co., Ltd. | Semiconductor device with improved current flow distribution |

| JP6589817B2 (ja) * | 2016-10-26 | 2019-10-16 | 株式会社デンソー | 半導体装置 |

| JP6780777B2 (ja) * | 2017-05-31 | 2020-11-04 | 富士電機株式会社 | 半導体装置 |

| CN110785852B (zh) * | 2017-12-06 | 2023-10-24 | 富士电机株式会社 | 半导体装置 |

-

2018

- 2018-09-11 JP JP2018169878A patent/JP6996461B2/ja active Active

-

2019

- 2019-08-29 CN CN201980058845.7A patent/CN112673466B/zh active Active

- 2019-08-29 WO PCT/JP2019/033935 patent/WO2020054447A1/ja not_active Ceased

-

2021

- 2021-03-10 US US17/197,308 patent/US11476355B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009021557A (ja) | 2007-06-14 | 2009-01-29 | Denso Corp | 半導体装置 |

| JP2012151470A (ja) | 2011-01-17 | 2012-08-09 | Infineon Technologies Austria Ag | 半導体素子および逆導通igbt |

| JP2016197678A (ja) | 2015-04-06 | 2016-11-24 | 三菱電機株式会社 | 半導体装置 |

| JP2016225560A (ja) | 2015-06-03 | 2016-12-28 | トヨタ自動車株式会社 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN112673466B (zh) | 2024-02-23 |

| US11476355B2 (en) | 2022-10-18 |

| WO2020054447A1 (ja) | 2020-03-19 |

| US20210202725A1 (en) | 2021-07-01 |

| CN112673466A (zh) | 2021-04-16 |

| JP2020043237A (ja) | 2020-03-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6996461B2 (ja) | 半導体装置 | |

| JP6589817B2 (ja) | 半導体装置 | |

| JP6443267B2 (ja) | 半導体装置 | |

| JP5636808B2 (ja) | 半導体装置 | |

| JP6641983B2 (ja) | 半導体装置 | |

| JP2007134625A (ja) | 半導体装置およびその製造方法 | |

| JP2016029710A (ja) | 半導体装置 | |

| JP7435214B2 (ja) | 半導体装置 | |

| WO2017199679A1 (ja) | 半導体装置 | |

| JP2016092163A (ja) | 半導体装置 | |

| US12191381B2 (en) | Semiconductor device | |

| WO2016114131A1 (ja) | 半導体装置 | |

| CN108735808A (zh) | 半导体开关元件及其制造方法 | |

| JP5151175B2 (ja) | 半導体装置 | |

| JP5664029B2 (ja) | 半導体装置 | |

| US20220310830A1 (en) | Semiconductor device | |

| JP2021145026A (ja) | 半導体装置 | |

| WO2019098122A1 (ja) | 半導体装置 | |

| JP2016096307A (ja) | 半導体装置 | |

| JP7338242B2 (ja) | 半導体装置 | |

| JP7294004B2 (ja) | 半導体装置 | |

| JP4830732B2 (ja) | 半導体装置 | |

| JP7596930B2 (ja) | 半導体装置 | |

| JP2025069398A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20201030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20201030 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201120 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211116 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211129 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6996461 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |