JP6181232B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6181232B2 JP6181232B2 JP2016092888A JP2016092888A JP6181232B2 JP 6181232 B2 JP6181232 B2 JP 6181232B2 JP 2016092888 A JP2016092888 A JP 2016092888A JP 2016092888 A JP2016092888 A JP 2016092888A JP 6181232 B2 JP6181232 B2 JP 6181232B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- memory cell

- conductive layer

- layer

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/404—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with one charge-transfer gate, e.g. MOS transistor, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/405—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with three charge-transfer gates, e.g. MOS transistors, per cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- H10W20/43—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Thin Film Transistor (AREA)

- Dram (AREA)

- Physics & Mathematics (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Geometry (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

Description

挙げられる(例えば特許文献1)。

オン状態にすることにより、メモリセルの選択動作を行い、選択したメモリセルにおいて

、例えばデータの書き込みなどの動作を行う。

るため、メモリセル毎に選択動作を行うことができなかった。

メモリセルも選択されることにより、該同じ行の全てのメモリセルのデータが変化してし

まい、データの再書き込みを行う必要があった。このため、データの書き込み時間も長か

った。

のメモリセルと、を少なくとも設ける。

ース、ドレイン、及び2つのゲートを有するトランジスタを用い、ソース及びドレインの

一方にはデータ信号を入力し、2つのゲートの一方の電圧を行方向にメモリセルを選択す

る信号である行選択信号により制御し、2つのゲートの他方の電圧を列方向にメモリセル

を選択する信号である列選択信号により制御する。つまり、各メモリセルにおける選択ト

ランジスタとして機能するトランジスタを、行方向にメモリセルを選択する行選択信号と

列方向にメモリセルを選択する列選択信号とを用いて選択する。

じ行選択信号を入力し、且つ異なる列選択信号を入力する。

力トランジスタとして機能するトランジスタとしては、ソース、ドレイン、2つのゲート

を有するトランジスタを用い、2つのゲートの一方を出力トランジスタとして機能するト

ランジスタのソース及びドレインの一方に電気的に接続させることによりダイオード接続

の状態にし、2つのゲートの他方を上記選択トランジスタとして機能するトランジスタの

ソース及びドレインの他方に電気的に接続させる。上記出力トランジスタとして機能する

トランジスタを用いることにより、出力トランジスタのリーク電流による、データ線とな

る配線における電圧の変動の抑制を図る。

ランジスタとして機能するトランジスタを備えることにより、さらに回路面積の縮小を図

る。

、本発明の趣旨及びその範囲から逸脱することなく実施の形態の内容を変更することは、

当業者であれば容易である。よって、本発明は、以下に示す実施の形態の記載内容に限定

されない。

の内容を互いに置き換えることができる。

の数は、序数の数に限定されない。

本実施の形態では、メモリセル毎の選択動作が可能な記憶装置の例について説明する。

ルを具備する。上記メモリセルは、例えばメモリセルアレイに設けられる。

リセル100(a,c)(cはaより大きい自然数)と、メモリセル100(d,b)(

dはbより大きい自然数)と、メモリセル100(d,c)と、を具備する。なお、必ず

しもメモリセル100(d,c)を設けなくてもよい。また、メモリセル100(a,b

)、メモリセル100(a,c)、メモリセル100(d,b)、及びメモリセル100

(d,c)以外にメモリセルを設けてもよい。また、メモリセル100(a,b)、メモ

リセル100(a,c)、メモリセル100(d,b)、及びメモリセル100(d,c

)のそれぞれの間の一つ又は複数にメモリセルを設けてもよい。このとき、そのメモリセ

ルは、メモリセル100(a,b)、メモリセル100(a,c)、メモリセル100(

d,b)、及びメモリセル100(d,c)と同じ構成又は異なる構成であってもよい。

設けられ、メモリセル100(d,b)と同じ行に設けられ、メモリセル100(a,c

)と同じ列に設けられる。

100(a,c)、メモリセル100(d,b)、及びメモリセル100(d,c)のそ

れぞれ)は、トランジスタ111と、データ保持回路112と、を備える。なお、図1(

A)において、同じメモリセル100に設けられたトランジスタ111及びデータ保持回

路112を、メモリセル100と同じ行列番号を記して表している。例えば、メモリセル

100(a,b)に設けられたトランジスタ111をトランジスタ111(a,b)と記

し、メモリセル100(a,b)に設けられたデータ保持回路112をデータ保持回路1

12(a,b)と記す。

。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト(V)で表されるこ

とがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、あ

る一点の電位と基準となる電位(基準電位ともいう)との電位差を、該一点の電圧として

用いる場合がある。

ランジスタである。

号が入力され、トランジスタ111の第2のゲートに第1の列選択信号が入力される。

号が入力され、トランジスタ111の第2のゲートに第2の列選択信号が入力される。

号が入力され、トランジスタ111の第2のゲートに第1の列選択信号が入力される。

号が入力され、トランジスタ111の第2のゲートに第2の列選択信号が入力される。

列方向にメモリセルを選択するパルス信号である。

ける少なくともデータの書き込み及びデータの保持を制御する機能を有し、選択トランジ

スタとして機能する。

ンジスタ111としては、例えばチャネルが形成される酸化物半導体層を含むトランジス

タ、又はチャネルが形成され、元素周期表における第14族の半導体(シリコンなど)を

含有する半導体層を含むトランジスタなどを用いることができる。このとき、第1のゲー

ト及び第2のゲートの間には、上記半導体層が設けられる。また、このとき、上記半導体

層を介して第2のゲートを第1のゲートと重畳させることにより記憶装置の回路面積を小

さくすることもできる。

しくは2.5eV以上、より好ましくは3eV以上である。また、上記酸化物半導体層は

、真性(I型ともいう)、又は実質的に真性である半導体層である。

ら見て、三角形、六角形、正三角形、又は正六角形の原子配列を有し、且つ、c軸方向(

層の厚さ方向ともいう)に垂直な方向に金属原子が層状に配列した相、又はc軸方向に垂

直な方向に金属原子と酸素原子が層状に配列した相(CAAC:c axis alig

ned crystalともいう)を含む酸化物の層を用いることもできる。CAACで

ある酸化物半導体層をトランジスタのチャネルが形成される層(チャネル形成層ともいう

)として用いることにより、例えば光によるトランジスタの劣化を抑制することができる

。

付与するドーパントが添加された一対の領域を有するトランジスタを用いることもできる

。ドーパントが添加された一対の領域を有する酸化物半導体層を含むトランジスタは、ド

ーパントが添加された一対の領域の間にチャネルが形成される。ドーパントが添加された

一対の領域の抵抗値は、チャネルが形成される領域(チャネル形成領域ともいう)より低

いことが好ましい。ドーパントが添加された一対の領域を有する酸化物半導体層を含むト

ランジスタを用いることにより、チャネルが形成される領域(チャネル形成領域ともいう

)と、トランジスタのソース又はドレインとの抵抗を小さくすることができるため、トラ

ンジスタの面積を小さくすること(微細化ともいう)ができる。

いたトランジスタよりオフ電流の低いトランジスタである。上記酸化物半導体層を含むト

ランジスタのオフ電流は、チャネル幅1μmあたり10aA(1×10−17A)以下、

好ましくはチャネル幅1μmあたり1aA(1×10−18A)以下、さらに好ましくは

チャネル幅1μmあたり10zA(1×10−20A)以下、さらに好ましくはチャネル

幅1μmあたり1zA(1×10−21A)以下、さらに好ましくはチャネル幅1μmあ

たり100yA(1×10−22A)以下である。

03と、を具備する。なお、図1(A)において、データ線101のそれぞれを、電気的

に接続されるメモリセル100と同じ列番号を記して表している。例えば、メモリセル1

00(a,b)に電気的に接続されたデータ線101をデータ線101_bと記して表す

。なお、図1(A)において、行選択線102のそれぞれを、電気的に接続されるメモリ

セル100と同じ行番号を記して表し、列選択線103のそれぞれを、電気的に接続され

るメモリセル100と同じ列番号を記して表している。例えば、メモリセル100(a,

b)に電気的に接続された列選択線103を列選択線103_bと記して表す。

おけるトランジスタ111のソース及びドレインの一方のそれぞれに電気的に接続され、

データ線101_cは、メモリセル100(a,c)及びメモリセル100(d,c)に

おけるトランジスタ111のソース及びドレインの一方のそれぞれに電気的に接続される

。データ線は、メモリセルとのデータのやりとりを行うための配線である。

おけるトランジスタ111の第1のゲートのそれぞれに電気的に接続され、行選択線10

2_dは、メモリセル100(d,b)及びメモリセル100(d,c)におけるトラン

ジスタ111の第1のゲートのそれぞれに電気的に接続される。行選択線は、行選択信号

が入力される配線である。

おけるトランジスタ111の第2のゲートのそれぞれに電気的に接続され、列選択線10

3_cは、メモリセル100(a,c)及びメモリセル100(d,c)におけるトラン

ジスタ111の第2のゲートのそれぞれに電気的に接続される。列選択線は、列選択信号

が入力される配線である。

ジスタの端子及び配線として機能させてもよい。

ータ保持回路112を設けなくてもよく、トランジスタ111のソース及びドレインの他

方を記憶ノードとして機能させる、又はトランジスタ111のソース及びドレインの他方

が記憶ノードに電気的に接続していればよい。

路、並びに容量素子及びトランジスタを用いた回路などを用いることができる。

駆動方法例について、図1(B)を用いて説明する。図1(B)は、図1(A)に示す記

憶装置の駆動方法例を説明するためのタイミングチャートである。ここでは、一例として

、メモリセル100(a,b)、メモリセル100(a,c)、メモリセル100(d,

b)、及びメモリセル100(d,c)のうち、M行N列目(Mはa又はd、Nはb又は

c)のメモリセル100(メモリセル100(M,N)ともいう)にデータを書き込む場

合について説明する。また、トランジスタ111は、Nチャネル型トランジスタとする。

また、トランジスタ111の閾値電圧は、列選択線103の電圧(列選択信号の電圧)に

応じてシフトする。

目のデータ線101(データ線101_Nともいう)の電圧を、データ信号に応じた電圧

にし、N本目のデータ線101以外のデータ線101(データ線101_otherとも

いう)の電圧を、基準電位Vrefと同等の値にする(図示せず)。また、M本目の行選

択線102(行選択線102_Mともいう)の電圧を、第Mの行選択信号により基準電位

Vrefより高い電圧VHにし、M本目以外の行選択線102(行選択線102_oth

erともいう)の電圧を、第M以外の行選択信号により基準電位Vrefと同等の値にし

、N本目の列選択線103(列選択線103_Nともいう)の電圧を、第Nの列選択信号

により基準電位Vrefと同等の値にし、N本目以外の列選択線103(列選択線103

_otherともいう)の電圧を、第N以外の列選択信号により基準電位Vrefより低

い電圧VLにする。なお、全ての行選択線102の電圧の設定より先に全ての列選択線1

03の電圧の設定を行う。また、記憶装置の仕様に応じて基準電位Vrefの値を設定す

る。また、選択されないメモリセル100においてトランジスタ111が確実にオフ状態

になるように電圧VLの値を適宜設定する。例えば、負電圧生成回路を用いて電圧VLを

生成することもできる。

)に応じた値に設定される。例えば、トランジスタ111がNチャネル型トランジスタの

場合、列選択線103の電圧を低くしていくと、トランジスタ111の閾値電圧は、正の

方向にシフトする。よって、M行N列目のメモリセル100が選択され、M行N列目のメ

モリセル100におけるトランジスタ111(トランジスタ111(M,N)ともいう)

がオン状態になり、N本目のデータ線101(データ線101_Nともいう)の電圧に応

じてM行N列目のメモリセル100にデータが書き込まれ、また、M行N列目以外のメモ

リセル100は選択されず、トランジスタ111がオフ状態になる。

それぞれの電圧を適宜変化させてメモリセル100毎に上記動作を行うことにより、全て

のメモリセル100にデータを書き込むことができる。なお、これに限定されず、例えば

各行のメモリセル100毎など、複数のメモリセル100毎にデータの書き込みを行って

もよい。

セルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、第1のメモリセル

と同じ列に設けられた第3のメモリセルと、を具備する。

セルのそれぞれが2つのゲートを有し、選択トランジスタとして機能する電界効果トラン

ジスタを備える。同じ行に設けられた第1のメモリセル及び第2のメモリセルにおいて、

電界効果トランジスタの2つのゲートの一方の電圧を同じ行選択信号により制御し、2つ

のゲートの他方の電圧を異なる列選択信号により制御する。また、同じ列に設けられた第

1のメモリセル及び第3のメモリセルにおいて、電界効果トランジスタの2つのゲートの

一方の電圧を異なる行選択信号により制御し、2つのゲートの他方の電圧を同じ列選択信

号により制御する。また、このとき、第1のゲート及び第2のゲートの間にチャネルが形

成される半導体層を設け、該半導体層を介して第2のゲートを第1のゲートと重畳させる

ことにより記憶装置の回路面積を小さくすることができる。

及び第2のメモリセルにおいて、電界効果トランジスタの2つのゲートの一方を同じ配線

に接続させることにより制御し、2つのゲートの他方を異なる配線に接続させることによ

り制御する。また、同じ列に設けられた第1のメモリセル及び第3のメモリセルにおいて

、電界効果トランジスタの2つのゲートの一方を異なる配線に接続させることにより制御

し、2つのゲートの他方を同じ配線に接続させることにより制御する。

リセルにおける電界効果トランジスタがオン状態のときに同じ行のメモリセルにおける電

界効果トランジスタをオフ状態にすることができる。よって、データの再書き込みを行う

必要がなくなるため、書き込み時間を短くすることもできる。また、2つのゲートを有す

るトランジスタを用いることにより、メモリセルにおける素子の数を増やすことなく、メ

モリセル毎に選択動作を行うことができる。

本実施の形態では、実施の形態1に示す記憶装置の例について説明する。

c)と、メモリセル200(d,b)と、メモリセル200(d,c)と、を具備する。

なお、必ずしもメモリセル200(d,c)を設けなくてもよい。また、メモリセル20

0(a,b)、メモリセル200(a,c)、メモリセル200(d,b)、及びメモリ

セル200(d,c)以外にメモリセルを設けてもよい。また、メモリセル200(a,

b)、メモリセル200(a,c)、メモリセル200(d,b)、及びメモリセル20

0(d,c)のそれぞれの間の一つ又は複数にメモリセルを設けてもよい。このとき、そ

のメモリセルは、メモリセル200(a,b)、メモリセル200(a,c)、メモリセ

ル200(d,b)、及びメモリセル200(d,c)と同じ構成又は異なる構成であっ

てもよい。

設けられ、メモリセル200(d,b)と同じ行に設けられ、メモリセル200(a,c

)と同じ列に設けられる。

(d,b)、及びメモリセル200(d,c)のそれぞれは、トランジスタ211と、ト

ランジスタ212と、を備える。なお、図2(A)において、同じメモリセル200に設

けられたトランジスタ211及びトランジスタ212を、メモリセル200と同じ行列番

号を記して表している。

トを有する。

号が入力され、トランジスタ211の第2のゲートに第1の列選択信号が入力される。

号が入力され、トランジスタ211の第2のゲートに第2の列選択信号が入力される。

号が入力され、トランジスタ211の第2のゲートに第1の列選択信号が入力される。

号が入力され、トランジスタ211の第2のゲートに第2の列選択信号が入力される。

ンジスタを用いることができる。

トを有する。

レインの一方に電気的に接続され、トランジスタ212はダイオード接続となる。

のドレインの他方に第1の読み出し選択信号が入力される。

ドレインの他方に第1の読み出し選択信号が入力される。

ドレインの他方に第2の読み出し選択信号が入力される。

ドレインの他方に第2の読み出し選択信号が入力される。

ンジスタ212は、実施の形態1の記憶装置におけるデータ保持回路に相当する。

ンジスタを用いることができる。また、トランジスタ212の構造を、トランジスタ21

1の構造と異なる構造にしてもよい。

03と、読み出し選択線204と、を具備する。なお、図2(A)において、行選択線2

02のそれぞれ及び読み出し選択線204のそれぞれを、電気的に接続されるメモリセル

200と同じ行番号を記して表し、データ線201のそれぞれ及び列選択線203のそれ

ぞれを、電気的に接続されるメモリセル200と同じ列番号を記して表している。

おけるトランジスタ211の第1のソース及び第1のドレインの一方のそれぞれ、並びに

メモリセル200(a,b)及びメモリセル200(d,b)におけるトランジスタ21

2の第2のソース及び第2のドレインの一方のそれぞれに電気的に接続され、データ線2

01_cは、メモリセル200(a,c)及びメモリセル200(d,c)におけるトラ

ンジスタ211の第1のソース及び第1のドレインの一方のそれぞれ、並びにメモリセル

200(a,c)及び200(d,c)におけるトランジスタ212の第2のソース及び

第2のドレインの一方のそれぞれに電気的に接続される。また、トランジスタ212の第

4のゲートは、トランジスタ211の第1のソース及び第1のドレインの他方に電気的に

接続される。トランジスタ212の第4のゲートの電圧は、メモリセルに記憶されるデー

タの状態を設定する電圧となる。

おけるトランジスタ211の第1のゲートのそれぞれに電気的に接続され、行選択線20

2_dは、メモリセル200(d,b)及びメモリセル200(d,c)におけるトラン

ジスタ211の第1のゲートのそれぞれに電気的に接続される。

おけるトランジスタ211の第2のゲートのそれぞれに電気的に接続され、列選択線20

3_cは、メモリセル200(a,c)及びメモリセル200(d,c)におけるトラン

ジスタ211の第2のゲートのそれぞれに電気的に接続される。

c)におけるトランジスタ212の第2のソース及び第2のドレインの他方のそれぞれに

電気的に接続され、読み出し選択線204_dは、メモリセル200(d,b)及びメモ

リセル200(d,c)におけるトランジスタ212の第2のソース及び第2のドレイン

の他方のそれぞれに電気的に接続される。読み出し選択線204は、データを読み出すメ

モリセルを選択する読み出し選択信号が入力される配線である。

ジスタの端子及び配線として機能させてもよい。

ば、トランジスタ212の上にトランジスタ211を設けてもよい。トランジスタ211

及びトランジスタ212を積層構造にすることにより、メモリセルの回路面積を小さくす

ることができる。

メモリセルを設けてもよい。これにより記憶装置の回路面積を小さくすることができる。

駆動方法例について、図2(B)を用いて説明する。図2(B)は、図2(A)に示す記

憶装置の駆動方法例を説明するためのタイミングチャートである。ここでは、一例として

、メモリセル200(a,b)、メモリセル200(a,c)、メモリセル200(d,

b)、及びメモリセル200(d,c)のうち、M行N列目のメモリセル200(メモリ

セル200(M,N)ともいう)にデータを書き込む場合の動作と、メモリセル200(

M,N)に記憶されたデータを読み出す場合の動作について説明する。また、トランジス

タ211及びトランジスタ212は、Nチャネル型トランジスタとする。また、基準電位

より大きい電圧VDDをデータ(1)とし、基準電位Vrefと同等の値の電圧をデータ

(0)とする。また、列選択線203の電圧(列選択信号の電圧)の値に応じてトランジ

スタ211の閾値電圧がシフトする。

タ線201(データ線201_Nともいう)の電圧を、データ信号に応じた電圧にし、N

本目のデータ線201以外のデータ線201(データ線201_otherともいう)の

電圧を、基準電位Vrefと同等の値にする(図示せず)。また、M本目の行選択線20

2(行選択線202_Mともいう)の電圧を、第Mの行選択信号により基準電位Vref

より高い電圧VHにし、M本目以外の行選択線202(行選択線202_otherとも

いう)の電圧を、第M以外の行選択信号により基準電位Vrefと同等の値にする。また

、N本目の列選択線203(列選択線203_Nともいう)の電圧を、第Nの列選択信号

により基準電位Vrefと同等の値にし、N本目以外の列選択線203(列選択線203

_otherともいう)の電圧を、第N以外の列選択信号により基準電位Vrefより低

い電圧VLにする。なお、全ての行選択線202の電圧の設定より先に全ての列選択線2

03の電圧の設定を行う。また、M本目の読み出し選択線204(読み出し選択線204

_Mともいう)の電圧を電圧VHにし、M本目以外の読み出し選択線204(読み出し選

択線204_otherともいう)の電圧を電圧VHにしてもよい。これにより、トラン

ジスタ212を確実にオフ状態にすることができるため、トランジスタ212のソース及

びドレインの間に流れるリーク電流を抑制することができる。

)に応じた値に設定される。よって、メモリセル200(M,N)が選択され、メモリセ

ル200(M,N)におけるトランジスタ211(トランジスタ211(M,N))がオ

ン状態になり、メモリセル200(M,N)におけるトランジスタ212(M,N)の第

4のゲートの電圧がN本目のデータ線201(データ線201_Nともいう)の電圧に応

じた値に設定され、メモリセル200(M,N)にデータが書き込まれる。また、メモリ

セル200(M,N)以外のメモリセルは選択されず、トランジスタ211がオフ状態に

なる。なお、トランジスタ211が確実にオフ状態になるように電圧VLの値を適宜設定

する。

ぞれ、及び読み出し選択線204のそれぞれの電圧を適宜変化させてメモリセル200毎

に上記動作を行うことにより、全てのメモリセル200にデータを書き込むことができる

。なお、これに限定されず、例えば各行のメモリセル200毎など、複数のメモリセル2

00毎にデータの書き込みを行ってもよい。

、N本目のデータ線201(データ線201_N)の電圧を、電圧VHにし、N本目のデ

ータ線201以外のデータ線201(データ線201_other)の電圧を、基準電位

Vrefと同等の値にする(図示せず)。また、M本目の行選択線202(行選択線20

2_M)の電圧を、第Mの行選択信号により基準電位Vrefと同等の値にし、M本目以

外の行選択線202(行選択線202_other)の電圧を、第M以外の行選択信号に

より基準電位Vrefと同等の値にする。また、N本目の列選択線203(列選択線20

3_N)の電圧を、第Nの列選択信号により基準電位Vrefと同等の値にし、N本目以

外の列選択線203(列選択線203_other)の電圧を、第N以外の列選択信号に

より基準電位Vrefと同等の値にする。また、M本目の読み出し選択線204(読み出

し選択線204_Mともいう)の電圧を基準電位Vrefより大きく、電圧VHより小さ

い電圧VMにし、M本目以外の読み出し選択線204(読み出し選択線204_othe

r)の電圧を電圧VHにする。なお、電圧VMの値は、トランジスタ212の第4のゲー

トの電圧が基準電位Vrefと同等の値のときにトランジスタ211がオフ状態になるよ

うに適宜設定される。

。

じて設定される。例えば、トランジスタ212がNチャネル型トランジスタの場合、トラ

ンジスタ212の第4のゲートの電圧が電圧VDDであるときには、トランジスタ212

の第4のゲートの電圧が基準電位Vrefと同等の値であるときに比べ、トランジスタ2

12の閾値電圧が負の方向にシフトする。

N)の第4のゲートの電圧が電圧VDD(データ(1))であれば、トランジスタ212

(M,N)がオン状態になり、データ線201_Nの電圧が変化する。また、このときト

ランジスタ212(M,N)がダイオード接続されているため、読み出し選択線204_

Mからデータ線201_Nへの方向に電流は流れない。

)の第4のゲートの電圧が基準電位Vrefと同等の値(データ(0))であれば、トラ

ンジスタ212(M,N)がオフ状態になり、データ線201_Nの電圧は変化しない。

メモリセル200(M,N)のデータを読み出すことができる。

ぞれ、及び読み出し選択線204のそれぞれの電圧を適宜変化させて各行のメモリセル2

00毎に上記動作を行うことにより、全てのメモリセル200のデータを読み出すことが

できる。このとき、同じ列の複数のメモリセル200のデータを順に読み出す場合には、

あるメモリセル200のデータを読み出した後、あるメモリセル200と同じ列の別のメ

モリセルのデータを読み出す前に、メモリセル200と同じ列にあり、メモリセル200

以外のメモリセルに電気的に接続されるデータ線201の電圧を電圧VHにする。

すように各メモリセル200に容量素子213を設けてもよい。

容量電極は、トランジスタ211の第1のソース及び第1のドレインの他方に電気的に接

続される。また、容量素子213の第2の容量電極は、接地される。また、容量素子21

3の第2の容量電極に所定の信号が入力されてもよい。

のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、第1のメ

モリセルと同じ列に設けられた第3のメモリセルと、を具備する。

セルのそれぞれが、第1のソース、第1のドレイン、第1のゲート、及び第2のゲートを

有する第1の電界効果トランジスタを備える。同じ行且つ異なる列に設けられた第1のメ

モリセル及び第2のメモリセルにおいて、第1の電界効果トランジスタの第1のゲートの

電圧を同じ行選択信号により制御し、第2のゲートの電圧を異なる列選択信号により制御

する。また、同じ列に設けられた第1のメモリセル及び第3のメモリセルにおいて、第1

の電界効果トランジスタの第1のゲートの電圧を異なる行選択信号により制御し、第2の

ゲートの電圧を同じ列選択信号により制御する。

及び第2のメモリセルにおいて、第1の電界効果トランジスタの第1のゲートを同じ配線

に接続させることにより制御し、第2のゲートを異なる配線に接続させることにより制御

する。また、同じ列に設けられた第1のメモリセル及び第3のメモリセルにおいて、第1

の電界効果トランジスタの第1のゲートを異なる配線に接続させることにより制御し、第

2のゲートを同じ配線に接続させることにより制御する。

リセルにおける電界効果トランジスタがオン状態のときに同じ行のメモリセルにおける電

界効果トランジスタをオフ状態にすることができる。よって、データの再書き込みを行う

必要がなくなるため、書き込み時間を短くすることもできる。

ルのそれぞれが、第2のソース、第2のドレイン、第3のゲート、及び第4のゲートを有

する第2の電界効果トランジスタを備え、第2の電界効果トランジスタの第3のゲートを

第2のソース及び第2のドレインの一方に電気的に接続させ、第4のゲートを第1の電界

効果トランジスタの第1のソース又は第1のドレインに電気的に接続させることにより、

第2の電界効果トランジスタがオフ状態のときに第2のソース及び第2のドレインの間に

流れるリーク電流を抑制することができるため、データ線となる配線における電圧の変動

を抑制することができ、記憶装置の信頼性を向上させることができる。

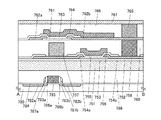

本実施の形態では、上記実施の形態2の記憶装置におけるメモリセルの構造例について、

図4を用いて説明する。図4は、本実施の形態におけるメモリセルの構造例を示す図であ

る。なお、ここでは、一例として、図2に示すメモリセルの構造例について説明する。な

お、図4では、実際の寸法と異なる構成要素を含む。

754aと、導電層754bと、絶縁層755と、導電層756と、導電層757と、導

電層758と、絶縁層760と、半導体層761と、導電層762aと、導電層762b

と、絶縁層763と、導電層764と、導電層765と、絶縁層766と、導電層767

と、を含む。

択トランジスタとして機能するトランジスタにおける、2つのゲートの一つ(列選択信号

が入力されるゲート)としての機能を有する。また、導電層751が列選択線としての機

能を有していてもよい。なお、トランジスタのゲートとしての機能を有する層をゲート電

極又はゲート配線ともいう。

タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又

はこれらを主成分とする合金材料の層を用いることができる。また、導電層751に適用

可能な材料の積層により、導電層751を構成することもできる。

。

選択トランジスタとして機能するトランジスタのゲート絶縁層としての機能を有する。

化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化ア

ルミニウム、酸化ハフニウム、有機絶縁材料(例えばポリイミド又はアクリルなど)など

の材料の層を用いることができる。また、絶縁層752に適用可能な材料の積層により絶

縁層752を構成してもよい。

導体(シリコンなど)を含有する半導体層などを用いることができる。

系金属酸化物、又は二元系金属酸化物などを用いることができる。

ることができる。

n−O系金属酸化物、In−Al−Zn−O系金属酸化物、Sn−Ga−Zn−O系金属

酸化物、Al−Ga−Zn−O系金属酸化物、又はSn−Al−Zn−O系金属酸化物な

どを用いることができる。

酸化物、Al−Zn−O系金属酸化物、Zn−Mg−O系金属酸化物、Sn−Mg−O系

金属酸化物、In−Mg−O系金属酸化物、In−Sn−O系金属酸化物、又はIn−G

a−O系金属酸化物などを用いることができる。

はZn−O系金属酸化物などを用いることもできる。また、上記酸化物半導体として適用

可能な金属酸化物は、酸化シリコンを含んでいてもよい。

=1:2(モル数比に換算するとIn2O3:ZnO=25:1乃至In2O3:ZnO

=1:4)、好ましくはIn:Zn=20:1乃至In:Zn=1:1(モル数比に換算

するとIn2O3:ZnO=10:1乃至In2O3:ZnO=1:2)、さらに好まし

くはIn:Zn=15:1乃至In:Zn=1.5:1(モル数比に換算するとIn2O

3:ZnO=15:2乃至In2O3:ZnO=3:4)の組成比である酸化物ターゲッ

トを用いてIn−Zn−O系金属酸化物の半導体層を形成することができる。例えば、I

n−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=

S:U:Rのとき、R>1.5S+Uとする。Inの量を多くすることにより、トランジ

スタの移動度を向上させることができる。

れる材料を用いることもできる。InLO3(ZnO)mのLは、Ga、Al、Mn、及

びCoから選ばれた一つ又は複数の金属元素を示す。

晶であって、ab面に垂直な方向から見て、三角形、六角形、正三角形、又は正六角形の

原子配列を有し、且つ、c軸方向に垂直な方向に金属原子が層状に配列した相、又はc軸

方向に垂直な方向に金属原子と酸素原子が層状に配列した相を有してもよい。

ルにおける選択トランジスタとして機能するトランジスタのソース又はドレインとしての

機能を有する。なお、トランジスタのソースとしての機能を有する導電層をソース電極又

はソース配線ともいう。また、トランジスタのドレインとしての機能を有する導電層をド

レイン電極又はドレイン配線ともいう。

ルにおける選択トランジスタとして機能するトランジスタのソース又はドレインとしての

機能を有する。

ム、銅、タンタル、チタン、モリブデン、若しくはタングステンなどの金属材料、又はこ

れらの金属材料を主成分とする合金材料の層を用いることができる。合金材料の層として

は、例えばCu−Mg−Al合金材料の層を用いることができる。

ることもできる。なお、導電層754a及び導電層754bに適用可能な導電性の金属酸

化物は、酸化シリコンを含んでいてもよい。

a及び導電層754bを構成することもできる。例えば、Cu−Mg−Al合金材料の層

の上に銅の層が設けられた積層により、導電層754a及び導電層754bを構成するこ

とにより、導電層754a及び導電層754bに接する他の層との密着性を高めることが

できる。

る。絶縁層755は、メモリセルにおける選択トランジスタとして機能するトランジスタ

のゲート絶縁層としての機能を有する。

に適用する材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、絶

縁層755に適用可能な材料の積層により絶縁層755を構成してもよい。

モリセルにおける選択トランジスタとして機能するトランジスタの2つのゲートの一つ(

行選択信号が入力されるゲート)としての機能を有する。また、導電層756が行選択線

としての機能を有していてもよい。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層756に適用可能な材料の積層により導電層756を構成してもよい。

的に接続される。導電層757は、出力トランジスタとして機能するトランジスタの2つ

のゲートの一つ(選択トランジスタとして機能するトランジスタの2つのゲートの一つに

電気的に接続されるゲート)としての機能を有する。なお、導電層757は導電層756

より厚いことが好ましい。導電層757を導電層756より厚くすることにより、導電層

756と他の導電層により生じる寄生容量を小さくすることができる。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層757に適用可能な材料の積層により導電層757を構成してもよい。

的に接続される。導電層758は、電極又は配線としての機能を有する。なお、導電層7

58は、導電層757より厚い。なお、必ずしも導電層758を設けなくてもよい。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層758に適用可能な材料の積層により導電層758を構成してもよい。

縁層760は、平坦化層、及びメモリセルにおける出力トランジスタとして機能するトラ

ンジスタのゲート絶縁層としての機能を有する。

、絶縁層760に適用可能な材料の積層により絶縁層760を構成してもよい。

753に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。

ルにおける出力トランジスタとして機能するトランジスタのソース又はドレインとしての

機能を有する。

62bは、メモリセルにおける出力トランジスタとして機能するトランジスタのソース又

はドレインとしての機能を有する。

に適用可能な材料の層のうち、導電層754a及び導電層754bに適用した材料の層と

同じ材料の層又は異なる材料の層を用いることができる。また、導電層762a及び導電

層762bに適用可能な材料の積層により導電層762a及び導電層762bを構成して

もよい。

る。絶縁層763は、メモリセルにおける出力トランジスタとして機能するトランジスタ

のゲート絶縁層としての機能を有する。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、絶

縁層763に適用可能な材料の積層により絶縁層763を構成してもよい。

れた開口部を介して導電層762bに電気的に接続される。導電層764は、メモリセル

における出力トランジスタとして機能するトランジスタの2つのゲートの一つ(出力トラ

ンジスタとして機能するトランジスタのソース及びドレインの一方に電気的に接続される

ゲート)としての機能を有する。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層764に適用可能な材料の積層により導電層764を構成してもよい。

続される。導電層765は、電極又は配線としての機能を有する。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層765に適用可能な材料の積層により導電層765を構成してもよい。

した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、絶縁層7

66に適用可能な材料の積層により絶縁層766を構成してもよい。

りを行う配線としての機能を有する。

のうち、導電層754a及び導電層754bに適用した材料の層と同じ材料の層又は異な

る材料の層を用いることができる。また、導電層767に適用可能な材料の積層により導

電層767を構成してもよい。

上記駆動回路の上に設けられたメモリセルの構造例について図5に示す。なお、図5にお

いて図4と同一の構成要素である部分では、図4に示すメモリセルの構造例の説明を適宜

援用することができる。

トランジスタが設けられた半導体層780の上に設けられる。

3bを有する。

に設けられた半導体層を半導体層780として用いることもできる。

よい。

与するドーパントが添加された領域である。領域782a及び領域782bは、メモリセ

ルにおける出力トランジスタとして機能するトランジスタのソース領域又はドレイン領域

としての機能を有する。

て設けられ、領域783a及び領域783bの間の領域がチャネル形成領域となる。領域

783aは、領域782aに接し、領域783bは、領域782bに接する。

型の導電型を付与するドーパントが添加された領域である。

2bのドーパントの濃度より低くてもよい。このとき、領域783a及び領域783bを

低濃度領域ともいう。また、このとき領域782a及び領域782bを高濃度領域と呼ん

でもよい。また、領域783a及び領域783bの深さは、領域782a及び領域782

bの深さより小さくてもよいが、これに限定されない。

るトランジスタのゲート絶縁層としての機能を有する。

化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化ア

ルミニウム、酸化ハフニウム、有機絶縁材料(例えばポリイミド又はアクリルなど)など

の材料の層を用いることができる。また、絶縁層784に適用可能な材料の積層により絶

縁層784を構成してもよい。

する半導体層780の領域が駆動回路を構成するトランジスタのチャネル形成領域になる

。導電層785は、駆動回路を構成するトランジスタのゲートとしての機能を有する。

に適用した材料の層と同じ材料の層又は異なる材料の層を用いることができる。また、導

電層785に適用可能な材料の積層により導電層785を構成することもできる。

る一対の側面の一方に接する。

る上記一対の側面の他方に接する。

層787a、及び絶縁層787bの上に設けられる。

としては、絶縁層784に適用可能な材料のうち、絶縁層784に適用した材料と同じ材

料の層又は異なる材料の層を用いることができる。また、絶縁層786a、絶縁層786

b、絶縁層787a、絶縁層787b、及び絶縁層788に適用可能な材料の積層により

、絶縁層786a、絶縁層786b、絶縁層787a、絶縁層787b、及び絶縁層78

8を構成することもできる。

制することができる。

作製方法例について、図6乃至図14を用いて説明する。

の一部をエッチングすることにより導電層751を形成する。

形成することにより第1の導電膜を形成することができる。

し、レジストマスクを用いることにより層又は膜の一部をエッチングすることができる。

なお、この場合、特に指定する場合を除き、エッチング処理後にレジストマスクを除去す

る。

を形成することにより絶縁層752を形成することができる。

部をエッチングすることにより半導体層753を形成する。

形成することにより酸化物半導体膜を形成することができる。なお、希ガス雰囲気下、酸

素雰囲気下、又は希ガスと酸素の混合雰囲気下で酸化物半導体膜を形成してもよい。例え

ば、酸素のみの雰囲気下で酸化物半導体膜を形成することにより、結晶性の高い酸化物半

導体膜を形成することができる。

[mol数比]の組成比である酸化物ターゲットを用いて酸化物半導体膜を形成すること

ができる。また、例えば、In2O3:Ga2O3:ZnO=1:1:2[mol数比]

の組成比である酸化物ターゲットを用いて酸化物半導体膜を形成してもよい。

が占める空間を除いた部分の体積の割合(相対密度ともいう)は、90%以上100%以

下、さらには95%以上99.9%以下であることが好ましい。相対密度の高い金属酸化

物ターゲットを用いることにより形成した酸化物半導体膜は、緻密な膜となる。

にし、基板750を100℃以上600℃以下、好ましくは200℃以上400℃以下に

加熱してもよい。基板750を加熱することにより、酸化物半導体膜の不純物濃度を低減

することができ、また、スパッタリング法による酸化物半導体膜の損傷を軽減することが

できる。

形成し、第2の導電膜の一部をエッチングすることにより、導電層754a及び導電層7

54bを形成する。

材料の膜を形成することにより第2の導電膜を形成することができる。また、導電層75

4a及び導電層754bに適用可能な材料の膜を積層させることにより第2の導電膜を形

成することもできる。

導電層754bの上に絶縁層755を形成する。

電膜の一部をエッチングすることにより、導電層756を形成することができる。

771及び開口部772を形成する。

膜を形成し、第4の導電膜の一部をエッチングすることにより導電層757を形成する。

膜を形成し、第5の導電膜の一部をエッチングすることにより導電層758を形成する。

することにより同一工程で導電層757及び導電層758を形成することもできる。

層756、導電層757、及び導電層758の上に絶縁層760を形成する。

成することにより絶縁層760を形成することができる。

露出させる。

の一部を除去して導電層758の上面を露出させることができる。

1を形成する。

を形成し、第6の導電膜の一部をエッチングすることにより導電層762a及び導電層7

62bを形成する。

電層762bを形成することができる。

bの上に絶縁層763を形成する。

電層762bの上面を露出させる。

7の導電膜を形成し、第7の導電膜の一部をエッチングすることにより導電層764を形

成する。

、第8の導電膜の一部をエッチングすることにより導電層765を形成する。

導電層765の上に絶縁層766を形成する。

露出させる。

の一部を除去して導電層765の上面を露出させることができる。

形成し、第9の導電膜の一部をエッチングすることにより導電層767を形成する。

00℃以上基板の歪み点未満の温度で加熱処理を行う。上記加熱処理を行うタイミングは

、酸化物半導体膜を形成した後であれば特に限定されない。また、上記加熱処理を複数回

行ってもよい。

からの熱伝導又は熱輻射により被処理物を加熱する装置を用いることができ、例えばGR

TA(Gas Rapid Thermal Annealing)装置又はLRTA(

Lamp Rapid Thermal Annealing)装置などのRTA(Ra

pid Thermal Annealing)装置を用いることができる。LRTA装

置は、例えばハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボン

アークランプ、高圧ナトリウムランプ、又は高圧水銀ランプなどのランプから発する光(

電磁波)の輻射により、被処理物を加熱する装置である。また、GRTA装置は、高温の

ガスを用いて加熱処理を行う装置である。高温のガスとしては、例えば希ガス、又は加熱

処理によって被処理物と反応しない不活性気体(例えば窒素)を用いることができる。

する過程で該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度のN2Oガス、又

は超乾燥エア(露点が−40℃以下、好ましくは−60℃以下の雰囲気)を導入してもよ

い。このとき、酸素ガス又はN2Oガスは、水、水素などを含まないことが好ましい。ま

た、加熱処理装置に導入する酸素ガス又はN2Oガスの純度を、6N以上、好ましくは7

N以上、すなわち、酸素ガス又はN2Oガス中の不純物濃度を1ppm以下、好ましくは

0.1ppm以下とすることが好ましい。酸素ガス又はN2Oガスの作用により、半導体

膜中の酸素欠乏に起因する欠陥を低減することができる。

(好ましくは200℃以上600℃以下、例えば250℃以上350℃以下)を行っても

よい。

ンジスタとして機能する第1の電界効果トランジスタと、出力トランジスタとして機能す

る第2の電界効果トランジスタの積層構造である。

界効果トランジスタを有する構造である。

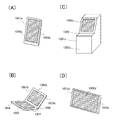

本実施の形態では、記憶装置の構成例について説明する。

の形態における記憶装置の構成例を示すブロック図である。

a(IDRV812aともいう)と、駆動回路812b(JDRV812bともいう)と

、複数のメモリセル(MCともいう)813と、を具備する。

力される。駆動制御回路811は、入力される書き込み制御信号、読み出し制御信号、及

びアドレス信号に応じて、複数の制御信号を生成して出力する機能を有する。例えば、駆

動制御回路811は、入力されるアドレス信号に応じて行アドレス信号及び列アドレス信

号を出力する機能を有する。

行アドレス信号に従って行方向に設けられた配線(例えば行選択線及び読み出し選択線を

含む)を選択し、選択した配線の電圧を設定する機能を有する。駆動回路812aは、例

えば第1のデコーダを備える。第1のデコーダは、入力された行アドレス信号に従って行

方向に設けられた配線を選択する機能を有する。

は、列方向に設けられた配線(例えば列選択線及びデータ線を含む)の電圧を設定する機

能を有する。駆動回路812bは、例えば第2のデコーダ及び複数のアナログスイッチを

備える。第2のデコーダは、列方向に設けられた配線を選択する機能を有し、複数のアナ

ログスイッチは、第2のデコーダから入力される信号に応じてデータ信号を出力するか否

かを制御する機能を有する。なお、駆動回路812bに読み出し回路を設けてもよい。読

み出し回路は、選択した配線に電気的に接続されたメモリセル813に記憶されたデータ

を読み出す機能を有する。

しては、上記実施の形態における記憶装置の構成を用いることができる。メモリセル81

3は、駆動回路812a及び駆動回路812bにより選択され、選択されたメモリセル8

13では、データの書き込み又はデータの読み出しが行われる。

セルを選択し、書き込み動作又は読み出し動作を行う。

、本実施の形態における記憶装置の例を示す模式図である。

メモリともいう。図16(A)に示す記憶装置は、筐体901aと、コネクタ部902a

と、を備える。

が設けられる。

の電子機器におけるUSBポートに接続可能な端子部である。

入して記憶装置と該電子機器を電気的に接続させることにより、例えば電子機器から記憶

装置へのデータの書き込み、又は記憶装置から該電子機器へのデータの読み出しを行うこ

とができる。

置は、筐体901bと、コネクタ部902bと、を備える。

が設けられる。

の電子機器におけるカードスロット部に接続可能な端子部である。

に挿入して記憶装置と該電子機器を電気的に接続させることにより、例えば電子機器から

記憶装置へのデータの書き込み、又は記憶装置から該電子機器へのデータの読み出しを行

うことができる。

ることにより、ノイズによるデータ信号への影響の少ない記憶装置を構成することができ

る。

本実施の形態では、上記実施の形態における記憶装置を備えた電子機器の例について説明

する。

する。

情報端末は、筐体1001aと、筐体1001aに設けられた表示部1002aと、を具

備する。

(A)に示す携帯型情報端末を操作するためのボタンのうち、一つ又は複数を設けてもよ

い。

外部機器とCPU及び記憶回路との間で信号の送受信を行うインターフェースと、外部機

器との信号の送受信を行うアンテナと、を備える。

タ、及び遊技機の一つ又は複数としての機能を有する。

に示す携帯型情報端末は、筐体1001bと、筐体1001bに設けられた表示部100

2bと、筐体1004と、筐体1004に設けられた表示部1005と、筐体1001b

及び筐体1004を接続する軸部1006と、を具備する。

筐体1004を動かすことにより、筐体1001bを筐体1004に重畳させることがで

きる。

続させるための接続端子、図17(B)に示す携帯型情報端末を操作するためのボタンの

うち、一つ又は複数を設けてもよい。

示させてもよい。なお、表示部1005を必ずしも設けなくてもよく、表示部1005の

代わりに、入力装置であるキーボードを設けてもよい。

と、記憶回路と、外部機器とCPU及び記憶回路との間で信号の送受信を行うインターフ

ェースと、を備える。なお、図17(B)に示す携帯型情報端末に、外部との信号の送受

信を行うアンテナを設けてもよい。

タ、及び遊技機の一つ又は複数としての機能を有する。

情報端末は、筐体1001cと、筐体1001cに設けられた表示部1002cと、を具

備する。

る。

路と、外部機器とCPU及び記憶回路との間で信号の送受信を行うインターフェースと、

を備える。なお、図17(C)に示す設置型情報端末に、外部との信号の送受信を行うア

ンテナを設けてもよい。

券などを出力する券出力部、硬貨投入部、及び紙幣挿入部の一つ又は複数を設けてもよい

。

ための情報通信端末(マルチメディアステーションともいう)、又は遊技機としての機能

を有する。

体1001dと、筐体1001dに設けられた表示部1002dと、を具備する。なお、

筐体1001dを支持する支持台を設けてもよい。

(D)に示す設置型情報端末を操作するためのボタンのうち、一つ又は複数を設けてもよ

い。

路と、外部機器とCPU及び記憶回路との間で信号の送受信を行うインターフェースと、

を備えてもよい。なお、図17(D)に示す設置型情報端末に、外部との信号の送受信を

行うアンテナを設けてもよい。

レビジョン装置としての機能を有する。

図17(A)乃至図17(D)に示す電子機器の記憶装置の一つとして用いられる。なお

、これに限定されず、例えば図17(A)乃至図17(D)に示す電子機器に記憶装置接

続部を設け、該記憶装置接続部に例えば図16(A)又は図16(B)に示す記憶装置を

接続させることにより、該記憶装置とのデータの読み書きを行ってもよい。

ける記憶装置が用いられた記憶装置を具備する構成である。

間保持することができるため、信頼性が向上し、消費電力を低減することができる。

101 データ線

102 行選択線

103 列選択線

111 トランジスタ

112 データ保持回路

200 メモリセル

201 データ線

202 行選択線

203 列選択線

204 選択線

211 トランジスタ

212 トランジスタ

213 容量素子

750 基板

751 導電層

752 絶縁層

753 半導体層

754a 導電層

754b 導電層

755 絶縁層

756 導電層

757 導電層

758 導電層

760 絶縁層

761 半導体層

762a 導電層

762b 導電層

763 絶縁層

764 導電層

765 導電層

766 絶縁層

767 導電層

771 開口部

772 開口部

780 半導体層

782a 領域

782b 領域

783a 領域

783b 領域

784 絶縁層

785 導電層

786a 絶縁層

786b 絶縁層

787a 絶縁層

787b 絶縁層

788 絶縁層

811 駆動制御回路

812a 駆動回路

812b 駆動回路

813 メモリセル

814 メモリセルアレイ

901a 筐体

901b 筐体

902a コネクタ部

902b コネクタ部

1001a 筐体

1001b 筐体

1001c 筐体

1001d 筐体

1002a 表示部

1002b 表示部

1002c 表示部

1002d 表示部

1003a 側面

1003b 側面

1003c 側面

1003d 側面

1004 筐体

1005 表示部

1006 軸部

1007 側面

1008 甲板部

Claims (4)

- 第1の配線と、

第2の配線と、

第3の配線と、

第4の配線と、

ソースと、ドレインと、第1のゲートと、第2のゲートと、半導体層と、を有する第1のトランジスタと、

ソースと、ドレインと、第1のゲートと、第2のゲートと、半導体層と、を有する第2のトランジスタと、を有し、

前記第1のトランジスタの半導体層は、前記第1のトランジスタの第1のゲートと前記第1のトランジスタの第2のゲートの間に設けられ、

前記第1のトランジスタの第1のゲートは、前記第1の配線と電気的に接続され、

前記第1のトランジスタの第2のゲートは、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第1のゲートは、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第2のゲートは、前記第4の配線と電気的に接続され、

前記第1のトランジスタの半導体層は、インジウムと、亜鉛と、酸素とを有し、

前記第2のトランジスタの半導体層は、インジウムと、亜鉛と、酸素とを有することを特徴とする半導体装置。 - 第1の配線と、

第2の配線と、

第3の配線と、

第4の配線と、

ソースと、ドレインと、第1のゲートと、第2のゲートと、半導体層と、を有する第1のトランジスタと、

ソースと、ドレインと、第1のゲートと、第2のゲートと、半導体層と、を有する第2のトランジスタと、を有し、

前記第1のトランジスタの第1のゲートは、前記第1の配線と電気的に接続され、

前記第1のトランジスタの第2のゲートは、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第1のゲートは、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第2のトランジスタの第2のゲートは、前記第4の配線と電気的に接続されることを特徴とする半導体装置。 - 請求項1又は2において、

容量素子を有し、

前記容量素子の一方の電極は、前記第1のトランジスタの第2のゲート及び前記第2のトランジスタのソース又はドレインの一方と電気的に接続され

前記容量素子の他方の電極は、接地される、又は所定の信号が入力される機能を有することを特徴とする半導体装置。 - 請求項1乃至3のいずれか一において、

前記第1のトランジスタは、前記第2のトランジスタ上に重なる領域を有し、

前記第2のトランジスタの第1のゲートは、前記第1のトランジスタの第2のゲートと同じ材料を有することを特徴とする半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011060175 | 2011-03-18 | ||

| JP2011060175 | 2011-03-18 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012053954A Division JP5933897B2 (ja) | 2011-03-18 | 2012-03-12 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016192552A JP2016192552A (ja) | 2016-11-10 |

| JP6181232B2 true JP6181232B2 (ja) | 2017-08-16 |

Family

ID=46828335

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012053954A Expired - Fee Related JP5933897B2 (ja) | 2011-03-18 | 2012-03-12 | 半導体装置 |

| JP2016092888A Active JP6181232B2 (ja) | 2011-03-18 | 2016-05-05 | 半導体装置 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012053954A Expired - Fee Related JP5933897B2 (ja) | 2011-03-18 | 2012-03-12 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US8760959B2 (ja) |

| JP (2) | JP5933897B2 (ja) |

| KR (1) | KR102001677B1 (ja) |

| CN (2) | CN102693755B (ja) |

| TW (2) | TWI540683B (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6100559B2 (ja) | 2012-03-05 | 2017-03-22 | 株式会社半導体エネルギー研究所 | 半導体記憶装置 |

| WO2013146039A1 (ja) * | 2012-03-30 | 2013-10-03 | シャープ株式会社 | 半導体記憶装置 |

| TWI661553B (zh) | 2012-11-16 | 2019-06-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| US9318484B2 (en) * | 2013-02-20 | 2016-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US20140269046A1 (en) * | 2013-03-15 | 2014-09-18 | Micron Technology, Inc. | Apparatuses and methods for use in selecting or isolating memory cells |

| JP6272713B2 (ja) * | 2013-03-25 | 2018-01-31 | 株式会社半導体エネルギー研究所 | プログラマブルロジックデバイス及び半導体装置 |

| JP6486712B2 (ja) * | 2014-04-30 | 2019-03-20 | 株式会社半導体エネルギー研究所 | 酸化物半導体膜 |

| JP6616102B2 (ja) | 2014-05-23 | 2019-12-04 | 株式会社半導体エネルギー研究所 | 記憶装置及び電子機器 |

| KR20170068511A (ko) | 2014-10-06 | 2017-06-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| US9847406B2 (en) | 2015-08-27 | 2017-12-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, storage device, resistor circuit, display device, and electronic device |

| JP6811084B2 (ja) | 2015-12-18 | 2021-01-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2017115214A1 (en) | 2015-12-28 | 2017-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the semiconductor device |

| US10043858B2 (en) | 2016-04-27 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| US10475869B2 (en) | 2016-08-23 | 2019-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device including display element and transistor |

| CN114730807A (zh) | 2019-11-29 | 2022-07-08 | 株式会社半导体能源研究所 | 半导体装置、显示装置及电子设备 |

| US12387805B2 (en) | 2019-12-13 | 2025-08-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| US11699391B2 (en) | 2021-05-13 | 2023-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display apparatus, and electronic device |

Family Cites Families (180)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5159260A (en) | 1978-03-08 | 1992-10-27 | Hitachi, Ltd. | Reference voltage generator device |

| FR2524679B1 (fr) | 1982-04-01 | 1990-07-06 | Suwa Seikosha Kk | Procede d'attaque d'un panneau d'affichage a cristaux liquides a matrice active |

| JPS5919486A (ja) | 1982-07-22 | 1984-01-31 | Sony Corp | 画像表示装置 |

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0756542B2 (ja) | 1985-09-25 | 1995-06-14 | カシオ計算機株式会社 | 液晶駆動回路 |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH01128563A (ja) * | 1987-11-13 | 1989-05-22 | Nec Corp | 半導体記憶装置 |

| JPH01154394A (ja) * | 1987-12-10 | 1989-06-16 | Fujitsu Ltd | 記憶装置 |

| US4922240A (en) | 1987-12-29 | 1990-05-01 | North American Philips Corp. | Thin film active matrix and addressing circuitry therefor |

| JP2653099B2 (ja) | 1988-05-17 | 1997-09-10 | セイコーエプソン株式会社 | アクティブマトリクスパネル,投写型表示装置及びビューファインダー |

| DE69108062T2 (de) | 1990-01-17 | 1995-07-20 | Toshiba Kawasaki Kk | Flüssigkristall-Anzeigevorrichtung mit aktiver Matrix. |

| KR950001360B1 (ko) | 1990-11-26 | 1995-02-17 | 가부시키가이샤 한도오따이 에네루기 겐큐쇼 | 전기 광학장치와 그 구동방법 |

| JPH04191723A (ja) | 1990-11-27 | 1992-07-10 | Toshiba Corp | 液晶駆動装置 |

| JP2688548B2 (ja) | 1991-09-10 | 1997-12-10 | シャープ株式会社 | 液晶パネル駆動用半導体装置 |

| JP2997356B2 (ja) | 1991-12-13 | 2000-01-11 | 京セラ株式会社 | 液晶表示装置の駆動方法 |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3212352B2 (ja) | 1992-04-09 | 2001-09-25 | カシオ計算機株式会社 | 表示駆動装置 |

| JPH06180564A (ja) | 1992-05-14 | 1994-06-28 | Toshiba Corp | 液晶表示装置 |

| US5807772A (en) | 1992-06-09 | 1998-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming semiconductor device with bottom gate connected to source or drain |

| JP3254007B2 (ja) | 1992-06-09 | 2002-02-04 | 株式会社半導体エネルギー研究所 | 薄膜状半導体装置およびその作製方法 |

| JPH0799251A (ja) * | 1992-12-10 | 1995-04-11 | Sony Corp | 半導体メモリセル |

| DE69410682T2 (de) | 1993-03-30 | 1999-01-21 | Asahi Glass Co. Ltd., Tokio/Tokyo | Anzeigevorrichtung und Steuerverfahren für Anzeigevorrichtung |

| US5477073A (en) | 1993-08-20 | 1995-12-19 | Casio Computer Co., Ltd. | Thin film semiconductor device including a driver and a matrix circuit |

| US5574475A (en) | 1993-10-18 | 1996-11-12 | Crystal Semiconductor Corporation | Signal driver circuit for liquid crystal displays |

| JPH07131030A (ja) | 1993-11-05 | 1995-05-19 | Sony Corp | 表示用薄膜半導体装置及びその製造方法 |

| JPH07134572A (ja) | 1993-11-11 | 1995-05-23 | Nec Corp | アクティブマトリクス型液晶表示装置の駆動回路 |

| US7081938B1 (en) | 1993-12-03 | 2006-07-25 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JPH07176184A (ja) | 1993-12-20 | 1995-07-14 | Mitsubishi Electric Corp | 半導体記憶装置と、その半導体記憶装置におけるデータの書込および読出方法 |

| JP3442449B2 (ja) | 1993-12-25 | 2003-09-02 | 株式会社半導体エネルギー研究所 | 表示装置及びその駆動回路 |

| US5570105A (en) | 1993-12-25 | 1996-10-29 | Semiconductor Energy Laboratory Co., Ltd. | Driving circuit for driving liquid crystal display device |

| JP2734962B2 (ja) | 1993-12-27 | 1998-04-02 | 日本電気株式会社 | 薄膜トランジスタ及びその製造方法 |

| JPH07211084A (ja) * | 1994-01-18 | 1995-08-11 | Sunao Shibata | 半導体装置 |

| JP3253808B2 (ja) | 1994-07-07 | 2002-02-04 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| CN1109347C (zh) | 1994-10-19 | 2003-05-21 | 英特尔公司 | 快速存储器的电源 |

| JP3630489B2 (ja) | 1995-02-16 | 2005-03-16 | 株式会社東芝 | 液晶表示装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| US6396078B1 (en) | 1995-06-20 | 2002-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with a tapered hole formed using multiple layers with different etching rates |

| JP3286152B2 (ja) | 1995-06-29 | 2002-05-27 | シャープ株式会社 | 薄膜トランジスタ回路および画像表示装置 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| WO1997006565A1 (en) | 1995-08-04 | 1997-02-20 | Seiko Epson Corporation | Process for preparing thin-film transistor, process for preparing active matrix substrate, and liquid crystal display |

| JP3647523B2 (ja) | 1995-10-14 | 2005-05-11 | 株式会社半導体エネルギー研究所 | マトリクス型液晶表示装置 |

| JP3409542B2 (ja) | 1995-11-21 | 2003-05-26 | ソニー株式会社 | 半導体装置の製造方法 |

| US5814834A (en) | 1995-12-04 | 1998-09-29 | Semiconductor Energy Laboratory Co. | Thin film semiconductor device |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP3516424B2 (ja) | 1996-03-10 | 2004-04-05 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置 |

| JP3759999B2 (ja) | 1996-07-16 | 2006-03-29 | 株式会社半導体エネルギー研究所 | 半導体装置、液晶表示装置、el装置、tvカメラ表示装置、パーソナルコンピュータ、カーナビゲーションシステム、tvプロジェクション装置及びビデオカメラ |

| JP3424891B2 (ja) | 1996-12-27 | 2003-07-07 | 三洋電機株式会社 | 薄膜トランジスタの製造方法および表示装置 |

| JPH10229197A (ja) | 1997-02-17 | 1998-08-25 | Sanyo Electric Co Ltd | 薄膜トランジスタ、薄膜トランジスタの製造方法 |

| KR100506099B1 (ko) | 1997-02-24 | 2005-09-26 | 산요덴키가부시키가이샤 | 다결정실리콘막제조방법,박막트랜지스터제조방법,및어닐링장치 |

| US6010923A (en) | 1997-03-31 | 2000-01-04 | Sanyo Electric Co., Ltd. | Manufacturing method of semiconductor device utilizing annealed semiconductor layer as channel region |

| JP3376247B2 (ja) | 1997-05-30 | 2003-02-10 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタ及び薄膜トランジスタを用いた半導体装置 |

| JPH1128563A (ja) * | 1997-07-07 | 1999-02-02 | Matsushita Electric Ind Co Ltd | 半田付け方法 |

| JPH11126491A (ja) | 1997-08-20 | 1999-05-11 | Fujitsu Ltd | 半導体記憶装置 |

| US6197624B1 (en) | 1997-08-29 | 2001-03-06 | Semiconductor Energy Laboratory Co., Ltd. | Method of adjusting the threshold voltage in an SOI CMOS |

| JP3552500B2 (ja) | 1997-11-12 | 2004-08-11 | セイコーエプソン株式会社 | 論理振幅レベル変換回路,液晶装置及び電子機器 |

| US5917199A (en) | 1998-05-15 | 1999-06-29 | Ois Optical Imaging Systems, Inc. | Solid state imager including TFTS with variably doped contact layer system for reducing TFT leakage current and increasing mobility and method of making same |

| JP2001051292A (ja) | 1998-06-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体表示装置 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP4386978B2 (ja) | 1998-08-07 | 2009-12-16 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| US6512271B1 (en) | 1998-11-16 | 2003-01-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP4202502B2 (ja) | 1998-12-28 | 2008-12-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| EP1020839A3 (en) | 1999-01-08 | 2002-11-27 | Sel Semiconductor Energy Laboratory Co., Ltd. | Semiconductor display device and driving circuit therefor |

| JP2001093988A (ja) * | 1999-07-22 | 2001-04-06 | Sony Corp | 半導体記憶装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| US6282137B1 (en) * | 1999-09-14 | 2001-08-28 | Agere Systems Guardian Corp. | SRAM method and apparatus |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP2002198499A (ja) * | 2000-12-26 | 2002-07-12 | Toshiba Corp | 半導体記憶装置 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP2003078026A (ja) * | 2001-09-05 | 2003-03-14 | Yoshifumi Ando | ダブルゲートmosトランジスタ構造による高集積メモリ回路 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7189992B2 (en) | 2002-05-21 | 2007-03-13 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures having a transparent channel |

| US7339187B2 (en) * | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7286383B1 (en) * | 2002-08-10 | 2007-10-23 | National Semiconductor Corporation | Bit line sharing and word line load reduction for low AC power SRAM architecture |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4339103B2 (ja) | 2002-12-25 | 2009-10-07 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| KR20070116889A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 박막의 기상성막방법 |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| AU2005302964B2 (en) | 2004-11-10 | 2010-11-04 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101397571B1 (ko) | 2005-11-15 | 2014-05-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제조방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| EP1895545B1 (en) | 2006-08-31 | 2014-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP4932415B2 (ja) | 2006-09-29 | 2012-05-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| US7710765B2 (en) | 2007-09-27 | 2010-05-04 | Micron Technology, Inc. | Back gated SRAM cell |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP5121478B2 (ja) * | 2008-01-31 | 2013-01-16 | 株式会社ジャパンディスプレイウェスト | 光センサー素子、撮像装置、電子機器、およびメモリー素子 |

| JP2009259337A (ja) * | 2008-04-17 | 2009-11-05 | Hitachi Ltd | 半導体装置 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| US8106400B2 (en) | 2008-10-24 | 2012-01-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101310473B1 (ko) | 2008-10-24 | 2013-09-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| KR101432764B1 (ko) | 2008-11-13 | 2014-08-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치의 제조방법 |

| US8130534B2 (en) * | 2009-01-08 | 2012-03-06 | Qualcomm Incorporated | System and method to read and write data a magnetic tunnel junction element |

| JP2010267705A (ja) | 2009-05-13 | 2010-11-25 | Panasonic Corp | 半導体メモリセルおよびその製造方法 |

| JP5730529B2 (ja) | 2009-10-21 | 2015-06-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR101712340B1 (ko) | 2009-10-30 | 2017-03-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 구동 회로, 구동 회로를 포함하는 표시 장치, 및 표시 장치를 포함하는 전자 기기 |

| KR102006729B1 (ko) * | 2009-12-28 | 2019-08-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 기억 장치와 반도체 장치 |

| KR101820776B1 (ko) | 2010-02-19 | 2018-01-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US8415657B2 (en) * | 2010-02-19 | 2013-04-09 | Intermolecular, Inc. | Enhanced work function layer supporting growth of rutile phase titanium oxide |

| US8305798B2 (en) * | 2010-07-13 | 2012-11-06 | Texas Instruments Incorporated | Memory cell with equalization write assist in solid-state memory |

| KR101979758B1 (ko) | 2010-08-27 | 2019-05-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 기억 장치, 반도체 장치 |

| JP5993141B2 (ja) | 2010-12-28 | 2016-09-14 | 株式会社半導体エネルギー研究所 | 記憶装置 |

-

2012

- 2012-03-12 JP JP2012053954A patent/JP5933897B2/ja not_active Expired - Fee Related

- 2012-03-13 US US13/418,546 patent/US8760959B2/en not_active Expired - Fee Related

- 2012-03-14 TW TW101108624A patent/TWI540683B/zh not_active IP Right Cessation

- 2012-03-14 TW TW105111848A patent/TWI600141B/zh not_active IP Right Cessation

- 2012-03-16 CN CN201210082547.1A patent/CN102693755B/zh not_active Expired - Fee Related

- 2012-03-16 KR KR1020120027072A patent/KR102001677B1/ko not_active Expired - Fee Related

- 2012-03-16 CN CN201610671533.1A patent/CN106057802B/zh not_active Expired - Fee Related

-

2014

- 2014-06-06 US US14/297,668 patent/US9385128B2/en not_active Expired - Fee Related

-

2016

- 2016-05-05 JP JP2016092888A patent/JP6181232B2/ja active Active

- 2016-06-27 US US15/193,189 patent/US9627386B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8760959B2 (en) | 2014-06-24 |

| CN106057802B (zh) | 2020-03-17 |

| US9627386B2 (en) | 2017-04-18 |

| CN102693755B (zh) | 2016-09-07 |

| US20160307901A1 (en) | 2016-10-20 |

| KR20120106642A (ko) | 2012-09-26 |

| TW201304069A (zh) | 2013-01-16 |

| US20140284673A1 (en) | 2014-09-25 |

| TWI600141B (zh) | 2017-09-21 |

| CN106057802A (zh) | 2016-10-26 |

| US9385128B2 (en) | 2016-07-05 |

| TW201626545A (zh) | 2016-07-16 |

| KR102001677B1 (ko) | 2019-07-18 |

| JP2012212499A (ja) | 2012-11-01 |

| TWI540683B (zh) | 2016-07-01 |

| CN102693755A (zh) | 2012-09-26 |

| JP5933897B2 (ja) | 2016-06-15 |

| US20120236634A1 (en) | 2012-09-20 |

| JP2016192552A (ja) | 2016-11-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6181232B2 (ja) | 半導体装置 | |

| JP6628845B2 (ja) | 半導体装置 | |

| US20180219028A1 (en) | Semiconductor device | |

| CN102592669B (zh) | 半导体装置及半导体存储装置 | |

| JP2023071841A (ja) | 半導体装置 | |

| CN102612749B (zh) | 半导体器件 | |

| KR101293262B1 (ko) | 반도체 장치 | |

| CN102742002B (zh) | 半导体器件及其驱动方法 | |

| JP5681570B2 (ja) | 半導体装置 | |

| WO2011114867A1 (en) | Semiconductor device and driving method of semiconductor device | |

| WO2011152233A1 (en) | Semiconductor device | |

| TWI564889B (zh) | 半導體裝置及半導體儲存裝置 | |

| TWI512949B (zh) | 半導體裝置及半導體儲存裝置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170207 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170411 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170627 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170719 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6181232 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |