JP4339103B2 - 半導体装置及び表示装置 - Google Patents

半導体装置及び表示装置 Download PDFInfo

- Publication number

- JP4339103B2 JP4339103B2 JP2003421672A JP2003421672A JP4339103B2 JP 4339103 B2 JP4339103 B2 JP 4339103B2 JP 2003421672 A JP2003421672 A JP 2003421672A JP 2003421672 A JP2003421672 A JP 2003421672A JP 4339103 B2 JP4339103 B2 JP 4339103B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- drain

- source

- electrically connected

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 51

- 239000000758 substrate Substances 0.000 claims description 75

- 239000003990 capacitor Substances 0.000 claims description 41

- 239000013078 crystal Substances 0.000 claims description 16

- 238000007667 floating Methods 0.000 description 16

- 230000008859 change Effects 0.000 description 10

- 239000011521 glass Substances 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 238000000034 method Methods 0.000 description 7

- 238000005070 sampling Methods 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 230000007423 decrease Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 239000000463 material Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 230000000630 rising effect Effects 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/003—Details of a display terminal, the details relating to the control arrangement of the display terminal and to the interfaces thereto

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

- H03K19/0185—Coupling arrangements; Interface arrangements using field effect transistors only

- H03K19/018507—Interface arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0267—Details of drivers for scan electrodes, other than drivers for liquid crystal, plasma or OLED displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0275—Details of drivers for data electrodes, other than drivers for liquid crystal, plasma or OLED displays, not related to handling digital grey scale data or to communication of data to the pixels by means of a current

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0286—Details of a shift registers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0289—Details of voltage level shifters arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0291—Details of output amplifiers or buffers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

Description

整流性素子が、ダイオード接続されたトランジスタであることを特徴とする半導体装置が提供される。

第3のトランジスタと直列に第2の整流性素子が接続されていることを特徴とする半導体装置が提供される。

第2の整流性素子が、ダイオード接続されたトランジスタであることを特徴とする半導体装置が提供される。

ダイオード接続されたトランジスタと、第1のトランジスタとが、同じ導電型を有することを特徴とする半導体装置が提供される。

第2の整流性素子であるダイオード接続されたトランジスタと、第1のトランジスタとが、同じ導電型を有することを特徴とする半導体装置が提供される。

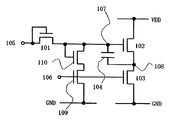

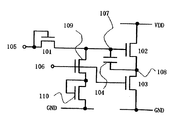

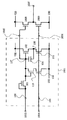

本実施の形態では、まず、発明が解決しようとする課題において説明した、2つ目の問題に対処したインバータ回路について説明する。つまり、入力端子に入力されるH信号の電位が、高電位側電源VDDよりも低い場合、ある端子の電位が、十分に上昇しない、という問題に対処したインバータ回路について、説明する。

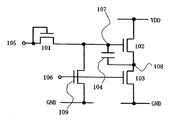

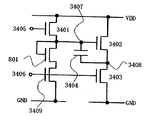

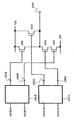

実施の形態1では、発明が解決しようとする課題において説明した、2つ目の問題に対処したインバータ回路について説明した。本実施の形態では、発明が解決しようとする課題において説明した、1つ目の問題に対処したインバータ回路について説明する。

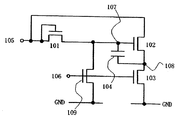

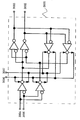

本実施の形態では、実施の形態1で説明した回路を改良することにより、発明が解決しようとする課題において説明した1つ目の問題と2つ目の問題に対処したインバータ回路について説明した。本実施の形態では、図34の回路を改良することにより、1つ目の問題に対処したインバータ回路について説明する。

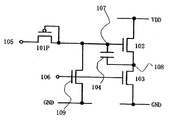

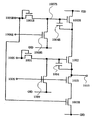

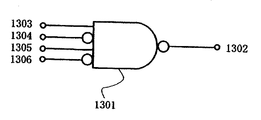

実施の形態1〜3においては、インバータ回路に適用した場合について述べてきた。次に、本実施の形態では、それ以外の回路に適用した場合の例を示す。

実施の形態1において、図2のインバータ回路では、出力端子は、端子108だけでなく、端子107を用いてもよいことは、説明した。そこで、本実施の形態では、出力端子107の出力を利用して、さまざまな回路を構成する例について説明する。つまり、端子108から信号を出力するインバータ回路を、レベル補正回路として動作させ、さまざまな回路を動作させる場合の例を示す。

出力されるサンプリングパルスが入力される。また、DFF回路などを用いて第2ラッチ回路(LAT2)2805を構成する場合は、端子2906、2907(または端子3006、3007)に相当する部分には、ラッチ制御線2809よりラッチパルス(Latch Pulse)が入力される。

Claims (18)

- 第1乃至第4のトランジスタを有し、

前記第1乃至第4のトランジスタは、Nチャネル型であり、

前記第1乃至第4のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続されていることを特徴とする半導体装置。 - 第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続されていることを特徴とする半導体装置。 - 第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、第2の出力端と電気的に接続されていることを特徴とする半導体装置。 - 第1乃至第6のトランジスタを有し、

前記第1乃至第6のトランジスタは、Nチャネル型であり、

前記第1乃至第6のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は第2の出力端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続されていることを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか一において、

容量素子を有し、

前記容量の一方の端子は、前記第3のトランジスタのゲートと電気的に接続され、前記容量の他方の端子は前記第3のトランジスタのソース又はドレインの他方と電気的に接続されていることを特徴とする半導体装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第4のトランジスタを有し、

前記第1乃至第4のトランジスタは、Nチャネル型であり、

前記第1乃至第4のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、第2の出力端と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第6のトランジスタを有し、

前記第1乃至第6のトランジスタは、Nチャネル型であり、

前記第1乃至第6のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は第2の出力端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第4のトランジスタを有し、

前記第1乃至第4のトランジスタは、Nチャネル型であり、

前記第1乃至第4のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、COGにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、COGにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、第2の出力端と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、COGにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第6のトランジスタを有し、

前記第1乃至第6のトランジスタは、Nチャネル型であり、

前記第1乃至第6のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は第2の出力端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、COGにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第4のトランジスタを有し、

前記第1乃至第4のトランジスタは、Nチャネル型であり、

前記第1乃至第4のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、TABにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、TABにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は第1乃至第5のトランジスタを有し、

前記第1乃至第5のトランジスタは、Nチャネル型であり、

前記第1乃至第5のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、第2の出力端と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、TABにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 絶縁基板上に設けられた画素部と、

前記絶縁基板上に設けられたゲート線駆動回路と、

信号線駆動回路とを有し、

前記画素部と前記ゲート線駆動回路は電気的に接続され、

前記画素部と前記信号線駆動回路は電気的に接続され、

前記ゲート線駆動回路は、第1乃至第6のトランジスタを有し、

前記第1乃至第6のトランジスタは、Nチャネル型であり、

前記第1乃至第6のトランジスタは、非晶質半導体を有し、

前記第1のトランジスタのソース又はドレインの一方には、第1の信号が入力され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートには、第2の信号が入力され、

前記第2のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第3のトランジスタのゲートは、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、第2の配線と電気的に接続され、前記第3のトランジスタのソース又はドレインの他方は、前記第4のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は第1の出力端子と電気的に接続され、

前記第4のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記第5のトランジスタのゲートは、前記第3のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第2の配線と電気的に接続され、前記第5のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は第2の出力端子と電気的に接続され、

前記第6のトランジスタのゲートは、前記第2のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記信号線駆動回路の少なくとも一部は、単結晶基板又はSOI基板を有するICチップに設けられ、

前記ICチップは、TABにより前記絶縁基板に実装されていることを特徴とする表示装置。 - 請求項6乃至請求項17のいずれか一において、

前記ゲート線駆動回路は容量素子を有し、

前記容量素子の一方の端子は、前記第3のトランジスタのゲートと電気的に接続され、前記容量素子の他方の端子は前記第3のトランジスタのソース又はドレインの他方と電気的に接続されていることを特徴とする表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003421672A JP4339103B2 (ja) | 2002-12-25 | 2003-12-18 | 半導体装置及び表示装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002374098 | 2002-12-25 | ||

| JP2003421672A JP4339103B2 (ja) | 2002-12-25 | 2003-12-18 | 半導体装置及び表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008271481A Division JP4574708B2 (ja) | 2002-12-25 | 2008-10-22 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004222256A JP2004222256A (ja) | 2004-08-05 |

| JP2004222256A5 JP2004222256A5 (ja) | 2007-02-08 |

| JP4339103B2 true JP4339103B2 (ja) | 2009-10-07 |

Family

ID=33495989

Family Applications (16)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003421672A Expired - Fee Related JP4339103B2 (ja) | 2002-12-25 | 2003-12-18 | 半導体装置及び表示装置 |

| JP2008271481A Expired - Lifetime JP4574708B2 (ja) | 2002-12-25 | 2008-10-22 | 表示装置 |

| JP2009160077A Expired - Fee Related JP5042279B2 (ja) | 2002-12-25 | 2009-07-06 | 半導体装置、表示装置、及び電子機器 |

| JP2010129156A Expired - Fee Related JP5211110B2 (ja) | 2002-12-25 | 2010-06-04 | 表示装置 |

| JP2012125687A Expired - Lifetime JP5393843B2 (ja) | 2002-12-25 | 2012-06-01 | 半導体装置、表示装置及び電子機器 |

| JP2013181981A Expired - Lifetime JP5619240B2 (ja) | 2002-12-25 | 2013-09-03 | 半導体装置、表示装置、及び電子機器 |

| JP2013181983A Expired - Lifetime JP5640126B2 (ja) | 2002-12-25 | 2013-09-03 | 半導体装置、表示装置及び電子機器 |

| JP2014104863A Expired - Lifetime JP5777769B2 (ja) | 2002-12-25 | 2014-05-21 | 半導体装置、表示装置及び電子機器 |

| JP2015094503A Expired - Lifetime JP5947952B2 (ja) | 2002-12-25 | 2015-05-05 | 半導体装置、表示装置及び電子機器 |

| JP2015235376A Expired - Lifetime JP6010679B2 (ja) | 2002-12-25 | 2015-12-02 | デジタル回路、半導体装置及び電子機器 |

| JP2016032690A Withdrawn JP2016146637A (ja) | 2002-12-25 | 2016-02-24 | 半導体装置 |

| JP2017031986A Withdrawn JP2017143523A (ja) | 2002-12-25 | 2017-02-23 | デジタル回路、半導体装置及び電子機器 |

| JP2017120180A Withdrawn JP2017200217A (ja) | 2002-12-25 | 2017-06-20 | 半導体装置及び表示装置 |

| JP2017131626A Withdrawn JP2017229074A (ja) | 2002-12-25 | 2017-07-05 | シフトレジスタ、半導体装置及び表示装置 |

| JP2017177475A Withdrawn JP2018029345A (ja) | 2002-12-25 | 2017-09-15 | 半導体装置 |

| JP2019153868A Pending JP2019216464A (ja) | 2002-12-25 | 2019-08-26 | 半導体装置 |

Family Applications After (15)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008271481A Expired - Lifetime JP4574708B2 (ja) | 2002-12-25 | 2008-10-22 | 表示装置 |

| JP2009160077A Expired - Fee Related JP5042279B2 (ja) | 2002-12-25 | 2009-07-06 | 半導体装置、表示装置、及び電子機器 |

| JP2010129156A Expired - Fee Related JP5211110B2 (ja) | 2002-12-25 | 2010-06-04 | 表示装置 |

| JP2012125687A Expired - Lifetime JP5393843B2 (ja) | 2002-12-25 | 2012-06-01 | 半導体装置、表示装置及び電子機器 |

| JP2013181981A Expired - Lifetime JP5619240B2 (ja) | 2002-12-25 | 2013-09-03 | 半導体装置、表示装置、及び電子機器 |

| JP2013181983A Expired - Lifetime JP5640126B2 (ja) | 2002-12-25 | 2013-09-03 | 半導体装置、表示装置及び電子機器 |

| JP2014104863A Expired - Lifetime JP5777769B2 (ja) | 2002-12-25 | 2014-05-21 | 半導体装置、表示装置及び電子機器 |

| JP2015094503A Expired - Lifetime JP5947952B2 (ja) | 2002-12-25 | 2015-05-05 | 半導体装置、表示装置及び電子機器 |

| JP2015235376A Expired - Lifetime JP6010679B2 (ja) | 2002-12-25 | 2015-12-02 | デジタル回路、半導体装置及び電子機器 |

| JP2016032690A Withdrawn JP2016146637A (ja) | 2002-12-25 | 2016-02-24 | 半導体装置 |

| JP2017031986A Withdrawn JP2017143523A (ja) | 2002-12-25 | 2017-02-23 | デジタル回路、半導体装置及び電子機器 |

| JP2017120180A Withdrawn JP2017200217A (ja) | 2002-12-25 | 2017-06-20 | 半導体装置及び表示装置 |

| JP2017131626A Withdrawn JP2017229074A (ja) | 2002-12-25 | 2017-07-05 | シフトレジスタ、半導体装置及び表示装置 |

| JP2017177475A Withdrawn JP2018029345A (ja) | 2002-12-25 | 2017-09-15 | 半導体装置 |

| JP2019153868A Pending JP2019216464A (ja) | 2002-12-25 | 2019-08-26 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (14) | US7202863B2 (ja) |

| JP (16) | JP4339103B2 (ja) |

| KR (4) | KR101019135B1 (ja) |

| CN (2) | CN101149893B (ja) |

| TW (1) | TWI307165B (ja) |

Families Citing this family (85)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100734081B1 (ko) * | 2001-06-28 | 2007-07-02 | 주식회사 하이닉스반도체 | 반도체 소자의 트랜치 형성방법 |

| JP4339103B2 (ja) | 2002-12-25 | 2009-10-07 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| JP4866623B2 (ja) * | 2005-06-03 | 2012-02-01 | 株式会社 日立ディスプレイズ | 表示装置及びその制御方法 |

| JP5291874B2 (ja) * | 2005-10-18 | 2013-09-18 | 株式会社半導体エネルギー研究所 | 半導体装置、シフトレジスタ、表示装置 |

| US9153341B2 (en) | 2005-10-18 | 2015-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Shift register, semiconductor device, display device, and electronic device |

| US7432737B2 (en) * | 2005-12-28 | 2008-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| JP5291877B2 (ja) * | 2005-12-28 | 2013-09-18 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR101437086B1 (ko) | 2006-01-07 | 2014-09-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치와, 이 반도체장치를 구비한 표시장치 및 전자기기 |

| TWI354976B (en) * | 2006-04-19 | 2011-12-21 | Au Optronics Corp | Voltage level shifter |

| US8330492B2 (en) | 2006-06-02 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device |

| EP1895545B1 (en) * | 2006-08-31 | 2014-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| GB2446842A (en) * | 2007-02-20 | 2008-08-27 | Seiko Epson Corp | Organic TFT Inverter Arrangement |

| JP5057828B2 (ja) * | 2007-04-16 | 2012-10-24 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| US8013633B2 (en) * | 2007-06-20 | 2011-09-06 | Hewlett-Packard Development Company, L.P. | Thin film transistor logic |

| JP2009077208A (ja) * | 2007-09-21 | 2009-04-09 | Sony Corp | 電圧レベルシフト機能を有するインタフェース回路、半導体集積回路、表示装置 |

| CN101878592B (zh) | 2007-12-28 | 2012-11-07 | 夏普株式会社 | 半导体装置和显示装置 |

| CN103036548B (zh) * | 2007-12-28 | 2016-01-06 | 夏普株式会社 | 半导体装置和显示装置 |

| WO2009084280A1 (ja) | 2007-12-28 | 2009-07-09 | Sharp Kabushiki Kaisha | 表示駆動回路、表示装置及び表示駆動方法 |

| RU2438194C1 (ru) | 2007-12-28 | 2011-12-27 | Шарп Кабусики Кайся | Схема управления линии запоминающего конденсатора и устройство отображения |

| US8314765B2 (en) | 2008-06-17 | 2012-11-20 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, display device, and electronic device |

| KR101539667B1 (ko) * | 2008-06-18 | 2015-07-28 | 삼성전자주식회사 | 인버터 소자 및 그 동작 방법 |

| JP5736114B2 (ja) | 2009-02-27 | 2015-06-17 | 株式会社半導体エネルギー研究所 | 半導体装置の駆動方法、電子機器の駆動方法 |

| US8872751B2 (en) | 2009-03-26 | 2014-10-28 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device having interconnected transistors and electronic device including the same |

| EP2234100B1 (en) | 2009-03-26 | 2016-11-02 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| EP2264899B1 (en) * | 2009-06-17 | 2014-07-30 | Epcos AG | Low-current logic-gate circuit |

| EP2264900B1 (en) * | 2009-06-17 | 2014-07-30 | Epcos AG | Low-current inverter circuit |

| JP5398831B2 (ja) | 2009-06-25 | 2014-01-29 | シャープ株式会社 | シフトレジスタおよびそれを備えた表示装置、ならびにシフトレジスタの駆動方法 |

| TWI783356B (zh) | 2009-09-10 | 2022-11-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置和顯示裝置 |

| WO2011033909A1 (en) * | 2009-09-16 | 2011-03-24 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, display device including the driver circuit, and electronic device including the display device |

| WO2011043194A1 (en) | 2009-10-09 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR102005736B1 (ko) | 2009-10-16 | 2019-07-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| KR101712340B1 (ko) * | 2009-10-30 | 2017-03-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 구동 회로, 구동 회로를 포함하는 표시 장치, 및 표시 장치를 포함하는 전자 기기 |

| WO2011070929A1 (en) | 2009-12-11 | 2011-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| KR101913111B1 (ko) * | 2009-12-18 | 2018-10-31 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| WO2011105180A1 (en) | 2010-02-23 | 2011-09-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device, semiconductor device, and driving method thereof |

| JP5678730B2 (ja) * | 2010-03-30 | 2015-03-04 | ソニー株式会社 | インバータ回路および表示装置 |

| KR101674690B1 (ko) * | 2010-03-30 | 2016-11-09 | 가부시키가이샤 제이올레드 | 인버터 회로 및 표시 장치 |

| JP5488817B2 (ja) * | 2010-04-01 | 2014-05-14 | ソニー株式会社 | インバータ回路および表示装置 |

| JP5581263B2 (ja) | 2010-05-13 | 2014-08-27 | 株式会社半導体エネルギー研究所 | バッファ回路 |

| JP5846789B2 (ja) * | 2010-07-29 | 2016-01-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2012017843A1 (en) | 2010-08-06 | 2012-02-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor integrated circuit |

| TWI411232B (zh) * | 2010-12-10 | 2013-10-01 | Au Optronics Corp | 移位暫存器電路 |

| US8928647B2 (en) * | 2011-03-04 | 2015-01-06 | Sony Corporation | Inverter circuit and display unit |

| JP5589904B2 (ja) * | 2011-03-04 | 2014-09-17 | ソニー株式会社 | インバータ回路および表示装置 |

| JP5933897B2 (ja) | 2011-03-18 | 2016-06-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI568181B (zh) * | 2011-05-06 | 2017-01-21 | 半導體能源研究所股份有限公司 | 邏輯電路及半導體裝置 |

| US9466618B2 (en) | 2011-05-13 | 2016-10-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including two thin film transistors and method of manufacturing the same |

| JP2012243971A (ja) * | 2011-05-20 | 2012-12-10 | Sony Corp | ブートストラップ回路、インバータ回路、走査回路、表示装置、及び、電子機器 |

| JP2013084333A (ja) | 2011-09-28 | 2013-05-09 | Semiconductor Energy Lab Co Ltd | シフトレジスタ回路 |

| US8736315B2 (en) * | 2011-09-30 | 2014-05-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2013130802A (ja) | 2011-12-22 | 2013-07-04 | Semiconductor Energy Lab Co Ltd | 半導体装置、画像表示装置、記憶装置、及び電子機器 |

| US8994439B2 (en) | 2012-04-19 | 2015-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, image display device, storage device, and electronic device |

| US9742378B2 (en) | 2012-06-29 | 2017-08-22 | Semiconductor Energy Laboratory Co., Ltd. | Pulse output circuit and semiconductor device |

| JP6239292B2 (ja) | 2012-07-20 | 2017-11-29 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI600022B (zh) * | 2012-07-20 | 2017-09-21 | 半導體能源研究所股份有限公司 | 脈衝輸出電路、顯示裝置、及電子裝置 |

| US8952723B2 (en) * | 2013-02-13 | 2015-02-10 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device and semiconductor device |

| US9318484B2 (en) * | 2013-02-20 | 2016-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9368625B2 (en) | 2013-05-01 | 2016-06-14 | Zeno Semiconductor, Inc. | NAND string utilizing floating body memory cell |

| JP6475424B2 (ja) | 2013-06-05 | 2019-02-27 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9214475B2 (en) * | 2013-07-09 | 2015-12-15 | Pixtronix, Inc. | All N-type transistor inverter circuit |

| JP6245422B2 (ja) * | 2013-07-24 | 2017-12-13 | Tianma Japan株式会社 | 走査回路、及び表示装置 |

| US9537478B2 (en) * | 2014-03-06 | 2017-01-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9450581B2 (en) | 2014-09-30 | 2016-09-20 | Semiconductor Energy Laboratory Co., Ltd. | Logic circuit, semiconductor device, electronic component, and electronic device |

| US10068927B2 (en) * | 2014-10-23 | 2018-09-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display module, and electronic device |

| WO2016079639A1 (ja) * | 2014-11-20 | 2016-05-26 | 株式会社半導体エネルギー研究所 | 半導体装置、回路基板および電子機器 |

| CN104599620B (zh) * | 2014-12-10 | 2017-09-26 | 华南理工大学 | 栅极集成驱动电路的反相器、栅极集成驱动器及驱动方法 |

| CN104883181B (zh) * | 2015-06-10 | 2018-03-16 | 京东方科技集团股份有限公司 | 或非门电路、移位寄存器、阵列基板及显示装置 |

| JP2017068032A (ja) * | 2015-09-30 | 2017-04-06 | ソニー株式会社 | 表示素子の駆動方法、表示装置、及び、電子機器 |

| US10297331B2 (en) | 2015-10-30 | 2019-05-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| US10033361B2 (en) * | 2015-12-28 | 2018-07-24 | Semiconductor Energy Laboratory Co., Ltd. | Level-shift circuit, driver IC, and electronic device |

| CN105529000B (zh) * | 2016-02-18 | 2018-01-23 | 京东方科技集团股份有限公司 | 信号生成单元、移位寄存器、显示装置及信号生成方法 |

| CN205621414U (zh) * | 2016-04-26 | 2016-10-05 | 京东方科技集团股份有限公司 | 静电放电电路、阵列基板和显示装置 |

| JP2018093483A (ja) | 2016-11-29 | 2018-06-14 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置及び電子機器 |

| US10153368B2 (en) * | 2017-03-01 | 2018-12-11 | Samsung Electronics Co., Ltd. | Unipolar complementary logic |

| CN106847220B (zh) * | 2017-03-15 | 2019-03-22 | 厦门天马微电子有限公司 | 移位寄存器、触控显示面板及其驱动方法、触控显示装置 |

| JP6730213B2 (ja) * | 2017-03-15 | 2020-07-29 | ラピスセミコンダクタ株式会社 | 半導体回路及び半導体装置 |

| JP7001442B2 (ja) * | 2017-11-28 | 2022-01-19 | ラピスセミコンダクタ株式会社 | 入出力回路 |

| US11626875B2 (en) * | 2018-04-20 | 2023-04-11 | Texas Instruments Incorporated | Stress reduction on stacked transistor circuits |

| US11831309B2 (en) * | 2018-04-20 | 2023-11-28 | Texas Instruments Incorporated | Stress reduction on stacked transistor circuits |

| CN109655877B (zh) * | 2019-01-04 | 2020-12-01 | 京东方科技集团股份有限公司 | 平板探测器的像素结构、平板探测器及摄像系统 |

| CN110223655A (zh) * | 2019-06-28 | 2019-09-10 | 昆山龙腾光电有限公司 | 栅极驱动电路及显示装置 |

| WO2021105828A1 (ja) * | 2019-11-29 | 2021-06-03 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、及び電子機器 |

| US11699391B2 (en) | 2021-05-13 | 2023-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display apparatus, and electronic device |

| CN113380172B (zh) * | 2021-06-07 | 2022-12-06 | 中国科学院微电子研究所 | 一种栅极驱动电路、驱动方法及goa电路 |

| CN117176138A (zh) * | 2022-05-27 | 2023-12-05 | 华为技术有限公司 | 逻辑门电路、集成电路及电子设备 |

Family Cites Families (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3506851A (en) | 1966-12-14 | 1970-04-14 | North American Rockwell | Field effect transistor driver using capacitor feedback |

| US3774055A (en) | 1972-01-24 | 1973-11-20 | Nat Semiconductor Corp | Clocked bootstrap inverter circuit |

| US3898479A (en) | 1973-03-01 | 1975-08-05 | Mostek Corp | Low power, high speed, high output voltage fet delay-inverter stage |

| JPS52119160A (en) | 1976-03-31 | 1977-10-06 | Nec Corp | Semiconductor circuit with insulating gate type field dffect transisto r |

| US4275313A (en) | 1979-04-09 | 1981-06-23 | Bell Telephone Laboratories, Incorporated | Current limiting output circuit with output feedback |

| JPS55156427U (ja) | 1979-04-27 | 1980-11-11 | ||

| JPS55156427A (en) | 1979-05-23 | 1980-12-05 | Sharp Corp | Bootstrap buffer circuit |

| JPS5694838A (en) | 1979-12-27 | 1981-07-31 | Toshiba Corp | Driving circuit |

| DE3026951A1 (de) | 1980-07-16 | 1982-02-04 | Siemens AG, 1000 Berlin und 8000 München | Treiberstufe in integrierter mos-schaltkreistechnik mit grossem ausgangssignalverhaeltnis |

| JPS58151719A (ja) | 1982-03-05 | 1983-09-09 | Sony Corp | パルス発生回路 |

| JPS5916424A (ja) | 1982-07-19 | 1984-01-27 | Toshiba Corp | 半導体回路 |

| JPS5916424U (ja) | 1982-07-23 | 1984-01-31 | 竹内 洋司 | 歯ブラシ |

| JPS6030217A (ja) * | 1983-07-28 | 1985-02-15 | Toshiba Corp | 半導体回路 |

| JPS60140924A (ja) | 1983-12-27 | 1985-07-25 | Nec Corp | 半導体回路 |

| JPS6298915A (ja) | 1985-10-25 | 1987-05-08 | Toshiba Corp | 高電位保持回路 |

| JPS63204815A (ja) | 1987-02-20 | 1988-08-24 | Hitachi Ltd | 半導体論理回路 |

| JPS6439118A (en) * | 1987-08-04 | 1989-02-09 | Nec Corp | Gaas semiconductor integrated circuit |

| US4804870A (en) | 1987-08-07 | 1989-02-14 | Signetics Corporation | Non-inverting, low power, high speed bootstrapped buffer |

| US4959697A (en) | 1988-07-20 | 1990-09-25 | Vtc Incorporated | Short channel junction field effect transistor |

| FR2651276B1 (fr) | 1989-08-28 | 1991-10-25 | Alsthom Gec | Condenseur en beton pour turbine a echappement axial et turbine munie d'un tel condenseur. |

| JPH03165171A (ja) | 1989-11-24 | 1991-07-17 | Ricoh Co Ltd | 密着型イメージセンサー |

| US5170155A (en) * | 1990-10-19 | 1992-12-08 | Thomson S.A. | System for applying brightness signals to a display device and comparator therefore |

| US7115902B1 (en) * | 1990-11-20 | 2006-10-03 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JPH04192920A (ja) * | 1990-11-27 | 1992-07-13 | Hitachi Ltd | Cmos論理出力回路 |

| JP3165171B2 (ja) | 1991-04-24 | 2001-05-14 | 電気化学工業株式会社 | キャスタブル組成物 |

| JPH0548420A (ja) * | 1991-08-08 | 1993-02-26 | Fujitsu Ltd | 出力回路 |

| JPH05182469A (ja) * | 1991-12-27 | 1993-07-23 | Mitsubishi Electric Corp | 半導体集積回路 |

| JPH05243946A (ja) * | 1992-02-28 | 1993-09-21 | G T C:Kk | インバータ回路 |

| JP2999328B2 (ja) | 1992-04-28 | 2000-01-17 | シャープ株式会社 | アクティブマトリクス基板 |

| JPH0698081A (ja) | 1992-09-14 | 1994-04-08 | Hitachi Ltd | 固体撮像素子 |

| KR960008735B1 (en) | 1993-04-29 | 1996-06-29 | Samsung Electronics Co Ltd | Mos transistor and the manufacturing method thereof |

| JPH06350433A (ja) * | 1993-06-11 | 1994-12-22 | Matsushita Electric Ind Co Ltd | Bi−CMOS出力回路 |

| TW264575B (ja) | 1993-10-29 | 1995-12-01 | Handotai Energy Kenkyusho Kk | |

| US5467038A (en) | 1994-02-15 | 1995-11-14 | Hewlett-Packard Company | Quick resolving latch |

| JP3402400B2 (ja) | 1994-04-22 | 2003-05-06 | 株式会社半導体エネルギー研究所 | 半導体集積回路の作製方法 |

| US5604704A (en) | 1994-05-30 | 1997-02-18 | Nec Corporation | Compound semiconductor static random access memory device equipped with precharging circuit controlled by boosted signal |

| JPH0850790A (ja) | 1994-05-30 | 1996-02-20 | Nec Corp | 半導体メモリ |

| US5434899A (en) | 1994-08-12 | 1995-07-18 | Thomson Consumer Electronics, S.A. | Phase clocked shift register with cross connecting between stages |

| JP3330746B2 (ja) | 1994-09-09 | 2002-09-30 | 新日本製鐵株式会社 | ブートストラップ回路 |

| JP3092506B2 (ja) | 1995-03-27 | 2000-09-25 | カシオ計算機株式会社 | 半導体装置およびこれを用いた表示駆動装置 |

| US5694061A (en) | 1995-03-27 | 1997-12-02 | Casio Computer Co., Ltd. | Semiconductor device having same conductive type MIS transistors, a simple circuit design, and a high productivity |

| JPH0933887A (ja) | 1995-07-18 | 1997-02-07 | Hitachi Ltd | 液晶表示装置 |

| JP3272209B2 (ja) * | 1995-09-07 | 2002-04-08 | アルプス電気株式会社 | Lcd駆動回路 |

| JP3436629B2 (ja) | 1996-01-08 | 2003-08-11 | シャープ株式会社 | 表示および撮像のための装置 |

| FR2743662B1 (fr) | 1996-01-11 | 1998-02-13 | Thomson Lcd | Perfectionnement aux registres a decalage utilisant des transistors mis de meme polarite |

| US5949398A (en) | 1996-04-12 | 1999-09-07 | Thomson Multimedia S.A. | Select line driver for a display matrix with toggling backplane |

| JP2921510B2 (ja) | 1996-10-07 | 1999-07-19 | 日本電気株式会社 | ブートストラップ回路 |

| TW451284B (en) * | 1996-10-15 | 2001-08-21 | Semiconductor Energy Lab | Semiconductor device and method of manufacturing the same |

| US5952991A (en) | 1996-11-14 | 1999-09-14 | Kabushiki Kaisha Toshiba | Liquid crystal display |

| KR100218506B1 (ko) | 1996-12-14 | 1999-09-01 | 윤종용 | 액정 표시 장치용 레벨 시프트 회로 |

| KR100235590B1 (ko) | 1997-01-08 | 1999-12-15 | 구본준 | 박막트랜지스터 액정표시장치의 구동방법 |

| JP3881079B2 (ja) * | 1997-03-14 | 2007-02-14 | 株式会社アドバンテスト | 半導体集積回路素子 |

| JP4090512B2 (ja) * | 1997-04-08 | 2008-05-28 | 日本オプネクスト株式会社 | 光モジュール |

| JPH10301087A (ja) | 1997-04-24 | 1998-11-13 | Hitachi Ltd | 液晶表示装置 |

| EP0887931A1 (en) * | 1997-06-24 | 1998-12-30 | STMicroelectronics S.r.l. | Protection circuit for controlling the gate voltage of a high voltage LDMOS transistor |

| JPH1186586A (ja) * | 1997-09-03 | 1999-03-30 | Furontetsuku:Kk | シフトレジスタ装置および表示装置 |

| US6229508B1 (en) * | 1997-09-29 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| US7196699B1 (en) | 1998-04-28 | 2007-03-27 | Sharp Kabushiki Kaisha | Latch circuit, shift register circuit, logical circuit and image display device operated with a low consumption of power |

| US6087853A (en) * | 1998-06-22 | 2000-07-11 | Lucent Technologies, Inc. | Controlled output impedance buffer using CMOS technology |

| JP3412131B2 (ja) * | 1998-06-23 | 2003-06-03 | 株式会社日立製作所 | 液晶表示装置 |

| JP3622516B2 (ja) | 1998-07-10 | 2005-02-23 | カシオ計算機株式会社 | 液晶駆動装置 |

| JP2000106617A (ja) | 1998-09-29 | 2000-04-11 | Canon Inc | 読取装置および読取システム |

| JP2000112444A (ja) | 1998-10-08 | 2000-04-21 | Casio Comput Co Ltd | 液晶駆動装置 |

| KR100281336B1 (ko) | 1998-10-21 | 2001-03-02 | 구본준 | 쉬프트 레지스터 회로 |

| GB2343068B (en) * | 1998-10-21 | 2000-12-13 | Lg Philips Lcd Co Ltd | Shift register |

| KR100438525B1 (ko) | 1999-02-09 | 2004-07-03 | 엘지.필립스 엘시디 주식회사 | 쉬프트 레지스터 회로 |

| US6384804B1 (en) | 1998-11-25 | 2002-05-07 | Lucent Techonologies Inc. | Display comprising organic smart pixels |

| US6501098B2 (en) | 1998-11-25 | 2002-12-31 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device |

| JP3609977B2 (ja) | 1999-07-15 | 2005-01-12 | シャープ株式会社 | レベルシフト回路および画像表示装置 |

| JP4627822B2 (ja) | 1999-06-23 | 2011-02-09 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP4651785B2 (ja) | 1999-07-23 | 2011-03-16 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2003509728A (ja) | 1999-09-11 | 2003-03-11 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | アクティブマトリックスelディスプレイ装置 |

| JP4359368B2 (ja) | 1999-10-29 | 2009-11-04 | 日本特殊陶業株式会社 | ガスセンサ |

| JP2001134238A (ja) * | 1999-11-05 | 2001-05-18 | Toshiba Corp | 表示装置 |

| TW587239B (en) | 1999-11-30 | 2004-05-11 | Semiconductor Energy Lab | Electric device |

| JP3734664B2 (ja) * | 2000-02-24 | 2006-01-11 | 株式会社日立製作所 | 表示デバイス |

| JP4416901B2 (ja) * | 2000-03-14 | 2010-02-17 | 株式会社半導体エネルギー研究所 | レベルシフタ |

| TW577241B (en) | 2000-03-28 | 2004-02-21 | Sanyo Electric Co | Display device |

| JP2001325798A (ja) * | 2000-05-16 | 2001-11-22 | Sony Corp | 論理回路およびこれを用いた表示装置 |

| US7339317B2 (en) | 2000-06-05 | 2008-03-04 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device having triplet and singlet compound in light-emitting layers |

| JP2001075542A (ja) * | 2000-07-10 | 2001-03-23 | Semiconductor Energy Lab Co Ltd | 補正システムおよびその動作方法 |

| JP2002176162A (ja) | 2000-08-10 | 2002-06-21 | Semiconductor Energy Lab Co Ltd | エリアセンサ及びエリアセンサを備えた表示装置 |

| US7030551B2 (en) | 2000-08-10 | 2006-04-18 | Semiconductor Energy Laboratory Co., Ltd. | Area sensor and display apparatus provided with an area sensor |

| JP4954404B2 (ja) | 2000-09-14 | 2012-06-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2002133890A (ja) | 2000-10-24 | 2002-05-10 | Alps Electric Co Ltd | シフトレジスタ |

| US7015882B2 (en) * | 2000-11-07 | 2006-03-21 | Sony Corporation | Active matrix display and active matrix organic electroluminescence display |

| TW546615B (en) | 2000-11-22 | 2003-08-11 | Hitachi Ltd | Display device having an improved voltage level converter circuit |

| JP4501048B2 (ja) * | 2000-12-28 | 2010-07-14 | カシオ計算機株式会社 | シフトレジスタ回路及びその駆動制御方法並びに表示駆動装置、読取駆動装置 |

| TW525139B (en) | 2001-02-13 | 2003-03-21 | Samsung Electronics Co Ltd | Shift register, liquid crystal display using the same and method for driving gate line and data line blocks thereof |

| KR100752602B1 (ko) | 2001-02-13 | 2007-08-29 | 삼성전자주식회사 | 쉬프트 레지스터와, 이를 이용한 액정 표시 장치 |

| US6753654B2 (en) * | 2001-02-21 | 2004-06-22 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and electronic appliance |

| KR100788391B1 (ko) * | 2001-02-27 | 2007-12-31 | 엘지.필립스 엘시디 주식회사 | 액정표시패널의 양 방향 구동 회로 |

| US6301172B1 (en) * | 2001-02-27 | 2001-10-09 | Micron Technology, Inc. | Gate voltage testkey for isolation transistor |

| JP4761643B2 (ja) * | 2001-04-13 | 2011-08-31 | 東芝モバイルディスプレイ株式会社 | シフトレジスタ、駆動回路、電極基板及び平面表示装置 |

| CN1212598C (zh) | 2001-04-26 | 2005-07-27 | 凌阳科技股份有限公司 | 液晶显示器的源驱动放大器 |

| JP4785271B2 (ja) * | 2001-04-27 | 2011-10-05 | 株式会社半導体エネルギー研究所 | 液晶表示装置、電子機器 |

| JP4439761B2 (ja) | 2001-05-11 | 2010-03-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置、電子機器 |

| TW582005B (en) | 2001-05-29 | 2004-04-01 | Semiconductor Energy Lab | Pulse output circuit, shift register, and display device |

| JP2003005710A (ja) * | 2001-06-25 | 2003-01-08 | Nec Corp | 電流駆動回路及び画像表示装置 |

| TW554558B (en) | 2001-07-16 | 2003-09-21 | Semiconductor Energy Lab | Light emitting device |

| US6788108B2 (en) | 2001-07-30 | 2004-09-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP4831895B2 (ja) | 2001-08-03 | 2011-12-07 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US7218349B2 (en) | 2001-08-09 | 2007-05-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP4869516B2 (ja) | 2001-08-10 | 2012-02-08 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN101257743B (zh) * | 2001-08-29 | 2011-05-25 | 株式会社半导体能源研究所 | 发光器件及这种发光器件的驱动方法 |

| KR100753365B1 (ko) * | 2001-10-16 | 2007-08-30 | 삼성전자주식회사 | 쉬프트 레지스터 및 이를 갖는 액정표시장치 |

| US7365713B2 (en) * | 2001-10-24 | 2008-04-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| US7456810B2 (en) * | 2001-10-26 | 2008-11-25 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and driving method thereof |

| KR20030038522A (ko) * | 2001-11-09 | 2003-05-16 | 산요 덴키 가부시키가이샤 | 광학 소자의 휘도 데이터를 초기화하는 기능을 갖는 표시장치 |

| JP4397555B2 (ja) | 2001-11-30 | 2010-01-13 | 株式会社半導体エネルギー研究所 | 半導体装置、電子機器 |

| KR100453635B1 (ko) * | 2001-12-29 | 2004-10-20 | 엘지.필립스 엘시디 주식회사 | 능동행렬 유기전기발광소자 |

| TWI310632B (en) * | 2002-01-17 | 2009-06-01 | Semiconductor Energy Lab | Electric circuit |

| JP2003216126A (ja) | 2002-01-25 | 2003-07-30 | Toshiba Corp | 駆動回路、電極基板及び平面表示装置 |

| TW536691B (en) * | 2002-03-19 | 2003-06-11 | Au Optronics Corp | Drive circuit of display |

| SG119186A1 (en) * | 2002-05-17 | 2006-02-28 | Semiconductor Energy Lab | Display apparatus and driving method thereof |

| AU2003240026A1 (en) | 2002-06-15 | 2003-12-31 | Samsung Electronics Co., Ltd. | Method of driving a shift register, a shift register, a liquid crystal display device having the shift register |

| KR100432651B1 (ko) * | 2002-06-18 | 2004-05-22 | 삼성에스디아이 주식회사 | 화상 표시 장치 |

| JP3092506U (ja) | 2002-09-01 | 2003-03-20 | 善嗣 上田 | 両手摺付踏台 |

| JP4460822B2 (ja) | 2002-11-29 | 2010-05-12 | 東芝モバイルディスプレイ株式会社 | 双方向シフトレジスタ、これを用いた駆動回路、平面表示装置 |

| US7738014B2 (en) * | 2002-12-05 | 2010-06-15 | Atlab Inc. | Image sensor and optical pointing system |

| JP4339103B2 (ja) * | 2002-12-25 | 2009-10-07 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| TW591583B (en) * | 2003-05-09 | 2004-06-11 | Toppoly Optoelectronics Corp | Current register unit and circuit, and image display device applying the current register unit |

| US7595775B2 (en) * | 2003-12-19 | 2009-09-29 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting display device with reverse biasing circuit |

| KR100705628B1 (ko) * | 2003-12-30 | 2007-04-11 | 비오이 하이디스 테크놀로지 주식회사 | 액정표시장치의 구동회로 |

| US7203264B2 (en) | 2005-06-28 | 2007-04-10 | Wintek Corporation | High-stability shift circuit using amorphous silicon thin film transistors |

-

2003

- 2003-12-18 JP JP2003421672A patent/JP4339103B2/ja not_active Expired - Fee Related

- 2003-12-22 KR KR1020030094579A patent/KR101019135B1/ko active IP Right Grant

- 2003-12-22 US US10/740,840 patent/US7202863B2/en active Active

- 2003-12-24 TW TW092136746A patent/TWI307165B/zh not_active IP Right Cessation

- 2003-12-25 CN CN2007101851542A patent/CN101149893B/zh not_active Expired - Lifetime

- 2003-12-25 CN CNB2003101216823A patent/CN100385476C/zh not_active Expired - Lifetime

-

2007

- 2007-02-15 US US11/675,122 patent/US7786985B2/en active Active

-

2008

- 2008-10-22 JP JP2008271481A patent/JP4574708B2/ja not_active Expired - Lifetime

- 2008-12-22 KR KR1020080130908A patent/KR101037728B1/ko active IP Right Grant

-

2009

- 2009-07-06 JP JP2009160077A patent/JP5042279B2/ja not_active Expired - Fee Related

-

2010

- 2010-06-04 JP JP2010129156A patent/JP5211110B2/ja not_active Expired - Fee Related

- 2010-08-04 US US12/849,885 patent/US8044906B2/en not_active Expired - Fee Related

- 2010-09-22 US US12/887,555 patent/US8059078B2/en not_active Expired - Fee Related

- 2010-10-21 KR KR1020100102879A patent/KR101123095B1/ko active IP Right Grant

-

2011

- 2011-03-04 KR KR1020110019349A patent/KR101123096B1/ko active IP Right Grant

- 2011-10-20 US US13/277,301 patent/US8456402B2/en not_active Expired - Lifetime

-

2012

- 2012-06-01 JP JP2012125687A patent/JP5393843B2/ja not_active Expired - Lifetime

-

2013

- 2013-05-31 US US13/906,934 patent/US8823620B2/en not_active Expired - Lifetime

- 2013-09-03 JP JP2013181981A patent/JP5619240B2/ja not_active Expired - Lifetime

- 2013-09-03 JP JP2013181983A patent/JP5640126B2/ja not_active Expired - Lifetime

-

2014

- 2014-05-21 JP JP2014104863A patent/JP5777769B2/ja not_active Expired - Lifetime

- 2014-08-29 US US14/472,748 patent/US9190425B2/en not_active Expired - Fee Related

-

2015

- 2015-05-05 JP JP2015094503A patent/JP5947952B2/ja not_active Expired - Lifetime

- 2015-11-16 US US14/941,739 patent/US9640135B2/en not_active Expired - Lifetime

- 2015-12-02 JP JP2015235376A patent/JP6010679B2/ja not_active Expired - Lifetime

-

2016

- 2016-02-24 JP JP2016032690A patent/JP2016146637A/ja not_active Withdrawn

-

2017

- 2017-02-23 JP JP2017031986A patent/JP2017143523A/ja not_active Withdrawn

- 2017-05-01 US US15/582,886 patent/US9881582B2/en not_active Expired - Lifetime

- 2017-06-20 JP JP2017120180A patent/JP2017200217A/ja not_active Withdrawn

- 2017-07-05 JP JP2017131626A patent/JP2017229074A/ja not_active Withdrawn

- 2017-09-15 JP JP2017177475A patent/JP2018029345A/ja not_active Withdrawn

-

2018

- 2018-01-26 US US15/880,590 patent/US10121448B2/en not_active Expired - Lifetime

- 2018-11-02 US US16/178,650 patent/US10373581B2/en not_active Expired - Fee Related

-

2019

- 2019-07-30 US US16/525,643 patent/US10867576B2/en not_active Expired - Lifetime

- 2019-08-26 JP JP2019153868A patent/JP2019216464A/ja active Pending

-

2020

- 2020-12-14 US US17/120,373 patent/US11217200B2/en not_active Expired - Lifetime

-

2021

- 2021-12-28 US US17/563,157 patent/US20220122562A1/en not_active Abandoned

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6010679B2 (ja) | デジタル回路、半導体装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090414 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090609 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090630 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090701 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4339103 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120710 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120710 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120710 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120710 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130710 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |