JP6140551B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6140551B2 JP6140551B2 JP2013134515A JP2013134515A JP6140551B2 JP 6140551 B2 JP6140551 B2 JP 6140551B2 JP 2013134515 A JP2013134515 A JP 2013134515A JP 2013134515 A JP2013134515 A JP 2013134515A JP 6140551 B2 JP6140551 B2 JP 6140551B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- oxide semiconductor

- electrode layer

- insulating film

- semiconductor film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

- H10D30/6715—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

- H10D30/6756—Amorphous oxide semiconductors

-

- H10D64/011—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H10P14/69433—

Landscapes

- Thin Film Transistor (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Memories (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

- Formation Of Insulating Films (AREA)

- Non-Volatile Memory (AREA)

- Liquid Crystal (AREA)

Description

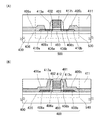

本実施の形態では、本発明の一態様の半導体装置について図面を用いて詳細に説明する。図1に本発明の一態様の半導体装置である、トランジスタ420の上面図および断面図を示す。図1(A)はトランジスタ420の上面図を示し、図1(B)は図1(A)に示す一点鎖線A−Bにおける断面図を示したものである。

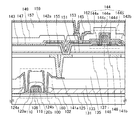

本実施の形態では、実施の形態1とは異なる、本発明の一態様のトランジスタについて説明する。なお、本実施の形態では、実施の形態1と同様の箇所については同様の符号を付し、詳細な説明は省略する。

本実施の形態では、実施の形態1および実施の形態2に示すトランジスタを使用した半導体装置の一例について図7および図8を用いて説明する。

本実施の形態では、本明細書に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を、図面を用いて説明する。

本実施の形態では、先の実施の形態で示した半導体装置を携帯電話、スマートフォン、電子書籍などの電子機器に応用した場合の例を図11乃至図14を用いて説明する。

102 下地絶縁膜

108 ゲート絶縁膜

110 ゲート電極層

116 半導体層

120a 側壁絶縁膜

120b 側壁絶縁膜

124a ソース電極層

124b ドレイン電極層

125 絶縁膜

131 絶縁膜

133 絶縁膜

135 絶縁膜

137 絶縁膜

141a 導電層

141b 導電層

142a ソース電極層

142b ドレイン電極層

143 窒化シリコン膜

144 酸化物半導体膜

144a 低抵抗領域

144b 低抵抗領域

144c 低抵抗領域

144d 低抵抗領域

144e チャネル形成領域

145 配線層

146 ゲート絶縁膜

147 絶縁膜

148 ゲート電極層

149 絶縁膜

151 絶縁膜

153 絶縁膜

155 絶縁膜

157 絶縁膜

159 配線層

160 トランジスタ

162 トランジスタ

164 容量素子

201 トランジスタ

202 トランジスタ

203 トランジスタ

204 トランジスタ

211 トランジスタ

212 トランジスタ

213 トランジスタ

214 トランジスタ

242 導電層

250 メモリセル

251 メモリセルアレイ

251a メモリセルアレイ

251b メモリセルアレイ

253 周辺回路

254 容量素子

256 導電層

257 導電層

258 配線層

259 配線層

260 トランジスタ

262 トランジスタ

271 配線層

272 配線層

273 導電層

274 導電層

275 導電層

276 導電層

277 導電層

400 基板

401 ゲート電極層

402 ゲート絶縁膜

403 チャネル形成領域

403a 領域

403b 領域

404a 低抵抗領域

404b 低抵抗領域

405a ソース電極層

405b ドレイン電極層

406a 低抵抗領域

406b 低抵抗領域

407 窒化シリコン膜

408a 低抵抗領域

408b 低抵抗領域

409 酸化物半導体膜

410a 低抵抗領域

410b 低抵抗領域

411 層間絶縁膜

412 絶縁膜

413a 側壁絶縁膜

413b 側壁絶縁膜

414 層間絶縁膜

420 トランジスタ

421 不純物元素

430 トランジスタ

436 下地絶縁膜

438 下地絶縁膜

509 酸化物半導体膜

520 トランジスタ

530 トランジスタ

540 トランジスタ

801 トランジスタ

803 トランジスタ

804 トランジスタ

805 トランジスタ

806 トランジスタ

807 Xデコーダー

808 Yデコーダー

811 トランジスタ

812 保持容量

813 Xデコーダー

814 Yデコーダー

901 RF回路

902 アナログベースバンド回路

903 デジタルベースバンド回路

904 バッテリー

905 電源回路

906 アプリケーションプロセッサ

907 CPU

908 DSP

910 フラッシュメモリ

911 ディスプレイコントローラ

912 メモリ回路

913 ディスプレイ

914 表示部

915 ソースドライバ

916 ゲートドライバ

917 音声回路

918 キーボード

919 タッチセンサ

950 メモリ回路

951 メモリコントローラ

952 メモリ

953 メモリ

954 スイッチ

955 スイッチ

956 ディスプレイコントローラ

957 ディスプレイ

1001 バッテリー

1002 電源回路

1003 マイクロプロセッサ

1004 フラッシュメモリ

1005 音声回路

1006 キーボード

1007 メモリ回路

1008 タッチパネル

1009 ディスプレイ

1010 ディスプレイコントローラ

9033 留め具

9034 スイッチ

9035 電源スイッチ

9036 スイッチ

9038 操作スイッチ

9630 筐体

9631 表示部

9631a 表示部

9631b 表示部

9632a 領域

9632b 領域

9633 太陽電池

9634 充放電制御回路

9635 バッテリー

9636 DCDCコンバータ

9637 コンバータ

9638 操作キー

9639 ボタン

Claims (5)

- 酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において500℃以下では水素分子の脱離量のピークを現さない半導体装置。 - 酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において550℃以下では水素分子の脱離量が1.5×1020個/cm3以下である半導体装置。 - 酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において、水素分子の脱離量が1.0×1020個/cm3以上となる温度が500℃以上である半導体装置。 - 請求項1乃至請求項3のいずれか一項において、

前記酸化物半導体膜が、c軸の向きが表面に対して概略垂直である結晶を含む半導体装置。 - 請求項1乃至請求項4のいずれか一項において、

前記酸化物半導体膜が、前記ソース電極層および前記ドレイン電極層と接する領域にリンまたはホウ素を含む半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013134515A JP6140551B2 (ja) | 2012-06-29 | 2013-06-27 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012147633 | 2012-06-29 | ||

| JP2012147633 | 2012-06-29 | ||

| JP2013134515A JP6140551B2 (ja) | 2012-06-29 | 2013-06-27 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017090183A Division JP6416316B2 (ja) | 2012-06-29 | 2017-04-28 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014030000A JP2014030000A (ja) | 2014-02-13 |

| JP2014030000A5 JP2014030000A5 (ja) | 2016-08-04 |

| JP6140551B2 true JP6140551B2 (ja) | 2017-05-31 |

Family

ID=49777168

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013134515A Active JP6140551B2 (ja) | 2012-06-29 | 2013-06-27 | 半導体装置 |

| JP2017090183A Active JP6416316B2 (ja) | 2012-06-29 | 2017-04-28 | 半導体装置の作製方法 |

| JP2018188198A Active JP6648233B2 (ja) | 2012-06-29 | 2018-10-03 | 半導体装置 |

| JP2020004239A Active JP6966578B2 (ja) | 2012-06-29 | 2020-01-15 | 半導体装置 |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017090183A Active JP6416316B2 (ja) | 2012-06-29 | 2017-04-28 | 半導体装置の作製方法 |

| JP2018188198A Active JP6648233B2 (ja) | 2012-06-29 | 2018-10-03 | 半導体装置 |

| JP2020004239A Active JP6966578B2 (ja) | 2012-06-29 | 2020-01-15 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US9472682B2 (ja) |

| JP (4) | JP6140551B2 (ja) |

| KR (2) | KR102099445B1 (ja) |

| TW (1) | TWI596778B (ja) |

Families Citing this family (47)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6224931B2 (ja) | 2012-07-27 | 2017-11-01 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2016027597A (ja) | 2013-12-06 | 2016-02-18 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9397149B2 (en) | 2013-12-27 | 2016-07-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN117690933A (zh) | 2013-12-27 | 2024-03-12 | 株式会社半导体能源研究所 | 发光装置 |

| KR102060377B1 (ko) * | 2014-01-27 | 2020-02-11 | 한국전자통신연구원 | 디스플레이 소자, 그 제조 방법, 및 이미지 센서 소자의 제조방법 |

| US9443876B2 (en) | 2014-02-05 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device including the semiconductor device, display module including the display device, and electronic device including the semiconductor device, the display device, and the display module |

| JP2015188062A (ja) | 2014-02-07 | 2015-10-29 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10290908B2 (en) | 2014-02-14 | 2019-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| US9443872B2 (en) * | 2014-03-07 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2015132694A1 (en) * | 2014-03-07 | 2015-09-11 | Semiconductor Energy Laboratory Co., Ltd. | Touch sensor, touch panel, and manufacturing method of touch panel |

| JP6585354B2 (ja) | 2014-03-07 | 2019-10-02 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6607681B2 (ja) * | 2014-03-07 | 2019-11-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9640669B2 (en) * | 2014-03-13 | 2017-05-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device including the semiconductor device, display module including the display device, and electronic appliance including the semiconductor device, the display device, and the display module |

| TWI657488B (zh) * | 2014-03-20 | 2019-04-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置、具有該半導體裝置的顯示裝置、具有該顯示裝置的顯示模組以及具有該半導體裝置、該顯示裝置和該顯示模組的電子裝置 |

| CN106165106B (zh) | 2014-03-28 | 2020-09-15 | 株式会社半导体能源研究所 | 晶体管以及半导体装置 |

| US10147823B2 (en) * | 2015-03-19 | 2018-12-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR102663128B1 (ko) * | 2015-04-13 | 2024-05-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US10192995B2 (en) * | 2015-04-28 | 2019-01-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9837547B2 (en) | 2015-05-22 | 2017-12-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising oxide conductor and display device including the semiconductor device |

| TWI613706B (zh) * | 2015-07-03 | 2018-02-01 | Au Optronics Corp. | 氧化物半導體薄膜電晶體及其製作方法 |

| WO2017006207A1 (en) * | 2015-07-08 | 2017-01-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9825177B2 (en) | 2015-07-30 | 2017-11-21 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of a semiconductor device using multiple etching mask |

| US9893202B2 (en) | 2015-08-19 | 2018-02-13 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| JP6851166B2 (ja) | 2015-10-12 | 2021-03-31 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9852926B2 (en) * | 2015-10-20 | 2017-12-26 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method for semiconductor device |

| US10243010B2 (en) * | 2015-11-30 | 2019-03-26 | Sharp Kabushiki Kaisha | Semiconductor substrate and display device |

| WO2017098369A1 (en) * | 2015-12-11 | 2017-06-15 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor film, semiconductor device, and display device |

| CN115172467A (zh) * | 2016-02-18 | 2022-10-11 | 株式会社半导体能源研究所 | 半导体装置、其制造方法、显示装置以及电子设备 |

| US10656483B2 (en) | 2016-03-14 | 2020-05-19 | Sharp Kabushiki Kaisha | Semiconductor apparatus and method for manufacturing semiconductor apparatus |

| CN115241045B (zh) | 2016-03-22 | 2025-04-04 | 株式会社半导体能源研究所 | 半导体装置以及包括该半导体装置的显示装置 |

| KR102711637B1 (ko) | 2016-05-19 | 2024-09-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 복합 산화물 반도체 및 트랜지스터 |

| KR102359245B1 (ko) * | 2016-07-08 | 2022-02-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 전자 기기 |

| US10147681B2 (en) * | 2016-12-09 | 2018-12-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US20210125988A1 (en) * | 2017-03-13 | 2021-04-29 | Semiconductors Energy Laboratory Co., Ltd. | Semiconductor Device and Method for Manufacturing Semiconductor Device |

| WO2018197994A1 (en) | 2017-04-28 | 2018-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of semiconductor device |

| US20180323246A1 (en) * | 2017-05-02 | 2018-11-08 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Organic light-emitting diode display panel and manufacturing method thereof |

| CN108226735B (zh) * | 2017-11-24 | 2020-11-06 | 京东方科技集团股份有限公司 | 一种有机薄膜晶体管电学特性的确定方法及介质 |

| US11289475B2 (en) | 2019-01-25 | 2022-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method of semiconductor device |

| CN118763123A (zh) | 2019-09-24 | 2024-10-11 | 乐金显示有限公司 | 薄膜晶体管及其基板及包括该薄膜晶体管的显示设备 |

| KR102854448B1 (ko) | 2019-10-08 | 2025-09-03 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 제조 방법 |

| JP7066672B2 (ja) * | 2019-12-19 | 2022-05-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP7424268B2 (ja) * | 2020-10-19 | 2024-01-30 | 住友電気工業株式会社 | トランジスタ |

| JP2022077434A (ja) * | 2020-11-11 | 2022-05-23 | 日本放送協会 | 薄膜トランジスタとその製造方法、及び表示装置 |

| CN113437144A (zh) * | 2021-05-22 | 2021-09-24 | 兰州大学 | 一种基于二硫化铼的场效应管及其制造方法 |

| CN115101542B (zh) * | 2021-12-09 | 2025-03-28 | 友达光电股份有限公司 | 半导体装置及其制造方法 |

| JP2024008440A (ja) * | 2022-07-08 | 2024-01-19 | 株式会社ジャパンディスプレイ | 半導体装置 |

| JP2024139916A (ja) * | 2023-03-28 | 2024-10-10 | 株式会社ジャパンディスプレイ | 半導体装置、表示装置、及び半導体装置の製造方法 |

Family Cites Families (150)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH04367277A (ja) | 1991-06-14 | 1992-12-18 | Nec Corp | 薄膜トランジスタおよびその製造方法 |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP2002198526A (ja) * | 2000-12-27 | 2002-07-12 | Fujitsu Ltd | 半導体装置の製造方法 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3909583B2 (ja) * | 2001-08-27 | 2007-04-25 | セイコーエプソン株式会社 | 電気光学装置の製造方法 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| SG115733A1 (en) * | 2004-03-12 | 2005-10-28 | Semiconductor Energy Lab | Thin film transistor, semiconductor device, and method for manufacturing the same |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| KR20070116889A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 박막의 기상성막방법 |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| AU2005302964B2 (en) | 2004-11-10 | 2010-11-04 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101397571B1 (ko) | 2005-11-15 | 2014-05-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제조방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| JP5015471B2 (ja) | 2006-02-15 | 2012-08-29 | 財団法人高知県産業振興センター | 薄膜トランジスタ及びその製法 |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP2007305645A (ja) * | 2006-05-09 | 2007-11-22 | Nec Corp | 磁気メモリ装置、及びその製造方法 |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| JP5105842B2 (ja) | 2006-12-05 | 2012-12-26 | キヤノン株式会社 | 酸化物半導体を用いた表示装置及びその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| JP5215589B2 (ja) | 2007-05-11 | 2013-06-19 | キヤノン株式会社 | 絶縁ゲート型トランジスタ及び表示装置 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP2008300678A (ja) * | 2007-05-31 | 2008-12-11 | Oki Electric Ind Co Ltd | 半導体素子の製造方法、及び半導体素子 |

| JP5069531B2 (ja) * | 2007-09-28 | 2012-11-07 | 富士フイルム株式会社 | 窒化シリコン膜の形成方法 |

| JP5213422B2 (ja) * | 2007-12-04 | 2013-06-19 | キヤノン株式会社 | 絶縁層を有する酸化物半導体素子およびそれを用いた表示装置 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP5264197B2 (ja) | 2008-01-23 | 2013-08-14 | キヤノン株式会社 | 薄膜トランジスタ |

| JP2009212504A (ja) * | 2008-02-08 | 2009-09-17 | Advanced Lcd Technologies Development Center Co Ltd | 薄膜半導体装置およびその製造方法 |

| JP5345328B2 (ja) | 2008-02-22 | 2013-11-20 | 住友電工デバイス・イノベーション株式会社 | 半導体装置の製造方法 |

| JP5704790B2 (ja) | 2008-05-07 | 2015-04-22 | キヤノン株式会社 | 薄膜トランジスタ、および、表示装置 |

| KR101496148B1 (ko) | 2008-05-15 | 2015-02-27 | 삼성전자주식회사 | 반도체소자 및 그 제조방법 |

| US8258511B2 (en) * | 2008-07-02 | 2012-09-04 | Applied Materials, Inc. | Thin film transistors using multiple active channel layers |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5430113B2 (ja) | 2008-10-08 | 2014-02-26 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| KR101634411B1 (ko) | 2008-10-31 | 2016-06-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 구동 회로, 표시 장치 및 전자 장치 |

| JP5515281B2 (ja) * | 2008-12-03 | 2014-06-11 | ソニー株式会社 | 薄膜トランジスタ、表示装置、電子機器および薄膜トランジスタの製造方法 |

| JP5781720B2 (ja) | 2008-12-15 | 2015-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| EP2515337B1 (en) | 2008-12-24 | 2016-02-24 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit and semiconductor device |

| US8115883B2 (en) | 2009-08-27 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| KR20120084751A (ko) | 2009-10-05 | 2012-07-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| CN104733540B (zh) | 2009-10-09 | 2019-11-12 | 株式会社半导体能源研究所 | 半导体器件 |

| WO2011043194A1 (en) | 2009-10-09 | 2011-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR20220038542A (ko) | 2009-10-21 | 2022-03-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 아날로그 회로 및 반도체 장치 |

| EP2494601A4 (en) | 2009-10-30 | 2016-09-07 | Semiconductor Energy Lab | SEMICONDUCTOR COMPONENT AND MANUFACTURING METHOD THEREFOR |

| KR20120106786A (ko) * | 2009-12-08 | 2012-09-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| WO2011074407A1 (en) * | 2009-12-18 | 2011-06-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101675113B1 (ko) | 2010-01-08 | 2016-11-11 | 삼성전자주식회사 | 트랜지스터 및 그 제조방법 |

| JP2011164302A (ja) | 2010-02-08 | 2011-08-25 | Seiko Epson Corp | 電気泳動表示装置、電子機器 |

| US8563095B2 (en) * | 2010-03-15 | 2013-10-22 | Applied Materials, Inc. | Silicon nitride passivation layer for covering high aspect ratio features |

| KR101806271B1 (ko) * | 2010-05-14 | 2017-12-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치의 제작 방법 |

| US9209314B2 (en) * | 2010-06-16 | 2015-12-08 | Semiconductor Energy Laboratory Co., Ltd. | Field effect transistor |

| JP2012015436A (ja) | 2010-07-05 | 2012-01-19 | Sony Corp | 薄膜トランジスタおよび表示装置 |

| JP5917035B2 (ja) | 2010-07-26 | 2016-05-11 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2012033836A (ja) | 2010-08-03 | 2012-02-16 | Canon Inc | トップゲート型薄膜トランジスタ及びこれを備えた表示装置 |

| US20120032172A1 (en) | 2010-08-06 | 2012-02-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2012043338A1 (ja) * | 2010-09-28 | 2012-04-05 | 凸版印刷株式会社 | 薄膜トランジスタ及びその製造方法、薄膜トランジスタを備える画像表示装置 |

| TWI535014B (zh) | 2010-11-11 | 2016-05-21 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| WO2012090799A1 (en) | 2010-12-28 | 2012-07-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9443984B2 (en) * | 2010-12-28 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5784479B2 (ja) | 2010-12-28 | 2015-09-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR101832361B1 (ko) | 2011-01-19 | 2018-04-16 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| JP6019329B2 (ja) | 2011-03-31 | 2016-11-02 | 株式会社Joled | 表示装置および電子機器 |

| US9478668B2 (en) * | 2011-04-13 | 2016-10-25 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor film and semiconductor device |

| US8748240B2 (en) | 2011-12-22 | 2014-06-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| TW201338173A (zh) | 2012-02-28 | 2013-09-16 | 新力股份有限公司 | 電晶體、製造電晶體之方法、顯示裝置及電子機器 |

| CN103367459B (zh) | 2012-03-28 | 2019-08-27 | 株式会社日本有机雷特显示器 | 半导体装置和电子设备 |

-

2013

- 2013-06-19 KR KR1020130070127A patent/KR102099445B1/ko not_active Expired - Fee Related

- 2013-06-19 TW TW102121736A patent/TWI596778B/zh not_active IP Right Cessation

- 2013-06-24 US US13/924,757 patent/US9472682B2/en active Active

- 2013-06-27 JP JP2013134515A patent/JP6140551B2/ja active Active

-

2016

- 2016-10-13 US US15/292,243 patent/US10811521B2/en active Active

-

2017

- 2017-04-28 JP JP2017090183A patent/JP6416316B2/ja active Active

-

2018

- 2018-10-03 JP JP2018188198A patent/JP6648233B2/ja active Active

-

2020

- 2020-01-15 JP JP2020004239A patent/JP6966578B2/ja active Active

- 2020-04-03 KR KR1020200041145A patent/KR102240219B1/ko not_active Expired - Fee Related

- 2020-10-14 US US17/070,349 patent/US11393918B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9472682B2 (en) | 2016-10-18 |

| JP6648233B2 (ja) | 2020-02-14 |

| JP2014030000A (ja) | 2014-02-13 |

| US11393918B2 (en) | 2022-07-19 |

| TW201419549A (zh) | 2014-05-16 |

| US20210184021A1 (en) | 2021-06-17 |

| KR102240219B1 (ko) | 2021-04-13 |

| KR20200038448A (ko) | 2020-04-13 |

| US10811521B2 (en) | 2020-10-20 |

| JP2020065080A (ja) | 2020-04-23 |

| KR102099445B1 (ko) | 2020-04-09 |

| TWI596778B (zh) | 2017-08-21 |

| US20170033205A1 (en) | 2017-02-02 |

| JP2017168854A (ja) | 2017-09-21 |

| JP6966578B2 (ja) | 2021-11-17 |

| KR20140002500A (ko) | 2014-01-08 |

| US20140001468A1 (en) | 2014-01-02 |

| JP2019024112A (ja) | 2019-02-14 |

| JP6416316B2 (ja) | 2018-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6966578B2 (ja) | 半導体装置 | |

| JP6689340B2 (ja) | 半導体装置 | |

| JP6496439B2 (ja) | 半導体装置 | |

| JP6254347B2 (ja) | 半導体装置 | |

| JP6245904B2 (ja) | 半導体装置 | |

| JP6068992B2 (ja) | 半導体装置の作製方法 | |

| JP6097037B2 (ja) | 半導体装置 | |

| JP2020031219A (ja) | 半導体装置 | |

| JP6026839B2 (ja) | 半導体装置 | |

| JP5806905B2 (ja) | 半導体装置 | |

| JP6022880B2 (ja) | 半導体装置及び半導体装置の作製方法 | |

| US20130087782A1 (en) | Oxide semiconductor film and semiconductor device | |

| JP6049479B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160614 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160614 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170324 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170404 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170501 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6140551 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |