JP5979570B2 - 半導体装置、及びそれを用いたインバータ - Google Patents

半導体装置、及びそれを用いたインバータ Download PDFInfo

- Publication number

- JP5979570B2 JP5979570B2 JP2015526160A JP2015526160A JP5979570B2 JP 5979570 B2 JP5979570 B2 JP 5979570B2 JP 2015526160 A JP2015526160 A JP 2015526160A JP 2015526160 A JP2015526160 A JP 2015526160A JP 5979570 B2 JP5979570 B2 JP 5979570B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- region

- gate

- source

- current

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/42—Conversion of DC power input into AC power output without possibility of reversal

- H02M7/44—Conversion of DC power input into AC power output without possibility of reversal by static converters

- H02M7/48—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/5387—Conversion of DC power input into AC power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/32—Means for protecting converters other than automatic disconnection

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output

- H02M7/66—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output with possibility of reversal

- H02M7/68—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output with possibility of reversal by static converters

- H02M7/72—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output with possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/79—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output with possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/797—Conversion of AC power input into DC power output; Conversion of DC power input into AC power output with possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/63—Vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/63—Vertical IGFETs

- H10D30/635—Vertical IGFETs having no inversion channels, e.g. vertical accumulation channel FETs [ACCUFET] or normally-on vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/669—Vertical DMOS [VDMOS] FETs having voltage-sensing or current-sensing structures, e.g. emulator sections or overcurrent sensing cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/114—PN junction isolations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/126—Top-view geometrical layouts of the regions or the junctions

- H10D62/127—Top-view geometrical layouts of the regions or the junctions of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

- H10D64/513—Disposition of the gate electrodes, e.g. buried gates within recesses in the substrate, e.g. trench gates, groove gates or buried gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/035—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon carbide [SiC] technology

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

- H10W10/01—Manufacture or treatment

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0009—Devices or circuits for detecting current in a converter

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/926—Multiple bond pads having different sizes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Inverter Devices (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Junction Field-Effect Transistors (AREA)

Description

(半導体装置の構造)

図1(a)は、本実施形態に係る半導体装置の概略を示す平面図である。図1(b)は、図1(a)におけるA−A’部分の概略を示す断面図である。図1(c)は、図1(b)における単位セル111の概略を示す断面図である。図1(d)は、図1(b)に示す素子分離領域110近傍を拡大して示す断面図である。本実施形態では、単位セル111がプレーナ型の金属‐絶縁体‐半導体電界効果トランジスタ(Metal‐Insulator‐Semiconductor Field Effect Transistor:MISFET)である例について説明する。

Ism=n×Iss ・・・(1)

Vgs=0のときのPchがダイオードの立ち上がり電圧Vf0に相当する。式(2)から、ボディ領域の不純物濃度Nbを大きくすることにより、|Vf0|を小さくすることができることがわかる。

次に、図2から図4を参照しながら、本実施形態に係る半導体装置の製造方法について説明する。図2から図4は、本実施形態に係る半導体装置の製造方法を示す断面図である。

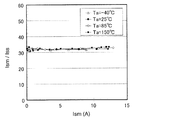

本実施形態に係る半導体装置1を試作し、電気特性を評価した。試作した半導体装置1において、ボディ領域7のn型不純物濃度は2×1018cm-3、ゲート絶縁膜12の膜厚は70nmとした。第2の炭化珪素半導体層11は、n型不純物濃度が1.1×1018cm-3のn型不純物層上に、膜厚75nmのアンドープ層を積層した構造とした。試作した半導体装置1における、センス領域に対するメイン領域の単位セル数比率は34である。試作した半導体装置1の順方向の閾値電圧Vth及び逆方向の立ち上がり電圧Vfを、プローバー及び半導体パラメータアナライザを用いて評価した。

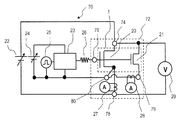

次に、電極パターンを形成した基板72上に試作した半導体装置1を実装し、大電流での評価を行った。図7は、本実施形態に係る半導体装置1のメイン領域20及びセンス領域21に同時に流れる順方向電流を評価するための測定系70の回路構成を示す図である。半導体装置1を実装した基板72は、ドレイン端子74、ゲート端子76、メイン領域ソース端子78、センス領域ソース端子79及びケルビン端子80を備えている。ドレイン端子74・メイン領域ソース端子78間にはVcc電源22が直列に接続されている。メイン領域20のメイン領域ソースパッド2は、基板上でメイン領域ソース端子78及びケルビン端子80に接続されている。

次に、試作した半導体装置1について、逆方向電流の評価を行った。図10は、本実施形態に係る半導体装置1のメイン領域20及びセンス領域21に同時に流れる逆方向電流を評価するための測定系90の回路構成を示す図である。

Vsense=−Iss×Rsense (4)

ここで、Issはセンス領域34に流れる電流、Rsenseはセンス抵抗36の抵抗値である。上記の式の右辺は、センス領域34に流れる電流がドレインからソースに向かって流れる、いわゆる順方向電流の場合には負の値となり、ソースからドレインに流れる、いわゆる逆方向電流の場合には正の値となる。

(半導体装置の構造)

次に、本開示の第2の実施形態に係る半導体装置について、図面を参照して説明する。図15(a)は、本実施形態に係る半導体装置の概略を示す平面図である。図15(b)は、図15(a)におけるA−A’部分の概略を示す断面図である。図15(c)は、図15(b)における単位セルの概略を示す断面図である。図15(d)は図15(b)における、メイン領域320とセンス領域321との境界部分を拡大して示す断面図である。

次に、図16から図18を参照しながら、本実施形態に係る半導体装置の製造方法を説明する。図16から図18は、本実施形態に係る半導体装置の製造方法を示す断面図である。

次に、本開示の第3の実施形態に係るインバータについて、図面を参照して説明する。図19は、本実施形態に係るインバータ402を備える負荷駆動システム400の構成を示すブロック図である。

次に、本開示の第4の実施形態に係るインバータについて、図面を参照して説明する。本実施形態のインバータは、回生電流を平滑コンデンサの電圧によって検出するのでなく、半導体装置を流れる逆方向電流によって検出する点で第3の実施の形態と異なる。

図27はチャネルダイオードの機能を有しない、従来の電流検出機能付の半導体装置501aから501fを用いたインバータのブロック図を示す。チャネルダイオードがないので、外付けの還流ダイオード502を各アームの半導体装置に逆並列に接続する必要がある。従来の電流検出機能付の半導体装置501は、順方向電流の検出はできるものの、外付けの還流ダイオードに流れる逆方向電流の検出は出来ない。したがって本開示の第4の実施形態のように、回生電流の検出を直接行うことはできず、平滑コンデンサの電圧を電圧検出部420で検出するか、外付け還流ダイオード用の電流検出器を別途設けないと、回生電流が流れているとの判断ができない。

2 メイン領域ソースパッド

3 センス領域ソースパッド

4 ゲートパッド

5 半導体基板

6 第1の炭化珪素半導体層

7 ボディ領域(ウェル領域)

8 ソース領域

9 コンタクト領域

10 ソース電極

11 第2の炭化珪素半導体層

12 ゲート絶縁膜

13 ゲート電極

14 層間絶縁膜

15 上部配線

16 ドレイン電極

17 裏面電極

18、19 終端ベース領域

20、320 メイン領域

21、321 センス領域

22 Vcc電源

23 ゲートドライバ

24 ゲートドライバ電源

25 パルス信号発生器

26 ゲート抵抗

27 大電流プローブ

28 小電流プローブ

29 電圧計

30 スイッチング用FET

31 Vdd電源ライン

32 リターンライン

33 メイン領域

34 センス領域

35 演算増幅器

36 センス抵抗

37、45 負荷

40 交流電源

41 チョークコイル

42 整流ダイオード

43 平滑コンデンサ

44a、44c、44e 上アーム

44b、44d、44f 下アーム

46 抵抗

47 スイッチング素子

48 電流電圧変換部

48U 電流電圧変換部(上アーム用)

48L 電流電圧変換部(下アーム用)

49 ゲート電圧制御部

70、90、200 測定系

72 基板

74、204 ドレイン端子

76、206 ゲート端子

78、208 メイン領域ソース端子

79、209 センス領域ソース端子

80、210 ケルビン端子

110 素子分離領域

111、311 単位セル

112 トレンチ

113 多結晶シリコン膜

114 ヴィアホール

400、500 負荷駆動システム

402 インバータ

404 整流回路

406 ダイオードブリッジ回路

408 3相ブリッジ回路

410 回生電力消費回路

420 電圧検出部

440、442、444 レグ

501a、501b、501c、501d、501e、501f 従来の電流検出機能付き半導体素子

502 外付け還流ダイオード

Claims (20)

- メイン領域およびセンス領域を含む第1導電型の半導体基板と、

前記第1導電型の半導体基板の前記メイン領域および前記センス領域にそれぞれ設けられており、金属−絶縁体−半導体電界効果トランジスタを有する複数の単位セルであって、前記センス領域に含まれる単位セルの数は、前記メイン領域に含まれる単位セルの数よりも小さく、前記メイン領域および前記センス領域のそれぞれにおいて、前記金属−絶縁体−半導体電界効果トランジスタが並列に接続された複数の単位セルと、

前記半導体基板の主面側に配置されたゲートパッドと

互いに絶縁された第1のソースパッドおよび第2のソースパッドと、

前記半導体基板の裏面側に配置されたドレインパッドと、

を備え、

各金属−絶縁体−半導体電界効果トランジスタは、

前記半導体基板の主面上に位置する第1導電型の第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に接する第2導電型のボディ領域と、

前記ボディ領域に接する第1導電型のソース領域と、

前記第1の炭化珪素半導体層上でかつ前記ボディ領域及び前記ソース領域の少なくとも一部に接して配置された第2の炭化珪素半導体層と、

前記第2の炭化珪素半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、

前記ソース領域に接触するソース電極と、

前記半導体基板の裏面側に配置されたドレイン電極と

を含み、

前記ソース電極の電位を基準とする前記ドレイン電極の電位をVds、

前記ソース電極の電位を基準とする前記ゲート電極の電位をVgs、

前記金属−絶縁体−半導体電界効果トランジスタのゲート閾値電圧をVthとすると、

前記Vdsが正の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記Vgsが前記Vth以上のとき、前記ドレイン電極から前記ソース電極へ電流を流し、

前記Vdsが負の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記VgsがVth未満のとき、前記ソース電極から前記ドレイン電極へ電流を流すダイオードとして機能し、

前記ダイオードの立ち上がり電圧の絶対値は、前記ボディ領域と前記第1の炭化珪素半導体層とにより構成されるボディダイオードの立ち上がり電圧の絶対値よりも小さく、

前記メイン領域に含まれる前記単位セルにおける前記ゲート電極及び前記センス領域に含まれる前記単位セルにおける前記ゲート電極は、前記ゲートパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ドレイン電極及び前記センス領域に含まれる前記単位セルにおける前記ドレイン電極は、前記ドレインパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ソース電極は、前記第1のソースパッドに電気的に接続され、

前記センス領域に含まれる前記単位セルにおける前記ソース電極は、前記第2のソースパッドに電気的に接続されており、

前記第2の炭化珪素半導体層の少なくとも一部は第1導電型の層であり、

前記第2の炭化珪素半導体層の他の少なくとも一部は、アンドープ層、または不純物濃度が1×10 17 cm -3 未満の第1導電型の層である、半導体装置。 - 前記ボディ領域のうち、少なくとも前記第2の炭化珪素半導体層に接する領域の不純物濃度が1×1018cm-3以上であり、

前記第2の炭化珪素半導体層の前記少なくとも一部の不純物濃度は1×1017cm-3以上4×1018cm-3以下であり、

前記第2の炭化珪素半導体層の厚さは20nm以上70nm以下である請求項1記載の半導体装置。 - 前記メイン領域と前記センス領域との境界に位置し、前記半導体基板上に位置する第1導電型の前記第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に設けられた第2導電型の素子分離領域と

をさらに備え、

前記素子分離領域上には第2の炭化珪素半導体層が配置されていない請求項1または2のいずれかに記載の半導体装置。 - 前記ボディ領域及び前記ソース領域を貫通し、前記第1の炭化珪素半導体層に達するトレンチをさらに備える、請求項1から3のいずれかに記載の半導体装置。

- 前記センス領域に流れる電流が100mA以下である、請求項1から4のいずれかに記載の半導体装置。

- 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、請求項1から5のいずれかに記載の半導体装置であるレグと、

前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部と、

前記電流電圧変換部から出力される前記電圧に基づいて、前記半導体装置の前記ゲートパッドに印加する電圧を制御するゲート電圧制御部と

を備えるインバータ。 - 前記電流電圧変換部は、

反転入力端子、非反転入力端子及び出力端子を有する演算増幅器と、

前記反転入力端子と前記出力端子とを接続する抵抗と、

を含む、請求項6に記載のインバータ。 - 前記演算増幅器は両電源タイプである、請求項7に記載のインバータ。

- 前記レグと並列に接続された平滑コンデンサと、

前記平滑コンデンサの電圧を検出する電圧検出部と、

負荷から前記インバータへ流れる回生電流を熱として消費するための抵抗および前記抵抗に流す回生電流を制御するスイッチング素子を含む回生電力消費回路と、

をさらに備え、

前記ゲート電圧制御部は、前記電圧検出部により検出された前記平滑コンデンサの電圧と、基準電圧値とを比較し、前記平滑コンデンサの電圧が前記基準電圧値を超えた場合、前記抵抗に前記回生電流が流れるように、前記スイッチング素子を制御する、請求項6から8のいずれかに記載のインバータ。 - 前記レグと並列に接続された平滑コンデンサと、

前記平滑コンデンサの電圧を検出する電圧検出部と

をさらに備え、

前記ゲート電圧制御部は、前記電圧検出部により検出された前記平滑コンデンサの電圧と、基準電圧値とを比較し、前記平滑コンデンサの電圧が前記基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にする、請求項6から9のいずれかに記載のインバータ。 - 前記レグと並列に接続された平滑コンデンサと、

負荷から前記インバータへ流れる回生電流を熱として消費するための抵抗および前記抵抗に流す回生電流を制御するスイッチング素子を含む回生電力消費回路と

をさらに備え、

前記ゲート電圧制御部は、前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記抵抗に前記回生電流が流れるように、前記スイッチング素子の動作を制御する、請求項6から8のいずれかに記載のインバータ。 - 前記レグと並列に接続された平滑コンデンサをさらに備え、

前記ゲート電圧制御部は、前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にする、請求項6から8のいずれかに記載のインバータ。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、請求項1から5のいずれかに記載の半導体装置であるレグと、前記レグと並列に接続された平滑コンデンサとを備えたインバータの制御方法であって、

前記平滑コンデンサの電圧を検出するステップと、

前記平滑コンデンサの電圧と、基準電圧値とを比較し、前記平滑コンデンサの電圧が前記基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にするステップと、

を含むインバータの制御方法。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、請求項1から5のいずれかに記載の半導体装置であるレグと、前記レグと並列に接続された平滑コンデンサと、前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部と、負荷から前記インバータへ流れる回生電流を熱として消費するための抵抗および前記抵抗に流す回生電流を制御するスイッチング素子を含む回生電力消費回路とを備えたインバータの制御方法であって、

前記電流電圧変換部から出力される出力電圧の値を検出するステップと、

前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記抵抗に前記回生電流が流れるように、前記スイッチング素子を動作させるステップと

を含むインバータの制御方法。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び前記下アームのうち少なくとも一方が、請求項1から5のいずれかに記載の半導体装置であるレグと、前記レグと並列に接続された平滑コンデンサと、前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部とを備えたインバータの制御方法であって、

前記電流電圧変換部から出力される出力電圧の値を検出するステップと、

前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にするステップと

を含むインバータの制御方法。 - 前記第2の炭化珪素半導体層の前記他の少なくとも一部は、アンドープ層である、請求項1記載の半導体装置。

- 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、

メイン領域およびセンス領域を含む第1導電型の半導体基板と、

前記第1導電型の半導体基板の前記メイン領域および前記センス領域にそれぞれ設けられており、金属−絶縁体−半導体電界効果トランジスタを有する複数の単位セルであって、前記センス領域に含まれる単位セルの数は、前記メイン領域に含まれる単位セルの数よりも小さく、前記メイン領域および前記センス領域のそれぞれにおいて、前記金属−絶縁体−半導体電界効果トランジスタが並列に接続された複数の単位セルと、

前記半導体基板の主面側に配置されたゲートパッドと

互いに絶縁された第1のソースパッドおよび第2のソースパッドと、

前記半導体基板の裏面側に配置されたドレインパッドと、

を備え、

各金属−絶縁体−半導体電界効果トランジスタは、

前記半導体基板の主面上に位置する第1導電型の第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に接する第2導電型のボディ領域と、

前記ボディ領域に接する第1導電型のソース領域と、

前記第1の炭化珪素半導体層上でかつ前記ボディ領域及び前記ソース領域の少なくとも一部に接して配置された第2の炭化珪素半導体層と、

前記第2の炭化珪素半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、

前記ソース領域に接触するソース電極と、

前記半導体基板の裏面側に配置されたドレイン電極と

を含み、

前記ソース電極の電位を基準とする前記ドレイン電極の電位をVds、

前記ソース電極の電位を基準とする前記ゲート電極の電位をVgs、

前記金属−絶縁体−半導体電界効果トランジスタのゲート閾値電圧をVthとすると、

前記Vdsが正の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記Vgsが前記Vth以上のとき、前記ドレイン電極から前記ソース電極へ電流を流し、

前記Vdsが負の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記VgsがVth未満のとき、前記ソース電極から前記ドレイン電極へ電流を流すダイオードとして機能し、

前記ダイオードの立ち上がり電圧の絶対値は、前記ボディ領域と前記第1の炭化珪素半導体層とにより構成されるボディダイオードの立ち上がり電圧の絶対値よりも小さく、

前記メイン領域に含まれる前記単位セルにおける前記ゲート電極及び前記センス領域に含まれる前記単位セルにおける前記ゲート電極は、前記ゲートパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ドレイン電極及び前記センス領域に含まれる前記単位セルにおける前記ドレイン電極は、前記ドレインパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ソース電極は、前記第1のソースパッドに電気的に接続され、

前記センス領域に含まれる前記単位セルにおける前記ソース電極は、前記第2のソースパッドに電気的に接続されており、

前記第2の炭化珪素半導体層の少なくとも一部は第1導電型の層である、半導体装置であるレグと、

前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部と、

前記電流電圧変換部から出力される前記電圧に基づいて、前記半導体装置の前記ゲートパッドに印加する電圧を制御するゲート電圧制御部と

前記レグと並列に接続された平滑コンデンサと、

前記平滑コンデンサの電圧を検出する電圧検出部と

を備え、

前記ゲート電圧制御部は、前記電圧検出部により検出された前記平滑コンデンサの電圧と、基準電圧値とを比較し、前記平滑コンデンサの電圧が前記基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にする、インバータ。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、

メイン領域およびセンス領域を含む第1導電型の半導体基板と、

前記第1導電型の半導体基板の前記メイン領域および前記センス領域にそれぞれ設けられており、金属−絶縁体−半導体電界効果トランジスタを有する複数の単位セルであって、前記センス領域に含まれる単位セルの数は、前記メイン領域に含まれる単位セルの数よりも小さく、前記メイン領域および前記センス領域のそれぞれにおいて、前記金属−絶縁体−半導体電界効果トランジスタが並列に接続された複数の単位セルと、

前記半導体基板の主面側に配置されたゲートパッドと

互いに絶縁された第1のソースパッドおよび第2のソースパッドと、

前記半導体基板の裏面側に配置されたドレインパッドと、

を備え、

各金属−絶縁体−半導体電界効果トランジスタは、

前記半導体基板の主面上に位置する第1導電型の第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に接する第2導電型のボディ領域と、

前記ボディ領域に接する第1導電型のソース領域と、

前記第1の炭化珪素半導体層上でかつ前記ボディ領域及び前記ソース領域の少なくとも一部に接して配置された第2の炭化珪素半導体層と、

前記第2の炭化珪素半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、

前記ソース領域に接触するソース電極と、

前記半導体基板の裏面側に配置されたドレイン電極と

を含み、

前記ソース電極の電位を基準とする前記ドレイン電極の電位をVds、

前記ソース電極の電位を基準とする前記ゲート電極の電位をVgs、

前記金属−絶縁体−半導体電界効果トランジスタのゲート閾値電圧をVthとすると、

前記Vdsが正の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記Vgsが前記Vth以上のとき、前記ドレイン電極から前記ソース電極へ電流を流し、

前記Vdsが負の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記VgsがVth未満のとき、前記ソース電極から前記ドレイン電極へ電流を流すダイオードとして機能し、

前記ダイオードの立ち上がり電圧の絶対値は、前記ボディ領域と前記第1の炭化珪素半導体層とにより構成されるボディダイオードの立ち上がり電圧の絶対値よりも小さく、

前記メイン領域に含まれる前記単位セルにおける前記ゲート電極及び前記センス領域に含まれる前記単位セルにおける前記ゲート電極は、前記ゲートパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ドレイン電極及び前記センス領域に含まれる前記単位セルにおける前記ドレイン電極は、前記ドレインパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ソース電極は、前記第1のソースパッドに電気的に接続され、

前記センス領域に含まれる前記単位セルにおける前記ソース電極は、前記第2のソースパッドに電気的に接続されており、

前記第2の炭化珪素半導体層の少なくとも一部は第1導電型の層である、半導体装置であるレグと、

前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部と、

前記電流電圧変換部から出力される前記電圧に基づいて、前記半導体装置の前記ゲートパッドに印加する電圧を制御するゲート電圧制御部と

前記レグと並列に接続された平滑コンデンサと、

を備え、

前記ゲート電圧制御部は、前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にする、インバータ。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、

メイン領域およびセンス領域を含む第1導電型の半導体基板と、

前記第1導電型の半導体基板の前記メイン領域および前記センス領域にそれぞれ設けられており、金属−絶縁体−半導体電界効果トランジスタを有する複数の単位セルであって、前記センス領域に含まれる単位セルの数は、前記メイン領域に含まれる単位セルの数よりも小さく、前記メイン領域および前記センス領域のそれぞれにおいて、前記金属−絶縁体−半導体電界効果トランジスタが並列に接続された複数の単位セルと、

前記半導体基板の主面側に配置されたゲートパッドと

互いに絶縁された第1のソースパッドおよび第2のソースパッドと、

前記半導体基板の裏面側に配置されたドレインパッドと、

を備え、

各金属−絶縁体−半導体電界効果トランジスタは、

前記半導体基板の主面上に位置する第1導電型の第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に接する第2導電型のボディ領域と、

前記ボディ領域に接する第1導電型のソース領域と、

前記第1の炭化珪素半導体層上でかつ前記ボディ領域及び前記ソース領域の少なくとも一部に接して配置された第2の炭化珪素半導体層と、

前記第2の炭化珪素半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、

前記ソース領域に接触するソース電極と、

前記半導体基板の裏面側に配置されたドレイン電極と

を含み、

前記ソース電極の電位を基準とする前記ドレイン電極の電位をVds、

前記ソース電極の電位を基準とする前記ゲート電極の電位をVgs、

前記金属−絶縁体−半導体電界効果トランジスタのゲート閾値電圧をVthとすると、

前記Vdsが正の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記Vgsが前記Vth以上のとき、前記ドレイン電極から前記ソース電極へ電流を流し、

前記Vdsが負の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記VgsがVth未満のとき、前記ソース電極から前記ドレイン電極へ電流を流すダイオードとして機能し、

前記ダイオードの立ち上がり電圧の絶対値は、前記ボディ領域と前記第1の炭化珪素半導体層とにより構成されるボディダイオードの立ち上がり電圧の絶対値よりも小さく、

前記メイン領域に含まれる前記単位セルにおける前記ゲート電極及び前記センス領域に含まれる前記単位セルにおける前記ゲート電極は、前記ゲートパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ドレイン電極及び前記センス領域に含まれる前記単位セルにおける前記ドレイン電極は、前記ドレインパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ソース電極は、前記第1のソースパッドに電気的に接続され、

前記センス領域に含まれる前記単位セルにおける前記ソース電極は、前記第2のソースパッドに電気的に接続されており、

前記第2の炭化珪素半導体層の少なくとも一部は第1導電型の層である、半導体装置であるレグと、前記レグと並列に接続された平滑コンデンサとを備えたインバータの制御方法であって、

前記平滑コンデンサの電圧を検出するステップと、

前記平滑コンデンサの電圧と、基準電圧値とを比較し、前記平滑コンデンサの電圧が前記基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にするステップと、

を含むインバータの制御方法。 - 上アーム及び下アームにより構成されるレグであって、前記上アーム及び下アームのうち少なくとも一方が、

メイン領域およびセンス領域を含む第1導電型の半導体基板と、

前記第1導電型の半導体基板の前記メイン領域および前記センス領域にそれぞれ設けられており、金属−絶縁体−半導体電界効果トランジスタを有する複数の単位セルであって、前記センス領域に含まれる単位セルの数は、前記メイン領域に含まれる単位セルの数よりも小さく、前記メイン領域および前記センス領域のそれぞれにおいて、前記金属−絶縁体−半導体電界効果トランジスタが並列に接続された複数の単位セルと、

前記半導体基板の主面側に配置されたゲートパッドと

互いに絶縁された第1のソースパッドおよび第2のソースパッドと、

前記半導体基板の裏面側に配置されたドレインパッドと、

を備え、

各金属−絶縁体−半導体電界効果トランジスタは、

前記半導体基板の主面上に位置する第1導電型の第1の炭化珪素半導体層と、

前記第1の炭化珪素半導体層に接する第2導電型のボディ領域と、

前記ボディ領域に接する第1導電型のソース領域と、

前記第1の炭化珪素半導体層上でかつ前記ボディ領域及び前記ソース領域の少なくとも一部に接して配置された第2の炭化珪素半導体層と、

前記第2の炭化珪素半導体層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極と、

前記ソース領域に接触するソース電極と、

前記半導体基板の裏面側に配置されたドレイン電極と

を含み、

前記ソース電極の電位を基準とする前記ドレイン電極の電位をVds、

前記ソース電極の電位を基準とする前記ゲート電極の電位をVgs、

前記金属−絶縁体−半導体電界効果トランジスタのゲート閾値電圧をVthとすると、

前記Vdsが正の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記Vgsが前記Vth以上のとき、前記ドレイン電極から前記ソース電極へ電流を流し、

前記Vdsが負の場合、前記金属−絶縁体−半導体電界効果トランジスタは、前記VgsがVth未満のとき、前記ソース電極から前記ドレイン電極へ電流を流すダイオードとして機能し、

前記ダイオードの立ち上がり電圧の絶対値は、前記ボディ領域と前記第1の炭化珪素半導体層とにより構成されるボディダイオードの立ち上がり電圧の絶対値よりも小さく、

前記メイン領域に含まれる前記単位セルにおける前記ゲート電極及び前記センス領域に含まれる前記単位セルにおける前記ゲート電極は、前記ゲートパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ドレイン電極及び前記センス領域に含まれる前記単位セルにおける前記ドレイン電極は、前記ドレインパッドに電気的に接続され、

前記メイン領域に含まれる前記単位セルにおける前記ソース電極は、前記第1のソースパッドに電気的に接続され、

前記センス領域に含まれる前記単位セルにおける前記ソース電極は、前記第2のソースパッドに電気的に接続されており、

前記第2の炭化珪素半導体層の少なくとも一部は第1導電型の層である、半導体装置であるレグと、前記レグと並列に接続された平滑コンデンサと、前記半導体装置の前記第2のソースパッドに接続され、前記ドレインパッドと前記第2のソースパッドとの間に流れる電流の値に対応した値の電圧を出力する電流電圧変換部とを備えたインバータの制御方法であって、

前記電流電圧変換部から出力される出力電圧の値を検出するステップと、

前記電流電圧変換部から出力される出力電圧の値と、逆方向基準電圧値とを比較し、前記出力電圧の絶対値が前記逆方向基準電圧値を超えた場合、前記ゲートパッドに印加する電圧を負にするステップと

を含むインバータの制御方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013144245 | 2013-07-10 | ||

| JP2013144245 | 2013-07-10 | ||

| PCT/JP2014/003561 WO2015004891A1 (ja) | 2013-07-10 | 2014-07-04 | 半導体装置、及びそれを用いたインバータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP5979570B2 true JP5979570B2 (ja) | 2016-08-24 |

| JPWO2015004891A1 JPWO2015004891A1 (ja) | 2017-03-02 |

Family

ID=52279597

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015526160A Expired - Fee Related JP5979570B2 (ja) | 2013-07-10 | 2014-07-04 | 半導体装置、及びそれを用いたインバータ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9543858B2 (ja) |

| JP (1) | JP5979570B2 (ja) |

| CN (1) | CN104781923B (ja) |

| WO (1) | WO2015004891A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11276757B2 (en) | 2017-12-14 | 2022-03-15 | Fuji Electric Co., Ltd. | Silicon carbide semiconductor device and method of manufacturing the same |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6432412B2 (ja) * | 2015-03-25 | 2018-12-05 | 株式会社デンソー | スイッチング素子の駆動装置 |

| JP2017069412A (ja) * | 2015-09-30 | 2017-04-06 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US9866245B2 (en) * | 2015-11-18 | 2018-01-09 | Linear Technology Corporation | Active differential resistors with reduced noise |

| US10705123B2 (en) * | 2015-12-18 | 2020-07-07 | Rohm Co., Ltd. | SiC semiconductor device with current sensing capability |

| TWI571025B (zh) * | 2016-01-21 | 2017-02-11 | 旺玖科技股份有限公司 | 負電壓保護系統 |

| JP6805620B2 (ja) * | 2016-08-10 | 2020-12-23 | 富士電機株式会社 | 半導体装置 |

| JP6653461B2 (ja) * | 2016-09-01 | 2020-02-26 | パナソニックIpマネジメント株式会社 | 半導体装置 |

| US10403623B2 (en) | 2017-07-06 | 2019-09-03 | General Electric Company | Gate networks having positive temperature coefficients of resistance (PTC) for semiconductor power conversion devices |

| JP7030734B2 (ja) | 2019-03-04 | 2022-03-07 | 株式会社日立製作所 | 半導体装置 |

| JP7342408B2 (ja) * | 2019-04-15 | 2023-09-12 | 富士電機株式会社 | 半導体装置 |

| CN112234030B (zh) * | 2019-07-15 | 2023-07-21 | 珠海格力电器股份有限公司 | 一种三相逆变功率芯片及其制备方法 |

| US11476084B2 (en) * | 2019-09-10 | 2022-10-18 | Applied Materials, Inc. | Apparatus and techniques for ion energy measurement in pulsed ion beams |

| WO2022210033A1 (ja) * | 2021-03-31 | 2022-10-06 | ローム株式会社 | 半導体装置 |

| DE102021129145A1 (de) | 2021-11-09 | 2023-05-11 | Audi Aktiengesellschaft | Verfahren zum aktiven Entladen eines elektrischen Energiespeichers, Steuereinrichtung, elektrische Schaltungseinrichtung und Kraftfahrzeug |

| CN119421460B (zh) * | 2025-01-07 | 2025-04-11 | 芯联集成电路制造股份有限公司 | 半导体器件及其制造方法 |

Family Cites Families (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2737211B2 (ja) * | 1989-03-08 | 1998-04-08 | 松下電器産業株式会社 | 三相交流電動機の可変速駆動装置 |

| JP3215164B2 (ja) | 1992-06-19 | 2001-10-02 | 東洋電機製造株式会社 | 電圧形インバータ装置 |

| KR950022023A (ko) | 1993-12-09 | 1995-07-26 | 김무 | 전동기 발전 제동 제어장치 |

| JPH0866056A (ja) * | 1994-08-24 | 1996-03-08 | Mitsubishi Electric Corp | インバータ装置 |

| JP3481813B2 (ja) | 1997-02-28 | 2003-12-22 | Nec化合物デバイス株式会社 | 半導体装置 |

| JP3357627B2 (ja) * | 1999-04-09 | 2002-12-16 | 株式会社三社電機製作所 | アーク加工装置用電源装置 |

| JP3635988B2 (ja) | 1999-05-27 | 2005-04-06 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP3484133B2 (ja) * | 2000-03-03 | 2004-01-06 | 株式会社日立製作所 | 内燃機関用点火装置および内燃機関点火用1チップ半導体 |

| JP3922038B2 (ja) | 2002-02-14 | 2007-05-30 | 株式会社豊田自動織機 | 電流検出機能付mos型電界効果トランジスタ |

| JP3997126B2 (ja) | 2002-08-29 | 2007-10-24 | 株式会社ルネサステクノロジ | トレンチゲート型半導体装置 |

| JP4622214B2 (ja) | 2003-07-30 | 2011-02-02 | トヨタ自動車株式会社 | 電流センシング機能を有する半導体装置 |

| JP4001120B2 (ja) * | 2004-02-19 | 2007-10-31 | トヨタ自動車株式会社 | 電圧変換装置 |

| JP4144541B2 (ja) * | 2004-03-19 | 2008-09-03 | 日産自動車株式会社 | 電圧駆動型半導体素子用駆動回路 |

| JP4601044B2 (ja) * | 2004-08-30 | 2010-12-22 | 日立アプライアンス株式会社 | 電力変換装置およびその電力変換装置を備えた空気調和機 |

| JP2007014059A (ja) * | 2005-06-28 | 2007-01-18 | Toyota Motor Corp | スイッチング回路 |

| JP4640200B2 (ja) * | 2006-02-10 | 2011-03-02 | トヨタ自動車株式会社 | 電圧変換装置および電圧変換器の制御方法 |

| KR101120757B1 (ko) * | 2006-06-29 | 2012-03-23 | 미쓰비시덴키 가부시키가이샤 | 회생 제동 장치 |

| JP4905208B2 (ja) * | 2006-10-25 | 2012-03-28 | 株式会社デンソー | 過電流検出回路 |

| JP4924086B2 (ja) * | 2007-02-21 | 2012-04-25 | 三菱電機株式会社 | 半導体装置 |

| JP4506808B2 (ja) | 2007-10-15 | 2010-07-21 | 株式会社デンソー | 半導体装置 |

| DE102008045410B4 (de) * | 2007-09-05 | 2019-07-11 | Denso Corporation | Halbleitervorrichtung mit IGBT mit eingebauter Diode und Halbleitervorrichtung mit DMOS mit eingebauter Diode |

| JP5045733B2 (ja) | 2008-12-24 | 2012-10-10 | 株式会社デンソー | 半導体装置 |

| JP5637175B2 (ja) * | 2008-12-24 | 2014-12-10 | 株式会社デンソー | 半導体装置 |

| JP4877337B2 (ja) * | 2009-02-17 | 2012-02-15 | トヨタ自動車株式会社 | 半導体装置 |

| CN102414818B (zh) * | 2009-04-30 | 2013-03-20 | 松下电器产业株式会社 | 半导体元件、半导体装置及电力变换器 |

| JP5289580B2 (ja) * | 2009-10-20 | 2013-09-11 | 三菱電機株式会社 | 半導体装置 |

| JP5553652B2 (ja) * | 2010-03-18 | 2014-07-16 | ルネサスエレクトロニクス株式会社 | 半導体基板および半導体装置 |

| WO2012029652A1 (ja) * | 2010-09-03 | 2012-03-08 | 三菱電機株式会社 | 半導体装置 |

| JP5724281B2 (ja) * | 2010-10-08 | 2015-05-27 | 富士電機株式会社 | パワー半導体デバイスの電流検出回路 |

| JP5170208B2 (ja) * | 2010-10-22 | 2013-03-27 | 富士電機株式会社 | パワー半導体デバイスの電流検出回路 |

| JP5694119B2 (ja) | 2010-11-25 | 2015-04-01 | 三菱電機株式会社 | 炭化珪素半導体装置 |

| CN103650333B (zh) * | 2011-07-12 | 2016-01-20 | 丰田自动车株式会社 | 车辆和车辆的控制方法 |

| US9112048B2 (en) * | 2011-08-17 | 2015-08-18 | Ramgoss Inc. | Vertical field effect transistor on oxide semiconductor substrate |

| JP5720641B2 (ja) * | 2012-08-21 | 2015-05-20 | 株式会社デンソー | スイッチングモジュール |

| KR101638754B1 (ko) * | 2012-09-06 | 2016-07-11 | 미쓰비시덴키 가부시키가이샤 | 반도체 장치 |

| JP2014138532A (ja) * | 2013-01-18 | 2014-07-28 | Fuji Electric Co Ltd | 電力変換装置 |

-

2014

- 2014-07-04 JP JP2015526160A patent/JP5979570B2/ja not_active Expired - Fee Related

- 2014-07-04 US US14/440,341 patent/US9543858B2/en not_active Expired - Fee Related

- 2014-07-04 WO PCT/JP2014/003561 patent/WO2015004891A1/ja not_active Ceased

- 2014-07-04 CN CN201480002917.3A patent/CN104781923B/zh not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11276757B2 (en) | 2017-12-14 | 2022-03-15 | Fuji Electric Co., Ltd. | Silicon carbide semiconductor device and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2015004891A1 (ja) | 2015-01-15 |

| US20150280611A1 (en) | 2015-10-01 |

| JPWO2015004891A1 (ja) | 2017-03-02 |

| US9543858B2 (en) | 2017-01-10 |

| CN104781923B (zh) | 2017-06-16 |

| CN104781923A (zh) | 2015-07-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5979570B2 (ja) | 半導体装置、及びそれを用いたインバータ | |

| JP6498363B2 (ja) | 炭化珪素半導体装置および電力変換装置 | |

| CN106463541B (zh) | 碳化硅半导体装置 | |

| US8785931B2 (en) | Semiconductor device | |

| JP4955128B2 (ja) | 半導体素子、半導体装置および電力変換器 | |

| US9450084B2 (en) | Wide band gap semiconductor device | |

| US20120057386A1 (en) | Semiconductor element, semiconductor device, and power converter | |

| JPWO2017208734A1 (ja) | 半導体装置 | |

| US20230139229A1 (en) | Semiconductor device and power converter | |

| JP2019161181A (ja) | 半導体装置、パワーモジュールおよび電力変換装置 | |

| JP6145165B2 (ja) | 半導体装置 | |

| CN116325176B (zh) | 碳化硅半导体装置以及电力变换装置 | |

| CN101986428B (zh) | 功率半导体部件、包括其的功率半导体组件及其操作方法 | |

| JP2022094415A (ja) | 炭化珪素からなるトレンチゲート構造の縦型mosfet | |

| CN114342089B (zh) | 碳化硅半导体装置以及电力变换装置 | |

| JP2012104856A (ja) | 半導体素子、半導体装置および電力変換器 | |

| JP2012079945A (ja) | 半導体装置 | |

| US20240355922A1 (en) | Semiconductor device, power conversion apparatus, and method of manufacturing semiconductor device | |

| US20210050458A1 (en) | Semiconductor power device and method for manufacture | |

| JP2018049912A (ja) | 半導体装置および電力変換装置 | |

| JP4918626B2 (ja) | 半導体素子、半導体装置および電力変換器 | |

| JP7113386B2 (ja) | 半導体装置 | |

| EP3996137B1 (en) | Semiconductor device | |

| CN219303673U (zh) | 单向高电压穿通瞬态电压抑制器件 | |

| JP6750589B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150507 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160314 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160705 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160715 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5979570 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |