我々は、ISFETの大きなアレイを特に構成し、それを使用して、DNA合成を含めた化学的プロセスの変化のモニタリングに基づいてDNA配列決定技術を促進することができるのを認識し、認めた。より一般的には、出願人らは、化学的に感受性のFET(すなわち、chemFET)の大きなアレイを使用して、価値ある情報をそのような分析物測定に基づいて得ることができる、化学的および/または生物学的プロセス(例えば、生物学的または化学的反応、細胞または組織の培養、またはモニタリング、神経活性、核酸配列決定等)の宿主において、種々の分析物(例えば、水素イオン、他のイオン、非イオン性分子または化合物等)の静的および/または動的濃度/レベルを検出し、測定することができるのを認識し、認めた。

従って、本開示の種々の実施形態は、一般に、1以上の分析物を測定するための大規模なFETアレイに関する発明的方法および装置に向けられる。本明細書中に開示される種々の実施形態において、FETアレイは、化学センサーとして作用する多数のchemFETを含む。先に議論したISFETは、イオン検出のために構成されたchemFET、および本明細書中に開示される種々の実施形態で使用することができるISFETの特別なタイプである。本開示によって考えられるchemFETの他のタイプは、酵素を使用して分析物を検出する酵素FET(EnFET)を含む。しかしながら、本開示はISFETおよびEnFETに限定されず、より一般的には、化学的感度のいくつかのタイプについて構成されるいずれのFETにも関することを認識されたい。本明細書中で用いるように、化学的感度は、広く、限定されるものではないが、有機、無機、天然に生じる、天然に生じない、および合成の、イオン、小分子のような化学的および生物学的化合物、核酸、蛋白質、ペプチド、多糖等のようなポリマーを含めた、注目するいずれの分子に対する感度も含む。

なお他の実施形態によると、本開示は、一般に、化学的または生物学的試料の分析における前記した大規模なchemFETアレイの使用に関する発明的方法および装置に向けられる。これらの試料は、分析物(例えば、イオンまたは他の成分)の存在、分析物に関する濃度または他の測定の高速の高密度決定を容易とするために、典型的には液体であり(または液体に溶解させ)および小さな容量のものである。

例えば、いくつかの実施形態は、「非常に大規模な」二次元のchemFETセンサーアレイ(例えば、256を超えるセンサー)に向けられ、ここに、そのようなアレイのセンサーを構成する1以上のchemFET−含有エレメントまたは「画素」は、アレイの画素に近接して起こる、1以上の独立した生物学的または化学的反応または事象をモニターするように構成される。いくつかの例示的な実施において、アレイは、アレイの個々のセンサーまたはセンサーのグループ上に1以上の反応チャンバー、または「ウェル」または「マイクロウェル」を形成する1以上のミクロ流体構造、および分析物試料(すなわち、分析物溶液)をウェルに送達し、それらを、測定の間にウェルから除去する装置にカップリングされていてよい。例えマイクロウェルが使用されない場合であっても、センサーアレイは、1以上の分析物の画素への送達のための、および測定の間における分析物の除去のための1以上のミクロ流体構造にカップリングされていてよい。従って、以下により詳細に議論されるように、保護するのが望まれる本開示の発明的態様は、分析物および、適切には、例えば、分析物の検出および測定で有用な他の試薬をウェルまたは画素へ、およびウェルまたは画素から流動させるのに使用することができる種々のミクロ流体構造、ウェルのアレイの製造方法、アレイ化されたウェルをアレイ化された画素とカップリングさせるための方法および構造、および例えば、装置をDNA配列決定または関連分析に用いる場合に、ウェルにDNA担持ビーズを負荷(loading)することを含めた、ウェルに分析すべき試料を負荷するための方法および装置を含む。

ミクロ流体に関しては、ユニークな参照電極およびフローセルへのそれらのカップリングも示される。

本発明の種々の態様において、特に注目する分析物は核酸合成の副産物である。そのような副産物は配列決定×合成方法の読出としてモニターすることができる。1つの特に重要な副産物は、(本明細書中においては、dNTPとも言われる)デオキシヌクレオチド三リン酸の、(配列決定プライマーのような)核酸の3’末端への負荷(または取込み)に際して放出される無機ピロホスフェート(PPi)である。PPiは水の存在下で(所望により、かつピロホスファターゼの存在下においてはかなりより迅速に)、オルトホスフェート(Pi)および遊離水素イオン(H+)に加水分解され得る。その結果、ヌクレオチドの取込み、またかくして、配列決定×合成反応を、PPi、Piおよび/またはH+を検出することによってモニターすることができる。慣用的にはPPiはchemFETによって検出されたり測定されたりしなかった。光学的ベースの配列決定×合成方法は、アデノシン三リン酸(ATP)へのそのスルフリラーゼ媒介変換、次いで、光の同時放出を伴う、従前に生じたATPの存在下でのルシフェリンのオキシルシフェリンへのルシフェラーゼ−媒介変換を介して、PPiを検出してきた。そのような検出は、本明細書中においては、PPiの「酵素的」検出という。本発明は、非酵素的方法を用いてPPiを検出する方法を提供する。本明細書中で用いる場合、PPiの非酵素的検出は、第一の場合においてPPiを生じさせ、または放出するのに必要ないずれかの酵素(例えば、ポリメラーゼ)以外の酵素を必要としないPPiの検出である。PPiの非酵素的検出の一例は、PPiのATPへの変換を必要としない検出方法である。

H+は、標準pHメーターを用い、あるいはいくつかの場合においては、ISFETを用いてpH変化を測定することによって検出されてきた。重要な事には、ISFETを用いてヌクレオチド取込を検出する全てではないが多くの先行する試みはpH変化のみに焦点を当てており、放出されたPPiの検出または測定には焦点を当てていなかった。

本発明では、PPi(またはPi)特異的受容体、取り込まれていないdNTP、またはそのいくつかの組合せの不存在下または存在下でH+(またはpHの変化)、PPi(またはPi)を検出することによって、核酸配列決定反応をモニタリングし、かくして、核酸のヌクレオチド配列を決定するための方法が考えられ、かくして、それを提供する。従って、いくつかの態様はpHモニタリングを狙っており、他方、他の態様は、FET表面と接触した溶液中のイオン種の変化から得られるそのような表面におけるイオンパルスをモニタリングし(および検出する)ことを狙っている。

かくして、本発明の種々の態様は、ヌクレオチドの核酸への取込みのインジケーターとして放出されたPPiを直接的に検出するための方法および装置を提供する。本発明は、本明細書中に記載されたchemFETアレイの使用を介してそれを行う。いくつかの実施形態において、核酸合成反応は、chemFETと接触している溶液中で行われ、放出されたPPiはchemFET表面によって検出され(または検知される)。重要な事には、PPiを直接的に検出する本発明のchemFETの能力を仮定すれば、そのような合成および/または配列決定反応を行うことができ、いくつかの例においては、実質的にpH感受性である環境(すなわち、pHの変化が、例えば、環境の強力な緩衝能力のため検出されない環境)において好ましくは行われる。

他の実施形態において、注目する分析物は水素イオンであって、本開示による大規模なISFETアレイは、具体的にはH+濃度の変化(すなわち、pHの変化)を測定するように構成される。

他の実施形態において、他の生物学的または化学的反応をモニターすることができ、chemFETアレイは、具体的には、水素イオンおよび/または注目する特定の生物学的または化学的プロセスの出現および/または進行に関連する重要な情報を提供する1以上の他の分析物を測定するように構成することができる。

種々の態様において、chemFETアレイは慣用的なCMOS(またはbiCMOSまたは他の適当な)加工技術を用いて製造することができ、特に、(対応する画素出力シグナルを得るために画素の全てをスキャニングする)全アレイからのデータの迅速な獲得を容易とするように構成される。

分析物の検出および測定に関しては、以下により詳細に議論される種々の実施形態において、本開示に従ったchemFETアレイによって測定された1以上の分析物は、生物学的または化学的プロセスに関する関連情報(例えば、核酸の相互に対するハイブリダイゼーション、抗原−抗体結合、受容体−リガンド結合、酵素−阻害剤結合、酵素−基板結合等のような結合事象)を供する種々の生物学的または化学的物質のいずれかを含むことができるのを認めるべきである。いくつかの態様において、分析物の存在または不存在を単に決定することに加えて、1以上の分析物の絶対的または相対的ならびに静的および/または動的レベルおよび/または濃度を測定する能力は、生物学的および化学的プロセスに関連する価値ある情報を提供する。他の態様において、注目する分析物または複数分析物の存在または不存在の単なる決定は、十分であり得る価値ある情報を提供することができる。

本開示の種々の発明的実施形態によるchemFETアレイは、種々の分析物のいずれかの1以上に対する感度のために構成することができる。1つの実施形態において、アレイの1以上のchemFETは、1以上の分析物に対する感度のために特に構成することができ、他の実施形態においては、所与のアレイの異なるchemFETは異なる分析物に対する感度のために構成することができる。例えば、1つの実施形態において、アレイの1以上のセンサー(画素)は、第1の分析物に対して感受性であるように構成された第1のタイプのchemFETを含むことができ、およびアレイの1以上の他のセンサーは、第1の分析物とは異なる第2の分析物に対して感受性であるように構成されたchemFETの第2のタイプを含むことができる。1つの実施形態において、第1および第2の分析物は相互に関連していてもよい。例として、第1および第2の分析物は、同一の生物学的または化学的反応/プロセスの副産物であってよく、従って、それらは同時に検出して、反応の出現(またはその欠如)を確認することができる。そのような冗長性は、好ましくは、いくつかの分析物検出方法にある。もちろん、chemFETの2を超える異なるタイプを、いずれかの所与のアレイで使用して、分析物の異なるタイプを検出し、および/または測定し、および所望により、結合事象のような生物学的または化学的プロセスをモニターすることができるのは認識すべきである。一般に、所与のセンサーアレイは「均一」であり、従って、同一分析物(例えば、pHまたは他のイオン濃度)を検出するおよび/または測定する実質的に同様または同一のタイプのchemFETよりなることができ、あるいはセンサーアレイは「不均一」であり、異なる分析物を検出し、および/または測定するための異なるタイプのchemFETを含むのは、本明細書中で議論したセンサーアレイの実施形態にいずれにおいても認識されるべきである。もう1つの実施形態において、アレイ中のセンサーは、検出されたおよび/または測定されたそのタイプ(またはクラス)の種がセンサーの間で異なってもよいが、分析物の単一タイプ(またはクラス)を検出しおよび/または測定するように構成することができる。例として、アレイ中の全てのセンサーは、核酸を検出し、および/または測定するように構成することができるが、各センサーは異なる核酸を検出し、および/または測定する。

なお他の態様において、出願人等は、図1〜7との関連において先に議論したMilgrew et al.のISFETアレイ設計、ならびに他の慣用的なISFETアレイ設計を特異的に改良して、画素のサイズを有意に低下させ、それにより、所与の半導体ダイサイズに対するchemFETアレイの画素の数を増加させた(すなわち、画素密度を増加させた)。種々の実施形態において、画素の密度のこの増加は、同時に、モニターされた生物学的および化学的プロセスに対応する出力シグナルのシグナル-対-ノイズ比率(SNR)、およびそのような出力シグナルをアレイから読むことができるスピードを増加させつつ達成される。特に、出願人らは、chemFET直線性についての要件を緩和し、1以上の限定された測定出力シグナル範囲(例えば、1〜14よりはむしろほぼ7〜9以下のpH範囲に対応する出力シグナル、ならびにpHに必ずしも有意に関連しない出力シグナル)に焦点を当てることによって、個々の画素の複雑性およびサイズを有意に低下させ、それにより、非常に大規模な密なchemFETアレイの実現を促進することができるのを認識し、認めた。また、出願人らは、chemFETアレイにおける画素選択に対する別のより複雑でないアプローチ(例えば、その複雑性はアレイのサイズと共に倍率変更する、図7に示された、Milgrew et al.の設計で使用される行および列デコーダーアプローチに対する代替法)、ならびにISFET応答モデリングおよびそのようなモデリングに基づくデータ外挿を含む種々のデータ処理技術は、有意に大きくかつ密なアレイからのデータの迅速な獲得を促進することも認識し、認めた。

chemFETアレイ製造に関しては、出願人らは、さらに、慣用的CMOS製造プロセスで使用される種々の技術、ならびに種々のポスト製造処理工程(ウエハ−の取扱い、洗浄、ダイシング、パッケージング等)は、いくつかの例においては得られたchemFETアレイの性能に悪影響し得るのを認識し、認めた。例えば、再度、図1を参照し、1つの潜在的問題点は、フローティングゲート構造70に関連する金属のエッチングの間にゲート酸化物65において誘導できるトラップされた電荷、およびどのようにしてそのようにトラップされた電荷がchemFET閾値電圧VTHに影響し得るかに関する。もう1つの潜在的問題点は、アルミニウム金属ベースのCMOS製造で通常使用される低温材料蒸着プロセスに由来する、chemFET不動態化層の密度/多孔度に関する(例えば、図1におけるISFET不動態化層72参照)。そのような低温プロセスは、一般に、慣用的なCMOSデバイスのための適切な不動態化層を供するが、その結果、分析物溶液と接触したchemFETについては潜在的に問題であり得る幾分低密度かつ多孔性の不動態化層をもたらしかねず;特に、低密度多孔性不動態化層は、経時的に、溶液中の分析物または他の物質を吸収しかねず、かつそれに飽和しかねず、これは、今度は、chemFET閾値電圧VTHにおいて望ましくない時間変化ドリフトを引き起こしかねない。この現象は、今度は、注目する1以上の特定の分析物の正確な測定を妨げるであろう。これまでの事を考慮すると、本明細書中で開示された他の発明的実施形態は、chemFETアレイの製造および製造後処理/取扱の種々の態様から生起し得るchemFETの性能に対する潜在的に有害な効果を緩和する方法および装置に関する。

従って、本発明の1つの実施形態は、CMOS製造されたセンサーのアレイを含む装置に向けられ、各センサーは1つの化学的に感受性の電界効果トランジスタ(chemFET)を含み、10μm2以下のアレイの表面の面積を占有する。

もう1つの実施形態は、エレクトロニクスセンサーの少なくとも512の行および少なくとも512の列を含めたエレクトロニクスセンサーの二次元アレイを含むセンサーアレイに向けられ、各センサーは、二次元アレイの表面に近接する分析物の存在および/または濃度を表す少なくとも1つの出力シグナルを供するように構成された1つの化学的に感受性の電界効果トランジスタ(chemFET)を含む。

もう1つの実施形態は、CMOS製造されたセンサーのアレイを含む装置に向けられ、各センサーは1つの化学的に感受性の電界効果トランジスタ(chemFET)を含む。CMOS−製造センサーのアレイは、256を超えるセンサーを含み、および該アレイの全てのchemFETからのchemFET出力シグナルのコレクションはデータのフレームを構成する。該装置は、さらに、該アレイにカップリングされ、かつ少なくとも1つのアレイ出力シグナルを生じさせて、秒当たり少なくとも1つのフレームのフレーム速度にて該アレイからのデータの多数のフレームを提供するように構成された制御回路を含む。1つの態様において、フレーム速度は秒当たり少なくとも10のフレームであってよい。もう1つの態様において、フレーム速度は秒当たり少なくとも20のフレームであってよい。なお他の態様において、フレーム速度は秒当たり少なくとも30、40、50、70フレーム、または100フレームまでであってよい。

もう1つの実施形態は、CMOS製造されたセンサーのアレイを含む装置に向けられ、各センサーは化学的に感受性の電界効果トランジスタ(chemFET)を含む。chemFETはフローティングゲート構造、および第1の半導体タイプを有し、かつ第2の半導体タイプを有する領域に製造されたソースおよびドレインを含み、ここに、第2の半導体タイプを有する領域をソースまたはドレインいずれかに電気的に結合させる導電体はない。

もう1つの実施形態は、エレクトロニクスセンサーのアレイを含む装置に向けられ、各センサーは、1つの化学的に感受性の電界効果トランジスタ(chemFET)を含めた3つの電界効果トランジスタ(FET)よりなる。

もう1つの実施形態は、エレクトロニクスセンサーのアレイを含む装置に向けられ、各センサーは3以下の電界効果トランジスタ(FET)を含み、ここに、3以下のFETは1つの化学的に感受性の電界効果トランジスタ(chemFET)を含む。

もう1つの実施形態はエレクトロニクスセンサーのアレイを含む装置に向けられ、各センサーは、1つの化学的に感受性の電界効果トランジスタ(chemFET)を含めた複数の電界効果トランジスタ(FET)、および該複数のFETに電気的に結合した複数の導電体を含み、ここに、該複数のFETは、該複数の導電体が、アレイの各センサーおよび相互結合する多数のセンサーによって占められるエリアを移動する4以下の導電体を含むように構成される。

もう1つの実施形態はCMOS製造されたセンサーのアレイを含む装置に向けられ、各センサーは1つの化学的に感受性の電界効果トランジスタ(chemFET)を含めた複数の電界効果トランジスタ(FET)を含み、ここに、各センサーにおけるFETの全ては同一のチャネルタイプのものであって、アレイ基板の単一半導体領域で実施される。

もう1つの実施形態は、複数の行および複数の列に配置された複数のエレクトロニクスセンサーを含むセンサーアレイに向けられる。各センサーは、アレイの表面に近接する分析物の存在および/または濃度を表す少なくとも1つ、ある場合には、少なくとも2つの出力シグナルを供するように構成された1つの化学的に感受性の電界効果トランジスタ(chemFET)を含む。複数の列の各列については、アレイは、さらに、列における各chemFETに対する一定のドレイン電流および一定のドレイン-対-ソース電圧を供するように構成された列回路を含み、該列回路は、2つの操作増幅器および各chemFETを持つケルビンブリッジ構成に配置されたダイオード−連結FETを含んで、一定のドレイン−対−ソース電圧を供す。

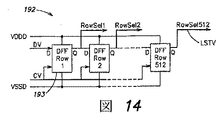

もう1つの実施形態は、複数の行および複数の列に配置された複数のエレクトロニクスセンサーを含むセンサーアレイに向けられる。各センサーは、アレイの表面に近接した溶液中のイオンの濃度を表す少なくとも1つの出力シグナル、ある例においては、少なくとも2つの出力シグナルを供するように構成された1つの化学的に感受性の電界効果トランジスタ(chemFET)を含む。アレイは、さらに、複数の行の各行を可能とするための少なくとも1つの行選択シフトレジスタ、および複数の列の各列からのchemFET出力シグナルを獲得するための少なくとも1つの列選択シフトレジスタを含む。

もう1つの実施形態は、CMOS製造されたセンサーのアレイを含む装置に向けられ、各センサーは化学的に感受性の電界効果トランジスタ(chemFET)を含む。chemFETはフローティングゲート構造、および第1の半導体タイプを有し、かつ第2の半導体タイプを有する領域に製造されたソースおよびドレインを含み、ここに、第2の半導体タイプを有する領域をソースまたはドレインいずれかに電気的に結合させる導電体はない。アレイは、CMOS−製造センサーの少なくとも512の行および少なくとも512の列の2次元アレイを含む。各センサーは、chemFETを含めた3つの電界効果トランジスタ(FET)よりなり、各センサーは3つのFETに電気的に結合した複数の導電体を含む。3つのFETは、複数の導電体が、各センサーによって占有されるエリアを移動し、およびアレイの多数のセンサーを相互に連結する4以下の導電体を含むように配置される。各センサー中のFETの全ては同一のチャネルタイプのものであって、アレイ基板の単一の半導体領域で実施される。アレイの全てのchemFETからのchemFET出力シグナルのコレクションは、データのフレームを構成する。該装置は、さらに、アレイにカップリングされ、かつ少なくとも1つのアレイ出力シグナルを生じさせて、秒当たり少なくとも20フレームのフレーム速度にてアレイからのデータの多数のフレームを供するように構成された制御回路を含む。

もう1つの実施形態は、CMOS製造されたセンサーのアレイを製造する方法に向けられ、各センサーは化学的に感受性の電界効果トランジスタ(chemFET)を含む。該方法は:a)アレイを含めた半導体ウェハーをダイシングして、該アレイを含めた少なくとも1つのダイシングされた部分を形成し;およびb)該少なくとも1つのダイシングされた部分で気体アニール形成を行うことを含む。A)アレイを含めた半導体ウェハーをダイシングして、アレイを含めた少なくとも1つのダイシングされた部分を形成し;次いでB)該少なくとも1つのダイシングされた部分に形成性ガスアニールの形成を行う。

もう1つの実施形態は、chemFETのアレイを製造する方法に向けられる。該方法は:a)アレイを含めた半導体ウェハーをダイシングして、該アレイを含めた少なくとも1つのダイシングされた部分を形成し;およびb)該少なくとも1つのダイシングされた部分で気体アニール形成を行うことを含む。chemFETのアレイを製造し;誘電性材料を該アレイ上に蒸着させ;形成性ガスアニールを、ダイシング工程前に該アレイに適用し;該アレイをダイシングし;次いで、該ダイシング工程後に形成性ガスアニールを適用する。該方法は、さらに、1以上の蒸着工程の間に半導体ウェハーを試験することを含むことができる。

もう1つの実施形態は、CMOS−製造センサーのアレイを加工する方法に向けられる。各センサーは、プラズマ増強化学気相蒸着(PECVD)を介して蒸着された窒化ケイ素および/またはオキシ窒化ケイ素の化学的に感受性の不動態化層を有する化学的に感受性の電界効果トランジスタ(chemFET)を含む。該方法は、不動態化層の多孔度を低下させ、および/または密度を増大させるように、化学的に感受性の不動態化層上に少なくとも1つのさらなる不動態化材料を蒸着することを含む。

本発明の他の態様は、限定されるものではないが、合成方法による配列決定に一体化されるものを含めた核酸合成反応をモニターする方法に関する。かくして、本発明の種々の態様は、核酸合成反応をモニターする方法、核酸へのヌクレオチドの取込を決定し、またはモニターする方法、ヌクレオチド取込の存在または不存在を決定する方法、取り込まれたヌクレオチドの数を決定する方法を提供する。

1つのそのような態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し(例えば、入れるまたは位置させ)、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、ここに、該鋳型核酸の各々は配列決定プライマーにハイブリダイズし(それにより、鋳型/プライマーハイブリッドを形成し)、およびポリメラーゼに結合され、(本明細書中においては上位概念的にdNTPともいう)1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し(または配列決定プライマーを延長(extending)させ)、次いで、該少なくとも1つのchemFETの電圧および/または電流の変化によって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。chemFETの、(およびかくして複数のchemFET)のアレイは少なくとも2、少なくとも3、少なくとも4、少なくとも5、少なくとも6、少なくとも7、少なくとも8、少なくとも9、少なくとも10、少なくとも100、少なくとも200、少なくとも300、少なくとも400、少なくとも500、少なくとも1000、少なくとも104、少なくとも105、少なくとも106、少なくとも107、またはそれ以上のchemFET(当該用語は本明細書中においては相互交換可能に用いられるので、またはchemFETセンサー、または複数センサー)を含むことができる。同様に、複数の反応チャンバーは、少なくとも2、少なくとも3、少なくとも4、少なくとも5、少なくとも6、少なくとも7、少なくとも8、少なくとも9、少なくとも10、少なくとも100、少なくとも200、少なくとも300、少なくとも400、少なくとも500、少なくとも1000、少なくとも104、少なくとも105、少なくとも106、少なくとも107、またはそれ以上の反応チャンバーであってよい。

もう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、該複数の反応チャンバーはchemFETアレイと接触しており、ここに、少なくとも1つのchemFETは各反応チャンバーと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズされ(それにより、鋳型/プライマーハイブリッドを形成し)、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって、新しい核酸ストランドを合成し(または配列決定プライマーを延長し)、次いで、少なくとも1つのchemFETにおける電圧および/または電流の変化によって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、該chemFETアレイはこれまでのアレイのいずれかである。

もう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置させ、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズされ、(それにより、鋳型/プライマーハイブリッドを形成させ)、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって(配列決定プライマーを延長させることによって)新しい核酸ストランドを合成し、次いで、アレイ内の少なくとも1つのchemFETにおける電圧および/または電流の変化によって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、隣接する反応チャンバー間の中心間距離(または「ピッチ」)は1〜10μmである。

もう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、該鋳型核酸の各々は配列決定プライマーにハイブリダイズし(それにより鋳型/プライマーハイブリッドを形成し)、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって(配列決定プライマーを延長することにより)新しい核酸ストランドを合成し、次いで、配列決定反応の副産物の生成によって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、(a)該chemFETアレイは256を超えるセンサーを含み、あるいは(b)隣接する反応チャンバー間の中心間距離は1〜10μmである。重要な実施形態において、配列決定反応副産物はPPiである。

なおもう1つの態様において、本発明は、標的核酸を断片化して(あるいは、例えば、豊富化されたエクソン単離との関係では単離して)、複数の断片化された(または単離された)核酸を生成させ、該複数の断片化された(または単離された)核酸の各々を個々のビーズに付着させて、各々が単一の断片化された(または単離された)核酸に付着された複数のビーズを生成させ、各ビーズ上で断片化された(または単離された)核酸の数を増幅させ、増幅された断片化された(単離された)核酸に付着された複数のビーズを、アレイ中の各センサーについての別々の反応チャンバーを有するchemFETアレイに送達し、ここに、唯1つのビーズが各反応チャンバーに位置しており、次いで、複数の反応チャンバーにおいて同時配列決定反応を行うことを含み、核酸を配列決定する方法を提供する。

本明細書中においてより詳細に記載されるように、配列決定すべき核酸は、次いで、引き続いて断片化される(すなわち、より短い核酸に変換される)より長い核酸から由来することができるか、あるいはそれらは本明細書中で考えられる反応にとって適した長さで単離することができ、かくして、短くする(または断片化する)必要はないであろうことは理解されるべきである。従って、標的核酸を断片化するプロセスというあらゆる態様および本明細書中で議論する限定については、該方法は、断片化の不存在下において標的核酸を単離することによって行うこともできるのは理解されるべきである。

なおもう1つの実施形態において、本発明は、標的核酸を断片化して、複数の断片化された核酸を生成させ、ビーズの存在下で各断片化された核酸を別々に増幅し、断片化された核酸の増幅されたコピーをビーズに結合させ、それにより、各々が複数の同一の断片化された核酸に付着された複数のビーズを生じさせ、各々が複数の同一の断片化された核酸に付着された複数のビーズを、アレイ中の各chemFETセンサーについての別々の反応チャンバーを有するchemFETアレイに送達し、ここに、唯1つのビーズが各反応チャンバー中に位置し、次いで、複数の反応チャンバーにおいて同時配列決定反応を行うことを含む、核酸を配列決定する方法を提供する。

もう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズされ(それにより、鋳型/プライマーハイブリッドを形成し)、およびポリメラーゼに結合されており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって(配列決定プライマーを延長することにより)新しい核酸ストランドを合成し、次いで、1以上の既知のヌクレオチド三リン酸の取込みのインジケーターとして配列決定副産物レベルの変化を検出することを含む、核酸を配列決定する方法を提供する。

レベルの変化は、1以上の既知のヌクレオチド三リン酸の取込みに先立ってのレベルに対するレベルの増加または減少であってよい。レベルの変化は、chemFETセンサーにおける電圧および/または電流の変化、またはpHの変化として読むことができるが、それに限定されるものではない。

もう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込、1以上の既知のヌクレオチド三リン酸の取込みのインジケーターとしてPPiの放出を直接的に検出することを含む、核酸を配列決定する方法を提供する。

もう1つの態様において、本発明は、鋳型核酸を断片化して、複数の断片化された核酸を生成し、該複数の断片化された核酸の各々からの1つのストランドを、個々に、ビーズに付着させて、各々が、それに付着した一本鎖の断片化された核酸を有する複数のビーズを生成させて、それに付着された一本鎖の断片化された核酸を有する複数のビーズを、エリア中の各センサー用の別々の反応チャンバーを有するchemFETアレイに送達し、ここに、唯1つのビーズが各反応チャンバー中に位置し、次いで、複数のチャンバー中で同時配列決定反応を行うことを含む、核酸を配列決定する方法を提供する。

1つの態様において、本発明は、反応チャンバーおよびchemFETのそのようなアセンブリの少なくとも3(および数百万まで)を含むアレイ中にて、chemFETと接触した反応チャンバー中の複数の同一鋳型核酸を配列決定することを含む、核酸を配列決定する方法を提供する。

もう1つの態様において、本発明は、少なくとも3つもchemFETを含むchemFETアレイのchemFETと接触した反応チャンバー中の鋳型核酸にハイブリダイズした配列決定プライマーの3’末端への、1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

1つの態様において、本発明は、標的核酸を断片化して、複数の断片化された核酸を生成し、複数の断片化された核酸の1以上を個々に増幅し、次いで、chemFETアレイを用いて個々に増幅された断片化された核酸を配列決定することを含む、核酸を配列決定する方法を提供する。1つの実施形態において、chemFETアレイは少なくとも3つのchemFETを含む。いくつかの実施形態において、chemFETアレイは少なくとも500のchemFET、または少なくとも100,000のchemFETを含む。いくつかの実施形態において、複数の断片化された核酸は、油中水型エマルジョン増幅方法を用いて個々に増幅される。

もう1つの実施形態において、本発明は、標的核酸を断片化して、複数の断片化された核酸を生成させ、複数の断片化された核酸の各々を個々のビーズに付着させて、各々が、単一の断片化された核酸に付着した複数のビーズを生成させ、各ビーズ上の複数の同一の断片化された核酸をもたらす各ビーズ上の断片化された核酸を増幅し、断片化された核酸に付着された複数のビーズを、アレイ中の各センサー用の別々の反応チャンバーを有するchemFETに送達し、ここに、唯1つのビーズが各反応チャンバーに位置しており、次いで、複数の反応チャンバー中で配列決定反応を同時に行うことを含む、核酸を配列決定する方法を提供する。

もう1つの態様において、本発明は、標的核酸を断片化して、複数の断片化された核酸を生成させ、該複数の断片化された核酸の内1以上を個々に増幅させ、次いで、chemFETアレイを用いて、約1〜10μmの中心間距離を有する複数の反応チャンバーにおいて増幅された断片化された核酸を個々に配列決定することを含む、核酸を配列決定する方法を提供する。種々の実施形態において、中心間距離は約9μm、約5μm、または約2μmである。

もう1つの態様において、本発明は複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、該複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、検出可能なpH変化の不存在下において、アレイ内の少なくとも1つのchemFETにおける電圧の変化により1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

もう1つの態様において、本発明は、複数の鋳型核酸を反応チャンバー中に配置し、ここに、複数の鋳型核酸は単一のビーズに付着され、鋳型核酸の各々は配列決定プライマーにハイブリダイズされており、およびポリメラーゼに結合しており、および反応チャンバーはchemFETと接触しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、chemFETにおける第一および第二の電圧パルスの検出により1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

なおもう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズされており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことにより新しい核酸ストランドを合成し、次いで、放出された無機ピロホスフェートを非酵素的に検出することにより1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。1つの実施形態において、検出工程は検出可能なpH変化の不存在下において行われる。

さらにもう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置し、ここに、複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、放出された無機ピロホスフェートおよび取り込まれていないヌクレオチド三リン酸を検出することによって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

1つの実施形態において、放出された無機ピロホスフェートはt0において検出され、および取り込まれていないヌクレオチド三リン酸は時間t1において検出される。関連する実施形態において、t1−t0の時間差は取り込まれた既知のヌクレオチド三リン酸の数を示す。

もう1つの態様において、本発明は、鋳型核酸を配列決定プライマーおよびポリメラーゼと、鋳型核酸が、鋳型/プライマーハイブリットを形成するために配列決定プライマーに結合するのを可能とし、かつポリメラーゼが鋳型/プライマーハイブリットに結合するのを可能とするのに十分な時間および条件で接触させ、ヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、放出された無機ピロホスフェートおよび取り込まれていないヌクレオチド三リン酸を検出することによって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

1つの実施形態において、放出された無機ピロホスフェートはt0において検出され、および取り込まれていないヌクレオチド三リン酸は時間t1において検出される。関連する実施形態において、t1およびt0の間の時間差(すなわち、t1−t0)は、取り込まれた既知のヌクレオチド三リン酸の数を示す。

更にもう1つの態様において、本発明は、鋳型核酸を配列決定プライマーおよびポリメラーゼと、鋳型核酸が、鋳型/プライマーハイブリッドを形成するために配列決定プライマーに結合するのを可能とし、かつポリメラーゼが鋳型/プライマーハイブリッドに結合するのを可能とするのに十分な時間および条件で接触させ、1以上の既知のヌクレオチド三リン酸を、順次に、低イオン強度環境において配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し(または配列決定プライマーを延長し)、次いで、chemFETにおける1以上の電圧パルスの検出によって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

実施形態に依存して、低イオン強度環境は1mM未満のMgCl2、0.5mM未満のMgCl2、100μM未満のMgCl2、または50μM未満のMgCl2を含むこともできる。他の実施形態において、低イオン強度環境は1mM未満のMnCl2、0.5mM未満のMnCl2、100μM未満のMnCl2、または50μM未満のMnCl2を含むこともできる。更に他の実施形態において、塩はもう1つのMg2+またはMn2+含有塩であってよく、あるいはそれはCa2+またはCo2+含有塩であってよく、またはそれは1以上のそのような塩の組合せであってよい。

もう1つの態様において、本発明は、chemFETと接触した溶液中で、ヌクレオチド三リン酸、鋳型/プライマーハイブリッド、およびポリメラーゼを合わせ、次いで、chemFETにおいて電圧パルスを検出することを含む、新しく合成された核酸への(または配列決定プライマーのようなプライマー上への)ヌクレオチド三リン酸の取込みを決定する方法を提供し、ここに、第一および第二の電圧パルスの検出はヌクレオチド三リン酸の取込みを示し、およびここに、第二の電圧パルスではなく第一の電圧パルスの検出はヌクレオチド三リン酸の取込みの欠如を示す。

1つの実施形態において、電圧パルスは、chemFETの不動態化層における結合事象から独立したchemFETにおいて検出される。

もう1つの態様において、本発明は、chemFETと接触した溶液中で、ヌクレオチド三リン酸、鋳型/プライマーハイブリッド、およびポリメラーゼを合わせ、次いで、chemFETの不動態化層における結合事象とは独立してchemFETにおける電圧パルスを検出することを含む、ヌクレオチド三リン酸の新しく合成された核酸への(または配列決定プライマーのようなプライマーの上への)取込みを決定する方法を提供し、ここに、第一および第二の電圧パルスの検出は少なくとも1つのヌクレオチド三リン酸の取込みを示す。

これまでのいくつかの態様の種々の実施形態において、第一の電圧パルスは時間t0で起こり、第二の電圧パルスは時間t1で起こり、t1−t0は取り込まれたヌクレオチド三リン酸の数を示す。種々の実施形態において、取り込まれたヌクレオチド三リン酸は既知である。種々の実施形態において、ヌクレオチド三リン酸は複数の同一のヌクレオチド三リン酸であり、鋳型/プライマーハイブリッドは複数の同一の鋳型/プライマーハイブリッドであって、ポリメラーゼは複数の同一のポリメラーゼである。別法として、ポリメラーゼは、同一でなく、むしろ2、3、またはそれを超えるタイプのポリメラーゼよりなることができる複数のポリメラーゼであってよい。いくつかの例において、2つのポリメラーゼの混合物を、適当な加工性を有する一方のもの、および取込みの適当な速度を有する他方のものと共に用いることができる。異なるポリメラーゼの比率は変化させることができ、本発明はこの点において限定されるものではない。同様に、鋳型/プライマーハイブリッドは、相互に同一でなくてもよい複数の鋳型/プライマーハイブリッドでよく、但し、単一の反応チャンバー中の、または単一のビーズに付着されたいずれかの鋳型/プライマーハイブリッドは相互に同一であるものとする。

更にもう1つの態様において、本発明は、複数の鋳型核酸を複数の反応チャンバー中に配置させ(例えば、入れるかまたは位置させ)、ここに、複数の反応チャンバーは各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し(または配列決定プライマーを延長し)、次いで、少なくとも1つのchemFETにおいて、高さh0を有する時間t0における第一の電圧パルスおよび高さh1を有する時間t1における第二のパルスを検出することによって、1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、h0およびh1は、各々、ベースラインを少なくとも約5mV超えておりおよびt1−t0は少なくとも1ミリ秒である。いくつかの実施形態において、t1−t0は少なくとも5ミリ秒、少なくとも10ミリ秒、少なくとも20ミリ秒、少なくとも30ミリ秒、少なくとも40ミリ秒、または少なくとも50ミリ秒である。

もう1つの態様において、本発明は、複数のビーズを複数の反応チャンバー中に配置し、ここに、各反応チャンバーは単一のビーズを含み、各ビーズは複数の同一の鋳型核酸に付着しており、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、およびここに、複数の反応チャンバーは各反応チャンバー用の少なくとも1つのchemFETを含むchemFETアレイと接触しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し(または配列決定プライマーを延長し)、次いで、第一および第二の電圧パルスをアレイ内で少なくとも1つのchemFETにおいて検出することによって、1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、chemFETアレイは少なくとも3つのchemFETを含む。

もう1つの態様において、本発明は、複数のビーズを複数の反応チャンバー中に配置し、ここに、各反応チャンバーは単一のビーズを含み、各ビーズは複数の同一の鋳型核酸に付着しており、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、およびここに、複数の反応チャンバーは、各反応チャンバー用の少なくとも1つのchemFETを含む化学的に感受性の電界効果トランジスタ(chemFET)アレイと接触しており、複数の既知の同一のヌクレオチド三リン酸を各反応チャンバーに導入することによって新しい核酸ストランドの合成(または配列決定プライマーの延長)を開始し、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、アレイ内の少なくとも1つのchemFETにおいて第一および第二の電圧パルスを検出することによって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

1つの実施形態において、各反応チャンバーは、複数の既知の三リン酸を各反応チャンバーに導入するに先立ってアデノシン三リン酸を含む。

もう1つの態様において、本発明は、(a)複数のビーズを複数の反応チャンバーに配置し、各反応チャンバーは単一のビーズを含み、各ビーズは複数の同一の鋳型核酸に付着しており、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、および各反応チャンバーは少なくとも1つのchemFETと接触しており、(b)複数の既知の同一のヌクレオチド三リン酸を核反応チャンバーに導入し、(c)もし鋳型核酸中の対応するヌクレオチドに対して相補的であれば、1以上のヌクレオチド三リン酸の配列決定プライマーの3’末端における順次の取込みを検出し、(d)反応チャンバーからの取り込まれていないヌクレオチド三リン酸を洗浄し、次いで、(e)異なる複数の既知のヌクレオチド三リン酸を用いて同一反応チャンバーにおいて工程(b)〜(d)を反復することを含む、核酸を配列決定する方法を提供する。

1つの実施形態において、1以上のヌクレオチド三リン酸の順次の取込みが、chemFETにおいて第一および第二の電圧パルスによって検出される。いくつかの実施形態において、工程(e)は、各異なる複数の既知のヌクレオチド三リン酸を各反応チャンバーに別々に導入することによって工程(b)〜(d)を反復することを含む。

もう1つの態様において、本発明は、複数のビーズを複数の反応チャンバー中に配置し、ここに、各反応チャンバーは単一のビーズを含み、各ビーズは複数の同一の鋳型核酸に付着しており、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、およびここに、複数の反応チャンバーの各々はchemFETアレイ中の少なくとも1つのchemFETと接触しており、二価カチオンを各反応チャンバーに導入することによって新しい核酸ストランドの合成を開始し、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込むことによって新しい核酸ストランドを合成し、次いで、アレイ内の少なくとも1つのchemFETにおいて第一および第二の電圧パルスを検出することによって1以上の既知のヌクレオチド三リン酸の取込みを検出することを含む、核酸を配列決定する方法を提供する。

1つの実施形態において、二価カチオンはMg2+である。もう1つの実施形態において、二価カチオンはMn2+である。なお更なる実施形態において、二価カチオンはMg2+およびMn2+の混合物である。実施形態に依存して、二価カチオンは1mM未満、または100μm未満または50μmの濃度におけるものである。

なおもう1つの態様において、本発明は、複数の同一の鋳型核酸を反応チャンバー中に配置し、ここに、反応チャンバーはchemFETと接触しており、およびここに、鋳型核酸の各々は配列決定プライマーにハイブリダイズしており、およびポリメラーゼに結合しており、1以上の既知のヌクレオチド三リン酸を、順次、配列決定プライマーの3’末端に取り込み、次いで、chemFETにおいて電圧パルスによって1以上の既知のヌクレオチド三リン酸の取り込みを検出することを含む、核酸を配列決定する方法を提供し、ここに、10〜1000ヌクレオチド三リン酸の取込みが検出される。

種々の実施形態は、本発明の種々のこれまでの態様に含まれ得るが、これらは便宜および簡略化のために以下において一旦引用される。

本発明の種々のこれまでの態様および実施形態は鋳型への配列決定プライマーのハイブリダイゼーション(または結合)を引用するが、本発明では、それ自体に(すなわち、分子内に)ハイブリダイズし、それにより、ヌクレオチド三リン酸が取り込まれ得る遊離3’末端を生起する配列決定プライマーおよび/または鋳型核酸の使用も考えられることを理解されたい。自己起点鋳型と本明細書中で呼ばれるそのような鋳型はこれまでの方法のいずれにおいても用いることができる。

同様に、本発明では、DNAニッカーゼのようなニッキング酵素が作用することができるそれらの遊離末端において特定の配列を有するように作成された二本鎖鋳型の使用が同等に考えられる。このようにして、ポリメラーゼはヌクレオチド三リン酸をニックされた部位において取り込む。これらの例において、別々の配列決定プライマーに対する要件はない。

いくつかの実施形態において、少なくとも10、少なくとも20、少なくとも30、少なくとも40、少なくとも50、少なくとも60、少なくとも70、少なくとも80、少なくとも90、または少なくとも100のヌクレオチド三リン酸の取込みが検出される。他の実施形態において、100〜1000ヌクレオチド三リン酸の取込みが検出される。なお他のいくつかの実施形態において、250〜750ヌクレオチド三リン酸の取込みが検出される。

いくつかの実施形態において、反応チャンバーは複数のパッキングビーズを含む。いくつかの実施形態において、検出工程は複数のパッキングビーズの存在下で起こる。

いくつかの実施形態において、反応チャンバーは可溶性非核酸ポリマーを含む。いくつかの実施形態において、検出工程は可溶性非核酸ポリマーの存在下で起こる。いくつかの実施形態において、可溶性非核酸ポリマーはポリエチレングリコール、またはPEA、またはデキストラン、またはアクリルアミド、またはセルロース(例えば、エチルセルロース)である。いくつかの実施形態において、ポリエチレングリコースのような非核酸ポリマーは単一のビーズに付着されている。いくつかの実施形態において、いくつかの例では、FET表面である反応チャンバーの底部を除いて、非核酸ポリマーは反応チャンバーの1以上の(または全ての)側に付着している。いくつかの実施形態において、非核酸ポリマーは、限定されるものではないが、ビオチニル化ポリエチレングリコールのようにビオチニル化されている。

いくつかの実施形態において、該方法は約7〜9、または約8.5〜9.5、または約9のpHで行われる。

いくつかの実施形態において、合成および/または検出工程は弱い緩衝液中で行われる。いくつかの実施形態において、弱い緩衝液は、緩衝剤としての、Tris−HCl、ホウ酸またはボレート緩衝液、アセテート、モルホリン、クエン酸、カルボン酸、またはリン酸を含む。

いくつかの実施形態において、合成および/または検出工程は約1mM Tris−HCl中で行われる。いくつかの実施形態において、合成および/または検出工程は1mM未満のTris−HCl中で行われる。いくつかの実施形態において、合成および/または検出工程は約0.9mM Tris−HCl、約0.8mM Tris−HCl、約0.7mM Tris−HCl、約0.6mM Tris−HCl、約0.5mM Tris−HCl、約0.4mM Tris−HCl、約0.3mM Tris−HCl、または約0.2mM Tris−HCl中で行われる。

いくつかの実施形態において、合成および/または検出工程は約1mMボレート緩衝液中で行われる。いくつかの実施形態において、合成および/または検出工程は約1mM未満のボレート緩衝液中で行われる。いくつかの実施形態において、合成および/または検出工程は約0.9mMボレート緩衝液、約0.8mMボレート緩衝液、約0.7mMボレート緩衝液、約0.6mMボレート緩衝液、約0.5mMボレート緩衝液、約0.4mMボレート緩衝液、約0.3mMボレート緩衝液、または約0.2mMボレート緩衝液中で行われる。

いくつかの実施形態において、検出工程は検出可能なpH変化の不存在下で行われる。いくつかの実施形態において、検出工程は一定のpHの環境で行われる。いくつかの実施形態において、chemFETは比較的pH非感受性である。いくつかの実施形態において、合成および/または検出工程は約0.5mM Tris−HCl中で行われる。

いくつかの実施形態において、合成および/または検出工程は低イオン強度環境で行われる。いくつかの実施形態において、合成および/または検出工程は、1mM未満のMgCl2またはMnCl2、0.5mM未満のMgCl2またはMnCl2、100μM未満のMgCl2またはMnCl2を含む低イオン強度環境で行われる。いくつかの実施形態において、合成および/または検出工程は、約100μm MgCl2またはMnCl2、約75μm MgCl2またはMnCl2、50μm MgCl2またはMnCl2、約40μm MgCl2またはMnCl2、約30μm MgCl2またはMnCl2、約20μm MgCl2またはMnCl2、約10μm MgCl2またはMnCl2を含む低イオン強度環境で行う。本発明では、同様に、他の二価カチオンの量が考えられ、従って、それはMgCl2、またはMnCl2のみに限定されないのは理解されるべきである。同様に、本発明では、2以上の二価カチオン(および/またはそれらの対応する塩)の使用が考えられることが理解されるべきであり、但し、合計イオン濃度は前記したレベルにおけるものであるものとする。

いくつかの実施形態において、合成および/または検出工程は約0.5mM TRISおよび約50μM MgCl2またはMnCl2中で行われる。

種々の実施形態において、ヌクレオチド三リン酸はブロックされていない。本明細書中で用いる場合、ブロックされていないヌクレオチド三リン酸は、(その3’末端において)核酸に取り込むことができる未修飾末端を持つヌクレオチド三リン酸であり、一旦それが取り込まれると、取り込むべき以下のヌクレオチド三リン酸に付着させることができる。ブロックされたdNTPは、対照的に、核酸に加えることができないか、あるいは核酸へのそれらの取込みはいずれかの更なるヌクレオチドの取込みを妨げる。種々の実施形態において、ヌクレオチド三リン酸はデオキシヌクレオチド三リン酸(dNTP)である。

種々の実施形態において、chemFETは窒化ケイ素不動態化層を含む。いくつかの実施形態において、chemFETは、無機ピロフォスフェート(PPi)受容体に付着された不動態化層を含む。いくつかの実施形態において、chemFETは、核酸に結合していない不動態化層を含む。

いくつかの実施形態において、各反応チャンバーは単一のchemFETと接触している。

いくつかの実施形態において、反応チャンバーは、0.5pL未満、0.1pL未満、0.05pL未満、0.01pL未満、0.005pL未満を含めた、約1ピコリットル(pL)と等しい、またはそれ未満の容量を有する。いくつかの実施形態において、反応チャンバーは1〜10μmの中心間間隔によって分離されている。いくつかの実施形態において、反応チャンバーは、約9μm、約5ミクロン、または約2ミクロンの中心間間隔によって分離されている。反応チャンバーは、例えば、それらのベースまたは底部において四角形の断面を有することができる。その例は8μm×8μmの断面、4μm×4μmの断面、または1.5μm×1.5μmの断面を含む。別法として、それらは、例えば、それらのベースまたは底部において三角形の断面を有することができる。その例は8μm×12μmの断面、4μm×6μmの断面、または1.5μm×2.25μmの断面を含む。

いくつかの実施形態において、ヌクレオチド三リン酸は(例えば、MgCl2の存在下で)Mg2+に、または(例えば、MnCl2の存在下で)Mn2+に予め浸漬させる。いくつかの実施形態において、ポリメラーゼは(例えば、MgCl2の存在下で)Mg2+または(例えば、MnCl2の存在下で)Mn2+に予め浸漬させる。

いくつかの実施形態において、該方法は単一の捕獲ビーズを含む反応チャンバーにおいて行われ、ここに、単一の捕獲ビーズ直径に対する反応チャンバー幅の比率は少なくとも0.7、少なくとも0.8、または少なくとも0.9である。

いくつかの実施形態において、ポリメラーゼは溶液中で遊離している。いくつかの実施形態において、ポリメラーゼはビーズに固定化されている。いくつかの実施形態において、ポリメラーゼは捕獲ビーズに固定化されている。いくつかの実施形態において、鋳型核酸は捕獲ビーズに付着されている。

いくつかの実施形態において、ヌクレオチド取込みを検出するに先立って、無機ピロホスフェート(PPi)は有意に加水分解されていない。いくつかの実施形態において、第1の電圧パルスを検出するに先立って、無機ピロホスフェート(PPi)は有意に加水分解されていない。

1つの態様において、本発明は、各々がその表面に配置されたPPi受容体を有する複数のchemFETセンサーを含むchemFETアレイを含む装置を提供し、ここに、該アレイは少なくとも3つのchemFETセンサーを含む。

1つの態様において、本発明は、各々がその表面に配置されたPPi受容体を有する複数のchemFETセンサーを含むchemFETアレイを含む装置を提供し、ここに、該アレイ中の隣接するchemFETセンサーは、約10μm未満の中心間距離だけ分離されている(例えば、.18μm CMOS製造を用い、ピッチは約2.8μmとすることができる)。

もう1つの態様において、本発明は、その表面にPPi選択的受容体が配置された化学的に感受性の電界効果トランジスタ(chemFET)を含む装置を提供する。PPi受容体はchemFET表面に固定化することができる。

なおもう1つの態様において、本発明は、各々がその表面に配置されたPPi受容体を有する複数のchemFETセンサーを含む化学的に感受性の電界効果トランジスタ(chemFET)アレイを含む装置を提供し、ここに、該複数はアレイ中のchemFETセンサーのサブ組である。関連する実施形態において、アレイは少なくとも3つのchemFETセンサーを含む。該サブ組はアレイ中のセンサーの10%、25%、33%、50%、75%以上を表すことができる。PPi選択的受容体は各chemFETの表面に固定化することができる。

いつくかの実施形態において、隣接する反応チャンバーの間の中心間距離は約1〜9μm、または約2〜9μm、約1μm、約2μm、約3μm、約4μm、約5μm、約6μm、約7μm、約8μm、または約9μmである。いくつかの実施形態において、chemFETアレイは256を超えるセンサー(および、所望により、256を超える対応する反応チャンバー(またはウエル))、300を超えるセンサー(および、所望により、300を超える対応する反応チャンバー)、400を超えるセンサー(および、所望により400を超える対応する反応チャンバー)、500を超えるセンサー(および、所望により500を超える対応する反応チャンバー)、600を超えるセンサー(および、所望により600を超える対応する反応チャンバー)、700を超えるセンサー(および、所望により700を超える対応する反応チャンバー)、800を超えるセンサー(および、所望により800を超える対応する反応チャンバー)、900を超えるセンサー(および、所望により900を超える対応する反応チャンバー)、103を超えるセンサー(および、所望により103を超える対応する反応チャンバー)、104を超えるセンサー(および、所望により104を超える対応する反応チャンバー)、105を超えるセンサー(および、所望により105を超える対応する反応チャンバー)、または106を超えるセンサー(および、所望により106を超える対応する反応チャンバー)を含む。いくつかの実施形態において、chemFETアレイはセンサーの少なくとも512の行および少なくとも512の列を含む。

いくつかの実施形態において、配列決定副産物はPPiである。いくつかの実施形態において、PPiは直接的に測定される。関連する実施形態において、PPiは、chemFETセンサーの表面に固定化されたPPi選択的受容体へのその結合によって検出される。もう1つの実施形態において、PPiは、PPi選択的受容体の不存在下で検出される。他の実施形態において、PPiはpH非依存性または非感受性環境で検出される。

いくつかの実施形態において、配列決定反応の副産物は水素イオンである。いくつかの実施形態において、配列決定反応副産物はPiである。なお他の実施形態において、chemFETは、本明細書中に記載したように、他のパラメーターと所望により組合せて、副産物のいずれかの組合せの変化を検出する。

いくつかの実施形態において、PPi選択的受容体は、図11Bに示された化合物1、化合物2、化合物3、化合物4、化合物5、化合物6、化合物7、化合物8、化合物9または化合物10である。いくつかの実施形態において、chemFETは、その各々がその表面に固定化されたPPi選択的受容体を含めて配置されたchemFETのアレイに存在する。いくつかの実施形態において、同一のPPi選択的受容体はアレイの各chemFETに配置されている。いくつかの実施形態において、アレイは256を超えるセンサーを含む。いくつかの実施形態において、アレイはセンサーの少なくとも512の行および少なくとも512の列を含む。いくつかの実施形態において、chemFETは反応チャンバーの底部に位置する。

もう1つの態様において、本発明は、その表面に配置された生物学的アレイまたは化学的アレイを有するchemFETアレイを含む装置を提供する。

生物学的アレイは核酸アレイ、限定されるものではないが、酵素アレイ、抗体アレイおよび抗体断片アレイを含めた蛋白質アレイ、細胞アレイなどであってよい。化学的アレイは有機小分子アレイ、または無機分子アレイであってよいが、それに限定されるものではない。chemFETアレイは少なくとも5、少なくとも10、少なくとも102、少なくとも103、少なくとも104、少なくとも105、少なくとも106、またはそれ以上のセンサーを含んでもよい。生物学的または化学的アレイは、複数の「セル」、または空間的に定義された領域に配置してもよく、およびこれらの領域の各々は、いくつかの実施形態においては、chemFETアレイ中の異なるセンサー上に位置させる。

なおもう1つの態様において、本発明は、chemFETアレイ上に配置された核酸アレイを試料と接触させ、次いで、該試料からの核酸の、核酸アレイ上の1以上の領域への結合を検出することを含む、核酸を検出する方法を提供する。

もう1つの態様において、本発明は、chemFETアレイ上に配置された蛋白質アレイを試料と接触させ、次いで、該試料からの蛋白質の、蛋白質アレイ上の1以上の領域への結合を検出することを含む、蛋白質を検出する方法を提供する。

尚もう1つの態様において、本発明は、chemFETアレイ上に配置された蛋白質アレイを試料と接触させ、次いで、該試料からの核酸の、蛋白質アレイ上の1以上の領域への結合を検出することを含む、核酸を検出する方法を提供する。

もう1つの態様において、本発明は、chemFETアレイ上に配置された抗体アレイを試料と接触させ、次いで、該試料からの抗原の、抗体アレイ上の1以上の領域への結合を検出することを含む、抗原を検出する方法を提供する。

もう1つの態様において、本発明は、chemFETアレイ上に配置された酵素アレイを試料と接触させ、次いで、該試料からの物質の、酵素アレイ上の1以上の領域への結合を検出することを含む、酵素基質または阻害剤を検出する方法を提供する。

これまでの概念、および以下により詳細に議論する更なる概念(但し、その様な概念は相互に矛盾しないものとする)の全ての組合せは、本明細書中で開示された発明的主題の一部であると考えられるのは認められるべきである。特に、本開示の最後に現れる特許請求される主題全ての組合せは、本明細書中で開示される発明的主題の一部であると考えられる。また、引用により一体化されるいずれかの開示において、やはり現れるであろう、本明細書中で明示的に使用される用語は、本明細書中に開示された特定の概念と最も合致する意味に従うべきであると認識されるべきである。

以下に示すのは、分析物の検出および/または測定のための大規模なchemFETアレイに関する本発明の方法および装置に関する種々の概念、およびその実施形態のより詳細な記載である。開示された概念は実施のいずれかの特定の様式に限定されないので、上記で導入され、および以下でより詳細に議論される種々の概念は、多数の方法のいずれかで実施できるのは認められるべきである。具体的な実施および適用の例は、主として、説明目的で供される。

本開示に従った種々の発明的実施形態は、少なくとも部分的には、マイクロエレクトロニクスのパワーをミクロ流体系の生体適合性と組み合わせる半導体ベースの/ミクロ流体ハイブリッド系に向けられる。以下のいくつかの例において、ハイブリッド系のマイクロエレクトロニクス部分は、説明の目的で、CMOS技術で実施される。しかしながら、他の半導体ベースの技術を利用して、本明細書中で議論される系のマイクロエレクトロニクス部分の種々の態様を実施できるので、該開示はこの点について限定的であることを意図しないことは認められるべきである。

本明細書中に開示される1つの実施形態は、化学的に感受性の電界効果トランジスタ(chemFET)の大きなセンサーアレイ(例えば、二次元アレイ)に向けられ、ここに、個々のchemFETセンサーエレメントまたはアレイの「画素」は、操作されていない試料中におけるあるいはアレイに近接して起こる化学的および/または生物学的プロセス(化学反応、細胞培養、神経活性、核酸配列決定プロセスなど)の結果としての、分析物の存在(または不存在)、分析物のレベル(または量)および/または分析物の濃度を検出するように構成されている。以下により詳細に議論する種々の実施形態において考えられるchemFETの例は、限定されるものではないが、イオン感受性電界効果トランジスタ(ISFET)および酵素感受性電界効果トランジスタ(ENFET)を含む。1つの例示的な実施において、1以上のミクロ流体構造はchemFETセンサーアレイ上方で製造されて、当てはまるように、注目する分析物を生産し、または消費することができる生物学的または化学的反応の含有および/または封じ込めを提供する。例えば、1つの実施においては、その上に所与のウェルが設けられた1以上のセンサーが、該所与のウェル中の分析物の存在、レベル、および/または濃度を検出し、測定するように、ミクロ流体構造は、アレイの1以上のセンサーの上方に配置された1以上の「ウェル」(例えば、小さな反応チャンバーまたは「反応ウェル」)として構成することができる。

もう1つの例示的実施において、本発明は、反応チャンバーの少なくとも1つの二次元アレイを含む高スループット配列決定のための系を含み、ここに、各反応チャンバーは化学的に感受性の電界効果トランジスタ(「chemFET」)にカップリングされており、各反応チャンバーは容量が10μm3(すなわち、1pL)以下である。好ましくは、各反応チャンバーは容量が.34pL以下、より好ましくは.096pL以下、.012pLさえである。反応チャンバーは、所望により、頂部における断面面積が22、32、42、52、62、72、82、92または102平方ミクロンとすることができる。好ましくは、アレイは少なくとも100、1,000、10,000、100,000または1,000,000の反応チャンバーを有する。反応チャンバーは、chemFETに容量的にカップリングさせることができ、好ましくは、chemFETに容量的にカップリングさせる。

いくつかの実施形態において、そのようなchemFETアレイ/マイクロ流体ハイブリッド構造を用いて、核酸を含有する注目する溶液/材料を分析することができる。例えば、そのような構造を使用して、核酸の配列決定をモニターすることができる。核酸の配列決定を行って、核酸の部分的または完全なヌクレオチド配列を決定し、核酸における単一ヌクレオチド多形の存在、いくつかの例においては、性質を検出し、いずれの治療方法が、対象の遺伝子メーキャップによって決定できるように、特定の疾患を有する対象を処置するのに最も有効であるかを決定し、2以上の状態の核酸発現プロフィールを決定し、比較し、(例えば、病気のおよび正常な組織の発現プロフィールの比較、あるいは未処理組織、および薬物、酵素、放射線または化学的処置で処理された組織の発現プロフィールの比較)、試料をハプロタイプ分析し(例えば、ヒト対象に存在する2つの対立遺伝子の各々についての遺伝子または遺伝子における変異の比較)、試料を核型分析し(例えば、肉眼での染色体または他のゲノムの異常を検出するための、胚のような細胞または組織の染色体メーキャップの分析)、および遺伝子型分析する(例えば、例えばキャリアの状態および/または種−族関係を決定するために1以上の遺伝子座の分析)ことができる。

本明細書中に記載された系を利用して、全ゲノムまたはそのいずれかの部分の核酸を配列決定することができる。配列決定することができるゲノムは哺乳動物ゲノム、好ましくはヒトゲノムを含む。かくして、1つの例示的な実施形態において、本発明は:ゲノムまたはその部分からの断片化された核酸を、反応チャンバーの少なくとも1つの二次元アレイを含む高スループット配列決定のための系に送達し、ここに、各反応チャンバーは化学的に感受性の電界効果トランジスタ(「chemFET」)にカップリングされており、および各反応チャンバーは容量が1pL以下であり、次いで、反応チャンバーのchemFETからのシグナルを介して反応チャンバーの少なくとも1つにおいて配列決定反応を検出することを含む、ゲノムまたはその部分を配列決定する方法を含む。

別法の例示的実施形態において、該方法は:ゲノムまたはその部分からの断片化された核酸を、反応チャンバーの二次元アレイを含む配列決定装置に送達し、ここに、反応チャンバーの各々は、関連するchemFETとの検知関係において配置され;次いで、関連するchemFETからのシグナルを介して反応チャンバーの少なくとも1つにおける配列決定反応を検出することを含む。

好ましくは、配列決定反応は、第一のデオキシリボヌクレオチド三リン酸(「dNTP」)を、反応チャンバーの各々に送達することによって行われる。好ましくは、送達工程は、第一のdNTPを実質的に同時に反応チャンバーの各々に送達することを含む。一旦、第一のdNTPが反応チャンバーに送達されれば、酵素は、典型的には、反応チャンバーに送達されて、いずれの使用されていないdNTPも分解し、続いて、洗浄して、反応チャンバーからの酵素の実質的に全てを除去する。好ましくは、該酵素はPPiも分解する。洗浄はいずれの分解されたdNTPまたは分解されたPPiも除去することもできる。

配列決定すべき核酸は、天然に生じるまたは天然に生じない核酸とすることができ、好ましくは、天然に生じる核酸である。核酸は、限定されるものではないが、デオキシリボ核酸(「DNA」)(例えば、メッセンジャーDNA、相補的DNA、または核DNA)、リボ核酸(「RNA」)(例えば、ミクロRNA、トランスファーRNA、メッセンジャーRNA、または小干渉性RNA)、またはペプチドを含めたいくつかの源のいずれから得ることもできる。該源がDNAである場合、該DNAは、限定されるものではないが、血液、唾液、脳脊髄液(「CSF」)、皮膚、毛髪、尿、糞、および粘膜を含めた、DNAを含有するいずれの体液または組織からも得ることができる。配列決定すべき核酸の出発量は、最小の試料の要件を決定する。単一のストランドにおける450塩基の平均を持ち、塩基当り325g/モルの平均分子量を持つ以下のビーズのサイズを考慮し、我々は以下の:

アレイで用いるのが考えられるビーズおよびマイクロウェルの数が与えられれば、かくして、試験すべき対象から採取された試料は3μgのオーダーであることのみが必要であるのは明らかであろう。

好ましくは、前記した方法を用い、少なくとも106の塩基対が1時間当たりに配列決定され、より好ましくは、少なくとも107塩基対が1時間当たりに配列決定され、なおより好ましくは、少なくとも108の塩基対が1時間当たりに配列決定され、なおより好ましくは、少なくとも109の塩基対が1時間当たりに配列決定され、最も好ましくは少なくとも1010の塩基対が1時間当たりに配列決定される。かくして、該方法を用いて、約24時間以内に、より好ましくは約20時間以内に、なおより好ましくは約15時間以内に、なおより好ましくは約10時間以内に、なおより好ましくは約5時間以内に、最も好ましくは、約1時間以内に全ヒトゲノムを配列決定することができる。

本明細書中に記載された系を利用して、約3μg以下のDNAから生物の全ゲノムを配列決定することができる。1つの実施形態において、本発明は、生物からの約3μg以下のDNAを化学的に感受性の電界効果トランジスタのアレイに送達し、次いで、ゲノムの配列を決定することを含む、生物の全ゲノムを配列決定する方法を含む。もう1つの実施形態において、本発明は、オプティックスまたは標識を使用することなく約1ng以下のDNAから完全なヒトゲノムを配列決定するのに適合したデバイスを含む。典型的には、該デバイスはchemFETアレイおよび/またはミクロ流体反応チャンバーのアレイおよび/または誘電性材料にカップリングされた半導体材料を含む。

前記した配列決定は、500μm、400μm、または300μmまでのイオン強度を有する反応混合物中で行うことができる。溶液のイオン強度Iは、溶液に存在する全てのイオンの濃度の関数である。

ここに、c

BはイオンBのモル濃度(モルdm

−3)であり、z

Bはそのイオンの電荷数であって、合計は溶液中の全てのイオンにわたって取られる。Mg

+2またはMn

2+濃度は1000μM、500μM、200μM、100μM、50μM、10μM、5μMまたは1μMであってさえよい。

前記した方法は、配列決定反応がロボティックスを介して行われるように自動化してもよい、加えて、反応チャンバーのchemFETからのシグナルを介して得られた配列決定情報は、ユーザーが配列決定反応の進行を遠隔的にモニターできるように、パーソナルコンピュータ、パーソナルデジタルアシスタント、携帯電話、ビデオゲームシステム、またはテレビに供することができる。このプロセスは、例えば、図71に示される。

また、本明細書中に記載された系を用いて、病気の同定および治療を助けることもできる。例えば、該系は、特定の病気に関連した配列を同定するために、または特定の有効成分に対する陽性の応答に関連する配列を同定するために用いることができる。

1つの実施形態において、本発明は、疾患を有する複数の対象からの核酸を、反応チャンバーの二次元アレイを含む配列決定装置に送達し、ここに、反応チャンバーの各々がchemFETに容量的にカップリングされており;該chemFETからのシグナルから核酸の配列を決定し;次いで、複数の対象からのDNA間の共通の配列を同定することを含む、疾患に関連する配列を同定する方法を含む。好ましくは、対象は哺乳動物、より好ましくはヒトである。好ましくは、疾患は癌、免疫抑制疾患、神経学的疾患、またはウイルス感染である。

もう1つの実施形態において、本発明は、1以上の配列決定装置を用い、活性剤に対して、陽性応答を呈した複数の対象からの、および陰性応答を有する複数の対象からのDNAを配列決定し、ここに、各配列決定装置はchemFETのアレイを含み;次いで、陽性応答を呈した複数の対象における、あるいは他の複数の対象には存在しない陰性応答を呈した対象からの共通のDNA配列を決定することを含む、特定の活性剤に対する陽性応答に関連する配列を同定する方法を含む。好ましくは、対象は哺乳動物、より好ましくはヒトである。

しかしながら、本明細書中に開示された概念のいくつかの説明的例は核酸プロセッシングに対して焦点を当てているが、本発明では、これらの概念のより広い適用が考えられ、これらの例に限定される意図はないことは認められるべきである。

図8は、一般に、本開示の1つの発明的実施形態に従った、大規模なchemFETアレイを含む核酸プロセッシング系1000を説明する。核酸プロセッシング系の例は核酸配列決定系である。以下の議論においては、アレイのchemFETセンサーは、限定されるものではないが、水素イオン濃度および/または核酸プロセッシングに関与する他のイオン種の濃度を含めた、静的および/または動的イオン濃度に対する感度について構成されたISFETとしての説明目的で記載される。しかしながら、本開示はこの点について限定されず、および説明的例としてISFETが使用される本明細書中で議論した実施形態のいずれにおいても、以下でさらに詳細に議論するように、chemFETの他のタイプを代替実施形態で同様に使用できることは認められるべきである。同様に、本発明の種々の態様および実施形態はセンサーとしてISFETを使用できるが、水素イオンではない1以上のイオン性種を検出できるのは認められるべきである。

系1000は、ISFETセンサーアレイ100およびミクロ流体フローセル200を含む半導体/ミクロ流体ハイブリッド構造300を含む。1つの態様において、フローセル200は、ISFETアレイ100の対応するセンサー上方に配置された(図8には示されない)多数のウェルを含むことができる。もう1つの態様において、フローセル200は、多数の配列決定試薬272(例えば、本明細書中においては上位概念的にはdNTPという塩基、dATP、dCTP、dGTP、dTTP、限定されるものではないが、Mg2+のような二価カチオン、洗浄溶液等)のフローセルに対する制御されかつ順序立てた許可(または導入)を介してフローセルに配置された1以上の同一の鋳型核酸の配列決定を容易とするように構成される。

図8に示されるように、配列決定試薬のフローセル200への許可は、コンピュータ260によって制御される1以上のバルブ270および1以上のポンプ274を介して達成することができる。多数の技術を用いて、種々のプロセッシング材料(例えば、溶液、試料、反応試薬、洗浄溶液等)をそのようなフローセルのウェルに対して許可する(すなわち、導入する)ことができる。図8に示されるように、塩基を含めた試薬は、それらがそこからウェルに拡散するフローセルへ(例えば、コンピュータ制御バルブ270およびポンプ274を介して)許可され得、あるいは試薬はインクジェットのような他の手段によってフローセルに加えることができる。なおもう1つの例において、フローセル200はいずれのウェルも含有できず、試薬の拡散特性を探索して、ISFETアレイ100の各センサーの間のクロス−トークを制限することができる。

本明細書中でより詳細に議論するように、本発明に従って提供される配列決定方法の種々の実施形態は、鋳型核酸の多数の同一コピーがそれらの表面に付着されたビーズを用いる。そのようなビーズは、一般に、本明細書中においては、核酸が「負荷された」という。好ましくは、各反応ウェルは単一のビーズのみを含む。それらの内には数十、数百、数千以上があり得る核酸が負荷されたビーズは、まず、フローセルに入り、次いで、個々のビーズが個々のウェルに入る。ビーズは受動的にまたはその他の方法でウェルに入ることができる。例えば、ビーズは、いずれかの適用された外力なくして重力を通じてウェルに入ることができる。ビーズは、限定されるものではないが、磁力または遠心力を含めた適用された外力を通じてウェルに入ることができる。いくつかの実施形態において、もし外力が適用されたならば、それは、ウェルの高さ/深さに対して横方向よりもむしろ、ウェルの高さ/深さに対して平行である方向に適用され、目的はできる限り多くのビーズを「捕獲する」ことである。好ましくは、ウェル(またはウェルアレイ)は攪拌されないというのは、例えば、ウェルの高さ/深さに対して垂直である適用された外力を通じて起こり得るからである。さらに、一旦ウェルがそのように負荷されたならば、それらは、ウェルからビーズを除去し得るいずれの他の力にも付されない。

さらに、本明細書中で議論されるように、核酸負荷ビーズに加えて、各ウェルは、本明細書中においては「パッキングビーズ」といわれる複数のより小さいビーズを含むこともできる。パッキングビーズは、ウェルに存在する分析物、試薬、反応パラメータ等と相互作用または干渉しないいずれかの不活性な材料で構成され得る。パッキングビーズはchemFET表面および核酸負荷ビーズの間に位置させることができ、その場合、それらは核酸負荷ビーズ前にウェルに導入してもよい。別法として、それらは、全て、核酸負荷ビーズの周りに位置させてもよく、その場合、それらは、核酸負荷ビーズの前に、その間におよび/または後にウェルに加えてもよい。なお他の実施形態において、パッキングビーズの大部分は核酸負荷ビーズの頂部に位置させてもよく、その場合、それらは核酸負荷ビーズ後にウェルに加えてもよい。

パッキングビーズは1以上の種々の機能を発揮することができる。例えば、パッキングビーズは、特に、もしそれらのいくらかの分率が核酸負荷ビーズの頂部に位置するならば、ウェルからの核酸負荷ビーズの除去を最小化し、または一緒に妨げるように作用することができる。パッキングビーズは、限定されるものではないが、PPiおよび取り込まれていないヌクレオチドを含めた、ウェルにおける溶液中の1以上の成分の拡散速度を減少させるように働くことができる。いくつかの実施形態において、パッキングビーズは、常磁性ビーズである。パッキングビーズは、Bangs Labratoriesのような源から商業的に入手可能である。

拡散は、反応チャンバーに増粘剤を含めることによってインパクトすることができる。そのような剤の一例は、核酸でないポリマー(すなわち、非核酸ポリマーである)。該ポリマーは天然に生じるものであっても、または天然に生ないものであってもよく、PPi、取り込まれていないヌクレオチド、および/または他の反応副産物または試薬の反応チャンバー底部に向けての拡散を減速させる以外は、それはいずれの性質であってもよく、但し、それはヌクレオチドの取込みおよび検出に干渉しないものとする。適当なポリマーの一例はポリエチレングリコール(PEG)である。他の例はPEA、デキストラン、アクリルアミド、セルロース(例えば、メチルセルロース)等を含む。該ポリマーは溶液中で遊離していてもよく、またそれは反応チャンバーの1以上の側に、捕獲ビーズに、および/または存在し得るいずれかのパッキングビーズに(共有結合により、または非共有結合により)固定化されていてもよい。非共有結合付着はビオチン−アビジン相互作用を介して達成することができる。

なお他の配列決定実施形態において、捕獲ビーズを使用する代わりに、ウェルを例えば、プライマー核酸の対を含めた1以上の核酸でコーティングすることができ、およびプライマーヌクレオチド配列に相補的なアダプターヌクレオチド配列を有する鋳型核酸をウェルに導入することができる。分析物または鋳型核酸を固定化することにおいて有用なこれらおよび他の剤をセンサーアレイ100に、チップパッキングの一部としての個々のダイに、またはウェルに、試料の処理直前に供することができる。ゾルゲルに関連する他の方法を用いて、ISFETアレイ100の表面近くに核酸のような剤を固定化することができる。

本明細書中でより詳細に議論するように、本発明において考えられる配列決定方法のいくつかの態様において鋳型核酸をウェルへの設置に先立って、またはその後に増幅してもよい。種々の方法が核酸を増幅するのに存在する。かくして、1つの態様において、一旦鋳型核酸がフローセル200のウェルに負荷されたならば、増幅をウェルにおいて実行し、得られた増幅された産物を変性し、および配列決定×合成し、または次いで実施してもよい。増幅方法は、限定されるものではないが、ブリッジ増幅、ローリングサークル増幅、あるいは等温または非−等温増幅技術を用いる他の戦略を含む。

まとめると、図8の系におけるフローセル200は、種々の様式で構成して、ISFETアレイ100に近接して1以上の分析物(または1以上の反応溶液)を供することができる。例えば、鋳型核酸を適当に近接させて、センサーアレイ100の1以上の画素に、あるいはセンサーアレイ上方に位置した支持体材料(例えば、1以上の「ビーズ」)上に直接的に付着させ、または適用してもよい。プロセッシング試薬(例えば、ポリメラーゼのような酵素)を、直接センサー上に、あるいはセンサーに近接した1以上の固体支持体上に置くこともできる。該デバイスは、少なくとも1つのセンサー−検出可能生成物(例えば、イオン濃度の変化)の検出および/または測定を含む多数のバイオセンサー適用のためにウェルまたはビーズ無くして用いることができるのは理解されるべきである。

図8の系1000においては、1つの実施形態によると、ISFETセンサーアレイ100はイオン種、特に、イオン種のレベル/量および/または濃度の変化をモニターする。重要な実施形態において、種は、核酸合成または配列決定反応から得られたものである。1つの特に重要なイオン種は、ヌクレオチド取込の結果として放出されるPPiである。一旦合成または配列決定反応が完了したならば、もう1つの重要な種は反応チャンバーに加えられた、および反応チャンバーに残る過剰のヌクレオチドである。そのようなヌクレオチドは、本明細書中においては、「取り込まれていないヌクレオチド」という。

本明細書中においてより詳細に議論されるように、本発明の種々の実施形態は、ISFETの静的および/または動的応答を含むモニタリング/測定技術に関することができる。核酸合成または配列決定反応の間におけるヌクレオチド取込の検出に関連する1つの実施形態において、検出/測定技術は、特に、図2Aに関連して先に議論したように、核酸合成または配列決定反応に関連する種々のイオン種の濃度変化を検出するために、ISFETの一過的または動的応答(イオン−段階的応答、または「イオンパルス」出力)に依拠している。核酸合成または配列決定反応の特定の例を供して、ISFETの一過的または動的応答を説明するが、他の実施形態によると、以下に議論されるISFETの一過的または動的応答は、核酸合成または配列決定反応の具体的例を超えた化学的および/または生物学的活性の他のタイプをモニターし/検知するために開発することができるのは認められるべきである。

1つの例示的実施において、従前の研究努力によって考えられた分析物溶液中の段階的または実質的に瞬間的なpH変化を超えて、本発明のいくつかの実施形態に従ったISFETの動的応答に依拠する検出/測定技術は、少なくとも部分的には、(例えば、ISFET上の反応ウェルの底部における)分析物/ISFETの不動態化層界面に近接する種々のイオン性種の異なる拡散に基づく。特に、出願人らは、もし分析物/不動態化層界面に近接したイオン強度の変化によって構成される与えられた刺激が、注目する各種の適当な拡散のため、不動態化層の能力よりも有意に速い速度で起こって、濃度変化の刺激に応答してその表面電荷密度を調整するならば(例えば、不動態化層表面に関連する特徴的な応答時定数τよりも速い)、イオン強度の段階的または実質的に瞬時の変化は、ISFETからのイオンパルス出力を観察するのに必ずしも必要とされないのを認識し、認めた。この原理は、DNA配列決定の例に対してのみならず、同様に、化学物質の他のタイプおよび化学反応検知に適用可能である。

本開示の目的では、十分に速いタイムスケールで起こる分析物溶液中のイオン強度のいずれかの有意な変化によって構成された刺激に対するISFETのパルス応答を「イオンパルス」といい、ここに、該パルスの振幅は方程式(17)によって記載されて、ここに、パルスの幅および形状(経時的なパルスの上昇および崩壊)は、イオン種に関連する拡散パラメーターに関し、(方程式(18)に関連して先に議論したように、1以上の特徴的な時定数τに反映されたように)分析物/不動態化層界面において、イオン強度の変化および平衡反応キネティックスを生起させる。(18)).本明細書中で議論された種々の実施形態において、分析物/不動態化層表面に近接するイオン種の濃度変化による1以上のパルスが、もしそのような濃度変化が、濃度変化の刺激に応答してその表面電荷密度を調整する不動態化層の能力よりも速い速度で起こるならば、ISFET出力シグナルで観察できる(例えば、イオン強度の変化は時間t<<τ以内に起こる)。再度、これまでから、イオン強度の段階的または瞬時の変化(例えば、ISFET不動態化層表面に対して鉛直な方向の高い流速)は、ISFETからのイオンパルス出力を観察するのに必要とされないのは認識されるべきである。

より具体的には、(相対的により低いイオン強度、例えば、<1モル/リットルの領域におけるデバイ理論の適用性を仮定して)方程式(10)および(11)を再度参照し、ISFETがイオン強度の変化の後に同一表面ポテンシャルに再度平衡化することを考慮されたい。これは、もしデバイスクリーニング長さがλ’に変化すれば、表面電荷密度は対向量だけ変化して、表面ポテンシャル定数を保つことを示唆する、すなわち:

方程式(18)に関連して先に議論したように、表面電荷密度σは、時定数τでの時間の指数関数として近似して記載することができる。従って、もし、分析物溶液中の時間変化イオン強度I(t)のため時間−変化デバイスクリーニング長さλ(t)があれば(方程式(12)および(13)参照)、表面電荷密度は微分方程式:

に従い、表面電荷密度は、連続して、デバイスクリーニング長さが時間と共に変化するにつれて初期表面ポテンシャルを与える値まで戻ろうとするのが観察できる。

方程式(15)から、298ケルビン度の温度Tにおいては、59.2mV/pHの理論的最大pH感度はα=1で達成できるのは認識されるであろう。時間の関数としての表面ポテンシャルは、以下の

のように、方程式(10)および(11)から、デバイスクリーニング長さの項において表わすことができる。

σ(t)を含む新しい変数g(t)を導入し、かつ方程式(12)を参照し、方程式(22)は、以下の

のように、時間変化イオン強度I(t)の項において書き換えることができ、それから以下の

が得られる:

方程式(23)および(24)は、ISFET出力シグナルにおけるイオンパルスの発生および総じてのプロフィールが、共に、分析物/不動態化層界面の表面キネティックスに関連する時定数τ、および時間I(t)の関数としてのイオン強度に依存し、これは、反応ウェルにおける各イオン種の濃度によって与えられ、というのは、それらは反応および拡散のため経時的に変化するからであることを示す。前記したように、これまでのことから、出願人らは、I(t)が、(時定数τによって特徴付けられるように)再度平衡化する表面電荷密度の能力よりも速い速度で変化する限り、イオンパルス出力が観察できることを認識し、認めており、ここに、パルスの開始のプロフィールは主としてI(t)によって決定され、パルスの崩壊プロフィールは主として時定数τによって決定される。再度、これまでの分析は、一般に分析物溶液に存在する実質的にいずれのイオン種にも適用され、従って、ISFETの一過的または動的応答を開発して、種々の化学的/または生物学的活性をモニターすることができる。

核酸合成または配列決定反応の具体的例に関しては、1つの実施形態において、アレイ100の例示的ISFETを使用して、合成または配列決定試薬の、ISFETに関連する、かつ従前に負荷された鋳型を含有する対応する反応ウェルへの添加に応答する、1以上のパルスを含む出力シグナルを供することができる。図8Aおよび8Bを参照し、この実施形態に従った例示的方法において、既知のヌクレオチド(すなわち、dNTP、ここに、NはA、C、GまたはTの1つをいう)が(以下にさらに議論する)適当な拡散パラメータにて反応ウェルに導入され、合成または配列決定反応を開始させ、ISFET出力シグナルにおいて検出された、(もし多数のパルスが発生するならば)イオンパルスの数、および順次のパルスの間の時間間隔はヌクレオチド取込みについて価値ある情報を提供する。

より具体的には、ヌクレオチド取込みを検出するための1つの実施形態に従った方法において、もし反応ウェルに導入された1以上のヌクレオチドがそれらの導入に際して取り込まれれば、PPiが発生する。図8Aは、1つの例示的実施における核酸合成または配列決定反応の間における、ISFET分析物/不動態化層界面に近接する分析物における時間の関数としての種々のイオン種の(μMで表わした)濃度を示すグラフである。図8Aに示された特別な例において、プロット41は時間の関数としてのPPiの濃度を示し、およびプロット43は(秒で表わした)時間の関数としてのdNTP濃度を示す。PPiの最初の濃度増加に実質的に対応する時間t=0秒および注目する種に対する特定の拡散パラメータにて、ほぼ15秒<t<17.5秒において、PPiの濃度は突然減少し、dNTPの濃度の対応する増加があることが観察することができる。本論議の目的では、反応ウェルへの許可に際しての所与のヌクレオチドタイプdNTPの各取込みは、「取込み事象」という。図8Aの例においては、以下でさらに議論するように、多数の取込み事象が期間0<t<17.5の間に起こり、そこでは、PPi濃度は上昇する。

図8Bは、図8Aにてプロフィールを示したものと同様な例示的核酸配列決定/合成反応についての時間の関数としてのISFET出力電圧の多数のプロットを示すグラフである。前記表1および方程式(3)、(4)、(5)および(16)を参照し、二酸化ケイ素または窒化ケイ素いずれかの不動態化層および、例えば、ほぼ8〜9の分析物pHに基づき、ほぼ−200mVのオーダーの「ベースライン」ISFET出力電圧が、図8Bに示されるように予測されるはずであることを認識し得る。関連するイオン種の適当な拡散パラメータを仮定すれば、ISFETの分析物/不動態化層界面に近接するPPiの初期の発生は、1以上の取込み事象のため、十分に速いイオン強度変化刺激I(t)を構成し、それにより、前記方程式(23)に従った表面ポテンシャルΨ0の変化、および前記方程式(3)、(4)および(5)によって与えられるISFET出力シグナルの対応する変化を引き起こし、その結果、ISFET出力シグナルにおいてイオンパルスをもたらす。別の言い方をすれば、1以上の取込み事象によるPPi発生の持続に拘わらず、十分に速い刺激を構成する初期のPPi発生に続き、分析物/不動態化層界面はいくらかの定常状態平衡に戻り、それにより、初期刺激に対する一過性の応答を完成させ、ISFETシグナルにおいてパルスを生起させ、その例は図8Bに示される。一般に、図8Bから、1つの例示的実施において、与えられたイオンパルスについての崩壊プロフィールに対する時定数τは、ほぼ2〜2.5秒のオーダーとなり得ることが観察できる。しかしながら、(例えば、方程式(19)に関連して先に議論したように)本発明の種々の実施形態はこの説明的例に限定されず、というのは、時定数τは、少なくとも部分的に、所与の不動態化層の材料依存性特性、ならびに分析物溶液のバルクpHに依存し得るからであることは認識されるべきである。

図8Bにおいては、時間の関数としてのISFET出力シグナルに対する多数の異なるプロットが示され、脚注は、示された出力シグナルを生起させる取込み事象の数を示すために注意書きNpoly=x(X=0,1,2,7)を使用する。…1以上の取込み事象(Npoly≠0)に対応する出力シグナルのプロットの全ては、その各ピークがいくらかの時間間隔によって分離される2つのパルスを含む。例えば、時間間隔47によって分離されたパルス45および49を含めた出力シグナルのプロットは、図8Aに示された濃度変化に対応し、脚注注意書きNpoly=7で標識され、これは、本例示的実施における時間間隔47が7つの取込み事象を表すことを示す。

より具体的には、ヌクレオチド取込みを検出するための例示的方法において、もしPPiが1以上の取込み事象に従って発生すれば、いくつかの点取込み中断において、プロット43により図8Aに示されるように、PPiはもはや発生せず、および取り込まれていないヌクレオチド(dNTP)の濃度は増大する。もし、拡散パラメータが、dNTPの増大した濃度が、PPiによるイオンパルスの完了の後に(すなわち、分析物/不動態化層界面が最初のPPi刺激に続いて定常状態に到達した後に)起こるようなものであれば、取り込まれていないヌクレオチドのこの増大した濃度が、ISFET出力シグナルにおける第二のイオンパルスを発生する第二のイオン刺激を構成し;再度、7つの取込み事象に対応する図8Aに示された濃度変化の説明的例を用い、その各ピークが時間間隔47によって分離される、取込み事象が一旦終了すれば、図8B中のプロットNpoly=7は、初期PPi発生に対応する第一のイオンパルス45、およびdNTPの増大した濃度に対応する第二のパルス49を含む。

より一般的には、出願人らは、いくらかの時間間隔によって分離された多数のパルスを含めた図8B中のISFET出力シグナルのいずれかについて、PPi発生による第一のイオンパルスおよび取り込まれていないヌクレオチドの増大した濃度による第二のイオンパルスの間の時間の間隔は、少なくとも部分的には、取込み事象の数に関連することを認識し、認めた。更に以下に議論するように、この時間間隔は、少なくとも部分的には、限定されるものではないが、反応ウェルの寸法、ウェル内のパッキング密度、ヌクレオチド配列決定または合成反応のキネティックス、関連する種の拡散係数、ヌクレオチド濃度、およびDNAの初期の量を含めた他のパラメータに関連することができる。図8Bにおける脚注Npoly=7に関連する出力シグナルに加えて、さらなる説明の目的で、多数の他のパルスが図8Bにおいて標識されており;特に、パルス53はNpoly=3と標識された出力シグナルにおいて2つのパルスの秒を構成し(すなわち、パルス45およびパルス53の間の時間間隔は3つの取込み事象に対応し)、およびパルス55はNpoly=5と標識された出力シグナルにおいて2つのパルスの秒を構成する(すなわち、パルス45およびパルス55の間の時間間隔は5つの取込み事象に対応する)。

ヌクレオチド取込みを検出するためのこれまでの方法のもう1つの態様において、もし所与のヌクレオチドdNTPのウェルへの導入に際してヌクレオチドが取り込まれなければ、PPiは発生せず、ウェルに関連するISFETに対する第一および唯一のイオン刺激は、それがウェルに対して許容されているので、dNTPの濃度の上昇である。その結果、単一のイオンパルスのみが発生し、再度、dNTPに対する適当な拡散パラメータを仮定する。この状況が、出力シグナルにおいて単一パルス51のみを含む、図8B中のNpoly=0として標識された出力シグナルによって示される。

従って、前記した方法は、以下のように、核酸合成または配列決定反応の有意な特徴付けを供する:

1)もし単一のイオンパルスのみがISFET出力シグナルに存在するならば、反応ウェルに導入されたヌクレオチドの取込みは無い(すなわち、dNTP刺激のみ);

2)もし2つの連続したイオンパルスがISFET出力シグナルに存在するならば、反応ウェルに導入されたヌクレオチドの取込みがある、(すなわちPPi刺激、続いてのdNTP刺激);および

3)2つの連続的イオンパルスの間の時間間隔は、取込み事象の数の関数である。

ヌクレオチド取込み検出について直ぐ上で議論した種々の概念に従った方法の種々の例示的実施において、ISFET出力シグナルに1または2のパルスが存在するか否かを単に決定するのは、ヌクレオチド取込みに対して有用な情報を提供することは認識されるべきである。よって、本発明に従った全ての方法が、もし存在すれば、多数のパルスの間の時間間隔をやはり分析するのに必要であるというのではない。しかしながら、再度、いくつかの例においては、1以上のイオンパルスを生起させる各種に関連する種々の拡散パラメータを考慮し、この時間間隔は取込み事象の数に関連するさらなる有用な情報を提供し、事実、いくらかの例示的実施はISFET出力シグナルに存在するパルスの数のみならず、パルスの間のタイミングを分析する。

先に議論したヌクレオチド取込み検出のための方法に関し、かつ方程式(17)を再度参照し、出願人らは、核酸合成または配列決定反応の種々のパラメータが改善され、および/または最適化されて、ISFET出力シグナルにおける所与のイオンパルスに関連するシグナル対ノイズ比(SNR)を増加させることができる(例えば、イオンパルスの振幅ΔΨ0を増大させることができる)ことを認識し、認めてきた。

まず、方程式(17)から、より高い初期平衡表面ポテンシャルΨ1(すなわち、所与のヌクレオチドdNPTの反応ウェルへの導入前の洗浄緩衝液の存在下における定常状態表面ポテンシャル)は、一般に、イオンパルスについてのより高い振幅ΔΨ0をもたらすことが認められる。1つの態様において、方程式(16)を再度参照し、出願人らは、より高いΨ1は、ISFETの不動態化層のpHpzc(すなわち、不動態化層表面においてゼロ電荷密度をもたらすバルク分析物pH)とは有意に異なるpHを有する洗浄緩衝液の選択によって促進されることを認めた。よって、種々の実施において、洗浄緩衝液は、不動態化層で使用される材料のタイプに基づいて適切に選択することができる。

方程式(15)から、298ケルビン度の温度Tにおいては、59.2mV/pHの理論的最大pH感度はα=1で達成できるのは認識されるであろう。方程式(15)から、出願人らは、ISFETの比較的高いpH感度(ΔΨ0/ΔpH)はより高いΨ1に寄与することもでき;このようにして、方程式(15)に関連して先に議論したように、大きな固有の緩衝能力βintを持つ不動態化層材料が望ましく、これは、方程式(15)に与えられた無次元感度因子αは大きなβintによって増加するからであることも認めた。また、しかしながら、この点に関しては、pHに対する高い感度は先に記載した特異的実施形態に従ったヌクレオチド取込み検出方法において必ずしも要件ではなく、これは、該方法は、主として、PPiおよびdNTP濃度変化の検出を前提としており、水素イオン濃度それ自体の測定を前提とするものではないからであることも認められるべきである。この状況は、(例えば、MOSFET本体効果を考慮して)より限定されたpH測定範囲および低下した直線性の要件の考慮に基づき、本明細書中で議論された種々のISFETアレイ最適化技術の前記した方法への適用性を強調する。もちろん、事実、本明細書中で議論された本発明の他の実施形態に従った方法は、反応インジケーターとしての水素イオン濃度および濃度変化に依拠することができる。いずれの場合においても、前記したように、出願人らは、有意に制限されたpH範囲にわたってさえ、ISFETの比較的高いpH感度は、いくつかの例においては、イオンパルスについての増大した振幅ΔΨ0および、よって、ISFET出力シグナルの増大したSNRを促進することができるのを認めた。

加えて、出願人らは、方程式(17)から、(dNTPの導入に先立って洗浄緩衝液から生じる)分析物溶液中の初期イオン強度による初期二重層キャパシタンスCdl,1の低下または最小化、および/または濃度変化刺激(すなわち、PPiの発生またはdNTPの増加)から生じる引き続いての二重層キャパシタンスCdl,2の増加または最大化もまたイオンパルスに対するより高い振幅ΔΨ0をもたらすことを認めた。従って、種々の実施において、低イオン強度緩衝液を適切に選択して、イオンパルスに対する増大した振幅ΔΨ0および、よって、ISFET出力シグナルの増大したSNRを促進することができる。

時間分解能に関して、先に示唆したように、パルス形状、ならびにいずれかの2つのパルスの間の時間間隔のいくつかの態様は、時間、および注目する種々のイオン種がISFETの分析物/不動態化層界面に近接して発生する速度の関数である。これらの点における重要なパラメータの例は、限定されるものではないが、分析物溶液の種々の構成要素(例えば、種々の試薬)が反応ウェルに受け入れられる流速、種々の種の各濃度および/または集合的濃度、ウェルに存在する鋳型材料の量、ウェルで起こり得る核酸配列決定または合成反応のキネティックス、および反応ウェルにおける種の拡散に影響する種々の因子(例えば、種々の種の拡散係数、反応ウェルの幾何学/寸法、パッキングビーズの存在およびサイズ、密度に影響する分析物溶液に対する添加剤)を含む。一般に、ISFET出力シグナルにおける1以上のイオンパルスの時間分解能に関連するパラメータは以下により詳細に議論する。

前記したように、いくつかの実施形態においては、pHの変化は、新しく合成された核酸ストランドに取り込まれたヌクレオチドの数に比例するので、ISFETを使用して、定常状態pH値を測定することができる。以下でより詳細に議論される他の実施形態において、FETセンサーアレイは、特に、注目する化学反応についての関連情報を供することができる他の分析物に対する感度に対して構成することができる。そのような修飾または構成の例は、本明細書中においてより詳細に議論するように、注目する分析物に結合するための分析物−特異的受容体の使用である。

(やはりコンピュータ260操作下にある)アレイコントローラ250を介して、ISFETアレイは、分析物の検出および/または測定に関連するデータ(例えば、アレイの各ISFETの出力シグナル)を獲得するように制御することができ、収集されたデータはコンピュータ260によって処理されて、鋳型核酸の(配列決定を含めた)プロセッシングに関する有意義な情報を得ることができる。

図8に示された系1000のISFETアレイ100に関しては、1つの実施形態において、1以上の分析物および/または反応をモニターし/測定するのに必要な全てのセンサーおよびエレクトロニクスを含む、標準CMOSプロセス(例えば、0.35マイクロメートルプロセス、0.18マイクロメートルプロセス)を用いて設計され、製造された集積回路としてアレイ100は実施される。再度、図1を参照し、ISFETアレイ100に関連して使用されるべき1以上の参照電極76を(例えば、フローセルの「使用されない」ウェルに配置された)フローセル200に入れることができ、そうでなければ、参照(例えば、配列決定試薬172の1以上)に暴露して、それに対してアレイ100の各ISFETに近接する分析物濃度の変化が比較されるベースラインを確立することができる。参照電極76はアレイ100、アレイコントローラ250、または直接的にコンピュータ260に電気的にカップリングさせて、アレイ100から得られた電圧シグナルに基づいて分析物測定を容易とすることができ;いくつかの実施においては、参照電極は電気的アースまたは他の所定のポテンシャルにカップリングさせることができるか、あるいは参照電極電圧をアースに関して測定して、以下にさらに議論するように、ISFET出力シグナル測定のための電気的参照を確立することができる。

ISFETアレイ100は、限定されるものではないが、2〜256のようにできるだけ少ない画素(例えば、二次元実施における16×16画素)を含めた一次元または二次元アレイとして、または54メガのようにできるだけ多い画素(例えば、二次元実施において7400×7400画素)として、任意の特定のサイズに限定されない。あるいは本明細書中に開示された概念に従った種々の化学的/生物学的分析目的で、より大きなものさえ製造し、使用することができる。図8に示された例示的系の1つの実施形態において、アレイの個々のISFETセンサーは、PPi、取り組まれていないヌクレオチド、水素イオン等に対する感度のために構成することができ;しかしながら、ISFETセンサーアレイの個々のセンサーは、種々の適用(例えば、ナトリウム、銀、鉄、臭素、ヨウ素、カルシウム、および硝酸塩のような他のイオンに対して感受性の材料は知られている)のためのイオン濃度の他のタイプに対する感度について特に構成することができるので、本開示はこの点において限定されないことも認められるべきである。

より一般的には、本開示の種々の実施形態に従ったchemFETアレイは、種々の分析物のいずれか1以上に対する感度について構成することができる。1つの実施形態において、アレイの1以上のchemFETは、1以上の分析物および/または1以上の結合事象に対する感度について特に構成することができ、他の実施形態においては、所与のアレイの異なるchemFETを、異なる分析物に対する感度について構成することができる。例えば、1つの実施形態において、アレイの1以上のセンサー(画素)は、第1の分析物に対して感受性であるように構成された第1のタイプのchemFETを含むことができ、およびアレイの1以上の他のセンサーは、第1の分析物とは異なる第2の分析物に対して感受性であるように構成されたchemFETの第2のタイプを含むことができる。1つの例示的な実施において、第1および第2の双方の分析物は、例えば、合成方法による配列決定におけるヌクレオチド取込のような特定の反応を示すことができる。もちろん、chemFETの2を超える異なるタイプをいずれかの所与のアレイで使用して、分析物および/または他の反応の異なるタイプを検出し、および/または測定することができることも認められるべきである。一般に、本明細書中で議論されたセンサーアレイの実施形態のいずれにおいても、所与のセンサーアレイは「均一」であってよく、実質的に同様なまたは同一のタイプのchemFETを含んで、分析物の同一タイプ(例えば、pHまたは他のイオン濃度)を検出し、および/または測定することができ、あるいはセンサーアレイは「不均一」であってよく、異なるタイプのchemFETを含んで、異なる分析物を検出し、および/または測定することができる。議論を簡単にするために、再度、ISFETの例をセンサーアレイの種々の実施形態において以下に議論するが、本開示はこの点において限定されず、分析物感度についての数個の他のオプションを(例えば、図11Aに関して)以下にさらに詳細に議論する。

種々の分析物のいずれか1以上に対する感度について構成されたchemFETアレイはエレクトロニクスチップに配置することができ、各チップは1以上の異なる生物学的反応を行うように構成することができる。ピンが、アレイの特徴、および/またはいずれの種類の生物学的反応が特定のチップで行われるべきかに関して、情報を系に運ぶような方法で暗号化されたピンによってアレイ出力を読む前記系の部分に、エレクトロニクスチップを結合させることができる。

1つの実施形態において、本発明は、チップおよび/またはチップで行うべき反応のタイプの特徴を同定する回路に情報を送達するための1以上のピンを含む、生物学的反応をそこで行うために構成されたエレクトロニクスチップを含む。そのようなtは限定されるものではないが、短ヌクレオチド多形検出、短タンデムリピート検出、または配列決定を含むことができる。

もう1つの実施形態において、本発明は:チップを受領するのに適合させたチップ受領モジュール;およびエレクトロニクスチップからの情報を検出するためのレシーバーを含む、1を超える生物学的反応をチップ上で実行するのに適合させた系を含み、ここに、情報はチップで行うべき生物学的反応を決定する。典型的には、該系は、さらに、選択された生物学的反応を行うための1以上の試薬を含む。

もう1つの実施形態において、本発明は:反応チャンバーの空間的位置、空間的位置に加えられたモノマーのタイプ、複数のモノマーを含む試薬と延長ポリマーとの完全な反応に要する時間についての情報をリレーするように構成された少なくとも1つの集積回路を含む、ポリマー鋳型を配列決定する装置を含む。

0.35マイクロメートルCMOSプロセッシング技術(またはより小さな特徴サイズが可能なCMOSプロセッシング技術)に基づく例示的な実施において、ISFETアレイ100の各画素は、ISFETおよび伴う可能化/選択成分を含むことができ、ほぼ10マイクロメートル×10マイクロメートル(すなわち、100マイクロメートル2)以下のアレイの表面に面積を占有することができ;別の言い方をすれば、10マイクロメートル以下のオーダーのピッチ(画素間隔の画素−対−中心の中心)を有するアレイを実現することができる。0.35マイクロメートルCMOSプロセッシング技術を用いる10マイクロメートル以下のオーダーのアレイピッチは、ISFETアレイを製造する従前の試みに対するサイズ低下の点での有意な改良を構成し、その結果、少なくとも12マイクロメートル以上のオーダーの画素サイズがもたらされた。

より具体的には、本明細書中で開示された発明的概念に基づいて以下にさらに議論するいくつかの実施形態において、ほぼ9マイクロメートルのアレイピッチは、関連行および列選択およびバイアス/読み出しエレクトロニクスと共に、256,000を超える画素を含めたISFETアレイ(例えば、512×512アレイ)が、7ミリメートル×7ミリメートル半導体ダイ上に製造されることを可能とし、および400万を超える画素含めた同様なセンサーアレイ(例えば、4メガを超える画素を生じる2048×2048アレイ)が、21ミリメートル×21ミリメートルダイ上で製造されるのを可能とする。他の例において、ほぼ5マイクロメートルのアレイピッチは、ほぼ1.55メガ−画素を含めたISFETアレイ(例えば、1348×1152アレイ)および関連エレクトロニクスが、9ミリメートル×9ミリメートルダイ上で製造され、および14メガを超える画素を含めたISFETセンサーアレイおよび関連エレクトロニクスが22ミリメートル×20ミリメートルダイ上で製造されるのを可能とする。なお他の実施において、0.35マイクロメートル未満の特徴サイズが可能である(例えば、0.18マイクロメートルCMOSプロセッシング技術)CMOS製造プロセスを用い、5マイクロメートルよりもかなり小さなピッチを持つISFETセンサーアレイを製造することができ(例えば、2.6マイクロメートルのアレイピッチ、または8または9マイクロメートル2未満の画素面積)、有意に密なISFETアレイを提供する。もちろん、(例えば、ほぼ20、50、100マイクロメートル以上のオーダーの)10マイクロメートルを超える画素サイズを、やはり本開示に従って、chemFETアレイの種々の実施形態で実施することができるのは認められるべきである。

当業者によって理解されるように、配列決定反応をミニチュア化する能力は、(ヒトゲノムのような)大きなゲノムの配列決定に関与する時間、コストおよび労力を低下させる。

図8に示される系の他の態様において、1以上のアレイコントローラ250を使用して、ISFETアレイ100を操作することができる(例えば、分析物測定を表す出力シグナルを得るためのアレイの各画素の選択/可能化)。種々の実施において、1以上のアレイコントローラを構成する1以上の構成要素を、ICチップの異なる部分におけるのを除いてアレイと同一の集積回路(IC)チップ、またはオフ−チップ上で、アレイそれ自体の画素エレメントと共に実施することができる。アレイ制御に関しては、ISFET出力シグナルのアナログ−デジタル変換はセンサーアレイ領域の外側に位置することを除いて、ISFETアレイと同一の集積回路チップ上で実施される回路によって行うことができる(センサーアレイ領域の外側にアナログ−デジタル変換回路を位置させるのは、より小さなピッチおよび、よって、より大きな数のセンサー、ならびに低下したノイズを可能とする)。以下にさらに議論される種々の例示的な実施において、アナログ−デジタル変換は、必要とされるシグナルの動的レンジに依存して、4−ビット、8−ビット、12−ビット、16−ビットまたは他のビット分解能であり得る。

本明細書中で用いるように、アレイはセンサーまたはウェルのようなエレメントの平面上配置である。該アレイは一次元または二次元であってよい。一次元アレイは、第1の次元においてエレメントの1つの列(または行)、および第2の次元において複数の列(または行)を有するアレイである。一次元アレイの例は1×5アレイである。二次元アレイは、第1および第2の次元双方において複数の列(または行)を有するアレイである。第1および第2の次元における列(または行)の数は同一であっても同一でなくてもよい。二次元アレイの例は5×10アレイである。

1以上の分析物を測定するための例示的系1000におけるchemFET(例えば、ISFET)アレイ100の役割の一般的概観を提供してきたが、以下に、種々の適用で使用することができる本開示の種々の発明的実施形態に従った例示的chemFETアレイのより詳細な記載を掲げる。再度、説明の目的で、本開示に従ったchemFETアレイを、ISFETアレイの特定の例を用いて以下に議論するが、chemFETの他のタイプを代替実施形態で使用してもよい。また、再度、説明の目的で、核酸配列決定適用の関連においてchemFETアレイを議論するが、本発明はそれに限定されるものではなく、むしろ、本明細書中に記載されたchemFETアレイについての種々の適用が考えられる。

先に述べたように、本明細書中で開示された種々の発明的実施形態は、図1〜7に関連して先に議論されたMilgrew et al.のISFETアレイ設計、ならびに他の従前のISFETアレイ設計を具体的に改良して、画素のサイズおよびアレイのピッチを有意に低下させ、それにより、所与の半導体ダイのサイズについてのISFETアレイの画素の数を増加させる(すなわち、画素密度を増加させる)。いくつかの実施において、画素密度の増加は、同時に、1以上の分析物に関する各測定に対応する出力シグナルのシグナル−対−ノイズ比率(SNR)、およびそのような出力シグナルをアレイから読むことができるスピードを増加させつつ達成される。特に、出願人らは、ISFET直線性に対する要件を緩和し、より制限されたシグナル出力/測定レンジ(例えば、1〜14よりむしろ、ほぼ7〜9以下のpH範囲に対応するシグナル出力、ならびに試料中のpH変化に有意に必ずしも関連しない出力シグナル)に焦点を当てることによって、個々の画素の複雑性およびサイズを有意に低下させることができ、それにより、非常に大規模な密なISFETアレイの実現を促進させることができることを認識し、認めてきた。

この目的で、図9は本開示の1つの発明的実施形態に従ったISFETアレイ100の1つの列102jを示し、ここに、ISFET画素設計は認識可能に単純化されて、小さな画素サイズを容易とする。列102jはnの画素を含み、その最初および最後を画素1051および105nとして図9に示す。図13に関連してさらに以下で議論するように、図9に示された列設計に基づく完全な二次元ISFETアレイ100は、一般に並んで配置される画素の連続的列を伴うmのそのような列102j(j=1、2、3、・・・m)を含む。もちろん、ISFETは、ハニカムパターンにおけるように、行−列グリッド以外にアレイ化してもよい。

図9に示された実施形態の1つの態様において、列102

jの各画素105

1〜105

nは、3つの構成要素のみ、すなわち、(Q1とも標識される)ISFET150、および2つのMOSFETスイッチQ2およびQ3を含む。MOSFETスイッチQ2およびQ3は、共に、nの行選択シグナル(

から

ロジック低活性)の内の1つに対して反応性であって、列102

jの所与の画素を可能とし、またはそれを選択する。列の全ての画素に適用される例として画素105

1を用い、トランジスタスイッチQ3は、ライン118

1を介する対応する行選択シグナルの受領に際して、ライン112

1を介して制御可能な電流ソース106

jをISFET150のソースにカップリングさせる。トランジスタスイッチQ2は、対応する行選択シグナルの受領に際して、ライン114

1を介して、ISFET150のソースを列バイアス/読出回路110

jにカップリングさせる。ISFET150のドレインは、ライン116

1を介して、バイアス/読み出し回路110

jに直接的にカップリングされる。かくして、画素当たり4つのシグナルラインのみ、すなわち、ライン112

1、114

1、116

1および118

1が、画素105

1の3つの構成要素を操作するのに必要とされる。mの列のアレイにおいて、所与の行選択シグナルが(例えば、各列における同一位置において)各列の1つの画素に同時に適用される。

図9において説明されるように、1つの実施形態に従った列102jについての設計は、図3に示されたMilgrew et al.の列設計に関連して先に議論したものと同様な一般的原理に基づく。特に、各画素のISFETは、可能とされると、一定のドレイン電流IDjおよび一定のドレイン−対−ソース電圧VDSjとで構成されて、前記方程式(3)に従って、可能とされた画素からの出力シグナルVSjを得る。この目的で、列102jは、列の全ての画素によって共有されて、可能とされた画素のISFETに一定のドレイン電流IDjを供する、アナログ回路陽性供給電圧VDDAにカップリングされ、かつバイアス電圧VB1に応答性である、制御可能な電流ソース106jを含む。1つの態様において、電流ソース106jは、2つの長−チャネルの長さおよび高い出力インピーダンスMOSFETを含めた電流ミラーとして実施される。また、該列は、やはり該列の全ての画素によって供給されて、可能とされた画素のISFETへ一定のドレイン−対−ソース電圧を供給するバイアス/読出回路110jも含む。バイアス/読出回路110jはケルビンブリッジ構成に基づき、バッファ増幅器として構成され、かつアナログ回路陽性供給電圧VDDAおよびアナログ供給電圧アースVSSAにカップリングされた、2つの操作増幅器107A(A1)および107B(A2)を含む。バイアス/読出回路は、アナログアースVSSAにカップリングされ、かつバイアス電圧VB2に対して応答性である、(電流ソース106jと同様な)制御可能な電流シンク108j、およびダイオード−連結MOSFET Q6も含む。バイアス電圧VB1およびVB2はタンデムに設定/制御されて、相補的なソースおよびシンク電流を供する。電流シンク108jによって引かれた電流の結果としてのダイオード−結合MOSFET Q6を横切って発生した電圧は操作増幅器によって強制されて、一定のドレイン−ソース電圧VDSjとして、可能とされた画素のISFETのドレインおよびソースを横切って出現する。

図3に説明されたMilgrew et al.の設計において示されたレジスタRSDjよりはむしろ、図9のバイアス/読出回路110jにおいてダイオード−連結MOSFET Q6を使用することによって、かなりの利点がCMOS製造プロセスにおいて提供され;具体的には、マッチングレジスタは、一般に±20%のオーダーの誤差許容でもって製造することができ、他方、CMOS製造プロセスにおけるMOSFETマッチングは±1%以上のオーダーである。一定のISFETドレイン−対−ソース電圧VDSjを供することを担う構成要素を列から列へマッチさせることができる程度は、列から列への測定精度(例えば、食い違い)に有意に影響する。かくして、レジスタよりはむしろMOSFET Q6を使用することは、列から列への測定食い違いを認識可能に緩和する。さらに、レジスタおよびISFETの熱的ドリフト特徴は認識可能に異なり得るが、MOSFETおよびISFETの熱的ドリフト特徴は、もし実質的に同一でなければ、実質的に同様であり;よって、MOSFE Q6におけるいずれの熱的ドリフトも、ISFET Q1からのいずれの熱的ドリフトも実質的にキャンセルし、その結果、アレイ温度の変化に伴ってより大きな測定安定性がもたらされる。

図9において、列バイアス/読出回路110jは、列からの出力シグナルVCOLjを供するための試料/ホールドおよびバッファ回路も含む。特に、画素1051〜105nのうちの1つを各画素においてトランジスタQ2およびQ3を介して可能とし、または選択した後に、増幅器107A(A1)の出力、すなわち、緩衝化VSjは、列試料およびホールドシグナルCOL SHに対して応答性であるスイッチ(例えば、伝達ゲート)の操作を介して、列試料およびホールドキャパシタCshに貯蔵される。試料およびホールドキャパシタのための適当なキャパシタンスの例は、限定されるものではないが、ほぼ500fF〜2pFの範囲を含む。サンプリングされた電圧は列出力バッファ増幅器111j(BUF)を介して緩衝化され、列出力シグナルVCOLjとして供される。図9にやはり示されるように、参照電圧VREFは、制御シグナルCALに対して応答性のスイッチを介して、バッファ増幅器111jに適応して、バッファ増幅器111jによる列間の非均一性の特徴付けを容易とし、かくして、読出後データ修正を可能とする。

図9Aは、バイアス/読出回路110jの増幅器107Aの1つについての例示的な回路ダイアグラムを示し(増幅器107Bは同一に実施され)、および図9Bは、増幅器107Aおよび107Bについての増幅器バイアスvs.バンド幅のグラフである。図9Aに示されるように、増幅器107Aは9つのMOSFET(M1〜M9)に基づいて多数の電流ミラーの配置を使用し、単位利得バッファとして構成され、そこでは、増幅器の入力および出力は、各々、IN+およびVOUTとして一般性について標識される。(対応するバイアス電流を表す)バイアス電圧VB4は増幅器のトランスインピーダンスを制御し、バンド幅の対照(すなわち、増大した電流を伴う増大したバンド幅)として働く。図9を再度参照し、試料およびホールドキャパシタCshのため、増幅器107Aの出力は、試料およびホールドスイッチが閉じられると、フィルタを実質的に駆動する。従って、認識可能に高いデータ速度を達成するには、バイアス電圧VB4を調整して、より高いバイアス電流および増大した増幅器バンド幅を供することができる。図9Bから、いくつかの例示的実施においては、少なくとも40MHzおよび有意にそれよりも大きな増幅器バンド幅が実現することができるのが観察できる。いくつかの実施において、100MHzと高い増幅器バンド幅は適切であって、高いデータ獲得率および(例えば、10〜20マイクロ秒のオーダーの)比較的より低い画素試料または「滞留」時間を容易とすることができる。

図9に示された実施形態のもう1つの態様において、図3に示されたMilgrew et al.の画素設計とは異なり、画素1051〜105nは、いずれかの伝達ゲート、またはn−チャネルおよびp−チャネル双方のFET構成要素を必要とする他のデバイスを含まず;特に、この実施形態の画素1051〜105nは同一タイプのFETデバイスのみを含む(すなわち、n−チャネルのみまたはp−チャネルのみ)。説明の目的で、図9に示された画素1051および105nは、p−チャネル構成要素のみ、すなわち、2つのp−チャネルMOSFET Q2およびQ3およびp−チャネルISFET 150を含むものとして示される。ISFETのソースをバイアス/読出回路110jにカップリングさせるために伝達ゲートを使用しないことによって、ISFET出力シグナル(すなわち、ISFETソース電圧VS)についてのいくらかの動的レンジを犠牲にすることができる。しかしながら、出願人らは、潜在的にいくらかの出力シグナル動的レンジに先行し(それにより、pHまたは他のイオン種の濃度変化のような所与の静的および/または動的化学的特性についての測定範囲を潜在的に制限する)ことによって、各画素における異なるタイプのFETデバイス(n−チャネルおよびp−チャネル双方)の要件を排除することができ、画素構成要素のカウントを低下させることができるのを認識し、認めてきた。図10〜12に関連してさらに以下で議論するように、これは、画素サイズの低下を有意に促進する。かくして、1つの態様において、低下した動的レンジおよびより小さな画素サイズの間で有益なトレードオフがある。

図9に示された実施形態のなおもう1つの態様において、Milgrew et al.の画素設計とは異なり、各画素1051〜105nのISFET 150はそのソースにつながれたその本体結合を有しない(すなわち、本体結合およびISFETのソースが操作の間に強制的に同一の電気ポテンシャルとなるような、それらをカップリングさせる導電体は無い)。むしろ、アレイの全てのISFETの本体結合は相互に結ばれ、本体バイアス電圧VBODYにつながれる。図9において明示的には示されてないが、MOSFET Q2およびQ3についての本体結合は、同様に、それらの各ソースにつながれていないが、むしろ本体バイアス電圧VBODYにつながれている。全てのp−チャネル構成要素を有する画素に基づく1つの例示的実施において、本体バイアス電圧VBODYは、図17との関係で以下にさらに議論するように、アレイ(例えば、VDDA)に利用可能な最高の電圧ポテンシャルにカップリングされている。

各ISFETのそのソースへの本体結合を試みないことによって、いくらかの非−ゼロのソース−対−本体電圧VSBの可能性は、図1に関連して先に議論したように、「本体効果」を生起させることができ、これは非線形関係に従ってISFETの閾値電圧VTHに影響する(かくして、方程式(3)、(4)および(5)によると、分析物活性の検出および/または測定に影響しかねず、分析物/不動態化層界面において表面ポテンシャルの変化を生起させる)。しかしながら、出願人らは、低下したISFET出力シグナル動的レンジに焦点を当てることによって、非−ゼロのソース−対−本体電圧からISFETにおいて生じるであろういずれの本体効果も相対的に最小であろうことを認識し、認めてきた。かくして、低下した動的レンジにわたって得られるであろういずれの測定非直線性も、(例えば、図17に関連して以下でさらに議論するように、アレイキャリブレーションおよびデータプロセッシング技術を介して)有意でないとして無視するか、あるいは考慮し、補償することができる。また、出願人は、その本体結合に対する各ISFETソースを試みないことによって、画素を構成するFETの全ては共通の本体結合を共有することができ、それにより、図10〜12に関連して以下でさらに議論するように、画素サイズの低下をさらに容易とすることができる。従って、もう1つの態様において、低下した直線性およびより小さな画素サイズの間に有益なトレードオフがある。

図10は、本開示の1つの発明的実施形態に従った、図9に示された画素1051についてのチップレイアウト設計の頂面図を示す。図11Aは、画素製造の層×層図を示す、線II――IIおよびIII――IIIの間の図10の右半分におけるさらなるエレメントを含めた、図10に示された画素の線I――Iに沿った複合断面図を示し、および図12A〜12Lは図11Aに示された製造層の各々の頂面図を供する(図12A〜12Lの各像はもう1つの頂部に重ねられて、図10に示された画素チップレイアウト設計を生じる)。1つの例示的な実施において、図10〜12に示された画素設計は、標準4−金属、2−ポリ、0.35マイクロメートルCMOSプロセスを用いて実現して、ほぼ9マイクロメートルの図10に示された寸法「e」、およびほぼ7マイクロメートルのISFET感受性エリアに対応する寸法「f」を有する幾何学的に四角形の画素を供することができる。

図10の頂面図において、(図10においてQ1と標識された)ISFET150は、一般に、画素説明の右側中心部分を占有し、およびISFETのゲート、ソースおよびドレインの各位置はQ1G、Q1SおよびQ1Dとして示される。MOSFET Q2およびQ3は、一般に、画素説明の左側中心部分を占有し;MOSFET Q2のゲートおよびソースはQ2GおよびQ2Sとして示され、およびMOSFET Q3のゲートおよびソースはQ3GおよびQ3Sとして示される。図10に示されるレイアウトの1つの態様において、MOSFET Q2およびQ3は、Q2/3Dとして示されたドレインを共有する。もう1つの態様において、一般に、ISFETは、そのチャネルが画素の第1の軸に沿って(例えば、線I――Iと平行に)存在するように形成され、他方、MOSFET Q2およびQ3は、それらのチャネルが第1の軸に対して垂直な第2の軸に沿って存在するのは、図10の頂面図から観察できる。また、図10は、画素を操作するのに必要な4つのライン、すなわち、Q3のソースにカップリングされたライン1121、Q2のソースにカップリングされたライン1141、ISFETのドレインにカップリングされたライン1161、およびQ2およびQ3のゲートにカップリングされた行選択ライン1181を示す。図9を参照し、所与の列における全ての画素は(例えば、図10中の画素を垂直方向に横切って走る)ライン112、114および116を共有し、所与の行における全ての画素は(例えば、図10中の画素を水平方向に横切って走る)ライン118を共有することは認めることができる;かくして、図9の画素設計および図10に示されたレイアウトに基づき、4つの金属線のみが各画素を移動するのに必要である。

ここで、図11Aの断面図を参照し、n−ウェル154中の(図10中の線I――Iに沿って存在する)高度にドープされたp−タイプの領域156および158は、ISFET多結晶シリコンゲート164およびゲート酸化物165下方にISFET p−チャネルが形成されるn−ウェルの領域160がその間に存在する、ISFETのソース(S)およびドレイン(D)を構成する。図10および11に示された発明的実施形態の1つの態様に従い、画素1051のFET構成要素の全ては、p−タイプの半導体基板152に形成された単一のn−タイプウェル154においてp−チャネルFETとして製造される。Milgrew et al.の設計とは異なり、1)画素における伝達ゲートについて要件はなく;および2)ISFETソースはnーウェルの本体結合に結び付けられていないゆえに、これは可能である。より具体的には、高度にドープされたn−タイプ領域162はn−ウェル154に対する本体結合(B)を供し、図10に示されるように、本体結合Bは、画素1051の周辺の周りの金属導電体322にカップリングされている。しかしながら、本体結合はISFETのソース領域156に直接的に電気的にカップリングされておらず(すなわち、本体連結およびソースを、それらが強制的に操作の間に同一電気ポテンシャルにあるようにそれらをカップリングする導電体はない)、また、画素中のいずれかの構成要素のゲート、ソースまたはドレインに直接的に電気的にカップリングした本体結合はない。かくして、画素の他のp−チャネルFET構成要素、すなわち、Q2およびQ3は同一のn−ウェル154において製造することができる。

図11Aの複合断面図において、MOSFET Q2およびQ3の共有されたドレイン(D)に対応する、高度にドープされたp−タイプの領域159も目に見える(図10において線I――Iに沿って存在する)。説明の目的で、MOSFET Q3の多結晶シリコンゲート166もまた図11A中に見えるが、このゲートは、図10中の線I――Iに沿って存在せず、むしろ、線I――Iに沿った断面の「面の背後に」存在する。しかしながら、簡単のために、図10に示されたMOSFET Q2およびQ3の各ソース、ならびにQ2のゲートは図11Aでは見えない。というのは、それらは共有されたドレインと同一の軸に沿って(すなわち、図の面に対して垂直に)存在するからである(もし図11Aに示されるならば、これらのエレメントは図11Aの複合断面図を不当に複雑とするであろう)。

図11Aに示された基板、ゲート酸化物、および多結晶シリコン層の上方に、多数のさらなる層が設けられて、それを通って導電性通路が形成される交互の金属層および酸化物層を含めた、種々の画素構成要素に対する電気的結合を確立する。4−金属CMOSプロセスの例に従い、これらの層は図11Aにおいて「接触」、「金属1」、「通路1」、「金属2」、「通路2」、「金属3」、「通路3」、および「金属4」として標識される。(より多いまたはより少ない金属層を使用してもよいことに留意されたい)。特に、ISFET電気的連結の理解を容易とするために、図11Aの複合断面図は、線II――IIおよびIII――IIIの間の、図10の頂面図の右側に、画素製造のさらなるエレメントを示す。ISFET電気的結合に関しては、最も頂部の金属層304は、その上方に、分析物―感受性不動態化層172が配置された、ISFET感受性エリア178に対応する。ISFET多結晶シリコンゲート164、および介在導電体306、308、312、316、320、326および338と共に、最も頂部の金属層304は、図1に示された慣用的ISFET設計と関連して先に議論されたのと同様な方法で、ISFET「フローティングゲート」構造170を形成する。ISFETドレインに対する電気的結合は、ライン1161にカップリングされた導電体340、328、318、314および310によって供される。ISFETソースは、導電体334および336および(図10中の線I−Iに沿って存在する)導電体324を介してMOSFET Q2およびQ3の共有されたドレインにカップリングされている。n−ウェル154に対する本体結合162は、導電体330および332を介して、「金属1」層上の画素の周辺の周りの金属導電体322に電気的にカップリングされている。

先に示したように、図12A〜12Lは、図11Aに示された製造層の各々の頂面図を供する(図12A〜12Lの各像はもう1つのものの頂部に重ねられて、図10に示された画素チップレイアウト設計を作り出す)。図12において、各層の文字を入れた頂面図、および図11Aの断面図の間の対応は以下の通りである;A)n−タイプのウェル154;B)インプラント;C)拡散;D)多結晶シリコンゲート164(ISFET)および166(MOSFET Q2およびQ3);E)接触;F)金属1;G)通路1;H)金属2;I)通路2;J)金属3;K)通路3;L)金属4(ISFETゲートに接触する頂部電極)。図12A〜12Lに示された種々の参照数字は、図11Aの複合断面図に存在する同一の特徴に対応する。

出願人らは、少なくともいくつかの適用においては、画素キャパシタンスは分析物測定のいくつかのタイプについてサイレントパラメータであってよいことを認識し、認めてきた。従って、画素レイアウトおよび設計に関連するもう1つの実施形態において、種々の通路および金属層は、寄生キャパシタンスについてのポテンシャルを少なくとも部分的に緩和して、画素操作の間に生起するように再度構成することができる。例えば、1つのそのような実施形態において、シグナルライン1121、1141、1161および1181、およびフローティングゲート構造170を構成する最も頂部の金属層304の間により大きな垂直方向の距離があるように画素は設計される。

直前に記載した実施形態において、再度図11Aを参照し、最も頂部の金属層304は金属4層中に形成され(また、図12L参照)、シグナルライン1121、1141、および1161は金属3層中に形成される(また、図12J参照)のは容易に観察できるであろう。また、図11Aの図においては見えないが、シグナルライン1181は金属2層中に形成されるのは図12Hから観察できる。これらのシグナルの1以上はアレイ操作の間に時々アースすることができるので、寄生キャパシタンスは、これらのシグナルラインのいずれかの1以上、および金属層304の間で生起することができる。これらのシグナルラインおよび金属層304の間の距離を増加させることによって、それらの寄生キャパシタンスは低下させることができる。

この目的で、もう1つの実施形態においては、いくつかの通路および金属層は、シグナルライン1121、1141、1161および1181が金属1および金属2層において実施され、金属3層が、フローティングゲート構造170の金属2層構成要素、および最も頂部の金属層304の間のジャンパーとしてのみ用いられ、それにより、シグナルラインおよび金属層304の間のより大きな距離を確実とするように再構成される。図10−1は、図9に示されたchemFETアレイの4つの隣接する画素のクラスターについてのそのようなチップレイアウト設計の正面図を示し、1つの特定の画素1051が同定され、標識されている。図11A−1は、画素製造の層×層図を示す、線II――IIの間の更なるエレメントを含めた図10―1に示された画素1051の線I――Iに沿った、隣接する画素の複合断面図を示し、図12―1A〜図12−1Lは、図11A−1に示された製造層の各々の頂面図を供する(図12−1A〜12−1Lの各像はもう1つのものの頂部に重ねられて、図10−1に示された画素チップレイアウト設計を作り出す)。

図10−1においては、画素頂面図レイアウトは、一般に、図10に示されたものと同様であることが観察できる。例えば、頂面図においては、ISFET 150は、一般に、各画素の右側中心部分を占有し、およびMOSFET Q2およびQ3は、一般に、画素説明の左側中心部分を占有する。図10に含まれた構成要素標識の多くは明瞭性のために図10−1から省略されているが、ISFET多結晶シリコンゲート164は、向きのために画素1051に示される。図10−1は、画素を操作するのに必要な4つのライン(1121、1141、1161および1181)も示す。図10および図10−1の間の1つの注目される差は、本体領域162に対する電気的結合を提供する(金属1層上に位置する)金属導電体322に関し;すなわち、図10においては、導電体322は画素の周辺を囲い、他方、図10−1においては、導電体322は画素の周辺を完全には囲わないが、不連続727を含む。これらの不連続727は、ライン1181が、金属1層上で製造され、画素を通って、行の隣接する画素に結合するのも可能とする。

ここで、図11A−1の断面図を参照し、3つの隣接する画素が断面に示され、中央画素は議論の目的で図10−1中の画素1051に対応する。図11Aの実施形態におけるように、画素1051のFET構成要素の全ては、単一のn−タイプのウェル154においてp−チャネルFETとして製造される。加えて、図11Aにおけるように、図11A−1の複合断面図においては、MOSFET Q2およびQ3の共有されたドレイン(D)に対応して、高度にドープされたp−タイプの領域159も目に見える(図10−1中の線I――Iに沿って存在する)。説明の目的で、MOSFET Q3の多結晶シリコンゲート166もまた図11A−1において見えるが、このゲートは図10−1中の線I−Iに沿って存在せず、むしろ線I――Iに沿った断面の「面の背後に」存在する。しかしながら、簡単のために、図10−1に示されたMOSFET Q2およびQ3の各ソース、ならびにQ2のゲートは図11A−1においては見えない。というのは、それらは共有されたドレインと同一の軸に沿って(すなわち、図面の面に垂直に)存在するからである。さらに、ISFETフローティングゲート電気的結合の理解を容易とするために、図11A−1の複合断面図は、図10−1の線II――IIの間の画素製造のさらなるエレメントを示す。

より具体的には、図11−Aの実施形態におけるように、最も頂部の金属層304は、その上方に、分析物−感受性不動態化層172が配置されたISFEF感受性エリア178に対応する。ISFET多結晶シリコンゲート164および介入導電体306、308、312、316、320、326および338と共に、最も頂部の金属層304は、ISFETフローティングゲート構造170を形成する。しかしながら、図11Aの実施形態とは異なり、ISFETドレインへの電気的結合は、金属3層よりはむしろ金属2層に形成されたライン1161にカップリングされた導電体340、328、および318によって供される。加えて、ライン1121および1141もまた、金属3層よりはむしろ金属2層に形成されたものとして図11A−1に示される。これらのライン、ならびにライン1181の構成は、図12−1A〜12−1Lの各像からさらに認識でき(ここに、各層の文字を付した頂面図、および図11A-1の断面図の間の対応は図12A−12Lとの関係で記載されたものと同一である);特に、金属導電体322と共にライン1181は金属1層において形成されるのは図12−1Fにおいて観察することができ、およびライン1121、1141および1161は金属2層に形成され、フローティングゲート構造170のジャンパー308のみを図12−1Jに示される金属3層に残すのが観察できる。

従って、シグナルライン1121、1141、1161および1181を金属1および金属2層に統合し、それにより、これらのシグナルライン、および金属4層におけるフローティングゲート構造170の最も頂部の層304の間の距離を増加させることによって、ISFETにおける寄生キャパシタンスを少なくとも部分的に緩和することができる。(例えば、シグナルラインおよびフローティングゲート構造の最も頂部の層の間の1以上の介入金属層を含めた)この一般的概念は、より大きな数の金属層を含む他の製造プロセスで実施することができるのは認められるべきである。例えば、画素シグナルラインおよび最も頂部の金属層の間の距離は、最も頂部の金属層に対するジャンパーのみがさらなる金属層において形成されたさらなる金属層(合計4を超える金属層)を加えることによって増加させることができる。特に、6―金属−層製造プロセスを使用することができ、そこでは、シグナルラインが金属1および金属2層を用いて製造され、フローティングゲート構造の最も頂部の金属層が金属6層で形成され、および最も頂部の金属層へのジャンパーが、(金属層の間の関連通路と共に)、各々、金属3、金属4および金属5層に形成される。6―金属―層製造プロセスに基づくもう1つの例示的な実施において、図10、11A、および12A〜12Lで示された一般的画素構成を使用することができ(金属2および金属3層上のシグナルライン)、そこでは、最も頂部の金属層は金属6層に形成され、およびジャンパーは、各々、金属4および金属5層に形成させる。

低下したキャパシタンスに関連するなおもう1つの態様において、最も頂部の金属層304(および、かくして、ISFET感受性エリア178)の寸法「f」を低下させて、隣接する画素の間の交差−キャパシタンスを低下させることができる。図11A-1で観察でき(および、ISFETアレイ上方でのウェル製造に向けられた他の実施形態に関連して以下でさらに議論されるように)、ウェル725は、ウェルの頂部における寸法「g」が画素ピッチ「e」よりも小さいが、ウェルの底部における寸法「f」よりはなお大きいように、テーパーが付された形状を有するように製造することができる。そのようなテーパリングに基づき、最も頂部の金属層304もまた、寸法「g」よりはむしろ寸法「f」にて設計して、隣接する画素の頂部金属層の間のさらなる空間を供することができる。いくつかの説明的非限定的実施において、9マイクロメートルのオーダーの寸法「e」を有する画素については、寸法「f」は(先に議論したように7マイクロメートルとは反対に)6マイクロメートルのオーダーとすることができる。5マイクロメートルのオーダーの寸法「e」を有する画素では、寸法「f」は3.5マイクロメートルのオーダーとすることができる。

かくして、各々、図10、11A、および12A〜12L、および図10−1、11A−1、および12−1A〜12−1Lで示された画素チップレイアウト設計は、種々の実施形態に従って、同一タイプのFETデバイスを画素の全ての構成要素のために使用でき、および全ての構成要素は単一のウェルにおいて実施できることを示す。これは、画素で必要な面積を劇的に低下させ、それにより、所与の面積における増大した画素密度を容易とする。

1つの例示的な実施において、ISFETのためのゲート酸化物165は、ほぼ75オングストロームのオーダーの厚みを有し、4.5fF/μm2の単位面積Cox当たりのゲート酸化物キャパシタンスを生起させるように製造することができる。加えて、多結晶シリコンゲート164は、1.2μmのチャネル幅Wおよび0.35〜0.6μmのチャネル長さL(すなわち、ほぼ2〜3.5の範囲のW/L)に対応する寸法にて製造でき、領域160のドーピングは、p−チャネルについてのキャリア移動度が190cm2/Vキs(すなわち1.9E10μm2/Vキs)となるように選択することができる。方程式(15)から、298ケルビン度の温度Tにおいては、59.2mV/pHの理論的最大pH感度はα=1で達成できるのは認識されるであろう。前記方程式(2)から、ほぼ170〜300μA/V2のオーダーのISFETトランスコンダクタンスパラメーターβがもたらされる。この例示的実施の他の態様において、アナログ供給電圧VDDAは3.3ボルトであって、VB1およびVB2は、5μAのオーダーの一定ISFETドレイン電流IDjを供るようにバイアスがかけられる(いくつかの実施において、VB1およびVB2はほぼ1μA〜20μAのドレイン電流を供するように調整することができる)。加えて、MOSFET Q6(図9中のバイアス/読出回路110j参照)は、Q6を横切った電圧が、5μAのIDjを仮定すると、800mVとなるような(すなわち、VDSj=800mV)、チャネルの長さに対する幅の比率を有するようなサイズとされる(例えば、ほぼ50のW/L)。方程式(15)から、298ケルビン度の温度Tにおいては、59.2mV/pHの理論的最大pH感度はα=1で達成できるのは認識されるであろう。前記方程式(3)から、これらの例示的パラメータに基づき、これは、ほぼ0〜2ボルトの範囲にわたってISFET閾値電圧変化についてほぼ0.5〜2.5ボルトの範囲にわたって画素出力電圧VSjを供する。

図11Aに示された分析物−感受性不動態化層172に関しては、例示的CMOS実施において、不動態化層は、水素を含めた種々のイオン種の濃度に対して有意に感受性とすることができ、窒化ケイ素(Si3N4)および/またはオキシ窒化ケイ素(Si2N2O)を含むことができる。慣用的なCMOSプロセスにおいて、不動態化層はこれらの材料の1以上の連続的動着によって形成することができ、これを使用して、一般的に、デバイスを処理し、またはコーティングして汚染に対して保護し、電気的安定性を増加させる。窒化ケイ素およびオキシ窒化ケイ素の材料の特性は、これらの材料を含む不動態化層がスクラッチ保護を供し、デバイス金属化を腐食させ、および/またはデバイス操作を不安定としかねない、水およびナトリウムの拡散に対する有利なバリアとして働くようなものである。窒化ケイ素および/またはオキシ窒化ケイ素を含めた不動態化層は、不動態化層がそれらが接触する分析物溶液からのプロトンを供与し、または受け取ることができる表面基を含有し、それにより、図1および2Aとの関係で先に議論したように、表面ポテンシャルおよびデバイス閾値電圧VTHを改変する点で、ISFETデバイスにおいてイオン−感受性も提供する。

(ほぼ650度摂氏の融点を有する)金属としてのアルミニウムを含むCMOSプロセスでは、窒化ケイ素および/またはオキシ窒化ケイ素不動態化層は、一般には、250〜350度摂氏のグロー放電が窒化ケイ素またはオキシ窒化ケイ素を形成する構成ガスをイオン化し、ウエハー表面で反応する活性種を作り出して、各材料の積層体を形成する、プラズマ−増強化学的気相蒸着法(PECVD)を介して形成される。1つの例示的プロセスにおいて、ほぼ1.0〜1.5μmのオーダーの厚みを有する不動態化層は、(0.2〜0.4μmのオーダーの)オキシ窒化ケイ素の薄層の初期蒸着、続いて、(0.5μmのオーダーの)オキシ窒化ケイ素のわずかにより厚い蒸着、および(0.5μmのオーダーの)窒化ケイ素の最終蒸着によって形成することができる。PECVDプロセスに関与する低い蒸着温度のため、アルミニウム金属化は有害に影響されない。

しかしながら、出願人らは、低温PECVDプロセスが慣用的CMOSデバイスに対して適切な不動態化を提供するが、低温プロセスの結果、一般には低密度かつ幾分多孔性の不動態化層をもたらし、これは、いくつかの場合において、ISFET閾値電圧安定性に悪影響しかねないことを認識し、認めてきた。特に、ISFETデバイス操作の間に、低密度多孔性不動態化層は、経時的に、溶液からのイオンを吸収でき、該イオンで飽和でき、これは、今度は、ISFET閾値電圧VTHにおいて望ましくない時間−変化ドリフトを引き起こしかねず、正確な測定を挑戦的なものとする。

これまでのことを考慮すると、1つの実施形態において、アルミニウムの代わりにタングステン金属を用いるCMOSプロセスを使用して、本発明の開示に従い、ISFETアレイを製造することができる。(3400度摂氏を超える)タングステンの高い融解温度は、窒化ケイ素またはオキシ窒化ケイ素不動態化層のための、より高い温度の低圧化学的気相蒸着(LPCVD)プロセス(例えば、ほぼ700〜800度摂氏)の使用を可能とする。LPCVDプロセスは、典型的には、不動態化層についての有意により密なかつ多孔性の低いフィルムをもたらし、それにより、ISFET閾値電圧のドリフトに導く、分析物溶液からのイオン吸収の潜在的な悪影響を緩和する。

アルミニウムベースのCMOSプロセスを使用して、本開示に従ってISFETアレイを製造するなおもう1つの実施形態において、図11Aに示された不動態化層172は、慣用的なCMOSプロセスで典型的に使用されたものを超えたさらなる蒸着および/または材料を含むことができる。例えば、不動態化層172は、先に議論した窒化ケイ素および/またはオキシ窒化ケイ素の初期低温プラズマ−援助蒸着(PECVD)を含むことができ;本議論の目的では、これらの慣用的蒸着は、不動態化層172の最初の部分172Aとして図11Aに示される。1つの実施形態において、最初の部分172Aに続いて、1以上のさらなる不動態化材料を配置して、少なくとも第2の部分172Bを形成して、密度を増大させ、総じての不動態化層172の多孔度(およびそれによる吸収)を低下させる。1つのさらなる部分172Bが、主として、図11Aでの説明の目的で、該開示はこの点において限定されない、というのは、総じての不動態化層172は2以上の構成部分を含むことができるからであり、そこでは、各部分は同一または異なる材料の1以上の層/蒸着を含むことができ、および各部分は同様にまたは異なって構成することができるのは認められるべきである。

不動態化層172の第2の部分172B(または他のさらなる部分)に適した材料の例は、限定されるものではないが、窒化ケイ素、オキシ窒化ケイ素、酸化アルミニウム(Al2O3)、酸化タンタル(Ta3O5)、酸化スズ(SnO2)および二酸化ケイ素(SiO2)を含む。1つの態様において、第2の部分172B(または他のさらなる部分)は、限定されるものではないが、RFスパッタリング、DCマグネトロンスパッタリング、熱または電子線蒸着、およびイオン−援助蒸着を含めた、種々の比較的低温のプロセスを介して蒸着することができる、もう1つの態様において、プレ−スパッタリングエッチングプロセスを、第2の部分172Bの蒸着に先立って使用し、第1の部分172Aに存在するいずれの天然酸化物も除去することができる(別法として、上昇した温度の水素雰囲気のような還元性雰囲気を使用して、第1の部分172Aに存在する天然酸化物を除去することができる)。なおもう1つの態様において、第2の部分172Bの厚みはほぼ0.04μm〜0.06μm(400〜600オングストローム)のオーダーとすることができ、第1の部分の厚みは、先に議論したように、1.0〜1.5μmのオーダーとすることができる。いくつかの例示的な実施において、第1の部分172Aは、1.0〜1.5μmの組合せ厚みを有するオキシ窒化ケイ素および窒化ケイ素の多数の層を含むことができ、第2の部分172Bは、ほぼ400〜600オングストロームの厚みを有する酸化アルミニウムまたは酸化タンタルいずれかの単一の層を含むことができる。再度、これまでの例示的厚みは、主として、説明目的で供されるものであり、開示はこれらの点において制限されないことが認められるべきである。

本発明に従い、水素イオン感受性不動態化層は、限定されるものではないが、PPiおよび取り込まれていないヌクレオチド三リン酸を含めた他の分析物に対しての感受性であることが判明した。例として、窒化ケイ素不動態化層は、PPiおよびヌクレオチド三リン酸の濃度の変化を検出することができる。同一のchemFETを用いてこれらの分析物の濃度変化を測定する能力は、単一アレイを用いて核酸を配列決定し、それにより、配列決定方法を単純化する能力を大いに促進する。

かくして、本明細書に記載されたchemFETアレイを用いて、種々の分析物を検出し、および/または測定することができ、そうすることによって、種々の反応および/または相互作用をモニターすることができるのは理解されるべきである。また、(pH変化の形態である)水素イオン検出に関するここでの議論は、便宜および簡潔性のためのものであり、および(他のイオンを含めた)他の分析物の静的または動的レベル/濃度を、これらの記載における水素に代えて置き換えることができるのも理解されるべきである。特に、分析物に存在する種々のイオン種のいずれか1以上の十分に速い濃度変化は、図2Aに関連して先に議論したように、chemFETの一過的または動的応答を介して検出することができる。また、分析物/不動態化層界面についての部位−解離(または部位−結合)モデルに関連して先に議論したように、分析物/不動態化層界面における平衡反応に関連する種々のパラメータ(例えば、順方向および逆方向平衡反応についての速度定数、不動態化層表面の単位面積当たりのプロトンドナー/アクセプター部位の合計数、固有の緩衝能力、ゼロ電荷の点におけるpH)は、材料依存性特性であって、かくして、不動態化層で使用される材料の選択によって影響されるのは認められるべきである。

本明細書中に記載されたISFETを含めたchemFETは、接触した場合に電場の変化をそれ自体が誘導することができるいずれの分析物も検出することができるか、あるいはそうでなければ、chemFET表面によって検知され、または検出される。分析物は、センサーによって検出されるためには荷電されている必要はない。例えば、実施形態に依存して、分析物は正に荷電され(すなわち、カチオン)、負に荷電され(すなわち、アニオン)、両性イオンであり、(すなわち、2つの等しいおよび反対の電荷を有することができるが、総じて中性である)、および極性であるが中性であってもよい。このリストは限定的な事を意図しない。というのは他の分析物クラスならびに各クラス内の種は、本明細書中に提供された開示に基づいて当業者によって容易に考えられるからである。

本発明の最も広い意味において、不動態化層はコーティングされていてもいなくてもよく、分析物は不動態化層と直接的に相互作用してもしなくてもよい。例として、不動態化層は窒化ケイ素を含むものでよく、分析物は水素イオン以外の何かであってもよい。具体的な例として、不動態化層は窒化ケイ素を含んでも良く、分析物はPPiであってよい。これらの例において、(すなわち、直接的にまたは間接的にのいずれかで不動態化層に付着されたPPi受容体の不存在下において)PPiは直接的に検出される。

もし検出されるべき分析物が水素(または別法として水酸化物)であれば、いずれかのイオン種の変化が不動態化層で検出できるように、弱い緩衝液を用いるのが好ましい。もし検出されるべき分析物が水素(または水酸化物)以外の何かであるが、反応または検出工程の間に溶液中のpH変化のいくらかの可能性があれば、pHの変化が分析物の検出に干渉しない場合、強い緩衝液を用いるのが好ましい。緩衝液は、pHの種々の程度の変化に対して抵抗するイオン性分子(またはイオン性分子を含む溶液)である。いくつかの緩衝液は、溶液中に加えられた、または溶液中で生じた酸または塩基を中和することができ、その結果、溶液中の有効なpH変化はない。いずれの緩衝液も適当であるが、それが所望の範囲においてpKaを有するこを条件とするのは理解されるべきである。いくつかの実施形態においては、適当な緩衝液は、6〜9、より好ましくは6.5〜8.5のpH範囲当たりで機能するものである。他の実施形態において、適当な緩衝液は、8.5〜9.5を含めた、7〜10のpH範囲当たりで機能するものである。

緩衝液の強度は相対的項である。というのは、それが注目する溶液に加えられた、または溶液中で生じた酸または塩基の性質、強度および濃度に依存するからである。弱い緩衝液は約少なくとも+/−0.005、約少なくとも+/−0.01、約少なくとも+/−0.015、約少なくとも+/−0.02、約少なくとも+/−0.03、約少なくとも+/−0.04、約少なくとも+/−0.05、約少なくとも+/−0.10、約少なくとも+/−0.15、約少なくとも+/−0.20、約少なくとも+/−0.25、約少なくとも+/−0.30、約少なくとも+/−0.35。約少なくとも+/−0.45、約少なくとも+/−0.50以上のpH変化の検出を可能とする緩衝液である(従って、そうでなければ制御することができない)。いくつかの実施形態において、pH変化は(例えば、ヌクレオチド取込み当たり)約0.005のオーダーであり、好ましくは、pHの増加である。強い緩衝液は、約少なくとも+/−0.005、約少なくとも+/-0.01、約少なくとも+/−0.015、約少なくとも+/−0.02、約少なくとも+/−0.03、約少なくとも+/−0.04、約少なくとも+/−0.05、約少なくとも+/−0.10、約少なくとも+/−0.15、約少なくとも+/−0.20、約少なくとも+/−0.25、約少なくとも+/−0.30、約少なくとも+/−0.35、約少なくとも+/−0.45、約少なくとも+/−0.50以上のpH変化を制御する緩衝液である。緩衝液の強度は、緩衝液種それ自体の濃度を変化させることによって変化させることができる。かくして、低濃度の緩衝液は低強度緩衝液であり得る。例は、1mM未満の(例えば、50〜100μM)緩衝液種を有するものを含む。pHの変化が読出である、本明細書中に記載された配列決定反応に適した弱い緩衝液の非限定的例は、0.1mM TrisまたはTricineである。適当な弱い緩衝液の例は実施例に供されており、また当該分野で公知でもある。より高い濃度の緩衝液はより強い緩衝液であり得る。その例は、1〜25mM緩衝液種を有するものを含む。PPiおよび/またはヌクレオチド三リン酸が直接的に読まれる、本明細書中に記載された配列決定反応に適した強い緩衝液の非限定的例は1、5または25mM(またはそれ以上の)TrisまたはTricineである。当業者であれば、本発明に含まれる反応および検出方法で用いられる最適な緩衝液を決定することができるであろう。

いくつかの実施形態において、不動態化層および/または複数層および/またはその上にコーティングされた分子は、アレイ読出の分析物特異性を指令する。

(pHの形態の)水素イオン、および本発明によって決定される他の分析物の検出は、窒化ケイ素(Si3N4)、オキシ窒化ケイ素(Si2N2O)、酸化ケイ素(SiO2)、酸化アルミニウム(Al2O3)、五酸化タンタル(Ta2O5)、酸化スズまたは酸化第二スズ(SnO2)等で作成された不動態化層を用いて行うことができる。

不動態化層は、限定されるものではないが、カルシウム、カリウム、ナトリウム、ヨウ素、マグネシウム、塩化物、リチウム、鉛、銀、カドミウム、ニトレート、フォスフェート、二水素フォスフェートなどを含めた他のイオン種を直接的に検出することもできる。

いくつかの実施形態において、不動態化層は注目する分析物に対する受容体でコーティングされる。好ましくは、受容体は注目する分析物、またはいくつかの例においては、分析物が属する剤のクラスに選択的に結合する。本明細書中で用いるように、分析物に選択的に結合する受容体は、その分析物に優先的に結合する分子である(すなわち、その分析物に対するその結合親和性は、いずれかの他の分析物に対するその結合親和性よりも大きい)。注目する分析物に対するその結合親和性は、いずれかの他の分析物に対するその結合親和性よりも2倍、3倍、4倍、5倍、6倍、7倍、8倍、9倍、10倍、15倍、20倍、25倍、30倍、40倍、50倍、100倍またはそれ以上であり得る。その相対的結合親和性に加えて、受容体は、注目する分析物に有効に結合するのに十分高い絶対結合親和性も有しなければならない(すなわち、それは十分な感度を有しなければならない)。ピコモル〜マイクロモル範囲に結合親和性を有する受容体も適当である。好ましくは、そのような相互作用は可逆的である。

受容体はいずれの性質のものであってもよい(例えば、化学物質、核酸、ペプチド、脂質、その組合せ等)。そのような実施形態において、分析物もまたいずれの性質のものであってもよいが、それに選択的に、いくつかの例においては、特異的に結合する受容体が存在するものとする。しかしながら、本発明はさらに、受容体の不存在下での分析物の検出が考えられるのは理解されるべきである。この例は、PPiまたはPi受容体の不存在下における不動態化層によるPPiおよびPiの検出である。

1つの態様において、本発明では、イオノフォアである受容体が考えられる。本明細書中で用いるように、イオノフォアは、アニオンまたはカチオンを問わず、イオン種に選択的に結合する分子である。本発明の関係では、イオノフォアは受容体であって、それが結合するイオンは分析物である。本発明のイオノフォアは微生物に由来する当該分野で認められたキャリアイオノフォア(すなわち、特定のイオンに結合する小さな脂質−可溶性分子)を含む。種々のイオノフォアがCalbiochemのような源から商業的に入手可能である。

いくつかのイオンの検出は、不動態化層それ自体の使用を通じて、または不動態化層上にコーティングされた受容体の使用を通じて達成することができる。例えば、カリウムは、ポリシロキサン、バリノマイシンまたはサリノマイシンを用いて選択的に検出することができ;ナトリウムはモネンシン、ナイスタチン、またはSQI-Prを用いて選択的に検出することができ;カルシウムはイオノマイシン、カルシマイシン(A23187)、またはCA1001(ETH 1001)を用いて選択的に検出することができる。

1を超えるイオンに結合することができる受容体もまたいくつかの例で用いることができる。例えば、ボベリシンを用いてカルシウムおよび/またはバリウムイオンを検出することができ、ニゲリシンを用いてカリウム、水素および/または鉛イオンを検出することができ、グラミシジンを用いて水素、ナトリウムおよび/またはカリウムイオンを検出することができる。当業者であれば、これらの化合物を、単一のイオン特異性が要求されない、あるいは化合物が結合する他のイオンが存在したり生じたりしないような(または不可能な)適用で用いることができる。同様に、特定の属の多数の種に結合する受容体もまた、該属内のただ1つの種が存在し、あるいは当該方法が種の間の区別を必要としないものを含めた、いくつかの実施形態でやはり有用であり得る。

もう1つの例として、ニューロトキシンに対する受容体は、Simonian Electroanalysis 2004, 16:1896−1906に記載されている。1896-1906.

限定されるものではないが、核酸配列決定適用を含めた他の実施形態において、PPiに選択的に結合する受容体を用いることができる。PPi受容体の例は図11B(1)〜(3)に示された化合物(化合物1〜10)を含む。化合物1はAngew,Chem Int(Ed 2004)43:4777−4780およびUS 2005/0119497 A1に記載されており、p−ナフチル−ビス[(ビス)2−ピリジルメチル]アミノ)メチル]フェノールという。化合物2はJ Am Chem Soc 2003 125:7752−7753およびUS 2005/0119497 A1に記載されており、p−(p−ニトロフェニルアゾ)−ビス[(ビス(2−ピリジルメチルー1)アミノ)メチル]フェノール(またはその二核Zn錯体)という。化合物1および2についての合成スキームはUS 2005/0119497 A1に供されている。化合物3はLee et al.Organic Letters 2007 9(2):243−246,およびSensors and Actuators B 1995 29:324−327に記載されている。化合物4は、Angew, Chem Int(Ed 2002)41(20):3811−3814に記載されている。化合物7、8および9についての例示的合成は図11C(1)〜(3)に示されている。化合物5はWO2007/002204に記載されており、ビス−Zn2+−ジピコリルアミン(Zn2+−DPA)とそこではいわれる。化合物6は、PPiに結合した11B(3)に示されている。(McDonough et al. Chem. Commun. 2006 2971−2973)化合物7の金属酸化物表面への結合は図11Eに示されている。

受容体は、共有結合により、または非-共有結合により、不動態化層に結合させることができる。受容体の不動態化層への共有結合は直接的または(例えば、リンカーを通じて)間接的であってよい。図11D(1)および(2)は、不動態化層へ受容体を共有結合により結合させるためのシラノール化学の使用を説明する。受容体は、例えば、脂肪族第一級アミン(底部左側パネル)またはアリールイソチオシアネート(底部右側パネル)を用いて不動態化層に固定化することができる。これらおよび他の実施形態において、それ自体が窒化ケイ素、酸化アルミニウム、酸化ケイ素、五酸化タンタルなどよりなることができる不動態化層を、その反応性表面基を介してシラネーション層に結合させる。FET表面への共有結合についてのシラノール化学に関するより詳細については、少なくとも以下の刊行物を参照することができる:窒化ケイ素については、Sensors and Actuators B 1995 29:324−327, Jpn J Appl Phys 1999 38:3912−3917およびLangmuir 2005 21:395−402参照;酸化ケイ素については、Protein Sci 1995 4:2532−2544およびAm Biotechnol Lab 2002 20(7):16−18参照;および酸化アルミニウムについては、Colloids and Surfaces 1992 63:1−9, Sensors and Actuators B 2003 89:40−47,およびBioconjugate Chem 1997 8:424−433参照。次いで、受容体をシラネーション層反応性基にコンジュゲートさせる。この後者の結合は、図11D(1)および(2)に説明されるように、二官能性リンカーの使用を通じて直接的にまたは間接的に起こり得る。

二官能性リンカーは、それに2つの物質が結合し得る少なくとも2つの反応性基を有する化合物である。いくつかの例において、反応性基はリンカーの反対末端に位置させる。いくつかの実施形態において、二官能性リンカーは、図11D(1)および(2)に示されたもののような普遍的二官能性リンカーである。普遍的リンカーは、種々の物質に連結させるのに用いることができるリンカーである。図11D(1)および(2)に示された化学は説明的であって限定的ではないことが理解されるべきである。

二官能性リンカーは、コンジュゲートさせるべき分子の性質に依存して、ホモ−二官能性リンカーまたはヘテロ−二官能性リンカーであってよい。ホモ−二官能性リンカーは2つの同一性反応基を有する。ヘテロ−二官能性リンカーは2つの異なる反応性基を有する。商業的に入手可能なリンカーの種々のタイプは以下の基の1以上と反応性である:第一級アミン、第二級アミン、スルフヒドリル、カルボキシル、カルボニルおよび炭水化物。アミン−特異的リンカーの例はビス(スルフォスクシンイミジル)スベレート、ビス[2−(スクシンイミドオキシカルボニルオキシ)エチル]スルホン、ジスクシンイミジルスベレート、ジスクシンイミジルタルタレート、ジメチルアジピメートキ2HCl、ジメチルピメリミデートキ2HCl、ジメチルスベリミデートキ2HCl、およびエチレングリコビス-[スクシンイミジル-[スクシネート]]である。スルフヒドリル基と反応性であるリンカーはビスマレイミドヘキサン、1,4-ジ−[3’-(2’−ピリジルジチオ)−プロピオンアミド]ブタン、1−[p−アジドサリチルアミド]−4−[ヨードアセタミド]ブタン、およびN−[4−(p−アジドサリチルアミド)ブチル]−3’−[2’−ピリジルジチオ]プロピオンアミドを含む。炭水化物と優先的に反応性のリンカーはアジドベンゾイルヒドラジンを含む。カルボキシル基と優先的に反応性のリンカーは4−[p−アジドサリチルアミド]ブチルアミンを含む。

アミンおよびスルフヒドリルと反応するヘテロ二感応性リンカーはN−スクシンイミジル−3−[2−ピリジルジチオ]プロピオネート、スクシンイミジル[4−ヨードアセチル]アミノベンゾエート、スクシンイミジル4−[N−マレイミドメチル]シクロヘキサン−1−カルボキシレート、m−マレイミドベンゾイル−N−ヒドロキシスクシンアミドエステル、スルホスクシンイミジル6−[3−[2−ピリジルジチオ]プロピオンアミド]ヘキサノエート、およびスルホスクシンイミジル4−[N−マレイミドメチル]シクロヘキサン−1−カルボキシレートを含む。カルボキシルおよびアミン基と反応するヘテロ二感応性リンカーは1−エチル−3−[3−ジメチルアミノプロピル]−カルボジイミド塩酸塩を含む。炭水化物およびスルフヒドリルと反応するヘテロ二感応性リンカーは、4−[N−マレイミドメチル]−シクロヘキサン−1−カルボキシルヒドラジド・2HCl、4−(4−N−マレイミドフェニル)−酪酸ヒドラジド・2HCl、および3−[2−ピリジルジチオ]プロイオニルヒドラジドを含む。

別法として受容体は不動態化層上に非共有結合的にコーティングすることができる。不動態化層上への受容体の非−共有結合蒸着はポリマーマトリックスの使用を含むことができる。ポリマーは天然に生じるものであっても、または天然に生じないものであってもよく、限定されるものでないが、核酸(例えば、DNA、RNA、PNA、LNA等、あるいはそのミミック、誘導体、または組合せ)、アミノ酸(例えば、ペプチド、蛋白質(天然または非天然)等、またはそのミミック、誘導体、または組合せ)、脂質、多糖、および感応性化ブロックコポリマーを含めたいずれのタイプのものであってもよい。受容体はポリマーマトリックス上に吸着されおよび/またはポリマーマトリックス内に捕獲されていてもよい。ポリマーの性質は、用いられるべき受容体、および/または検出されるべき分析物の性質に依存するであろう。

別法として、受容体はポリマーに共有結合によりコンジュゲートされ、または架橋されていてもよい(例えば、それは感応性化ポリマー上に「グラフト化」されていてもよい)。

適当なペプチドポリマーの例はポリ−リシン(例えば、ポリ−L−リシン)である。他のポリマーの例は、ポリエチレングリコール(PEG)、ポリアミド、ポリカーボネート、ポリアルキレン、ポリアルキレングリコール、ポリアルキレンオキサイド、ポリアルキレンテレフタレート、ポリビニルアルコール、ポリビニルエーテル、ポリビニルエステル、ポリビニルハライド、ポリビニルピロリドン、ポリグリコリド、ポリシロキサン、ポリウレタン、アルキルセルロース、ヒドロキシアルキルセルロース、セルロースエーテル、セルロースエステル、ニトロセルロースを含むブロックコポリマー、アクリル酸およびメタクリル酸エステルのポリマー、メチルセルロース、エチルセルロース、ヒドロキシプロピルセルロース、ヒドロキシプロピルメチルセルロース、ヒドロキシブチルメチルセルロース、酢酸セルロース、プロピオン酸セルロース、酢酸酪酸セルロース、酢酸フタル酸セルロース、カルボキシルエチルセルロース、三酢酸セルロース、硫酸セルロースナトリウム塩ポリ(メチルメタクリレート)、ポリ(エチルメタクリレート)、ポリ(ブチルメタクリレート)、ポリ(イソブチルメタクリレート)、ポリ(ヘキシルメタクリレート)、ポリ(イソデシルメタクリレート)、ポリ(ラウリルメタクリレート)、ポリ(フェニルメタクリレート)、ポリ(メチルアクリレート)、ポリ(イソプロピルアクリレート)、ポリ(イソブチルアクリレート)、ポリ(オクタデシルアクリレート)、ポリエチレン、ポリプロピレン、ポリ(エチレングリコール)、ポリ(エチレンオキサイド)、ポリ(エチレンテレフタレート)、ポリ(ビニルアルコール)、ポリ酢酸ビニル、ポリ塩化ビニル、ポリスチレン、ポリヒアルロン酸、カゼイン、ゼラチン、グルチン、ポリアンヒドリド、ポリアクリル酸、アルジネート、キトサン、ポリ(メチルメタクリレート)、ポリ(エチルメタクリレート)、ポリ(ブチルメタクリレート)、ポリ(イソブチルメタクリレート)、ポリ(ヘキシルメタクリレート)、ポリ(イソデシルメタクリレート)、ポリ(ラウリルメタクリレート)、ポリ(フェニルメタクリレート)、ポリ(メチルアクリレート)、ポリ(イソプロピルアクリレート)、ポリ(イソブチルアクリレート)、およびポリ(オクタデシルアクリレート)、ポリ(ラクチド−グリコリド)、コポリオキサレート、ポリカプロラクトン、ポリエステルアミド、ポリオルトエステル、ポリヒドロキシ酪酸、ポリアンヒドリド、ポリ(スチレン−b−イソブチレン−b−スチレン)(SIBS)ブロックコポリマー、エチレンビニルアセテート、ポリ(メタアクリル酸)、乳酸およびグリコール酸のポリマー、ポリアンヒドリド、ポリ(オルト)エステル、ポリウレタン、ポリ(酪酸)、ポリ(吉草酸)、およびポリ(ラクチド−コカプロラクトン)、アルジネート、およびデキストランおよびセルロースを含めた他の多糖コラーゲン、アルブミン、および他の親水性蛋白質ゼインおよび他のプロルアミンおよび疎水性蛋白質のような天然ポリマー、そのコポリマーおよび混合物、ならびに化学基、例えば、アルキル、アルキレンの置換および/または付加、ヒドロキシル化、酸化、および当業者によってルーチン的に成される他の修飾を含めたその化学的誘導体を含む。

ISFET閾値電圧の安定性および/または予測性に関するもう1つの論点は、アレイ製造の間における、またはアレイ製造に続いての種々の加工活動(例えば、プラズマ金属エッチング、ウエハー洗浄、ダイシング、パッケージング、取扱等のようなラインのバックエンド処理)の結果としての、CMOS−製造デバイスの金属層に(特に)蓄積しかねないトラップされた電荷を含む。特に図11Aを参照し、トラップされた電荷はいくつかの例においては、ISFETフローティングゲート構造170を構成する種々の導電体304、306、308、312,316、320、326、338、および164の1以上に蓄積しかねない。この現象は、関連文献においては、「アンテナ効果」とも言われる。