JP4968681B2 - 半導体回路とそれを用いた表示装置並びにその駆動方法 - Google Patents

半導体回路とそれを用いた表示装置並びにその駆動方法 Download PDFInfo

- Publication number

- JP4968681B2 JP4968681B2 JP2007185974A JP2007185974A JP4968681B2 JP 4968681 B2 JP4968681 B2 JP 4968681B2 JP 2007185974 A JP2007185974 A JP 2007185974A JP 2007185974 A JP2007185974 A JP 2007185974A JP 4968681 B2 JP4968681 B2 JP 4968681B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- circuit

- signal

- output

- scanning

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0283—Arrangement of drivers for different directions of scanning

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0492—Change of orientation of the displayed image, e.g. upside-down, mirrored

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Shift Register Type Memory (AREA)

- Liquid Crystal (AREA)

Description

Crystal Display)が開発されている。

前記画素は、前記第1の走査回路、又は前記第2の走査回路を構成する単位レジスタから出力された出力信号によって制御される。

複数の画素が配列された画素アレイと、前記画素アレイを間に相対して配置され、前記複数の画素に走査信号をラインごとに供給する第1、第2の走査回路を備えた表示装置の駆動方法であって、

前記第1の走査回路が出力信号を出力している期間、前記第2の走査回路は出力信号を出力しない状態とされ、

前記第2の走査回路が出力信号を出力している期間、前記第1の走査回路は出力信号を出力しない状態とされ、

前記第1の走査回路の走査方向と、前記第2の走査回路の走査方向とが相反していることを特徴とする。

前記出力信号を発生する第1の出力用トランジスタ(図14のTr6)、及び第2の出力用トランジスタ(Tr5)と、

前記第1の出力用トランジスタ(Tr6)、及び第2の出力用トランジスタ(Tr5)をオフ状態とする第1の制御信号線(VSS)と、前記第1の制御信号線とは異なる電位の第2の制御信号線(CLK(n))と、

前記単位レジスタの出力信号を転送する出力信号線(OUT)と、

を備えている。

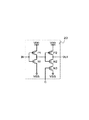

NMOSトランジスタ(N1)とPMOSトランジスタ(P1)から構成されたインバータ回路と、

高電位電源線、及び低電位電源線と、前記単位レジスタの出力信号を転送する出力信号線から構成されており、

前記スイッチ回路(N3)が、低電位電源線(VSS)と、出力信号線(OUT)との間、又は高電位電源線(VDD)と出力信号線(OUT)との間に配置されている。このため、スイッチ回路をオン状態、又はオフ状態とすることにより、走査回路の出力信号を出力する状態、又は出力しない状態に制御することが可能となる。

NMOSトランジスタ(N1)とPMOSトランジスタ(P1)とから構成されたインバータ回路と、

高電位電源線、及び低電位電源と、前記単位レジスタの出力信号を転送する出力信号線から構成されており、

前記第1のスイッチ回路(N3)が、低電位電源線(VSS)と、出力信号線(OUT)との間に設置され、

前記第2のスイッチ回路(P3)が、高電位電源線(VDD)と、出力信号線(OUT)との間に設置されている。

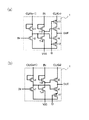

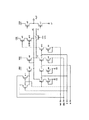

本発明の第1の実施例について説明する。図1は、本実施例の表示装置を示す構成を示す図である。図2は、図1のA−A’線の断面を模式的に示す図である。図3(a)、(b)は、本実施例の走査回路の構成を示すブロック図である。図4は、本実施例のシフトレジスタ(単位レジスタ)の構成を示す図である。図5は、本実施例の表示装置の画素部分の回路構成を示す図である。

第2の走査回路6のD2端子、D1端子は、FW信号、RV信号が接続される。

次に本発明の第2の実施例について説明する。本発明の第2の実施例の表示装置の構成は、第1の実施例と同様、図1、及び図2に示した構成とされる。ただし、表示部4を構成する画素は、図7に示したPMOSトランジスタの構成である。ゲートとドレインが端子CLK(n+1)端子に接続されたPMOSトランジスタTr1と、PMOSトランジスタTr1のソースにドレインが接続されゲートがINに接続されソースがVDDに接続されたPMOSトランジスタTr2と、ゲートとドレインが端子INに接続されたPMOSトランジスタTr3と、PMOSトランジスタTr3のソース(ノードA)にドレインが接続され、PMOSトランジスタTr2のドレイン(ノードB)にゲート接続されソースがVDDに接続されたPMOSトランジスタTr4と、ドレインがCLK(n)端子に接続され、PMOSトランジスタTr3のソース(ノードA)にゲートが接続され、ドレインが端子OUTに接続されたPMOSトランジスタTr5と、ドレインが端子OUTに接続され、ソースがVDDに接続されたPMOSトランジスタTr6と、PMOSトランジスタTr2のドレインとPMOSトランジスタTr6のゲート間に接続され、ゲートが端子D1に接続されたPMOSトランジスタTr7と、PMOSトランジスタTr6のゲートにドレインが接続され、ゲートが端子D2に接続され、ソースがVSSに接続されたPMOSトランジスタTr8を備えている。

次に、本発明の第3の実施例を説明する。本実施例の表示装置の構成は、前記第1の実施例と同様、図1及び図2に示した構成とされるが、表示部4を構成する画素は、図5に示した構成である。また、走査回路の構成についても、第1の実施例と同様、図3(a)、図3(b)に示した構成とされる。

次に、本発明の第4の実施例を説明する。本発明の第4の実施例の表示装置の構成は、前記第1の実施例と同様、図1、及び図2に示した構成と同一とされる。

次に本発明の第5実施例を説明する。本発明の第5の実施例の表示装置の構成は、前記第1の実施例と同様、図1、及び図2に示した構成と同一とされる。また、走査回路は第4の実施例と同様、図15(a)、(b)に示した構成と同一であるが、本実施例において、スタート信号(ST1、ST2)は、好ましくは信号STが用いられる。

次に、本発明の第6の実施例を説明する。本発明の第6の実施例の表示装置の構成は、図1に示した構成と同一である。本実施例においても、表示部4の両側に、第1の走査回路5、及び第2の走査回路6が配置されており、各々の走査回路の出力は、共通のゲートバスライン7で接続されている。また、図1の表示部4を構成する画素については、図5の構成が望ましい。

次に、本発明の第7の実施例を説明する。本発明の第7の実施例の表示装置の構成は、第6実施例と同様、図1に示す構成と同一である。本実施例においても、表示部4の両側に、第1の走査回路5、及び第2の走査回路6が配置されており、各々の走査回路の出力は、共通のゲートバスライン7で接続されている。また、図1の表示部4を構成する画素については、図5、又は図7のいずれの構成でも構わない。

次に、本発明の第8の実施例を説明する。本実施例の表示装置の構成は、前記第6実施例と同様、図1に示した構成と同一とされる。本実施例においても、表示部4の両側に、第1の走査回路5、及び第2の走査回路6が配置されており、各々の走査回路の出力は、共通のゲートバスライン7で接続されている。また、図1の表示部4を構成する画素については、図5、又は図7のいずれの構成でも構わない。また、走査回路の構成は、第7実施例に示した図24の構成と同一である。本実施例では、出力回路20の構成が、第7実施例と相違している。図26に、本実施例の出力回路20の回路構成を示す。

2 走査回路

3 回路基板

4 表示部

5 第1の走査回路

6 第2の走査回路

7 ゲートバスライン

8 ソースIC

9 端子列

10 データバスライン

11 液晶部

12 保持容量

13 スイッチトランジスタ

14 対向基板

16 共通配線

20 出力回路

21 画素

101 アレイ基板

102 走査線駆動回路

103 信号線駆動回路

104 垂直シフトレジスタ

105 レベルシフタ

106 水平シフトレジスタ

110 画素スイッチ(スイッチング素子、薄膜トランジスタ:TFT)

111 液晶

120 データ線

Claims (23)

- それぞれが単位レジスタを複数有する第1の走査回路と第2の走査回路を備え、

前記第1の走査回路と前記第2の走査回路の対応する単位レジスタの出力同士が互いに接続され、

前記第1の走査回路と前記第2の走査回路の前記単位レジスタは、

制御信号に基づき、出力信号を出力する状態又は出力しない状態に、出力の状態を切り替える回路要素を備えている、ことを特徴とする半導体回路。 - 前記第1及び第2の走査回路の一方が出力信号を出力している期間、他方は出力信号を出力しない状態とされる、ことを特徴とする請求項1記載の半導体回路。

- 前記第1の走査回路の走査方向と、前記第2の走査回路の走査方向とが相反していることを特徴とする請求項1記載の半導体回路。

- 前記回路要素が、走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号を、前記制御信号として入力し、オン・オフ制御される第1のスイッチ回路と第2のスイッチ回路を備え、

前記第1のスイッチ回路は、前記単位レジスタ内において、前記出力信号を発生する出力用トランジスタのゲート電極と、前記ゲート電極を制御する配線との間に配置され、

前記第2のスイッチ回路は、前記第1のスイッチ回路と、前記出力用トランジスタとの間のノードと、前記出力用トランジスタをオフ状態とし得る信号線との間に配置されていることを特徴とする請求項1記載の半導体回路。 - 前記回路要素が、走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号によって、オン・オフ制御される第1乃至第4のスイッチ回路を備え、

前記第1のスイッチ回路は、前記単位レジスタ内において、

前記出力信号を発生する第1の出力用トランジスタのゲート電極と、前記ゲート電極を制御する配線との間に配置され、

前記第2のスイッチ回路は、前記第1のスイッチ回路と、前記第1の出力用トランジスタとの間のノードと、前記第1の出力用トランジスタをオフ状態とし得る信号線との間に配置され、

前記第3のスイッチ回路が、前記単位レジスタ内の、前記第1の出力用トランジスタとは異なる電位の制御信号を発生する第2の出力用トランジスタのゲート電極と、前記ゲート電極を制御する配線との間に配置され、

前記第4のスイッチ回路が、前記第3のスイッチ回路と、前記第2の出力用トランジスタとの間のノードと、前記第2の出力用トランジスタをオフ状態とし得る信号線との間に配置されている、ことを特徴とする請求項1記載の半導体回路。 - 前記回路要素が、

走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号によってゲート制御される第1のスイッチ回路、及び第2のスイッチ回路と、

前記出力信号を発生する第1の出力用トランジスタ、及び第2の出力用トランジスタと、

前記第1の出力用トランジスタをオフ状態とする第1の信号線と、

前記第2の出力用トランジスタをオフ状態とする第2の信号線と、

前記単位レジスタの出力信号を転送する出力信号線とを備え、

前記第1のスイッチ回路は、前記出力信号線と、前記第1の制御信号線との間に設置され、

前記第2のスイッチ回路が、前記出力信号線と、前記第2の制御信号線との間に設置されていることを特徴とする請求項1記載の半導体回路。 - 前記回路要素が、走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号によってオン・オフ制御されるスイッチ回路と、

逆導電型の2つのトランジスタを含むインバータ回路と、

高電位電源線、及び低電位電源線と、

前記単位レジスタの出力信号を転送する出力信号線と、

を備え、

前記スイッチ回路が、前記低電位電源線と前記出力信号線との間、又は、前記高電位電源線と前記出力信号線との間に、配置されている、

ことを特徴とする請求項1記載の半導体回路。 - 前記回路要素が、走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号によってゲート制御される第1のスイッチ回路、および第2のスイッチ回路と、

逆導電型の2つのトランジスタを含むインバータ回路と、

高電位電源線、及び低電位電源と、

前記単位レジスタの出力信号を転送する出力信号線とを備え、

前記第1のスイッチ回路が、前記低電位電源線と前記出力信号線との間に設置され、

前記第2のスイッチ回路が、前記高電位電源線と前記出力信号線との間に設置されていることを特徴とする請求項1記載の半導体回路。 - 前記回路要素が、走査方向を指定する信号、又は前記走査方向を指定する信号から生成された信号によってオン・オフ制御されるスイッチ回路を備え、

前記出力信号を発生する回路が、

逆導電型の2つのトランジスタを含むインバータ回路を備え、

前記スイッチ回路が、前記出力信号配線と前記インバータ回路の出力ノードとの間に配置されていることを特徴とする請求項1記載の半導体回路。 - 前記第1の走査回路を構成する前記単位レジスタと、前記第2の走査回路を構成する前記単位レジスタの回路構成及び回路配置が、回路動作に影響する範囲において等しいことを特徴とする請求項1記載の半導体回路。

- 前記第1の走査回路及び前記第2の走査回路が、それぞれ、NMOSトランジスタで形成されていることを特徴とする請求項1記載の半導体回路。

- 前記第1の走査回路及び前記第2の走査回路が、それぞれ、PMOSトランジスタで形成されていることを特徴とする請求項1記載の半導体回路。

- 前記第1の走査回路及び前記第2の走査回路が、それぞれ、CMOSで形成されていることを特徴とする請求項1記載の半導体回路。

- 前記単位レジスタが、

ゲートとドレインが第2のクロック端子に接続された第1のトランジスタと、

ドレインが前記第1のトランジスタのソースに接続され、ゲートが入力端子に接続されソースが第1の電源に接続された第2のトランジスタと、

ゲートとドレインが前記入力端子に接続された第3のトランジスタと、

ドレインが前記第3のトランジスタのソースに接続され、ゲートが前記第2のトランジスタのドレインに接続され、ソースが第1の電源に接続された第4のトランジスタと、

ドレインが第1のクロック端子に接続され、ゲートが前記第3のトランジスタのソースに接続され、ドレインが出力端子に接続された第5のトランジスタと、

ドレインが前記出力端子に接続され、ソースが前記第1の電源に接続された第6のトランジスタと、

前記第1のトランジスタのソースと前記第2のトランジスタのドレインの接続点と、前記第6のトランジスタのゲート間に接続され、ゲートが第1の制御端子に接続された第7のトランジスタと、

ドレインが前記第6のトランジスタのゲートに接続されゲートが第2の制御端子に接続されソースが第1の電源に接続された第8のトランジスタと、

を備えている、ことを特徴とする請求項1記載の半導体回路。 - 前記単位レジスタは、3相クロックで駆動され、

前記各走査回路を構成する複数の前記単位レジスタは縦列に接続され、初段の単位レジスタに入力されたパルスの位相を単位レジスタでシフトさせながら後段の単位レジスタに伝達する構成とされ、

前記第1、第2のクロック端子には、3相クロックのうち、相隣る位相のクロックが入力され、

初段の単位レジスタの入力信号端子には、パルスが入力され、

単位レジスタの出力端子は対応するゲートラインに接続されるとともに、後段の単位レジスタの入力端子に接続され、

前記第1の走査回路の単位レジスタにおいて、前記第1、第2の制御端子には、順方向シフト、逆方向シフトのときに活性化する信号がそれぞれ入力され、

前記第2の走査回路の単位レジスタにおいて、前記第1、第2の制御端子には、逆方向シフト、順方向シフトのときに活性化する信号がそれぞれ入力される、ことを特徴とする、請求項14記載の半導体回路。 - 前記単位レジスタが、

ドレインとゲートが第2のクロック端子に接続された第1のトランジスタと、

ドレインが前記第1のトランジスタのソースに接続され、ゲートが入力端子に接続され、ソースが第1電源に接続された第2のトランジスタと、

ドレインとゲートが前記入力端子に接続された第3のトランジスタと、

ドレインが前記第3のトランジスタのソースに接続され、ゲートが前記第1のトランジスタのソースと前記第2のトランジスタのドレインの接続点に接続され、ソースが第1電源に接続された第4のトランジスタと、

ドレインが第1のクロック端子に接続されソースが出力端子に接続された第5のトランジスタと、

ドレインが前記出力端子にドレインが接続されソースが第1電源に接続された第6のトランジスタと、

前記第1のトランジスタのソースと前記第2のトランジスタのドレインの接続点と、前記第6のトランジスタのゲート間に接続され、ゲートが前記第1の制御端子に接続された第7のトランジスタと、

前記第6のトランジスタのゲートと第1の電源間に接続され、ゲートが第2の制御端子に接続された第8のトランジスタと、

前記第3のトランジスタのソースと前記第4のトランジスタのドレインの接続点と、前記第5のトランジスタのゲート間に接続され、ゲートが第1の制御端子に接続された第9のトランジスタと、

前記第5のトランジスタのゲートにドレインが接続され、ソースが第1電源に接続され、ゲートが前記第2の制御端子に接続された第10のトランジスタと、

を備えている、ことを特徴とする、請求項1記載の半導体回路。 - 前記単位レジスタは、3相クロックで駆動され、

前記各走査回路を構成する複数の前記単位レジスタは縦列に接続され、初段の単位レジスタに入力されたパルスの位相を単位レジスタでシフトさせながら後段の単位レジスタに伝達する構成とされ、

前記第1、第2のクロック端子には、3相クロックの相隣る位相のクロックが入力され、

初段の単位レジスタの入力信号端子には、パルスが入力され、前記単位レジスタの出力端子は対応するゲートラインに接続されるとともに、後段の単位レジスタの入力端子に接続され、

前記第1の走査回路の単位レジスタにおいて、前記第1、第2の制御端子には、順方向シフト、逆方向シフトのときに活性化する信号がそれぞれ入力され、

前記第2の走査回路の単位レジスタにおいて、前記第1、第2の制御端子には、逆方向シフト、順方向シフトのときに活性化する信号がそれぞれ入力される、ことを特徴とする、請求項16記載の半導体回路。 - 前記単位レジスタが、

ドレインとゲートが第2のクロック端子に接続された第1のトランジスタと、

ドレインが前記第1のトランジスタのソースに接続され、ゲートが入力端子に接続され、ソースが第1電源に接続された第2のトランジスタと、

ドレインとゲートが前記入力端子に接続された第3のトランジスタと、

ドレインが前記第3のトランジスタのソースに接続され、ゲートが前記第1のトランジスタのソースと前記第2のトランジスタのドレインの接続点に接続され、ソースが第1電源に接続された第4のトランジスタと、

ドレインが第1のクロック端子に接続され、ソースが出力端子に接続された第5のトランジスタと、

ドレインが前記出力端子にドレインが接続され、ゲートが前記第1のトランジスタのソースと前記第2のトランジスタのドレインの接続点と前記第4のトランジスタのゲートに接続された第6のトランジスタと、

ドレインが前記第6のトランジスタのソースに接続され、ゲートが第1の制御端子に接続され、ソースが前記第1電源に接続された第7のトランジスタと、

を備えている、ことを特徴とする、請求項1記載の半導体回路。 - 前記単位レジスタは、3相クロックで駆動され、

前記各走査回路を構成する複数の前記単位レジスタは縦列に接続され、初段の単位レジスタに入力されたパルスの位相を単位レジスタでシフトさせながら後段の単位レジスタに伝達する構成とされ、

前記第1、第2のクロック端子には、3相クロックの相隣る位相のクロックが入力され、

初段の単位レジスタの入力信号端子には、パルスが入力され、前記単位レジスタの出力端子は対応するゲートラインに接続されるとともに、後段の単位レジスタの入力端子に接続され、

前記第1の走査回路の単位レジスタにおいて、前記第1の制御端子には、順方向シフトのときに活性化する信号が入力され、

前記第2の走査回路の単位レジスタにおいて、前記第1の制御端子には、逆方向シフトのときに活性化する信号が入力される、ことを特徴とする、請求項18記載の半導体回路。 - 前記単位レジスタが、前記第1のクロック端子と前記第5のトランジスタのドレインの間に、ゲートが前記第1の制御端子に接続された第8のトランジスタをさらに備えている、ことを特徴とする請求項18記載の半導体回路。

- 前記単位レジスタが、入力信号をクロック信号に応答してラッチするラッチ回路と、

前記ラッチ回路の出力を受け、第1の制御信号に基づき、出力がオン・オフ制御される出力回路を備えていることを特徴とする請求項1記載の半導体回路。 - 複数の画素が配列された画素アレイと、前記画素を活性化する半導体回路とを具備した表示装置において、

前記半導体回路は、請求項1乃至21のいずれか一項に記載の半導体回路よりなり、

前記画素は、前記第1の走査回路、又は前記第2の走査回路を構成する単位レジスタから出力された出力信号によって制御されることを特徴とする表示装置。 - 複数の画素が配列された表示部を間に対向配置され、走査信号をラインごとに供給する第1、第2の走査回路を備えた表示装置の駆動方法であって、

前記第1の走査回路が出力信号を出力している期間、前記第2の走査回路は出力信号を出力しない状態とされ、

前記第2の走査回路が出力信号を出力している期間、前記第1の走査回路は出力信号を出力しない状態とされ、

前記第2の走査回路の走査方向は前記第1の走査回路の走査方向と逆方向であり、双方向走査を行う、ことを特徴とする表示装置の駆動方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007185974A JP4968681B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体回路とそれを用いた表示装置並びにその駆動方法 |

| US12/174,808 US20090021466A1 (en) | 2007-07-17 | 2008-07-17 | Semiconductor circuit, display apparatus employing the same, and driving method therefor |

| CN200810133833.XA CN101350179B (zh) | 2007-07-17 | 2008-07-17 | 半导体电路和使用该半导体电路的显示装置以及其驱动方法 |

| US13/339,804 US8654056B2 (en) | 2007-07-17 | 2011-12-29 | Semiconductor circuit and display apparatus employing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007185974A JP4968681B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体回路とそれを用いた表示装置並びにその駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009027265A JP2009027265A (ja) | 2009-02-05 |

| JP4968681B2 true JP4968681B2 (ja) | 2012-07-04 |

Family

ID=40264440

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007185974A Active JP4968681B2 (ja) | 2007-07-17 | 2007-07-17 | 半導体回路とそれを用いた表示装置並びにその駆動方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US20090021466A1 (ja) |

| JP (1) | JP4968681B2 (ja) |

| CN (1) | CN101350179B (ja) |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3183390B2 (ja) * | 1995-09-05 | 2001-07-09 | キヤノン株式会社 | 光電変換装置及びそれを用いた撮像装置 |

| JP4439761B2 (ja) * | 2001-05-11 | 2010-03-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置、電子機器 |

| US8330492B2 (en) | 2006-06-02 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device |

| JP5540430B2 (ja) * | 2009-04-14 | 2014-07-02 | Nltテクノロジー株式会社 | 走査線駆動回路、表示装置及び走査線駆動方法 |

| WO2010150607A1 (en) | 2009-06-25 | 2010-12-29 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| KR101653246B1 (ko) * | 2010-02-03 | 2016-09-12 | 삼성디스플레이 주식회사 | 표시 패널의 구동 방법 및 이를 수행하기 위한 표시 장치 |

| JP2011164534A (ja) * | 2010-02-15 | 2011-08-25 | Hitachi Displays Ltd | 表示装置 |

| KR101798260B1 (ko) * | 2010-03-12 | 2017-11-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| KR101840181B1 (ko) * | 2010-05-21 | 2018-03-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 펄스 출력 회로, 시프트 레지스터, 및 표시 장치 |

| CN101846835B (zh) * | 2010-06-11 | 2012-11-07 | 华映光电股份有限公司 | 对向扫描讯号发送系统及其方法 |

| JP5839896B2 (ja) | 2010-09-09 | 2016-01-06 | 株式会社半導体エネルギー研究所 | 表示装置 |

| CN102411891B (zh) * | 2010-09-21 | 2014-10-08 | 群康科技(深圳)有限公司 | 显示装置及其驱动方法 |

| KR101696480B1 (ko) * | 2010-10-12 | 2017-01-13 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| JP5679172B2 (ja) | 2010-10-29 | 2015-03-04 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| KR101778650B1 (ko) * | 2011-02-23 | 2017-09-15 | 삼성디스플레이 주식회사 | 표시 패널 및 이를 포함하는 표시 장치 |

| CN102646387B (zh) * | 2011-05-19 | 2014-09-17 | 京东方科技集团股份有限公司 | 移位寄存器及行扫描驱动电路 |

| JP5774911B2 (ja) * | 2011-06-01 | 2015-09-09 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN102222488B (zh) * | 2011-06-27 | 2013-07-03 | 福建华映显示科技有限公司 | 非晶硅显示装置 |

| KR101473843B1 (ko) | 2012-04-25 | 2014-12-17 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR20140020484A (ko) * | 2012-08-08 | 2014-02-19 | 삼성디스플레이 주식회사 | 주사 구동 장치 및 그 구동 방법 |

| CN204577057U (zh) * | 2012-10-05 | 2015-08-19 | 夏普株式会社 | 显示装置 |

| CN103268032B (zh) * | 2012-12-28 | 2016-07-06 | 上海中航光电子有限公司 | 一种阵列基板、显示面板和显示装置 |

| CN104008779B (zh) * | 2014-05-27 | 2017-03-15 | 上海天马有机发光显示技术有限公司 | 移位寄存器及其驱动方法、移位寄存器组及其驱动方法 |

| TWI500015B (zh) * | 2014-06-20 | 2015-09-11 | Au Optronics Corp | 雙向選擇電路、應用此雙向選擇電路的閘極驅動器與測試電路 |

| KR102397388B1 (ko) * | 2014-07-24 | 2022-05-13 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 표시 모듈 및 전자 기기 |

| CN104200769B (zh) * | 2014-08-19 | 2016-09-28 | 上海和辉光电有限公司 | 扫描信号产生电路 |

| CN104409054B (zh) * | 2014-11-03 | 2017-02-15 | 深圳市华星光电技术有限公司 | 低温多晶硅薄膜晶体管goa电路 |

| CN104537973A (zh) * | 2014-12-29 | 2015-04-22 | 厦门天马微电子有限公司 | 一种移位寄存器、栅极驱动电路、阵列基板和显示面板 |

| CN104575436B (zh) * | 2015-02-06 | 2017-04-05 | 京东方科技集团股份有限公司 | 移位寄存器单元、栅极驱动电路及显示装置 |

| US10297331B2 (en) * | 2015-10-30 | 2019-05-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| JP6705687B2 (ja) * | 2016-04-04 | 2020-06-03 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN110010078B (zh) * | 2019-03-14 | 2022-02-08 | 合肥京东方卓印科技有限公司 | 移位寄存器单元、栅极驱动电路和显示装置 |

| CN110085171A (zh) | 2019-04-22 | 2019-08-02 | 上海天马有机发光显示技术有限公司 | 一种显示面板、其驱动方法及显示装置 |

| CN110033737B (zh) * | 2019-05-31 | 2021-10-26 | 上海天马有机发光显示技术有限公司 | 一种扫描电路、显示面板及显示装置 |

| CN111653228A (zh) * | 2020-06-17 | 2020-09-11 | 京东方科技集团股份有限公司 | 移位寄存单元的驱动方法、栅极驱动电路和显示装置 |

| CN119785730A (zh) * | 2025-01-24 | 2025-04-08 | 京东方科技集团股份有限公司 | 像素驱动方法、显示设备、时序控制器和存储介质 |

Family Cites Families (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US442839A (en) * | 1890-12-16 | Envelope machine | ||

| US2575544A (en) * | 1949-01-26 | 1951-11-20 | Jr Julius A Zinn | Method and apparatus for closing and sealing containers |

| US4008850A (en) * | 1962-01-29 | 1977-02-22 | St. Regis Paper Company | Gusseted pinch bottom bag |

| BE639342A (ja) * | 1962-11-14 | 1900-01-01 | ||

| DE3408722A1 (de) * | 1983-12-08 | 1985-06-20 | Karl-Heinz Dr. 4802 Halle Sengewald | Abreissbeutel aus thermoplastischer kunststoffolie |

| US5048692A (en) * | 1990-04-03 | 1991-09-17 | Colgate-Palmolive Company | Bag closure structure in which a single resealable closure acts as both the primary and secondary closures |

| US5410583A (en) * | 1993-10-28 | 1995-04-25 | Rca Thomson Licensing Corporation | Shift register useful as a select line scanner for a liquid crystal display |

| US5721302A (en) * | 1994-06-06 | 1998-02-24 | Wood; Benny R. | Water dispersible adhesive |

| JPH0855493A (ja) * | 1994-08-10 | 1996-02-27 | Sanyo Electric Co Ltd | シフトレジスタ及び表示装置の駆動回路 |

| US5654970A (en) * | 1995-12-22 | 1997-08-05 | Xerox Corporation | Array with redundant integrated self-testing scan drivers |

| TW491954B (en) * | 1997-11-10 | 2002-06-21 | Hitachi Device Eng | Liquid crystal display device |

| JP3843658B2 (ja) * | 1998-09-22 | 2006-11-08 | セイコーエプソン株式会社 | 電気光学装置の駆動回路及び電気光学装置並びに電子機器 |

| JP3858486B2 (ja) * | 1998-11-26 | 2006-12-13 | セイコーエプソン株式会社 | シフトレジスタ回路、電気光学装置および電子機器 |

| KR100430099B1 (ko) * | 1999-03-02 | 2004-05-03 | 엘지.필립스 엘시디 주식회사 | 쉬프트 레지스터 회로 |

| TW548476B (en) * | 1999-12-01 | 2003-08-21 | Chi Mei Optoelectronics Corp | Liquid crystal display module, scanning method of liquid crystal panel and its scan circuit board |

| TW495729B (en) * | 1999-12-01 | 2002-07-21 | Chi Mei Electronics Corp | Liquid crystal display module and scanning circuit board thereof |

| DE10106289A1 (de) * | 2001-02-06 | 2002-08-29 | Windmoeller & Hoelscher | Verfahren zum Herstellen von Seitenfaltensäcken aus Kunststoffolie |

| JP4761643B2 (ja) * | 2001-04-13 | 2011-08-31 | 東芝モバイルディスプレイ株式会社 | シフトレジスタ、駆動回路、電極基板及び平面表示装置 |

| JP4310939B2 (ja) * | 2001-06-29 | 2009-08-12 | カシオ計算機株式会社 | シフトレジスタ及び電子装置 |

| KR100803163B1 (ko) * | 2001-09-03 | 2008-02-14 | 삼성전자주식회사 | 액정표시장치 |

| US6897281B2 (en) * | 2002-04-05 | 2005-05-24 | Noveon Ip Holdings Corp. | Breathable polyurethanes, blends, and articles |

| US7129744B2 (en) * | 2003-10-23 | 2006-10-31 | Viciciv Technology | Programmable interconnect structures |

| JP4006284B2 (ja) * | 2002-07-17 | 2007-11-14 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| SE524961C2 (sv) * | 2002-08-16 | 2004-11-02 | Celanese Emulsions Norden Ab | Vattenburen sampolymerdispersion och dess användning i ytbeläggningar |

| JP4460822B2 (ja) | 2002-11-29 | 2010-05-12 | 東芝モバイルディスプレイ株式会社 | 双方向シフトレジスタ、これを用いた駆動回路、平面表示装置 |

| JP4391107B2 (ja) | 2003-03-19 | 2009-12-24 | パナソニック株式会社 | 固体撮像装置、固体撮像装置の駆動方法およびカメラ |

| JP2004134053A (ja) | 2003-08-28 | 2004-04-30 | Seiko Epson Corp | シフトレジスタ回路、電気光学装置の駆動回路、電気光学装置および電子機器 |

| US7683860B2 (en) * | 2003-12-02 | 2010-03-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device, driving method thereof, and element substrate |

| US6991592B2 (en) * | 2004-02-05 | 2006-01-31 | Genpak Llc | Method of folding flat bottom bag |

| JP5190722B2 (ja) * | 2005-05-20 | 2013-04-24 | Nltテクノロジー株式会社 | ブートストラップ回路並びにこれを用いたシフトレジスタ、走査回路及び表示装置 |

| JP4793121B2 (ja) * | 2005-08-24 | 2011-10-12 | セイコーエプソン株式会社 | 電気光学装置、及びこれを備えた電子機器 |

| JP2007114343A (ja) * | 2005-10-19 | 2007-05-10 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| FR2897542B1 (fr) * | 2006-02-21 | 2008-06-06 | Promiles Snc | Table de tennis de table |

| JP4912000B2 (ja) * | 2006-03-15 | 2012-04-04 | 三菱電機株式会社 | シフトレジスタ回路およびそれを備える画像表示装置 |

| US7731425B2 (en) * | 2006-06-15 | 2010-06-08 | Standard Multiwall Bag Manufacturing Co. | Polywoven pinch bottom open mouth bag |

| KR101263531B1 (ko) * | 2006-06-21 | 2013-05-13 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR101243807B1 (ko) * | 2006-06-30 | 2013-03-18 | 엘지디스플레이 주식회사 | 쉬프트 레지스터 |

| JP2008020675A (ja) * | 2006-07-13 | 2008-01-31 | Mitsubishi Electric Corp | 画像表示装置 |

| JP2007048439A (ja) * | 2006-08-25 | 2007-02-22 | Casio Comput Co Ltd | シフトレジスタ及び電子装置 |

| US8164562B2 (en) * | 2006-10-24 | 2012-04-24 | Samsung Electronics Co., Ltd. | Display device and driving method thereof |

-

2007

- 2007-07-17 JP JP2007185974A patent/JP4968681B2/ja active Active

-

2008

- 2008-07-17 US US12/174,808 patent/US20090021466A1/en not_active Abandoned

- 2008-07-17 CN CN200810133833.XA patent/CN101350179B/zh active Active

-

2011

- 2011-12-29 US US13/339,804 patent/US8654056B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009027265A (ja) | 2009-02-05 |

| US20120112992A1 (en) | 2012-05-10 |

| CN101350179A (zh) | 2009-01-21 |

| CN101350179B (zh) | 2013-07-24 |

| US20090021466A1 (en) | 2009-01-22 |

| US8654056B2 (en) | 2014-02-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4968681B2 (ja) | 半導体回路とそれを用いた表示装置並びにその駆動方法 | |

| JP5224241B2 (ja) | 双方向シフトレジスタ、それを用いた表示装置 | |

| JP5472781B2 (ja) | シフトレジスタ及び表示装置並びにシフトレジスタの駆動方法 | |

| JP4912186B2 (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| CN102810303B (zh) | 显示装置 | |

| JP4990034B2 (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| JP4761643B2 (ja) | シフトレジスタ、駆動回路、電極基板及び平面表示装置 | |

| CN100583297C (zh) | 移位寄存器电路和具备该电路的图像显示装置 | |

| JP4912023B2 (ja) | シフトレジスタ回路 | |

| CN100397446C (zh) | 脉冲输出电路、移位寄存器和显示器件 | |

| US8937614B2 (en) | Bidirectional shift register and display device using the same | |

| JP5527647B2 (ja) | シフトレジスタ | |

| US6989810B2 (en) | Liquid crystal display and data latch circuit | |

| JP5132884B2 (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| US20070024568A1 (en) | Shift register and display device using same | |

| JP2021529410A (ja) | シフトレジスターおよび駆動方法、ゲート駆動回路および表示装置 | |

| JP6009153B2 (ja) | 表示装置 | |

| KR100838653B1 (ko) | 시프트 레지스터 회로 및 그것을 구비한 화상표시장치 | |

| CN113178221A (zh) | 移位寄存器及其驱动方法、栅极驱动电路、显示装置 | |

| US20030063048A1 (en) | Active matrix display device and data line switching circuit, switching section drive circuit, and scanning line drive circuit thereof | |

| CN101026011A (zh) | 移位寄存器电路及设有该电路的图像显示装置 | |

| JP2010049768A (ja) | シフトレジスタ及び表示装置 | |

| JP2007207411A (ja) | シフトレジスタ回路およびそれを備える画像表示装置 | |

| JP4832100B2 (ja) | 表示装置 | |

| JP3506222B2 (ja) | 論理回路及び画像表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100611 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120208 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120306 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120327 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150413 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4968681 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |