JP4659751B2 - 低k誘電体を半導体製造プロセスにおいて形成する方法 - Google Patents

低k誘電体を半導体製造プロセスにおいて形成する方法 Download PDFInfo

- Publication number

- JP4659751B2 JP4659751B2 JP2006536603A JP2006536603A JP4659751B2 JP 4659751 B2 JP4659751 B2 JP 4659751B2 JP 2006536603 A JP2006536603 A JP 2006536603A JP 2006536603 A JP2006536603 A JP 2006536603A JP 4659751 B2 JP4659751 B2 JP 4659751B2

- Authority

- JP

- Japan

- Prior art keywords

- dielectric layer

- layer

- forming

- low

- dielectric

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P70/00—Cleaning of wafers, substrates or parts of devices

- H10P70/20—Cleaning during device manufacture

- H10P70/23—Cleaning during device manufacture during, before or after processing of insulating materials

- H10P70/234—Cleaning during device manufacture during, before or after processing of insulating materials the processing being the formation of vias or contact holes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/074—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H10W20/075—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers of multilayered thin functional dielectric layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/074—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H10W20/077—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers on sidewalls or on top surfaces of conductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/093—Manufacture or treatment of dielectric parts thereof by modifying materials of the dielectric parts

- H10W20/096—Manufacture or treatment of dielectric parts thereof by modifying materials of the dielectric parts by contacting with gases, liquids or plasmas

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P70/00—Cleaning of wafers, substrates or parts of devices

- H10P70/10—Cleaning before device manufacture, i.e. Begin-Of-Line process

- H10P70/18—Cleaning before device manufacture, i.e. Begin-Of-Line process by combined dry cleaning and wet cleaning

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

- Cleaning Or Drying Semiconductors (AREA)

Description

当業者であれば、これらの図における構成要素が説明を簡単かつ明瞭にするために示され、そして必ずしも寸法通りには描かれていないことが分かるであろう。例えば、これらの図における幾つかの構成要素の寸法を他の構成要素に対して誇張して描いて本発明の実施形態を理解し易くしている。

とができる。導電層30は銅であることが好ましいが、別の導電材料とすることができる。キャップ層32は、テトラエチルオルトシリケート(TEOS)を使用して形成される酸化物であることが好ましいが、他の誘電体材料とすることができる。誘電体24は複合層であり、上層はSiCOH、またはフッ素及びTEOS(FTEOS)を使用して形成される酸化物のいずれかであることが好ましい。CMPプロセスを誘電体層24に適用して、CMP処理後の層24の表面上の材料を変えることができるようにする。CMPプロセスを実行する前の層24上の材料の好適な組み合わせは、シリコンリッチな酸化物、シリコンリッチな酸窒化物、TEOS酸化物であり、この組み合わせにより、層24の上部表面は、素子10が形成されるウェハ全体に渡って同じとはならない。半導体素子10は、低kバリア層26及び低K誘電体28から成る複合層、及び低kバリア層34及び低K誘電体層36から成る複合層を形成する方法を除いた従来の手段によって形成することができる従来構造である。

によって歩留まりが著しく改善された。

Claims (4)

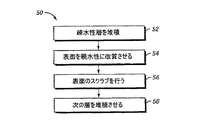

- 半導体基板の上に層を形成するための方法であって、

半導体基板を設ける工程と、

疎水性表面を有する第1誘電体層を前記基板の上に形成する工程と、

前記第1誘電体層を酸素プラズマ処理することによって、前記疎水性表面を親水性表面に改質する工程と、

前記親水性表面をスクラブ処理することによって、前記第1誘電体層の表面に接着しているパーティクルを除去する工程と、

第2誘電体層を前記第1誘電体層の上に形成する工程とを備える、方法。 - 半導体構造の製造方法であって、

半導体基板を設ける工程と、

シリコン、炭素、及び窒素を含有する第1誘電体層を前記基板の上に形成する工程と、

前記第1誘電体層を酸素プラズマで処理する工程と、

前記第1誘電体層をスクラブ処理することによって、前記第1誘電体層の表面に接着しているパーティクルを除去する工程と、

第2誘電体層を前記第1誘電体層の上に形成する工程とを備え、前記第1誘電体層は疎水性表面を有していたものが、前記第1誘電体層を処理する前記工程によって、前記疎水性表面のほぼ全てが親水性表面に改質される、製造方法。 - スクラブ処理する工程では、水を用いた洗浄水溶液でスクラブ洗浄する、請求項1又は2記載の方法。

- 前記第1誘電体層を形成する工程は、

シリコン、炭素、及び窒素から成る第1誘電体層を形成する工程を備え、

前記第1誘電体層を形成する工程、及び前記第1誘電体層を処理する工程は、インサイチュー(in−situ)で行われる、請求項1又は2記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/690,060 US6902440B2 (en) | 2003-10-21 | 2003-10-21 | Method of forming a low K dielectric in a semiconductor manufacturing process |

| PCT/US2004/024904 WO2005045914A1 (en) | 2003-10-21 | 2004-07-30 | Method of forming a low k dielectric in a semiconductor manufacturing process |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007509499A JP2007509499A (ja) | 2007-04-12 |

| JP2007509499A5 JP2007509499A5 (ja) | 2007-09-13 |

| JP4659751B2 true JP4659751B2 (ja) | 2011-03-30 |

Family

ID=34521542

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006536603A Expired - Fee Related JP4659751B2 (ja) | 2003-10-21 | 2004-07-30 | 低k誘電体を半導体製造プロセスにおいて形成する方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6902440B2 (ja) |

| JP (1) | JP4659751B2 (ja) |

| KR (1) | KR101054676B1 (ja) |

| CN (1) | CN100501937C (ja) |

| TW (1) | TW200515532A (ja) |

| WO (1) | WO2005045914A1 (ja) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6913992B2 (en) | 2003-03-07 | 2005-07-05 | Applied Materials, Inc. | Method of modifying interlayer adhesion |

| US7030041B2 (en) | 2004-03-15 | 2006-04-18 | Applied Materials Inc. | Adhesion improvement for low k dielectrics |

| US7253125B1 (en) | 2004-04-16 | 2007-08-07 | Novellus Systems, Inc. | Method to improve mechanical strength of low-k dielectric film using modulated UV exposure |

| US7112541B2 (en) * | 2004-05-06 | 2006-09-26 | Applied Materials, Inc. | In-situ oxide capping after CVD low k deposition |

| US9659769B1 (en) | 2004-10-22 | 2017-05-23 | Novellus Systems, Inc. | Tensile dielectric films using UV curing |

| US8980769B1 (en) | 2005-04-26 | 2015-03-17 | Novellus Systems, Inc. | Multi-station sequential curing of dielectric films |

| US8889233B1 (en) | 2005-04-26 | 2014-11-18 | Novellus Systems, Inc. | Method for reducing stress in porous dielectric films |

| US8454750B1 (en) | 2005-04-26 | 2013-06-04 | Novellus Systems, Inc. | Multi-station sequential curing of dielectric films |

| US7189658B2 (en) * | 2005-05-04 | 2007-03-13 | Applied Materials, Inc. | Strengthening the interface between dielectric layers and barrier layers with an oxide layer of varying composition profile |

| US7273823B2 (en) * | 2005-06-03 | 2007-09-25 | Applied Materials, Inc. | Situ oxide cap layer development |

| US7498270B2 (en) * | 2005-09-30 | 2009-03-03 | Tokyo Electron Limited | Method of forming a silicon oxynitride film with tensile stress |

| JP4422671B2 (ja) * | 2005-12-06 | 2010-02-24 | トヨタ自動車株式会社 | 半導体装置とその製造方法 |

| US8987085B2 (en) * | 2006-08-01 | 2015-03-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Methods for improving uniformity of cap layers |

| US10037905B2 (en) * | 2009-11-12 | 2018-07-31 | Novellus Systems, Inc. | UV and reducing treatment for K recovery and surface clean in semiconductor processing |

| US8465991B2 (en) | 2006-10-30 | 2013-06-18 | Novellus Systems, Inc. | Carbon containing low-k dielectric constant recovery using UV treatment |

| US7851232B2 (en) * | 2006-10-30 | 2010-12-14 | Novellus Systems, Inc. | UV treatment for carbon-containing low-k dielectric repair in semiconductor processing |

| US20100267231A1 (en) * | 2006-10-30 | 2010-10-21 | Van Schravendijk Bart | Apparatus for uv damage repair of low k films prior to copper barrier deposition |

| US8211510B1 (en) | 2007-08-31 | 2012-07-03 | Novellus Systems, Inc. | Cascaded cure approach to fabricate highly tensile silicon nitride films |

| KR100928502B1 (ko) * | 2007-11-05 | 2009-11-26 | 주식회사 동부하이텍 | 반도체 소자 및 그의 제조 방법 |

| US9050623B1 (en) | 2008-09-12 | 2015-06-09 | Novellus Systems, Inc. | Progressive UV cure |

| JP5507909B2 (ja) | 2009-07-14 | 2014-05-28 | 東京エレクトロン株式会社 | 成膜方法 |

| JP5398853B2 (ja) * | 2012-01-26 | 2014-01-29 | 東京エレクトロン株式会社 | プラズマ処理方法及びプラズマ処理装置 |

| CN103854962B (zh) * | 2012-11-28 | 2017-05-17 | 中芯国际集成电路制造(上海)有限公司 | 晶圆刻蚀后的清洗方法 |

| CN104681404A (zh) * | 2013-11-27 | 2015-06-03 | 中芯国际集成电路制造(上海)有限公司 | 接触孔的制作方法和半导体器件的湿法清洗方法 |

| US9437484B2 (en) * | 2014-10-17 | 2016-09-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Etch stop layer in integrated circuits |

| KR101611133B1 (ko) * | 2015-05-18 | 2016-04-08 | 성균관대학교산학협력단 | 3차원 구조의 가스 센서 및 이의 제조방법 |

| US10008382B2 (en) | 2015-07-30 | 2018-06-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device having a porous low-k structure |

| US9847221B1 (en) | 2016-09-29 | 2017-12-19 | Lam Research Corporation | Low temperature formation of high quality silicon oxide films in semiconductor device manufacturing |

| JP6989207B2 (ja) | 2018-05-15 | 2022-01-05 | 住友電工デバイス・イノベーション株式会社 | キャパシタの製造方法 |

| CN109994371B (zh) * | 2019-03-26 | 2021-10-15 | 上海华力集成电路制造有限公司 | 一种改善氮掺杂碳化物堆叠后的清洁产生水痕的方法 |

| CN110444468A (zh) * | 2019-08-29 | 2019-11-12 | 上海华力微电子有限公司 | 一种消除生成硬掩模ndc层后产生的凸块缺陷的方法 |

| KR102665267B1 (ko) * | 2022-10-06 | 2024-05-13 | 한국생명공학연구원 | 감도가 개선된 국소 표면 플라즈몬 공명 센서 및 이의 제조방법 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US114000A (en) * | 1871-04-25 | Improvement in buggies | ||

| US87534A (en) * | 1869-03-09 | Improvement in feather-renovators | ||

| US68853A (en) * | 1867-09-17 | peters | ||

| US1089643A (en) * | 1913-04-02 | 1914-03-10 | William O Hoppe | Preboiler for steam-boilers. |

| US5607773A (en) * | 1994-12-20 | 1997-03-04 | Texas Instruments Incorporated | Method of forming a multilevel dielectric |

| US5944906A (en) * | 1996-05-24 | 1999-08-31 | Micron Technology Inc | Wet cleans for composite surfaces |

| JP3028080B2 (ja) * | 1997-06-18 | 2000-04-04 | 日本電気株式会社 | 半導体装置の構造およびその製造方法 |

| JPH11251312A (ja) * | 1998-03-06 | 1999-09-17 | Matsushita Electron Corp | 半導体装置の製造方法 |

| US6468362B1 (en) | 1999-08-25 | 2002-10-22 | Applied Materials, Inc. | Method and apparatus for cleaning/drying hydrophobic wafers |

| US6531412B2 (en) | 2001-08-10 | 2003-03-11 | International Business Machines Corporation | Method for low temperature chemical vapor deposition of low-k films using selected cyclosiloxane and ozone gases for semiconductor applications |

| US20030087534A1 (en) | 2001-09-10 | 2003-05-08 | Rensselaer Polytechnic Institute | Surface modification for barrier to ionic penetration |

| CN1179613C (zh) * | 2001-09-20 | 2004-12-08 | 联华电子股份有限公司 | 一种改善有机低介电常数层附着力的表面处理方法 |

| JP2003188254A (ja) | 2001-12-18 | 2003-07-04 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| US20030155657A1 (en) * | 2002-02-14 | 2003-08-21 | Nec Electronics Corporation | Manufacturing method of semiconductor device |

| US6812167B2 (en) * | 2002-06-05 | 2004-11-02 | Taiwan Semiconductor Manufacturing Co., Ltd | Method for improving adhesion between dielectric material layers |

-

2003

- 2003-10-21 US US10/690,060 patent/US6902440B2/en not_active Expired - Fee Related

-

2004

- 2004-07-30 WO PCT/US2004/024904 patent/WO2005045914A1/en not_active Ceased

- 2004-07-30 CN CNB2004800290719A patent/CN100501937C/zh not_active Expired - Fee Related

- 2004-07-30 KR KR1020067007734A patent/KR101054676B1/ko not_active Expired - Fee Related

- 2004-07-30 JP JP2006536603A patent/JP4659751B2/ja not_active Expired - Fee Related

- 2004-08-23 TW TW093125368A patent/TW200515532A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| US6902440B2 (en) | 2005-06-07 |

| JP2007509499A (ja) | 2007-04-12 |

| KR20060101758A (ko) | 2006-09-26 |

| WO2005045914A1 (en) | 2005-05-19 |

| CN1864251A (zh) | 2006-11-15 |

| TW200515532A (en) | 2005-05-01 |

| CN100501937C (zh) | 2009-06-17 |

| KR101054676B1 (ko) | 2011-08-08 |

| US20050085082A1 (en) | 2005-04-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4659751B2 (ja) | 低k誘電体を半導体製造プロセスにおいて形成する方法 | |

| CN101330043B (zh) | 利用低介电层填充金属线间空隙的半导体器件的制造方法 | |

| KR101126850B1 (ko) | 이중 라이너 캡핑층 상호접속 구조물 | |

| TWI825142B (zh) | 用以改善選擇性沉積製程中之選擇性的預處理方法 | |

| TW201733069A (zh) | 半導體元件結構 | |

| US6417098B1 (en) | Enhanced surface modification of low K carbon-doped oxide | |

| TW200407979A (en) | Method of manufacturing low K layer | |

| JP3997859B2 (ja) | 半導体装置の製造方法および製造装置 | |

| CN1103492C (zh) | 形成平坦内金属介电层的方法 | |

| CN102820216B (zh) | 半导体器件的制备方法 | |

| US20040171277A1 (en) | Method of forming a conductive metal line over a semiconductor wafer | |

| US6881590B2 (en) | Re-performable spin-on process | |

| US6926590B1 (en) | Method of improving device performance | |

| KR20220123983A (ko) | 기판처리방법 및 이를 포함하는 반도체 소자 제조방법 | |

| KR100333059B1 (ko) | 웨이퍼세정방법및이를수행하기위한세정장치 | |

| KR100972061B1 (ko) | 반도체 소자의 패드 알루미늄 처리 방법 | |

| KR19990024816A (ko) | 스핀 온 글래스층을 이용한 층간 절연층 형성방법 | |

| TWI899525B (zh) | 半導體晶圓的清洗溶液及其清洗方法 | |

| KR100875819B1 (ko) | 반도체 소자의 제조 방법 | |

| KR0181905B1 (ko) | 반도체소자의 제조방법 | |

| JP2005353870A (ja) | 半導体装置の製造方法 | |

| KR20230052682A (ko) | 기판처리방법 및 이를 이용하는 반도체 소자 제조방법 | |

| TW400599B (en) | Method of confirming the reasons of the defects in the IC process | |

| KR20080114041A (ko) | 반도체 소자의 제조방법 | |

| KR20100050972A (ko) | 반도체 소자의 금속배선 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070725 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070725 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100527 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100601 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100901 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100908 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101001 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101207 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101227 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140107 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |