JP4154598B2 - 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 - Google Patents

液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 Download PDFInfo

- Publication number

- JP4154598B2 JP4154598B2 JP2003301589A JP2003301589A JP4154598B2 JP 4154598 B2 JP4154598 B2 JP 4154598B2 JP 2003301589 A JP2003301589 A JP 2003301589A JP 2003301589 A JP2003301589 A JP 2003301589A JP 4154598 B2 JP4154598 B2 JP 4154598B2

- Authority

- JP

- Japan

- Prior art keywords

- common

- potential

- liquid crystal

- state

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 71

- 238000000034 method Methods 0.000 title claims description 55

- 239000000758 substrate Substances 0.000 claims description 37

- 239000011159 matrix material Substances 0.000 claims description 25

- 239000010409 thin film Substances 0.000 claims description 17

- 230000005669 field effect Effects 0.000 claims description 13

- 230000005540 biological transmission Effects 0.000 claims description 12

- 230000000295 complement effect Effects 0.000 claims description 3

- 101100284008 Dictyostelium discoideum comH gene Proteins 0.000 description 13

- 238000010586 diagram Methods 0.000 description 10

- 230000002441 reversible effect Effects 0.000 description 7

- 239000000463 material Substances 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 230000000593 degrading effect Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 239000004988 Nematic liquid crystal Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3655—Details of drivers for counter electrodes, e.g. common electrodes for pixel capacitors or supplementary storage capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Power Engineering (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

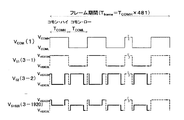

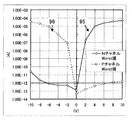

VS1〜1920(3−1〜1920)はデータ線入力端子(302−1〜1920)に入力される映像信号電位であり、最高電位VVIDEOH〜最低電位VVIDEOLの範囲内であって、その詳細波形は表示する画像により異なる。本実施例ではデータ線1(202−1)に接続された画素では白(透過)表示、データ線2(202−2)に接続された画素では黒(非透過)表示、データ線1920(202−1920)に接続された画素ではグレー(半透過)表示をそれぞれ行うように、また画素電極への充電完了・画素ス一チング素子OFF後、プレチャージ信号として白レベル信号を入力した後、コモン反転タイミングではフローティングするようにしてVS1、VS2およびVS1920の波形を描いている。VS1〜1920(3−1〜1920)の映像信号の出力開始・停止タイミングやプレチャージタイミングは点順次駆動、線順次駆動、ブロック順次駆動などの駆動方式によりそれぞれ異なるが、いずれの場合でもコモン反転タイミングではデータ線をフローティング状態にしておくべきである。本実施例では線順次駆動を前提としている。

以上の条件を勘案した本実施例での各電位の設定値として、例えばVWHITE=0.5(V)、VBLACK=4.0(V)となるような液晶材料並びに貼り合わせギャップを選択したとするなら、VH=8.5(V)、VGON=7.5(V)、VCOMH=6.5(V)、VVIDEOH=6(V)、VVIDEOL=2.5(V)、VCOML=2(V)、VGOFF=1(V)、VL=0(V)とすれば良い。

また、図2の350に示したようなクロックドインバーターによるシフトレジスタ構成でなく、フリップフロップ回路や伝送ゲートによるシフトレジスタ構成に置き換えても良いし、シフトレジスタでなく様々な順次選択回路を用い、それにあわせて図2の論理回路部を変更してもちろん構わない。

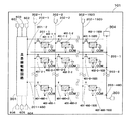

201−1〜480:走査線1〜480

202−1〜1920:データ線1〜1920

301:走査線駆動回路

303:コモン電極電位入力端子

304:対向導通部

350:シフトレジスタ

351−1〜480:第一のクロックドインバーター

352−1〜480:第二のクロックドインバーター

353−1〜480:第一のインバーター

402−1〜480−1〜1920:画素電極(1〜480,1〜1920)

505−1〜480:第一NAND回路

506−1〜480:第二インバーター

507−1〜480:第二NAND回路

508−1〜480:第三NAND回路

509−1〜480:第四NAND回路

510−1〜480:第五NAND回路

511−1〜480:第一トランジスター

512−1〜480:第二トランジスター

601:CLK信号端子

602:CLKX信号端子

603:XST信号端子

604:HENB端子

605:LENB端子

606:LCHG端子

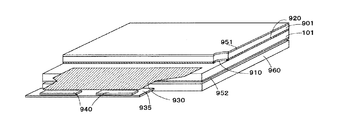

901:対向基板

Claims (20)

- 一対の基板間に液晶層を封入してなり、前記一対の基板の一方の基板には複数の走査線と複数のデータ線と前記各走査線および前記各データ線に接続された画素スイッチング素子と前記画素スイッチング素子に接続された画素電極とを有し、更に前記画素電極に対して液晶を介して対向配置されたコモン電極を有し、

前記複数の走査線に接続された前記画素スイッチング素子をローインピーダンス状態にする一つ又は複数の選択電位と、該走査線に接続された前記画素スイッチング素子をハイインピーダンス状態にする一つ又は複数の非選択電位とを走査線毎に異なったタイミングで順次出力する走査線駆動回路が、前記複数の走査線に接続されてなり、前記走査線駆動回路は異なる電位を有した複数の電源配線と接続されてなる液晶表示装置の駆動方法において、

前記コモン電極を相対的に高い電位のコモン・ハイ状態と相対的に低い電位のコモン・ロー状態の交互に反転駆動するコモン反転駆動であり、かつ前記コモン電極の電位が前記コモン・ハイ状態から前記コモン・ロー状態に、ならびに前記コモン・ロー状態から前記コモン・ハイ状態に切り換えるコモン反転動作は、前記複数の走査線の少なくとも一部が前記複数の電源配線から電気的に分離されているフローティング状態であり、

前記複数の走査線は、

前記選択電位の電源と比較的低い電気抵抗で接続された状態の選択状態である期間と、

前記非選択電位の電源と比較的低い電気抵抗で接続された状態の非選択状態である期間と、

前記フローティング状態である期間とをそれぞれ有する、

ことを特徴とした液晶表示装置の駆動方法。 - 前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記走査線が前記フローティング状態となるタイミングでは該走査線の電位は前記非選択電位と概略等しく、かつ前記コモン電極が前記コモン・ハイ状態である

ことを特徴とする請求項1に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、

前記走査線が前記フローティング状態となるタイミングでは該走査線の電位は前記非選択電位と概略等しく、かつ前記コモン電極が前記コモン・ロー状態である

ことを特徴とする請求項1に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はNチャネル型電界効果トランジスターよりなる第一スイッチングトランジスターとPチャネル型電界効果トランジスターよりなる第二スイッチングトランジスターより構成される相補型伝送ゲートであり、

前記走査線は前記第一スイッチングトランジスターに接続される第一走査線と前記第二スイッチングトランジスターに接続される第二走査線よりなり、

前記第一走査線が前記フローティング状態となるタイミングでは前記第一走査線の電位は前記非選択電位と概略等しくかつ前記コモン電極が前記コモン・ハイ状態であり、

さらに前記第二走査線が前記フローティング状態となるタイミングでは前記第二走査線の電位は前記非選択電位と概略等しくかつ前記コモン電極が前記コモン・ロー状態であることを特徴とする請求項1に記載の液晶表示装置の駆動方法。 - 前記非選択状態である期間の長さは一定でないことを特徴とする

請求項1から4のいずれか一項に記載の液晶表示装置の駆動方法。 - 前記複数の走査線は前記選択状態から次に前記選択状態になるまでの間に複数の前記非選択状態を有し、さらに前記複数の非選択状態の間に前記フローティング状態を有する,

請求項1から5のいずれか一項に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記選択状態の間にある複数の非選択状態のうち前記選択状態直後のものを除いた2回目以降の非選択状態は常に前記コモン電極が前記コモン・ハイ状態である時に実施され、かつ前記2回目以降の非選択状態中に前記コモン反転動作を生じない

ことを特徴とした請求項6に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、

前記選択状態の間にある複数の非選択状態のうち前記選択状態直後のものを除いた2回目以降の非選択状態は常に前記コモン電極が前記コモン・ロー状態である時に実施され、かつ前記2回目以降の非選択状態中に前記コモン反転動作を生じない

ことを特徴とした請求項6に記載の液晶表示装置の駆動方法。 - 前記コモン電極がコモン・ハイ状態である期間長と、コモン・ロー状態である期間長は等しくないことを特徴とする請求項1から8のいずれか一項に記載の液晶表示装置の駆動方法。

- 前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記コモン電極がコモン・ハイ状態である期間長はコモン・ロー状態である期間長より大きい

ことを特徴とする請求項9に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、

前記コモン電極がコモン・ハイ状態である期間長はコモン・ロー状態である期間長より小さい

ことを特徴とする請求項9に記載の液晶表示装置の駆動方法。 - 前記非選択電位は前記コモン電極の電位によらず概略一定の値である

請求項1から11のいずれか一項に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はNチャネル型電界効果トランジスターであり、

前記非選択電位の値が、前記データ線に印加される映像信号電位の最低値に前記画素スイッチング素子のしきい値を足した値より低く、前記映像信号電位の最低値から前記コモン・ハイ状態での前記コモン電極の電位を引き前記コモン・ロー状態での前記コモン電極の電位を足した値より高い

ことを特徴とする請求項12に記載の液晶表示装置の駆動方法。 - 前記画素スイッチング素子はPチャネル型電界効果トランジスターであり、前記非選択電位の値が、前記データ線に印加される映像信号電位の最高電位に画素スイッチング素子のしきい値を足した値より高く、前記コモン・ハイ状態での前記コモン電極のへの印加電位から前記コモン・ロー状態での前記コモン電極の印加電位を引いた値に前記映像信号電位の最高値を足した値より低い

ことを特徴とする請求項12に記載の液晶表示装置の駆動方法。 - 前記コモン・ハイ状態のときの前記非選択電位と前記コモン・ロー状態のときの前記非選択電位が相互に異なり、

前記コモン・ハイ状態のときの前記非選択電位が前記コモン・ロー状態のときの前記非選択電位より大きい

ことを特徴とする請求項1から11のいずれか一項に記載の液晶表示装置の駆動方法。 - 前記コモン反転動作では少なくとも前記複数のデータ線の一部、より望ましくは全ての前記複数のデータ線がフローティング状態であることを特徴とする請求項1から15のいずれか一項に記載の液晶表示装置の駆動方法。

- 請求項1から16のいずれか一項に記載の駆動方法を用いて画像を表示する液晶表示装置。

- 前記走査線の数の二乗を画像表示部の対角方向の長さに乗じた係数が30000以上であることを特徴とする請求項17に記載の液晶表示装置。

- 前記走査線駆動回路の少なくとも一部は前記アクティブマトリクス基板上に形成された薄膜トランジスターによって構成されている駆動回路内蔵型液晶表示装置である請求項17および18に記載の液晶表示装置。

- 請求項17から19のいずれか一項に記載の液晶表示装置を用いて画像を表示する機能を有したバッテリーで駆動される携帯電子機器。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003301589A JP4154598B2 (ja) | 2003-08-26 | 2003-08-26 | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 |

| US10/921,811 US7414602B2 (en) | 2003-08-26 | 2004-08-20 | Method of driving liquid crystal display device, liquid crystal display device, and portable electronic apparatus |

| CN2004100644128A CN1591103B (zh) | 2003-08-26 | 2004-08-24 | 液晶显示装置的驱动法、液晶显示装置及便携式电子机器 |

| KR1020040066969A KR100634068B1 (ko) | 2003-08-26 | 2004-08-25 | 액정 표시 장치의 구동법, 액정 표시 장치 및 휴대형전자기기 |

| TW093125560A TWI286238B (en) | 2003-08-26 | 2004-08-26 | Driving method for liquid crystal display, liquid crystal display, and portable electronic machine |

| US12/216,432 US8248338B2 (en) | 2003-08-26 | 2008-07-03 | Method of driving liquid crystal display device, liquid crystal display device, and portable electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003301589A JP4154598B2 (ja) | 2003-08-26 | 2003-08-26 | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005070539A JP2005070539A (ja) | 2005-03-17 |

| JP2005070539A5 JP2005070539A5 (ja) | 2006-05-25 |

| JP4154598B2 true JP4154598B2 (ja) | 2008-09-24 |

Family

ID=34225073

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003301589A Expired - Lifetime JP4154598B2 (ja) | 2003-08-26 | 2003-08-26 | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7414602B2 (ja) |

| JP (1) | JP4154598B2 (ja) |

| KR (1) | KR100634068B1 (ja) |

| CN (1) | CN1591103B (ja) |

| TW (1) | TWI286238B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4449784B2 (ja) * | 2005-02-28 | 2010-04-14 | エプソンイメージングデバイス株式会社 | 電気光学装置、駆動方法および電子機器 |

| JP4419897B2 (ja) | 2005-03-30 | 2010-02-24 | エプソンイメージングデバイス株式会社 | 液晶表示装置の駆動法、液晶表示装置及び電子機器 |

| JP4432852B2 (ja) * | 2005-07-11 | 2010-03-17 | エプソンイメージングデバイス株式会社 | 液晶装置及び電子機器 |

| JP4650133B2 (ja) * | 2005-07-13 | 2011-03-16 | エプソンイメージングデバイス株式会社 | 電気光学装置、駆動方法および電子機器 |

| KR100743498B1 (ko) * | 2005-08-18 | 2007-07-30 | 삼성전자주식회사 | 표시 장치의 전류 구동 데이터 드라이버 및 이를 가지는표시 장치 |

| US7324098B1 (en) * | 2006-07-26 | 2008-01-29 | Chunghwa Picture Tubes, Ltd. | Driving circuit for display device |

| KR101277975B1 (ko) * | 2006-09-07 | 2013-06-27 | 엘지디스플레이 주식회사 | 쉬프트 레지스터 및 이를 구비한 데이터 드라이버,액정표시장치 |

| JP4415393B2 (ja) * | 2006-09-26 | 2010-02-17 | エプソンイメージングデバイス株式会社 | 駆動回路、液晶装置、電子機器、および液晶装置の駆動方法 |

| JP2008107780A (ja) * | 2006-09-29 | 2008-05-08 | Matsushita Electric Ind Co Ltd | 信号伝達回路,表示データ処理装置,および表示装置 |

| KR101415064B1 (ko) * | 2007-12-11 | 2014-07-04 | 엘지디스플레이 주식회사 | 액정표시장치의 구동 제어 장치 및 방법 |

| KR101469096B1 (ko) * | 2008-06-27 | 2014-12-15 | 삼성전자주식회사 | 게이트 드라이버 및 그 구동 방법과 이를 적용한디스플레이 패널 구동 장치 |

| CN102804250B (zh) * | 2009-06-17 | 2015-08-19 | 夏普株式会社 | 显示驱动电路、显示装置和显示驱动方法 |

| TWI396179B (zh) * | 2009-08-26 | 2013-05-11 | Raydium Semiconductor Corp | 低功率之顯示面板驅動方法及驅動電路 |

| JP6491821B2 (ja) * | 2014-04-07 | 2019-03-27 | 株式会社ジャパンディスプレイ | 表示装置 |

| WO2016080500A1 (ja) * | 2014-11-21 | 2016-05-26 | シャープ株式会社 | アクティブマトリクス基板、及びそれを備えた表示装置 |

| CN107402462B (zh) * | 2017-09-21 | 2020-06-05 | 深圳市华星光电技术有限公司 | 液晶显示面板及控制方法 |

| CN107702885B (zh) * | 2017-09-29 | 2019-08-30 | 中国水利水电科学研究院 | 床面颗粒起悬时间的提取方法 |

| CN109147694B (zh) | 2018-09-03 | 2021-09-10 | 明基智能科技(上海)有限公司 | 防止画面残影的方法及显示系统 |

| TWI679625B (zh) * | 2018-09-04 | 2019-12-11 | 明基電通股份有限公司 | 防止畫面殘影的方法及顯示系統 |

| CN113140191A (zh) * | 2021-04-16 | 2021-07-20 | 武汉华星光电技术有限公司 | 一种显示装置 |

Family Cites Families (64)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4652872A (en) * | 1983-07-07 | 1987-03-24 | Nec Kansai, Ltd. | Matrix display panel driving system |

| JPS6249399A (ja) | 1985-08-29 | 1987-03-04 | キヤノン株式会社 | 表示装置 |

| JP2607719B2 (ja) | 1990-03-07 | 1997-05-07 | 富士写真フイルム株式会社 | 感光材料現像装置 |

| US6893906B2 (en) | 1990-11-26 | 2005-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and driving method for the same |

| JP3013259B2 (ja) | 1990-11-13 | 2000-02-28 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US20010050664A1 (en) | 1990-11-13 | 2001-12-13 | Shunpei Yamazaki | Electro-optical device and driving method for the same |

| TW209895B (ja) | 1990-11-26 | 1993-07-21 | Semiconductor Energy Res Co Ltd | |

| US5233448A (en) * | 1992-05-04 | 1993-08-03 | Industrial Technology Research Institute | Method of manufacturing a liquid crystal display panel including photoconductive electrostatic protection |

| JP2607719Y2 (ja) | 1993-11-24 | 2002-07-08 | カシオ計算機株式会社 | 液晶表示装置 |

| DE69508682T2 (de) * | 1994-09-06 | 1999-09-30 | Kabushiki Kaisha Toshiba, Kawasaki | Anzeigevorrichtung |

| JP2626595B2 (ja) * | 1994-11-17 | 1997-07-02 | 日本電気株式会社 | アクティブマトリクス型液晶ディスプレイ一体型タブレット及びその駆動方法 |

| JPH08166499A (ja) | 1994-12-12 | 1996-06-25 | Nissin High Voltage Co Ltd | 電子線照射装置 |

| US6229515B1 (en) * | 1995-06-15 | 2001-05-08 | Kabushiki Kaisha Toshiba | Liquid crystal display device and driving method therefor |

| KR0172881B1 (ko) | 1995-07-12 | 1999-03-20 | 구자홍 | 액정표시장치의 구조 및 구동방법 |

| CN100356434C (zh) * | 1995-12-14 | 2007-12-19 | 精工爱普生株式会社 | 显示装置及其驱动方法 |

| KR100219116B1 (ko) * | 1996-03-30 | 1999-09-01 | 구자홍 | 티에프티 엘시디 디스플레이의 구동방법 |

| TW329002B (en) | 1996-06-05 | 1998-04-01 | Zenshin Test Co | Apparatus and method for inspecting a LCD substrate |

| JPH10104300A (ja) | 1996-06-05 | 1998-04-24 | Advantest Corp | Lcd基板検査装置及び方法 |

| JP3486859B2 (ja) | 1996-06-14 | 2004-01-13 | 大林精工株式会社 | 液晶表示装置 |

| JP3567183B2 (ja) | 1996-08-19 | 2004-09-22 | 大林精工株式会社 | 液晶表示装置 |

| JP3716580B2 (ja) * | 1997-02-27 | 2005-11-16 | セイコーエプソン株式会社 | 液晶装置及びその製造方法、並びに投写型表示装置 |

| US6084562A (en) | 1997-04-02 | 2000-07-04 | Kabushiki Kaisha Toshiba | Flat-panel display device and display method |

| JP3774855B2 (ja) | 1997-04-25 | 2006-05-17 | 大林精工株式会社 | 液晶表示装置と製造方法. |

| JPH10333117A (ja) | 1997-05-28 | 1998-12-18 | Sharp Corp | 液晶表示装置の駆動装置 |

| JPH1124041A (ja) * | 1997-06-30 | 1999-01-29 | Toshiba Corp | 液晶表示装置 |

| US6177968B1 (en) * | 1997-09-01 | 2001-01-23 | Canon Kabushiki Kaisha | Optical modulation device with pixels each having series connected electrode structure |

| JP3050191B2 (ja) * | 1997-11-12 | 2000-06-12 | 日本電気株式会社 | 液晶表示装置 |

| US6433841B1 (en) * | 1997-12-19 | 2002-08-13 | Seiko Epson Corporation | Electro-optical apparatus having faces holding electro-optical material in between flattened by using concave recess, manufacturing method thereof, and electronic device using same |

| CN1263610A (zh) | 1998-03-19 | 2000-08-16 | 松下电器产业株式会社 | 液晶显示元件及其制造方法 |

| JP3147867B2 (ja) | 1998-08-26 | 2001-03-19 | 日本電気株式会社 | アクティブマトリクス型液晶表示装置の駆動回路 |

| JP2000098334A (ja) | 1998-09-28 | 2000-04-07 | Alps Electric Co Ltd | 液晶表示装置 |

| US7379039B2 (en) * | 1999-07-14 | 2008-05-27 | Sony Corporation | Current drive circuit and display device using same pixel circuit, and drive method |

| JP3379491B2 (ja) | 1999-10-22 | 2003-02-24 | 日本電気株式会社 | 液晶表示装置 |

| JP3659103B2 (ja) * | 1999-12-28 | 2005-06-15 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 |

| US6856307B2 (en) * | 2000-02-01 | 2005-02-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor display device and method of driving the same |

| JP5051942B2 (ja) | 2000-02-01 | 2012-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2001222621A (ja) | 2000-02-14 | 2001-08-17 | Fujitsu Ltd | 保守支援端末装置、保守管理装置および保守支援方法 |

| TWI282457B (en) * | 2000-04-06 | 2007-06-11 | Chi Mei Optoelectronics Corp | Liquid crystal display component with defect restore ability and restoring method of defect |

| JP2001356741A (ja) * | 2000-06-14 | 2001-12-26 | Sanyo Electric Co Ltd | レベルシフタ及びそれを用いたアクティブマトリクス型表示装置 |

| JP3723747B2 (ja) * | 2000-06-16 | 2005-12-07 | 松下電器産業株式会社 | 表示装置およびその駆動方法 |

| JP3750565B2 (ja) * | 2000-06-22 | 2006-03-01 | セイコーエプソン株式会社 | 電気泳動表示装置の駆動方法、駆動回路、および電子機器 |

| JP2002091342A (ja) * | 2000-07-10 | 2002-03-27 | Toshiba Corp | マトリクスアレイ基板 |

| JP4123711B2 (ja) * | 2000-07-24 | 2008-07-23 | セイコーエプソン株式会社 | 電気光学パネルの駆動方法、電気光学装置、および電子機器 |

| JP3915400B2 (ja) * | 2000-11-28 | 2007-05-16 | 株式会社日立製作所 | 画像表示装置及び画像表示装置の駆動方法 |

| JP3494146B2 (ja) * | 2000-12-28 | 2004-02-03 | 日本電気株式会社 | 有機el駆動回路及びパッシブマトリクス有機el表示装置並びに有機el駆動方法 |

| GB2372620A (en) * | 2001-02-27 | 2002-08-28 | Sharp Kk | Active Matrix Device |

| JP3608613B2 (ja) * | 2001-03-28 | 2005-01-12 | 株式会社日立製作所 | 表示装置 |

| JP3774858B2 (ja) | 2001-04-07 | 2006-05-17 | 大林精工株式会社 | 液晶表示装置とその駆動方法 |

| JP3791355B2 (ja) | 2001-06-04 | 2006-06-28 | セイコーエプソン株式会社 | 駆動回路、及び駆動方法 |

| JP3956748B2 (ja) * | 2001-06-26 | 2007-08-08 | セイコーエプソン株式会社 | 表示装置、その駆動回路、その駆動方法および電子機器 |

| JP2003173174A (ja) | 2001-09-25 | 2003-06-20 | Sharp Corp | 画像表示装置および表示駆動方法 |

| US20030103022A1 (en) * | 2001-11-09 | 2003-06-05 | Yukihiro Noguchi | Display apparatus with function for initializing luminance data of optical element |

| JP3944394B2 (ja) * | 2002-01-08 | 2007-07-11 | 株式会社日立製作所 | 表示装置 |

| JP3520418B2 (ja) * | 2002-02-04 | 2004-04-19 | セイコーエプソン株式会社 | 演算増幅回路、駆動回路及び演算増幅回路の制御方法 |

| JP4225777B2 (ja) * | 2002-02-08 | 2009-02-18 | シャープ株式会社 | 表示装置ならびにその駆動回路および駆動方法 |

| JP4030863B2 (ja) * | 2002-04-09 | 2008-01-09 | シャープ株式会社 | 電気光学装置、それを用いた表示装置、その駆動方法、並びに、その重みの設定方法 |

| JP3677011B2 (ja) * | 2002-04-30 | 2005-07-27 | アルプス電気株式会社 | 液晶表示装置 |

| JP4701589B2 (ja) * | 2002-09-30 | 2011-06-15 | セイコーエプソン株式会社 | 液晶装置と投射型表示装置 |

| JP2004317785A (ja) * | 2003-04-16 | 2004-11-11 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置および電子機器 |

| JP2005005227A (ja) * | 2003-06-16 | 2005-01-06 | Hitachi Displays Ltd | 有機el発光表示装置 |

| JP2005321457A (ja) * | 2004-05-06 | 2005-11-17 | Seiko Epson Corp | 走査線駆動回路、表示装置及び電子機器 |

| US7221413B2 (en) * | 2004-08-05 | 2007-05-22 | Au Optronics Corporation | Thin film transistor array substrate and repairing method thereof |

| JP4419897B2 (ja) * | 2005-03-30 | 2010-02-24 | エプソンイメージングデバイス株式会社 | 液晶表示装置の駆動法、液晶表示装置及び電子機器 |

| JP4432852B2 (ja) * | 2005-07-11 | 2010-03-17 | エプソンイメージングデバイス株式会社 | 液晶装置及び電子機器 |

-

2003

- 2003-08-26 JP JP2003301589A patent/JP4154598B2/ja not_active Expired - Lifetime

-

2004

- 2004-08-20 US US10/921,811 patent/US7414602B2/en active Active

- 2004-08-24 CN CN2004100644128A patent/CN1591103B/zh not_active Expired - Lifetime

- 2004-08-25 KR KR1020040066969A patent/KR100634068B1/ko not_active Expired - Lifetime

- 2004-08-26 TW TW093125560A patent/TWI286238B/zh not_active IP Right Cessation

-

2008

- 2008-07-03 US US12/216,432 patent/US8248338B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005070539A (ja) | 2005-03-17 |

| CN1591103B (zh) | 2010-04-28 |

| CN1591103A (zh) | 2005-03-09 |

| US8248338B2 (en) | 2012-08-21 |

| US20090027321A1 (en) | 2009-01-29 |

| KR20050022376A (ko) | 2005-03-07 |

| US20050052393A1 (en) | 2005-03-10 |

| US7414602B2 (en) | 2008-08-19 |

| KR100634068B1 (ko) | 2006-10-13 |

| TWI286238B (en) | 2007-09-01 |

| TW200517716A (en) | 2005-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8248338B2 (en) | Method of driving liquid crystal display device, liquid crystal display device, and portable electronic apparatus | |

| US8456400B2 (en) | Liquid crystal device and electronic apparatus | |

| CN101196632B (zh) | 电光装置、扫描线驱动电路及电子设备 | |

| JP5306762B2 (ja) | 電気光学装置及び電子機器 | |

| KR100519468B1 (ko) | 평면표시장치 | |

| KR100627762B1 (ko) | 평면 표시 패널의 구동 방법 및 평면 표시 장치 | |

| TW200919435A (en) | Electro-optical device, driving circuit, and electronic apparatus | |

| US7312638B2 (en) | Scanning line driving circuit, display device, and electronic apparatus | |

| JP5346379B2 (ja) | 画素回路及び表示装置 | |

| TW200834527A (en) | Driving circuit and driving method of liquid crystal device, liquid crystal device, and electronic apparatus | |

| JP4419897B2 (ja) | 液晶表示装置の駆動法、液晶表示装置及び電子機器 | |

| US7609247B2 (en) | Driving circuit for liquid crystal display device, liquid crystal display device, method of driving liquid crystal display device, and electronic apparatus | |

| JP4148064B2 (ja) | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 | |

| JP4957169B2 (ja) | 電気光学装置、走査線駆動回路および電子機器 | |

| JP2011013420A (ja) | 電気光学装置、その駆動方法および電子機器 | |

| JP4650133B2 (ja) | 電気光学装置、駆動方法および電子機器 | |

| JP2005241741A (ja) | 液晶表示装置の駆動法、液晶表示装置及び電子機器 | |

| JP2009223174A (ja) | 電気光学装置、駆動回路および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060329 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060329 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080219 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080410 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080421 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080611 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080624 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110718 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4154598 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110718 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120718 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120718 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130718 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |