JP3659103B2 - 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 - Google Patents

電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 Download PDFInfo

- Publication number

- JP3659103B2 JP3659103B2 JP37530499A JP37530499A JP3659103B2 JP 3659103 B2 JP3659103 B2 JP 3659103B2 JP 37530499 A JP37530499 A JP 37530499A JP 37530499 A JP37530499 A JP 37530499A JP 3659103 B2 JP3659103 B2 JP 3659103B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- line

- scanning

- electro

- optical device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims description 9

- 239000000758 substrate Substances 0.000 claims description 41

- 239000000463 material Substances 0.000 claims description 6

- 238000006243 chemical reaction Methods 0.000 claims description 4

- 230000003213 activating effect Effects 0.000 claims description 3

- 239000004973 liquid crystal related substance Substances 0.000 description 83

- 230000003071 parasitic effect Effects 0.000 description 26

- 238000010586 diagram Methods 0.000 description 10

- 239000010408 film Substances 0.000 description 10

- 239000004065 semiconductor Substances 0.000 description 7

- 239000003086 colorant Substances 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 238000005070 sampling Methods 0.000 description 5

- 101100367244 Arabidopsis thaliana SWA1 gene Proteins 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 230000007704 transition Effects 0.000 description 4

- 238000007667 floating Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 244000025254 Cannabis sativa Species 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000004815 dispersion polymer Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000000382 optic material Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000005693 optoelectronics Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2014—Display of intermediate tones by modulation of the duration of a single pulse during which the logic level remains constant

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Liquid Crystal Display Device Control (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

【発明の属する技術分野】

本発明は、低消費電力な電気光学装置、電気光学装置の駆動回路および駆動方法、この電気光学装置を表示部に用いた電子機器に関する。

【0002】

【従来の技術】

従来の電気光学装置、例えば、液晶装置の駆動回路は、画像表示領域に配線されたデータ線や走査線などに、画像信号や走査信号などを所定タイミングで供給するためのデータ線駆動回路や、走査線駆動回路などから構成されている。

【0003】

このデータ線駆動回路の構成は、入力画像信号がアナログ信号かあるいはデジタル信号かで大きく相違する。しかし、複数の階調表示を行う場合には、入力画像信号の形態に拘わらず、液晶にアナログ信号の電圧を印加する必要がある。したがって、入力画像信号がデジタル信号である場合には、入力画像信号にDA変換を施して液晶にアナログ信号電圧を印加しなければならない。

【0004】

このDA変換の一手法として、PWM(Pulse Width Modulation)法が知られている。図12は、PWM法を適用した液晶装置の構成を示すブロック図である。この図に示すように従来の液晶装置は、データ線駆動回路130'、走査線駆動回路140'、スイッチ群150、および画像表示領域AAから構成されている。

【0005】

画像表示領域AAにおいては、X方向に沿って平行に複数本の走査線112が配列して形成され、また、これと直交するY方向に沿って平行に複数本のデータ線114が形成されている。そして、これらの走査線112とデータ線114との各交点においては、各画素を制御するためのスイッチたる薄膜トランジスタ(Thin Film Transistor:以下TFTと称する。)が設けられている。

【0006】

この例では、TFT116のゲート電極が走査線112に接続される一方、TFT116のソース電極がデータ線114に接続されるとともに、TFT116のドレイン電極が画素電極118に接続されている。そして、各画素は、画素電極118と、対向基板に形成された共通電極と、これら両電極間に挟持された液晶とによって構成される結果、走査線112とデータ線114との各交点に対応して、マトリクス状に配列することとなる。なお、各データ線114は、液晶を介して共通電極と対向しており、また各走査線112と交差しているため各データ線114には寄生容量が付随する。

【0007】

データ線駆動回路140'は、入力画像データDに基づいて、各データ線114に対応した選択信号を線順次で出力する。各選択信号がアクティブとなる期間は、当該選択信号に対応する画素に表示すべき入力画像データ値に応じて定める。スイッチ群150を構成する各スイッチ151の入力端子には、ランプ波信号LSが供給され、その出力端子は各データ線114と接続されており、その制御端子には各選択信号が供給されている。各スイッチ151は各選択信号がアクティブの期間中、オン状態となるように構成されている。したがって、各データ線114には、画素に表示すべき入力画像データ値に応じた期間だけ、ランプ波信号LSが供給されることになる。この結果、各データ線114の寄生容量には、入力画像データ値に応じた期間だけランプ波信号が書き込まれることになる。一方、走査線駆動回路130'は、各水平走査期間毎にアクティブとなる走査信号を生成し、各走査信号を各走査線112に各々出力している。

【0008】

以上の構成において、ある走査線112が走査信号によって選択されると、当該水平走査期間においては、当該走査線112に接続された各TFT116がオン状態となる。このとき、各データ線114の寄生容量には、入力画像データ値に応じた期間だけランプ波信号LSが書き込まれるので、画素電極118には入力画像データ値に応じた電圧が印加され、TFT116がオフ状態になると印加電圧が保持されることになる。これにより、入力画像データの指示する階調値に応じた階調を表示することが可能となる。

【0009】

【発明が解決しようとする課題】

ところで、上述した液晶装置では、ランプ波信号LSを各データ線114の寄生容量に書き込み、寄生容量の電圧をTFT116を介して各画素に取り込むようになっている。このため、ランプ波信号LSの駆動回路は、寄生容量に対して書き込みが十分行えるだけの駆動能力を有する必要がある。

【0010】

しかしながら、画像表示領域AAが比較的小型のものであっても、データ線114の寄生容量値は1本当たり20PF程度はある。いわゆるXGA(1024画素×768画素)形式の液晶装置では、R,G,B各色毎に、1024本のデータ線を備えるので、データ線114の寄生容量値の合計は約61nFとなってしまう。ここで、入力画像データが6ビットであるとすれば、61nFの容量に対して1/64H期間に充電を完了する必要がある。したがって、ランプ波信号LSの駆動回路としては、大きな負荷を駆動できるもの使用しなければならず、回路規模が増大するといった問題があった。さらに、大きな負荷を駆動するため、駆動回路の消費電力が増大するといった問題があった。

【0011】

本発明は、上述した事情に鑑みてなされたもので、その目的とするところは、駆動負荷を軽減した電気光学装置、その駆動回路、並びに、この電気光学装置を表示部に用いた電子機器を提供することにある。

【0012】

【課題を解決するための手段】

上記目的を達成するため本発明に係る電気光学装置の駆動方法にあっては、複数のデータ線と、複数の走査線と、前記走査線と前記データ線との交差に対応する各画素電極と、各走査線に対応する複数の信号供給線とを備えた電気光学装置を駆動することを前提とし、前記各走査線を順次選択する各走査信号を各々供給し、前記各走査信号がアクティブになると、これに同期して基準信号を前記各信号供給線に順次供給し、画像データの指示する階調値に応じた期間だけアクティブとなるパルス幅変調信号を各データ線に各々供給し、前記各走査線と前記各データ線との交差に対応した各画素において、当該画素に対応する走査線とデータ線とが同時にアクティブとなる期間では、当該画素に対応する信号供給線から前記基準信号を取り込んで前記画素電極に印加する一方、当該画素に対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、前記画素電極の電圧を保持することを特徴とする。

【0013】

この発明によれば、基準信号は、各走査信号がアクティブになると、これに同期して各信号供給線に順次供給されることになる。したがって、基準信号を駆動する駆動回路の負荷は、1本の信号供給線に付随する寄生容量となるので、負荷を軽減することができる。この結果、基準信号を供給する工程において、消費電流を大幅に削減することが可能となる。

【0014】

次に、本発明に係る電気光学装置は、一対の基板間に電気光学物質を狭持してなることを前提とし、一方の基板上に、複数のデータ線と、複数の走査線と、前記走査線と前記データ線との交差に対応して設けられた複数の画素電極と、各走査線に対応する複数の信号供給線と、前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、選択された信号供給線に基準信号を供給する信号供給手段と、前記走査線と前記データ線との交差に対応して各々設けられ、対応する走査線とデータ線とが同時にアクティブとなる期間では前記信号供給線から前記基準信号を取り込んで前記画素電極に印加する一方、対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、前記画素電極の電圧を保持する電圧保持手段とを備えたことを特徴とする。

【0015】

この発明によれば、信号供給手段は、前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、選択された信号供給線に基準信号を供給する。一方、各走査線は順次選択されるようになっている。このため、基準信号が供給される信号供給線は1本である。したがって、基準信号を駆動する駆動回路の負荷は、1本の信号供給線に付随する寄生容量となるので、負荷を大幅に軽減することができる。さらに、駆動回路の回路構成を簡易なものにすることができ、くわえて、駆動回路の消費電流を大幅に削減することが可能となる。

【0016】

ここで、前記信号供給手段は、前記各信号供給線毎に設けられ、前記信号供給線の一端が一方の端子に接続され、対応する走査線の信号によってオン・オフが制御されるスイッチング素子と、前記各スイッチング素子の他方の端子に各々接続されるともに前記基準信号が供給される共通信号線とを備えることが好ましい。この発明では、スイッチング素子を走査線の信号によってオン・オフさせることができるので、選択しようとしている走査線に対応する信号供給線のみに基準信号を供給することが可能となる。

【0017】

また、前記電圧保持手段は、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えることが望ましい。

【0018】

この発明では、第1トランジスタ素子と第2トランジスタ素子がゲート線と走査線の電圧によって制御され、第1および第2トランジスタ素子が同時にオン状態となった時に、信号供給線の電圧が画素電極に印加される。ここで、信号供給線には対応する走査線が選択された場合に基準信号が供給されるので、第1および第2トランジスタ素子が同時にオン状態になると、基準信号が画素電極に印加される。これにより、画像データの階調値に応じた階調表示が可能となる。くわえて、データ線は第1トランジスタ素子のソース電極に接続されるので、データ線に付随する寄生容量の値を小さくすることができ、これにより、データ線を駆動する駆動回路の負荷を減らし消費電流を削減することができる。

【0019】

また、前記電圧保持手段は、前記走査線と前記データ線との交差に対応して各々設けられ、前記データ線にゲート電極が接続され、前記信号供給線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がソース電極に接続され、前記走査線にゲート電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えるものであってもよい。この発明では、第1および第2トランジスタ素子が同時にオン状態となった時に、信号供給線の電圧が画素電極に印加される。ここで、信号供給線には対応する走査線が選択された場合に基準信号が供給されるので、第1および第2トランジスタ素子が同時にオン状態になると、基準信号が画素電極に印加される。これにより、画像データの階調値に応じた階調表示が可能となる。

【0020】

次に、本発明に係る電気光学装置の駆動回路にあっては、前記基準信号を発生する基準信号発生手段と、画像データを線順次データに変換する変換手段と、前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し前記データ線に出力するパルス幅変調手段と、前記基準信号を発生する基準信号発生手段と、前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線駆動手段とを備えることを特徴とする。この発明によれば、パルス幅変調信号を各データ線に線順次で供給するとともに走査信号を生成する一方、基準信号を生成するから、電気光学装置を駆動して階調表示を行わせることができる。

【0021】

また、本発明に係る電気光学装置の駆動回路にあっては、電気光学装置が、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを備えることを前提とし、前記基準信号を発生する基準信号発生手段と、画像データを線順次データに変換する変換手段と、前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し前記データ線に出力するパルス幅変調手段と、前記基準信号を発生する基準信号発生手段と、前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線駆動手段とを備え、前記各走査信号のローレベル電位を、前記パルス幅変調信号のローレベル電位より約前記第2トランジスタの閾値電圧だけ高電位に設定することを特徴とする。

【0022】

この発明によれば、各走査信号のローレベル電位を、パルス幅変調信号のローレベル電位より約第2トランジスタの閾値電圧だけ高電位に設定したので、走査線の非選択期間において当該走査線に対応する第1トランジスタ素子をオン状態とオフ状態の境界で動作させることができ、第2トランジスタ素子のゲート電極がフローティング状態となることを回避できる。このため、第2トランジスタ素子を、走査線の非選択期間において確実にオフ状態とすることが可能となる。

【0023】

くわえて、この電気光学装置の駆動回路において、前記パルス幅変調手段は、前記パルス幅変調信号のハイレベル電位が、前記基準信号の最大電位より少なくとも前記第2トランジスタ素子の閾値電圧だけは高くなるように前記パルス幅変調信号を生成し、前記走査線駆動手段は、前記走査信号のハイレベル電位が、前記パルス幅変調信号のハイレベル電位より少なくとも前記第1トランジスタ素子の閾値電圧だけは高くなるように前記走査信号を生成することが望ましい。この発明によれば、パルス幅変調信号がハイレベルの時に、第1トランジスタ素子と第2トランジスタ素子とを確実にオン状態にして基準信号を画素電極に印加することが可能となる。

【0024】

また、前記基準信号は、ランプ波信号であることが好ましい。但し、基準信号を用いてガンマ補正を施す場合には、ガンマ補正カーブに従った基準信号を用いればよい。

【0025】

さらに、上述した駆動回路を、電気光学装置の前記一方の基板に形成してもよい。この場合、駆動回路を構成するトランジスタ素子を前記第1および第2トランジスタ素子と同一の製造プロセスで作成することによって、製造コストを削減できる。

【0026】

くわえて、上記目的を達成するために、本発明に係る電子機器にあっては、上記電気光学装置を備えることを特徴としているので、消費電力が削減される。

【0027】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して説明する。

【0028】

<第1実施形態>

まず、本発明の第1実施形態に係る電気光学装置について、電気光学材料として液晶を用いた液晶装置を例にとって説明する。

【0029】

<液晶装置の全体構成>

図1は、この液晶装置の電気的な構成を示すブロック図である。この図に示されるように、液晶装置は、液晶パネル100と制御回路200とを備える。このうち、制御回路200は、各部で使用されるタイミング信号や制御信号など(必要に応じて後述する)を出力するものである。

【0030】

ここで、液晶パネル100は、後述するように、素子基板と対向基板とが互いに電極形成面を対向して貼付された構成となっている。そして、素子基板上に、走査線駆動回路130、データ線駆動回路140および画像表示領域AAが構成されている。以下、これらの構成について説明する。

【0031】

<画像表示領域の構成>

次に、画像表示領域AAの電気的な構成について説明する。素子基板にあっては、図1においてX方向に沿って平行に複数本(m本)の走査線112が配列して形成され、さらに、各走査線112に対応して複数本(m本)の信号供給線113が配列して形成されている。また、これと直交するY方向に沿って平行に複数本(n本)のデータ線114が形成されている。ここで、各画素は、画素電極118と、対向基板に形成された共通電極(後述)と、これら両電極間に挟持された液晶とによって構成される。各画素は、走査線112とデータ線114との各交点に対応して、マトリクス状に配列することとなる。なお、このほかに、蓄積容量(図示省略)が、各画素毎に、電気的にみて、画素電極118と共通電極とに挟持された液晶に対して並列に形成される構成としても良い。

【0032】

走査線112とデータ線114との各交点においては、各画素を制御するためのスイッチたるTFT116およびTFT117が設けられている。TFT116のゲート電極は走査線112に接続される一方、TFT116のソース電極がデータ線114に接続されるとともに、TFT116のドレイン電極がTFT117のゲート電極に接続されている。また、TFT117のソース電極は信号供給線113に接続されるとともに、そのドレイン電極は画素電極118と接続されている。したがって、TFT116とTFT117が同時にオン状態になると、信号供給線113の電圧が画素電極118に印加されることになる。

【0033】

くわえて、各信号供給線113の一端は、各スイッチSWを介して共通信号線111と接続されている。この共通信号線111には、制御回路100から2H周期のランプ波信号LSが供給される。各スイッチSWは、対応する走査線112の電圧によって制御され、走査線112の走査信号Y1〜Ymがアクティブとなる期間において、オン状態となるようになっている。

【0034】

ここで、走査信号Y1〜Ymは水平走査期間毎に順次アクティブとなる信号である。したがって、各スイッチSWのうちオン状態となるのは常に1個だけであるから、ランプ波信号LSの駆動回路は、1本の信号供給線113に接続されることになる。この結果、ランプ波信号LSの駆動回路の負荷は、主として1本の信号供給線113に付随する寄生容量となる。すなわち、上述した構成によれば、従来のようにY方向に延在する総てのデータ線114の寄生容量が負荷となるのではなく、X方向に延在する1本の信号供給線113に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができる。

【0035】

さて、走査線駆動回路130とデータ線駆動回路140は、後述するように、透明性および絶縁性を有するガラス等からなる素子基板の対向面にあって、表示領域の周辺部に形成されるものである。ここで、走査線駆動回路130とデータ線駆動回路140の構成素子は、画素を駆動するTFT116,117と共通の製造プロセスで形成されるPチャネル型TFTおよびNチャネル型TFTを組み合わせて構成されるため、製造効率の向上や、製造コストの低下、素子特性の均一化などが図られている。

【0036】

<データ線駆動回路の構成>

次に、本実施形態に係るデータ線駆動回路140について説明する。データ線駆動回路140は、Xシフトレジスタ141、画像データ供給線142、スイッチ群SWA,SWB、第1ラッチ部143、第2ラッチ部144、および比較部145から構成されている。

【0037】

まず、Xシフトレジスタ141は、水平走査期間の最初に供給される転送開始パルスDXを、クロック信号CLXおよびその反転クロック信号CLXINVにしたがって順次シフトすることによって、各サンプリング信号S1〜Snを所定の順番で出力するよう構成されている。

【0038】

次に、画像データ供給線142は、画像データをパラレル形式で供給するものである。画像データDが1サンプル当たりjビットであれば、画像データ供給線142はj本の配線から構成される。なお、この例では、画像データDは1サンプル当たり6ビットであり、画像データ供給線142は6本の配線で構成されているものとするが、例えば、画像データが“カラー”である場合には、画像データ供給線142の本数は18本(=6(ビット幅)×3本(R/G/B))となる。

【0039】

次に、スイッチ群SWAは、n個のスイッチSWA1〜SWAnから構成されている。各スイッチSWA1〜SWAnの入出力端子は、画像データ供給線142と第1ラッチ部143とに接続されており、さらに各スイッチSWA1〜SWAnの制御端子にはサンプリング信号S1〜Snが供給されている。ここで、1個のスイッチは、1個のサンプリング信号によって6ビットの画像データを第1ラッチ部143に供給するか否かを制御できるようになっている。そして、各スイッチSWA1〜SWAnは、サンプリング信号S1〜Snがアクティブの場合にオン状態となり、非アクティブの場合にオフ状態となる。

【0040】

次に、第1ラッチ部143は、n個のラッチ回路から構成されており、スイッチ群SWAから供給される画像データD1〜Dnをラッチする。これにより、画像データDを点順次データに変換することができる。

【0041】

次に、スイッチ群SWBは、n個のスイッチSWB1〜SWBnから構成されている。各スイッチSWB1〜SWBnの入出力端子は、第1ラッチ部143と第2ラッチ部144に接続されており、さらに各スイッチSWB1〜SWBnの制御端子には転送信号TRSが供給されている。そして、各スイッチSWB1〜SWBnは、転送信号TRSがアクティブの場合にオン状態となり、非アクティブの場合にオフ状態となる。ここで、転送信号TRSは水平走査期間の終了時にアクティブとなる信号である。

【0042】

次に、第2ラッチ部144は、n個のラッチ回路から構成されており、スイッチ群SWBから供給される画像データD1〜Dnをラッチする。上述ように転送信号TRSは水平走査期間の終了時にアクティブとなるので、第2ラッチ部144の各出力信号は、画像データDを線順次データに変換したものとなる。すなわち、Xシフトレジスタ141、画像データ供給線142、スイッチ群SWA,SWB、第1ラッチ部143、および第2ラッチ部144は、画像データDを線順次データに変換する手段として機能する。

【0043】

次に、比較部145について説明する。図2は、比較部145とその周辺回路の構成を示すブロック図である。この図に示すように比較部145は、n個の単位回路R1〜Rnから構成されている。各単位回路R1〜Rnは、比較器1451とSRラッチ1452を備えている。また、制御部200にはカウンタ210が設けられおり、このカウンタ210は、水平走査期間の始まりからカウンタクロック信号CLKをカウントして、そのカウント結果を示すカウントデータCNTを生成し、比較部145に出力する。くわえて、制御部200は水平走査期間の始まりにおいてHレベルとなるセット信号SETを比較部145に出力する。

【0044】

各単位回路R1〜Rnにおいて、比較器1451は、画像データD1〜DnとカウントデータCNTとを比較して、両者が一致する場合にHレベルとなる一方、不一致の場合にLレベルとなる比較信号CSを、SRラッチ1452のリセット端子に供給する。各単位回路R1〜RnのSRラッチ1452は、セット端子に供給されるセット信号SETがHレベルになるとその論理レベルをHレベルに遷移させ、その後、比較信号CSがHレベルになるとその論理レベルをLレベルに遷移させて、PWM信号(パルス幅変調信号)X1〜Xnを生成する。

【0045】

図3は、画像データの値とPWM信号の波形を示したタイミングチャートである。この図に示すように、各PWM信号のHレベル期間は、各画像データの指示する階調値に応じた期間となる。

【0046】

このようにして得られたPWM信号X1〜Xnは、データ線駆動回路140の各出力信号として、n本のデータ線114に各々供給される。なお、PWM信号X1〜Xnは、SRラッチ1452の出力信号をレベルシフトして生成するようにしてもよい。

【0047】

<走査線駆動回路の構成>

次に、走査線駆動回路130について説明する。走査線駆動回路130は、Yシフトレジスタおよびレベルシフタ回路から構成されている。Yシフトレジスタは、水平走査期間の最初に供給される転送開始パルスDYを、クロック信号CLYおよびその反転クロック信号CLYINVにしたがって順次シフトすることによって、信号y1〜ymを所定の順番で出力するよう構成されている。レベルシフト回路は、Yシフトレジスタの各出力信号に所定の電圧だけレベルシフトを施すように構成されている。レベルシフト回路の各出力信号は、走査信号Y1〜Ymとしてm本の走査線に供給される。

【0048】

<各種波形の関係>

次に、上述したランプ波信号LS、PWM信号X1〜Xn、走査信号Y1〜Ymの電圧レベルについて説明する。図4は、1画素の周辺回路と各種信号の電圧レベルとの関係の一例を示す図である。なお、この図においてVCOMは対向電極の電位であり、Vth1はTFT116の閾値電圧、Vth2はTFT117の閾値電圧である。

【0049】

この図に示すようにランプ波信号LSは、奇数番目の水平走査期間Hoddにおいて電位VLSminから電位VLSaまでの間を直線的に増加する一方、偶数番目の水平走査期間Hevenにおいては電位VLSmaxから電位VLSbまでの間を直線的に減少する。ここで、対向電極の電位VCOMと電位VLSaとの差分は電位VCOMと電位VLSbとの差分と略等しく、また、対向電極の電位VCOMと電位VLSmaxとの差分は電位VCOMと電位VLSminとの差分と略等しくなるように設定してある。奇数番目の水平走査期間Hoddと偶数番目の水平走査期間Hevenにおいて、ランプ波信号LSの波形を対向電極の電位VCOMを中心として極性反転させたのは、液晶に交流電圧を印加することにより、液晶の劣化を防止するためである。

【0050】

なお、反転するか否かについては、一般には、▲1▼走査線112単位の極性反転であるか、▲2▼データ線114単位の極性反転であるか、▲3▼画素単位の極性反転であるか、▲4▼画面単位の極性反転であるかに応じて定められ、その反転周期は、1水平走査期間、1垂直走査期間またはドットクロック周期に設定される。ただし、本実施形態にあっては説明の便宜上、▲1▼走査線112単位の極性反転である場合を例にとって説明するが、本発明をこれに限定する趣旨ではない。

【0051】

次に、走査信号YのHレベル電位YHは、PWM信号XのHレベル電位XHよりVth1+α1だけ高電位側に設定している。これは、TFT116において、ソース電極の電位がXHとなった場合にゲート電極の電位をXH+Vth1+α1にして、TFT116を確実にオン状態にするためである。なお、α1の値は0V〜5V程度である。

【0052】

次に、PWM信号XのHレベル電位XHは、ランプ波信号LSの最大電位VLSmaxよりVth2+α2だけ高電位側に設定している。TFT116がオン状態になると、TFT117のゲート電極電位Qは、TFT116のソース電極電位と等しくなる。一方、TFT117のソース電極電位の最大値は、信号供給線113にランプ波信号LSが供給されVLSmaxとなったときである。PWM信号XのHレベル電位XHを、VLSmax+Vth2+α2としたのは、この場合にも、TFT117を確実にオン状態にして画素電極118に電位VLSmaxを印加するためである。なお、α2の値は0V〜5V程度である。

【0053】

この例では、時刻t1から時刻t3の期間において、走査信号YがHレベルとなり、TFT116がオン状態となる。このため、当該期間にTFT117のゲート電極にはPWM信号Xが印加される。そして、PWM信号XがHレベルとなる時刻t1から時刻t2までの期間において、TFT117がオン状態となり、画素電極118にランプ波信号LSが印加される。すると、画素電極118を介して液晶に画像データDの値に応じた電圧が印加されることになる。そして、時刻t2に至ると、PWM信号XがHレベルからLレベルに遷移するため、TFT117はオフ状態となる。液晶は等価的に容量成分を有するので、TFT117がオフ状態となっても電圧を保持する。これにより、画素は、画像データDの階調値に応じた階調表示を行うことができる。

【0054】

一方、走査信号YのLレベル電位YLは、PWM信号XのLレベル電位XLより約Vth1だけ高電位側に設定している。これは、当該画素の非選択期間において、TFT117のゲート電極がフローティングとなることを防止するためである。TFT116は、期間Taにおいてはオフ状態となるが、期間Tbにおいては、オン状態とオフ状態の境界にある。換言すれば、期間Tbにおいては、高インピーダンスでソース電極とドレイン電極とが接続されている。ところで、TFT117のゲート電極には、小さな値ではあるが浮遊容量が等価的に接続されている。このため、期間Tbにあっては、この浮遊容量に電荷が充電されるので、期間TaにおいてTFT116が完全にオフ状態になっても、TFT117のゲート電極電位Qは、非選択期間において電位XLを維持する。したがって、非選択期間においてTFT117は完全にオフ状態になるから、画素電極118と対向電極との間に蓄積された電荷がTFT117を介して漏れることがない。これにより、表示画像の品質を向上させることができる。

【0055】

<第1実施形態の動作>

次に、上述した構成に係る液晶装置における動作について説明する。図5は、液晶装置の動作を説明するためのタイミングチャートである。走査線駆動回路130には、垂直走査期間の最初にパルスDYが供給され、クロック信号CLYおよびその反転クロック信号CLYINVによって順次シフトされて、走査線112に走査信号Y1,Y2,Y3,…,Ymが順次出力される。これにより、複数の走査線112が1本ずつ線順次に下方向に選択されることとなる。

【0056】

一方、共通信号線111には、図5(a)に示すランプ波信号LSが常に供給されており、各走査線112に対応して設けられた各スイッチSWがオン状態になると、ランプ波信号LSが信号供給線113に供給される。図5(b)〜(e)に示すように走査信号Y1,Y2,Y3,…,Ymは、アクティブとなるHレベル期間が重複しないので、各スイッチSWは同時にオン状態となることがない。したがって、ランプ波信号LSの駆動回路は、各スイッチSWによって選択された1本の信号供給線113にのみ接続される。この結果、当該駆動回路の負荷は、共通信号線111に付随する寄生容量と1本の信号供給線113に付随する寄生容量の合計となる。

【0057】

ところで、寄生容量は、共通信号線111や信号供給線113が形成される素子基板と液晶を介して対向する対向基板の対向電極との間、またはデータ線114との間に発生する。ここで、共通信号線111は、後述するシール材の部分(図7および図8参照)やあるいは走査線駆動回路130とともに素子基板の周辺部分に形成する。このため、共通信号線111の寄生容量値は信号供給線113の寄生容量値と比較して小さくなり、駆動回路の負荷は、主として1本の信号供給線113に付随する寄生容量によって定まる。

【0058】

すなわち、本実施形態の液晶装置によれば、従来のようにY方向に延在する全てのデータ線114の寄生容量が負荷となるのではなく、X方向に延在する1本の信号供給線113に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができる。この結果、駆動回路の回路構成を簡易なものにすることができ、しかも消費電流を大幅に削減することが可能となる。

【0059】

次に、図1に示す左上の画素に着目すると、当該画素のTFT116のソース電極には、PWM信号X1(図5(i)参照)が供給される。このPWM信号X1は、以下のようにして生成される。

【0060】

まず、第2ラッチ部144において図5(g)に示すように線順次の画像データD1が生成され、これが比較部145を構成する単位回路R1の比較器1451に供給される。

【0061】

次に、比較器1451は画像データD1とカウントデータCNTとを比較して両者が一致すると比較信号CSの論理レベルをHレベルにする。上述したようにSRラッチ1452はセット信号SETの立ち上がりエッジで出力信号をHレベルに遷移させるとともに比較信号CSの立ち上がりエッジで出力信号をLレベルに遷移させるから、例えば、セット信号SETと比較信号CSが図5(f),(h)に示すものであるとすれば、PWM信号X1は図5(i)に示すものとなる。ここで、PWM信号X1のHレベル期間は、画像データD11,D12,D13…に応じた期間となる。換言すれば、PWM信号X1は、画像データD1の指示する階調値に応じてパルス幅が変調されたパルス幅変調信号である。

【0062】

図5(k)に示す期間Tでは走査信号Y1とPWM信号X1がともにHレベルとなるから、図1に示す左上の画素のTFT116とTFT117は、期間Tにおいて同時にオン状態になる。すると、図5(j)に示すランプ波信号LSがTFT117を介して画素電極118に印加される。そして、期間Tを過ぎると、TFT117はオフ状態となる。このため、画素電極118の電位は、図5(l)に示すように期間Tを経過した後には一定電位が維持されることになる。これにより、画像データD11の階調値に応じた電圧V11が液晶に印加され、階調表示が行われる。

【0063】

このように、本実施形態においては、ランプ波信号LSを1本の信号供給線113にのみ供給するようにしたので、液晶装置の消費電流を大幅に削減することができる。くわえて、走査線112が非選択となる期間にあっては、TFT116をオン状態とオフ状態の境界で動作させるようにしたので、TFT117を確実にオフさせることができ、表示画像の品質を向上させることが可能となる。

【0064】

<第2実施形態>

上述した第1実施形態にあっては、TFT116のゲート電極を走査線112に接続し、そのソース電極をデータ線114に接続し、そのドレイン電極をTFT117のゲート電極に接続するとともに、TFT117のソース電極を信号供給線113に接続し、そのドレイン電極を画素電極118に接続した。そして、第1実施形態の液晶装置は、スイッチSWを介してランプ波信号LSを信号供給線113に供給することによって、ランプ波信号LSの駆動回路の負荷を軽減するものであった。本発明は、これ以外の構成でも負荷を軽減して駆動回路の消費電流を減少させることが可能である。そこで、第1実施形態とは異なる第2実施形態について説明する。

【0065】

図6は、第2実施形態に係る液晶装置のブロック図である。第2実施形態の液晶装置は、1画素に対応するTFTの構成を除いて、図1に示す第1実施形態の液晶装置と同様に構成されている。図6において、走査線112とデータ線114との各交点においては、各画素を制御するためのスイッチたるTFT116aおよびTFT117aが設けられている。TFT116aのゲート電極はデータ線114に接続される一方、TFT116aのソース電極が信号供給線113に接続されるとともに、TFT116aのドレイン電極がTFT117aのソース電極に接続されている。また、TFT117aのゲート電極は走査線112に接続されるとともに、そのドレイン電極は画素電極118と接続されている。したがって、TFT116aとTFT117aが同時にオン状態になると、信号供給線113の電圧が画素電極118に印加されることになる。

【0066】

この例では、TFT116aとTFT117aの各ゲート電極が、データ線114と走査線112に各々接続されているので、第1実施形態のようにTFT117がフローティング状態となることを回避するためにPWM信号Xおよび走査信号Yの論理レベルについて対策を講じる必要はない。

【0067】

ところで、一般に、TFTのゲート電極は、CMOS構造の電界効果トランジスタと同様に、半導体層の上に極薄い酸化絶縁膜を形成し、この酸化絶縁膜の上にアルミニウム等で電極を設けることによって形成される。一方、ソース電極やドレイン電極は半導体層と直接接続されている。このため、ゲート電極は酸化絶縁膜を介して半導体層と容量結合している。したがって、ゲート容量値はソース容量値よりも大きいといえる。

【0068】

第2実施形態の液晶装置では、データ線114にTFT116aのゲート電極が接続されているから、第1実施形態の液晶装置はデータ線114の寄生容量値が第2実施形態の液晶装置に比較して小さくなるという点で、有利である。

【0069】

しかしながら、第2実施形態の液晶装置においても、各走査線112に対応して設けられた各スイッチSWが同時にオン状態になることはないから、ランプ波信号LSの駆動回路は、各スイッチSWによって選択された1本の信号供給線113にのみ接続される。したがって、当該駆動回路の負荷は、主として1本の信号供給線113に付随する寄生容量によって定まる。

【0070】

この結果、第2実施形態の液晶装置によれば、第1実施形態の液晶装置と同様に、X方向に延在する1本の信号供給線113に付随する寄生容量が負荷となるので、駆動回路の負荷を大幅に削減することができ、駆動回路の回路構成を簡易なものにすることができ、しかも消費電流を大幅に削減することが可能となる。

【0071】

<液晶パネルの構成例>

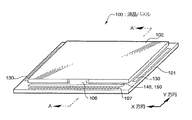

次に、上述した各実施形態に係るデータ線駆動回路140を有する液晶パネル100の全体構成について図7および図8を参照して説明する。ここで、図11は、液晶パネル100の構成を示す斜視図であり、図8は、図7におけるA−A’線の断面図である。

【0072】

これらの図に示されるように、液晶パネル100は、画素電極118等が形成されたガラスや、半導体、石英などの素子基板101と、共通電極108等が形成されたガラスなどの透明な対向基板102とが、スペーサ103の混入されたシール材104によって一定の間隙を保って、互いに電極形成面が対向するように貼り合わせられるとともに、この間隙に電気光学材料としての液晶105が封入された構造となっている。なお、シール材104は、対向基板102の基板周辺に沿って形成されるが、液晶105を封入するために一部が開口している。このため、液晶105の封入後に、その開口部分が封止材106によって封止されている。

【0073】

ここで、素子基板101の対向面であって、シール材104の外側一辺においては、上述したデータ線駆動回路140およびサンプリング回路150が形成されて、Y方向に延在するデータ線114を駆動する構成となっている。さらに、この一辺には複数の外部回路接続端子107が形成されて、制御回路200からの各種信号を入力する構成となっている。また、この一辺に隣接する2辺には、2個の走査線駆動回路130が形成されて、X方向に延在する走査線112をそれぞれ両側から駆動する構成となっている。なお、走査線112に供給される走査信号の遅延が問題にならないのであれば、走査線駆動回路130を片側1個だけに形成する構成でも良い。

【0074】

一方、対向基板102の共通電極108は、素子基板101との貼合部分における4隅のうち、少なくとも1箇所において設けられた導通材によって、素子基板101との電気的導通が図られている。ほかに、対向基板102には、液晶パネル100の用途に応じて、例えば、第1に、ストライプ状や、モザイク状、トライアングル状等に配列したカラーフィルタが設けられ、第2に、例えば、クロムやニッケルなどの金属材料や、カーボンやチタンなどをフォトレジストに分散した樹脂ブラックなどの遮光膜が設けられ、第3に、液晶パネル100に光を照射するバックライトが設けられる。なお、色光変調の用途の場合には、カラーフィルタは形成されずに遮光膜が対向基板102に設けられる。

【0075】

くわえて、素子基板101および対向基板102の対向面には、それぞれ所定の方向にラビング処理された配向膜(図示省略)などが設けられる一方、その各背面側には配向方向に応じた偏光板(図示省略)がそれぞれ設けられる。ただし、液晶105として、高分子中に微小粒として分散させた高分子分散型液晶を用いれば、前述の配向膜や偏光板などが不要となる結果、光利用効率が高まるので、高輝度化や低消費電力化などの点において有利である。

【0076】

なお、走査線駆動回路130やデータ線駆動回路140等の周辺回路の一部または全部を、素子基板101に形成する替わりに、例えば、TAB(Tape Automated Bonding)技術を用いてフィルムに実装された駆動用ICチップを、素子基板101の所定位置に設けられる異方性導電フィルムを介して電気的および機械的に接続する構成としても良いし、駆動用ICチップ自体を、COG(Chip On Grass)技術を用いて、素子基板101の所定位置に異方性導電フィルムを介して電気的および機械的に接続する構成としても良い。

【0077】

<素子基板の構成など>

また、各実施形態においては、液晶パネル100の素子基板101をガラス等の透明な絶縁性基板により構成して、当該基板上にシリコン薄膜を形成するとともに、当該薄膜上にソース、ドレイン、チャネルが形成されたTFTによって、画素のスイッチング素子(TFT116)、走査線駆動回路130、データ線駆動回路140の素子を構成するものとして説明したが、本発明はこれに限られるものではない。

【0078】

例えば、素子基板101を半導体基板により構成して、当該半導体基板の表面にソース、ドレイン、チャネルが形成された絶縁ゲート型電界効果トランジスタによって、画素のスイッチング素子や駆動回路120の素子を構成しても良い。このように素子基板101を半導体基板により構成する場合には、透過型の電気光学装置として用いることができないため、画素電極118をアルミニウムなどで形成して、反射型として用いられることとなる。また、単に、素子基板101を透明基板として、画素電極118を反射型にしても良い。

【0079】

さらに、電気光学材料としては、液晶のほかに、エレクトロルミネッセンス素子などを用いて、その電気光学効果により表示を行う表示装置にも適用可能である。すなわち、本発明は、上述した液晶装置と類似の構成を有するすべての電気光学装置に適用可能である。

【0080】

<ランプ信号およびPWM信号について>

上述した各実施形態では、図4に示すように直線的に増加または減少するランプ波信号LSを基準信号として用いることによって、PWM信号のパルス幅に応じた電圧を画素電極118に印加するようにしたが、本発明の特徴は、スイッチSWを介して基準信号を供給する点にあるので、基準信号はランプ波信号LSに限定されるものではない。例えば、基準信号を液晶のガンマ補正特性に応じたものにして、ガンマ補正を施すようにしてもよい。この場合、基準信号の波形は非線形に単調減少または単調増加させればよい。

【0081】

また、上述した各実施形態において画像データのLSBに対応するPWM信号のパルス幅は、画像データ値の大小に拘わらず一定であったが、本発明はこれに限定されるものではなく、ガンマ補正特性に応じた粗密を持たせるようにしてもよい。例えば、画像データ値が小さいときには、画像データのLSBに対応するPWM信号のパルス幅を広くし、画像データ値が大きくなるにつれ当該パルス幅を狭くし、画像データ値が中心値を取る時に最小となり、これを越えると次第に大きくなるように設定すればよい。

【0082】

<電子機器>

次に、上述した液晶装置を各種の電子機器に適用される場合について説明する。

【0083】

<その1:プロジェクタ>

まず、この液晶パネル100をライトバルブとして用いたプロジェクタについて説明する。図9は、このプロジェクタの構成を示す平面図である。この図に示されるように、プロジェクタ1100内部には、ハロゲンランプ等の白色光源からなるランプユニット1102が設けられている。このランプユニット1102から射出された投射光は、内部に配置された3枚のミラー1106および2枚のダイクロイックミラー1108によってRGBの3原色に分離されて、各原色に対応するライトバルブとしての液晶パネル100R、100Bおよび100Gにそれぞれ導かれる。ここで、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ1122、リレーレンズ1123および出射レンズ1124からなるリレーレンズ系1121を介して導かれる。

【0084】

さて、液晶パネル100R、100Bおよび100Gの構成は、上述した液晶パネル100と同等であり、画像信号処理回路(図示省略)から供給されるR、G、Bの原色信号でそれぞれ駆動されるものである。そして、これらの液晶パネルによって変調された光は、ダイクロイックプリズム1112に3方向から入射される。このダイクロイックプリズム1112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成される結果、投射レンズ1114を介して、スクリーン1120にカラー画像が投射されることとなる。

【0085】

ここで、各液晶パネル100R、100Bおよび100Gによる表示像について着目すると、液晶パネル100Gによる表示像は、液晶パネル100R、100Bによる表示像に対して左右反転していることが必要となる。このため、水平走査方向は、液晶パネル100Gと、液晶パネル100R、100Bとでは互いに逆方向の関係となる。なお、液晶パネル100R、100Bおよび100Gには、ダイクロイックミラー1108によって、R、G、Bの各原色に対応する光が入射するので、カラーフィルタを設ける必要はない。

【0086】

<その2:モバイル型コンピュータ>

次に、この液晶パネルを、モバイル型のパーソナルコンピュータに適用した例について説明する。図10は、このパーソナルコンピュータの構成を示す斜視図である。図において、コンピュータ1200は、キーボード1202を備えた本体部1204と、液晶表示ユニット1206とから構成されている。この液晶表示ユニット1206は、先に述べた液晶パネル100の背面にバックライトを付加することにより構成されている。

【0087】

<その3:携帯電話>

さらに、この液晶パネルを、携帯電話に適用した例について説明する。図11は、この携帯電話の構成を示す斜視図である。図において、携帯電話1300は、複数の操作ボタン1302のほか、受話口1304、送話口1306とともに、液晶パネル100を備えるものである。この液晶パネル100にも、必要に応じてその背面にバックライトが設けられる。

【0088】

なお、電子機器としては、図9〜図11を参照して説明した他にも、液晶テレビや、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種電子機器に対して、各実施形態の液晶パネル、さらには電気光学装置が適用可能なのは言うまでもない。

【0089】

【発明の効果】

以上説明したように本発明によれば、基準信号が供給される信号供給線は1本である。したがって、基準信号を駆動する駆動回路の負荷は、1本の信号供給線に付随する寄生容量となるので、負荷を大幅に軽減することができる。さらに、駆動回路の回路構成を簡易なものにすることができ、くわえて、駆動回路の消費電流を大幅に削減することが可能となる。

【図面の簡単な説明】

【図1】 本発明の第1実施形態に係る液晶装置の全体構成を示すブロック図である。

【図2】 同液晶装置における比較部の構成を示すブロック図である。

【図3】 画像データの値とPWM信号の波形を示したタイミングチャートである。

【図4】 1画素の周辺回路と各種信号の電圧レベルとを示す図である。

【図5】 同液晶装置の動作を説明するためのタイミングチャートである。

【図6】 本発明の第2実施形態に係る液晶装置の全体構成を示すブロック図である。

【図7】 液晶パネルの構造を示す斜視図である。

【図8】 同液晶パネルの構造を説明するための一部断面図である。

【図9】 同液晶装置を適用した電子機器の一例たるプロジェクタの構成を示す断面図である。

【図10】 同液晶装置を適用した電子機器の一例たるパーソナルコンピュータの構成を示す斜視図である。

【図11】 同液晶装置を適用した電子機器の一例たる携帯電話の構成を示す斜視図である。

【図12】 従来の液晶装置の全体構成を示すブロック図である。

【符号の説明】

100……液晶パネル

101……素子基板

102……対向基板

111……共通信号線

112……走査線

113……信号供給線

114……データ線

116,116a……TFT(第1トランジスタ素子)

117,117a……TFT(第2トランジスタ素子)

130……走査線駆動回路

140……データ線駆動回路

SW……スイッチ(信号供給手段)

LS……ランプ波信号(基準信号)

Claims (9)

- 複数のデータ線と、複数の走査線と、前記走査線と前記データ線との交差に対応する複数の画素と、各走査線に対応する複数の信号供給線とを備えた電気光学装置の駆動方法であって、

前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、

前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子とを有した各画素に対して、

前記各走査線を順次選択する各走査信号を各々供給し、

前記各走査信号がアクティブになると、これに同期して基準信号を前記各信号供給線に順次供給し、

画像データの指示する階調値に応じた期間だけアクティブとなるパルス幅変調信号を各データ線に各々供給し、

前記画素は、当該画素に対応する走査線とデータ線とが同時にアクティブとなる期間では、当該画素に対応する信号供給線から前記基準信号を取り込み、当該画素に対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、取り込んだ前記基準信号に基づく電圧を保持する

ことを特徴とする電気光学装置の駆動方法。 - 一対の基板間に電気光学物質を狭持してなる電気光学装置において、

複数のデータ線と、

複数の走査線と、

前記走査線と前記データ線との交差に対応して設けられた複数の画素と、

各走査線に対応する複数の信号供給線と、

前記各信号供給線の中から、対応する走査線がアクティブとなっているものを選択し、選択された信号供給線に基準信号を供給する信号供給手段と、を有し、

前記画素は、前記走査線と前記データ線との交差に対応して各々設けられ、前記走査線にゲート電極が接続され、前記データ線にソース電極が接続される第1トランジスタ素子と、前記走査線と前記データ線との交差に対応して各々設けられ、前記第1トランジスタ素子のドレイン電極がゲート電極に接続され、前記信号供給線にソース電極が接続され、前記画素電極にドレイン電極が接続される第2トランジスタ素子と、を有し、

前記走査線と前記データ線との交差に対応して各々設けられ、対応する走査線とデータ線とが同時にアクティブとなる期間では前記信号供給線から前記基準信号を取り込み、対応する走査線とデータ線とのうちいずれか一方が非アクティブとなる期間では、取り込んだ前記基準信号に基づく電圧を保持することを特徴とする電気光学装置。 - 前記信号供給手段は、

前記各信号供給線毎に設けられ、前記信号供給線の一端が一方の端子に接続され、対応する走査線の信号によってオン・オフが制御されるスイッチング素子と、

前記各スイッチング素子の他方の端子に各々接続されるともに前記基準信号が供給される共通信号線と

を備えることを特徴とする請求項2に記載の電気光学装置。 - 請求項2に記載の電気光学装置を駆動する電気光学装置の駆動回路であって、

前記基準信号を発生する基準信号発生手段と、

画像データを線順次データに変換する変換手段と、

前記線順次データのデータ値に基づいてパルス幅を変調したパルス幅変調信号を生成し前記データ線に出力するパルス幅変調手段と、

前記各走査線を順次アクティブとする各走査信号を生成し前記走査線に出力する走査線駆動手段と

を備えることを特徴とする電気光学装置の駆動回路。 - 請求項4に記載の電気光学装置を駆動する電気光学装置の駆動回路であって、

前記各走査信号のローレベル電位を、前記パルス幅変調信号のローレベル電位より前記第2トランジスタの閾値電圧だけ高電位に設定することを特徴とする電気光学装置の駆動回路。 - 前記パルス幅変調手段は、前記パルス幅変調信号のハイレベル電位が、前記基準信号の最大電位より少なくとも前記第2トランジスタ素子の閾値電圧だけは高くなるように前記パルス幅変調信号を生成し、

前記走査線駆動手段は、前記走査信号のハイレベル電位が、前記パルス幅変調信号のハイレベル電位より少なくとも前記第1トランジスタ素子の閾値電圧だけは高くなるように前記走査信号を生成する

ことを特徴とする請求項4に記載の電気光学装置の駆動回路。 - 前記基準信号は、ランプ波信号であることを特徴とする請求項4乃至6のいずれか1項に記載の電気光学装置の駆動回路。

- 請求項6に記載の駆動回路を、前記一方の基板に形成したことを特徴とする請求項2に記載の電気光学装置。

- 請求項8に記載の電気光学装置を備えたとことを特徴とする電子機器。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP37530499A JP3659103B2 (ja) | 1999-12-28 | 1999-12-28 | 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 |

| US09/742,184 US6781565B2 (en) | 1999-12-28 | 2000-12-22 | Electro-optical device, driving circuit and driving method of electro-optical device, and electronic apparatus |

| CNB001375172A CN1173322C (zh) | 1999-12-28 | 2000-12-27 | 电光装置、电光装置的驱动电路和驱动方法 |

| TW089128042A TW494378B (en) | 1999-12-28 | 2000-12-27 | Electro-optical device, driving circuit and driving method of electro-optical device, and electronic apparatus |

| KR10-2000-0082788A KR100417310B1 (ko) | 1999-12-28 | 2000-12-27 | 전기 광학 장치, 전기 광학 장치의 구동 회로 및 구동방법, 전자기기 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP37530499A JP3659103B2 (ja) | 1999-12-28 | 1999-12-28 | 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001188519A JP2001188519A (ja) | 2001-07-10 |

| JP3659103B2 true JP3659103B2 (ja) | 2005-06-15 |

Family

ID=18505301

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP37530499A Expired - Lifetime JP3659103B2 (ja) | 1999-12-28 | 1999-12-28 | 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6781565B2 (ja) |

| JP (1) | JP3659103B2 (ja) |

| KR (1) | KR100417310B1 (ja) |

| CN (1) | CN1173322C (ja) |

| TW (1) | TW494378B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7385579B2 (en) * | 2000-09-29 | 2008-06-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method of driving the same |

| DE60219325T2 (de) * | 2001-08-01 | 2008-01-03 | Koninklijke Philips Electronics N.V. | Verfahren und einrichtung zur gammakorrektur |

| TW523724B (en) * | 2001-08-09 | 2003-03-11 | Chi Mei Electronics Corp | Display panel with time domain multiplex driving circuit |

| KR100493385B1 (ko) * | 2002-12-17 | 2005-06-07 | 엘지.필립스 엘시디 주식회사 | 액정표시패널의 양 방향 구동 회로 |

| TWI405156B (zh) * | 2003-01-06 | 2013-08-11 | Semiconductor Energy Lab | 電路、顯示裝置及電子機器 |

| JP4074207B2 (ja) * | 2003-03-10 | 2008-04-09 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| JP2004317785A (ja) * | 2003-04-16 | 2004-11-11 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置および電子機器 |

| JP4154598B2 (ja) * | 2003-08-26 | 2008-09-24 | セイコーエプソン株式会社 | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 |

| JP2005091652A (ja) * | 2003-09-17 | 2005-04-07 | Hitachi Ltd | 表示装置 |

| US20050140634A1 (en) * | 2003-12-26 | 2005-06-30 | Nec Corporation | Liquid crystal display device, and method and circuit for driving liquid crystal display device |

| KR100997477B1 (ko) * | 2004-04-29 | 2010-11-30 | 삼성에스디아이 주식회사 | 가변의 계조 표현력을 가진 전계 방출 디스플레이 장치 |

| KR101022658B1 (ko) * | 2004-05-31 | 2011-03-22 | 삼성에스디아이 주식회사 | 신호 지연 저감형 전자 방출 장치 구동방법 |

| KR101133764B1 (ko) * | 2005-03-14 | 2012-04-09 | 삼성전자주식회사 | 박막 트랜지스터, 박막 트랜지스터 표시판 및 그 제조 방법 |

| US20070188419A1 (en) * | 2006-02-11 | 2007-08-16 | Samsung Electronics Co., Ltd. | Voltage transfer method and apparatus using organic thin film transistor and organic light emitting diode display device including the same |

| CN101324715B (zh) * | 2007-06-15 | 2011-04-20 | 群康科技(深圳)有限公司 | 液晶显示装置及其驱动方法 |

| JP2011095564A (ja) * | 2009-10-30 | 2011-05-12 | Seiko Epson Corp | 電気泳動表示装置とその駆動方法、及び電子機器 |

| JP5499638B2 (ja) * | 2009-10-30 | 2014-05-21 | セイコーエプソン株式会社 | 電気泳動表示装置とその駆動方法、及び電子機器 |

| JP2021117369A (ja) * | 2020-01-27 | 2021-08-10 | ソニーセミコンダクタソリューションズ株式会社 | 表示装置 |

| CN111540322B (zh) * | 2020-05-19 | 2021-12-03 | Tcl华星光电技术有限公司 | 显示屏的极性翻转控制方法及显示终端 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5266936A (en) * | 1989-05-09 | 1993-11-30 | Nec Corporation | Driving circuit for liquid crystal display |

| US5194974A (en) | 1989-08-21 | 1993-03-16 | Sharp Kabushiki Kaisha | Non-flicker liquid crystal display with capacitive charge storage |

| JPH0470897A (ja) | 1990-07-12 | 1992-03-05 | Nec Corp | 液晶表示パネルの駆動回路およびその駆動方法 |

| JP2674307B2 (ja) | 1990-11-13 | 1997-11-12 | 日本電気株式会社 | 液晶表示パネルの駆動方法 |

| JP3235121B2 (ja) * | 1991-07-31 | 2001-12-04 | 日本電気株式会社 | 液晶駆動回路 |

| JPH06314080A (ja) * | 1993-04-14 | 1994-11-08 | Internatl Business Mach Corp <Ibm> | 液晶表示装置 |

| JPH07225567A (ja) * | 1994-02-14 | 1995-08-22 | Oki Electric Ind Co Ltd | アクティブマトリクス型液晶表示装置の階調駆動回路及びその液晶表示装置 |

| JP3275991B2 (ja) * | 1994-07-27 | 2002-04-22 | シャープ株式会社 | アクティブマトリクス型表示装置及びその駆動方法 |

| US5587329A (en) | 1994-08-24 | 1996-12-24 | David Sarnoff Research Center, Inc. | Method for fabricating a switching transistor having a capacitive network proximate a drift region |

| US5959598A (en) * | 1995-07-20 | 1999-09-28 | The Regents Of The University Of Colorado | Pixel buffer circuits for implementing improved methods of displaying grey-scale or color images |

| JPH10153986A (ja) * | 1996-09-25 | 1998-06-09 | Toshiba Corp | 表示装置 |

| JP3832125B2 (ja) * | 1998-01-23 | 2006-10-11 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| US6426594B1 (en) * | 1998-02-23 | 2002-07-30 | Seiko Epson Corporation | Electro-optical device and method for driving the same |

| JP3644240B2 (ja) * | 1998-03-24 | 2005-04-27 | セイコーエプソン株式会社 | 電気光学装置用のデジタルドライバ回路及びこれを備えた電気光学装置 |

| US6278423B1 (en) * | 1998-11-24 | 2001-08-21 | Planar Systems, Inc | Active matrix electroluminescent grey scale display |

| JP3699850B2 (ja) * | 1999-01-29 | 2005-09-28 | シャープ株式会社 | 表示装置および液晶表示装置 |

| JP3564347B2 (ja) * | 1999-02-19 | 2004-09-08 | 株式会社東芝 | 表示装置の駆動回路及び液晶表示装置 |

| JP4562835B2 (ja) * | 1999-11-05 | 2010-10-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

-

1999

- 1999-12-28 JP JP37530499A patent/JP3659103B2/ja not_active Expired - Lifetime

-

2000

- 2000-12-22 US US09/742,184 patent/US6781565B2/en not_active Expired - Lifetime

- 2000-12-27 KR KR10-2000-0082788A patent/KR100417310B1/ko not_active Expired - Lifetime

- 2000-12-27 CN CNB001375172A patent/CN1173322C/zh not_active Expired - Lifetime

- 2000-12-27 TW TW089128042A patent/TW494378B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| CN1302054A (zh) | 2001-07-04 |

| KR100417310B1 (ko) | 2004-02-05 |

| TW494378B (en) | 2002-07-11 |

| US20010017610A1 (en) | 2001-08-30 |

| JP2001188519A (ja) | 2001-07-10 |

| KR20010070359A (ko) | 2001-07-25 |

| CN1173322C (zh) | 2004-10-27 |

| US6781565B2 (en) | 2004-08-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6778163B2 (en) | Liquid crystal display device, driving circuit, driving method, and electronic apparatus | |

| JP4123711B2 (ja) | 電気光学パネルの駆動方法、電気光学装置、および電子機器 | |

| JP3659103B2 (ja) | 電気光学装置、電気光学装置の駆動回路および駆動方法、電子機器 | |

| JP3835113B2 (ja) | 電気光学パネルのデータ線駆動回路、その制御方法、電気光学装置、および電子機器 | |

| JP3832240B2 (ja) | 液晶表示装置の駆動方法 | |

| JP3498570B2 (ja) | 電気光学装置の駆動回路及び駆動方法並びに電子機器 | |

| JP2000310963A (ja) | 電気光学装置の駆動回路及び電気光学装置並びに電子機器 | |

| JP4196999B2 (ja) | 液晶表示装置の駆動回路、液晶表示装置、液晶表示装置の駆動方法、および電子機器 | |

| JP3767315B2 (ja) | 電気光学パネルの駆動方法、そのデータ線駆動回路、電気光学装置、及び電子機器 | |

| JP4093232B2 (ja) | 電気光学装置、電気光学装置の駆動回路、電気光学装置の駆動方法および電子機器 | |

| JP3661523B2 (ja) | 電気光学装置の駆動方法、駆動回路および電気光学装置ならびに電子機器 | |

| JP2002149133A (ja) | 電気光学装置の駆動回路及び駆動方法 | |

| JP4179396B2 (ja) | 電気光学装置、および電子機器 | |

| CN100401366C (zh) | 电光装置的驱动电路及驱动方法,电光装置和电子设备 | |

| JP4419394B2 (ja) | 電気光学パネルの駆動方法及び駆動回路、これを用いた電気光学パネル、並びに電子機器 | |

| JP3659079B2 (ja) | 電気光学パネルの駆動回路、電気光学パネル及び電子機器 | |

| JP2000310964A (ja) | 電気光学装置の駆動回路及び電気光学装置並びに電子機器 | |

| JP3677969B2 (ja) | 液晶表示パネルの駆動装置、液晶表示装置及び電子機器 | |

| JP3837998B2 (ja) | レベル変換回路、データ線駆動回路、電気光学装置および電子機器 | |

| JP2004233807A (ja) | 液晶装置及びその駆動方法並びに電子機器 | |

| JP4111212B2 (ja) | 駆動回路、電気光学装置、および電子機器 | |

| JP4017000B2 (ja) | 電気光学装置、および電子機器 | |

| JP2007310422A (ja) | 液晶表示装置の駆動回路 | |

| JP2007122082A (ja) | 液晶表示装置の駆動回路及び駆動方法 | |

| JP2005326750A (ja) | 電気光学パネルの駆動回路及び方法、電気光学装置並びに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041005 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041012 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050222 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050307 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3659103 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080325 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090325 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090325 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100325 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100325 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110325 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120325 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120325 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130325 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140325 Year of fee payment: 9 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |