JP4701589B2 - 液晶装置と投射型表示装置 - Google Patents

液晶装置と投射型表示装置 Download PDFInfo

- Publication number

- JP4701589B2 JP4701589B2 JP2003198659A JP2003198659A JP4701589B2 JP 4701589 B2 JP4701589 B2 JP 4701589B2 JP 2003198659 A JP2003198659 A JP 2003198659A JP 2003198659 A JP2003198659 A JP 2003198659A JP 4701589 B2 JP4701589 B2 JP 4701589B2

- Authority

- JP

- Japan

- Prior art keywords

- scanning

- image signal

- liquid crystal

- lines

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/04—Partial updating of the display screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0209—Crosstalk reduction, i.e. to reduce direct or indirect influences of signals directed to a certain pixel of the displayed image on other pixels of said image, inclusive of influences affecting pixels in different frames or fields or sub-images which constitute a same image, e.g. left and right images of a stereoscopic display

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/02—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the way in which colour is displayed

Description

【発明の属する技術分野】

本発明は、液晶装置とその駆動方法ならびに投射型表示装置に関し、特に投射型表示装置に搭載される液晶ライトバルブに用いて好適な液晶装置とその駆動方法の構成に関するものである。

【0002】

【従来の技術】

液晶プロジェクタ等の投射型表示装置に搭載される光変調手段として、液晶ライトバルブが知られている。液晶ライトバルブは、液晶層を挟持して対向配置され、液晶層に電圧を印加するための電極を具備する一対の基板を主体として構成されている。通常、液晶ライトバルブにはアクティブマトリクス型の液晶セルが用いられており、画像の高精細化が進められている。

【0003】

液晶ライトバルブの駆動方式には、液晶の焼付きや劣化を防ぐため、ドット反転、ライン反転、面反転等の反転駆動方式が従来から採用されている。上記の各反転駆動方式には一長一短があるが、ドット反転やライン反転の場合、クロストークが抑制できる利点がある反面、隣接する画素電極に逆極性の電位が書き込まれるため、隣接画素間で横電界が発生し、この横電界によるディスクリネーションに起因して光抜けが生じる恐れがある。上述したように、液晶ライトバルブでは高精細化が求められる事情から、この光抜けは、コントラスト低下や開口率低下を引き起こし、表示品位を低下させる大きな要因となる。そこで、この観点から、横電界の発生のない面反転駆動方式の採用が求められている。

【0004】

ところが、面反転駆動方式には別の問題点があった。

すなわち、面反転駆動においては、1本のデータ線に着目した場合、当該データ線から信号が供給される全ての画素に対して、反転周期を1フィールドとすると、所定の1フィールドで同極性の画像信号(電位)が書き込まれる。そして、次のフィールドに移った瞬間、当該データ線に供給される画像信号の極性が反転する。このとき、表示領域の上側から下側へ走査線を走査する場合、表示領域の上側の画素では、画像信号が書き込まれた後、保持期間のほとんどの時間で、当該データ線に印加される画像信号の極性が画素の電位と同極性であるのに対し、下側の画素では、画像信号が書き込まれた後、保持期間のほとんどの時間で、データ線には画素とは逆極性の画像信号が印加される状態となる。このように、表示領域の上側と下側で、データ線の電位が画素電極に与える影響に違いが生じ、そのため画面上の場所によって表示が不均一になるという問題があった。

【0005】

そこで、クロストークを抑制でき、画面の均一性を確保する手段として、1水平期間内を第1期間と第2期間とに分割し、第1期間において走査線に駆動パルスを供給するとともにデータ線に画像信号を供給することによって各画素電極に画像信号を印加する一方、第2期間においては走査線に駆動パルスを供給せずにデータ線に前とは逆極性の画像信号を供給する技術が提案されている(例えば、特許文献1)。

【0006】

【特許文献1】

特開平5−313608号公報

【0007】

【発明が解決しようとする課題】

しかしながら、上記の特許文献1に記載された技術では、画素の書き込みに用いることのできる時間が通常の半分になり、書き込みが不充分になる等の問題が生じる。

本発明は、上記の課題を解決するためになされたものであって、クロストークを抑制できるとともに画面内の表示品位の均一性を確保でき、さらに書き込み不足等の問題が生じることのない液晶装置とその駆動方法を提供することを目的とする。

【0008】

【課題を解決するための手段】

上記の目的を達成するために、本発明の液晶装置は、互いに交差する複数のデータ線および複数の走査線と、前記データ線および前記走査線の交差に対応して設けられた画素と、所定期間毎に所定電位に対する電位の極性が反転する画像信号を前記複数のデータ線の各々に供給するとともに、各々が異なるタイミングで立ち上がる複数のパルス信号に基づいて、1水平期間毎に前記複数の走査線のうち所定本数の走査線を飛び越しつつ、前記複数の走査線の各々を選択する駆動回路部とを有し、任意の1水平期間において、前記画像信号のうちの正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接するとともに、負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接するように、前記駆動回路部により駆動が行われることを特徴とする。

【0009】

本発明の液晶装置における駆動回路部は、データ線側については、単位期間毎に極性が反転する画像信号を出力するものであり、例えば前記単位期間を1水平期間とすると、極性反転については従来のライン反転駆動と同様の動作を行うものである。一方、走査線側については、画面の上側から下側へ向けて線順次走査を行うのではなく、一部(複数本)の走査線を飛び越しつつ、行ったり来たりしながら全ての走査線にわたって走査を行うものである。このような駆動回路部の動作に基づいて、画像信号のうちの正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号、あるいは負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号のいずれかが各走査線毎に供給される。

【0010】

このとき、任意の1垂直期間に着目すると、正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接し、負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接しているので、これら隣接した複数の走査線に対応する領域内には、正極性電位が書き込まれた画素、負極性電位が書き込まれた画素のいずれか一方しか存在しないことになる。よって、画面内のある程度の広さを持った正電位印加領域と負電位印加領域とが形成され、これらが所定の周期で反転することになり、特定の領域については面反転駆動を行った場合と同じく、隣接画素間で同極性にすることができる。

【0011】

しかしながら、本発明の場合、結果的に特定の領域について面反転駆動が行われながらも、データ線側についてはあくまでも従来のライン反転駆動と同様の動作を行っているので、データ線側を面反転方式で駆動したときのように画面の上側の画素と下側の画素で画素電極−データ線間の時間的な電位の関係に大きな差異が生じることがなく、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる。また、[発明が解決しようとする課題]の項で記載した「1水平期間を第1期間と第2期間とに分割し、第2期間においては走査線に駆動パルスを供給せずにデータ線に前とは逆極性の画像信号を供給する」従来の技術と異なり、1水平期間の大部分を画素への書き込みに費やすので、書き込みが不充分になる等の問題が生じることもない。

【0012】

また、本発明の液晶装置は、互いに交差する複数のデータ線および複数の走査線と、前記データ線および前記走査線の交差に対応して設けられた画素と、所定期間毎に所定電位に対する電位の極性が反転する画像信号を前記複数のデータ線の各々に供給するとともに、各々が異なるタイミングで立ち上がる複数のパルス信号に基づいて、1水平期間毎に前記複数の走査線のうち所定本数の走査線を飛び越しつつ、前記複数の走査線の各々を選択する駆動回路部とを有し、1垂直期間において、前記所定電位に対して正極性の電位の画像信号が各前記データ線に印加される時間と、前記所定電位に対して負極性の電位の画像信号が各前記データ線に印加される時間とが略等しいことを特徴とする。

この構成によれば、データ線をほぼ完全に交流化することが可能となり、またデータ線に接続されている、正極性に書き込まれた画素と、負極性に書き込まれた画素の数をほぼ同数にすることができるので、画面内におけるデータ線と画素電極の関係をより均一化することができる、という効果が得られる。

【0013】

また、1垂直期間において、隣接する2本の走査線に対応する2つの画素群が、1垂直期間の50%以上の時間、同極性の電位が書き込まれた状態にあることが望ましい。

本発明の場合、従来の一般的な面反転駆動とは異なり、任意の1垂直期間で見たときに、1つの画面内に正電位印加領域と負電位印加領域とからなる複数の領域が存在することになる。よって、各領域内では隣接する画素に同極性の電位が印加されているが、各領域間の境界では隣接する画素に逆極性の電位が印加されることになる。ここで、各領域は単位期間毎に1走査線ずつ画面上を移動していくので、1つの画素に着目すると、1垂直期間内において隣接する画素に同極性の電位が書き込まれている時間と逆極性の電位が書き込まれている時間が存在する。ここで、同極性の電位が書き込まれている時間が1垂直期間の50%以上であれば、隣接画素が逆極性であるときに発生する横電界による光漏れを軽減することができる、という効果が得られる。

【0014】

なお、本明細書で言う「正電位印加領域」、「負電位印加領域」等の「領域」とは、画面上での絶対的な場所を示す意味で用いているのではなく、ある微小時間内において印加電位の極性が同一の状態にある範囲を示す意味で用いている語句である。したがって、この「領域」は、時間を経ることにより画面上を移動する。

【0015】

また、前記画像信号の前記所定電位に対する極性が反転する単位期間が、1水平期間であることが望ましい。

本発明において、「前記画像信号の極性が反転する単位期間」は、1水平期間に限らず、例えば2水平期間、4水平期間など、複数の水平期間単位であっても本発明の作用、効果を得ることができる。しかしながら、1水平期間とした場合、全ての走査線を同じ状態にすることができる、という効果が得られる。逆に、1水平期間以外の場合は、その期間の最初に選択される走査線と最後に選択される走査線では、データ線と画素電極の関係に多少の差異が生じてしまう。

【0016】

本発明の液晶装置における具体的な走査の順序としては、例えば前記複数の走査線の数を2m本としたときに、駆動回路部が、所定の走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給した後、所定の走査線からm本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、以降上記の動作を繰り返し、2水平期間毎に隣接する走査線に対応する画素群に同極性の電位を書き込むように動作すればよい。

【0017】

もしくは、前記複数の走査線の数を4m本としたときに、駆動回路部が、所定の走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線からm本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線から2m本分離れた走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線から3m本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、以降上記の動作を繰り返し、4水平期間毎に隣接する走査線に対応する画素群に同極性の電位を書き込むように動作すればよい。

【0018】

前者の方法は、1画面内を1つの正電位印加領域と1つの負電位印加領域の2つの領域に分割する例であり、後者の方法は、1画面内を2つの正電位印加領域と2つの負電位印加領域の4つの領域に分割する例である。

分割数を少なくした場合(2分割の場合)には、1垂直期間で隣接画素が同極性となっている時間を最大とすることができる。一方、分割数を多くした場合(4分割の場合)には、表示画像によるデータ線電位の偏りをより均一にすることが可能となり、クロストークをさらに目立たなくすることができるようになる。

【0019】

また、画像信号を一旦蓄えた後、前記走査線の走査順序に従って画素へ書き込む画像信号が読み出されるフレームメモリが備えられていることが望ましい。

この構成によれば、フレームメモリによって画像データが一旦蓄えられた後、走査線の走査順序に従って画素へ書き込む画像データが読み出され、データ線に供給される。

【0020】

また、本発明の液晶装置は、マトリクス状に配列して設けられた複数の画素と、前記複数の画素に画像信号を供給する駆動回路部とを備え、上記駆動回路部は、画像信号と当該画像信号を遅延させた画像信号とを、1水平期間毎に交互に供給し、1垂直走査期間毎に前記画像信号の所定電位に対する極性を反転させることを特徴とする。

【0021】

例えば1つのフィールドデータを偶数(2m)個のフィールドデータとして書き込む場合について考える。この場合、駆動回路部では、あるフィールドの書き込みが始まると、これから例えば映像信号における1/2m垂直期間だけずれたタイミングで次フィールドの書き込みが開始される。そして、これらのフィールドでは、あるフィールドの1ラインが書き込まれた後、このラインから一部(複数本)の走査線を飛び越した位置に存在する次フィールドのラインにデータが書き込まれるようにして描画が行なわれる。この際、データ線に出力されるデータの極性を1水平期間毎に反転させることで1フィールド内のデータの極性を等しくし且つ連続するフィールドの間でデータの極性を異ならせることができる。

【0022】

このように本液晶装置では、走査線側については、複数本の走査線を飛び越しつつ、行ったり来たりしながら全ての走査線にわたって走査が行なわれる。そして、任意の1垂直期間で見たときに、画面内には各フィールドに対応して正電位印加領域と負電位印加領域とからなる複数の領域が存在することとなる。すなわち、本構成は前述の液晶装置の構成を巨視的な観点から表現したものであり、よって、前述したのと同様の効果がえられる。つまり、各領域内では擬似的に面反転駆動が行なわれながらも、データ線側についてはあくまでも従来のライン反転駆動と略同様の動作が行なわれるため、データ線側を面反転駆動したときのように画面の上側の画素と下側の画素とで画素電極−データ線間の時間的な電位の関係に大きな差異が生じることがなく、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる。

【0023】

また、[発明が解決しようとする課題]の項で記載した「1水平期間を第1期間と第2期間とに分割し、第2期間においては走査線に駆動パルスを供給せずにデータ線に前とは逆極性の画像信号を供給する」従来の技術と異なり、1水平期間の大部分を画素への書き込みに費やすので、書き込みが不充分になる等の問題が生じることもない。

またこのように駆動する事により、走査線を映像信号に同期したタイミングで移動させながら、2つの走査線を、入力される映像信号に対して半分の時間に設定される書き込みに水平期間のそれぞれに交互に割り当てることによって、書き込み走査の周波数を、映像信号の倍にすることができる。

【0024】

また、本発明の液晶装置は、マトリクス状に配列して設けられた複数の画素と、上記画素に画像信号を供給する駆動回路部と、前記画像信号を記憶するメモリが備えられ、上記駆動回路部は、1垂直走査期間分の画像信号をもとに、第1,第2の2つの1垂直走査期間分の画像信号を生成する際に、外部から入力された画像信号を第1の1垂直走査期間分の画像信号とし、前記外部から入力された画像信号を上記メモリに記憶させて上記外部から入力された画像信号に対して遅延させて第2の1垂直走査期間分の画像信号とし、前記第1,第2の1垂直走査期間分の画像信号を1水平期間毎に交互に出力するとともに、前記第2の1垂直走査期間分の画像信号の所定電位に対する電位の極性と前記第1の1垂直走査期間分の画像信号の電位の所定電位に対する極性とが逆極性になるようにすることを特徴とする。このような構成とすることで、メモリ容量を少なくし、部材コストを低減することができる。

【0025】

例えば第2のフィールドデータの書き込み開始時期を第1のフィールドデータに対して映像信号における1/2垂直期間だけ遅延させる場合について考える。この例では、外部から入力された画像信号により画面の上半分の画像がデータ線に出力される間、この上半分の画像データはメモリにも出力され、ここで記憶される。そして、画像信号により画面の下半分の画像がデータ線に出力される間、メモリからは映像信号における1/2垂直期間前の画像データ(即ち、画面の上半分の画像データ)がデータ線に出力される。この外部及びメモリからのデータはデータ線に対して1水平期間毎に交互に出力される。

【0026】

一方、走査線側では、画面の上段側と下段側の走査線が1水平期間毎に交互に選択されるため、画面には上段側と下段側との間で画像が交互に書き込まれる。つまり、この構成では、外部からの画像信号によって1ライン毎に画像が書き込まれる間に、メモリから読み出された画像データによっても画像が書き込まれるため、画像は実質的に倍速で(外部から入力される画像信号の2倍の周波数で)書き込まれることとなる。通常、倍速駆動を行なう場合には2フィールド分のメモリが必要になるが、本構成では、外部からの画像信号をそのままデータ線に出力することで画面の半分が書き込まれるため、メモリ容量は表示画面全体の半分の容量だけあればよい。このため、通常のものに比べてメモリ容量が1/4で済み、部材コストを大幅に低減することができる。また、本構成では画素に対して倍速書き込みが行なわれるので、フリッカが抑制される。

【0027】

また、前述の液晶装置を構成面から見た場合には、本液晶装置は以下のように特徴付けられる。すなわち、本発明の液晶装置は、互いに交差する複数のデータ線及び複数(m本)の走査線と、前記データ線及び走査線の交差に対応して設けられた画素と、これらの画素からなる画像表示領域を備えた液晶装置において、前記画像表示領域は、複数の走査線からなり所定電位に対して正極性の画像信号が供給される表示領域と、複数の走査線からなり前記所定電位に対して負極性の画像信号が供給される表示領域とを、それぞれ1乃至複数を含むn個の表示領域からなり、前記n個の表示領域の走査線に走査信号を供給する走査ドライバと、前記n個の表示領域のデータ線に画像信号を供給するデータドライバとを備え、前記走査ドライバには、画像信号における1垂直期間内にn個のゲート出力パルスがそれぞれ異なるタイミングで入力され、前記n個のゲート出力パルスがそれぞれクロック信号に同期して前記走査ドライバにおいてシフトされるとともに、各走査線には、順次にパルスが立ち上がるn個のイネーブル信号のいずれかが割り当てられ、前記走査ドライバは、各走査線に、前記n個のゲート出力パルスのそれぞれと、前記走査線ごとに割り当てられたイネーブル信号とに基づき前記走査信号を論理合成して出力する論理合成回路を備え、前記走査ドライバは、前記n個のゲート出力パルスとn個のイネーブル信号に基づくm個の走査信号を、m本の走査線にそれぞれ出力し、前記データドライバは、前記m本の走査線がそれぞれ属する表示領域に対応した極性の画像信号を、前記走査信号が出力される順番で前記データ線に出力することを特徴とする。なお、nは2以上の整数を表わしている。

【0028】

この構成では、映像信号における1垂直期間内においてn個のゲート出力パルスが画像表示領域内の別々の走査線位置に立ち上がり、それぞれがクロック信号に同期して画像表示領域の上段側から下段側に向けてシフトしていく。そして、走査信号は、これらのゲート出力パルスの立ち上がる走査線の内、イネーブル信号により選択されたものに対して出力される。これにより、走査線を一部(複数本)飛び越した形で走査を行なうことが可能となる。

【0029】

また、前記n個のゲート出力パルスは、互いに前記画像信号の1/2垂直期間だけずれたタイミングで上記走査ドライバに入力される2つのパルスであり、前記n個のイネーブル信号は、交互にパルスが立ち上がる第1,第2のイネーブル信号であり、上記走査ドライバでは同時にパルスが立ち上がる前記2つのゲート出力パルスのそれぞれと、交互にパルスが立ち上がる第1,第2のイネーブル信号のそれぞれと、に基づいて、2つの走査信号が順次出力され、前記2つの走査信号はそれぞれ、画像信号における1/2垂直期間に対応する分だけずれた位置にある各走査線に出力され、前記複数の走査線を配列方向において第1及び第2の2つの領域に分けたときに、前記第1のイネーブル信号は前記第1の領域に配置された複数の走査線に割り当てられ、前記第2のイネーブル信号は前記第2の領域に配置された複数の走査線に割り当てられることが望ましい。

【0030】

この構成では、同時に2つのゲート出力パルスが映像信号における1/2画面分ずれた位置に立ち上がり、それぞれがクロック信号に同期して画像表示領域の上段側から下段側に向けてシフトしていく。そして、走査信号は、これらのゲート出力パルスの立ち上がる走査線の内、イネーブル信号により選択されたものに対して出力される。この際、第1のイネーブル信号は第1の表示領域、第2のイネーブル信号は第2の表示領域にそれぞれ割り当てられているため、走査線は画像表示領域の上段側のものと下段側のものとが交番的に選択されることとなる。これにより、1/2画面分の走査線を飛び越しつつ、画像表示領域の上段側と下段側とを行ったり来たりしながら全ての走査線にわたって走査を行なうことができる。

【0031】

また、前記n個のゲート出力パルスは、前記画像信号の1/4垂直期間だけずれたタイミングで前記走査ドライバに入力される4つのパルスであり、前記n個のイネーブル信号は、順次パルスが立ち上がる第1〜第4の4つのイネーブル信号であり、上記走査線ドライバでは同時にパルスが立ち上がる4つのゲート出力パルスと、順次パルスが立ち上がる第1〜第4の4つのイネーブル信号のいずれかとに基づいて4つの走査信号が順次出力され、前記4つの走査信号はそれぞれ、画像信号における1/4垂直期間に対応する分ずつ、ずれた位置にある各走査線に出力され、前記複数の走査線を配列方向に沿って第1から第4の4つの領域に分けたときに、前記第1から第4のイネーブル信号はそれぞれ前記第1から第4の領域のいずれかに配置された複数の走査線に割り当てられることが望ましい。

【0032】

この構成では、同時に4つのゲート出力パルスが映像信号における1/4画面分ずれた位置に立ち上がり、それぞれがクロック信号に同期して画像表示領域の上段側から下段側に向けてシフトしていく。そして、走査信号は、これらのゲート出力パルスの立ち上がる走査線の内、イネーブル信号により選択されたものに対して出力される。この際、第1のイネーブル信号は第1の表示領域、第2のイネーブル信号は第2の表示領域、第3のイネーブル信号は第3の表示領域、第4のイネーブル信号は第4の表示領域にそれぞれ割り当てられているため、走査線は第1,第2,第3,第4の表示領域内のものが交番的に選択されることとなる。これにより、1/4画面分の走査線を飛び越しつつ、各表示領域を行ったり来たりしながら全ての走査線にわたって走査を行なうことができる。

【0033】

また、前記n個のゲート出力パルスは、前記画像信号の1/2垂直期間だけずれたタイミングで前記走査ドライバに入力される2つのパルスであり、前記n個のイネーブル信号は、交互にパルスが立ち上がる第1,第2のイネーブル信号であり、上記走査ドライバでは同時にパルスが立ち上がる前記2つのゲート出力パルスのそれぞれと、交互にパルスが立ち上がる第1,第2のイネーブル信号のそれぞれとに基づいて、2つの走査信号が順次出力され、前記2つの走査信号はそれぞれ、画像信号における1/2垂直期間に対応する分だけずれた位置にある各走査線に出力され、前記第1のイネーブル信号は前記複数の走査線のうち奇数番目の走査線に割り当てられ、前記第2のイネーブル信号は前記複数の走査線のうち偶数番目の走査線に割り当てられることが望ましい。

この構成では、映像信号における1垂直期間内において2つのゲート出力パルスが1/2画面分ずれた位置に立ち上がり、それぞれがクロック信号に同期して画像表示領域の上段側から下段側に向けてシフトしていく。

【0034】

例えば、2つのゲート出力パルスは最上部側からk本目と、s+k本目(sは奇数)の走査線位置に立ち上がることができる。このとき、走査信号は、これらのゲート出力パルスの立ち上がる走査線の内、イネーブル信号により選択されたものに対して出力される。この際、第1のイネーブル信号は画像表示領域の最上部側から奇数本目、第2のイネーブル信号は偶数本目の走査線に割り当てられているため、第1,第2のイネーブル信号を、走査線ドライバのシフトクロックと位相をずらしながら、例えば第1,第1,第2,第2,第1,第1,・・・の順序で立ち上げることで、画像表示領域の最上部側から1本目,s+1本目,2本目,s+2本目,3本目,s+3本目,・・・の順序で、画面の上段側,下段側の走査線が交互に選択されることとなる。

【0035】

また、これらの構成では、前記画像信号を記憶するメモリが備えられ、外部から入力された画像信号は上記データドライバに供給される一方、上記メモリに記憶され、上記データドライバは、外部から入力された画像信号と、上記メモリから読み出された画像信号とを1水平期間毎に交互に前記データ線に供給し、上記メモリから読み出された画像信号の所定電位に対する極性と、上記外部から供給された画像信号の所定電位に対する極性とは互いに逆の極性であることが好ましい。このような構成とすることで、メモリ容量を少なくし、部材コストを低減することができる。

【0036】

つまり、この構成では、外部からの画像信号によって1ライン毎に画像が書き込まれる間に、メモリから読み出された画像データによっても画像が書き込まれるため、画像は実質的に倍速で(外部から入力される画像信号の2倍の周波数で)書き込まれることとなる。通常、倍速駆動を行なう場合には2画面分(2フィールド分)のメモリが必要となるが、本構成では、外部から入力された画像信号をそのままデータ線に出力することで画面の半分が書き込まれるため、メモリ容量は表示画面全体の半分の容量だけあればよい。このため、通常のものに比べてメモリ容量が1/4で済み、部材コストを大幅に低減することができる。また、本構成では画素に対して倍速書き込みが行なわれるので、フリッカが抑制される。

【0037】

本発明の液晶装置の駆動方法は、互いに交差する複数のデータ線および複数の走査線と、前記データ線および前記走査線の交差に対応して設けられた画素とを有する液晶装置の駆動方法であって、所定期間毎に所定電位に対する極性が反転する画像信号を前記複数のデータ線の各々に供給するとともに、各々が異なるタイミングで立ち上がる複数のパルス信号に基づいて、1水平期間毎に、前記複数の走査線のうち所定本数の走査線を飛び越しつつ前記複数の走査線の各々を選択し、任意の1水平期間において、前記画像信号の前記所定電位に対する正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接し、前記所定電位に対する負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接するように駆動を行うことを特徴とする。

【0038】

本発明の液晶装置の駆動方法によれば、上記本発明の液晶装置と同様の作用、効果が得られる。

すなわち、任意の1水平期間毎に、正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接し、負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号が供給される複数の走査線が互いに隣接しているので、画面内のある程度の広さを持った正電位印加領域と負電位印加領域とが所定の周期で反転し、それぞれの領域としては面反転駆動が行われる。本発明の場合、結果的に領域毎には面反転駆動が行われながらも、データ線側については従来のライン反転駆動と同様の動作を行っているので、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる。また、1水平期間の大部分を画素への書き込みに費やすので、書き込みが不充分になる等の問題が生じることもない。

【0039】

また、1垂直期間において、前記所定電位に対して正極性の電位の画像信号が各前記データ線に印加される時間と、前記所定電位に対して負極性の電位の画像信号が各前記データ線に印加される時間とが等しいことが望ましい。また、1垂直期間において、隣接する2本の走査線に対応する2つの画素群に対して、1垂直期間の50%以上の時間、同極性の電位を書き込むことが望ましい。また、画像信号の所定電位に対する極性が反転する単位期間を1水平期間とすることが望ましい。

【0040】

具体的な走査の順序として、例えば前記複数の走査線の数を2m本としたときに、所定の走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給した後、所定の走査線からm本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、以降上記の動作を繰り返し、2水平期間毎に隣接する走査線に対応する画素群に同極性の電位を書き込むことができる。

【0041】

あるいは、前記複数の走査線の数を4m本としたときに、所定の走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線からm本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線から2m本分離れた走査線に対して正極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、所定の走査線から3m本分離れた走査線に対して負極性電位の印加期間に対応するタイミングで立ち上がるパルス信号を供給し、以降上記の動作を繰り返し、4水平期間毎に隣接する走査線に対応する画素群に同極性の電位を書き込むことができる。

【0042】

また、書き込み走査周波数を100Hz以上の周波数にすることが望ましい。

これにより、画素への書き込み極性差に起因するフリッカを目立たなくすることが可能となる。

【0043】

また、本発明の液晶装置の駆動方法は、画像信号が供給される複数の画素がマトリクス状に配列された液晶装置の駆動方法であって、画像信号と画像信号を遅延させた画像信号とを、1水平期間毎に交互に供給するとともに、1垂直走査期間毎に前記画像信号の所定電位に対する極性を反転させることを特徴とする。

【0044】

このような駆動方法では、データ線については従来と略同様のライン反転駆動を行なうことでクロストークを抑制しつつ、一方では、画面内にある程度の広さを持った正電位印加領域と負電位印加領域とを形成することで、画面の場所による表示の不均一を回避することができる。また、1水平期間の大部分を画素の書き込みに費やすので、書き込みが不十分になる等の問題が生じることもない。

【0045】

また、このような液晶装置に、メモリを設け、外部から入力された画像信号とメモリから読み出された画像データとを用いて駆動を行なうようにしてもよい。

すなわち、本発明の液晶装置の駆動方法は、画像表示領域にマトリクス状に配列され、画像信号が供給される複数の画素と、メモリとを備えた液晶装置の駆動方法であって、1垂直走査期間分の画像信号をもとに第1,第2の1垂直走査期間分の画像信号を生成する際に、外部から入力された画像信号を第1の1垂直走査期間分の画像信号とし、前記外部から供給された画像信号を上記メモリに記憶させて上記外部から供給された画像信号に対して遅延させて第2の1垂直走査期間分の画像信号とし、前記第1,第2の1垂直走査期間分の画像信号を1水平期間毎に交互に出力して前記画素に供給し、前記第2の1垂直走査期間分の画像信号の所定電位に対する極性と前記第1の1垂直走査期間分の画像信号の所定電位に対する極性とを逆極性にすることを特徴とする。

【0046】

この駆動方法によってもクロストークを抑制しつつ、画面の場所による表示の不均一を回避できる。また、本駆動方法では、1つのフレームデータを複数のフィールドデータに分けたことで、実質的に倍速以上で駆動されることとなるため、フリッカを抑制することができる。通常、倍速等の駆動を行なう場合には、2フィールド分のメモリ容量が必要となるが、本方法では、外部からの画像信号をそのままデータ線に出力することで画面の一部が書き込まれるため、必要となるメモリ容量は1フィールド分よりも少なくて済む。例えば、1つのフレームデータを2つのフィールドデータに分けた場合には、駆動は倍速で行なわれ、メモリは1/2フィールド分あればよい。このため、部材コストが大幅に低減され、コスト的に有利となる。

【0047】

本発明の投射型表示装置は、照明装置と、前記照明装置から射出される光を変調する光変調装置と、前記光変調装置により変調された光を投射する投射装置とを有する投射型表示装置であって、前記光変調装置として、上記本発明の液晶装置を備えたことを特徴とする。また、画像信号を一旦蓄えた後、前記走査線の走査順序に従って画素へ書き込む画像信号が読み出されるフレームメモリが備えられることが好ましい。

この構成によれば、上記本発明の液晶装置を備えたことで表示品位に優れた投射型表示装置を実現することができる。

【0048】

【発明の実施の形態】

[第1の実施の形態]

以下、本発明の第1の実施の形態を図1〜図10を参照して説明する。

本実施の形態では、投射型表示装置の光変調装置として用いる液晶ライトバルブ(液晶装置)の例を挙げて説明する。

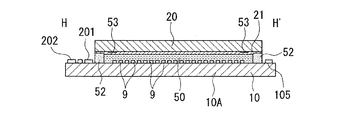

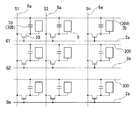

図1は本実施の形態の液晶ライトバルブの概略構成図、図2は図1のH−H’線に沿う断面図、図3は液晶ライトバルブを構成するマトリクス状に形成された複数の画素の等価回路図、図4は駆動回路部を含むブロック図、図5は駆動回路部内の走査ドライバの構成を示す回路図、図6は図5中の要部の詳細回路図、図7は液晶ライトバルブの動作を説明するためのタイミングチャート、図8は図7中の要部を取りだして示すタイミングチャート、図9は画面のイメージを示す図、図10は画面の動きを説明するための図である。なお、各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

【0049】

(液晶ライトバルブの全体構成)

本実施の形態の液晶ライトバルブ1の構成は、図1および図2に示すように、TFTアレイ基板10上に、シール材52が対向基板20の縁に沿うように設けられており、その内側に並行して額縁としての遮光膜53(周辺見切り)が設けられている。シール材52の外側の領域には、データドライバ(データ線駆動回路)201および外部回路接続端子202がTFTアレイ基板10の一辺に沿って設けられており、走査ドライバ(走査線駆動回路)104がこの一辺に隣接する2辺に沿って設けられている。

【0050】

さらに、TFTアレイ基板10の残る一辺には、画像表示領域の両側に設けられた走査ドライバ104間を接続するための複数の配線105が設けられている。また、対向基板20のコーナー部の少なくとも1箇所においては、TFTアレイ基板10と対向基板20との間で電気的導通をとるための上下導通材106が設けられている。そして、図2に示すように、図1に示したシール材52とほぼ同じ輪郭を持つ対向基板20がシール材52によりTFTアレイ基板10に固着されており、TFTアレイ基板10と対向基板20との間にTN液晶等からなる液晶層50が封入されている。また、図1に示すシール材52に設けられた開口部52aは液晶注入口であり、封止材25によって封止されている。

【0051】

図3において、本実施の形態における液晶ライトバルブ1の画像表示領域を構成するマトリクス状に形成された複数の画素には夫々、画素電極9と当該画素電極9をスイッチング制御するためのTFT30とが形成されており、画像信号が供給されるデータ線6aがTFT30のソース領域に電気的に接続されている。本実施の形態の液晶ライトバルブ1は、n本のデータ線6aと2m本の走査線3aとを有している(n,mはともに自然数)。データ線6aに書き込む画像信号S1、S2、…、Snは、この順に線順次に供給しても構わないし、相隣接する複数のデータ線6a同士に対して、グループ毎に供給するようにしても良い。

【0052】

また、TFT30のゲートには走査線3aが電気的に接続されており、所定のタイミングで各走査線3aにパルス的に走査信号G1、G2、…、G2mを後述するように飛び越しつつ印加するように構成されている。画素電極9は、TFT30のドレインに電気的に接続されており、スイッチング素子であるTFT30を一定期間だけオン状態とすることにより、データ線6aから供給される画像信号S1、S2、…、Snを所定のタイミングで書き込む。画素電極9を介して液晶に書き込まれた所定レベルの画像信号S1、S2、…、Snは、対向基板20に形成された共通電極との間で一定期間保持される。ここで、保持された画像信号がリークするのを防ぐために、画素電極9と共通電極との間に形成される液晶容量と並列に蓄積容量70が設けられている。

【0053】

本実施の形態の液晶ライトバルブ1の駆動回路部60は、上述のデータドライバ201、走査ドライバ104の他、図4に示すように、コントローラ61、第1フレームメモリ62、第2フレームメモリ63の2画面分のフレームメモリ、DAコンバータ64などから構成されている。第1フレームメモリ62、第2フレームメモリ63のうちの一方は外部から入力された1フレーム分の映像を一時的に蓄えるためのもの、また他方は表示用に用いられ、1フレーム毎に役割が入れ替わるものである。コントローラ61は、垂直同期信号Vsync、水平同期信号Hsync、ドットクロック信号dotclk、および画像信号DATAが入力され、第1フレームメモリ62、第2フレームメモリ63の制御、および書き込む走査線3aに対応したデータのフレームメモリからの読み出しを行う。DAコンバータ64は、フレームメモリから読み出されたデータをDA変換してデータドライバ201に供給するものである。

【0054】

走査ドライバ104の構成は、図5に示すように、コントローラ61からゲート出力パルスDY、クロック信号CLY、反転クロック信号CLY’がそれぞれ入力されるシフトレジスタ66と、シフトレジスタ66からの出力が入力される2m個のAND回路67を有している。2m本の走査線3aが画面中央部のm本目とm+1本目を境として2つのブロックに分かれており、シフトレジスタ66からの各出力に2つのイネーブル信号のいずれかが接続されている。すなわち、走査線G1〜Gmに対応するAND回路67にはシフトレジスタ66からの出力とイネーブル信号ENB1が入力され、走査線Gm+1〜G2mに対応するAND回路67にはシフトレジスタ66からの出力とイネーブル信号ENB2が入力される構成となっている。画面中央部において、シフトレジスタ66の内部構成を含めて示したのが図6である。

【0055】

(液晶ライトバルブの動作)

上記構成の駆動回路部60の動作を図7、図8を用いて説明する。

駆動回路部60においては、図7に示すように、入力される映像信号の1垂直期間中にゲート出力パルスDYが2回出力される。ゲート出力パルスDYは、1水平期間毎に1パルスが立ち上がるクロック信号CLYによって走査ドライバ104のシフトレジスタ66中をシフトしていく。ここで、図8(図7の符号Aの個所を拡大したもの)に示すように、ゲート出力パルスDYが画面中央部の異なるイネーブル信号によって制御される領域(具体的にはGm+1本目の走査線)に差し掛かったとき、イネーブル信号ENB1とイネーブル信号ENB2の位相が逆転する。以上の動作によって、ゲートパルスは走査線m本分離れた画面上の2個所に交互に出力される。すなわち、所定の走査線からm本離れた走査線に飛び越しては前記所定の走査線の次段の走査線に戻り、その走査線からm本離れた走査線に飛び越してはまたその次段の走査線に戻るというように(つまり、走査線G1、走査線Gm+1、走査線G2、走査線Gm+2、G3、…という順序で)順次出力される。ここでイネーブル信号ENB1、ENB2はそのパルス幅が入力される映像信号の1水平期間の約1/2となっている。このようにゲート出力パルスDY、イネーブル信号ENB1、ENB2を出力する事により、ライトバルブにとっての1水平期間は、入力される映像信号の1/2となる。

【0056】

一方、データドライバ201からの出力であるデータ信号Sxは、コモン電位LCCOMを中心として1水平期間毎に正極性電位と負極性電位とに極性が反転する。したがって、データ信号Sx側が1水平期間毎に極性反転しつつ、ゲートパルス側は上記の順番で走査線m本分離れた画面の2個所に交互に出力されることになる。その結果、画面上は、図9に示すように、ある1水平期間に着目すると、例えば走査線G3〜Gm+2に対応するドットは正極性電位のデータが書き込まれる領域(以下、単に正極性領域という)となり、走査線G1〜G2及びGm+3〜G2mに対応するドットは負極性電位のデータが書き込まれる領域(以下、単に負極性領域という)となるというように、画面内があたかも異なる極性のデータが書き込まれた正極性領域と負極性領域の3つの領域に分割されたような状態となる。

【0057】

図9は任意の1水平期間の瞬間を見た画面のイメージを示しており、図10は時間の流れを追って画面上の極性の変化の状態を示すものである。図10の横軸を時間(単位:1水平期間)とすると、例えば第1水平期間では走査線G2mに対応するドットに負電位が書き込まれ、次の第2水平期間では第1水平期間で負電位が書き込まれていた走査線Gm+1に対応するドットに正電位が書き込まれ、次の第3水平期間では第1、第2水平期間で正電位が書き込まれていた走査線G1に対応するドットに負電位が書き込まれ、この書き込み動作が以降繰り返される。したがって、正極性領域と負極性領域はそれぞれ2水平期間毎に1ラインずつ移動していき、走査線が画面の半分を移動したときに正極性領域と負極性領域とが完全に反転する。つまり1画面の書き換えが行われたことになる。この方法によると、走査線が全画面を移動することにより、書き換えは2度行われる事になり、結果的に入力映像信号に対し、1垂直期間が1/2になることになる。

【0058】

換言すると、本実施形態では、1つのフィールドデータを連続した複数のフィールドデータとして、書き込み開始時期を1垂直期間内でずらしながら1水平期間毎に交番的に書き込むとともに、連続したフィールドの間でデータの書き込み極性を反転させている。具体的には、1つのフィールドデータを互いに極性の異なる第1,第2の2つのフィールドデータに分け、これらのフィールドデータを1/2垂直期間だけシフトさせて重ね書きしている。このため、走査線側については、一部(複数本)の走査線を飛び越しつつ、行ったり来たりしながら全ての走査線にわたって走査が行なわれる。このため、任意の1垂直期間で見たときに、画面内には各フィールドに対応して正電位印加領域と負電位印加領域とからなる複数の領域が存在することとなる。

【0059】

本実施の形態の液晶ライトバルブにおいては、このように画面の半分の広さを持った正極性領域と負極性領域とが1垂直期間で反転することになり、領域毎には面反転駆動が行われる。1垂直期間において、任意の1ドットと隣接する1ドットとの間は2/2mの時間だけは逆極性電位となるが、残りの大部分の時間(2m−2)/2mは同極性電位となっているので、ディスクリネーションはほとんど発生しない。一方、データ線6a側は図8に信号波形を示したように、信号極性については従来のライン反転駆動と同様の動作を行っているので、従来の面反転方式で駆動したときのように画面の上側の画素と下側の画素で画素電極−データ線間の時間的な電位の関係に大きな差異が生じることがなく、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる。また、従来の技術と異なり、1水平期間の大部分を画素への書き込みに費やすので、書き込みが不充分になる等の問題が生じることもない。

また本実施の形態の場合、走査周波数は入力映像信号周波数の倍の周波数である100Hz以上の周波数となるので、フリッカを確実に抑制することができる。

【0060】

[第2の実施の形態]

以下、本発明の第2の実施の形態を図11、図12を参照して説明する。

本実施の形態の液晶ライトバルブ(液晶装置)の基本構成は第1の実施の形態とほぼ同様であり、画面内を4分割して面反転を行う点のみが異なっている。すなわち、本実施形態は、1つのフィールドデータを第1,第2,第3,第4の連続した4つのフィールドデータとして、書き込み開始時期を1/4垂直期間だけシフトさせて重ね書きした駆動例である。なお、1フィールド内ではデータの書き込み極性は等しく、隣接するフィールド同士(即ち、第1と第2,第2と第3,第3と第4,第4と第1のフィールド同士)ではそのデータの書き込み極性が互いに異なるようにしている。

図11は本実施の形態の液晶ライトバルブにおける任意の1水平期間の瞬間を見た画面のイメージを示す図、図12は液晶ライトバルブの動作を説明するためのタイミングチャートである。本実施の形態では液晶ライトバルブの基本構成に関する説明は省略し、動作についてのみ説明する。

【0061】

第1の実施の形態では走査線3aの数を2m本としたが、本実施の形態においては便宜上4m本とする。そして、走査ドライバ104内を、走査線G1〜Gm、走査線Gm+1〜G2m、走査線G2m+1〜G3m、走査線G3m+1〜G4mの4つのブロックに分割し、4つのイネーブル信号を用いる。またこのとき、入力される映像信号の1垂直期間中にゲート出力パルスDYは4回出力される。

【0062】

本実施の形態の場合、図12に示すように、ゲートパルスは走査線m本分離れた画面上の4個所に順番に出力される。すなわち、所定の走査線からm本離れた走査線に飛び越し、さらにその走査線からm本離れた走査線(最初の走査線からは2m本離れた走査線)に飛び越し、さらにその走査線からm本離れた走査線(最初の走査線からは3m本離れた走査線)に飛び越した後、前記所定の走査線の次段の走査線に戻るというように(つまり、走査線G1、走査線Gm+1、走査線G2m+1、走査線G3m+1、走査線G2、走査線Gm+2、走査線G2m+2、走査線G3m+2、…という順序で)順次出力される。

【0063】

一方、データドライバ201からの出力であるデータ信号Sxは、コモン電位LCCOMを中心として1水平期間毎に正極性電位と負極性電位とに極性が反転する。したがって、データ信号Sx側が1水平期間毎に極性反転しつつ、ゲートパルス側は上記の順番で走査線m本分ずつ離れた画面の4個所に順番に出力されることになる。その結果、画面上は、図11に示すように、ある1水平期間に着目すると、例えば走査線G1〜G2,に対応するドットは負極性領域となり、G3〜Gm+2に対応するドットは正極性領域となり、走査線Gm+3〜G2m+2に対応するドットは負極性領域となり、走査線G2m+3〜G3m+2に対応するドットは正極性領域となり、走査線G3m+3〜G4mに対応するドットは負極性領域となるというように、画面内があたかも異なる極性のデータが書き込まれた正極性領域と負極性領域の5つの領域に分割されたような状態となる。

【0064】

この書き込み動作が以降繰り返され、正極性領域と負極性領域はそれぞれ4水平期間毎に1ドットずつ移動していき、1垂直期間で画面の1/4を移動する。つまり、1垂直期間で正極性領域と負極性領域とが完全に反転する。

【0065】

本実施の形態においても、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる、書き込みが不充分になる等の問題が生じることがない、といった第1の実施の形態と同様の効果を得ることができる。

【0066】

[第3の実施の形態]

以下、本発明の第3の実施の形態を図13を参照して説明する。

本実施の形態の液晶ライトバルブ(液晶装置)の基本構成は第1、第2の実施の形態とほぼ同様であり、走査線の走査順序のみが異なっている。

図13は本実施の形態の液晶ライトバルブの動作を説明するためのタイミングチャートである。本実施の形態では液晶ライトバルブの基本構成に関する説明は省略し、動作についてのみ説明する。

【0067】

本実施の形態では走査線3aの数を2m本とする。第1、第2の実施の形態では、データドライバ201からの出力であるデータ信号Sxがコモン電位LCCOMを中心として1水平期間毎に正極性電位と負極性電位とに極性反転していた。これに対して、本実施の形態では、図13に示すように、データ信号Sxがコモン電位LCCOMを中心として2水平期間毎に正極性電位と負極性電位とに極性反転している。

【0068】

そして、本実施の形態の場合、ゲートパルスは隣接する2本の走査線に連続して出力された後、走査線m本分を飛び越し、隣接する2本の走査線に連続して出力される。すなわち、所定の走査線に出力され、その走査線に隣接する走査線に出力され、前記所定の走査線からm本離れた走査線に飛び越して出力され、その走査線に隣接する走査線に出力され、前記所定の走査線に隣接する走査線に隣接する走査線に再度戻って出力され、以降この順番が繰り返される(つまり、走査線G1、走査線G2、走査線Gm+1、走査線Gm+2、走査線G3、走査線G4、走査線Gm+3、走査線Gm+4、…という順序)。

【0069】

本実施の形態の場合、ある1水平期間に着目すると、画面上は図9に示す第1の実施の形態と同様、例えば走査線G3〜Gm+2に対応するドットは正極性領域となり、走査線G1〜G2及びGm+3〜G2mに対応するドットは負極性領域となるというように、画面内があたかも異なる極性のデータが書き込まれた正極性領域と負極性領域の3つの領域に分割されたような状態となる。そして、この書き込み動作が以降の水平期間でも繰り返され、正極性領域と負極性領域はそれぞれ2水平期間毎に1ドットずつ移動していき、1垂直期間で画面の半分を移動する。つまり、1垂直期間で正極性領域と負極性領域とが完全に反転する。

【0070】

本実施の形態においても、クロストークを抑制しつつ、画面の場所による表示の不均一を回避することができる、書き込みが不充分になる等の問題が生じることがない、といった第1、第2の実施の形態と同様の効果を得ることができる。

【0071】

[第4の実施の形態]

以下、本発明の第4の実施の形態を図15〜図18を参照して説明する。

本実施の形態の液晶ライトバルブ(液晶装置)の基本構成は第1の実施の形態とほぼ同様であり、駆動回路に備えられるメモリ及び走査ドライバの形態のみ異なっている。

【0072】

本実施の形態の液晶ライトバルブ1の駆動回路部80は、図15に示すように、データドライバ201、走査ドライバ108、コントローラ81、メモリ82、DAコンバータ64などから構成されている。メモリ82は外部から入力された半画面分(1/2フィールド分)の映像を一時的に蓄えるとともに、この記憶されたデータにより1/2垂直期間だけ遅延した画像信号を作り出すためのものである。コントローラ81は、垂直同期信号Vsync、水平同期信号Hsync、ドットクロック信号dotclk、および画像信号DATAが入力され、メモリ82の制御、および書き込む走査線3aに対応したデータのメモリからの読み出しを行う。DAコンバータ64は、外部から入力された画像信号DATA及びこれと並行してメモリ82から読み出される画像データをDA変換してデータドライバ201に供給するものである。なお、外部からの画像信号DATAとメモリ82から読み出された画像データとは、DAコンバータ64に対して書き込みに対する1水平期間毎に交番的に出力される。

【0073】

走査ドライバ108の構成は、図16に示すように、コントローラ81からゲート出力パルスDY、クロック信号CLY、反転クロック信号CLY’がそれぞれ入力されるシフトレジスタ66と、シフトレジスタ66からの出力が入力される2m個のAND回路67を有している。2m本の走査線3aは画像表示領域の最上部から奇数本目に配置されたものと偶数本目に配置されたものとの2つのブロックに分かれており、シフトレジスタ66からの各出力に2つのイネーブル信号のいずれかが接続されている。すなわち、偶数本目の走査線G2,G4,・・・,Gm,Gm+2,・・・,G2mに対応するAND回路67にはシフトレジスタ66からの出力とイネーブル信号ENB1が入力され、奇数本目の走査線G1,G3,・・・,Gm+1,Gm+3,・・・,G2m−1に対応するAND回路67にはシフトレジスタ66からの出力とイネーブル信号ENB2が入力される構成となっている。画面中央部において、シフトレジスタ66の内部構成を含めて示したのが図17である。

【0074】

上記構成の駆動回路部80の動作を図18を用いて説明する。

駆動回路部80においては、映像信号の1垂直期間中にゲート出力パルスDYが2回出力される。ここでそれぞれのDYは走査線の数で奇数本離れるタイミングで出力される。ゲート出力パルスDYは、映像信号の1水平期間毎に1パルスが立ち上がるクロック信号CLYによって走査ドライバ108のシフトレジスタ66中をシフトしていく。一方、イネーブル信号ENB1,ENB2は、ENB1,ENB1,ENB2,ENB2,ENB1,ENB1,ENB2,ENB2,・・・の順で、書き込みの2水平期間毎に交番的に立ち上がり、これらのイネーブル信号の立ち上がり位置に対応する走査線に対して走査信号が出力される。ここで2つの走査線は、DYの出力タイミングに従い、奇数本離れた場所にあるのでそれぞれは異なるイネーブル信号により出力が制御される。以上の動作によって、ゲートパルスは走査線m本分離れた画面上の2個所に交互に出力される。すなわち、所定の走査線からm本離れた走査線に飛び越しては前記所定の走査線の次段の走査線に戻り、その走査線からm本離れた走査線に飛び越してはまたその次段の走査線に戻るというように(つまり、走査線G1、走査線Gm+1、走査線G2、走査線Gm+2、G3、…という順序で)順次出力される。

【0075】

一方、データドライバ201からの出力であるデータ信号Sxは、コモン電位LCCOMを中心として書き込みの1水平期間毎に正極性電位と負極性電位とに極性が反転する。したがって、データ信号Sx側が書き込みの1水平期間毎に極性反転しつつ、ゲートパルス側は上記の順番で走査線m本分離れた画面の2個所に交互に出力されることになる。その結果、画面上は、例えば図9に示すように、ある1水平期間に着目すると、例えば走査線G3〜Gm+2に対応するドットは正極性電位のデータが書き込まれる領域(以下、単に正極性領域という)となり、走査線G1〜G2及びGm+3〜G2mに対応するドットは負極性電位のデータが書き込まれる領域(以下、単に負極性領域という)となるというように、画面内があたかも異なる極性のデータが書き込まれた正極性領域と負極性領域の3つの領域に分割されたような状態となる。すなわち、本実施形態では、イネーブル信号の立て方は異なるものの、上記第1実施形態と同様の走査が行なわれる。

【0076】

換言すると、本実施形態では、1つのフィールドデータを連続した第1,第2のフィールドデータとして、外部から入力された画像信号を第1のフィールドデータとしてそのまま書き込みつつ、この画像信号を上記メモリに記憶させて上記画像信号に対して遅延した第2のフィールドデータを作り出し、これらのフィールドデータを交番的に書き込むとともに、第2のフィールドデータの極性を第1のフィールドデータに対して反転させている。

【0077】

このため、本実施形態でも、クロストークを抑制しつつ、画面の場所による表示の不均一を回避できる。また、本実施形態では、1つのフレームデータを2つのフィールドデータとして、一方のフィールドデータに外部から入力される画像信号をそのまま用いているため、画像は実質的に倍速(即ち、外部から入力される画像信号の2倍の周波数)で書き込まれることとなる。通常、倍速駆動を行なう場合には、2画面分(2フィールド分)のメモリ容量が必要となるが、本構成では、外部からの画像信号をそのままデータ線に出力することで画面の半分が書き込まれるため、メモリ容量は表示画面全体の半分の容量(即ち、1/2フィールド分)だけあればよい。このため、通常のものに比べてメモリ容量が1/4で済み、部材コストを大幅に低減することができる。また、本実施形態では、画素に対して倍速書き込みが行なわれるので、フリッカが抑制される。

【0078】

[投射型液晶装置]

図14は上記実施の形態の液晶ライトバルブを3個用いた、いわゆる3板式の投射型液晶表示装置(液晶プロジェクタ)の一例を示す概略構成図である。図中、符号1100は光源、1108はダイクロイックミラー、1106は反射ミラー、1122,1123,1124はリレーレンズ、100R,100G,100Bは液晶ライトバルブ、1112はクロスダイクロイックプリズム、1114は投射レンズ系を示す。

【0079】

光源1100は、メタルハライド等のランプ1102とランプ1102の光を反射するリフレクタ1101とから構成されている。青色光・緑色光反射のダイクロイックミラー1108は、光源1100からの白色光のうちの赤色光を透過させるとともに、青色光と緑色光とを反射する。透過した赤色光は反射ミラー1106で反射され、赤色光用液晶ライトバルブ100Rに入射される。

【0080】

一方、ダイクロイックミラー1108で反射された色光のうち、緑色光は、緑色光反射のダイクロイックミラー1108によって反射され、緑色用液晶ライトバルブ100Gに入射される。一方、青色光は、第2のダイクロイックミラー1108も透過する。青色光に対しては、光路長が緑色光、赤色光と異なるのを補償するために、入射レンズ1122、リレーレンズ1123、出射レンズ1124を含むリレーレンズ系からなる導光手段1121が設けられ、これを介して青色光が青色光用液晶ライトバルブ100Bに入射される。

【0081】

各ライトバルブ100R,100G,100Bにより変調された3つの色光はクロスダイクロイックプリズム1112に入射する。このプリズムは、4つの直角プリズムが貼り合わされ、その内面に赤色光を反射する誘電体多層膜と青色光を反射する誘電体多層膜とが十字状に形成されたものである。これらの誘電体多層膜によって3つの色光が合成されて、カラー画像を表す光が形成される。合成された光は、投射光学系である投射レンズ系1114によってスクリーン1120上に投射され、画像が拡大されて表示される。

【0082】

上記構成の投射型液晶表示装置においては、上記実施の形態の液晶ライトバルブを用いたことにより、表示の均一性に優れた投射型液晶表示装置を実現することができる。

【0083】

なお、本発明の技術範囲は上記実施の形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。例えば上記の実施の形態では画面上を異なる極性電位を書き込む2つの領域あるいは4つの領域に分割した例を示したが、分割数はこれに限るものではなく、さらに分割数を多くしても良い。ただし、分割数を多くすればする程、隣接する走査線に逆極性電位が印加された状態となる時間が長くなる。その場合でも、時間にして少なくとも1垂直期間の50%以上の割合で同極性電位が印加された状態とすることが望ましい。また、各領域内での走査の順序については上記実施の形態に限らず、適宜変更が可能である。

【0084】

また、上記第4実施形態では、1つのフィールドデータを2つのフィールドデータに分けたが、この代わりに、1つのフィールドデータを3つ以上のフィールドデータに分けることも可能である。この場合、いずれかのフィールドデータに外部からの画像信号を用い、それ以外のフィールドデータには、それぞれ別々のメモリに記憶されたデータを用いる。

【0085】

また、上記実施形態ではTFTを用いたアクティブマトリクス型の液晶装置を例に挙げて説明したが、本発明はこれに限定されず、例えば画素スイッチング素子にTFD(Thin Film Diode)を用いたものや、パッシブマトリクス型のもの等、複数の画素をマトリクス駆動する種々の表示装置に対しても本発明を適用することができる。

【0086】

【発明の効果】

以上、詳細に説明したように、本発明によれば、クロストークを抑制しつつ、画面の場所による表示の不均一を回避できるとともに、書き込みが不充分になる等の問題が生じることがない液晶装置を実現することができる。

【図面の簡単な説明】

【図1】 本発明の第1の実施の形態の液晶ライトバルブの概略構成を示す平面図である。

【図2】 図1のH−H’線に沿う断面図である。

【図3】 同、液晶ライトバルブを構成するマトリクス状に形成された複数の画素の等価回路図である。

【図4】 同、液晶ライトバルブの駆動回路部を含むブロック図である。

【図5】 同、駆動回路部内の走査ドライバの構成を示す回路図である。

【図6】 図5中の要部の詳細回路図である。

【図7】 同、液晶ライトバルブの動作を説明するためのタイミングチャートである。

【図8】 図7中の要部を取りだして示すタイミングチャートである。

【図9】 同、液晶ライトバルブの画面のイメージを示す図である。

【図10】 同、画面の動きを説明するための図である。

【図11】 本発明の第2の実施の形態の液晶ライトバルブの画面のイメージを示す図である。

【図12】 同、液晶ライトバルブの動作を説明するためのタイミングチャートである。

【図13】 本発明の第3の実施の形態の液晶ライトバルブの動作を説明するためのタイミングチャートである。

【図14】 本発明の液晶装置を用いた投射型表示装置の一例を示す概略構成図である。

【図15】 本発明の第4の実施の形態の液晶ライトバルブの駆動回路部を含むブロック図である。

【図16】 同、駆動回路部内の走査ドライバの構成を示す回路図である。

【図17】 図16中の要部の詳細回路図である。

【図18】 同、液晶ライトバルブの動作を説明するためのタイミングチャートである。

【符号の説明】

1 液晶ライトバルブ

3a 走査線

6a データ線

9 画素電極

30 TFT(スイッチング素子)

60,80 駆動回路部

61,81 コントローラ

62 第1フレームメモリ

63 第2フレームメモリ

82 メモリ(FIFO)

104,108 走査ドライバ

201 データドライバ

Claims (7)

- 互いに交差する複数のデータ線及び複数(m本)の走査線と、前記データ線及び走査線の交差に対応して設けられた画素と、これらの画素からなる画像表示領域を備えた液晶装置において、

前記画像表示領域は、複数の走査線からなり所定電位に対して正極性の画像信号が供給される表示領域と、複数の走査線からなり前記所定電位に対して負極性の画像信号が供給される表示領域とを、それぞれ1乃至複数を含むn個の表示領域からなり、

前記n個の表示領域の走査線に走査信号を供給する走査ドライバと、前記n個の表示領域のデータ線に画像信号を供給するデータドライバとを備え、

前記走査ドライバには、画像信号における1垂直期間内にn個のゲート出力パルスがそれぞれ異なるタイミングで入力され、前記n個のゲート出力パルスがそれぞれクロック信号に同期して前記走査ドライバにおいてシフトされるとともに、各走査線には、順次にパルスが立ち上がるn個のイネーブル信号のいずれかが割り当てられ、

前記走査ドライバは、各走査線に、前記n個のゲート出力パルスのそれぞれと、前記走査線ごとに割り当てられたイネーブル信号とに基づき前記走査信号を論理合成して出力する論理合成回路を備え、

前記走査ドライバは、前記n個のゲート出力パルスとn個のイネーブル信号に基づくm個の走査信号を、m本の走査線にそれぞれ出力し、

前記データドライバは、前記m本の走査線がそれぞれ属する表示領域に対応した極性の画像信号を、前記走査信号が出力される順番で前記データ線に出力することを特徴とする液晶装置。 - 前記n個のゲート出力パルスは、互いに前記画像信号の1/2垂直期間だけずれたタイミングで上記走査ドライバに入力される2つのパルスであり、

前記n個のイネーブル信号は、交互にパルスが立ち上がる第1,第2のイネーブル信号であり、

上記走査ドライバでは同時にパルスが立ち上がる前記2つのゲート出力パルスのそれぞれと、交互にパルスが立ち上がる第1,第2のイネーブル信号のそれぞれと、に基づいて、2つの走査信号が順次出力され、

前記2つの走査信号はそれぞれ、画像信号における1/2垂直期間に対応する分だけずれた位置にある各走査線に出力され、

前記複数の走査線を配列方向において第1及び第2の2つの領域に分けたときに、前記第1のイネーブル信号は前記第1の領域に配置された複数の走査線に割り当てられ、前記第2のイネーブル信号は前記第2の領域に配置された複数の走査線に割り当てられることを特徴とする請求項1に記載の液晶装置。 - 前記n個のゲート出力パルスは、前記画像信号の1/4垂直期間だけずれたタイミングで前記走査ドライバに入力される4つのパルスであり、

前記n個のイネーブル信号は、順次パルスが立ち上がる第1〜第4の4つのイネーブル信号であり、

上記走査線ドライバでは同時にパルスが立ち上がる4つのゲート出力パルスと、順次パルスが立ち上がる第1〜第4の4つのイネーブル信号のいずれかとに基づいて4つの走査信号が順次出力され、

前記4つの走査信号はそれぞれ、画像信号における1/4垂直期間に対応する分ずつ、ずれた位置にある各走査線に出力され、

前記複数の走査線を配列方向に沿って第1から第4の4つの領域に分けたときに、前記第1から第4のイネーブル信号はそれぞれ前記第1から第4の領域のいずれかに配置された複数の走査線に割り当てられることを特徴とする請求項1に記載の液晶装置。 - 前記n個のゲート出力パルスは、前記画像信号の1/2垂直期間だけずれたタイミングで前記走査ドライバに入力される2つのパルスであり、

前記n個のイネーブル信号は、交互にパルスが立ち上がる第1,第2のイネーブル信号であり、

上記走査ドライバでは同時にパルスが立ち上がる前記2つのゲート出力パルスのそれぞれと、交互にパルスが立ち上がる第1,第2のイネーブル信号のそれぞれとに基づいて、2つの走査信号が順次出力され、

前記2つの走査信号はそれぞれ、画像信号における1/2垂直期間に対応する分だけずれた位置にある各走査線に出力され、

前記第1のイネーブル信号は前記複数の走査線のうち奇数番目の走査線に割り当てられ、前記第2のイネーブル信号は前記複数の走査線のうち偶数番目の走査線に割り当てられることを特徴とする請求項1に記載の液晶装置。 - 前記画像信号を記憶するメモリが備えられ、

外部から入力された画像信号は上記データドライバに供給される一方、上記メモリに記憶され、

上記データドライバは、外部から入力された画像信号と、上記メモリから読み出された画像信号とを1水平期間毎に交互に前記データ線に供給し、上記メモリから読み出された画像信号の所定電位に対する極性と、上記外部から供給された画像信号の所定電位に対する極性とは互いに逆の極性であることを特徴とする請求項1に記載の液晶装置。 - 照明装置と、前記照明装置から射出される光を変調する光変調装置と、前記光変調装置により変調された光を投射する投射装置とを有する投射型表示装置であって、

前記光変調装置として、請求項1ないし5のいずれか一項に記載の液晶装置を備えたことを特徴とする投射型表示装置。 - 画像信号を一旦蓄えた後、前記走査線の走査順序に従って画素へ書き込む画像信号が読み出されるフレームメモリが備えられたことを特徴とする請求項6に記載の投射型表示装置。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003198659A JP4701589B2 (ja) | 2002-09-30 | 2003-07-17 | 液晶装置と投射型表示装置 |

| CNB031575293A CN100498478C (zh) | 2002-09-30 | 2003-09-23 | 液晶装置及其驱动方法以及投影式显示装置 |

| US10/667,340 US7265742B2 (en) | 2002-09-30 | 2003-09-23 | Liquid crystal device, drive method therefor, and projection type display apparatus |

| EP03256039A EP1406242A3 (en) | 2002-09-30 | 2003-09-25 | Liquid crystal device, drive method therefor, and projection type display apparatus |

| KR1020030066797A KR100572553B1 (ko) | 2002-09-30 | 2003-09-26 | 액정 장치와 그 구동 방법 및 투사형 표시 장치 |

| TW092126714A TWI229832B (en) | 2002-09-30 | 2003-09-26 | Liquid crystal device, drive method therefor, and projection type display apparatus |

| US11/602,394 US7800604B2 (en) | 2002-09-30 | 2006-11-21 | Liquid crystal device, drive method therefor, and projection type display apparatus |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002287449 | 2002-09-30 | ||

| JP2002287449 | 2002-09-30 | ||

| JP2003198659A JP4701589B2 (ja) | 2002-09-30 | 2003-07-17 | 液晶装置と投射型表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010106226A Division JP5494196B2 (ja) | 2002-09-30 | 2010-05-06 | 表示装置、電子機器および投射型表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004177930A JP2004177930A (ja) | 2004-06-24 |

| JP2004177930A5 JP2004177930A5 (ja) | 2006-06-08 |

| JP4701589B2 true JP4701589B2 (ja) | 2011-06-15 |

Family

ID=31996231

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003198659A Expired - Fee Related JP4701589B2 (ja) | 2002-09-30 | 2003-07-17 | 液晶装置と投射型表示装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7265742B2 (ja) |

| EP (1) | EP1406242A3 (ja) |

| JP (1) | JP4701589B2 (ja) |

| KR (1) | KR100572553B1 (ja) |

| CN (1) | CN100498478C (ja) |

| TW (1) | TWI229832B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005234212A (ja) * | 2004-02-19 | 2005-09-02 | Seiko Epson Corp | 電気光学装置、その駆動回路および電子機器 |

Families Citing this family (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4701589B2 (ja) * | 2002-09-30 | 2011-06-15 | セイコーエプソン株式会社 | 液晶装置と投射型表示装置 |

| JP4516280B2 (ja) * | 2003-03-10 | 2010-08-04 | ルネサスエレクトロニクス株式会社 | 表示装置の駆動回路 |

| JP4239892B2 (ja) * | 2003-07-14 | 2009-03-18 | セイコーエプソン株式会社 | 電気光学装置とその駆動方法ならびに投射型表示装置、電子機器 |

| JP4543632B2 (ja) * | 2003-08-07 | 2010-09-15 | 日本電気株式会社 | 液晶表示装置及び液晶表示装置駆動方法 |

| JP4154598B2 (ja) | 2003-08-26 | 2008-09-24 | セイコーエプソン株式会社 | 液晶表示装置の駆動法、液晶表示装置及び携帯型電子機器 |

| JP4559091B2 (ja) * | 2004-01-29 | 2010-10-06 | ルネサスエレクトロニクス株式会社 | 表示装置用駆動回路 |

| JP4590879B2 (ja) * | 2004-02-12 | 2010-12-01 | セイコーエプソン株式会社 | 液晶装置、液晶装置の駆動回路及びその駆動方法並びに電子機器 |

| EP1564715A3 (en) * | 2004-02-12 | 2006-11-08 | Seiko Epson Corporation | Driving circuit and driving method for electro-optical device |

| JP4561260B2 (ja) * | 2004-09-08 | 2010-10-13 | セイコーエプソン株式会社 | 電気光学装置用駆動回路及び駆動方法並びに電気光学装置及び電子機器 |

| JP2005309049A (ja) * | 2004-04-21 | 2005-11-04 | Sony Corp | 表示装置 |

| JP4010308B2 (ja) | 2004-05-24 | 2007-11-21 | ソニー株式会社 | 表示装置および表示装置の駆動方法 |

| JP4622320B2 (ja) * | 2004-06-04 | 2011-02-02 | セイコーエプソン株式会社 | 電気光学装置の駆動回路及び駆動方法、電気光学装置並びに電子機器 |

| JP2005345879A (ja) * | 2004-06-04 | 2005-12-15 | Seiko Epson Corp | 電気光学装置の駆動回路及び駆動方法、電気光学装置並びに電子機器 |

| JP2005352315A (ja) * | 2004-06-11 | 2005-12-22 | Seiko Epson Corp | 電気光学装置用駆動回路及び電気光学装置用駆動方法、並びに、電気光学装置及び電子機器 |

| TWI253050B (en) * | 2004-07-14 | 2006-04-11 | Au Optronics Corp | Method of multiple-frame scanning for a display |

| JP2006030529A (ja) | 2004-07-15 | 2006-02-02 | Seiko Epson Corp | 電気光学装置用駆動回路及び電気光学装置用駆動方法、並びに電気光学装置及び電子機器 |

| JP4581851B2 (ja) | 2004-07-27 | 2010-11-17 | セイコーエプソン株式会社 | 電気光学装置の駆動回路及び駆動方法、電気光学装置並びに電子機器 |

| JP4529582B2 (ja) * | 2004-08-12 | 2010-08-25 | セイコーエプソン株式会社 | 電気光学装置及び電子機器、並びに電気光学装置用駆動方法及び検査方法 |

| JP4561259B2 (ja) * | 2004-09-08 | 2010-10-13 | セイコーエプソン株式会社 | 電気光学装置用駆動回路及び駆動方法並びに電気光学装置及び電子機器 |

| KR20060029352A (ko) * | 2004-10-01 | 2006-04-06 | 삼성전자주식회사 | 어레이 기판과, 이를 갖는 표시패널 및 표시장치 |

| JP4196924B2 (ja) * | 2004-10-07 | 2008-12-17 | セイコーエプソン株式会社 | 電気光学装置、その駆動方法および電子機器 |

| JP5008302B2 (ja) * | 2004-12-06 | 2012-08-22 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2006062212A1 (en) | 2004-12-06 | 2006-06-15 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus using the same |

| US7847776B2 (en) * | 2005-01-12 | 2010-12-07 | Seiko Epson Corporation | Drive circuit of electro-optical device, driving method of electro-optical device, and electro-optical device having the same |

| JP4508122B2 (ja) | 2005-04-11 | 2010-07-21 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP4581836B2 (ja) * | 2005-05-19 | 2010-11-17 | セイコーエプソン株式会社 | 液晶装置、液晶装置の駆動方法、プロジェクタ及び直視型表示装置 |

| JP4572748B2 (ja) * | 2005-06-10 | 2010-11-04 | エプソンイメージングデバイス株式会社 | 電気光学装置、駆動方法および電子機器 |

| JP4887977B2 (ja) * | 2005-11-21 | 2012-02-29 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の駆動方法、電圧モニタ方法および電子機器 |

| JP2007212499A (ja) * | 2006-02-07 | 2007-08-23 | Seiko Epson Corp | 液晶装置及びプロジェクタ |

| JP4735328B2 (ja) * | 2006-02-28 | 2011-07-27 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP2007293264A (ja) * | 2006-03-28 | 2007-11-08 | Seiko Epson Corp | 電気光学装置及びその駆動方法並びに電子機器 |

| JP4145937B2 (ja) * | 2006-04-24 | 2008-09-03 | セイコーエプソン株式会社 | 液晶装置、その制御回路および電子機器 |

| JP4400593B2 (ja) | 2006-05-19 | 2010-01-20 | セイコーエプソン株式会社 | 電気光学装置、その駆動方法および電子機器 |

| KR101263531B1 (ko) * | 2006-06-21 | 2013-05-13 | 엘지디스플레이 주식회사 | 액정표시장치 |

| JP4281776B2 (ja) | 2006-09-29 | 2009-06-17 | セイコーエプソン株式会社 | 電気光学装置、および、その駆動方法 |

| JP4281775B2 (ja) | 2006-09-29 | 2009-06-17 | セイコーエプソン株式会社 | 電気光学装置、走査線駆動回路、駆動方法および電子機器 |

| KR101400383B1 (ko) * | 2006-12-22 | 2014-05-27 | 엘지디스플레이 주식회사 | 액정표시장치 및 이의 구동방법 |

| EP2149874A4 (en) * | 2007-04-26 | 2011-11-30 | Sharp Kk | LIQUID CRYSTAL DISPLAY |

| JP4501962B2 (ja) * | 2007-05-21 | 2010-07-14 | セイコーエプソン株式会社 | 画像表示装置 |

| JP5035671B2 (ja) * | 2007-05-30 | 2012-09-26 | 奇美電子股▲ふん▼有限公司 | 表示装置の駆動装置および駆動方法 |

| JP5540469B2 (ja) * | 2008-02-07 | 2014-07-02 | セイコーエプソン株式会社 | 電気光学装置の駆動方法、電気光学装置及び電子機器 |

| JP2010156856A (ja) * | 2008-12-27 | 2010-07-15 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| JP5439060B2 (ja) * | 2009-06-30 | 2014-03-12 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP5442754B2 (ja) * | 2009-10-28 | 2014-03-12 | シャープ株式会社 | アクティブマトリクス基板、液晶パネル、液晶表示装置、液晶表示ユニット、テレビジョン受像機 |

| JP6102066B2 (ja) | 2012-03-13 | 2017-03-29 | セイコーエプソン株式会社 | 走査線駆動回路,電子光学装置および電子機器 |

| JP6255973B2 (ja) | 2013-12-18 | 2018-01-10 | セイコーエプソン株式会社 | 電気光学装置、及び電子機器 |

| KR20150071550A (ko) | 2013-12-18 | 2015-06-26 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN106920527B (zh) * | 2017-05-05 | 2018-02-02 | 惠科股份有限公司 | 一种显示面板的驱动方法、驱动装置及显示装置 |

| JP6596527B2 (ja) | 2018-03-09 | 2019-10-23 | 浜松ホトニクス株式会社 | 空間光変調器、光変調装置、及び空間光変調器の駆動方法 |

| JP7111678B2 (ja) * | 2019-09-30 | 2022-08-02 | 浜松ホトニクス株式会社 | 光変調装置、及び空間光変調器の駆動方法 |

| CN111261126B (zh) * | 2020-03-24 | 2022-03-18 | 合肥京东方光电科技有限公司 | 显示面板的驱动方法、驱动装置及显示面板 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08304766A (ja) * | 1995-05-02 | 1996-11-22 | Sony Corp | プラズマアドレス表示装置 |

| JPH09130708A (ja) * | 1995-10-31 | 1997-05-16 | Victor Co Of Japan Ltd | 液晶画像表示装置 |

| JPH09197377A (ja) * | 1996-01-11 | 1997-07-31 | Casio Comput Co Ltd | 液晶駆動方法および液晶駆動装置 |

| JPH11295697A (ja) * | 1998-04-15 | 1999-10-29 | Seiko Epson Corp | 液晶表示装置の駆動方法及び電子機器 |

| JP2001166280A (ja) * | 1999-12-10 | 2001-06-22 | Nec Corp | 液晶表示装置の駆動方法 |

| JP2003044021A (ja) * | 2001-05-14 | 2003-02-14 | Thomson Licensing Sa | ディスプレイ極性のインタリーブによるフリッカ減少方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5376944A (en) * | 1990-05-25 | 1994-12-27 | Casio Computer Co., Ltd. | Liquid crystal display device with scanning electrode selection means |

| JPH05313608A (ja) | 1992-05-12 | 1993-11-26 | Sharp Corp | 液晶表示パネルの駆動装置 |

| TW270993B (en) * | 1994-02-21 | 1996-02-21 | Hitachi Seisakusyo Kk | Matrix liquid crystal display and driving circuit therefor |

| US6545653B1 (en) * | 1994-07-14 | 2003-04-08 | Matsushita Electric Industrial Co., Ltd. | Method and device for displaying image signals and viewfinder |

| JP3516382B2 (ja) * | 1998-06-09 | 2004-04-05 | シャープ株式会社 | 液晶表示装置及びその駆動方法並びに走査線駆動回路 |

| KR100303206B1 (ko) * | 1998-07-04 | 2001-11-30 | 구본준, 론 위라하디락사 | 도트 인버젼 방식 액정 패널 구동 장치 |

| JP2001209027A (ja) | 2000-01-25 | 2001-08-03 | Mitsubishi Electric Corp | 液晶表示装置およびその駆動方法 |

| JP3747768B2 (ja) * | 2000-03-17 | 2006-02-22 | 株式会社日立製作所 | 液晶表示装置 |

| JP2002049360A (ja) * | 2000-08-02 | 2002-02-15 | Victor Co Of Japan Ltd | 液晶表示装置 |

| KR20020052137A (ko) * | 2000-12-23 | 2002-07-02 | 구본준, 론 위라하디락사 | 액정표시장치 |

| JP2002244623A (ja) * | 2001-02-16 | 2002-08-30 | Matsushita Electric Ind Co Ltd | 液晶表示装置の駆動方式および駆動回路 |

| KR100859467B1 (ko) * | 2002-04-08 | 2008-09-23 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 구동방법 |

| JP4701589B2 (ja) * | 2002-09-30 | 2011-06-15 | セイコーエプソン株式会社 | 液晶装置と投射型表示装置 |

| JP4581488B2 (ja) * | 2003-08-12 | 2010-11-17 | セイコーエプソン株式会社 | 表示装置およびその駆動方法、並びに投射型表示装置 |

| JP2007212499A (ja) * | 2006-02-07 | 2007-08-23 | Seiko Epson Corp | 液晶装置及びプロジェクタ |

-

2003

- 2003-07-17 JP JP2003198659A patent/JP4701589B2/ja not_active Expired - Fee Related

- 2003-09-23 CN CNB031575293A patent/CN100498478C/zh not_active Expired - Fee Related

- 2003-09-23 US US10/667,340 patent/US7265742B2/en active Active

- 2003-09-25 EP EP03256039A patent/EP1406242A3/en not_active Withdrawn

- 2003-09-26 KR KR1020030066797A patent/KR100572553B1/ko active IP Right Grant

- 2003-09-26 TW TW092126714A patent/TWI229832B/zh not_active IP Right Cessation

-

2006

- 2006-11-21 US US11/602,394 patent/US7800604B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08304766A (ja) * | 1995-05-02 | 1996-11-22 | Sony Corp | プラズマアドレス表示装置 |

| JPH09130708A (ja) * | 1995-10-31 | 1997-05-16 | Victor Co Of Japan Ltd | 液晶画像表示装置 |

| JPH09197377A (ja) * | 1996-01-11 | 1997-07-31 | Casio Comput Co Ltd | 液晶駆動方法および液晶駆動装置 |

| JPH11295697A (ja) * | 1998-04-15 | 1999-10-29 | Seiko Epson Corp | 液晶表示装置の駆動方法及び電子機器 |

| JP2001166280A (ja) * | 1999-12-10 | 2001-06-22 | Nec Corp | 液晶表示装置の駆動方法 |

| JP2003044021A (ja) * | 2001-05-14 | 2003-02-14 | Thomson Licensing Sa | ディスプレイ極性のインタリーブによるフリッカ減少方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005234212A (ja) * | 2004-02-19 | 2005-09-02 | Seiko Epson Corp | 電気光学装置、その駆動回路および電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100498478C (zh) | 2009-06-10 |

| KR20040028528A (ko) | 2004-04-03 |

| TWI229832B (en) | 2005-03-21 |

| KR100572553B1 (ko) | 2006-04-24 |

| US20070063953A1 (en) | 2007-03-22 |

| US7800604B2 (en) | 2010-09-21 |

| CN1493907A (zh) | 2004-05-05 |

| US20050099379A1 (en) | 2005-05-12 |

| EP1406242A3 (en) | 2005-11-02 |

| JP2004177930A (ja) | 2004-06-24 |

| TW200415556A (en) | 2004-08-16 |

| US7265742B2 (en) | 2007-09-04 |

| EP1406242A2 (en) | 2004-04-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4701589B2 (ja) | 液晶装置と投射型表示装置 | |

| US7352348B2 (en) | Driving circuit and driving method for electro-optical device | |

| JP4239892B2 (ja) | 電気光学装置とその駆動方法ならびに投射型表示装置、電子機器 | |

| US7474302B2 (en) | Electro-optical device, driving method of electro-optical device, driving circuit of electro-optical device and electronic apparatus | |

| JP4581488B2 (ja) | 表示装置およびその駆動方法、並びに投射型表示装置 | |

| JP4543633B2 (ja) | 画像表示装置とその駆動方法ならびに投射型表示装置 | |

| JP5494196B2 (ja) | 表示装置、電子機器および投射型表示装置 | |

| JP2005250382A (ja) | 電気光学装置の駆動方法、電気光学装置および電子機器 | |

| JP4635704B2 (ja) | 液晶装置、駆動方法、直視型表示装置及びプロジェクタ | |

| JP4179289B2 (ja) | 電気光学装置、その駆動方法及び電子機器 | |

| JP4590879B2 (ja) | 液晶装置、液晶装置の駆動回路及びその駆動方法並びに電子機器 | |

| JP4617680B2 (ja) | 液晶装置、液晶装置の駆動回路及びその駆動方法並びに電子機器 | |

| JP4581836B2 (ja) | 液晶装置、液晶装置の駆動方法、プロジェクタ及び直視型表示装置 | |

| JP4561260B2 (ja) | 電気光学装置用駆動回路及び駆動方法並びに電気光学装置及び電子機器 | |

| JP2005227473A (ja) | 液晶装置、液晶装置の駆動回路及びその駆動方法並びに電子機器 | |

| JP2006078621A (ja) | 電気光学装置用駆動回路及び駆動方法並びに電気光学装置及び電子機器 | |

| JP2011053698A (ja) | 液晶装置、駆動方法、直視型表示装置及びプロジェクタ | |

| JP2006078619A (ja) | 電気光学装置用駆動回路及び駆動方法並びに電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060403 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20060404 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060405 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20060406 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090520 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090609 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090810 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090811 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100309 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100507 Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101109 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101203 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110221 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4701589 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |