JP2016514430A - クロック情報を信号状態の遷移に組み込むマルチワイヤシグナリングのためのトランスコーディング方法 - Google Patents

クロック情報を信号状態の遷移に組み込むマルチワイヤシグナリングのためのトランスコーディング方法 Download PDFInfo

- Publication number

- JP2016514430A JP2016514430A JP2015561729A JP2015561729A JP2016514430A JP 2016514430 A JP2016514430 A JP 2016514430A JP 2015561729 A JP2015561729 A JP 2015561729A JP 2015561729 A JP2015561729 A JP 2015561729A JP 2016514430 A JP2016514430 A JP 2016514430A

- Authority

- JP

- Japan

- Prior art keywords

- transition

- symbol

- sequence

- converting

- raw

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/125—Discriminating pulses

- H03K5/1252—Suppression or limitation of noise or interference

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/153—Arrangements in which a pulse is delivered at the instant when a predetermined characteristic of an input signal is present or at a fixed time interval after this instant

- H03K5/1534—Transition or edge detectors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0264—Arrangements for coupling to transmission lines

- H04L25/0272—Arrangements for coupling to multiple lines, e.g. for differential transmission

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/14—Channel dividing arrangements, i.e. in which a single bit stream is divided between several baseband channels and reassembled at the receiver

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/38—Synchronous or start-stop systems, e.g. for Baudot code

- H04L25/40—Transmitting circuits; Receiving circuits

- H04L25/49—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/38—Synchronous or start-stop systems, e.g. for Baudot code

- H04L25/40—Transmitting circuits; Receiving circuits

- H04L25/49—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems

- H04L25/4906—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems using binary codes

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/38—Synchronous or start-stop systems, e.g. for Baudot code

- H04L25/40—Transmitting circuits; Receiving circuits

- H04L25/49—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems

- H04L25/493—Transmitting circuits; Receiving circuits using code conversion at the transmitter; using predistortion; using insertion of idle bits for obtaining a desired frequency spectrum; using three or more amplitude levels ; Baseband coding techniques specific to data transmission systems by transition coding, i.e. the time-position or direction of a transition being encoded before transmission

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0054—Detection of the synchronisation error by features other than the received signal transition

- H04L7/0066—Detection of the synchronisation error by features other than the received signal transition detection of error based on transmission code rule

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/027—Speed or phase control by the received code signals, the signals containing no special synchronisation information extracting the synchronising or clock signal from the received signal spectrum, e.g. by using a resonant or bandpass circuit

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Power Engineering (AREA)

- Nonlinear Science (AREA)

- Dc Digital Transmission (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

Abstract

Description

本特許出願は、

2013年3月7日に出願した「Transcoding Method For Multi-Wire Signaling That Embeds Clock Information In Transition Of Signal State」という名称の米国仮出願第61/774408号、

2013年3月13日に出願した「Transcoding Method For Multi-Wire Signaling That Embeds Clock Information In Transition Of Signal State」という名称の米国仮出願第61/778768号、

2013年3月7日に出願した「Circuit To Recover A Clock Signal From Multiple Wire Data Signals That Changes State Every State Cycle And Is Immune To Data Inter-Lane Skew As Well As Data State Transition Glitches」という名称の米国仮出願第61/774247号、

の優先権を主張し、これらのすべては、本明細書によって本明細書の譲受人に譲渡され、参照によって本明細書に明白に組み込まれている。

複数のワイヤにわたる差動シグナリングを使用する搬送トランスコーディングシステムのための様々なトランスコーディング方法。

図1は、送信デバイス102と受信デバイス104との間で使用される4の階乗の変調データの符号化/復号方式を例示する。階乗のデータの符号化/復号方式は、符号化器110、送信回路112、物理ワイヤ107(たとえば、4つの導体、ライン、または電気経路)、四面体終端ネットワーク(tetrahedron termination network)106、および受信回路114、および復号器116を含んでよい。送信回路112は、データストリームを直列化する並直列変換器118、および複数のドライバ120を含んでよい。受信回路114は、複数の受信機122、およびデータストリームを非直列化する直並列変換器124を含んでよい。四面体終端ネットワーク106が送信機102および受信機104の各々のインターフェースに実際に存在し、複数のワイヤ(すなわち、この例ではワイヤA、B、C、およびD)が、送信機102および受信機104の終端ネットワーク間で連結されることは、明らかである。この例では、6つのドライバ120は、4つの導体にわたって送信される4つの差動信号を生成するために使用されてよい。しかしながら、他の数のドライバおよび差動信号は、他の実装において使用されてよい。

図4は、マルチワイヤ送信経路を介して、送信デバイス402と受信デバイス404との間で使用される、別の4の階乗の変調データの符号化/復号方式を例示する。送信デバイス402において、符号化器408、並直列変換器(SER:serializer)モジュール410、複数の差動ドライバ412、および終端ネットワーク406は、4の階乗の変調データの符号化方式を実装するように適合されてよい。受信機404において、終端ネットワーク406、受信機または受け手414、直並列変換器(DES:deserializer)モジュール410、および復号器412は、4の階乗の変調データ復号方式を実装するように適合されてよい。終端ネットワーク406が送信デバイス402および受信デバイス404の各々のインターフェースに実際に存在し、複数のワイヤ(すなわち、この例ではワイヤA、B、C、およびD)が、送信デバイス402および受信デバイス404の終端ネットワーク間で連結されることは、明らかであろう。

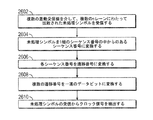

図7は、送信機702におけるビットからシンボル遷移番号への変換、そして次に受信機704におけるシンボル遷移番号からビットへの変換を例示する。送信機702は、m個のシンボル遷移番号T0〜Tm-1を生成するために、バイナリ情報、ビットを「ビット/m×T」変換器706に供給する。受信機704は、m個のシンボル遷移番号、T0〜Tm-1を受信し、それは、バイナリ情報、ビットを読み出すために「m×T/ビット」変換器708に供給される。1つのT当たりr個の可能なシンボル遷移状態、T0〜Tm-1が存在する場合、m個の遷移は、rm個の異なる状態を送信できる。N!の差動シグナリングの場合、r=n!-1である。結果的に、遷移T0…Tm-1は、(n!-1)mの異なる状態を有することができるデータを含む。

図8は、シーケンスシンボルとシンボル遷移番号との間の変換を例示する。この変換は、現シーケンスシンボル番号(Cs)に対する前シーケンスシンボル番号(Ps)から、遷移番号(T)に、各遷移をマッピングする。送信デバイスにおいて、シンボル遷移番号は、シーケンスシンボル番号に変換されている。相対的な変換方式が使用されているので、遷移番号は、2つの連続したシーケンスシンボル番号804が同一ではないことを保証する。

T=Ps+1≦Cs

?Cs-(Ps+1)

:Cs-(Ps+1)+6

Cs=Ps+1+T<6

?Ps+1+T

:Ps+1+T-6

T=Ps+1≦Cs

?Cs-(Ps+1)

:Cs-(Ps+1)+n!

Cs=Ps+1+T<n!

?Ps+1+T

:Ps+1+T-n!

図9は、(n=3のワイヤシステムの場合の)未処理の値とシーケンスシンボル番号へとの間の変換を例示している表である。n=3のこの例において、未処理データ値X、Y、およびZの組合せは、1組のシーケンスシンボル番号0〜5のうちの1つにマッピングされてよい。未処理の値X、Y、およびZの組合せ(たとえば、{X、Y、Z})は、未処理シンボルを表す。簡略記号-x、+x、+y、-y、+z、および-zは、3相システム(ここでn=3)の場合の6つの未処理シンボルの各々を表すために、使用される。未処理シンボルはサイクルごとに変化する(すなわち、2つの連続した未処理シンボルは同一ではない)ことが保証されるので、1つの未処理シンボルから次の未処理シンボルへの遷移はクロック信号を抽出するために使用可能である。

図27は、導体、ワイヤ、またはラインA、B、およびC間の差動信号によって定められる状態に基づいて、クロック(タイミング情報)が組み込まれた、送信デバイス2700と受信デバイス2701との間の3本ワイヤ差動シグナリングを例示する。

図10は、様々なノード間の電流フローと同様に、ドライバへの入力および受信機からの出力を示す3本ワイヤ終端ネットワーク1002を例示する。n=3の場合のこのトランスコーディング方式は、ゼロの差動電圧を生じさせ、したがって不正な状態となる、2つのパターン(ZYX)=(000)および(111)を有する。ゼロの差動電圧は不正であり、なぜならそれらが互いに区別できず、したがって、正確な復号を妨げるからである。不正な状態は、符号化のために使用してはならない。残る6つの(正当な)状態は、(ZYX)=(001)、(010)、(100)、(110)、(101)、および(011)である。

図18は、nの階乗(n!)のトランスコーディング方式に一般化した、例示的な送信および受信デバイスを例示しているブロック図であり、ここで、nは使用されるワイヤ(たとえば、導体、ライン)の数であり、mはシンボル/グループであり、wは、直並列変換器(DES)1806および並直列変換器(SER)1826ブロックのビット幅である。この例では、受信デバイス1802は、DESブロック1806を含む復号器1804を含んでよい。復号器1804は、図6で例示され、説明されるものと同様に動作してよい。加えて、送信デバイス1822は、SERブロック1826を含む符号化器1824を含んでよい。符号化器1824は、図5で例示され、説明されるものと同様に動作してよい。

マルチワイヤシグナリング符号化を実行するための符号化回路が提供される。そのような符号化回路の様々な例およびそこで実行される機能は、図4(送信機402)、図5、図7、図8、図9、図13、図14、図15(符号化器1504)、図16(符号化器1604)、および図18(符号化器1824)において、見出される。ビット/遷移番号変換器は、一連のデータビットを複数のm個の遷移番号に変換するために機能する。遷移番号/シーケンス番号変換器は、各遷移番号を1組のシーケンス番号の中からのあるシーケンス番号に変換するために機能する。1組のシーケンス番号の中からのあるシーケンス番号に各遷移番号を変換することは、複数の遷移番号を1つのシーケンス番号に変換することを含んでよい。シーケンス番号/未処理シンボル変換器は、シーケンス番号を未処理シンボルに変換するために機能する。

マルチワイヤシグナリング復号を実行するための復号回路が提供される。そのような復号回路およびそこで実行される機能の様々な例は、図4(受信機402)、図6、図7、図8、図9、図13、図14、図17(復号器1704)、および図18(復号器1804)において見出される。複数の差動受信機は、複数のn本のワイヤにわたって拡散された未処理シンボルを受信するために機能してよい。様々な例において、複数のn本のワイヤは、3または4本以上である。

使用されるワイヤの数および選択されるシンボル/グループに応じて、異なる利用割合が達成されるだろう。「利用率」は、グループ当たりのビット数が送信できる効率を意味し得る。これらの例において、「利用率」は、送信されるグループ当たりのビットの整数と、所与の数の導体およびグループ当たりのシンボルについて送信可能な、グループ当たりのビットの理論的な数との間の割合として表されてよい。

104 受信機

106 四面体終端ネットワーク

107 物理ワイヤ

108 クロックチャネル

110 符号化器

112 送信回路

114 受信回路

116 復号器

118 並直列変換器

120 複数のドライバ

122 複数の受信機

124 直並列変換器

202 送信機

204 受信機

206 四面体終端ネットワーク

208a ドライバ

208b 受信機

210 符号化器

212 送信回路

214 受信回路

216 復号器

302 送信デバイス

304 受信デバイス

306 符号化/復号方式

308 位相ロックループ

318 並直列変換器

324 直並列変換器

326 クロック信号

328 クロック信号

402 送信デバイス

404 受信デバイス

406 終端ネットワーク

408 符号化器

410 並直列変換器モジュール

410 直並列変換器モジュール

412 復号器

418 クロックデータ再生回路

426 クロック信号

428 クロック信号

502 ビット/遷移シンボル変換器

504 遷移シンボル/シーケンスシンボル変換器

506 シーケンスシンボル/未処理シンボル変換器

508 ドライバ

602 シンボル遷移/ビット変換器

604 シーケンスシンボル/遷移シンボル変換器

606 未処理シンボル/シーケンスシンボル変換器

608 受信機

702 送信機

704 受信機

706 「ビット/m×T」変換器

708 「m×T/ビット」変換器

802 表

804 シーケンスシンボル番号

1002 3本ワイヤ終端ネットワーク

1102 4本ワイヤ終端ネットワーク

1104 様々なノード間の電流フロー

1106 表

1107 ドライバ/受け手

1202 送信機/受信機トランスコーディング方式

1502 送信機

1504 符号化器

1506 ビット/シンボル遷移番号変換器

1602 送信機

1604 符号化器

1606 ビット/シンボル遷移番号変換器

1608 シンボル遷移番号/シーケンスシンボル番号変換器

1610 シーケンスシンボル番号/未処理シンボル変換器

1612 ドライバ

1702 受信デバイス

1703 受信機

1704 復号器

1706 未処理シンボル/シーケンスシンボル番号変換器

1708 シーケンスシンボル番号/シンボル遷移番号変換器

1710 シンボル遷移番号/未処理ビット変換器

1802 受信機

1804 復号器

1806 直並列変換器

1822 送信機

1824 符号化器

1826 並直列変換器

1912 受信機

1914 直並列変換器

2700 送信デバイス

2701 受信デバイス

2703 状態図

2704 線図

2705 線図

2708 マルチラインバス

2710 3ポート受信機

2712 複数の受信機

2714 第1の差動信号

2716 第2の差動信号

2718 第3の差動信号

2720 復号回路

2802 表

Claims (41)

- マルチワイヤシグナリング符号化を実行するための方法であって、

一連のデータビットを複数のm個の遷移番号に変換するステップと、

1組のシーケンス番号の中からのあるシーケンス番号に各遷移番号を変換するステップと、

前記シーケンス番号を未処理シンボルに変換するステップと、

複数の差動ドライバを介して、かつ複数のn本のワイヤにわたって拡散されて、前記未処理シンボルを送信するステップと、を含み、遷移番号からシーケンス番号への前記変換は2つの連続した未処理シンボルが同一でないことを保証するので、クロック信号は未処理シンボルの前記送信に効果的に組み込まれる、方法。 - 1組のシーケンス番号の中からのあるシーケンス番号に各遷移番号を変換するステップが、

複数の遷移番号をシーケンス番号に変換するステップを含む、請求項1に記載の方法。 - 前記シーケンス番号を未処理シンボルに変換するステップが、

前記シーケンス番号を複数の未処理シンボルに変換するステップを含む、請求項1に記載の方法。 - 前記複数のn本のワイヤが、以上である、請求項1に記載の方法。

- 前記複数のn本のワイヤが、以上である、請求項1に記載の方法。

- 前記未処理シンボルは、前記複数のn本のワイヤのすべての対にかけられるゼロでない差動電圧を有することが保証される、請求項1に記載の方法。

- 前記n本のワイヤの対にかけられるnの階乗の差動信号について、rmの可能な異なる状態が前記遷移番号によって表され、ここでrはn!-1である、請求項1に記載の方法。

- 前記シーケンス番号が、直前のシーケンスシンボル番号からの遷移に基づいて、遷移番号から選択される、請求項1に記載の方法。

- 前記クロック信号を使用して、未処理シンボルの送信を同期させるステップ

をさらに含む、請求項1に記載の方法。 - マルチワイヤシグナリング符号化を実行するための符号化回路であって、

一連のデータビットを複数のm個の遷移番号に変換するためのビット/遷移番号変換器と、

各遷移番号を1組のシーケンス番号の中からのあるシーケンス番号に変換するための遷移番号/シーケンス番号変換器と、

前記シーケンス番号を未処理シンボルに変換するためのシーケンス番号/未処理シンボル変換器と、

複数のn本のワイヤにわたって拡散された、前記未処理シンボルを送信するための複数の差動ドライバと、を含み、遷移番号からシーケンス番号への前記変換は2つの連続した未処理シンボルが同一でないことを保証するので、クロック信号は未処理シンボルの前記送信に効果的に組み込まれる、符号化回路。 - 1組のシーケンス番号の中からのあるシーケンス番号に各遷移番号を変換するステップが、複数の遷移番号をシーケンス番号に変換するステップを含む、請求項10に記載の符号化回路。

- 前記シーケンス番号を未処理シンボルに変換するステップが、前記シーケンス番号を複数の未処理シンボルに変換するステップを含む、請求項10に記載の符号化回路。

- 前記複数のn本のワイヤが、3本以上である、請求項10に記載の符号化回路。

- 前記複数のn本のワイヤが、4本以上である、請求項10に記載の符号化回路。

- 前記未処理シンボルは、前記n本のワイヤのすべての対にかけられるゼロでない差動電圧を有することが保証される、請求項10に記載の符号化回路。

- 前記n本のワイヤの対にかけられるnの階乗の差動信号について、rmの可能な異なる状態が前記遷移番号によって表され、ここでrはn!-1である、請求項10に記載の符号化回路。

- 前記複数の差動ドライバはnC2に等しく、ここでnC2=n(n-1)/2である、請求項10に記載の符号化回路。

- 前記複数の差動ドライバがn個に等しい、請求項10に記載の符号化回路。

- 前記シーケンス番号が、直前のシーケンスシンボル番号からの遷移に基づいて、前記遷移番号から選択される、請求項10に記載の符号化回路。

- 一連のデータビットを複数のm個の遷移番号に変換するための手段と、

各遷移番号を1組のシーケンス番号の中からのあるシーケンス番号に変換するための手段と、

前記シーケンス番号を未処理シンボルに変換するための手段と、

複数の差動ドライバを介して、かつ複数のn本のワイヤにわたって拡散されて、前記未処理シンボルを送信するための手段と、を含み、遷移番号からシーケンス番号への前記変換は2つの連続した未処理シンボルが同一でないことを保証するので、クロック信号は未処理シンボルの送信に効果的に組み込まれる、符号化回路。 - マルチワイヤシグナリング復号を実行するための方法であって、

複数の差動受信機を介して、複数のn本のワイヤにわたって拡散された、未処理シンボルを受信するステップと、

前記未処理シンボルを1組のシーケンス番号の中からのあるシーケンス番号に変換するステップと、

各シーケンス番号を遷移番号に変換するステップと、

複数の遷移番号を一連のデータビットに変換するステップと、

クロック信号を未処理シンボルの前記受信から抽出するステップと

を含む方法。 - 各シーケンス番号を遷移番号に変換するステップが、

シーケンス番号を複数の遷移番号に変換するステップを含む、請求項21に記載の方法。 - 前記未処理シンボルを1組のシーケンス番号の中からのあるシーケンス番号に変換するステップが、

複数の未処理シンボルをシーケンス番号に変換するステップを含む、請求項21に記載の方法。 - 前記複数のn本のワイヤが、以上である、請求項21に記載の方法。

- 前記複数のn本のワイヤが、以上である、請求項21に記載の方法。

- 前記未処理シンボルは、前記n本のワイヤのすべての対にかけられるゼロでない差動電圧を有することが保証される、請求項21に記載の方法。

- 前記n個のドライバにわたるnの階乗の差動シグナリングについて、rmの可能な異なる状態が前記遷移番号によって表され、ここでrはn!-1である、請求項21に記載の方法。

- 前記遷移番号が、前記シーケンス番号から選択され、直前のシーケンスシンボル番号に基づく、請求項21に記載の方法。

- 前記クロック信号を使用して、未処理シンボルの受信を同期させるステップ

をさらに含む、請求項21に記載の方法。 - マルチワイヤシグナリング復号を実行するための復号回路であって、

複数のn本のワイヤにわたって拡散された、未処理シンボルを受信する、複数の差動受信機と、

前記未処理シンボルを1組のシーケンス番号の中からのあるシーケンス番号に変換するための、未処理シンボル/シーケンス番号変換器と、

各シーケンス番号を遷移番号に変換するための、シーケンス番号/遷移番号変換器と、

複数の遷移番号を一連のデータビットに変換するための、遷移番号/ビット変換器と、

クロック信号を未処理シンボルの前記受信から抽出するための、クロックデータ再生回路と

を含む復号回路。 - 各シーケンス番号を遷移番号に変換するステップが、シーケンス番号を複数の遷移番号に変換するステップを含む、請求項30に記載の復号回路。

- 前記未処理シンボルを1組のシーケンス番号の中からのあるシーケンス番号に変換するステップが、複数の未処理シンボルをシーケンス番号に変換するステップを含む、請求項30に記載の復号回路。

- 前記複数のn本のワイヤが、3本以上である、請求項30に記載の復号回路。

- 前記複数のn本のワイヤが、4本以上である、請求項30に記載の復号回路。

- 前記未処理シンボルは、前記複数のn本のワイヤのすべての対にかけられるゼロでない差動電圧を有することが保証される、請求項30に記載の復号回路。

- 前記n個のドライバにわたるnの階乗の差動シグナリングについて、rmの可能な異なる状態が前記遷移番号によって表され、ここでrはn!-1である、請求項30に記載の復号回路。

- 前記複数の差動ドライバはnC2に等しく、ここでnC2=n(n-1)/2である、請求項30に記載の復号回路。

- 前記複数の差動ドライバがn個に等しい、請求項30に記載の復号回路。

- 前記遷移番号が、前記シーケンス番号から選択され、直前のシーケンスシンボル番号に基づく、請求項30に記載の復号回路。

- 未処理シンボル受信は、前記クロック信号を使用して同期させる、請求項30に記載の復号回路。

- マルチワイヤシグナリング復号を実行するための復号回路であって、

複数の差動受信機を介して、複数のn本のワイヤにわたって拡散された、未処理シンボルを受信するための手段と、

前記未処理シンボルを1組のシーケンスシンボル番号の中からのあるシーケンスシンボル番号に変換するための手段と、

各シーケンスシンボル番号を遷移番号に変換するための手段と、

複数の遷移番号を一連のデータビットに変換するための手段と、

クロック信号を未処理シンボルの前記受信から抽出するための手段と

を含む復号回路。

Applications Claiming Priority (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361774408P | 2013-03-07 | 2013-03-07 | |

| US201361774247P | 2013-03-07 | 2013-03-07 | |

| US61/774,408 | 2013-03-07 | ||

| US61/774,247 | 2013-03-07 | ||

| US201361778768P | 2013-03-13 | 2013-03-13 | |

| US61/778,768 | 2013-03-13 | ||

| US14/199,898 US9337997B2 (en) | 2013-03-07 | 2014-03-06 | Transcoding method for multi-wire signaling that embeds clock information in transition of signal state |

| US14/199,898 | 2014-03-06 | ||

| PCT/US2014/021979 WO2014138644A1 (en) | 2013-03-07 | 2014-03-07 | Transcoding method for multi-wire signaling that embeds clock information in transition of signal state |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016514430A true JP2016514430A (ja) | 2016-05-19 |

| JP2016514430A5 JP2016514430A5 (ja) | 2017-03-30 |

Family

ID=51487808

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015561728A Active JP6461018B2 (ja) | 2013-03-07 | 2014-03-07 | 状態周期ごとに状態を変えるとともにデータのレーン間スキューおよびデータ状態遷移グリッチに |

| JP2015561729A Ceased JP2016514430A (ja) | 2013-03-07 | 2014-03-07 | クロック情報を信号状態の遷移に組み込むマルチワイヤシグナリングのためのトランスコーディング方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015561728A Active JP6461018B2 (ja) | 2013-03-07 | 2014-03-07 | 状態周期ごとに状態を変えるとともにデータのレーン間スキューおよびデータ状態遷移グリッチに |

Country Status (8)

| Country | Link |

|---|---|

| US (3) | US9363071B2 (ja) |

| EP (2) | EP2965459B1 (ja) |

| JP (2) | JP6461018B2 (ja) |

| KR (2) | KR102205823B1 (ja) |

| CN (2) | CN105009535B (ja) |

| ES (1) | ES2705045T3 (ja) |

| HU (1) | HUE042572T2 (ja) |

| WO (2) | WO2014138644A1 (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9231790B2 (en) | 2007-03-02 | 2016-01-05 | Qualcomm Incorporated | N-phase phase and polarity encoded serial interface |

| US9711041B2 (en) | 2012-03-16 | 2017-07-18 | Qualcomm Incorporated | N-phase polarity data transfer |

| US8064535B2 (en) * | 2007-03-02 | 2011-11-22 | Qualcomm Incorporated | Three phase and polarity encoded serial interface |

| US9374216B2 (en) | 2013-03-20 | 2016-06-21 | Qualcomm Incorporated | Multi-wire open-drain link with data symbol transition based clocking |

| US9178690B2 (en) * | 2013-10-03 | 2015-11-03 | Qualcomm Incorporated | N factorial dual data rate clock and data recovery |

| US9313058B2 (en) | 2013-03-07 | 2016-04-12 | Qualcomm Incorporated | Compact and fast N-factorial single data rate clock and data recovery circuits |

| US9363071B2 (en) | 2013-03-07 | 2016-06-07 | Qualcomm Incorporated | Circuit to recover a clock signal from multiple wire data signals that changes state every state cycle and is immune to data inter-lane skew as well as data state transition glitches |

| US9118457B2 (en) * | 2013-03-15 | 2015-08-25 | Qualcomm Incorporated | Multi-wire single-ended push-pull link with data symbol transition based clocking |

| EP2816765B1 (en) * | 2013-06-17 | 2016-10-12 | ST-Ericsson SA | Three-wire three-level digital interface |

| US9735948B2 (en) | 2013-10-03 | 2017-08-15 | Qualcomm Incorporated | Multi-lane N-factorial (N!) and other multi-wire communication systems |

| US9203599B2 (en) | 2014-04-10 | 2015-12-01 | Qualcomm Incorporated | Multi-lane N-factorial (N!) and other multi-wire communication systems |

| US9755818B2 (en) | 2013-10-03 | 2017-09-05 | Qualcomm Incorporated | Method to enhance MIPI D-PHY link rate with minimal PHY changes and no protocol changes |

| US9426082B2 (en) * | 2014-01-03 | 2016-08-23 | Qualcomm Incorporated | Low-voltage differential signaling or 2-wire differential link with symbol transition clocking |

| CN106063181B (zh) * | 2014-03-06 | 2018-03-13 | 高通股份有限公司 | 接收机电路和在接收机电路上操作的方法 |

| US9246666B2 (en) * | 2014-03-27 | 2016-01-26 | Intel Corporation | Skew tolerant clock recovery architecture |

| TWI690177B (zh) | 2014-11-05 | 2020-04-01 | 日商新力股份有限公司 | 傳送裝置、傳送方法及通信系統 |

| US9621332B2 (en) | 2015-04-13 | 2017-04-11 | Qualcomm Incorporated | Clock and data recovery for pulse based multi-wire link |

| US9812057B2 (en) | 2015-08-05 | 2017-11-07 | Qualcomm Incorporated | Termination circuit to reduce attenuation of signal between signal producing circuit and display device |

| WO2017062132A1 (en) * | 2015-10-05 | 2017-04-13 | Qualcomm Incorporated | Multi-lane n-factorial encoded and other multi-wire communication systems |

| US10157161B2 (en) * | 2015-10-16 | 2018-12-18 | Qualcomm Incorporated | Conditional embedding of dynamically shielded information on a bus |

| US9819523B2 (en) * | 2016-03-09 | 2017-11-14 | Qualcomm Incorporated | Intelligent equalization for a three-transmitter multi-phase system |

| US9742597B1 (en) * | 2016-03-29 | 2017-08-22 | Xilinx, Inc. | Decision feedback equalizer |

| US10705894B2 (en) | 2016-05-30 | 2020-07-07 | Samsung Electronics Co., Ltd. | Electronic device for authenticating application and operating method thereof |

| KR101825301B1 (ko) * | 2016-08-22 | 2018-02-02 | 한양대학교 산학협력단 | 신호 전송 장치 및 방법과, 신호 수신 장치 |

| CN106385251A (zh) * | 2016-09-14 | 2017-02-08 | 豪威科技(上海)有限公司 | 时钟数据恢复电路 |

| KR20180061560A (ko) | 2016-11-29 | 2018-06-08 | 삼성전자주식회사 | 통신 환경에 의존하여 지연을 조절하는 전자 회로 |

| EP3634831A4 (en) | 2017-05-17 | 2021-03-10 | Illa Designs, LLC | CAR SEAT BASE |

| KR101985082B1 (ko) * | 2017-07-17 | 2019-05-31 | 숭실대학교산학협력단 | 위상 고정 루프 회로를 이용하지 않는 순수 디지털 클록 데이터 복원 장치 |

| KR102223031B1 (ko) * | 2019-03-20 | 2021-03-04 | 삼성전자주식회사 | 향상된 브레이드 클락 시그널링을 이용한 차동 신호 처리장치 |

| CN110134178B (zh) * | 2019-04-29 | 2023-04-07 | 中山大学 | 一种无线时钟树、方法和电路 |

| US11095425B2 (en) | 2019-10-25 | 2021-08-17 | Qualcomm Incorporated | Small loop delay clock and data recovery block for high-speed next generation C-PHY |

| US11687428B2 (en) | 2021-01-20 | 2023-06-27 | Stmicroelectronics International N.V. | Glitch suppression apparatus and method |

| KR102265187B1 (ko) * | 2021-02-08 | 2021-06-16 | 슈가스 주식회사 | 클럭 복구 회로 |

| WO2023287437A1 (en) * | 2021-07-16 | 2023-01-19 | Lattice Semiconductor Corporation | Communication systems and methods |

| CN113810319B (zh) * | 2021-11-17 | 2022-02-08 | 伟恩测试技术(武汉)有限公司 | 时钟数据发送电路、接收电路、恢复电路和方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04230147A (ja) * | 1990-05-21 | 1992-08-19 | Philips Gloeilampenfab:Nv | 多重レベルの差動信号伝送を提供するデータ伝送システムおよび装置 |

| JP3360861B2 (ja) * | 1993-03-02 | 2003-01-07 | 株式会社ソニー木原研究所 | シリアルディジタルデータの伝送方法及び伝送装置 |

| US6556628B1 (en) * | 1999-04-29 | 2003-04-29 | The University Of North Carolina At Chapel Hill | Methods and systems for transmitting and receiving differential signals over a plurality of conductors |

Family Cites Families (163)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4280221A (en) | 1979-05-31 | 1981-07-21 | The Boeing Company | Digital data communication system |

| DE3329773A1 (de) | 1983-08-18 | 1985-02-28 | Siemens AG, 1000 Berlin und 8000 München | Verfahren und anordnung zur zeitgleichen flankenanpassung mehrerer taktsynchroner datenfluesse |

| US4644547A (en) | 1984-06-28 | 1987-02-17 | Westinghouse Electric Corp. | Digital message format for two-way communication and control network |

| US4839907A (en) | 1988-02-26 | 1989-06-13 | American Telephone And Telegraph Company, At&T Bell Laboratories | Clock skew correction arrangement |

| US5748043A (en) | 1994-05-03 | 1998-05-05 | Koslov; Vitali Ivanovich | Digital PLL frequency synthesizer |

| JP3349830B2 (ja) | 1994-07-29 | 2002-11-25 | 沖電気工業株式会社 | クロック発生回路 |

| US5493538A (en) | 1994-11-14 | 1996-02-20 | Texas Instruments Incorporated | Minimum pulse width address transition detection circuit |

| US5835498A (en) | 1995-10-05 | 1998-11-10 | Silicon Image, Inc. | System and method for sending multiple data signals over a serial link |

| US5959568A (en) | 1996-06-26 | 1999-09-28 | Par Goverment Systems Corporation | Measuring distance |

| US5859669A (en) | 1996-11-26 | 1999-01-12 | Texas Instruments Incorporated | System for encoding an image control signal onto a pixel clock signal |

| US5862180A (en) * | 1997-02-01 | 1999-01-19 | Heinz; Gary L. | Differential encoding of self-clocking data streams |

| US6028639A (en) | 1997-12-19 | 2000-02-22 | Thomson Consumer Electronics, Inc. | Process and apparatus for converting an MPEG-2 bitstream into SMPTE-259 compatible bitstream |

| US6564269B1 (en) | 1998-09-10 | 2003-05-13 | Silicon Image, Inc. | Bi-directional data transfer using the video blanking period in a digital data stream |

| CA2250538A1 (en) | 1998-10-30 | 2000-04-30 | Mosaid Technologies Incorporated | Duty cycle regulator |

| US6526112B1 (en) | 1999-06-29 | 2003-02-25 | Agilent Technologies, Inc. | System for clock and data recovery for multi-channel parallel data streams |

| US6320406B1 (en) | 1999-10-04 | 2001-11-20 | Texas Instruments Incorporated | Methods and apparatus for a terminated fail-safe circuit |

| JP3425905B2 (ja) | 1999-10-14 | 2003-07-14 | Necエレクトロニクス株式会社 | クロック信号抽出回路及びそれを有するパラレルディジタルインタフェース並びにクロック信号抽出方法及びそれを有するパラレルデータビット信号の同期化方法 |

| US7124221B1 (en) | 1999-10-19 | 2006-10-17 | Rambus Inc. | Low latency multi-level communication interface |

| US6728908B1 (en) | 1999-11-18 | 2004-04-27 | California Institute Of Technology | I2C bus protocol controller with fault tolerance |

| KR100708078B1 (ko) | 2000-05-04 | 2007-04-16 | 삼성전자주식회사 | 디지털 비디오 데이터 전송방법, 수신방법, 전송장치,그리고 수신장치 |

| US6763477B1 (en) * | 2000-07-31 | 2004-07-13 | Hewlett-Packard Development Company, L.P. | Method and apparatus for transmitting and receiving data using a self clocking link protocol |

| US6845131B1 (en) | 2000-10-03 | 2005-01-18 | Spectrum Signal Processing Inc. | Differential signaling power management |

| JP4234337B2 (ja) | 2000-11-17 | 2009-03-04 | テキサス インスツルメンツ インコーポレイテッド | データ伝送システムにおける又は関する改善 |

| KR20020054053A (ko) | 2000-12-27 | 2002-07-06 | 엘지전자 주식회사 | 동기식 전송 모드의 랜덤 패턴을 고려한 프레임 검출 장치및 그 방법 |

| US7158593B2 (en) | 2001-03-16 | 2007-01-02 | Silicon Image, Inc. | Combining a clock signal and a data signal |

| US6624766B1 (en) | 2001-05-09 | 2003-09-23 | Kestrel Solutions, Inc. | Recovery and transmission of return-to-zero formatted data using non-return-to-zero devices |

| US6874097B1 (en) | 2001-06-01 | 2005-03-29 | Maxtor Corporation | Timing skew compensation technique for parallel data channels |

| US7061939B1 (en) | 2001-06-13 | 2006-06-13 | Juniper Networs, Inc. | Source synchronous link with clock recovery and bit skew alignment |

| US6799239B2 (en) | 2001-10-23 | 2004-09-28 | Storage Technology Corporation | Centrally distributed serial bus |

| US7346357B1 (en) | 2001-11-08 | 2008-03-18 | At&T Corp. | Frequency assignment for multi-cell IEEE 802.11 wireless networks |

| US6838712B2 (en) | 2001-11-26 | 2005-01-04 | Micron Technology, Inc. | Per-bit set-up and hold time adjustment for double-data rate synchronous DRAM |

| US7190754B1 (en) | 2001-12-24 | 2007-03-13 | Rambus Inc. | Transceiver with selectable data rate |

| JP2003258844A (ja) | 2002-03-01 | 2003-09-12 | Fujitsu Ltd | インターネットプロトコルネットワークの網終端装置及びその冗長系運転方法 |

| US7167527B1 (en) | 2002-05-02 | 2007-01-23 | Integrated Memory Logic, Inc. | System and method for multi-symbol interfacing |

| DE60211684T2 (de) | 2002-07-22 | 2007-05-10 | Texas Instruments Inc., Dallas | Verfahren und Einrichtung für die parallele Synchronisation von mehreren seriellen Datenströmen |

| US20040028164A1 (en) | 2002-08-07 | 2004-02-12 | Hongtao Jiang | System and method for data transition control in a multirate communication system |

| US8230114B2 (en) | 2002-08-07 | 2012-07-24 | Broadcom Corporation | System and method for implementing a single chip having a multiple sub-layer PHY |

| US6731000B1 (en) | 2002-11-12 | 2004-05-04 | Koninklijke Philips Electronics N.V. | Folded-flex bondwire-less multichip power package |

| JP2006517767A (ja) * | 2003-01-29 | 2006-07-27 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 一定全電流を用いるデータ通信 |

| US7076377B2 (en) | 2003-02-11 | 2006-07-11 | Rambus Inc. | Circuit, apparatus and method for capturing a representation of a waveform from a clock-data recovery (CDR) unit |

| US7397848B2 (en) | 2003-04-09 | 2008-07-08 | Rambus Inc. | Partial response receiver |

| US7986732B2 (en) | 2003-04-10 | 2011-07-26 | Nec Corporation | Moving picture compression/encoding method conversion device and moving picture communication system |

| US7395347B2 (en) | 2003-08-05 | 2008-07-01 | Newisys, Inc, | Communication between and within multi-processor clusters of multi-cluster computer systems |

| US7358869B1 (en) | 2003-08-20 | 2008-04-15 | University Of Pittsburgh | Power efficient, high bandwidth communication using multi-signal-differential channels |

| US7072355B2 (en) | 2003-08-21 | 2006-07-04 | Rambus, Inc. | Periodic interface calibration for high speed communication |

| GB0319756D0 (en) | 2003-08-22 | 2003-09-24 | 4Links Ltd | An alternative data-recovery method for spacewire and improved distribution of timecodes |

| JP2005086662A (ja) | 2003-09-10 | 2005-03-31 | Seiko Epson Corp | 半導体装置 |

| US7668271B2 (en) | 2003-09-30 | 2010-02-23 | Rambus Inc. | Clock-data recovery (“CDR”) circuit, apparatus and method for variable frequency data |

| JP4874113B2 (ja) | 2003-10-22 | 2012-02-15 | エヌエックスピー ビー ヴィ | 伝送媒体によってデータユニットを送り、受信する方法および装置 |

| US7313208B2 (en) | 2003-11-03 | 2007-12-25 | Zenith Electronics Corporation | Pre-equalization for low-cost DTV translators |

| US7463680B2 (en) | 2003-12-16 | 2008-12-09 | California Institute Of Technology | Deterministic jitter equalizer |

| JP2005210695A (ja) | 2003-12-22 | 2005-08-04 | Kawasaki Microelectronics Kk | データ伝送方式およびデータ伝送回路 |

| US7030676B2 (en) | 2003-12-31 | 2006-04-18 | Intel Corporation | Timing circuit for separate positive and negative edge placement in a switching DC-DC converter |

| US20050219083A1 (en) | 2004-03-16 | 2005-10-06 | Boomer James B | Architecture for bidirectional serializers and deserializer |

| US20050207280A1 (en) | 2004-03-16 | 2005-09-22 | Fowler Michael L | Bit clock with embedded word clock boundary |

| DE102004013093B3 (de) | 2004-03-17 | 2005-07-21 | Infineon Technologies Ag | Empfängerschaltung für ein Gegentaktübertragungsverfahren |

| US7102407B2 (en) | 2004-03-31 | 2006-09-05 | Intel Corporation | Programmable clock delay circuit |

| US7821428B2 (en) | 2004-06-03 | 2010-10-26 | Silicon Laboratories Inc. | MCU with integrated voltage isolator and integrated galvanically isolated asynchronous serial data link |

| US7061266B2 (en) | 2004-07-06 | 2006-06-13 | Intel Corporation | Methods and apparatus for improving impedance tolerance of on-die termination elements |

| US6933866B1 (en) | 2004-09-14 | 2005-08-23 | Avid Technology, Inc. | Variable data rate receiver |

| JP4604627B2 (ja) | 2004-09-22 | 2011-01-05 | ソニー株式会社 | エンコーダ装置およびデコーダ装置 |

| KR20060040429A (ko) | 2004-11-05 | 2006-05-10 | 삼성전자주식회사 | 무선-랜을 이용한 디지털 방송 데이터 제공 장치 및 그 방법 |

| US20060123177A1 (en) | 2004-12-02 | 2006-06-08 | Ati Technologies, Inc. | Method and apparatus for transporting and interoperating transition minimized differential signaling over differential serial communication transmitters |

| US7307554B2 (en) | 2004-12-20 | 2007-12-11 | Kawasaki Microelectronics, Inc. | Parallel data transmission method and parallel data transmission system |

| US20060168615A1 (en) | 2005-01-21 | 2006-07-27 | Adimos Inc. | System circuit application and method for wireless transmission of multimedia content from a computing platform |

| US8041845B2 (en) | 2005-02-11 | 2011-10-18 | Mstar Semiconductor, Inc. | Method for detecting digital video interface off-line mode and associated receiver |

| US7787526B2 (en) | 2005-07-12 | 2010-08-31 | Mcgee James Ridenour | Circuits and methods for a multi-differential embedded-clock channel |

| US20070073932A1 (en) | 2005-09-13 | 2007-03-29 | Alcatel | Method and apparatus for a configurable data path interface |

| US8222917B2 (en) | 2005-11-03 | 2012-07-17 | Agate Logic, Inc. | Impedance matching and trimming apparatuses and methods using programmable resistance devices |

| US9544602B2 (en) | 2005-12-30 | 2017-01-10 | Sharp Laboratories Of America, Inc. | Wireless video transmission system |

| US7502953B2 (en) | 2006-01-05 | 2009-03-10 | International Business Machines Corporation | Dynamically adding additional masters onto multi-mastered IIC buses with tunable performance |

| US7844762B2 (en) | 2006-02-24 | 2010-11-30 | Silicon Image, Inc. | Parallel interface bus to communicate video data encoded for serial data links |

| US7746937B2 (en) | 2006-04-14 | 2010-06-29 | Formfactor, Inc. | Efficient wired interface for differential signals |

| JP4129050B2 (ja) | 2006-04-27 | 2008-07-30 | 松下電器産業株式会社 | 多重差動伝送システム |

| CN101356787B (zh) | 2006-04-27 | 2011-11-16 | 松下电器产业株式会社 | 多路复用差动传送系统 |

| US8000412B1 (en) | 2006-06-01 | 2011-08-16 | Netlogic Microsystems, Inc. | Low power serial link |

| JP4783245B2 (ja) | 2006-09-01 | 2011-09-28 | 株式会社日立製作所 | 送受信機、送信機、ならびに受信機 |

| JP4940846B2 (ja) | 2006-09-13 | 2012-05-30 | 富士通セミコンダクター株式会社 | 通信試験回路及び通信インタフェース回路並びに通信試験方法 |

| CN101523783B (zh) | 2006-09-29 | 2012-12-12 | 株式会社Ntt都科摩 | 发送装置以及发送帧构成方法 |

| US9319143B2 (en) | 2006-10-13 | 2016-04-19 | Menara Networks, Inc. | 40G/100G/200G/400G pluggable optical transceivers with advanced functionality |

| US7667500B1 (en) | 2006-11-14 | 2010-02-23 | Xilinx, Inc. | Glitch-suppressor circuits and methods |

| US7881415B2 (en) | 2006-12-29 | 2011-02-01 | Atmel Corporation | Communication protocol method and apparatus for a single wire device |

| US9711041B2 (en) | 2012-03-16 | 2017-07-18 | Qualcomm Incorporated | N-phase polarity data transfer |

| US8064535B2 (en) * | 2007-03-02 | 2011-11-22 | Qualcomm Incorporated | Three phase and polarity encoded serial interface |

| US7541838B2 (en) | 2007-03-27 | 2009-06-02 | Intel Corporation | Transmitter swing control circuit and method |

| JP2008242884A (ja) | 2007-03-28 | 2008-10-09 | Matsushita Electric Ind Co Ltd | I2cバス制御回路 |

| WO2008130878A2 (en) | 2007-04-19 | 2008-10-30 | Rambus Inc. | Techniques for improved timing control of memory devices |

| JP5180634B2 (ja) | 2007-04-24 | 2013-04-10 | パナソニック株式会社 | 差動伝送線路 |

| EP2156555A4 (en) | 2007-06-05 | 2013-07-24 | Rambus Inc | TECHNIQUES FOR MULTIPLE CODING WITH AN EMBEDDED CLOCK |

| JP2009021978A (ja) | 2007-06-11 | 2009-01-29 | Panasonic Corp | 伝送ケーブル |

| US20090037006A1 (en) | 2007-08-03 | 2009-02-05 | Transtechnology, Inc. | Device, medium, data signal, and method for obtaining audio attribute data |

| JP2009077188A (ja) | 2007-09-21 | 2009-04-09 | Hitachi Ltd | 半導体装置 |

| US8159376B2 (en) | 2007-12-07 | 2012-04-17 | Rambus Inc. | Encoding and decoding techniques for bandwidth-efficient communication |

| ATE545091T1 (de) | 2007-12-19 | 2012-02-15 | Rambus Inc | Asymmetrische kommunikation bei gemeinsamen verbindungen |

| US7962681B2 (en) * | 2008-01-09 | 2011-06-14 | Qualcomm Incorporated | System and method of conditional control of latch circuit devices |

| GB2456517A (en) | 2008-01-15 | 2009-07-22 | Andrzej Radecki | Serial data communication circuit for use with transmission lines using both data and clock to enable recovery of data synchronously |

| US7808418B2 (en) * | 2008-03-03 | 2010-10-05 | Qualcomm Incorporated | High-speed time-to-digital converter |

| US8848810B2 (en) | 2008-03-05 | 2014-09-30 | Qualcomm Incorporated | Multiple transmitter system and method |

| WO2009111175A1 (en) | 2008-03-06 | 2009-09-11 | Rambus Inc. | Error detection and offset cancellation during multi-wire communication |

| US20090243681A1 (en) | 2008-03-26 | 2009-10-01 | Rambus Inc. | Embedded Source-Synchronous Clock Signals |

| US9030976B2 (en) | 2008-03-27 | 2015-05-12 | Silicon Image, Inc. | Bi-directional digital interface for video and audio (DIVA) |

| US8184651B2 (en) | 2008-04-09 | 2012-05-22 | Altera Corporation | PLD architecture optimized for 10G Ethernet physical layer solution |

| US20100027607A1 (en) | 2008-06-10 | 2010-02-04 | Tad Kwasniewski | Apparatus for time-domain pre-emphasis and time-domain equalization and associated methods |

| US8081705B2 (en) | 2008-06-27 | 2011-12-20 | Crestron Electronics Inc. | Digital video physical layer using a multi-level data code |

| US7710144B2 (en) | 2008-07-01 | 2010-05-04 | International Business Machines Corporation | Controlling for variable impedance and voltage in a memory system |

| US8094766B2 (en) | 2008-07-02 | 2012-01-10 | Teradyne, Inc. | Tracker circuit and method for automated test equipment systems |

| US20100040169A1 (en) | 2008-08-15 | 2010-02-18 | Rambus Inc. | Coding methods and systems for improved error margins |

| US8184760B2 (en) | 2008-09-02 | 2012-05-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Adaptive elastic buffer for communications |

| US8886987B2 (en) | 2008-09-19 | 2014-11-11 | Advantest (Singapore) Pte Ltd | Data processing unit and a method of processing data |

| JP4645717B2 (ja) | 2008-09-26 | 2011-03-09 | ソニー株式会社 | インタフェース回路および映像装置 |

| FR2937203B1 (fr) | 2008-10-13 | 2011-03-18 | Sagem Defense Securite | Dispositif de reconstitution de l'horloge d'un signal nrz et systeme de transmissoin associe. |

| KR101061989B1 (ko) | 2008-12-03 | 2011-09-05 | (주)신창코넥타 | 스페이서 및 그 스페이서를 포함하는 차량용 클럭 스프링 장치 |

| WO2010077564A1 (en) | 2008-12-08 | 2010-07-08 | Analog Devices Inc. | Multimedia switching over wired or wireless connections in a distributed environment |

| US20100183053A1 (en) | 2009-01-20 | 2010-07-22 | Tran Duke H | System and apparatus for data transmission |

| CN102396170A (zh) | 2009-04-16 | 2012-03-28 | 日本电气株式会社 | 检测并行信号之间时滞的方法和系统 |

| TWI398151B (zh) | 2009-04-17 | 2013-06-01 | Univ Nat Taiwan | 資料時脈回復電路 |

| US7791370B1 (en) | 2009-05-21 | 2010-09-07 | Altera Corporation | Clock distribution techniques for channels |

| KR101079603B1 (ko) | 2009-08-11 | 2011-11-03 | 주식회사 티엘아이 | 3레벨 전압을 이용하는 차동 데이터 송수신 장치 및 차동 데이터 송수신 방법 |

| US8621128B2 (en) | 2009-12-04 | 2013-12-31 | St-Ericsson Sa | Methods and systems for reliable link startup |

| US8606184B1 (en) | 2009-12-08 | 2013-12-10 | Qualcomm Incorporated | Coexistence message processing mechanism for wireless devices |

| US8077063B2 (en) * | 2010-01-18 | 2011-12-13 | Freescale Semiconductor, Inc. | Method and system for determining bit stream zone statistics |

| JP2011172156A (ja) | 2010-02-22 | 2011-09-01 | Sony Corp | コンテンツ再生システム、コンテンツ受信装置、音声再生装置、コンテンツ再生方法およびプログラム |

| JP5537192B2 (ja) | 2010-03-04 | 2014-07-02 | スパンション エルエルシー | 受信装置及びゲイン設定方法 |

| US8649445B2 (en) | 2011-02-17 | 2014-02-11 | École Polytechnique Fédérale De Lausanne (Epfl) | Methods and systems for noise resilient, pin-efficient and low power communications with sparse signaling codes |

| JP2012029214A (ja) | 2010-07-27 | 2012-02-09 | Rohm Co Ltd | インタフェース回路およびそれを用いた電子機器 |

| JP5602662B2 (ja) | 2011-03-02 | 2014-10-08 | ルネサスエレクトロニクス株式会社 | 信号配線システム及びジッタ抑制回路 |

| US8294502B2 (en) | 2011-03-04 | 2012-10-23 | Altera Corporation | Delay circuitry |

| US8659957B2 (en) | 2011-03-07 | 2014-02-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of driving semiconductor device |

| TWI459774B (zh) | 2011-04-29 | 2014-11-01 | Ind Tech Res Inst | 非同步主從式串列通訊系統及應用其之資料傳輸方法與控制模組 |

| US20120307886A1 (en) | 2011-05-31 | 2012-12-06 | Broadcom Corporation | Adaptive Video Encoding Based on Predicted Wireless Channel Conditions |

| US8698558B2 (en) | 2011-06-23 | 2014-04-15 | Qualcomm Incorporated | Low-voltage power-efficient envelope tracker |

| JP2013021445A (ja) * | 2011-07-08 | 2013-01-31 | Kawasaki Microelectronics Inc | 遷移検出回路 |

| US8599913B1 (en) | 2011-08-01 | 2013-12-03 | Pmc-Sierra Us, Inc. | Data regeneration apparatus and method for PCI express |

| US9219560B2 (en) | 2011-10-25 | 2015-12-22 | Cavium, Inc. | Multi-protocol SerDes PHY apparatus |

| US8687752B2 (en) | 2011-11-01 | 2014-04-01 | Qualcomm Incorporated | Method and apparatus for receiver adaptive phase clocked low power serial link |

| JP2013110554A (ja) | 2011-11-21 | 2013-06-06 | Panasonic Corp | 送信装置、受信装置及びシリアル伝送システム |

| US20140168010A1 (en) | 2011-12-22 | 2014-06-19 | Farrokh Mohamadi | Extended range, high data rate, point-to-point crosslink placed on fixed or mobile elevated platforms |

| US9838226B2 (en) | 2012-01-27 | 2017-12-05 | Apple Inc. | Methods and apparatus for the intelligent scrambling of control symbols |

| US9020418B2 (en) | 2012-02-29 | 2015-04-28 | Fairchild Semiconductor Corporation | Methods and apparatus related to a repeater |

| US8959268B2 (en) | 2012-03-09 | 2015-02-17 | Canon Kabushiki Kaisha | Information processing apparatus, serial communication system, method of initialization of communication therefor and serial communication apparatus |

| US9071407B2 (en) | 2012-05-02 | 2015-06-30 | Ramnus Inc. | Receiver clock test circuitry and related methods and apparatuses |

| US8446903B1 (en) | 2012-05-22 | 2013-05-21 | Intel Corporation | Providing a load/store communication protocol with a low power physical unit |

| US8996740B2 (en) | 2012-06-29 | 2015-03-31 | Qualcomm Incorporated | N-phase polarity output pin mode multiplexer |

| US9179117B2 (en) | 2012-07-02 | 2015-11-03 | Kabushiki Kaisha Toshiba | Image processing apparatus |

| US8686754B2 (en) | 2012-07-05 | 2014-04-01 | Stmicroelectronics International N.V. | Configurable lane architecture in source synchronous systems |

| US8934854B2 (en) | 2012-08-29 | 2015-01-13 | Crestcom, Inc. | Transmitter with peak-tracking PAPR reduction and method therefor |

| KR101984902B1 (ko) | 2012-09-14 | 2019-05-31 | 삼성전자 주식회사 | 단방향의 리턴 클락 신호를 사용하는 임베디드 멀티미디어 카드, 이를 제어하는 호스트, 및 이들을 포함하는 임베디드 멀티미디어 카드 시스템의 동작 방법 |

| US9244872B2 (en) | 2012-12-21 | 2016-01-26 | Ati Technologies Ulc | Configurable communications controller |

| US9235540B1 (en) | 2013-03-01 | 2016-01-12 | Altera Corporation | Flexible high speed forward error correction (FEC) physical medium attachment (PMA) and physical coding sublayer (PCS) connection system |

| US9374216B2 (en) | 2013-03-20 | 2016-06-21 | Qualcomm Incorporated | Multi-wire open-drain link with data symbol transition based clocking |

| US9071220B2 (en) | 2013-03-07 | 2015-06-30 | Qualcomm Incorporated | Efficient N-factorial differential signaling termination network |

| US9178690B2 (en) | 2013-10-03 | 2015-11-03 | Qualcomm Incorporated | N factorial dual data rate clock and data recovery |

| US9313058B2 (en) | 2013-03-07 | 2016-04-12 | Qualcomm Incorporated | Compact and fast N-factorial single data rate clock and data recovery circuits |

| US9363071B2 (en) | 2013-03-07 | 2016-06-07 | Qualcomm Incorporated | Circuit to recover a clock signal from multiple wire data signals that changes state every state cycle and is immune to data inter-lane skew as well as data state transition glitches |

| US9118457B2 (en) | 2013-03-15 | 2015-08-25 | Qualcomm Incorporated | Multi-wire single-ended push-pull link with data symbol transition based clocking |

| US9369237B2 (en) * | 2013-08-08 | 2016-06-14 | Qualcomm Incorporated | Run-length detection and correction |

| US9735948B2 (en) | 2013-10-03 | 2017-08-15 | Qualcomm Incorporated | Multi-lane N-factorial (N!) and other multi-wire communication systems |

| US9203599B2 (en) | 2014-04-10 | 2015-12-01 | Qualcomm Incorporated | Multi-lane N-factorial (N!) and other multi-wire communication systems |

| US9755818B2 (en) | 2013-10-03 | 2017-09-05 | Qualcomm Incorporated | Method to enhance MIPI D-PHY link rate with minimal PHY changes and no protocol changes |

| US9215063B2 (en) | 2013-10-09 | 2015-12-15 | Qualcomm Incorporated | Specifying a 3-phase or N-phase eye pattern |

| US9231527B2 (en) | 2013-11-22 | 2016-01-05 | Qualcomm Incorporated | Circuits and methods for power amplification with extended high efficiency |

| US20150220472A1 (en) | 2014-02-05 | 2015-08-06 | Qualcomm Incorporated | Increasing throughput on multi-wire and multi-lane interfaces |

| KR101668858B1 (ko) | 2014-04-28 | 2016-10-24 | 주식회사 이타기술 | 다채널 비디오 스트림 전송 방법, 그리고 이를 이용한 관제 시스템 |

-

2014

- 2014-03-06 US US14/199,322 patent/US9363071B2/en active Active

- 2014-03-06 US US14/199,898 patent/US9337997B2/en active Active

- 2014-03-07 KR KR1020157026568A patent/KR102205823B1/ko active IP Right Grant

- 2014-03-07 EP EP14712537.1A patent/EP2965459B1/en active Active

- 2014-03-07 JP JP2015561728A patent/JP6461018B2/ja active Active

- 2014-03-07 HU HUE14712537A patent/HUE042572T2/hu unknown

- 2014-03-07 ES ES14712537T patent/ES2705045T3/es active Active

- 2014-03-07 WO PCT/US2014/021979 patent/WO2014138644A1/en active Application Filing

- 2014-03-07 CN CN201480012199.8A patent/CN105009535B/zh not_active Expired - Fee Related

- 2014-03-07 WO PCT/US2014/021958 patent/WO2014138640A1/en active Application Filing

- 2014-03-07 KR KR1020157027168A patent/KR20150121724A/ko not_active Application Discontinuation

- 2014-03-07 JP JP2015561729A patent/JP2016514430A/ja not_active Ceased

- 2014-03-07 EP EP14715752.3A patent/EP2965482A1/en not_active Withdrawn

- 2014-03-07 CN CN201480012389.XA patent/CN105027490B/zh active Active

-

2016

- 2016-01-11 US US14/992,450 patent/US9673969B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04230147A (ja) * | 1990-05-21 | 1992-08-19 | Philips Gloeilampenfab:Nv | 多重レベルの差動信号伝送を提供するデータ伝送システムおよび装置 |

| US5166956A (en) * | 1990-05-21 | 1992-11-24 | North American Philips Corporation | Data transmission system and apparatus providing multi-level differential signal transmission |

| JP3360861B2 (ja) * | 1993-03-02 | 2003-01-07 | 株式会社ソニー木原研究所 | シリアルディジタルデータの伝送方法及び伝送装置 |

| US6556628B1 (en) * | 1999-04-29 | 2003-04-29 | The University Of North Carolina At Chapel Hill | Methods and systems for transmitting and receiving differential signals over a plurality of conductors |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2965482A1 (en) | 2016-01-13 |

| WO2014138644A1 (en) | 2014-09-12 |

| CN105027490A (zh) | 2015-11-04 |

| JP2016513920A (ja) | 2016-05-16 |

| US20140254733A1 (en) | 2014-09-11 |

| ES2705045T3 (es) | 2019-03-21 |

| KR20150121718A (ko) | 2015-10-29 |

| US9337997B2 (en) | 2016-05-10 |

| US20160127121A1 (en) | 2016-05-05 |

| HUE042572T2 (hu) | 2019-07-29 |

| US9363071B2 (en) | 2016-06-07 |

| EP2965459A1 (en) | 2016-01-13 |

| WO2014138640A1 (en) | 2014-09-12 |

| EP2965459B1 (en) | 2018-10-24 |

| US9673969B2 (en) | 2017-06-06 |

| CN105009535A (zh) | 2015-10-28 |

| JP6461018B2 (ja) | 2019-01-30 |

| KR20150121724A (ko) | 2015-10-29 |

| CN105009535B (zh) | 2018-05-18 |

| US20140254732A1 (en) | 2014-09-11 |

| CN105027490B (zh) | 2018-03-16 |

| KR102205823B1 (ko) | 2021-01-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9673969B2 (en) | Transcoding method for multi-wire signaling that embeds clock information in transition of signal state | |

| US5777567A (en) | System and method for serial to parallel data conversion using delay line | |

| EP2926260A1 (en) | Methods and systems for chip-to-chip communication with reduced simultaneous switching noise | |

| WO2008151251A1 (en) | Techniques for multi-wire encoding with an embedded clock | |

| EP3268868B1 (en) | Farewell reset and restart method for coexistence of legacy and next generation devices over a shared multi-mode bus | |

| KR20100060616A (ko) | 데이터 송신 장치, 데이터 수신 장치, 데이터 전송 시스템 및 데이터 전송 방법 | |

| EP3114792B1 (en) | Clock recovery circuit for multiple wire data signals | |

| US9426082B2 (en) | Low-voltage differential signaling or 2-wire differential link with symbol transition clocking | |

| TW201810959A (zh) | 用於符號轉變時鐘轉碼的偵錯和糾錯的翻轉位元 | |

| JP2018506915A (ja) | データリンク電力低減およびスループット向上のためのマルチ変調 | |

| KR20180065119A (ko) | 데이터 통신을 위한 수신기 | |

| TWI698092B (zh) | 用於高速序列資料通訊系統的編碼和解碼架構及其相關方法、實體層電路、發射器與接收器及其中的通訊系統 | |

| Sathasivam et al. | Implementation of HDB3 Encoder Chip Design | |

| TW201924296A (zh) | 簡化的三相映射及寫碼 | |

| CN114363131B (zh) | 用于多模式信道的物理编码子层极性推断与自动翻转方法及装置 | |

| JP2005333508A (ja) | 信号変換装置およびドライバ装置 | |

| CN114363131A (zh) | 用于多模式信道的物理编码子层极性推断与自动翻转方法及装置 | |

| JP2017501493A (ja) | レシーバクロックのみを用いるCCIeレシーバ論理レジスタ書込み | |

| Simic et al. | New CAN Bus Line Coding Scheme | |

| JP2007243984A (ja) | 同時双方向データ送受信システム | |

| JP2005354431A (ja) | 順序論理回路 | |

| JP2015104126A (ja) | インデックス化入出力符号通信 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180228 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180326 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180615 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20181203 |

|

| A045 | Written measure of dismissal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A045 Effective date: 20190422 |