JP2009135464A - 光電変換装置の製造方法 - Google Patents

光電変換装置の製造方法 Download PDFInfo

- Publication number

- JP2009135464A JP2009135464A JP2008277605A JP2008277605A JP2009135464A JP 2009135464 A JP2009135464 A JP 2009135464A JP 2008277605 A JP2008277605 A JP 2008277605A JP 2008277605 A JP2008277605 A JP 2008277605A JP 2009135464 A JP2009135464 A JP 2009135464A

- Authority

- JP

- Japan

- Prior art keywords

- single crystal

- semiconductor layer

- crystal semiconductor

- layer

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

- H10F71/121—The active layers comprising only Group IV materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

- H10F71/139—Manufacture or treatment of devices covered by this subclass using temporary substrates

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Photovoltaic Devices (AREA)

Abstract

【解決手段】太陽電池を用いた光電変換装置の製造方法に関し、絶縁表面を有する支持基板に、所定の深さに損傷層が形成された複数の単結晶半導体基板を配列し、損傷層を境界として単結晶半導体基板の表層部を薄く分離することにより支持基板の一面に単結晶半導体層を形成し、単結晶半導体層の分離により露出した面側からレーザビームを照射して、単結晶半導体層の表面を平坦化する。

【選択図】図6

Description

本発明に係る光電変換装置は、光エネルギーを吸収して光励起キャリアを生成する半導体層、すなわち光電変換層を単結晶半導体、代表的には単結晶シリコンで形成する。この光電変換層は、インゴット又はウエハ状の単結晶半導体基体の表層部を分離して絶縁表面を有する基板上に固定したものから形成される。

図4は、あるサイズの円形の単結晶半導体基板から、光電変換層を形成するために、所定の外形寸法の転置用半導体基板を切り出す態様として、図1とは異なるものを示す。単結晶半導体基板100の代表例は単結晶シリコンウエハであり、その他多結晶シリコンウエハも適用可能である。転置用半導体基板101は、各頂点が単結晶半導体基板100の円周に内接する正方形とすることで面積を最大にすることができるが、必ずしも正方形とする必要はないのは図1の場合と同様である。

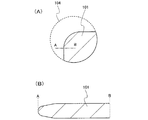

図6は、転置用半導体基板101を支持基板105に貼り合わせるときの配置について、その一例を示している。

本形態では、単結晶半導体基板から薄い単結晶半導体層を分離して、絶縁表面を有する基板若しくは絶縁性の基板上に単結晶半導体層を転置することによって、太陽電池を用いた光電変換装置を製造する方法について図面を参照して説明する。

本形態は、実施形態1と異なる製造工程を図16(A)〜(C)に示す。図16(A)に示すように、転置用半導体基板101に保護膜106を形成し、保護膜106を通して一導電型を付与する不純物を添加して第1不純物半導体層107を形成した後、図16(B)に示すように、保護膜106をそのまま残して、水素のクラスターイオンを打ち込み損傷層109を形成する。その後、図16(C)に示すように、保護膜106を除去し、第1電極108を形成する。

本形態は、実施形態1と異なる製造工程を図17(A)〜(C)に示す。図17(A)に示すように、転置用半導体基板101に第1電極108を形成し、図17(B)に示すように、第1電極108を通して一導電型を付与する不純物を添加して第1不純物半導体層107を形成する。そして、図17(C)に示すように、第1電極108と第1不純物半導体層107を通して水素のクラスターイオンを打ち込み損傷層109を形成する。

本形態は、実施形態1と異なる製造工程を図18(A)〜(C)に示す。図18(A)に示すように、転置用半導体基板101に第1電極108を形成し、図18(B)に示すように、第1電極108を通して水素のクラスターイオンを打ち込み損傷層109を形成する。そして、図18(C)に示すように、第1電極108を通して一導電型を付与する不純物を添加して第1不純物半導体層107を形成する。

本形態は、実施形態1と異なる製造工程を図19(A)〜(C)に示す。図19(A)に示すように、転置用半導体基板101に保護膜106を形成し、水素のクラスターイオンを打ち込み損傷層109を形成し、図19(B)に示すように、保護膜106をそのまま残して、一導電型を付与する不純物を添加して第1不純物半導体層107を形成する。そして、図19(C)に示すように、保護膜106を除去し、第1電極108を形成する。

本形態は、実施形態1と異なる製造工程を図20(A)〜(C)に示す。図20(A)に示すように、転置用半導体基板101に保護膜106を形成し、保護膜106を通して水素のクラスターイオンを打ち込み損傷層109を形成し、図20(B)に示すように、保護膜106を除去し、第1電極108を形成する。そして、図20(C)に示すように、第1電極108を通して一導電型を付与する不純物を添加して第1不純物半導体層107を形成する。

本形態は、実施形態1と異なる製造工程を図21(A)〜(C)に示す。支持基板105上に単結晶半導体層112を接着し、第2不純物半導体層113を形成し、レーザ処理を行った後(図11(B))、図21(A)に示すように反射防止膜116を形成する。その後、図21(B)で示すように、単結晶半導体層112aの端部をエッチングして第1電極108を露出させ、図21(C)で示すように第2電極115及び補助電極114を形成する。第2電極115は反射防止膜116上に形成されるが、絶縁破壊電圧を瞬間的に印加してバーンインコンタクトを形成することにより電極として機能させることができる。

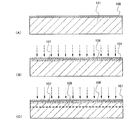

本形態では、実施形態1と異なる製造方法を図22(A)〜(C)、図23(A)、(B)に示す。支持基板105上に単結晶半導体層112を接着した後(図9(B))、図22(A)で示すように、単結晶半導体層112に残留する結晶欠陥の修復をするために、レーザ処理を行う。レーザビーム118を単結晶半導体層112に照射することで、単結晶半導体層112の少なくとも表面側は溶融し、後の冷却過程で固相状態の下層部を種結晶として再単結晶化する。その過程で単結晶半導体層112の表面は平坦化されて単結晶半導体層112bを得ることができる。このレーザ処理のとき、少なくともレーザビームの照射領域は、250℃から600℃の温度に加熱されていることが好ましい。照射領域を加熱しておくことで、レーザビームの照射による溶融時間を長くすることができ、欠陥の修復をより効果的に行うことができる。レーザビーム118の照射により単結晶半導体層112の表面側は溶融するものの、支持基板105は殆ど加熱されないので、ガラス基板のような耐熱性の低い基板を支持基板105として用いることが可能になる。また、第1電極108は耐熱性金属で形成されているので、上記温度で加熱されても単結晶半導体層112に悪影響を及ぼすことがない。第1電極108と第1不純物半導体層107の界面ではシリサイドが形成され、より電流が流れ易くなる。

本形態は、実施形態1と異なる製造工程を図24(A)〜(C)、図25(A)、図25(B)に示す。支持基板105上に単結晶半導体層112を接着した後(図9(B))、図22(A)で説明したように、図24(A)で示すように、単結晶半導体層112に残留する結晶欠陥の修復をするためにレーザ処理を行う。

本形態は、実施形態1と異なる製造工程を図26(A)〜(C)に示す。支持基板105上に単結晶半導体層112を接着した後(図9(B))、図22(A)で説明したように、図26(A)で示すように、単結晶半導体層112に残留する結晶欠陥の修復をするために、レーザ処理を行う。レーザビーム118を単結晶半導体層112に照射することで、単結晶半導体層112の少なくとも表面側は溶融し、後の冷却過程で固相状態の下層部を種結晶として再単結晶化する。その過程で単結晶半導体層112の表面は平坦化されて単結晶半導体層112bを得ることができる。

本形態は、実施形態1と異なる製造工程を図27(A)〜(C)に示す。支持基板105上に単結晶半導体層112を接着し(図9(B))、単結晶半導体層112に残留する結晶欠陥の修復をするために、レーザ処理を行った後(図22(A))、図27(A)で示すように、単結晶半導体層112bに絶縁層119を形成する。

12 太陽光発電モジュール

100 単結晶半導体基板

101 転置用半導体基板

102 切断線

103 切断線

104 角部

105 支持基板

106 保護膜

107 第1不純物半導体層

108 第1電極

109 損傷層

110 接着層

111 バリア層

112 単結晶半導体層

112a 単結晶半導体層

112b 単結晶半導体層

113 第2不純物半導体層

113a 第2不純物半導体層

113b 第2不純物半導体層

114 補助電極

115 第2電極

116 反射防止膜

117 イオンビーム

118 レーザビーム

119 絶縁層

120 第1裏面電極

121 第2裏面電極

122 充電制御回路

123 蓄電池

124 負荷

126 矩形領域

200 イオン源

201 フィラメント

202 フィラメント電源

203 電源制御部

204 ガス供給部

205 引出し電極系

206 載置台

207 質量分析管

208 質量分析計

209 排気系

210 レーザ発振器

211 光学系

212 ガス噴射筒

213 ガス供給部

214 流量制御部

215 ガス加熱部

216 ガス供給部

217 シリンドリカルレンズアレイ

218 シリンドリカルレンズ

219 ミラー

220 ダブレットシリンドリカルレンズ

221 光導入窓

222 基板ステージ

223 ガイドレール

224 スライダ

Claims (11)

- 水素のクラスターイオンを70%以上含むイオンビームを単結晶半導体基板に照射して、前記単結晶半導体基板の表面から所定の深さに損傷層を形成し、

前記単結晶半導体基板の前記イオンビームの照射面側に少なくとも一導電型の第1不純物半導体層と、前記第1不純物半導体層に接する第1電極と、前記第1電極上に接合層と、を形成し、

絶縁表面を有する支持基板の一面に、複数の前記単結晶半導体基板を、前記接合層を密接させて配列し、

加熱処理を行うことにより、前記支持基板上に単結晶半導体層を残存させたまま、前記損傷層を境界として前記単結晶半導体基板の一部を分離し、

前記単結晶半導体層の、前記単結晶半導体基板の一部の分離により露出した面側に、前記一導電型とは逆の導電型の第2不純物半導体層を形成し、

前記第2不純物半導体層側から前記単結晶半導体層にレーザビームを照射して、前記単結晶半導体層の表面を平坦化することを特徴とする光電変換装置の製造方法。 - 請求項1において、

前記単結晶半導体層にレーザビームを照射した後に、前記単結晶半導体層の一部を除去して前記第1電極を露出させ、

前記第1電極に接する補助電極と、前記第2不純物半導体層上に第2電極と、を形成することを特徴とする光電変換装置の製造方法。 - 水素のクラスターイオンを70%以上含むイオンビームを単結晶半導体基板に照射して、前記単結晶半導体基板の表面から所定の深さに損傷層を形成し、

前記単結晶半導体基板の前記イオンビームの照射面側に少なくとも一導電型の第1不純物半導体層と、前記第1不純物半導体層に接する第1電極と、前記第1電極上に接合層と、を形成し、

絶縁表面を有する支持基板の一面に、複数の前記単結晶半導体基板を、前記接合層を密接させて配列し、

加熱処理を行うことにより、前記支持基板上に単結晶半導体層を残存させたまま、前記損傷層を境界として前記単結晶半導体基板の一部を分離し、

前記単結晶半導体層の、前記単結晶半導体基板の一部の分離により露出した面側から前記単結晶半導体層にレーザビームを照射して、前記単結晶半導体層の表面を平坦化し、

前記レーザビームを照射した面側に、前記一導電型とは逆の導電型の第2不純物半導体層を形成することを特徴とする光電変換装置の製造方法。 - 請求項3において、

前記第2不純物半導体層を形成した後に、前記単結晶半導体層の一部を除去して前記第1電極を露出させ、

前記第1電極に接する補助電極と、前記第2不純物半導体層上に第2電極と、を形成することを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項4のいずれか一項において、

前記単結晶半導体層の前記レーザビームの照射領域は、250℃から600℃の温度に加熱されていることを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項5のいずれか一項において、

前記水素のクラスターイオンは、水素イオンであって質量が水素分子よりも重いクラスターイオンであることを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項6のいずれか一項において、

前記クラスターイオンは、H3 +であることを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項7のいずれか一項において、

前記レーザビームの照射は、窒素雰囲気中で行われることを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項8のいずれか一項において、

前記損傷層を、前記単結晶半導体基板の表面から10μm未満の深さに形成することを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項9のいずれか一項において、

前記支持基板は、一辺が500mm以上の四辺形のガラス基板であることを特徴とする光電変換装置の製造方法。 - 請求項1乃至請求項10のいずれか一項において、

前記単結晶半導体基板の直径が300mm以上であることを特徴とする光電変換装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008277605A JP2009135464A (ja) | 2007-11-01 | 2008-10-29 | 光電変換装置の製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007285252 | 2007-11-01 | ||

| JP2007285253 | 2007-11-01 | ||

| JP2008277605A JP2009135464A (ja) | 2007-11-01 | 2008-10-29 | 光電変換装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009135464A true JP2009135464A (ja) | 2009-06-18 |

| JP2009135464A5 JP2009135464A5 (ja) | 2011-10-20 |

Family

ID=40588485

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008277605A Withdrawn JP2009135464A (ja) | 2007-11-01 | 2008-10-29 | 光電変換装置の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7964429B2 (ja) |

| JP (1) | JP2009135464A (ja) |

| CN (1) | CN101842910B (ja) |

| WO (1) | WO2009057669A1 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010087495A (ja) * | 2008-09-05 | 2010-04-15 | Semiconductor Energy Lab Co Ltd | 光電変換装置及びその作製方法 |

| KR101077504B1 (ko) | 2010-08-17 | 2011-10-28 | 엘지전자 주식회사 | 태양전지 모듈 |

| WO2012026357A1 (ja) * | 2010-08-26 | 2012-03-01 | 信越化学工業株式会社 | 太陽電池用基板及び太陽電池 |

| JP2014060441A (ja) * | 2013-11-27 | 2014-04-03 | Shin Etsu Chem Co Ltd | 太陽電池の製造方法 |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090139558A1 (en) * | 2007-11-29 | 2009-06-04 | Shunpei Yamazaki | Photoelectric conversion device and manufacturing method thereof |

| EP2075850A3 (en) * | 2007-12-28 | 2011-08-24 | Semiconductor Energy Laboratory Co, Ltd. | Photoelectric conversion device and manufacturing method thereof |

| JP5438986B2 (ja) | 2008-02-19 | 2014-03-12 | 株式会社半導体エネルギー研究所 | 光電変換装置の製造方法 |

| US7943414B2 (en) * | 2008-08-01 | 2011-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate |

| SG161151A1 (en) * | 2008-10-22 | 2010-05-27 | Semiconductor Energy Lab | Soi substrate and method for manufacturing the same |

| SG162675A1 (en) * | 2008-12-15 | 2010-07-29 | Semiconductor Energy Lab | Manufacturing method of soi substrate and manufacturing method of semiconductor device |

| US8178422B2 (en) * | 2009-03-31 | 2012-05-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of measurement in semiconductor fabrication |

| KR101038967B1 (ko) * | 2009-12-21 | 2011-06-07 | 엘지전자 주식회사 | 태양 전지 및 그 제조 방법 |

| US8704083B2 (en) * | 2010-02-11 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and fabrication method thereof |

| KR101699312B1 (ko) * | 2011-01-28 | 2017-01-24 | 엘지전자 주식회사 | 태양 전지 및 그 제조 방법 |

| JP2013058562A (ja) | 2011-09-07 | 2013-03-28 | Semiconductor Energy Lab Co Ltd | 光電変換装置 |

| USD711817S1 (en) * | 2011-10-12 | 2014-08-26 | Azur Space Solar Power Gmbh | Solar panel |

| KR101832230B1 (ko) | 2012-03-05 | 2018-04-13 | 엘지전자 주식회사 | 태양 전지 및 이의 제조 방법 |

| DE102012110971B4 (de) * | 2012-11-14 | 2025-03-20 | Schott Ag | Verfahren zur Herstellung von linienförmig aufgereihten Schädigungsstellen in einem transparenten Werkstück sowie Verfahren und Vorrichtung zum Trennen eines Werkstücks |

| JP6397273B2 (ja) * | 2013-10-21 | 2018-09-26 | アイメック・ヴェーゼットウェーImec Vzw | シリコン太陽電池のモジュールレベル処理 |

| US10971329B2 (en) * | 2016-02-05 | 2021-04-06 | Hitachi High-Tech Corporation | Field ionization source, ion beam apparatus, and beam irradiation method |

| JP6909618B2 (ja) | 2017-04-19 | 2021-07-28 | 株式会社日立ハイテクサイエンス | イオンビーム装置 |

| US11742437B2 (en) * | 2020-03-27 | 2023-08-29 | Stmicroelectronics Ltd | WLCSP with transparent substrate and method of manufacturing the same |

| CN113451231B (zh) * | 2020-03-27 | 2025-06-13 | 意法半导体有限公司 | 具有透明基底的wlcsp及其制造方法 |

| CN111463301A (zh) * | 2020-05-19 | 2020-07-28 | 东方日升新能源股份有限公司 | 一种硅片/电池片、光伏电池组件及载具、设计排布方法 |

| CN113921639A (zh) * | 2020-10-12 | 2022-01-11 | 上海晶澳太阳能科技有限公司 | 硅片及制备方法、电池片、电池切片、电池串及光伏组件 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04307741A (ja) * | 1991-04-04 | 1992-10-29 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH05283724A (ja) * | 1992-04-01 | 1993-10-29 | Sanyo Electric Co Ltd | 光起電力装置の製造方法 |

| JPH08255762A (ja) * | 1995-03-17 | 1996-10-01 | Nec Corp | 半導体デバイスの製造方法 |

| JPH09255487A (ja) * | 1996-03-18 | 1997-09-30 | Sony Corp | 薄膜半導体の製造方法 |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| JP2000150940A (ja) * | 1998-11-18 | 2000-05-30 | Denso Corp | 半導体微粒子集合体及びその製造方法 |

| JP2001077044A (ja) * | 1999-09-01 | 2001-03-23 | Japan Atom Energy Res Inst | シリコン系結晶薄板の製造方法および光電変換素子用基板の製造方法 |

| JP2002100789A (ja) * | 2000-09-25 | 2002-04-05 | National Institute Of Advanced Industrial & Technology | 太陽電池の製造方法 |

| JP2002231628A (ja) * | 2001-02-01 | 2002-08-16 | Sony Corp | 半導体薄膜の形成方法及び半導体装置の製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| JP2006186016A (ja) * | 2004-12-27 | 2006-07-13 | Sanyo Electric Co Ltd | 太陽電池モジュール |

| WO2007106180A2 (en) * | 2005-11-07 | 2007-09-20 | Applied Materials, Inc. | Photovoltaic contact and wiring formation |

Family Cites Families (72)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4180618A (en) * | 1977-07-27 | 1979-12-25 | Corning Glass Works | Thin silicon film electronic device |

| US4633034A (en) * | 1985-02-08 | 1986-12-30 | Energy Conversion Devices, Inc. | Photovoltaic device and method |

| US4665277A (en) * | 1986-03-11 | 1987-05-12 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | Floating emitter solar cell |

| JPH01227307A (ja) | 1988-03-08 | 1989-09-11 | Asahi Glass Co Ltd | 透明導電体 |

| ATE195390T1 (de) * | 1990-05-07 | 2000-08-15 | Canon Kk | Solarzelle |

| JPH04276665A (ja) * | 1991-03-04 | 1992-10-01 | Canon Inc | 集積型太陽電池 |

| FR2681472B1 (fr) * | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| JP3360919B2 (ja) * | 1993-06-11 | 2003-01-07 | 三菱電機株式会社 | 薄膜太陽電池の製造方法,及び薄膜太陽電池 |

| US6906383B1 (en) * | 1994-07-14 | 2005-06-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacture thereof |

| JP3381443B2 (ja) * | 1995-02-02 | 2003-02-24 | ソニー株式会社 | 基体から半導体層を分離する方法、半導体素子の製造方法およびsoi基板の製造方法 |

| JPH1093122A (ja) * | 1996-09-10 | 1998-04-10 | Nippon Telegr & Teleph Corp <Ntt> | 薄膜太陽電池の製造方法 |

| JP4103968B2 (ja) * | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| JP3492142B2 (ja) * | 1997-03-27 | 2004-02-03 | キヤノン株式会社 | 半導体基材の製造方法 |

| JPH10284431A (ja) * | 1997-04-11 | 1998-10-23 | Sharp Corp | Soi基板の製造方法 |

| US6033974A (en) * | 1997-05-12 | 2000-03-07 | Silicon Genesis Corporation | Method for controlled cleaving process |

| JPH10335683A (ja) | 1997-05-28 | 1998-12-18 | Ion Kogaku Kenkyusho:Kk | タンデム型太陽電池およびその製造方法 |

| US6534380B1 (en) * | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| US6388652B1 (en) * | 1997-08-20 | 2002-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Electrooptical device |

| US6686623B2 (en) * | 1997-11-18 | 2004-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile memory and electronic apparatus |

| US6331208B1 (en) * | 1998-05-15 | 2001-12-18 | Canon Kabushiki Kaisha | Process for producing solar cell, process for producing thin-film semiconductor, process for separating thin-film semiconductor, and process for forming semiconductor |

| JP2000012864A (ja) * | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP3385972B2 (ja) * | 1998-07-10 | 2003-03-10 | 信越半導体株式会社 | 貼り合わせウェーハの製造方法および貼り合わせウェーハ |

| US6271101B1 (en) * | 1998-07-29 | 2001-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Process for production of SOI substrate and process for production of semiconductor device |

| JP4476390B2 (ja) * | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000124092A (ja) * | 1998-10-16 | 2000-04-28 | Shin Etsu Handotai Co Ltd | 水素イオン注入剥離法によってsoiウエーハを製造する方法およびこの方法で製造されたsoiウエーハ |

| KR20000040104A (ko) * | 1998-12-17 | 2000-07-05 | 김영환 | 실리콘 온 인슐레이터 웨이퍼의 제조방법 |

| JP2001160540A (ja) | 1999-09-22 | 2001-06-12 | Canon Inc | 半導体装置の製造方法、液相成長法及び液相成長装置、太陽電池 |

| JP4450126B2 (ja) * | 2000-01-21 | 2010-04-14 | 日新電機株式会社 | シリコン系結晶薄膜の形成方法 |

| US20010053559A1 (en) * | 2000-01-25 | 2001-12-20 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating display device |

| JP2002050781A (ja) * | 2000-08-02 | 2002-02-15 | Toyota Motor Corp | タンデム型太陽電池およびその製造方法 |

| FR2894990B1 (fr) * | 2005-12-21 | 2008-02-22 | Soitec Silicon On Insulator | Procede de fabrication de substrats, notamment pour l'optique,l'electronique ou l'optoelectronique et substrat obtenu selon ledit procede |

| JP3697214B2 (ja) * | 2001-03-16 | 2005-09-21 | キヤノン株式会社 | 半導体膜の製造方法 |

| JP2002348198A (ja) | 2001-05-28 | 2002-12-04 | Nissin Electric Co Ltd | 半導体素子エピタキシャル成長用基板及びその製造方法 |

| JP2003017723A (ja) | 2001-06-29 | 2003-01-17 | Shin Etsu Handotai Co Ltd | 半導体薄膜の製造方法及び太陽電池の製造方法 |

| US7119365B2 (en) * | 2002-03-26 | 2006-10-10 | Sharp Kabushiki Kaisha | Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate |

| JP4103447B2 (ja) | 2002-04-30 | 2008-06-18 | 株式会社Ihi | 大面積単結晶シリコン基板の製造方法 |

| JP2004014958A (ja) | 2002-06-11 | 2004-01-15 | Fuji Electric Holdings Co Ltd | 薄膜多結晶太陽電池とその製造方法 |

| US6908797B2 (en) * | 2002-07-09 | 2005-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| JP4289837B2 (ja) * | 2002-07-15 | 2009-07-01 | アプライド マテリアルズ インコーポレイテッド | イオン注入方法及びsoiウエハの製造方法 |

| JP4328067B2 (ja) * | 2002-07-31 | 2009-09-09 | アプライド マテリアルズ インコーポレイテッド | イオン注入方法及びsoiウエハの製造方法、並びにイオン注入装置 |

| JP2004087667A (ja) | 2002-08-26 | 2004-03-18 | Hitachi Cable Ltd | 結晶シリコン系薄膜半導体装置の製造方法 |

| US6818529B2 (en) * | 2002-09-12 | 2004-11-16 | Applied Materials, Inc. | Apparatus and method for forming a silicon film across the surface of a glass substrate |

| US7508034B2 (en) * | 2002-09-25 | 2009-03-24 | Sharp Kabushiki Kaisha | Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device |

| JP4387091B2 (ja) * | 2002-11-05 | 2009-12-16 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| US7399681B2 (en) * | 2003-02-18 | 2008-07-15 | Corning Incorporated | Glass-based SOI structures |

| US7176528B2 (en) * | 2003-02-18 | 2007-02-13 | Corning Incorporated | Glass-based SOI structures |

| EP1624494A4 (en) * | 2003-05-13 | 2007-10-10 | Asahi Glass Co Ltd | TRANSPARENT CONDUCTIVE SUBSTRATE FOR A SOLAR BATTERY AND METHOD FOR THE PRODUCTION THEREOF |

| JP2005036077A (ja) * | 2003-07-18 | 2005-02-10 | Sumitomo Chemical Co Ltd | 接着性フィルム |

| JP2005050905A (ja) | 2003-07-30 | 2005-02-24 | Sharp Corp | シリコン薄膜太陽電池の製造方法 |

| JP2005129602A (ja) * | 2003-10-22 | 2005-05-19 | Shin Etsu Handotai Co Ltd | 太陽電池セルの製造方法及び太陽電池セル |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| JP2005268682A (ja) | 2004-03-22 | 2005-09-29 | Canon Inc | 半導体基材及び太陽電池の製造方法 |

| US7534702B2 (en) * | 2004-06-29 | 2009-05-19 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| US7473969B2 (en) * | 2004-08-18 | 2009-01-06 | Corning Incorporated | High strain glass/glass-ceramic containing semiconductor-on-insulator structures |

| US7410882B2 (en) * | 2004-09-28 | 2008-08-12 | Palo Alto Research Center Incorporated | Method of manufacturing and structure of polycrystalline semiconductor thin-film heterostructures on dissimilar substrates |

| EP1962340A3 (en) * | 2004-11-09 | 2009-12-23 | S.O.I. TEC Silicon | Method for manufacturing compound material wafers |

| US7247545B2 (en) * | 2004-11-10 | 2007-07-24 | Sharp Laboratories Of America, Inc. | Fabrication of a low defect germanium film by direct wafer bonding |

| US7148124B1 (en) * | 2004-11-18 | 2006-12-12 | Alexander Yuri Usenko | Method for forming a fragile layer inside of a single crystalline substrate preferably for making silicon-on-insulator wafers |

| DE602004013163T2 (de) * | 2004-11-19 | 2009-05-14 | S.O.I. Tec Silicon On Insulator Technologies S.A. | Verfahren zur Herstellung eines Germanium-On-Insulator-Wafers (GeOI) |

| JP2006332162A (ja) * | 2005-05-24 | 2006-12-07 | Kaneka Corp | シリコン系積層型薄膜太陽電池 |

| FR2888663B1 (fr) * | 2005-07-13 | 2008-04-18 | Soitec Silicon On Insulator | Procede de diminution de la rugosite d'une couche epaisse d'isolant |

| KR101299604B1 (ko) * | 2005-10-18 | 2013-08-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| WO2007118121A2 (en) * | 2006-04-05 | 2007-10-18 | Silicon Genesis Corporation | Method and structure for fabricating solar cells using a layer transfer process |

| JP2007281316A (ja) * | 2006-04-11 | 2007-10-25 | Sumco Corp | Simoxウェーハの製造方法 |

| US7579654B2 (en) * | 2006-05-31 | 2009-08-25 | Corning Incorporated | Semiconductor on insulator structure made using radiation annealing |

| US20070281440A1 (en) | 2006-05-31 | 2007-12-06 | Jeffrey Scott Cites | Producing SOI structure using ion shower |

| FR2911430B1 (fr) * | 2007-01-15 | 2009-04-17 | Soitec Silicon On Insulator | "procede de fabrication d'un substrat hybride" |

| CN101281912B (zh) * | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| CN101652867B (zh) * | 2007-04-06 | 2012-08-08 | 株式会社半导体能源研究所 | 光伏器件及其制造方法 |

| WO2008132904A1 (en) * | 2007-04-13 | 2008-11-06 | Semiconductor Energy Laboratory Co., Ltd. | Photovoltaic device and method for manufacturing the same |

| KR101440930B1 (ko) * | 2007-04-20 | 2014-09-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | Soi 기판의 제작방법 |

| EP1993127B1 (en) * | 2007-05-18 | 2013-04-24 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of SOI substrate |

-

2008

- 2008-10-23 CN CN2008801145513A patent/CN101842910B/zh not_active Expired - Fee Related

- 2008-10-23 WO PCT/JP2008/069708 patent/WO2009057669A1/en active Application Filing

- 2008-10-29 US US12/260,302 patent/US7964429B2/en not_active Expired - Fee Related

- 2008-10-29 JP JP2008277605A patent/JP2009135464A/ja not_active Withdrawn

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04307741A (ja) * | 1991-04-04 | 1992-10-29 | Seiko Epson Corp | 半導体装置の製造方法 |

| JPH05283724A (ja) * | 1992-04-01 | 1993-10-29 | Sanyo Electric Co Ltd | 光起電力装置の製造方法 |

| JPH08255762A (ja) * | 1995-03-17 | 1996-10-01 | Nec Corp | 半導体デバイスの製造方法 |

| JPH09255487A (ja) * | 1996-03-18 | 1997-09-30 | Sony Corp | 薄膜半導体の製造方法 |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| JP2000150940A (ja) * | 1998-11-18 | 2000-05-30 | Denso Corp | 半導体微粒子集合体及びその製造方法 |

| JP2001077044A (ja) * | 1999-09-01 | 2001-03-23 | Japan Atom Energy Res Inst | シリコン系結晶薄板の製造方法および光電変換素子用基板の製造方法 |

| JP2002100789A (ja) * | 2000-09-25 | 2002-04-05 | National Institute Of Advanced Industrial & Technology | 太陽電池の製造方法 |

| JP2002231628A (ja) * | 2001-02-01 | 2002-08-16 | Sony Corp | 半導体薄膜の形成方法及び半導体装置の製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| JP2006186016A (ja) * | 2004-12-27 | 2006-07-13 | Sanyo Electric Co Ltd | 太陽電池モジュール |

| WO2007106180A2 (en) * | 2005-11-07 | 2007-09-20 | Applied Materials, Inc. | Photovoltaic contact and wiring formation |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010087495A (ja) * | 2008-09-05 | 2010-04-15 | Semiconductor Energy Lab Co Ltd | 光電変換装置及びその作製方法 |

| US8604334B2 (en) | 2008-09-05 | 2013-12-10 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device |

| KR101077504B1 (ko) | 2010-08-17 | 2011-10-28 | 엘지전자 주식회사 | 태양전지 모듈 |

| WO2012026357A1 (ja) * | 2010-08-26 | 2012-03-01 | 信越化学工業株式会社 | 太陽電池用基板及び太陽電池 |

| JP2012049285A (ja) * | 2010-08-26 | 2012-03-08 | Shin Etsu Chem Co Ltd | 太陽電池用基板及び太陽電池 |

| RU2569902C2 (ru) * | 2010-08-26 | 2015-12-10 | Син-Эцу Кемикал Ко., Лтд. | Подложка для солнечного элемента и солнечный элемент |

| KR101877277B1 (ko) * | 2010-08-26 | 2018-07-11 | 신에쓰 가가꾸 고교 가부시끼가이샤 | 태양전지용 기판 및 태양전지 |

| US10141466B2 (en) | 2010-08-26 | 2018-11-27 | Shin-Etsu Chemical Co., Ltd. | Substrate for solar cell, and solar cell |

| JP2014060441A (ja) * | 2013-11-27 | 2014-04-03 | Shin Etsu Chem Co Ltd | 太陽電池の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090117680A1 (en) | 2009-05-07 |

| WO2009057669A1 (en) | 2009-05-07 |

| CN101842910A (zh) | 2010-09-22 |

| CN101842910B (zh) | 2013-03-27 |

| US7964429B2 (en) | 2011-06-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2009135464A (ja) | 光電変換装置の製造方法 | |

| JP5286046B2 (ja) | 光電変換装置の製造方法 | |

| JP5352190B2 (ja) | 光電変換装置 | |

| JP5248995B2 (ja) | 光電変換装置の製造方法 | |

| US8008169B2 (en) | Method for manufacturing photoelectric conversion device | |

| JP5315008B2 (ja) | 光電変換装置 | |

| JP5248994B2 (ja) | 光電変換装置の製造方法 | |

| US7947523B2 (en) | Method for manufacturing photoelectric conversion device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110901 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110901 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120717 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120718 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130416 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130827 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20131029 |