CN107039387B - 引线框架、半导体装置及引线框架的制造方法 - Google Patents

引线框架、半导体装置及引线框架的制造方法 Download PDFInfo

- Publication number

- CN107039387B CN107039387B CN201710012575.9A CN201710012575A CN107039387B CN 107039387 B CN107039387 B CN 107039387B CN 201710012575 A CN201710012575 A CN 201710012575A CN 107039387 B CN107039387 B CN 107039387B

- Authority

- CN

- China

- Prior art keywords

- lead

- frame

- lead frame

- resin

- leads

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49537—Plurality of lead frames mounted in one device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4821—Flat leads, e.g. lead frames with or without insulating supports

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3142—Sealing arrangements between parts, e.g. adhesion promotors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49548—Cross section geometry

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49558—Insulating layers on lead frames, e.g. bridging members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49589—Capacitor integral with or on the leadframe

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49861—Lead-frames fixed on or encapsulated in insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Abstract

本发明提供一种引线框架、半导体装置及引线框架的制造方法。一种引线框架,其包括:第一引线框架,包括第一引线;第二引线框架,包括第二引线,所述第二引线接合到所述第一引线;以及树脂部,设置在所述第一引线框架与所述第二引线框架之间,其中,所述第一引线和所述第二引线各自包括埋置在所述树脂部中的埋置部、及从所述树脂部突出的突出部,所述第一引线的所述埋置部与所述第二引线的所述埋置部在所述树脂部中接合。

Description

技术领域

本发明涉及一种引线框架及半导体装置。

背景技术

以往,作为包括引线框架的半导体装置,例如已知QFN(Quad Flat No Lead:四边扁平无引脚)等无引线半导体装置。在该半导体装置中,近来,需要增加端子的个数,并且与其对应地将端子设置成多个列等。

然而,为了将端子设置成多个列,需要设置具有窄间距的配线。引线框架的配线通过蚀刻将金属板的上下表面贯穿而形成。由于蚀刻不仅在深度方向上进行而且在宽度方向上进行,因此如果金属板较厚,则配线之间的空间变宽,并且无法将配线设置成具有窄间距。因此,以往使用厚度约为0.2mm的金属板。然而,为了设置具有较窄间距的配线,研究了使用较薄的金属板。

然而,如果通过蚀刻薄金属板来形成配线,则配线变形的可能性增加。因此,难以实现使用比一定程度以上更薄的金属板的引线框架。

<现有技术文献>

<专利文献>

专利文献1:日本特开2000-307049号公报

发明内容

<本发明所要解决的问题>

鉴于上述问题,本发明的目的在于提供一种即使薄型化也难以变形的引线框架。

<用于解决问题的方案>

根据一个实施方式,提供一种引线框架,其包括:第一引线框架,包括第一引线;第二引线框架,包括第二引线,所述第二引线接合到所述第一引线;以及树脂部,设置在所述第一引线框架与所述第二引线框架之间,其中,所述第一引线和所述第二引线各自包括埋置在所述树脂部中的埋置部、及从所述树脂部突出的突出部,所述第一引线的所述埋置部与所述第二引线的所述埋置部在所述树脂部中接合。

附图说明

当参照附图阅读以下的详细说明时,本发明的其他目的、特征及优点将变得更加明显。

图1是表示第一实施方式的引线框架的例子的俯视图。

图2A至图2D是表示构成第一实施方式的引线框架的单元引线框架的例子的图。

图3A至图3C是表示第一实施方式的引线框架的制造步骤的例子的图(其1)。

图4A至图4C是表示第一实施方式的引线框架的制造步骤的例子的图(其2)。

图5A至图5D是表示第一实施方式的引线框架的制造步骤的例子的图(其3)。

图6是表示包括第一实施方式的引线框架的半导体装置的例子的剖视图。

图7是表示第一实施方式的引线框架的变形例1的剖视图。

图8A至图8D是表示第一实施方式的引线框架的变形例1的制造步骤的例子的图。

图9是表示第一实施方式的引线框架的变形例2的剖视图。

图10A至图10D是表示第一实施方式的引线框架的变形例2的制造步骤的例子的图。

图11是表示第一实施方式的引线框架的变形例3的剖视图。

图12A至图12C是表示第一实施方式的引线框架的变形例3的制造步骤的例子的图。

图13是表示第一实施方式的引线框架的变形例4的剖视图。

图14A至图14D是表示第一实施方式的引线框架的变形例4的制造步骤的例子的图(其1)。

图15A至图15C是表示第一实施方式的引线框架的变形例4的制造步骤的例子的图(其2)。

图16是表示构成第一实施方式的引线框架的变形例5的单元引线框架的例子的剖视图。

图17是表示使用第一实施方式的引线框架的变形例5的半导体装置的例子的剖视图。

图18是表示图2C的由虚线包围的部分放大图。

符号说明

1 引线框架

5、6 半导体装置

10 基板框架

10x、34z 狭缝

20 单元引线框架组

30、30A、30B、30C、30D、30E 单元引线框架

31、32、33、34 框架

31y、31z、32y、32z、33y 凹部

32t、32x 开口部

39 树脂部

39a 树脂部的下表面

39b 树脂部的上表面

40 电子元件

45 接合部

51、61 半导体芯片

52 金属配线

53、63 密封树脂

62 凸块

310、320、330、340 金属板

310a、320a 金属板的上表面

310b,320b 金属板的下表面

311 芯片安装部

311e 埋置部

311p 突出部

312、322、332 引线

312e、322e 埋置部

312p、322p 突出部

315、315A、315B、315D 外部连接端子

321 接合垫

323、343 配线

344 垫

具体实施方式

以下,参照示例性实施例对本发明进行说明。本领域技术人员将认识到利用本发明的教导能够完成各种变形例并且本发明不限定于为了说明而示出的实施例。

(第1实施方式)

(引线框架的结构)

图1是表示第一实施方式的引线框架1的例子的俯视图。如图1所示,引线框架1包括在俯视图中具有大致矩形形状的基板框架10,在基板框架10中多个单元引线框架组20以在其间具有空间的方式排列。单元引线框架组20是排列成矩阵的多个单元引线框架30的组。

在图1的例子中,三个单元引线框架组20排列成一行。然而,可以任意地确定排列的单元引线框架组20的数量。此外,单元引线框架组20可以排列成多列。此外,虽然在图1中的每个相邻的单元引线框架组20之间设置有狭缝10x,然而也不一定设置有狭缝10x。

对于引线框架1的材料,例如可以使用铜(Cu)、Cu基合金、铁-镍(Fe-Ni)、Fe-Ni基合金等。引线框架1的厚度例如可以大约为0.2mm。

单元引线框架30是在其上安装有半导体芯片的半导体芯片安装区域。此外,单元引线框架30最终被切割为单个半导体装置。对于图1所示的例子,每个单元引线框架组20由排列成6行6列的单元引线框架30构成。然而,构成每个单元引线框架组20的单元引线框架30的数量可以任意确定。

图2A至图2D是表示构成第一实施方式的引线框架1的单元引线框架30的例子的图。图2A是俯视图,图2B是仰视图,图2C是沿图2A和图2B的A-A线的剖视图,图2D是沿图2A和图2B的B-B线的剖视图。图18是表示图2C的由虚线包围的部分放大图。

如图2A至图2D所示,单元引线框架30包括框架31、框架32、及树脂部39。在本实施方式中,框架31是本发明的第一引线框架的典型示例。框架32是本发明的第二引线框架的典型示例。

在本实施方式中,单元引线框架30的框架32侧被称为上侧或一侧,单元引线框架30的框架31侧被称为下侧或另一侧。此外,各部件的框架32侧的表面被称为一个表面或上表面,各部件的框架31侧的表面被称为另一个表面或下表面。然而,单元引线框架30可以沿相反方向使用或者可以以任意角度使用。此外,在本实施方式中,“俯视图中”是指在垂直于框架32的一个表面的方向上观察物体,“平面形状”是指在垂直于框架32的一个表面的方向上观察到的物体的形状。

单元引线框架30具有框架32的下表面与框架31的上表面重叠并且通过焊接彼此接合的结构。树脂部39填充到在框架31的上表面与框架32的下表面所形成的空间中。树脂部39被形成为从由框架31的上表面与框架32的下表面所形成的空间沿水平方向延伸至在俯视图中不与框架31和框架32重叠的区域,并且形成矩形形状的外缘。单元引线框架30的厚度(最厚部分处的厚度)例如可以为大约0.2mm。在下文中将对单元引线框架30的各部件进行详细说明。

框架31包括芯片安装部311(晶片垫)以及多个引线312。框架31的厚度(最厚部分处的厚度)例如可以为大约0.1mm。引线312是第一引线的典型示例。

在芯片安装部311上安装有半导体芯片。芯片安装部311例如可以设置在框架31的大致中央部。芯片安装部311包括埋置在树脂部39中的埋置部311e(参见图18)以及从树脂部39的下表面39a突出的突出部311p(参见图18)。芯片安装部311的厚度例如可以为大约0.1mm。芯片安装部311与各个引线312电绝缘。

这里,“埋置在树脂部39中的”部分是指在存在于在厚度方向上设有树脂部39的范围内的部分。这对于其他部件也同样。

引线312例如可以设置成围绕芯片安装部311的多个列。引线312包括埋置在树脂部39中的埋置部312e(参见图18)以及从树脂部39的下表面39a突出的突出部312p(参见图18)。引线312的厚度例如为大约0.1mm。引线312的平面形状例如可以为直径大约为0.2mm的圆形。

框架32包括多个接合垫321、多个引线322及多个配线323。框架32在大致中央部设有使框架31的芯片安装部311的上表面露出的开口部32x。框架32的厚度(最厚部分处的厚度)例如为大约0.1mm。引线322是本发明的第二引线的典型示例。

接合垫321经由金属配线而与安装在框架31的芯片安装部311上的半导体芯片的电极连接的部分。接合垫321例如可以设置成围绕开口部32x(框架31的芯片安装部311)。接合垫321可以设置在多个列中。接合垫321设置在树脂部39的上表面39b,并且不包括埋置在树脂部39中的部分。接合垫321的厚度可以是框架32的厚度(最厚部分处的厚度)的一半,例如可以为大约0.05mm。

引线322被设置成在俯视图中分别与框架31的引线312重叠。引线322包括埋置在树脂部39中的埋置部322e(参见图18)以及从树脂部39的上表面39b突出的突出部322p。引线322的埋置部322e与相应的引线312的埋置部312e通过焊接在树脂部39中接合,并且形成外部连接端子315。引线322的厚度可以为大约0.1mm。引线322的平面形状可以是直径约为0.2mm的圆形。

在引线322的上表面形成有凹部32y。更具体地,凹部32y设置在形成于引线322的埋置部322e的正上方的突出部322p处。凹部32y作为焊接用标记设置,并且通过设置凹部32y能够使框架32的厚度局部地变薄从而能够提高焊接效率。在本实施方式中,由于引线312与引线322主要通过焊接来接合,因此凹部32y设置在引线322的上表面。然而,引线312与引线322以外的部分可以通过焊接而接合。例如,在本实施方式中,在接合垫321的内侧的框架32的多处(图2A至图2D所示的例子中的8处)也设有凹部32y。之后,通过焊接在该处的框架31与框架32接合。考虑到所需的接合强度等,可以在任意选择的这里所示以外的部分将框架31与框架32焊接。此时,凹部32y可以设置在该些任意选择的部分处。

在框架32的下表面形成有凹部32z。凹部32z的深度为框架32的厚度(最厚部分处的厚度)的大约一半,例如可以为大约0.05mm。此外,在框架31的上表面形成有凹部31z。凹部31z的深度为框架31的厚度(最厚部分处的厚度)的大约一半,例如可以为大约0.05mm。树脂部39被填充在由框架32的凹部32z和框架31的凹部31z形成的空间中,并且延伸至该空间的外部。对于树脂部39的材料,例如可以使用热固性环氧系树脂等。树脂部39的厚度例如可以为大约0.1mm。

利用相应的凹部32z在引线322的埋置部322e的侧面形成收缩部,并利用相应的凹部31z在引线312的埋置部312e的侧面形成收缩部。树脂部39被填充在引线322的埋置部322e的侧面上的收缩部和引线312的埋置部312e的侧面上的收缩部中。由此,对于每个外部连接端子315形成锚部(anchor),防止外部连接端子315从树脂部39被拔出。同样地,在芯片安装部311的侧面形成有锚部,防止芯片安装部311从树脂部39被拔出。

优选在引线312和引线322的与树脂部39的表面接触的部分进行表面粗化处理或氧化处理,以便提高引线312及322与树脂部39的粘附性。

配线323可以设置在树脂部39的上表面39b的任意选择的区域,在该区域未设有接合垫321和引线322。配线323不包括埋置在树脂部39中的部分。配线323可以分别适当地与接合垫321和引线322电连接。配线323的厚度可以是框架32的厚度(最厚部分处的厚度)的大约一半,例如可以为0.05mm。配线323的线/间隔(line/space)例如可以为大约30μm/60μm。

这里,线/间隔的线表示配线宽度,并且线/间隔的间隔表示相邻配线之间的间隔(配线间隔)。例如,当表述为线/间隔=30μm/60μm时,这意味着配线宽度为30μm,相邻配线之间的间隔为60μm。

(引线框架的制造方法)

接着,示出单元引线框架30的同时对实施方式1的引线框架1的制造方法进行说明。图3A至图5D是表示第一实施方式的引线框架1的制造步骤的例子的图。图3及图4A分别是俯视图,图3B及图4B分别是仰视图,图3C及图4C分别是沿图3A及图4A中的A-A线的剖视图。图5A至图5D是与图3C及图4C对应的剖视图。

首先,在图3A至图3C所示的步骤中,准备金属板310。接着,对金属板310的上表面310a进行半蚀刻以形成凹部31z。通过半蚀刻形成的各个凹部31z中的侧面和底面之间的角部在剖视图中具有R形状,为圆形且不尖锐。这里,金属板310的下表面310b由于未被蚀刻因此为平坦表面。

金属板310的上表面310a的未形成有凹部31z的部分成为芯片安装部311及多个引线312。虽然为了便于说明而在图3A至图3C中对成为芯片安装部311及引线312的部分付予了符号,然而成为芯片安装部311及引线312的部分在该阶段仍然一体地形成而未彼此分离。

对于金属板310的材料,例如可以使用铜(Cu)、Cu基合金、铁-镍(Fe-Ni)、Fe-Ni基合金等。金属板310的厚度例如可以为大约0.1mm。凹部31z的深度例如可以为大约0.05mm。在图3A中,为了便于说明,用灰色图案表示形成有凹部31z的区域(半蚀刻的区域)。这意味着图3A中不具有灰色图案的区域突出。

接着,在图4A至图4C所示的步骤中,准备金属板320。接着,对金属板320的上表面320a进行半蚀刻以形成凹部32y。此外,对金属板320的下表面320b进行半蚀刻以形成凹部32z。此外,通过在俯视图中重叠的位置上对金属板320的上表面320a和下表面320b分别进行半蚀刻而形成贯穿金属板320的开口部32x。通过半蚀刻形成的各个凹部32y及32z中的侧面和底面之间的角部在剖视图中具有R形状,为圆形且不尖锐。

未形成有凹部32y的部分分别成为接合垫321及配线323。形成有凹部32y的部分分别成为引线322。虽然为了便于说明而在图4A至图4C中对成为接合垫321、引线322及配线323的部分付予了符号,然而成为接合垫321、引线322及配线323的部分在该阶段仍然一体地形成而未彼此分离。

金属板320的材料例如可以与金属板310的材料相同。金属板320的厚度例如可以为大约0.1mm。凹部32y及32z的深度例如可以为大约0.05mm。在图4A及图4B中,为了便于说明,分别用灰色图案表示形成有凹部32y及32z的区域(半蚀刻的区域)。这意味着图4A及图4B中不具有灰色图案的区域突出。

接着,在图5A所示的步骤中,将金属板320放置在金属板310上,使得分别成为引线312的部分与成为引线322的部分在俯视图中互相重叠(使得凹部31z与相应的凹部32z分别互相面对而形成空间)。以下,将成为引线312的部分称为“将成为引线312的部分”,并将成为引线322的部分称为“将成为引线322的部分”。接着,对作为标记的凹部32y从箭头B的方向照射激光束,以使将成为引线312的部分和将成为引线322的部分的金属材料局部熔融,并将金属板310和金属板320接合(激光焊接)。作为激光束,例如可以使用利用二次谐振波(SHG)等的绿色激光。在此情况中,激光束的波长例如可以为大约532nm。在图5A中,灰色图案示意性地表示金属材料局部熔融的部分(未在其他图中示出)。

接着,在图5B所示的步骤中,用下模具510和上模具520夹持图5A所示的结构。如图5C所示,在由金属板310和金属板320形成的空间部分中填充树脂,并将树脂固化以形成树脂部39。树脂部39例如可以利用转移模塑、压缩模塑、射出模塑等形成。对于树脂部39的材料,例如可以使用热固性环氧系树脂等。

接着,在图5D所示的步骤中,在从下模具510和上模具520释放出图5C所示的结构后,通过蚀刻除去金属板310及320的预定部分。由此,金属板310的将成为芯片安装部311和引线312的部分被彼此分离,并在树脂部39的下表面39a侧形成框架31。此外,金属板320的将成为接合垫321、引线322及配线323的部分被彼此分离,并在树脂部39的上表面39b侧形成框架32。此外,在此时,树脂部39的一部分在框架32的上表面侧和框架31的下表面侧露出。通过上述步骤,包括单元引线框架30的引线框架1被完成(参见图1及图2A至图2D)。

这里,优选在图5A和图5B所示的步骤之间在金属板310及320的表面上进行表面粗化处理或黑化处理(氧化处理)以便提高金属板310及320与树脂部39之间的粘附性。表面粗化处理是在金属板310及320的表面形成凹凸以利用锚固效应提高金属板310及320与树脂部39之间的粘附性。此外,黑化处理(氧化处理)是在金属板310及320的表面化学地形成氧化膜,从而抑制在金属板310及320的表面形成会降低金属板310及320与树脂部39之间的粘附性的不稳定的氧化膜。

如此一来,根据第一实施方式的引线框架1,通过第一蚀刻在金属板310和金属板320各自中形成凹部,并且通过焊接将金属板310和金属板320接合以利用凹部形成空间。接着,在由金属板310和金属板320形成的空间部分中形成树脂部39之后,通过第二蚀刻除去金属板310及320的预定部分以形成接合垫321、配线323等。

当通过第二蚀刻除去金属板310及320的预定部分时,由于第一蚀刻(半蚀刻)使得将成为接合垫321和配线323的部分的厚度为金属板320的大约一半。因此,能够通过第二蚀刻形成具有更窄间距(更小线/间隔)的接合垫321和配线323。因此,能够增加接合垫321的数量以及分别与接合垫321连接的外部连接端子315的数量。

尽管传统引线框架的配线的线/间隔为大约100μm/100μm,但对于配线323,能够实现大约30μm/60μm的线/间隔。

此外,由于接合垫321和配线323形成在树脂部39上,因此当接合垫321及配线323的间距变得更窄并且接合垫321及配线323各自的数量增加时接合垫321及配线323变形的可能性能够被降低。

(半导体装置的例子)

图6是表示包括第一实施方式的引线框架(单元引线框架30)的半导体装置5的例子的剖视图。

如图6所示,半导体装置5包括单元引线框架30、半导体芯片51、金属配线52、及密封树脂53。半导体装置5是QFN型半导体装置。

半导体芯片51经由如芯片贴覆膜(die attach film)等粘合层等(图中未示出)以面朝上的方式安装在单元引线框架30的芯片安装部311的上表面上。半导体芯片51的电极(图中未示出)分别经由如金配线、铜配线等金属配线52(接合线)与单元引线框架30的接合垫321电连接。

密封树脂53设置成覆盖单元引线框架30、半导体芯片51及金属配线52的上表面。对于密封树脂53的材料,可以使用具有良好刚性的环氧系树脂等。密封树脂53可以含有如二氧化硅(SiO2)等填料。

为了制造半导体装置5,首先,将半导体芯片51经由如芯片贴覆膜等粘合层等(图中未示出)以面朝上的方式安装在图1所示的引线框架1的各个单元引线框架30的芯片安装部311的上表面上。

接着,将形成在半导体芯片51的上表面的电极分别利用线接合经由金属配线52与单元引线框架30的接合垫321电连接。

接着,形成密封树脂53以覆盖单元引线框架30、半导体芯片51及金属配线52的上表面侧。密封树脂53例如可以利用转移模塑、压缩模塑、射出模塑等形成。密封树脂53例如可以针对图1所示的每个单元引线框架组20形成。

之后,通过利用切割器等进行切割而将对其形成有密封树脂53等的单元引线框架组20单片化为单元引线框架30以完成多个半导体装置5(参见图6)。

如此一来,通过使用包括单元引线框架30的引线框架1,能够实现与传统产品相比增加了外部连接端子315数量的半导体装置5。

此外,构成外部连接端子315的引线312的下端部从树脂部39的下表面39a突出。因此,当将半导体装置5安装在配线板等上时,焊料在引线312的突出部312p(参见图18)的侧面上湿润地扩展。因此,能够提高半导体装置5与配线板等之间的连接上的可靠性。

(第一实施方式的变形例1)

在第一实施方式的变形例1中,对引线的层叠结构与第一实施方式不同的引线框架的例子进行说明。需要说明的是,在第一实施方式的变形例1中,对于在上述实施方式中已经说明的相同部件付予相同的符号并不再重复说明。

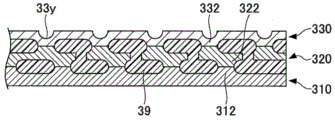

图7是表示第一实施方式的引线框架的变形例1的剖视图,其中仅放大表示单元引线框架30A的引线附近。图7所示的单元引线框架30A包括框架31、框架32、框架33及树脂部39。在本实施方式中,框架31是本发明的第一引线框架的典型示例。此外,框架33是本发明的第二引线框架的典型示例。

单元引线框架30A具有如下的结构,框架32的下表面重叠在框架31的上表面上并被焊接,然后框架33的下表面重叠在框架32的上表面上并被焊接。树脂部39被填充到由框架31的上表面和框架32的下表面形成空间、以及由框架32的上表面和框架33的下表面形成空间中。树脂部39被形成为从由框架31的上表面与框架32的下表面所形成的空间、及由框架32的上表面与框架33的下表面所形成的空间延伸至在俯视图中不与框架31、框架32及框架33重叠的区域,并且形成矩形形状的外缘。

与第一实施方式类似,分别在框架31和框架32中形成引线312和引线322。引线312和引线322被设置成在俯视图中彼此重叠并且分别通过焊接而接合。在框架33中形成引线332。引线332设置在引线322的上方以使其中心在俯视图中分别从引线312及322的中心偏移(偏离),并且通过焊接而接合到引线322。框架32和框架33分别在用作标记而形成的凹部33y的位置处被焊接。

引线312是本发明的第一引线的典型示例。引线332是本发明的第二引线的典型示例。引线322是本发明的第三引线的典型示例。

这里,尽管在图中未示出,但在单元引线框架30A中的框架33中形成有接合垫321及配线323。此外,可以在框架32中形成分别与配线323类似的配线。

如此一来,通过在单元引线框架30A中依次层叠引线312、引线322及引线332而形成外部连接端子315A。通过层叠引线312、引线322及引线332所形成的外部连接端子315A具有所谓的交错通孔(staggered via)结构,该结构中的上下方向上彼此相邻的引线设置在俯视图中的不同位置。

此外,不仅是框架32,可以在框架31与框架33之间设置两个以上的框架(如埋置在树脂部39中的框架)。在此情况中,能够实现层叠有四个以上引线的具有所谓的交错通孔的外部连接端子315A。

图8A至图8D是表示第一实施方式的引线框架的变形例1的制造步骤的例子的图。图8A至图8D主要是用于对引线的制造步骤进行说明的图,表示出对应于图7的剖面。

首先,在进行类似于上述图3A至图4C所示的步骤后,在图8A所示的步骤中,类似于图5A所示的步骤,将金属板320放置在金属板310上,使得分别成为引线312的部分与成为引线322的部分在俯视图中互相重叠。接着,对作为标记的凹部32y从箭头B的方向照射激光束,以使将成为引线312的部分和将成为引线322的部分的金属材料局部熔融,并将金属板310和金属板320接合(激光焊接)。

接着,在图8B所示的步骤中,类似于图5B及图5C所示的步骤,在由金属板310和金属板320形成的空间部分中填充树脂,并将树脂固化以形成树脂部39。之后,通过激光处理等蚀刻在金属板320中形成选择性地露出树脂部39的上表面的开口部32t。

接着,在图8C所示的步骤中,类似于图4A至图4C所示的步骤,形成设有成为引线332的部分(以下将其称为“将成为引线332的部分”)、凹部33y及凹部33z的金属板330。此外,通过蚀刻在金属板320的上表面形成凹部32z’。此时,凹部32z’被形成为分别包括凹部33y。接着,将金属板330放置在金属板320上,使得将成为引线332的部分的中心在将成为引线322的部分上、在俯视图中分别从将成为引线312的部分的中心偏移。接着,对作为标记的凹部33y从箭头B的方向照射激光束,以使将成为引线322的部分和将成为引线332的部分的金属材料局部熔融,并将金属板320和金属板330接合(激光焊接)。

接着,在图8D所示的步骤中,类似于图5B及图5C所示的步骤,在由金属板320和金属板330形成的空间部分(包括开口部32t)中填充树脂,并使其固化。由此,形成对由金属板310和金属板320形成的空间部分、开口部32t、及由金属板320和金属板330形成的空间部分连续地填充的树脂部39。

之后,类似于图5D所示的步骤,在图8D所示的结构中,通过蚀刻除去金属板310及330的预定部分。由此,形成了具有所谓的交错通孔结构、并且包括分别层叠有引线312、引线322及引线332的外部连接端子315A的图7所示的单元引线框架30A。配线323等可以在通过蚀刻将金属板310及330的预定部分除去时形成。

如此一来,通过层叠三个以上的框架,使得三维排列成为可能,能够提高引线框架的设计自由度。

(第一实施方式的变形例2)

在第一实施方式的变形例2中,对引线的结构不同于第一实施方式的引线结构的引线框架的另一个例子进行说明。在第一实施方式的变形例2中,对于在上述实施方式中已经说明的相同部件付予相同的符号并不再重复说明。

图9是表示第一实施方式的引线框架的变形例2的剖视图,其中仅放大表示单元引线框架30B的引线附近。

图9所示的单元引线框架30B与单元引线框架30A(参见图7)的不同之处在于引线312、引线322及引线332在俯视图中分别层叠在相同的位置,以形成所谓的层叠通孔(stacked via)结构的外部连接端子315B。此外,单元引线框架30B与单元引线框架30A(参见图7)的不同之处在于分别在引线312的下表面形成凹部31y,以分别代替引线322的上表面上所形成的凹部32y。

这里,尽管未在图中示出,然而在单元引线框架30B的框架33中形成有接合垫321及配线323。此外,可以在框架32中形成与配线323类似的配线。

此外,不仅是框架32,可以在框架31与框架33之间设置两个以上的框架(如埋置在树脂部39中的框架)。在此情况中,能够实现层叠有四个以上引线的具有所谓的层叠通孔的外部连接端子315B。

图10A至图10D是表示第一实施方式的引线框架的变形例2的制造步骤的例子的图。图10A至图10D主要是用于对引线的制造步骤进行说明的图,表示出对应于图9的剖面。

首先,进行类似于上述图3A至图4C所示的步骤。然而,在金属板320的各个将成为引线322的部分的上表面未形成凹部32y。代替地,在金属板310的各个将成为引线312的部分的下表面形成有凹部31y。之后,在图10A所示的步骤中,类似于图5A所示的步骤,将金属板320放置在金属板310上,使得分别成为引线312的部分与成为引线322的部分在俯视图中互相重叠。接着,对作为标记的凹部31y从箭头B的方向照射激光束,以使将成为引线312的部分和将成为引线322的部分的金属材料局部熔融,并将金属板310和金属板320接合(激光焊接)。

接着,在图10B所示的步骤中,类似于图8B所示的步骤,在由金属板310和金属板320形成的空间部分中填充树脂,并将树脂固化以形成树脂部39。之后,通过激光处理等蚀刻在金属板320中形成选择性地露出树脂部39的上表面的开口部32t。

接着,在图10C所示的步骤中,类似于图8C所示的步骤,形成设有将成为引线332的部分、凹部33y及凹部33z的金属板330。此外,通过蚀刻在金属板320的上表面形成凹部32z’。接着,将金属板330放置在金属板320上,使得将成为引线332的部分的中心在将成为引线322的部分上、在俯视图中分别与将成为引线312的部分的中心一致。接着,对作为标记的凹部33y从箭头B的方向照射激光束,以使将成为引线322的部分和将成为引线332的部分的金属材料局部熔融,并将金属板320和金属板330接合(激光焊接)。

接着,在图10D所示的步骤中,类似于图8D所示的步骤,在由金属板320和金属板330形成的空间部分(包括开口部32t)中填充树脂,并使其固化。由此,形成对由金属板310和金属板320形成的空间部分、开口部32t、及由金属板320和金属板330形成的空间部分连续地填充的树脂部39。

之后,类似于图5D所示的步骤,在图10D所示的结构中,通过蚀刻除去金属板310及330的预定部分。由此,形成了具有所谓的层叠通孔结构、并且包括分别层叠有引线312、引线322及引线332的外部连接端子315B的图9所示的单元引线框架30B。配线323等可以在通过蚀刻将金属板310及330的预定部分除去时形成。

如此一来,通过层叠三个以上的框架,使得三维排列成为可能,能够提高引线框架的设计自由度。

(第一实施方式的变形例3)

在第一实施方式的变形例3中,对在树脂部中包括有电子元件的引线框架的例子进行说明。需要说明的是,在第一实施方式的变形例3中,对于在上述实施方式中已经说明的相同部件付予相同的符号并不再重复说明。

图11是表示第一实施方式的引线框架的变形例3的剖视图,其中仅放大表示单元引线框架30C的引线附近。

图11所示的单元引线框架30C与单元引线框架30(参见图2A至图2D)的不同之处在于在框架31与框架32之间所形成的空间中安装有电子元件40并且电子元件40被树脂部39密封。此外,单元引线框架30C与单元引线框架30(参见图2A至图2D)的不同之处在于在各个引线312的下表面形成有凹部31y。

电子元件40是例如设有2个端子的电子部件,其一个端子经由接合部45与一个引线322连接,另一个端子经由另一个接合部45与另一个引线322连接。对于电子元件40,例如可以使用层叠陶瓷电容器等。对于接合部45,例如可以使用焊料或导电膏(银膏等)。

图12A至图12C是表示第一实施方式的引线框架的变形例3的制造步骤的例子的图。图12A至图12C主要是用于安装电子元件的步骤进行说明的图,表示出对应于图11的剖面。

首先,在进行类似于上述图4A至图4C所示的步骤后,在图12A所示的步骤中,在金属板320的凹部32z中经由结合部45安装电子元件40。

接着,在进行类似于上述图3A至图3C所示的步骤后,在图12B所示的步骤中,类似于图5A所示的步骤,将金属板320从图12A所示的状态翻转后,放置在金属板310上使得分别成为引线312的部分与成为引线322的部分在俯视图中互相重叠。接着,对作为标记的凹部32y从箭头B的方向照射激光束,以使将成为引线312的部分和将成为引线322的部分的金属材料局部熔融,并将金属板310和金属板320接合(激光焊接)。由此,将电子元件40安装在金属板310的凹部31z和金属板320的凹部32z中。

接着,在图12C所示的步骤中,类似于图5B及图5C所示的步骤,在由金属板310和金属板320形成的空间部分中填充树脂,并将树脂固化以形成树脂部39。由此,电子元件40被树脂部39密封。

之后,类似于图5D所示的步骤,在图12C所示的结构中,通过蚀刻除去金属板310及330的预定部分。由此,形成了图11所示的单元引线框架30C。

如此一来,通过使用在彼此层叠的框架之间安装有电子元件的单元引线框架30C,从而能够获得传统难以实现的安装有电子元件的QFN型半导体装置。此外,由于电子元件能够设在半导体芯片的电源附近,因此当电子元件是层叠陶瓷电容器时,能够提高除去噪声的效果。

(第一实施方式的变形例4)

在第一实施方式的变形例4中,对在树脂部中也形成配线的引线框架的例子进行说明。需要说明的是,在第一实施方式的变形例4中,对于在上述实施方式中已经说明的相同部件付予相同的符号并不再重复说明。

图13是表示第一实施方式的变形例4的单元引线框架30D的剖视图,其中仅放大表示单元引线框架30D的引线附近。

图13所示的单元引线框架30D包括框架31、框架32、框架34及树脂部39。框架34包括配线343及垫344。在本实施方式中,框架31是本发明的第一引线框架的典型示例。框架32是本发明的第二引线框架的典型示例。

单元引线框架30D具有框架31的引线312的上表面与框架34的垫344的下表面被焊接、并且框架32的引线322的下表面与框架34的垫344的上表面被焊接的结构。引线312、引线322及垫344例如可以被设置为在俯视图中彼此重叠。

在由框架31的上表面和框架32的下表面所形成的空间中填充有树脂部39,并且构成框架34的配线343和垫344被埋置在树脂部39中。配线343和垫344的厚度例如可以为大约15μm。配线343可以被形成为与配线323相比的高密度。配线343的线/间隔例如可以为大约30μm/30μm。垫344的尺寸可以任意地确定以适于引线312及322的焊接。配线343是本发明的第三引线的典型示例。因此,第三引线不必形成在引线框架中。

此外,不仅是框架34,可以在框架31与框架33之间设置两个以上的框架(如埋置在树脂部39中的框架)。在此情况中,可以在树脂部39中埋置两层以上配线。

图14A至图15C是表示第一实施方式的变形例4的引线框架的制造步骤的例子的图。图14A至图15C主要是用于制造引线的步骤进行说明的图,表示出对应于图13的剖面。

首先,在图14A所示的步骤中,准备金属板310。接着,类似于图3A至图3C所示的步骤,通过半蚀刻而在金属板310的上表面形成凹部31z。未形成有凹部31z的区域的部分成为芯片安装部311(未在图14A及图15C中示出)及多个引线312。此外,通过半蚀刻在金属板310的下表面形成凹部31y。金属板310的厚度例如可以为大约0.1mm。

接着,在图14B所示的步骤中,准备比金属板310薄的金属板340。接着,通过对一个表面进行半蚀刻而形成狭缝34z以形成将成为配线343的部分及将成为垫344的部分。金属板340的厚度例如可以为大约30μm。狭缝34z的宽度例如可以为大约30μm。狭缝34z之间的间隔例如可以为大约30μm。狭缝34z的深度例如可以为大约15μm。

接着,在图14C所示的步骤中,在金属板310上放置金属板340使得将成为引线312的部分与将成为垫344的部分在俯视图中重叠。接着,对作为标记的凹部31y从箭头B的方向照射激光束,以使将成为引线312的部分与将成为垫344的部分的金属材料局部熔融,并将金属板310与金属板340接合(激光焊接)。

接着,在图14D所示的步骤中,类似于图5B及图5C所示的步骤,在由金属板310和金属板340形成的空间部分中填充树脂,并通过使其固化而形成树脂部39。接着,在图15A所示的步骤中,对金属板340的上表面进行半蚀刻以除去连接将成为配线343的部分与将成为垫344的部分的部分。由此,配线343和垫344被独立地形成并完成了框架34。

接着,在图15B所示的步骤中,类似于图4A至图4C所示的步骤,形成设有将成为引线322的部分及凹部32y的金属板320。接着,将金属板320层叠在配线343及垫344上以使将成为引线322的部分分别被放置在垫344上。接着,在图15C所示的步骤中,对对作为标记的凹部32y从箭头B的方向照射激光束,以使将成为引线322的部分与将成为垫344的部分的金属材料局部熔融,并将金属板320与垫344接合(激光焊接)。

接着,类似于图14D所示的步骤,在由金属板320和框架34形成的空间部分中填充树脂,并通过使其固化而形成树脂部39。接着,类似于图5D所示的步骤,在图15C所示的结构中通过蚀刻而将金属板310及320的预定部分除去。由此,形成了图13所示单元引线框架30D。

这里,图15A所示的结构可以被用作最终产品。这意味着也可以使用由框架31、框架34及树脂部39构成的引线框架。

如此一来,通过在树脂部39中埋置高密度配线,从而能够提高引线框架的设计自由度。

(第一实施方式的变形例5)

在第一实施方式的变形例5中,对用于倒装芯片方式(flip-chip)安装的引线框架的例子进行说明。需要说明的是,在第一实施方式的变形例5中,对于在上述实施方式中已经说明的相同部件付予相同的符号并不再重复说明。

图16是表示构成第一实施方式的变形例5的引线框架的单元引线框架30E的例子的剖视图。

如图16所示,单元引线框架30E与单元引线框架30(参见图2A至图2D)的不同之处在于芯片安装部311未设置在框架31,并且接合垫321未设置在框架32。单元引线框架30E是用于倒装芯片方式安装的半导体装置的引线框架。由于在引线322的上表面分别形成凸块,因此在引线322的上表面未形成凹部32y,并且引线322的上表面是平坦的。这意味着,在本实施方式中,引线322的上表面不是将被焊接的部分,并且将被焊接的部分分别设置在引线322的附近。

(半导体装置的例子)

图17是表示使用第一实施方式的变形例5的引线框架的半导体装置6的例子的剖视图。

如图17所示,半导体装置6包括单元引线框架30E、半导体芯片61、凸块62及密封树脂63。半导体装置6是QFN型半导体装置。

半导体芯片61被倒装芯片方式安装在单元引线框架30E的上表面侧上。具体来说,半导体芯片61的电极(图中未示出)分别通过凸块62被连接到单元引线框架30E的引线322的上表面。对于凸块62,例如可以使用焊料凸块。在该情况下,对于焊料的材料,例如可以使用包含Pb的合金、Sn和Cu的合金、Sn和Ag的合金、以及Sn、Ag和Cu的合金等。

密封树脂63被设置为覆盖单元引线框架30E和半导体芯片61的上表面。对于密封树脂63的材料,例如可以使用具有良好刚性的环氧类树脂等。密封树脂63可以包含如二氧化硅(SiO2)等填料。这里,可以设置底部填充树脂以填充单元引线框架30E的上表面与半导体芯片61之间的空间,之后可以设置密封树脂63。

为了制造半导体装置6,首先,将半导体芯片61以面朝下的方式倒装芯片方式安装在与图1所示的引线框架类似排列的多个单元引线框架30E上。具体来说,在每个单元引线框架30E的引线322的上表面的预定区域涂覆膏状焊料等。之后,将半导体芯片61放置在单元引线框架30E上以使每个半导体芯片61的电极位于膏状焊料等的上方。接着,使膏状焊料等熔融并固化,从而通过回流等而形成凸块62。由此,半导体芯片61分别被倒装芯片方式安装在单元引线框架30E上。

接着,在将底部填充树脂填充在单元引线框架30E的上表面与半导体芯片61之间的空间中后,如果需要,形成密封树脂63以覆盖单元引线框架30E的上表面及半导体芯片61。密封树脂63例如可以通过例如可以利用转移模塑、压缩模塑、射出模塑等形成。密封树脂63例如可以针对图1所示的每个单元引线框架组20形成。

之后,通过利用切割器等进行切割而将对其形成有密封树脂63等的单元引线框架组20单片化为单元引线框架30E以完成多个半导体装置6(参见图16)。

如此一来,通过使用包括单元引线框架30E的引线框架1,能够实现与传统产品相比增加了外部连接端子315数量的半导体装置6。

此外,构成外部连接端子315的引线312的下端部从树脂部39的下表面39a突出。因此,当将半导体装置6安装在配线板等上时,焊料在引线312的突出部312p(参见图18)的侧面上湿润地扩展。因此,能够提高半导体装置6与配线板等之间的连接上的可靠性。

根据所公开的技术,提供了一种即使更薄也几乎不会变形的引线框架。

尽管已经具体地示出并描述了引线框架及半导体装置的优选实施方式,然而应当理解在不脱离由权利要求书限定的本发明的主旨及范围的情况下,可以在其中进行微小的修改。

本发明不限定于具体公开的实施方式,并且在不脱离本发明的主旨及范围的情况下可以进行诸多变更和修改。

例如,尽管在上述实施方式及变形例中描述了通过焊接而将框架接合的例子,然而代替焊接,框架可以通过导电粘合剂而接合。或者,框架可以通过机械接合方法而接合。

此外,上述实施方式及变形例可以被任意组合。

本申请以2016年1月18日申请的日本专利申请第2016-007413号作为要求优先权的基础,本申请援引该日本专利申请的全部内容。

Claims (14)

1.一种引线框架,其包括:

树脂部,包括第一表面和与所述第一表面相反的第二表面;

多条第一引线,从第一引线框架形成所述多条第一引线;以及

多条第二引线,从第二引线框架形成所述多条第二引线,

其中,所述第一引线和所述第二引线分别贯穿所述树脂部的所述第一表面和所述第二表面,

其中,所述第一引线和所述第二引线分别在所述树脂部中接合。

2.根据权利要求1所述的引线框架,其中,在所述第一引线和所述第二引线的分别与所述树脂部的表面接触的部分进行表面粗化处理或氧化处理。

3.根据权利要求1所述的引线框架,其中,在所述第一引线和各所述第二引线中的一者的突出部设有凹部。

4.根据权利要求1所述的引线框架,其还包括晶片垫,在所述晶片垫上安装有半导体芯片,所述晶片垫从所述第一引线框架和所述第二引线框架中的一者形成。

5.根据权利要求1所述的引线框架,其中,埋置在所述树脂部中的每条第一引线的侧面和埋置在所述树脂部中的每条第二引线的侧面各自设有收缩部。

6.根据权利要求1所述的引线框架,所述引线框架还包括多条第三引线,每条第三引线设在各第一引线与各第二引线之间,其中,

所述第三引线埋置在所述树脂部中,

每条第一引线与每条第二引线经由各第三引线在所述树脂部中接合。

7.根据权利要求6所述的引线框架,其中,所述第三引线为线/间隔比所述第二引线的线/间隔窄的高密度引线。

8.根据权利要求1所述的引线框架,其中,在所述树脂部中埋置有电子元件,所述电子元件与所述第一引线和所述第二引线中的一者电连接。

9.根据权利要求1所述的引线框架,其中,

所述第一引线和所述第二引线分别从所述树脂部的所述第一表面和所述第二表面突出。

10.根据权利要求1所述的引线框架,其中,

在所述树脂部中形成有多个开口,每个开口从所述树脂部的所述第一表面延伸至所述树脂部的所述第二表面,

其中,每条第一引线包括埋置在所述树脂部的各开口中的埋置部和从所述树脂部的所述第一表面突出的突出部,

其中,每条第二引线包括埋置在所述树脂部的各开口中的埋置部和从所述树脂部的所述第二表面突出的突出部,并且

其中,每条第一引线的所述埋置部和每条第二引线的所述埋置部在所述树脂部的各开口中接合。

11.根据权利要求10所述的引线框架,其中,每条第一引线和每条第二引线形成各开口中从所述第一表面到所述第二表面贯穿所述树脂部并且还分别在所述第一表面和所述第二表面上方延伸的引线。

12.根据权利要求1所述的引线框架,其还包括:

配线,从所述第一引线框架和所述第二引线框架中的一者形成该配线,所述配线没有被埋置在所述树脂部中使得所述配线形成在所述树脂部的所述第一表面和所述第二表面中的一个表面上。

13.一种半导体装置,其包括:

根据权利要求1所述的引线框架;

半导体芯片,安装在所述引线框架上;以及

密封树脂,密封所述半导体芯片。

14.一种引线框架的制造方法,其包括:

对第一金属板的一个表面进行蚀刻以形成在所述一个表面设有凹部的第一框架;

对第二金属板的一个表面进行蚀刻以形成在所述一个表面设有凹部的第二框架;

以使所述第一框架的所述凹部与所述第二框架的所述凹部互相面对而形成空间的方式将所述第一框架与所述第二框架接合;

在所述空间中填充树脂并使所述树脂固化以形成树脂部;以及

通过蚀刻将所述第一框架和所述第二框架各自的预定部分除去,以在所述第一框架和所述第二框架中一者上形成设在所述树脂部的表面的引线。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016007413A JP6577373B2 (ja) | 2016-01-18 | 2016-01-18 | リードフレーム及びその製造方法、半導体装置 |

| JP2016-007413 | 2016-01-18 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN107039387A CN107039387A (zh) | 2017-08-11 |

| CN107039387B true CN107039387B (zh) | 2021-09-28 |

Family

ID=59313966

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201710012575.9A Active CN107039387B (zh) | 2016-01-18 | 2017-01-09 | 引线框架、半导体装置及引线框架的制造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9972560B2 (zh) |

| JP (1) | JP6577373B2 (zh) |

| CN (1) | CN107039387B (zh) |

| TW (1) | TWI700789B (zh) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7021970B2 (ja) * | 2018-02-13 | 2022-02-17 | 株式会社三井ハイテック | リードフレーム、樹脂付きリードフレーム、樹脂付きリードフレームの製造方法および半導体装置の製造方法 |

| KR20200067453A (ko) * | 2018-12-04 | 2020-06-12 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조방법 |

| JP7232123B2 (ja) | 2019-05-14 | 2023-03-02 | 新光電気工業株式会社 | 配線基板、電子装置、及び配線基板の製造方法 |

| JP7382210B2 (ja) | 2019-11-15 | 2023-11-16 | 新光電気工業株式会社 | 配線基板、電子装置及び配線基板の製造方法 |

| JP2022078831A (ja) | 2020-11-13 | 2022-05-25 | 新光電気工業株式会社 | 配線基板、電子装置及び配線基板の製造方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101958305A (zh) * | 2010-09-04 | 2011-01-26 | 江苏长电科技股份有限公司 | 双面图形芯片正装模组封装结构及其封装方法 |

| CN102165586A (zh) * | 2008-09-30 | 2011-08-24 | 凸版印刷株式会社 | 引线框基板以及该引线框基板的制造方法 |

| CN103094222A (zh) * | 2011-10-27 | 2013-05-08 | 三星电机株式会社 | 半导体封装及其制造方法以及半导体封装模块 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5691455A (en) * | 1979-12-26 | 1981-07-24 | Fujitsu Ltd | Lead frame for manufacturing of semiconductor device |

| JPH03295262A (ja) * | 1990-04-13 | 1991-12-26 | Mitsubishi Electric Corp | リードフレームおよびその製造方法 |

| JP3198243B2 (ja) * | 1995-12-13 | 2001-08-13 | 富士通株式会社 | 半導体装置及びその製造方法 |

| KR100230515B1 (ko) * | 1997-04-04 | 1999-11-15 | 윤종용 | 요철이 형성된 리드 프레임의 제조방법 |

| KR100285664B1 (ko) * | 1998-05-15 | 2001-06-01 | 박종섭 | 스택패키지및그제조방법 |

| JP3072291B1 (ja) | 1999-04-23 | 2000-07-31 | 松下電子工業株式会社 | リ―ドフレ―ムとそれを用いた樹脂封止型半導体装置およびその製造方法 |

| WO2002009180A1 (en) * | 2000-07-25 | 2002-01-31 | Ssi Inc | Plastic package base, air cavity type package and their manufacturing methods |

| JP4695796B2 (ja) * | 2001-09-27 | 2011-06-08 | 富士通セミコンダクター株式会社 | 半導体装置、半導体装置ユニットおよびその製造方法 |

| JP4189161B2 (ja) * | 2002-03-15 | 2008-12-03 | 新日本無線株式会社 | リードフレーム及び半導体装置並びにそれらの製造方法 |

| KR100470897B1 (ko) * | 2002-07-19 | 2005-03-10 | 삼성전자주식회사 | 듀얼 다이 패키지 제조 방법 |

| JP4266717B2 (ja) * | 2003-06-13 | 2009-05-20 | 三洋電機株式会社 | 半導体装置の製造方法 |

| JP2006049698A (ja) * | 2004-08-06 | 2006-02-16 | Denso Corp | 樹脂封止型半導体装置 |

| JP4566799B2 (ja) * | 2005-03-31 | 2010-10-20 | 大日本印刷株式会社 | 樹脂封止型電子部品内蔵半導体装置および電子部品内蔵リードフレーム |

| US7405106B2 (en) * | 2006-05-23 | 2008-07-29 | International Business Machines Corporation | Quad flat no-lead chip carrier with stand-off |

| JP5197953B2 (ja) * | 2006-12-27 | 2013-05-15 | 新光電気工業株式会社 | リードフレーム及びその製造方法、及び半導体装置 |

| KR101187903B1 (ko) * | 2007-07-09 | 2012-10-05 | 삼성테크윈 주식회사 | 리드 프레임 및 이를 구비한 반도체 패키지 |

| KR101443972B1 (ko) * | 2012-10-31 | 2014-09-23 | 삼성전기주식회사 | 일체형 전력 반도체 모듈 |

| JP6055279B2 (ja) * | 2012-11-07 | 2016-12-27 | アピックヤマダ株式会社 | 半導体装置、半導体チップの実装用基板、および、それらの製造方法 |

| JP2014192222A (ja) * | 2013-03-26 | 2014-10-06 | Shinko Electric Ind Co Ltd | リードフレーム及び半導体装置 |

| KR101963271B1 (ko) * | 2014-01-28 | 2019-07-31 | 삼성전기주식회사 | 파워모듈 패키지 및 그 제조방법 |

| JP2015154042A (ja) * | 2014-02-19 | 2015-08-24 | 大日本印刷株式会社 | リードフレームおよびその製造方法、ならびに半導体装置およびその製造方法 |

| JP6325975B2 (ja) * | 2014-12-19 | 2018-05-16 | 新光電気工業株式会社 | リードフレーム、半導体装置 |

-

2016

- 2016-01-18 JP JP2016007413A patent/JP6577373B2/ja active Active

- 2016-12-30 TW TW105144148A patent/TWI700789B/zh active

-

2017

- 2017-01-06 US US15/399,791 patent/US9972560B2/en active Active

- 2017-01-09 CN CN201710012575.9A patent/CN107039387B/zh active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102165586A (zh) * | 2008-09-30 | 2011-08-24 | 凸版印刷株式会社 | 引线框基板以及该引线框基板的制造方法 |

| CN101958305A (zh) * | 2010-09-04 | 2011-01-26 | 江苏长电科技股份有限公司 | 双面图形芯片正装模组封装结构及其封装方法 |

| CN103094222A (zh) * | 2011-10-27 | 2013-05-08 | 三星电机株式会社 | 半导体封装及其制造方法以及半导体封装模块 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN107039387A (zh) | 2017-08-11 |

| JP6577373B2 (ja) | 2019-09-18 |

| JP2017130493A (ja) | 2017-07-27 |

| TW201737430A (zh) | 2017-10-16 |

| US20170207148A1 (en) | 2017-07-20 |

| TWI700789B (zh) | 2020-08-01 |

| US9972560B2 (en) | 2018-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107039387B (zh) | 引线框架、半导体装置及引线框架的制造方法 | |

| US6545366B2 (en) | Multiple chip package semiconductor device | |

| KR101117848B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US4974057A (en) | Semiconductor device package with circuit board and resin | |

| JP3481444B2 (ja) | 半導体装置及びその製造方法 | |

| JP5341337B2 (ja) | 半導体装置及びその製造方法 | |

| US6441495B1 (en) | Semiconductor device of stacked chips | |

| KR20060121823A (ko) | 가역 리드리스 패키지, 및 이를 제조 및 사용하기 위한방법 | |

| US20080315415A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP2011040602A (ja) | 電子装置およびその製造方法 | |

| KR100606295B1 (ko) | 회로 모듈 | |

| KR100240748B1 (ko) | 기판을 갖는 반도체 칩 패키지와 그 제조 방법 및 그를 이용한적층 패키지 | |

| CN111312682B (zh) | 紧凑型引线框封装件 | |

| JP4845090B2 (ja) | 回路装置の製造方法 | |

| WO2012108469A1 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP4598316B2 (ja) | 樹脂封止型半導体装置およびその製造方法 | |

| JP2956659B2 (ja) | 半導体装置およびそのリードフレーム | |

| JP3939707B2 (ja) | 樹脂封止型半導体パッケージおよびその製造方法 | |

| JP2021082638A (ja) | 配線基板、電子装置及び配線基板の製造方法 | |

| JP7467214B2 (ja) | 配線基板、電子装置及び配線基板の製造方法 | |

| JP4140012B2 (ja) | チップ状電子部品、その製造方法及び実装構造 | |

| JP2014150213A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2012227320A (ja) | 半導体装置 | |

| KR101179514B1 (ko) | 적층 반도체 패키지 및 그의 제조 방법 | |

| KR100456482B1 (ko) | 패터닝된 리드 프레임을 이용한 볼 그리드 어레이 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |