CN100416636C - 信号线驱动电路、发光装置及其驱动方法 - Google Patents

信号线驱动电路、发光装置及其驱动方法 Download PDFInfo

- Publication number

- CN100416636C CN100416636C CNB028265548A CN02826554A CN100416636C CN 100416636 C CN100416636 C CN 100416636C CN B028265548 A CNB028265548 A CN B028265548A CN 02826554 A CN02826554 A CN 02826554A CN 100416636 C CN100416636 C CN 100416636C

- Authority

- CN

- China

- Prior art keywords

- current source

- circuit

- current

- signal

- mentioned

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3283—Details of drivers for data electrodes in which the data driver supplies a variable data current for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

- G09G3/325—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror the data current flowing through the driving transistor during a setting phase, e.g. by using a switch for connecting the driving transistor to the data driver

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0814—Several active elements per pixel in active matrix panels used for selection purposes, e.g. logical AND for partial update

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

晶体管的特性产生离散。本发明是一种信号线驱动电路,具有与多根布线分别对应的多个恒流源电路和移位寄存器,其特征在于:上述多个电流源电路中的每一个都具有电容装置和供给装置,上述电容装置按照从上述移位寄存器供给的采样脉冲,将供给的电流变换成电压,上述供给装置供给与上述变换后的电压对应的电流。

Description

技术领域

本发明涉及信号线驱动电路,此外,还涉及具有上述信号线驱动电路的发光装置的技术。

背景技术

近年来,正在兴起进行图像显示的显示装置的开发。作为显示装置,使用液晶元件进行图像显示的液晶显示装置因其高画质、超薄、重量轻等优点而被广泛使用。

另一方面,近年来又兴起使用自发光元件的发光装置的开发。发光装置除现有的液晶显示装置的优点之外,又具有适合于动画显示的较快响应速度、低电压和低功耗等特征,作为下一代显示器件受到很大的关注。

作为在发光装置上显示多灰度的图像时的灰度表现方法,可以举出模拟灰度方式和数字灰度方式。前者的模拟灰度方式是模拟控制流过发光元件的电流的大小而得到灰度的方式。后者的数字灰度方式是只利用发光元件的导通状态(辉度大致是100%的状态)和截止状态(辉度大致是0%的状态)这样2个状态进行驱动的方式。在数字辉度方式中,因只能直接显示2个灰度,故提出与别的方式组合显示多灰度的图像的方法。

此外,作为象素的驱动方法,若按输入象素的信号种类分类,可以举出电压输入方式和电流输入方式。前者的电压输入方式是将向象素输入的视频信号(电压)输入到驱动元件的栅极,使用该驱动元件去控制发光元件的辉度的方式。后者的电流输入方式是通过使发光元件流过设定的信号电流去控制发光元件的辉度的方式。

这里,使用图16(A)简单说明使用电压驱动方式的发光装置的一例象素电路及其驱动方法。图16(A)所示的象素具有信号线501、扫描线502、开关TFT503、驱动TFT504、电容元件505、发光元件506和电源507、508。

当扫描线502的电位变化,使开关TFT503导通时,输入信号线501的视频信号输入到驱动TFT504的栅极。根据输入的视频信号的电位决定驱动TFT504的栅源间的电压,从而决定流过驱动TFT504的源漏间的电流。该电流供给发光元件506,使该发光元件506发光。作为驱动发光元件的半导体元件,可以使用多晶硅晶体管。但是,多晶硅晶体管因晶粒边界缺陷,容易产生阈值或导通电流等电特性的离散。在图16(A)所示的象素中,若驱动TFT504的特性对每一个象素离散,则当输入相同的视频信号时,因与其对应的驱动TFT504的漏极电流的大小不同,故发光元件506的辉度离散。

为了解决上述问题,可以向发光元件供给所要的电流而不受驱动发光元件的TFT特性的左右。根据这一观点提出能控制向发光元件供给的电流的大小而不受TFT特性左右的电流输入方式。

其次,使用图16(B)和17简单说明使用电流输入方式的发光装置中象素电路的一例及其驱动方法。图16(B)所示的象素具有信号线601、第1~第3扫描线602~604、电流线605、TFT606~609、电容元件610和发光元件611。电流源电路612配置在各信号线(各列)。

使用图17说明从写入视频信号到发光的动作。在图17中,表示各部分的图号以图16为准。图17(A)~(C)模式地示出电流的路径。图17(D)示出视频信号写入时流过各路径的电流关系,图17(E)示出视频信号写入时电容元件610积蓄的电压、即TFT608栅源极间的电压。

首先,向第1和第2扫描线602、603输入脉冲,使TFT606、607导通。这时,将流过信号线601的信号电流记作Idata。因信号线601流过信号电流Idata,故如图17(A)所示,在象素内,电流分成I1和I2两路流过。它们的关系如图17(D)所示,当然是:Idata=I1+I2。

TFT606导通的瞬间,因电容元件610中尚未保存电荷,故TFT608截止。因此,I2=0,Idata=I1。其间,电容元件610的两电极之间流过电流,在该电容元件610中进行电荷的积蓄。

接着,电容元件610逐渐积蓄电荷,两电极间开始产生电位差(图17(E))。当两电极的电位差到达Vth(图17(E)中的A点)时,TFT608导通产生I2。如前所述,因Idata=I1+I2,故I1逐渐减小,但依然流过电流,电容元件610进一步积蓄电荷。

电容元件610继续积蓄电荷,直到TFT608的栅源极间的电压达到所要的电压。即,继续积蓄电荷,直至达到TFT608仅能够流过Idata电流的电压。不久,若电荷的积蓄终结(图17(E)中的B点),则不流过电流I2。因TFT608完全导通,故Idata=I2(图17(B))。通过以上动作,完成对象素写入信号的动作。最后,结束对第1和第2扫描线602、603的选择,TFT606、607截止。

接着,向第3扫描线604输入脉冲,TFT609导通。因电容元件610保持刚才已写入的VGS,故TFT608导通,电流线605流过等于Idata的电流。因此,发光元件611发光。这时,若TFT608工作在饱和区,即使TFT608的源漏极间的电压变化,流过发光元件611的发光电流IEL也不变。

如上所述,电流输入方式是指将TFT609的漏极电流设定为和电流源电路612设定的信号电流Idata相同的电流值,使发光元件611以和该漏极电流对应的辉度发光的方式。通过使用上述构成的象素,可以抑制构成象素的TFT的特性离散的影响,并可以向发光元件供给所要的电流。

但是,在使用电流输入方式的发光装置中,有必要向象素准确地输入与视频信号对应的电流。若担任向象素输入信号电流的信号线驱动电路(在图16中相当于电流源电路612)由多晶硅晶体管构成,则因其特性产生离散,故该信号电路也产生离散。

即,在使用电流输入方式的发光装置中,有必要抑制构成象素和信号线驱动电路的TFT的特性离散的影响。但是,通过使用图16(B)所示结构的象素,虽然可以抑制构成象素的TFT特性离散的影响,但抑制构成信号线驱动电路的TFT特性离散的影响很困难。

在此,使用图18简单说明配置在对电流输入方式的象素进行驱动的信号线驱动电路中的电流源电路的结构及其动作。

图18(A)(B)中的电流源电路612与图16(B)所示的电流源电路612相当。电流源电路612具有恒流源555~558。恒流源555~558通过经端子551~554输入的信号进行控制。从恒流源555~558供给的电流的大小各不相同,其比设定为1∶2∶4∶8。

图18(B)是表示电流源电路612的电路结构的图,图中的恒流源555~558相当于晶体管。晶体管555~558的导通电流取决于L(栅极长度)/W(栅极宽度)的比(1∶2∶4∶8),变成1∶2∶4∶8。由此,电流源电路612可以按24=16级控制电流的大小。即,对4位数字视频信号,可以输出具有16级灰度的模拟值的电流。再有,该电流源电路612由多晶硅晶体管构成,和象素部在同一块衬底上一体地形成。

这样,以前提出过内部装有电流源电路的信号线驱动电路的方案。(例如参照非专利文献1、2)

此外,在数字灰度方式中,为了表现多灰度的图像,采用数字灰度方式和面积灰度方式组合的方式(以下记作面积灰度方式)及数字灰度方式和时间灰度方式组合的方式(以下记作时间灰度方式)。面积灰度方式是将一个象素分割成多个副象素,对各个副象素选择发光和不发光,利用在一个象素中发光的面积和除此之外的面积的差去表现灰度的方式。时间灰度方式是通过控制发光元件发光的时间去表现灰度的方式。具体地说,将1帧期间分割成长度不同的多个子帧期间,选择各期间的发光元件的发光或不发光,利用1帧期间内发光时间长度的差去表现灰度。在数字灰度方式中,为了表现多灰度的图像,提出数字灰度方式和时间灰度方式组合的方式(以下记作时间灰度方式)。(例如参照专利文献1)

【非专利文献1】

服部励治、其余3名,“信学技报”,ED2001-8,电流指定型多晶硅TFT有源矩阵驱动有机LED显示电路仿真,p.7-14

【非专利文献2】

ReijiH etal.“AM-LCD’01”,OLED-4,p.223-226

【专利文献1】

特开2001-5426号公报

上述电流源电路612通过设计L/W来设定晶体管的导通电流,使其为1∶2∶4∶8。但是,晶体管555~558因制作工序和使用衬底的不同产生的栅极长度、栅极宽度和栅极绝缘膜的膜厚离散的原因,产生阈值或移动度的离散。因此,使晶体管555~558的导通电流如设计的那样准确地为1∶2∶4∶8很困难。即,供给象素的电流因所在列的不同而产生离散。

为了使晶体管555~558的导通电流如设计的那样准确地为1∶2∶4∶8,有必要使所有列的电流源电路的特性完全一样。即,虽然有必要使具有信号线驱动电路的电流源电路的特性完全一样,但实现起来非常困难。

发明内容

本发明是鉴于上述问题提出的,其目的在于提供能抑制TFT的特性离散的影响向象素供给所要的信号电流的信号线驱动电路。进而,本发明的目的在于提供一种发光装置,通过使用能抑制TFT的特性离散的影响的电路结构的象素,可以抑制构成象素和驱动电路双方的TFT的特性离散的影响,向发光元件供给所要的信号电流。

本发明提供设置有能抑制TFT的特性离散的影响以流过所要的恒定电流的电路(电流源电路)结构的信号线驱动电路。进而,本发明提供具有上述信号线驱动电路的发光装置。

本发明提供对各列配置了电流源电路的信号线驱动电路。

在本发明的信号线驱动电路中,将配置在具有信号线驱动电路的各信号线(各列)上的电流源电路设计成使用参考恒流源供给规定的信号电流。在设定了信号电流的电流源电路中,具有供给与参考恒流源成比例的电流的能力。结果,通过使用上述电流源电路,可以抑制信号线驱动电路的TFT的特性离散的影响。而且,利用视频信号控制决定是否从电流源电路向象素供给已设定的信号电流的开关。

即,当有必要使信号线流过与视频信号成比例的信号电流时,配置决定是否从电流源电路向信号线驱动电路供给信号电流的开关,该开关由视频信号控制。这里,将决定是否从电流源电路向信号线驱动电路供给信号电流的开关称作信号电流控制开关。

再有,参考恒流源也可以在衬底上和信号线驱动电路一体形成。此外,也可以在衬底的外部配置IC等,也可以输入恒定的电流作为参考电流。

使用图1、2概略说明本发明的信号线驱动电路。在图1、2中,示出从第i列到(i+2)列共3根信号线的外围信号线驱动电路。

首先,对需要使信号线流过与视频信号成比例的信号电流的情况进行说明。

在图1中,信号线驱动电路403在信号线(各列)上配置电流源电路420。电流源电路420具有端子a、端子b和端子c。端子a输入设定信号。从与电流线连接的参考恒流源109向端子b供给电流(参考电流)。此外,端子c经开关101(信号电流控制开关)输出电流源电路420中保持的信号。即,电流源电路420受从端子a输入的设定信号的控制,从端子b供给电流(参考电流),从端子c输出与该电流(参考电流)成比例的电流(信号电流)。开关101(信号电流控制开关)配置在电流源电路420和象素之间,上述开关101(信号电流控制开关)的通断受视频信号控制。

其次,使用图2说明和图1的结构不同的本发明的信号线驱动电路。在图2中,信号线驱动电路403对每一根信号线(各列)设置2个以上的电流源电路。而且,电流源电路420具有多个电流源电路。这里,假定各列配置2个电流源电路,电流源电路420具有第1电流源电路421和第2电流源电路422。第1电流源电路421和第2电流源电路422具有端子a、端子b、端子c和端子d。端子a输入设定信号。从与电流线连接的参考恒流源109向端子b供给电流(参考电流)。端子c经开关101(信号电流控制开关)输出第1电流源电路421和第2电流源电路422保持的信号(信号电流)。从端子d输入控制信号。即电流源电路420受从端子a输入的设定信号和从端子d输入的控制信号的控制,从端子b供给电流(参考电流),从端子c输出与该电流(参考电流)成比例的电流(信号电流)。开关101(信号电流控制开关)配置在电流源电路420和象素之间,上述开关101(信号电流控制开关)的通断受视频信号控制。

将结束对电流源电路420进行信号电流的写入(设定信号电流、利用参考电流设定信号电流、电流源电路420能输出信号电流已被确定)的动作称作设定动作,将向象素输入信号电流的动作(电流源电路420输出信号电流的动作)称作输入动作。在图2中,因输入第1电流源电路421和第2电流源电路422的控制信号相互不同,故第1电流源电路421和第2电流源电路422一个进行设定动作,另一个进行输入动作。由此,各列可以同时进行2个动作。

再有,电流源电路的设定动作可以在任意时间,以任意时序,进行任意次数。此外,在图1、2所示的信号线驱动电路中,叙述了向信号线供给与视频信号成比例的信号电流的情况。但本发明并不限于此。例如,有必要向和信号线不同的别的线路供给电流。这时,不必配置开关101(信号电流控制开关)。对于不配置该开关的情况,图34与图1对应、图35与图2对应示出。这时,电流向象素电流线输出。向信号线输出视频信号。

在本发明中,1个移位寄存器有2个作用。1个作用是控制电流源电路,另一个作用是控制视频信号的电路、即控制为显示图像而工作的电路的作用,例如,具有控制锁存电路、采样开关及开关101(信号电流控制开关)等的作用。在上述结构的本发明中,因不必配置控制电流源电路的电路和控制视频信号的电路等各个电路,故可以减少配置的电路的元件数,进而,可以减少元件数,所以,可以缩小线路图的面积。这样,可以提高制作时的成品率,并可以降低成本。此外,若能减小线路图的面积,因框缘窄故能实现框体的小型化。

再有,移位寄存器由触发电路或译码电路等构成。当移位寄存器由触发电路构成时,通常,多根布线从第1列到最后1列按顺序选择。另一方面,当移位寄存器由译码电路构成时,多根布线或者从第1列到最后1列按顺序选择,或者随机选择。移位寄存器可以按其用途选择具有能按顺序选择多根布线的功能的结构,或选择具有能随机选择的功能的结构。

但是,当选择具有能随机选择多根布线的功能的结构时,也能随机输出供给电流源电路的设定信号。因此,电流源电路的设定动作也不是按照从第1列到最后1列的顺序进行,而是可以随机进行。这样,便可以自由设定电流源电路进行设定动作的期间。此外,可以减小电流源电路的电容元件中保持的电荷的泄漏所产生的影响。这样,若电流源电路的设定动作能随机进行,则当电流源电路的设定动作出现问题时,可以弱化该问题的影响。

再有,在本发明中,TFT可以替换使用了通常的单结晶的晶体管、使用了SOI的晶体管或有机晶体管等而使用。

本发明提供具有上述电流源电路的信号线驱动电路。而且,本发明提供一种发光装置,通过使用抑制了TFT的特性离散影响的电路结构的象素,可以抑制构成象素和驱动电路两者的TFT的特性离散的影响,并可以向发光元件供给所要的信号电流。

附图说明

图1是信号线驱动电路的图。

图2是信号线驱动电路的图。

图3是信号线驱动电路的图(1位)。

图4是信号线驱动电路的图(1位)。

图5是信号线驱动电路的图(1位)。

图6是信号线驱动电路的图(1位)。

图7是信号线驱动电路的图(3位)。

图8是信号线驱动电路的图(3位)。

图9是表示时序的图。

图10是表示时序的图。

图11是表示时序的图。

图12是表示发光装置外观的图。

图13是发光装置的象素的电路图。

图14是说明本发明的驱动方法的图。

图15是表示本发明的发光装置的图。

图16是发光装置的象素的电路图。

图17是说明发光装置的象素的动作的图。

图18是电流源电路的图。

图19是说明电流源电路的动作的图。

图20是说明电流源电路的动作的图。

图21是说明电流源电路的动作的图。

图22是表示使用本发明的电子机器的图。

图23是电流源电路的电路图。

图24是电流源电路的电路图。

图25是电流源电路的电路图。

图26是信号线驱动电路的图(3位)。

图27是信号线驱动电路的图(3位)。

图28是说明电流源电路的驱动方法的时序图。

图29是信号线驱动电路的图(3位)。

图30是参考恒流源的电路图。

图31是参考恒流源的电路图。

图32是参考恒流源的电路图。

图33是参考恒流源的电路图。

图34是信号线驱动电路的图。

图35是信号线驱动电路的图。

图36是电流源电路的电路图。

图37是电流源电路的电路图。

图38是电流源电路的电路图。

图39是电流源电路的电路图。

图40是电流源电路的电路图。

图41是电流源电路的电路图。

图42是信号线驱动电路的图。

图43是移位寄存器的图。

图44是移位寄存器和时序的图。

图45是表示时序的图。

图46是移位寄存器的图。

图47是信号线驱动电路的图。

图48是信号线驱动电路的图。

图49是信号线驱动电路的图。

图50是信号线驱动电路的图。

图51是信号线驱动电路的图。

图52是信号线驱动电路的图。

图53是信号线驱动电路的图。

图54是信号线驱动电路的图。

图55是信号线驱动电路的图。

图56是信号线驱动电路的图。

图57是信号线驱动电路的图。

图58是信号线驱动电路的图。

图59是信号线驱动电路的图。

图60是信号线驱动电路的图。

图61是信号线驱动电路的图。

图62是信号线驱动电路的图。

图63是信号线驱动电路的图。

图64是信号线驱动电路的图。

图65是信号线驱动电路的图。

图66是信号线驱动电路的图。

图67是信号线驱动电路的图。

图68是信号线驱动电路的图。

图69是信号线驱动电路的图。

图70是信号线驱动电路的图。

图71是象素的电路图。

图72是表示时序的图。

图73是表示时序的图。

图74是表示时序的图。

图75是表示时序的图。

图76是表示时序的图。

图77是表示时序的图。

图78是表示时序的图。

图79是表示时序的图。

图80是表示时序的图。

图81是表示时序的图。

图82是表示时序的图。

图83是表示时序的图。

图84是表示时序的图。

图85是表示时序的图。

图86是表示时序的图。

图87是电流源电路的布线图。

具体实施方式

(实施形态1)

在本实施形态中,说明本发明的信号线驱动电路具备的电流源电路的结构及其动作。

在本发明中,从端子a输入的信号相当于从移位寄存器供给的采样脉冲。但是,因电流源电路的结构或驱动方式等原因,采样脉冲不直接输入,而是输入从与设定控制线(在图1中未示出)连接的逻辑运算器的输出端子供给的信号。上述逻辑运算器的2个输入端子,一个输入采样脉冲,另一个输入从设定控制线供给的信号。即,电流源电路420的设定按照采样脉冲或从与设定控制线连接的逻辑运算器的输出端子供给的信号的时序进行。

再有,移位寄存器具有使用了多列触发电路(FF)等的结构。而且,向上述移位寄存器输入时钟信号(S-CLK)、启动脉冲(S-SP)和时钟反相信号(S-CLKb),把按照这些信号的时序顺序输出的信号称作采样脉冲。

此外,在上述逻辑运算器的2个输入端子中,对其中一个输入采样脉冲,对另一个输入从设定控制线供给的信号。在逻辑运算器中,进行输入的2个信号的逻辑运算,从输出端子输出信号。假如逻辑运算器是NAND,则在图14(C)所示的时序图中,可以在期间Tb,从控制线向NAND输入高(High)的信号,在其余期间,从控制线向NAND输入低(Low)的信号。

移位寄存器由触发电路或译码电路等构成。当移位寄存器由触发电路构成时,通常对多根布线从第1列到最后一列按顺序进行选择。另一方面,当移位寄存器由译码电路构成时,对多根布线或者从第1列到最后一列按顺序进行选择,或者随机选择。移位寄存器可以按其用途选择具有能按顺序选择多根布线的功能的结构,或选择具有能随机选择的功能的结构。

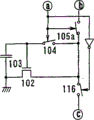

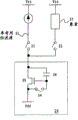

在图23(A)中,具有开关104、105a、116、晶体管102(n沟道型)和保持该晶体管102的栅源电压VGS的电容元件103的电路相当于电流源电路420。

在图23(A)所示的电流源电路中,利用经端子a输入的采样脉冲使开关104、105a接通。这样,从与电流线连接的参考恒流源109(以下记作恒流源109)经端子b供给电流(参考电流),使电容元件103保持规定的电荷。而且,电容元件103将电荷保持下来,直到从恒流源109流出的电流(参考电流)和晶体管102的漏极电流相等。

其次,利用经端子a输入的信号使开关104、105a断开。这样,因电容元件103保持规定的电荷,故晶体管102具有流过与电流(参考电流)对应大小的电流的能力。而且,假如开关101(信号电流控制开关)、116处于导通状态,则与信号线连接的象素经端子c流过电流。这是因为晶体管102的栅极电压通过电容元件103设定为规定的栅极电压,该晶体管102的漏极区流过与电流(参考电流)对应的漏极电流。因此,可以控制输入到象素的电流的大小,而与构成信号线驱动电路的晶体管的特性离散无关。

再有,当不配置开关101(信号电流控制开关)时,若开关116导通,则经端子c向与信号线连接的象素供给电流。

再有,开关104、105a的连接结构不限于图23(A)所示的结构。例如,也可以使开关104的一端与端子b连接,另一端与晶体管102的栅极连接,进而,使开关105a的一端经开关104与端子b连接,另一端与开关116连接。

或者,开关104配置在端子b和晶体管102的栅极之间,开关105a配置在端子b和开关116之间。即,对电流源电流配置的开关的个数、布线的根数及其连接没有特别的限制。但是,可以参照图36(A)那样来配置开关,使在设定动作时象图36(A1)那样连接,在输入动作时,象图36(A2)那样连接。

再有,在图23(A)所示的电流源电流中,设定信号的动作(设定动作)和把信号输入象素的动作(输入动作)不能同时进行。

在图23(B)中,具有开关124、125、晶体管122(n沟道型)、保持该晶体管122的栅源电压VGS的电容元件123和晶体管126(n沟道型)的电路相当于电流源电路420。

晶体管126起作为开关或一部分电流源用晶体管的作用。

在图23(B)所示的电流源电路中,利用经端子a输入的采样脉冲使开关124、125接通。这样,从与电流线连接的恒流源109经端子b供给电流(参考电流),使电容元件123保持规定的电荷。而且,电容元件123将电荷保持下来,直到从恒流源109流出的电流(参考电流)和晶体管122的漏极电流相等。再有,若开关124导通,因晶体管126的栅源极间的电压VGS变成0V,故晶体管126截止。

其次,利用经端子a输入的信号使开关124、125断开。这样,因电容元件123保持规定的电荷,故晶体管122具有流过与电流(参考电流)对应大小的电流的能力。而且,假如开关101(信号电流控制开关)处于导通状态,则经端子c向与信号线连接的象素供给电流。这是因为晶体管122的栅极电压通过电容元件123设定为规定的栅极电压,该晶体管122的漏极区流过与信号电流Idata对应的漏极电流。因此,可以控制输入到象素的电流的大小,而与构成信号线驱动电路的晶体管的特性离散无关。

再有,若开关124、125截止,晶体管125的栅极和源极的电位不相等。结果,电容元件123中保持的电荷还分配给晶体126,上述晶体管126自动导通。这里,晶体管122、126串联连接,且栅极相互连接。因此,晶体管122、126作为多栅晶体管动作。即,在设定动作和输入动作时,晶体管的栅极长度L不同。因此,设定动作时,从端子b供给的电流值可以比输入动作时从端子c供给的电流值大。因此,配置在端子b和参考恒流源之间的各种负载(布线电阻、交叉电容等)能更快充电。因此,可以使设定动作很快完成。再有,当没有配置开关101(信号电流控制开关)时,若晶体管126导通,则经端子c向与信号线连接的象素供给电流。

此外,对电流源电流配置的开关的个数、布线的根数及其连接没有特别的限制。即,可以参照图36(B)那样来配置布线或开关,使在设定动作时象图36(B1)那样连接,在输入动作时,象图36(B2)那样连接。特别,在图36(B2)中,若能使电容元件107保持的电荷不泄漏即可。

再有,在图23(B)所示的电流源电流中,使电流源电路具有流过信号电流的能力而进行的设定动作和向象素供给该信号电流的输入动作(向象素输出电流)不能同时进行。

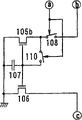

在图23(C)中,具有开关108、110、晶体管105b、106(n沟道型)和保持该晶体管105b、106的栅源极间电压VGS的电容元件107的电路相当于电流源电路420。

在图23(C)所示的电流源电路中,利用经端子a输入的采样脉冲使开关108、110接通。这样,从与电流线连接的恒流源109经端子b供给电流(参考电流),使电容元件107保持规定的电荷。而且,电容元件107将电荷保持下来,直到从恒流源109流出的电流(参考电流)和晶体管105b的漏极电流相等。这时,因晶体管105b和晶体管106的栅极相互连接,故晶体管105b和晶体管106的栅极电压可以由电容107保持。

其次,利用经端子a输入的信号使开关108、110断开。这时,因电容元件107保持规定的电荷,故晶体管106具有流过与电流(参考电流)对应大小的电流的能力。而且,假如开关101(信号电流控制开关)处于导通状态,则经端子c向与信号线连接的象素供给电流。这是因为晶体管106的栅极电压通过电容元件107设定为规定的栅极电压,该晶体管106的漏极区流过与电流(参考电流)对应的漏极电流。因此,可以控制输入到象素的电流的大小,而与构成信号线驱动电路的晶体管的特性离散无关。

再有,当没有配置开关101(信号电流控制开关)时,则电流经端子c流过与信号线连接的象素。

这时,为了使晶体管106的漏极区准确地流过与信号电流对应的漏极电流,有必要使晶体管105b和晶体管106的特性相同。更详细地说,必须使晶体管105b和晶体管106的移动度、阈值等值相同。此外,在图23(C)中,可以任意设定晶体管105b和晶体管106的W/L的值,向象素供给与从恒流源109供给的电流成比例的电流。

此外,在晶体管105b和晶体管106中,通过将与恒流源109连接的晶体管的W/L设定的大些,可以从该恒流源109供给大电流,从而提高写入速度。

再有,在图23所示的电流源电流中,使电流源电路具有流出信号电流的能力而进行的设定动作和向象素输入该信号电流的输入动作能够同时进行。

图23(D)(E)所示的电流源电路除开关110的连接不同之外,具有和图23(C)的电流源电路相同的结构。此外,因图23(D)(E)所示的电流源电路420的动作参照准照图23(C)所示的电流源电路的动作,故省略其说明。

再有,对电流源电流配置的开关的个数、布线的根数及其连接没有特别的限制。即,可以参照图36(C)那样来配置布线或开关,使在设定动作时象图36(C1)那样连接,在输入动作时,象图36(C2)那样连接。特别,在图36(C2)中,若能使电容元件107保持的电荷不泄漏即可。

在图37(A)中,具有开关195b、195c、195d、195f、晶体管195a和电容元件195e的电路相当于电流源电路。在图37(A)所示的电流源电路中,利用经端子a输入的信号使开关195b、c、d、f接通。这样,从与电流线连接的恒流源109经端子b供给电流,使电容元件195e保持规定的电荷,直到从恒流源109供给的信号电流和晶体管195a的漏极电流相等。

其次,利用经端子a输入的信号使开关195b、195c、195d、195f断开。这时,因电容元件195e保持规定的电荷,故晶体管195a具有流过与信号电流对应大小的电流的能力。这是因为晶体管195a的栅极电压通过电容元件195e设定为规定的栅极电压,该晶体管195a的漏极区流过与电流(参考电流)对应的漏极电流。在该状态下,经端子c向外部供给电流。再有,在图37(A)所示的电流源电路中,使电流源电路具有流过信号电流的能力的设定动作和向象素输入该信号电流的输入动作不能同时进行。但是,利用经端子a输入的信号使受控制的开关接通,而且,当端子c不流过电流时,有必要将端子c和其它电位的布线连接。若设该布线的电位为Va,只要是使从端子B流过来的电流直接流过的电位,该Va取什么样的值都可以。作为一个例子,可以是电源电压Vdd。

再有,对开关的个数、布线的根数及其连接没有特别的限制。即,可以参照图37(B)(C)那样来配置开关,使在设定动作时象图37(B1)(C1)那样连接,在输入动作时,象图37(B2)(C2)那样连接。

再有,在图23(A)(C)~(E)的电流源电路420中,电流流动的方向(从象素向信号线驱动电路的方向)相同,晶体管102、105b、106的导电类型可以是p沟道型。

因此,图24(A)示出电流流动的方向(从象素向信号线驱动电路的方向)相同、使图23(A)所示的晶体管102为p沟道型时的电路图。在图23(A)中,通过在栅源间配置电容元件,即使源极电位变化,也能保持栅源极间的电压。此外,图24(B)~(D)示出电流流动的方向(从象素向信号线驱动电路的方向)相同、使图23(C)~(E)所示的晶体管105b、106为p沟道型时的电路图。

图38(A)示出在图37所示的构成中使晶体管105a为p沟道型的情况。图38(B)示出在图23(B)所示的构成中使晶体管122、126为p沟道型的情况。

在图40中,具有开关104、116、晶体管102和电容元件103等的电路与电流源电路相当。

图40(A)相当于将图23(A)的一部分变更后的电路。在图40(A)所示的电流源电路中,在电流源的设定动作时和输入动作时,晶体管的栅极宽度W不同。即,设定动作时象图40(B)那样连接,输入动作时象图40(C)那样连接,栅极宽度w不同。因此,设定动作时从端子b供给的电流值可以比输入动作时从端子c供给的电流值大。为此,配置在端子b和参考恒流源之间的各种负载(布线电阻、交叉电容等)能更快充电。因此,可以使设定动作很快完成。再有,图40示出将图23(A)的一部分变更后的电路。但是,对除图23之外的电路或图24、图37、图39、图38等电路也容易适用。

再有,在图23、图24、图37所示的电流源电路中,电流从象素向信号线驱动电路方向流动。但是,电流不仅仅从象素向信号线驱动电路方向流动,有时也从信号线驱动电路向象素方向流动。电流向哪个方向流动取决于象素的构成。当电流从信号线驱动电路向象素方向流动时,可以在图23中将Vss(低电位电源)变更成Vdd(高电位电源),使晶体管102、105b、106、122、126为p沟道型即可。此外,在图24中将Vss变更成Vdd,使晶体管102、105b、106为n沟道型即可。

再有,在上述所有的电流源电路中配置的电容元件因可以用晶体管栅极电容等去替代,所以,也可以不配置。

图23(A)~(E)、图38(A)(B)的电路可以配置布线或开关,在设定动作时象图39(A1)~(D1)那样连接,在输入动作时,象图39(A2)~(D2)那样连接。开关的个数和布线的根数没有特别限制。

以下,详细说明图23(A)和图24(A)、图23(C)~(E)和图23(B)~(D)的电流源电路的动作。首先,使用图19说明图23(A)和图24(A)的电流源电路的动作。

图19(A)~(C)典型地示出电流在电路元件间流动的路径。图19(D)示出将信号电流写入电流源电路时各路径流过的电流和时间的关系,图19(E)示出将信号电流写入电流源电路时电容元件16积蓄的电压、即晶体管15的栅源极间电压和时间的关系。在图19(A)~(C)所示的电路图中,11是参考恒流源(以下记作恒流源),开关12~14是具有开关功能的元件,15是晶体管,16是电容元件,17是象素。而且,具有开关14、晶体管15和电容元件16的电路相当于电流源电路20。

晶体管15的源极区与Vss连接,漏极区与恒流源11连接。电容元件16的一个电极与Vss(晶体管15的源极)连接,另一个电极与开关14(晶体管15的栅极)连接。电容元件16起保持晶体管15的栅源极间电压的作用。

象素17由发光元件或晶体管等构成。发光元件具有阳极和阴极以及夹在上述阳极和上述阴极之间的发光层。发光层使用周知的发光材料作成,此外,发光层有单层结构和层叠结构2种结构,可以使用任何一种结构。进而,发光层中的发光有从单重态激励状态返回基态时的发光(荧光)和从三重态激励状态返回基态时的发光(磷光),可以使用一种或两种发光。此外,发光层由有机材料或无机材料等周知的材料构成。

实际上,电流源电路20设在信号线驱动电路中,从设在信号线驱动电路中的电流源电路20经具有信号线或象素的电路元件等向发光元件供给与信号电流对应的电流。但是,在图19中,为了简单说明恒流源11、电流源电流20和象素17的关系,省略详细构成的图示。

首先,使用图19(A)(B)说明电流源电路20保持信号电流Idata的动作(设定动作)。在图19(A)中,开关12、14导通,开关13截止。从恒流源11供给信号电流,电流从该恒流源11向电流源电路20的方向流动。这时,如图19(A)所示,在电流源电路20内,电流的路径分为I1和I2两路。该关系如图19(D)所示,当然,信号电流满足Idata=I1+I2的关系。

在恒流源11开始流出电流的瞬间,因电容元件16没有保存电荷,故晶体管15截止。因此,I2=0,Idata=I1。

接着,电容元件16逐渐积蓄电荷,电容元件16的两电极间开始产生电位差(图19(E))。当两电极的电位差到达Vth(图19(E)中的A点)时,晶体管15导通,I2>0。如上所述,因Idata=I1+I2,故I1逐渐减小,但依然流过电流。电容元件16进一步积蓄电荷。

电容元件16的两电极间的电位差变成晶体管15的栅源极间的电压。因此,电容元件16继续积蓄电荷,直到晶体管15的栅源极间的电压达到所要的电压,即,达到使晶体管15能够流过Idata的电流时栅源极间的电压。若电荷的积蓄终结(图19(E)中的B点),不流过电流I2,进而,因晶体管15完全导通,故Idata=I2(图19(B))。

其次,使用图19(C)说明将信号电流Idata输入象素的动作(输入动作)。在图19(C)中,开关13导通,开关12、14截止。因电容元件16保持规定的电荷,故晶体管15导通,与信号电流对应的电流经开关13和晶体管15项向Vss方向流动,向象素供给规定的信号电流。这时,若使晶体管15工作在饱和区,则即使该晶体管15的源漏极间的电压变化,也能向发光元件供给恒定的电流。

在图19所示的电流源电路20中,如图19(A)~图19(C)所示,首先分成使信号电流Idata对电流源电路20的写入结束的动作(设定动作,相当于图19(A)(B))和向象素输入信号电流Idata的动作(输入动作,相当于图19(C))。接着,根据输入到象素的信号电流Idata,向发光元件供给电流。

在图19所示的电流源电路20中,设定动作和输入动作不能同时进行。因此,当有必要使设定动作和输入动作同时进行时,最好对与多个象素连接的信号线、并且配置在象素部的多根的信号线中的每一根至少设置2个电流源电路。若能够在不向象素输入信号电流Idata的期间内进行设定动作,则即便对每一根信号线(各列)只设置1个电流源电路亦可。

此外,图19(A)~(C)的晶体管15是n沟道型,当然,晶体管15也可以是p沟道型。图19(F)示出晶体管15是p沟道型时的电路图。在图19(F)中,31是参考恒流源,开关32~34是具有开关功能的元件,35是晶体管,36是电容元件,37是象素。具有开关34、晶体管35和电容元件36的电路相当于电流源电路24。

晶体管35是p沟道型,晶体管35的源极区和漏极区,一个与Vdd连接,另一个与恒流源31连接。而且,电容元件36的一个电极与Vdd连接,另一个电极与开关36连接。电容元件36起保持晶体管35的栅源极间电压的作用。

图19(F)所示的电流源电路24的动作因除电流流动的方向不同之外,和上述电流源电路20的动作相同,故这里省略其说明。再有,当设计电流流动的方向不变、而改变了晶体管15的极性的电流源电路时,可以参考图23所示的电路图。

再有,在图41中,电流流动的方向和图19(F)相同,设晶体管35是n沟道型。电容元件36连接在晶体管35的栅源极之间。晶体管35的源极电位在设定动作时和输入动作时不同。但是,即使晶体管35的源极电位变化,因栅源间的电压被保持,故动作正常。

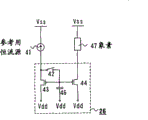

接着,使用图20、21说明图23(C)~(E)和图24(B)~(D)的电流源电路的动作。图20(A)~(C)典型地示出电流流过电路元件间的路径。图20(D)示出将信号电流写入电流源电路时各路径流过的电流和时间的关系,图20(E)示出将信号电流写入电流源电路时电容元件46积蓄的电压、即晶体管43、44的栅源极间电压和时间的关系。此外,在图20(A)~(C)所示的电路图中,41是参考恒流源(以下记作恒流源41),开关42是具有开关功能的元件,43、44是晶体管,46是电容元件,47是象素。具有开关42、晶体管43、44和电容元件46的电路相当于电流源电路25。

n沟道型晶体管43的源极区与Vss连接,漏极区与恒流源41连接。n沟道型晶体管44的源极区与Vss连接,漏极区与象素47的端子48连接。而且,电容元件46的一个电极与Vss(晶体管43、44的源极)连接,另一个电极与晶体管43、44的栅极连接。电容元件46起保持晶体管43、44的栅源极间电压的作用。

再有,实际上,电流源电路25设在信号线驱动电路中,从设在该信号线驱动电路中的电流源电路25经具有信号线或象素的电路元件等向发光元件流过与信号电流对应的电流。但是,在图20中,为了简单说明恒流源41、电流源电流25和象素47的关系,省略详细构成的图示。

在图20的电流源电路25中,晶体管43和晶体管44的尺寸很重要。因此,对于晶体管43和晶体管44的尺寸相同和不同的情况,按标记进行说明。在图20(A)~图20(C)中,当晶体管43和晶体管44的尺寸相同时,使用信号电流Idata进行说明。当晶体管43和晶体管44的尺寸不同时,使用信号电流Idata1和信号电流Idata2进行说明。再有,晶体管43和晶体管44的尺寸使用每个晶体管的W(栅极宽度)/L(栅极长度)的值来判断。

首先,说明晶体管43和晶体管44的尺寸相同的情况。接着,使用图20(A)(B)说明首先将信号电流Idata保持在电流源电路20中的动作。在图20(A)中,若开关42导通,使用参考恒流源41设定信号电流Idata,从恒流源41向电流源电路25的方向流过电流。这时,因从参考恒流源41流过信号电流Idata,故如图20(A)所示,在电流源电路25内,电流分成I1和I2两个路径流动。这时的关系如图20(D)所示,当然,信号电流满足Idata=I1+I2的关系。

在恒流源41开始流出电流的瞬间,因电容元件46没有保存电荷,故晶体管43、44截止。因此,I2=0,Idata=I1。

接着,电容元件46逐渐积蓄电荷,电容元件46的两电极间开始产生电位差(图20(E))。当两电极的电位差到达Vth(图20(E)中的A点)时,晶体管43和44导通,I2>0。如上所述,因Idata=I1+I2,故I1逐渐减小,但依然流过电流。电容元件46进一步积蓄电荷。

电容元件46的两电极间的电位差变成晶体管43和44的栅源极间的电压。因此,电容元件46继续积蓄电荷,直到晶体管43和44的栅源极间电压达到所要的电压,即,达到使晶体管15能够流过Idata的电流时栅源极间的电压。若电荷的积蓄终结(图20(E)中的B点),则不流过电流I2,进而,因晶体管43和44完全导通,故Idata=I2(图20(B))。

其次,使用图20(C)说明将信号电流Idata输入象素的动作。首先,开关42截止。因电容元件46保持规定的电荷,故晶体管43和44导通,从象素47流过与信号电流Idata相等的电流。由此向象素输入信号电流Idata。这时,若晶体管44工作在饱和区,即使该晶体管44的源漏极间的电压变化,也能使象素中流过的电流不变。

再有,对于图20那样的电流镜电路,即使开关42截止,也能利用从恒流源41供给的电流,使电流流过象素47。即,能同时进行对电流源电路25设定信号的动作(设定动作)和向象素输入信号的动作(输入动作)。

其次,说明晶体管43和晶体管44的尺寸不同的情况。电流源电路25的动作因和上述动作相同故这里省略其说明。若晶体管43和晶体管44的尺寸不同,恒流源41中设定的信号电流Idata1必然和流过象素47的信号电流Idata2不同。两者的差别取决于晶体管43和晶体管44的W(栅极宽度)/L(栅极长度)的值的差别。

通常,希望使晶体管43的W/L值比晶体管44的W/L值大。这是因为若晶体管43的W/L值变大,则能够使信号电流Idata1变大的缘故。这时,当用信号电流Idata1设定电流源电路时,因可以对负载(交叉电容、布线电阻)充电,故可以很快地进行设定动作。

图20(A)~(C)所示的电流源电路25的晶体管43和44是n沟道型,当然,电流源电路25的晶体管43和44也可以是p沟道型。这里,图21示出晶体管43和44是p沟道型时的电路图。

在图21中,41是恒流源,开关42是具有开关功能的半导体元件,43、44是晶体管(p沟道型),46是电容元件,47是象素。在本实施形态中,开关42、晶体管43、44、电容元件46是相当于电流源电路26的电路。

p沟道型晶体管43的源极区与Vdd连接,漏极区与与恒流源41连接。p沟道型晶体管44的源极区与Vdd连接,漏极区与象素47的端子48连接。而且,电容元件46的一个电极与Vdd(源极)连接,另一个电极与晶体管43和44的栅极连接。电容元件46起保持晶体管43和44的栅源极间电压的作用。

图21所示的电流源电路24的动作因除电流流动的方向不同之外,和上述电流源电路20(A)~(C)的动作相同,故这里省略其说明。再有,当设计电流流动的方向不变、而改变晶体管43和44的极性的电流源电路时,可以参考图23所示的电路图。

此外,若不改变电流流动的方向,也可以改变晶体管的极性。因参照图36的动作,故在此省略其说明。

总结以上所述,在图19的电流源电路中,象素中流过和恒流源设定的信号电流Idata相同大小的电流。换言之,恒流源设定的信号电流Idata和象素流过的电流值相同,不受设置在电流源电路的晶体管的特性离散的影响。

此外,在图19的电流源电路和图6(B)的电流源电路中,在进行设定动作的期间,不能从电流源电路向象素输出信号电流Idata。因此,最好对每一根信号线设置2个电流源电路,对一个电流源电路进行设定信号的动作(设定动作),使用另一个电流源电路进行对象素输入电流Idata的动作(输入动作)。

只是,当设定动作和输入动作不能同时进行时,也可以对各列只设置1个电流源电路。再有,图37(A)、图38(A)的电流源电路和图19的电流源电路除连接和电流流动的路径不同之外,其构成相同。图40(A)的电流源电路和图19的电流源电路除从恒流源供给电流及从电流源电路流出的电流的大小不同之外,其构成相同。此外,图23(B)和图38(B)的电流源电路和图19的电流源电路除从恒流源供给电流及从电流源电路流出的电流的大小不同之外,其构成相同。即,只是在图40(A)的构成中,晶体管的栅极宽度W在设定动作时和输入动作时不一样,在图23(B)和图38(B)的结构中,晶体管的栅极长度L在设定动作时和输入动作时不一样,除此之外和图19的电流源电路结构相同。

另一方面,在图20、21的电流源电路中,在恒流源中设定的信号电流Idata和流过象素的电流值依赖于设置在电流源电路中的2个晶体管的尺寸。即,可以任意设计设置在电流源电路的2个晶体管的尺寸(W(栅极宽度)/L(栅极长度))从而任意改变在恒流源中设定的信号电流Idata和流过象素的电流。只是,当2个晶体管的阈值或移动度等特性产生离散时,很难向象素输出正确的信号电流Idata。

此外,在图20、21的电流源电路中,可以在进行设定动作的期间向象素输入信号。即,可以同时进行设定信号的动作(设定动作)和向象素输入信号的动作(输入动作)。因此,如图19的电流源电路那样,不必对1根信号线设置2个电流源电路。

具有上述结构的本发明可以抑制TFT的特性离散的影响,并向外部供给所要的电流。

(实施形态2)

如上所述,在图19(和图40(A)、图23(B)、图38(B)等)所示的电流源电路中,最好设计成对每一根信号线(各列)设置2个电流源电路,一个电流源电路进行设定动作,另一个电流源电路进行输入动作(向象素输出电流)。这是因为不能同时进行设定动作和输入动作。在本实施形态中,使用图25说明图2所示的第1电流源电路421或第2电流源电路422的结构及其动作。

再有,信号线驱动电路具有电流源电路420、移位寄存器和锁存电路等。

在本发明中,从端子a输入的信号表示从移位寄存器来的采样脉冲。即,图2的设定信号相当于从移位寄存器来的采样脉冲。而且,在本发明中,按照从移位寄存器来的采样脉冲的时序进行电流源电路420的设定。

但是,因电流源电路的结构或驱动方式等原因,采样脉冲不直接输入,而是输入从与设定控制线(在图2中未示出)连接的逻辑运算器的输出端子供给的信号。上述逻辑运算器的2个输入端子,一个输入采样脉冲,另一个输入从设定控制线供给的信号。

电流源电路420受经端子a输入的设定信号控制,从端子b供给电流(参考电流),从端子c输出和该电流(参考电流)成比例的电流。

在图25(A)中,具有开关134~139、晶体管132(n沟道型)和保持该晶体管132的栅源极间电压VGS的电容元件133的电路相当于第1电流源电路421或第2电流源电路422。

在第1电流源电路421或第2电流源电路422中,利用经端子a输入的信号使开关134、136接通。利用经端子d从控制线输入的信号使开关135、137接通。这样,从与电流线连接的参考恒流源109经端子b供给电流(参考电流),使电容元件133保持规定的电荷。而且,电容元件133将电荷保持下来,直到从恒流源109流出的电流(参考电流)和晶体管132的漏极电流相等。

其次,利用经端子a、d输入的信号使开关134~137断开。这一来,因电容元件133保持规定的电荷,故晶体管132具有流过与信号电流Idata对应大小的电流的能力。而且,假如开关101(信号电流控制开关)、138、139处于导通状态,则经端子c向与信号线连接的象素供给电流。这时,晶体管132的栅极电压通过电容元件133维持在规定的栅极电压上,晶体管132的漏极区流过与信号电流Idata对应的漏极电流。因此,可以控制流过象素的电流的大小,而与构成信号线驱动电路的晶体管的特性离散无关。

再有,当不配置开关101(信号电流控制开关)时,若开关138、139处于导通状态,则与信号线连接的象素经端子c流过电流。

在图25(B)中,具有开关144~147、晶体管142(n沟道型)、保持该晶体管142的栅源极间电压VGS的电容元件143和晶体管148(n沟道型)的电路相当于第1电流源电路421和第2电流源电路422。

在第1电流源电路421和第2电流源电路422中,利用经端子a输入的信号使开关144、146接通。利用经端子d从控制线输入的信号使开关145、147接通。这样,从与电流线连接的恒流源109经端子b供给电流(参考电流),使电容元件143保持电荷。而且,电容元件143将电荷保持下来,直到从恒流源109流出的电流(参考电流)和晶体管142的漏极电流相等。再有,若开关144、145导通,因晶体管148的栅源极间电压VGS为0V,故晶体管148自动截止。

其次,利用经端子a、d输入的信号使开关144~147断开。这样,因电容元件143保持规定的电荷,故晶体管142具有流过与信号电流Idata对应大小的电流的能力。而且,假如开关101(信号电流控制开关)处于导通状态,则经端子c向与信号线连接的象素供给电流。这时,晶体管142的栅极电压通过电容元件143维持在规定的栅极电压上,该晶体管142的漏极区流过与信号电流Idata对应的漏极电流。因此,可以控制流过象素的电流的大小,而与构成信号线驱动电路的晶体管的特性离散无关。

再有,若开关144、145截止,晶体管142的栅极和源极的电位不相等。结果,电容元件143保持的电荷还分配给晶体148,晶体管148自动导通。这里,晶体管142、148串联连接,且栅极相互连接。因此,晶体管142、148作为多栅晶体管动作。即,在设定动作和输入动作时,晶体管的栅极长度L不同。因此,设定动作时,从端子b供给的电流值可以比输入动作时从端子c供给的电流值大。因此,配置在端子b和参考恒流源之间的各种负载(布线电阻、交叉电容等)能更快充电。因此,可以使设定动作很快完成。再有,当没有配置开关101(信号电流控制开关)时,若晶体管144、145截止,则与信号线连接的象素经端子c流过电流。

这里,图25(A)的结构相当于在图23(A)结构的基础上追加端子d。图25(B)的结构相当于在图23(B)构成的基础上追加端子d。这样,通过在图23(A)(B)的结构的基础上追加串接的开关并进行修正,变成追加了d的图25(A)(B)所示的结构。再有,通过在第1电流源电路421或第2电流源电路422中配置2个串接的开关,从而可以任意使用图23、24、38、37、40等所示的电流源电路的结构。

再有,在图2中,示出了对每一根信号线设置具有第1电流源电路421和第2电流源电路422两个电流源电路的电流源电路420,但本发明不限于此。对每一根信号线的电流源电路的个数没有特别限制,可以任意设定。多个电流源电路可以设定成分别设置对应的恒流源,并根据该恒流源对电流源电路设定信号电流。例如,可以对每一根信号线设置3个电流源电路420,而且,在各电流源电流420中,根据不同的参考恒流源109设定信号电流。例如,在1个电流源电流420中,使用1位用的参考恒流源设定信号电流,在1个电流源电流420中,使用2位用的参考恒流源设定信号电流,在1个电流源电流420中,使用3位用的参考恒流源设定信号电流。由此,可以进行3位显示。

具有上述构成的本发明,可以抑制TFT的特性离散的影响,可以向外部供给所要的电流。

本实施形态可以和实施形态1任意组合。

(实施形态3)

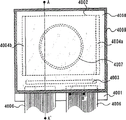

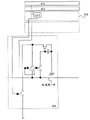

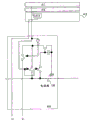

在本实施形态中,使用图15说明具有本发明的信号线驱动电路的发光装置的结构。

在图15(A)中,发光装置在衬底401上具有将多个象素配置成矩阵状的象素部402,在象素部402的周围具有信号线驱动电路403和第1、第2扫描线驱动电路404、405。在图15(A)中,具有信号线驱动电路403和2组扫描线驱动电路404、405,但本发明不限于此。驱动电路的个数可以根据象素的结构任意设计。经FPC406从外部向信号线驱动电路403和第1、第2扫描线驱动电路404、405供给信号。

使用图15(B)说明第1、第2扫描线驱动电路404、405的结构及其动作。第1、第2扫描线驱动电路404、405具有移位寄存器407和缓冲器408。移位寄存器407按照时钟信号(G-CLK)、启动脉冲(S-SP)和反相时钟信号(G-CLKb),依次输出采样脉冲。然后,经缓冲器408放大后的采样脉冲输入扫描线,使其逐行变成选择状态。按顺序从信号线向由选出的扫描线控制的象素写入信号。

再有,也可以在移位寄存器407和缓冲器408之间配置电平移动电路。通过配置电平移动电路,可以使电压幅度变大。

本实施形态可以和实施形态1、2任意组合。

(实施形态4)

在本实施形态中,说明图15(A)所示的信号线驱动电路403的详细构成及其动作。在本实施形态中,说明进行1位数字灰度显示时使用的信号线驱动电路403。

首先,说明与图1对应的情况。在此,说明按线的顺序驱动的情况。

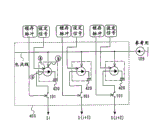

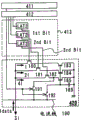

图6(A)示出进行1位数字灰度显示时的信号线驱动电路403的概略图。信号线驱动电路403具有移位寄存器411、第1锁存电路412、第2锁存电路413和恒流源电路414。

简单说明其动作,移位寄存器411使用多个触发电路(FF)等构成,按照时钟信号(S-CLK)、启动脉冲(S-SP)和反相时钟信号(S-CLKb)的时序,依次输出采样脉冲。

移位寄存器411输出的采样脉冲输入第1锁存电路412。第1锁存电路412输入数字视频信号,按照采样脉冲输入的时序将视频信号保持在各列中。

在第1锁存电路412中,当直到最后一列数字视频信号保持完毕时,在水平回描线期间,向第2锁存电路413输入锁存脉冲,第1锁存电路412保持的视频信号一齐向第2锁存电路413传送。这样,第2锁存电路413保持的视频信号整行地同时供给恒流电路414。

在第2锁存电路413保持的视频信号供给恒流电路414的期间,移位寄存器411再次输出采样脉冲。此后,重复该动作,进行1帧视频信号的处理。再有,恒流电路411有时具有将数字信号变换成模拟信号的作用。

而且,在本发明中,从移位寄存器411输出的采样脉冲输入恒流电路414。

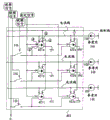

此外,恒流电路414设置多个电流源电路420。在图6(B)中,概略示出从第i列到第(i+2)列的3根信号线的信号线驱动电路。

电流源电路420由经端子a输入的信号控制。此外,经端子b,从与电流线连接的参考恒流源109供给电流。在电流源电路420和与信号线Sn连接的象素之间设置开关101(信号电流控制开关),上述开关101(信号电流控制开关)由视频信号控制。当视频信号是明信号时,从电流源电路420向象素供给电流。相反,当视频信号是暗信号时,控制开关101(信号电流控制开关),不向象素供给电流。即,电流源电路420具有流动规定电流的能力,是否向象素供给该电流由开关101(信号电流控制开关)控制。

在本发明中,经端子a输入到电流源电路420的信号相当于从移位寄存器供给的采样脉冲。根据电流源电路的构成或驱动方式等,采样脉冲不直接输入,而输入从与设定控制线(在图6中,未图示)连接的逻辑运算器的输出端子供给的信号。

此外,上述逻辑运算器的2个输入端子,1个输入采样脉冲,另一个输入从设定控制线供给的信号。即,电流源电路420的设定按照采样脉冲或从与设定控制线连接的逻辑运算器的输出端子供给的信号的时序进行。

再有,图42示出具有设定控制线和逻辑运算器的信号线驱动电路。在图42所示的结构中,也可以配置开关等去代替逻辑运算器。

此外,电流源电路420的结构可以任意使用图23、24、38、37、40等所示的电流源电路420的结构。

进而,在电流源电路420中,不仅采用1种结构,也可以采用多种结构。再有,当在电流源电路420中使用图23(A)、图24(A)所示的结构时,在进行输入动作的期间,不能进行设定动作。因此,有必要在不进行输入动作的期间进行设定动作。但是,在1帧中,因不进行输入动作的期间有时是分散的,故这时最好不按顺序选择各列,而可以选择任意列。因此,作为移位寄存器,最好使用能随机选择的译码电路等。作为一个例子,图43示出译码电路。若使用图43所示的译码电路,则电流源电路的设定动作也不是从第1列到最后1列按顺序进行,而是可以随机进行。由此,进行设定动作的时间长度可以任意设定得很长。

除上述译码电路之外,还可以使用图44(A)所示的电路。在图44(A)中,从移位寄存器输出的脉冲和从输出控制线(第1~第3输出控制线)供给的信号输入逻辑运算器。如图44(B)所示,通过控制各输出控制线的脉冲,可以从第1列到最后1列按顺序输出采样脉冲。即,可以输出和过去一样的波形。

此外,当想要进行和过去不同的动作时,如图45(A)所示,在将第1输出控制线置于选择状态的状态下,使第2和第3输出控制线为非选择状态。这样,第1列的采样脉冲可以在比过去长的期间内输出。因此,在输出第1列采样脉冲之后,输出第4列采样脉冲。同样,如图45(B)所示,在将第2输出控制线置于选择状态的状态下,使第1和第3输出控制线为非选择状态。这样,第2列的采样脉冲可以在比过去长的期间内输出。而且,在输出第2列采样脉冲之后,输出第5列采样脉冲。在上述结构中,从第1列到最后1列不是完全随机进行选择,但可以在比通常长的期间内只选择某1特定的列。因此,可以更自由地进行电流源电路的设定动作。

进而,也可以使用图46所示的电路。在图46中,根据控制1和控制2来控制其动作。若使控制1和控制2处于选择状态,则配置在第1移位寄存器和第2移位寄存器之间的开关变成导通状态,配置在第2移位寄存器和第3移位寄存器之间的开关变成导通状态。即,第1移位寄存器、第2移位寄存器和第3移位寄存器变成接通的状态。在这样的状态下,若输入启动脉冲信号SP,则从第1移位寄存器来的脉冲移位到第2移位寄存器中,从第2移位寄存器来的脉冲移位到第3移位寄存器中。即,可以输出和过去一样的波形。而且,当想要进行和过去不同的动作时,使控制1处于非选择状态。这样,配置在第1移位寄存器和第2移位寄存器之间的开关变成非导通状态,配置在第2移位寄存器和SP1之间的开关变成导通状态。而且,将启动脉冲信号输入到SP1而不是SP。这样,从第2移位寄存器输出采样脉冲。即,在从第1列到最后1列中,从中间的列开始输出采样脉冲。此外,当进而想要进行别的动作时,使控制2处于非选择状态。这样,配置在第2移位寄存器和第3移位寄存器之间的开关变成非导通状态,配置在第3移位寄存器和SP2之间的开关变成导通状态。而且,将启动脉冲信号输入SP2。这样,从第3移位寄存器开始输出采样脉冲。这样,在图46的结构中,从第1列到最后一列不是完全随机进行选择,但可以只选择某特定范围的列。这时,通过降低时钟信号的频率,可以在比过去长的期间内进行选择。因此,可以更自由地进行电流源电路的设定动作。

这样,便产生各种各样的优点,譬如,可以随机地、或在某种程度上自由地选择列或电流源电路并进行电流源电路的设定动作。例如,当能进行设定动作的期间在1帧中分散开时,可以选择任意的列,则可以提高自由度,并延长设定动作的时间。其它的优点还有,可以使电流源电路420中的电容元件(例如,相当于图23(A)的电容元件103、图23(B)的电容元件123和图23(B)的电容元件107等)的电荷泄漏的影响不太明显。

在电流源电路420中配置电容元件。但是,可以用晶体管的栅极电容等去代替电容元件。该电容元件通过电流源电路的设定动作来积蓄电荷。电流源电路的设定动作在理想的情况下只在电源输入时进行1次即可。即,在使信号线驱动电路动作时,只在进行该动作的最初的期间进行1次即可。这是因为电容元件积蓄的电荷量不变,也不必使其随动作状态或时间等变化。实际上,在电容元件中,或是有各种各样的噪声,或是与电容元件连接的晶体管有漏电流流过。结果,有时,电容元件积蓄的电荷量会随时间变化。当电荷量变化时,从电流源电路输出的电流、即输入象素的电流也变化。结果,象素的辉度变化。因此,为了使电容元件积蓄的电荷不变,必须以某一周期定期进行电流源电路的设定动作,使电荷重新充电,使变化了的电荷再次恢复,并重新保持正确的电荷量。

假如电容元件的电荷变动量大时,若进行电流源电路的设定动作,使电荷重新充电,使变化了的电荷再次恢复,并重新保持正确的电荷量,则随之而来的是电流源电路输出的电流量的变动也变大。因此,若从第1列开始按顺序进行设定动作,则电流源电路输出的电流量的变动有时会对显示产生妨碍,甚至达到不能目视确认的程度。即,从第1列开始顺序产生的象素辉度的变化有时会对显示产生妨碍,甚至达到不能目视确认的程度。这时,若不从第1列开始按顺序进行设定动作,而随机进行设定动作,则可以使电流源电路输出的电流量的变动不太明显。这样,通过随机选择多根布线,可以带来各种各样的优点。

另一方面,当电流源电流420采用图23(C)~(E)所示的结构时,设定动作和输入动作可以同时进行。但是,当使用设定动作和输入动作可以同时进行的电流源电路时,因或者使电流源电路输出的电流量的变动不太明显,或者使进行设定动作的期间变长都有可能实现,所以能随机选择这一点很有效。

此外,在图6(B)中,是一列一列地进行设定动作的,但并不限于此。也可以如图47所示那样,同时多列进行设定动作。这里,将同时多列进行设定动作称作多相化。再有,在图47中,配置了2个参考恒流源109,但也可以根据与该2个参考恒流源分开配置的参考恒流源来进行设定动作。

下面,说明图6(B)所示的恒流电路414的详细结构及其动作。

这里,图5表示电流源电路的一部分使用图23(C)的结构时的电路。图48示出电流源电路的一部分使用图23(A)的结构时的电路。图3、4如图2所示那样,是1列配置多个(2个)电流源电路的电路,并示出电流源电路的一部分使用图23(A)的结构时的电路。首先,说明图3、4所示的构成。

首先,说明具有图6(A)所示结构的电流源电路的恒流电路414。在图6(A)所示的结构中,将信号保持在电流源电路中的设定动作和从电流源电路向象素输入信号的动作(输入动作)不能同时进行。因此,最好对每一根信号线设置2个电流源电路,1个电流源电路进行设定动作,另一个电流源电路进行输入动作。

在图3、4的各列设置的电流源电路420中,是否对信号线Si(1≤i≤n)输出规定的信号电流由具有从第2锁存电路413输入的数字视频信号的信息进行控制。

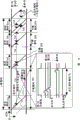

在图3中,电流源电路420具有第1电流源电路421和第2电流源电路422。而且,第1电流源电路421和第2电流源电路422一个进行设定动作,另一个进行输入动作。第1电流源电路421和第2电流源电路422具有多个电路元件。第1电流源电路421具有NAND70、反相器71、反相器72、模拟开关73、模拟开关74、晶体管75~77及电容元件78。第2电流源电路422具有NAND80、反相器81、反相器82、反相器89、模拟开关83、模拟开关84、晶体管85~87及电容元件88。在本实施形态中,晶体管75~77和晶体管85~87全部是n沟道型。

在第1电流源电路421中,NAND70的输入端子与移位寄存器411和控制线92连接,NAND70的输出端子与反相器71的输入端子连接。反相器71的输出端子与晶体管75和晶体管76的栅极连接。

模拟开关具有4个端子。而且根据输入到4个端子中的2个端子的信号,使剩下的2个端子之间导通或截止。

模拟开关73根据从NAND70的输出端子输入的信号和从反相器71的输出端子输入的信号选择导通或截止。反相器72的输入端子与控制线92连接。而且,模拟开关74根据从控制线92和反相器72的输出端子输入的信号选择导通或截止。

晶体管75的源极区和漏极区,一个与电流线93连接,另一个与晶体管77的源极区和漏极区的一个连接。晶体管76的源极区和漏极区,一个与电流线93连接,另一个与电容元件78的一个端子和晶体管77的栅极连接。晶体管77的源极区和漏极区,一个与Vss连接,另一个与模拟开关73连接。

参考恒流源(未图示)与电流线93连接。

电容元件78的一个电极与Vss连接,另一个电极与晶体管77的栅极连接。电容元件78起保持晶体管77的栅源极间电压的作用。

在第2电流源电路422中,反相器89的输入端子与控制线89连接。而且,反相器89的输出端子与NAND80的一个输入端子连接。NAND80的另一个输出端子与移位寄存器411连接。NAND80的输出端子与反相器81的输入端子连接。反相器81的输出端子与晶体管85和晶体管86的栅极连接。

模拟开关83根据从NAND80的输出端子输入的信号和从反相器81的输出端子输入的信号选择导通或截止。反相器82的输入端子与控制线92连接。而且,模拟开关84根据从控制线92和反相器82的输出端子输入的信号选择导通或截止。

晶体管85的源极区和漏极区,一个与电流线93连接,另一个与晶体管87的源极区和漏极区中的一个连接。晶体管86的源极区和漏极区,一个与电流线93连接,另一个与电容元件88的一个端子和晶体管87的栅极连接。晶体管87的源极区和漏极区,一个与Vss连接,另一个与模拟开关83连接。

电容元件88的一个电极与Vss连接,另一个电极与晶体管87的栅极连接。电容元件88起保持晶体管87的栅源极间电压的作用。

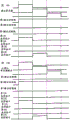

这里,使用图28说明图3的电流源电路的动作。

图28示出设定控制线92和第1~3行扫描线的时序图。而且,使用图3说明期间A的电流源电路420的动作,使用图4说明期间B的电流源电路420的动作。在期间A,第1电流源电路421进行设定动作,第2电流源电路422进行输入动作。在期间B,第1电流源电路421进行输入动作,第2电流源电路422进行设定动作。

首先,说明期间A的电流源电路420的动作。开始说明进行设定动作的第1电流源电路421的动作。

在期间A,从设定控制线92输入的信号是High。而且,按顺序,从移位寄存器411项各列输入采样脉冲(相当于High信号)。NAND70对从移位寄存器411和设定控制线92输入的信号(均为High)进行逻辑运算再输出Low。反相器71对输入的信号(Low)进行逻辑运算,再输出High。

从反相器71的输出端子向晶体管75和76的栅极输入信号(High),晶体管75和76导通。这样,从电流线93供给的电流经晶体管75和76,流过电容元件78再到达Vss。电容元件78开始积蓄电荷。

然后,电容元件78逐渐积蓄电荷,两电极间开始产生电位差。当该电位差达到Vth时,晶体管77由截止变导通。电容元件78进行电荷的积蓄,直到其两电极的电位差、即晶体管77的栅源极间电压达到所要的电压。换言之,继续进行电荷地积蓄直至达到使晶体管77中能够流过信号电流时的电压。然后,经过一定的时间,结束电荷的积蓄。

这时,模拟开关73和模拟开关74导通。

其次,说明进行输入动作(向象素输出电流)的第2电流源电路422的动作。在第2电流源电路422中,已进行设定动作,电容元件88保持规定的电荷。

在期间A,从设定控制线92输入的信号是High。反相器89对输入的信号(High)进行逻辑运算再输出Low。NAND80对从反相器89和移位寄存器411输入的信号进行逻辑运算,再输出High。反相器81对输入的信号(High)进行逻辑运算再输出Low。

从反相器81的输出端子向晶体管85和86的栅极输入信号(Low),晶体管85和86截止。

另一方面,模拟开关83因从NAND80的输出端子输入的信号(High)和从反相器81的输出端子输入的信号(Low)而导通。模拟开关84因从设定控制线92输入的信号(High)和从反相器82的输出端子输入的信号(Low)而导通。

电容元件88保持规定的电荷,晶体管87导通。在该状态下,晶体管87的漏极电流和信号电流相等。

模拟开关90根据从第2锁存电路413输入的信号和从反相器90输入的信号导通或截止。在图3所示的构成中,当从第2锁存电路413输入High信号时,模拟开关90导通,当从第2锁存电路413输入Low信号时,模拟开关90截止。

这里,假定从第2锁存电路413输入High信号,模拟开关90导通。这样,电流从信号线(Si)流过晶体管87再到达Vss。这时的电流值和信号电流相等。换言之,规定的信号电流供给与信号线(Si)连接的象素。

这时,若晶体管87工作在饱和区,即使该晶体管87的源漏极间的电压变化,供给象素的电流也不变。

其次,使用图4说明期间B的电流源电路420的动作。首先,说明进行输入动作(向象素输出电流)的第1电流源电路421的动作。在第1电流源电路421中,已进行设定动作,电容元件78保持规定的电荷。

在期间B,从设定控制线92输入的信号是Low。NAND70对从移位寄存器411和设定控制线92输入的信号进行逻辑运算,再输出High。反相器71对输入的信号(High)进行逻辑运算再输出Low。

从反相器71的输出端子向晶体管75和76的栅极输入信号(Low),晶体管75和76截止。

另一方面,模拟开关73因从NAND70的输出端子输入的信号(High)和从反相器71的输出端子输入的信号(Low)而导通。模拟开关74因从设定控制线92输入的信号(Low)和从反相器72的输出端子输入的信号(High)而导通。

电容元件78保持规定的电荷,晶体管77导通。在该状态下,晶体管77的漏极电流和信号电流相等。

这里,假定从第2锁存电路413输入High信号,模拟开关90导通。这样,电流从信号线(S1)流过晶体管77再到达Vss。这时的电流值和信号电流相等。换言之,规定的信号电流供给与信号线(S1)连接的象素。

这时,若晶体管77工作在饱和区,则即使该晶体管77的源漏极间的电压变化,供给象素的电流也不变。

其次,说明在期间B进行设定动作的第2电流源电路422的动作。

在期间B,从设定控制线92输入的信号是Low。反相器89对输入的信号(Low)进行逻辑运算,再输出High。NAND80对从反相器89和移位寄存器411输入的信号(一个是High)进行逻辑运算,再输出Low。然后,反相器81对输入的信号(Low)进行逻辑运算再输出High。

从反相器81的输出端子向晶体管85和86的栅极输入信号(High),晶体管85和86导通。这样,从电流线93供给的电流经晶体管85和86,流过电容元件88再到达Vss。接着,电容元件88开始积蓄电荷。

然后,电容元件88逐渐积蓄电荷,两电极间开始产生电位差。当该电位差达到Vth时,晶体管87由截止变导通。电容元件88进行电荷的积蓄,直到其两电极的电位差、即晶体管87的栅源极间电压达到所要的电压。换言之,继续进行电荷地积蓄直至达到使晶体管87中仅能够流过信号电流时的电压。这时,模拟开关83和84截止。

再有,在使用图28说明的上述动作中,每一行都进行设定动作和输入动作的切换。但是,本发明不限于此。也可以每几行才进行设定动作和输入动作的切换。

这里,设图3、4所示的电流源电路420所具有的晶体管全部是n沟道型,但本发明不限于此。在图3、4所示的电流源电路420中,也可以使用p沟道型的晶体管。再有,使用p沟道型的晶体管时的电流源电路420的动作除了电流流动的方向改变和电容元件不与Vss而与Vdd连接之外,和上述动作相同。

此外,当图3、4所示的电流源电路420使用p沟道型的晶体管时、Vss和Vdd互换时,即电流流动的方向不变时,若与图23和图24对比使用,则用起来很容易。此外,单纯作为开关使用的晶体管,什么样的极性都可以。

其次,使用图5说明和上述不同的恒流电路414的结构及其动作。在设在各列的电流源电路420中,是否对信号线Si(1≤i≤n)输出规定的信号电流由具有从第2锁存电路413输入的数字视频信号所具有的信息进行控制。

再有,图5的结构如图1所示,是1列配置1个电流源电路的电路。

在图5(A)~(C)中,电流源电路420具有晶体管94~97和电容元件99。在本实施形态中,晶体管94~97全部是n沟道型。

晶体管94的栅极输入从第2锁存电路413来的信号。晶体管94的源极区和漏极区,一个与源极信号线(S1)连接,另一个与晶体管95的源极区和漏极区中的一个连接。

晶体管97和晶体管98的栅极输入从移位寄存器411来的采样脉冲。晶体管97的源极区和漏极区,一个与晶体管96的源极区和漏极区中的一个连接,另一个与电容元件99的一个电极连接。晶体管98的源极区和漏极区,一个与电流线93连接,另一个与晶体管96的源极区和漏极区中的一个连接。

电容元件99的一个电极与晶体管95和晶体管96的栅极连接,另一个电极与Vss连接。电容元件99起保持晶体管95和晶体管96的栅源极间电压的作用。

晶体管95的源极区和漏极区,一个与Vss连接,另一个与晶体管94的源极区和漏极区中的一个连接。

这里,使用图5(A)~图5(C)说明图5所示的电流源电路420的动作。

首先,从移位寄存器411向晶体管97和98的栅极输入采样脉冲,两晶体管导通。这样,从电流线93供给的电流经晶体管98和97,流向电容元件99。这时,第2锁存电路413不向晶体管94的栅极输入信号,晶体管94截止。

接着,电容元件99逐渐积蓄电荷,两电极间开始产生电位差。当该电位差达到Vth时,晶体管95和96导通。

接着,电容元件99进行电荷的积蓄,直到其两电极的电位差、即晶体管95和96的栅源极间电压达到所要的电压。换言之,继续进行电荷的积蓄直至达到使晶体管95和96中仅能够流过与信号电流对应的电流时的电压(图5(A))。

接着,经过一定的时间,结束电荷的积蓄(图5(B))。

接下来,从第2锁存电路413输入的信号(相当于数字视频信号)使晶体管94导通。这时,移位寄存器411不向晶体管94的栅极输入采样脉冲,晶体管97和98截止。而且,因电容元件99保持规定的电荷,故晶体管95和96导通。这样,电流从信号线(S1)经晶体管94和95向Vss方向流去。这时的电流值和信号电流相等。换言之,向与信号线(S1)连接的象素供给规定的信号电流。

这时,如果晶体管95工作在饱和区,则即使晶体管95的源漏极间的电压变化,供给象素的电流也不变。

此外,在本实施形态中,具有图5所示的电流源电路420的晶体管全部是n沟道型,但本发明不限于此。在图5所示的电流源电路420中,也可以使用p沟道型的晶体管。再有,使用p沟道型的晶体管时的电流源电路420的动作除了电流流动的方向改变和电容元件不与Vss而与Vdd连接之外,和上述动作相同。

此外,如图21、图23(C)~图23(E)、图24(B)~图24(D)等所示,具有电流源电路420的电路元件可以具有不同的连接结构。这时的电流源电路420的动作因和使用图5说明了的电流源电路420的动作相同,故在本实施形态中省略其说明。

此外,当图5所示的电流源电路420使用p沟道型的晶体管时、Vss和Vdd互换时,即电流流动的方向不变时,若与图23和图24对比使用,则用起来很容易。再有,单纯作为开关使用的晶体管,什么样的极性都可以。

再有,图5的结构如图1所示,是1列配置1个电流源电路的电路。这时,若电流源电路420使用图23(A)、24(A)所示的构成,则在进行输入动作(向象素输出电流)的期间不能进行设定动作。因此,必须在不进行输入动作(向象素输出电流)的期间进行设定动作。另一方面,若电流源电路420使用图23(C)~(E)所示的结构,则即使1列配置1个电流源电路,也能同时进行设定动作和输入动作。

接下来,图49、图50、图51示出图42(A)(B)所示的恒流电路414的详细构成。这里,图49示出对和图42(B)中的恒流电路414相当的部分使用图1所示的电路的结构,进而示出对电流源电路的部分使用图23(C)的结构。图50示出对和图42(B)中的恒流电路414相当的部分使用图1所示的电路的结构及对电流源电路的部分使用图23(A)的结构。图51示出对和图42(B)中的恒流电路414相当的部分使用图2所示的电路的结构,进而示出对电流源电路的部分使用图23(A)的构成。

再有,在图49、图50所示的结构中,配置了逻辑运算器,但也可以取代该逻辑运算器而配置开关等。上述逻辑运算器因控制是否进行电流源电路的设定动作的切换,故只要是能够对切换该设定动作进行控制的电路,使用什么样的电路都行。此外,在图51中,通过控制从第1设定控制线供给的信号去切换是否进行电流源电路的设定动作。此外,通过控制从第2设定控制线供给的信号,在对每1列配置的2个电流源电路中,控制使用哪个电流源电路进行设定动作,使用哪个电流源电路进行输入动作。

接下来,说明与图34对应的情况。到此为止,说明了按线的顺序驱动的情况。下面,说明按点的顺序驱动的情况。在图52(A)中,从视频线供给的视频信号按照由移位寄存器411供给的采样脉冲的时序进行采样。电流源电路420的设定按照由移位寄存器411供给的采样脉冲的时序进行。作为1个例子,在具有图52(A)的结构时,按点的顺序进行驱动。

再有,经端子a输入电流源电路420的信号因电流源电路的结构或驱动方式等原因,采样脉冲不直接输入,而是输入从与设定控制线(在图52(A)中未示出)连接的逻辑运算器的输出端子供给的信号。上述逻辑运算器的2个输入端子,一个输入采样脉冲,另一个输入从设定控制线供给的信号。即,电流源电路420的设定按照采样脉冲或从与设定控制线连接的逻辑运算器的输出端子供给的信号的时序进行。

再有,只在输出采样脉冲再从视频线供给视频信号的期间,开关101(信号电流控制开关)才导通,并且,在不输出采样脉冲、视频线不供给视频信号时,开关101(信号电流控制开关)截止,在这种情况下不能正确动作。这是因为在象素中用来输入电流的开关一直处于导通状态。在该状态下,若开关101(信号电流控制开关)截止,因不能对象素输入电流,故不能输入正确的信号。

因此,为了能保持从视频线供给的视频信号,并维持开关101(信号电流控制开关)的状态,配置锁存电路452。锁存电路452可以单单由电容元件和开关构成,也可以由SRAM电路构成。这样,输出采样脉冲,按顺序对每1列从视频线供给视频信号,根据该视频信号使开关101处于(信号电流控制开关)导通或截止的状态,控制对象素的电流供给,由此,可以实现点顺序驱动。

但是,当按顺序从第1列到最后1列进行选择时,在从第1列到最后1列中,在最初的列中,向象素输入信号的期间长。另一方面,在从第1列到最后1列中,最后的列中即使输入视频信号,下一行的象素也会很快被选中。结果,向象素输入信号的期间变短。这时,如图52(B)所示,通过将配置在象素部402的扫描线从中央分开,可以使向象素输入信号的期间变长。这时,在象素部402的左侧和右侧各配置1个扫描线驱动电路,使用该扫描线驱动电路驱动象素。这样,即使是同一行的象素,右侧的象素和左侧的象素输入信号的期间可以错开。图52(C)示出配置在第1、2行的右侧和左侧的扫描线驱动电路的输出波形和移位寄存器411的启动脉冲(S-SP)。通过这样来动作,即便是左侧的象素,也能够使向象素输入信号的期间变长,所以,容易进行点顺序驱动。

再有,电流源电路420的设定动作可以按照任意的时序、对配置在任意列的电流源电路、进行任意的次数,而与是线顺序驱动还是点顺序驱动无关。但是,理想的情况是,只要连接在配置于电流源电路420中的晶体管的栅源极之间的电容元件保持规定的电荷,则只在进行设定动作时进行1次即可。或者,可以在电容元件保持的规定的电荷放电(变化)时进行。此外,关于电流源电路420的设定动作,进行所有列的电流源电路420的设定动作不管需要多长的期间都可以。即,可以在1帧期间内进行所有列的电流源电路420的设定动作。或者,可以在1帧期间内进行几列的电流源电路420的设定动作,结果,花费好几帧的期间进行所有列的电流源电路420的设定动作亦可。

此外,在本实施形态中,说明了对各列配置1个电流源电路的情况,但本发明不限于此,也可以配置多个电流源电路。

此外,对于本发明的信号线驱动电路中的电流源电路,图87示出其线路图,图88示出对应的电路图。

具有上述结构的本发明,可以抑制TFT的特性离散的影响,向外部供给所要的电流。

本实施形态可以和实施形态1~3任意组合。

(实施形态5)

在本实施形态中,说明图15(A)所示的信号线驱动电路的详细结构及其动作,但只就进行3位数字灰度显示时使用的信号线驱动电路403进行说明。

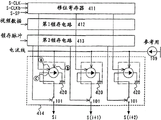

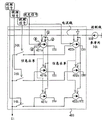

在图26中,示出进行3位数字灰度显示时使用的信号线驱动电路403的概略图。信号线驱动电路403具有移位寄存器411、第1锁存电路412、第2锁存电路413和恒流电路414。

简单说明其动作,移位寄存器411使用多个触发电路(FF)等构成,输入时钟信号(S-CLK)、启动脉冲(S-SP)和反相时钟信号(S-CLKb)。按照这些信号的时序,依次输出采样脉冲。

从移位寄存器411输出的采样脉冲输入第1锁存电路412。第1锁存电路412输入3位数字视频信号(数字数据1~数字数据3),按照输入采样脉冲的时序将视频信号保持在各列中。

在第1锁存电路412中,当直到最后一列数字视频信号保持完毕时,在水平回描线期间,向第2锁存电路413输入锁存脉冲,第1锁存电路412保持的3位视频信号(数字数据1~数字数据3)一齐向第2锁存电路413传送。这样,第2锁存电路413保持的3位视频信号(数字数据1~数字数据3)整行地同时输入恒流电路414。

在第2锁存电路413保持的3位数字视频信号(数字数据1~数字数据3)输入恒流电路414的期间,移位寄存器411再次输出采样脉冲。此后,重复该动作,进行1帧视频信号的处理。

再有,恒流电路411有时具有将数字信号变换成模拟信号的作用。此外,恒流电路414设置多个电流源电路420。在图27中,示出从第i列到第(i+2)列的3根信号线的信号线驱动电路的概略图。

再有,在图27中,示出配置了与各位对应的参考恒流源109的情况。

电流源电路420具有端子a、端子b和端子c。电流源电路420由经端子a输入的信号控制。此外,经端子b,从与电流线连接的参考恒流源109供给电流。在电流源电路420和与信号线Sn连接的象素之间设置开关(信号电流控制开关)111~113,上述开关(信号电流控制开关)111~113由1位~3位视频信号控制。当视频信号是明信号时,从电流源电路420向象素供给电流。相反,当视频信号是暗信号时,控制上述开关(信号电流控制开关)111~113,不向象素供给电流。即,电流源电路420具有流动规定电流的能力,是否向象素供给该电流由开关(信号电流控制开关)111~113控制。

再有,经端子a输入到电流源电路420的信号相当于从移位寄存器供给的采样脉冲。根据电流源电路的结构或驱动方式等,采样脉冲不直接输入,而输入从与设定控制线(在图27中,未图示)连接的逻辑运算器的输出端子供给的信号。上述逻辑运算器的2个输入端子,1个输入采样脉冲,另一个输入从设定控制线供给的信号。即,电流源电路420的设定按照采样脉冲或从与设定控制线连接的逻辑运算器的输出端子供给的信号的时序进行。

在图27中,当配置在各信号线的电流源电路420由图23(A)(B)所示的电路构成时,从与控制线连接的逻辑运算器的输出端子输入的信号相当于设定信号。此外,当对各信号线配置的电流源电路420由图23(C)~(E)所示的电路构成时,从移位寄存器来的采样脉冲相当于设定信号。

这里,图53示出在图27所示的结构中使用了上述设定控制线和逻辑运算器的结构。再有,在图53中配置了逻辑运算器,但也可以配置开关等去代替逻辑运算器。

再有,在图27或图53中,电流线和参考恒流源与各位对应配置。而且,从各位的电流源供给的电流值的总和供给信号线。即,电流电路414具有数字一模拟变换的功能。

此外,在图27或图53所示的信号线驱动电路中,对1位~3位中的每一个分别配置专用的参考恒流源109,但本发明不限于此。如图54所示,也可以配置个数比位数少的参考恒流源109。例如,只配置最高位(这里是第3位)的参考恒流源109,设定从配置在1列的多个电流源电路选出的1个电流源电路。而且,使用已进行设定动作的电流源电路进行其它电流源电路的动作。换言之,在配置于1列的多个电流源电路中,可以共享设定信息。

例如,只对3位用的电流源电路420进行设定动作。而且,使用已进行设定动作的电流源电路420,使其它1位用、2位用的电流源电路420共享信息。更具体地说,在电流源电路420中,将供给电流的晶体管(在图23(A)中,相当于晶体管102)的栅极端子连接起来,把源极端子也连接起来。结果,共享信息的晶体管(供给电流的晶体管)的栅源极间的电压相等。

再有,在图54中,不是对最低位(这里是1位)的电流源电路、而是对最高位(这里是3位)的电流源电路也进行设定动作。而且,使用已进行设定动作的最高位的电流源电路,和其它电流源电路共享信息。这样,通过对值最大的位的电流源电路进行设定动作,可以减小位之间的电流源电路的特性离散的影响。当假如对最低位(这里是1位)的电流源电路进行设定动作、而和最高位的电流源电路共享信息时,若各电流源电路的特性离散,高位的电流值就不是正确的值。因高位的电流源电路输出的电流值大,一旦特性有一点点离散,则该离散的影响会很大。输出的电流值的离散也很大。相反,当对最高位(这里是3位)的电流源电路进行设定动作、而和最低位的电流源电路共享信息时,即使各电流源电路的特性离散,因输出电流值小,故因离散引起的电流值的差较小,影响就小。

而且,在本实施形态中,为了举例说明进行3位数字灰度显示的情况,而对每一根信号线设置3个电流源电路420。当将从与1根信号线连接的3个电流源电路420供给的信号电流设定为1∶2∶4时,可以按23=8级控制电流的大小。

电流源电路420的结构可以任意使用图23、24、37、38、40等所示的电流源电路420的结构。在电流源电路420中,也可以不仅采用1种构成而采用多种构成。

下面,作为一个例子,使用图7、图8、图29、图55说明图27、图54所示的恒流源电路414的详细结构及其动作。在设在图7的各列的电流源电路420中,是否对信号线Si(1≤i≤n)输出规定的信号电流受从第2锁存电路413输入的数字视频信号所具有的信息控制。

图55示出配置和位数相等个数的参考恒流源109、在图27所示的信号线驱动电路中使用图1所示的电流源电路、在电流源电路中使用图23(A)的构成的电路图。在图55中,在设定动作时,为了防止电流泄漏,使晶体管A~C截止。或者,也可以与晶体管A~C串联配置开关,使其在设定动作时断开。此外,图7示出配置和位数相等个数的参考恒流源109、在图27所示的信号线驱动电路中使用图2所示的电流源电路、在电流源电路中使用图23(A)所示结构的电路图。图8示出配置个数比位数少的参考恒流源109、在图54所示的信号线驱动电路中使用图1所示的恒流电路、在电流源电路中使用图23(C)所示结构的电路图。图29示出配置个数比位数少的参考恒流源109、在图54所示的信号线驱动电路中使用图1所示的恒流电路、在电流源电路中使用图23(A)所示结构的电路图。

电流源电路420具有由1位数字视频信号控制的第1电流源电路423a和第2电流源电路424a、由2位数字视频信号控制的第1电流源电路423b和第2电流源电路424b、由3位数字视频信号控制的第1电流源电路423c和第2电流源电路424c。此外,电流源电路420具有模拟开关170a和反相器171a、模拟开关170b、反相器171b、模拟开关170c和反相器171c。

第1电流源电路423a~423c和第2电流源电路424a~424c,一个进行设定动作,另一个进行向象素输入信号的动作(输入动作、向象素输入电流)。第1电流源电路423a~423c和第2电流源电路424a~424c具有多个电路元件。图7示出第1电流源电路423a和第2电流源电路424a,因第1电流源电路423b、423c和第2电流源电路424b、424c的电路图参考第1电流源电路423a和第2电流源电路424a,故在本实施形态中省略其图示。

第1电流源电路423a具有NAND150a、反相器151a、反相器152a、模拟开关153a、模拟开关154a、晶体管155a~157a和电容元件158a。第2电流源电路424a具有NAND160a、反相器161a、反相器162a、反相器169a、模拟开关163a、模拟开关164a、晶体管165a~167a和电容元件168a。在本实施形态中,晶体管155a~157a和晶体管165a~167a全部是n沟道型。

在第1电流源电路423a中,NAND150a的输入端子与移位寄存器411和第1控制线425a连接,NAND150a的输出端子与反相器151a的输入端子连接。反相器151a的输出端子与晶体管155a和晶体管156a的栅极连接。

模拟开关153a根据从NAND150a的输出端子输入的信号和从反相器151a的输出端子输入的信号选择导通或非导通。反相器152a的输入端子与第1控制线425a连接。模拟开关154a根据从第1控制线425a和反相器152a的输出端子输入的信号选择导通或非导通。

晶体管155a的源极和漏极区,一个与第1电流线426a连接,另一个与晶体管157a的源极区和漏极区的一个连接。晶体管156a的源极和漏极区,一个与第1电流线426a连接,另一个与电容元件158a的一个端子和晶体管157a的栅极连接。晶体管157a的源极和漏极区,一个与Vss连接,另一个与模拟开关153a连接。

电容元件158a的一个端子与Vss连接,另一个端子与晶体管157a的栅极连接。电容元件158a起保持晶体管157a的栅源极间电压的作用。

在第2电流源电路424a中,反相器169a的输入端子与第1控制线425a连接。反相器169a的输出端子与NAND160a的一个输入端子连接。NAND160a的另一个输入端子与移位寄存器411连接。NAND160a的输出端子与反相器161a的输入端子连接。反相器161a的输出端子与晶体管165a和晶体管166a的栅极连接。

模拟开关163a根据从NAND160a的输出端子输入的信号和从反相器161a的输出端子输入的信号选择导通或非导通。反相器162a的输入端子与第1控制线425a连接。模拟开关164a根据从第1控制线425a和反相器162a的输出端子输入的信号选择导通或非导通。

晶体管165a的源极和漏极区,一个与第1电流线426a连接,另一个与晶体管167a的源极区和漏极区的一个连接。晶体管166a的源极和漏极区,一个与第1电流线426a连接,另一个与电容元件168a的一个端子和晶体管167a的栅极连接。晶体管167a的源极和漏极区,一个与Vss连接,另一个与模拟开关163a连接。

电容元件168a的一个端子与Vss连接,另一个端子与晶体管167a的栅极连接。电容元件168a起保持晶体管167a的栅源极间电压的作用。

而且,因图7所示的第1电流源电路423a和第2电流源电路424a的动作和图3、图4所示的第1电流源电路421和第2电流源电路422的动作相同,故在本实施形态中省略其说明。

再有,在图7所示的电流源电路420中,从第1电流源电路423a或第2电流源电路424a供给的信号电流和从第1电流源电路423b或第2电流源电路424b供给的信号电流及从第1电流源电路423c或第2电流源电路424c供给的信号电流的总和流入信号线Si。即,若设定从第1电流源电路423a或第2电流源电路424a供给的信号电流和从第1电流源电路423b或第2电流源电路424b供给的信号电流及从第1电流源电路423c或第2电流源电路424c供给的信号电流为1∶2∶4,则可以按23=8级控制电流的大小。

在图7所示的电流源电路420中,利用3位数字视频信号选择模拟开关170a~170c的导通或截止。当假定模拟开关170a~170c全部导通时,供给信号线的电流变成从第1电流源电路423a或第2电流源电路424a供给的信号电流和从第1电流源电路423b或第2电流源电路424b供给的信号电流及从第1电流源电路423c或第2电流源电路424c供给的信号电流的总和。当假定只有模拟开关170a导通时,只有从第1电流源电路423a或第2电流源电路424a供给的信号电流供给信号线。

因从电流源电路供给的电流值不同,故有必要将流过第1电流线426a~第3电流线426c的电流值设定为1∶2∶4。

这里,图7所示的电流源电路420具有的晶体管全部是n沟道型,但本发明不限于此。电流源电路420也可以使用p沟道型晶体管。当使用p沟道型晶体管时,因电流源电路420的动作除了电流流动的方向不同和电容元件与Vdd而不与Vss连接之外均与上述动作相同,故省略其说明。

此外,在图7中,省略了电流源电路423b、423c和电流源电路424b、424c的详细电路结构的图示,但电流源电路423b、423c和电流源电路424b、424c不是图23(A)所示结构的电流源电路,可以使用图23(C)~(E)所示结构的电流源电路。即,进行多位数字灰度显示时使用的信号线驱动电路所使用的电流源电路可以将多种结构组合起来设计。

此外,当电流源电路使用p沟道型晶体管时,在不交换Vss和Vdd的情况下,即在电流流动的方向不变的情况下,若将图23和图24对照使用,则用起来很容易。此外,对单纯作为开关工作的晶体管的极性没有特别的限制。

其次,使用图8说明和上述不同的恒流电路414的结构及其动作。在图8的电流源电路420中,是否对信号线Si(1≤i≤n)输出规定的信号电流由从第2锁存电路413输入的数字视频信号所具有的信息进行控制。

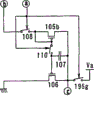

电流源电路420具有晶体管180~188和电容元件189。在本实施形态中,晶体管180~188全部是n沟道型。

晶体管180的栅极输入从第2锁存电路413来的1位数字视频信号。晶体管180的源极区和漏极区,一个与源极信号线(Si)连接,另一个与晶体管183的源极区和漏极区的一个连接。

晶体管181的栅极输入从第2锁存电路413来的2位数字视频信号。晶体管181的源极区和漏极区,一个与源极信号线(Si)连接,另一个与晶体管184的源极区和漏极区的一个连接。

晶体管182的栅极输入从第2锁存电路413来的3位数字视频信号。晶体管182的源极区和漏极区,一个与源极信号线(Si)连接,另一个与晶体管185的源极区和漏极区的一个连接。

晶体管183~晶体管185的源极区和漏极区,一个与Vss连接,另一个与晶体管180~晶体管182的源极区和漏极区的一个连接。晶体管186的源极区和漏极区,一个与Vss连接,另一个与晶体管188的源极区和漏极区的一个连接。

晶体管187和晶体管188的栅极输入从移位寄存器411来的信号。晶体管187的源极区和漏极区,一个与晶体管186的源极区和漏极区的一个连接,另一个与电容元件189的一个电极连接。晶体管188的源极区和漏极区,一个与电流线190连接,另一个与晶体管186的源极区和漏极区的一个连接。

电容元件189的一个电极与晶体管183~晶体管186的栅极连接,另一个电极与Vss连接。电容元件189起保持晶体管183~晶体管186的栅源极间电压的作用。

图8所示的电流源电路420的设计除追加了晶体管180、181、183、184之外,其他与使用图5所示的电流源电路420的动作相同。因此,这里省略图8所示的电流源电路420的动作说明。

再有,图8所示的电流源电路如图54所示,表示配置了个数比位数少的参考恒流源109的情况。

此外,在图8所示的电流源电路420中,晶体管183~185的漏极电流的总和流入信号线Si。这里,将晶体管183~185各自的漏极电流设定为1∶2∶4,可以按23=8级控制电流的大小。即,从晶体管183~185供给的电流值的差异起因于将晶体管183~185的W/L值设定为1∶2∶4,各自的导通电流设定为1∶2∶4。

而且,在图8所示的电流源电路420中,利用3位数字视频信号,来选择晶体管180~182的导通或截止。例如,当晶体管180~182全部导通时,供给信号线的电流是晶体管183~185的漏极电流的总和。当只有晶体管18导通时,只有晶体管183的漏极电流供给信号线。

这样,通过使晶体管183~185的栅极端子互相连接,可以共享设定动作的信息。再有,这里是在相同列的晶体管内共享信息,但本发明不限于此。例如,也可以和相同列之外的晶体管共享设定动作的信息。即,为了使设定动作的信息相同,也可以使晶体管的栅极端子与别的列的晶体管连接。由此,可以减少应设定的电流源电路的个数。因此,可以缩短进行设定动作所必要的时间。此外,因可以减少电路的数量,故可以减小线路图的面积。

此外,在图29中,示出与图8不同的电路构成的电流源电路420。在图29所示的电流源电路420中,取代晶体管186~188而配置开关191、192。

而且,在图29所示的电流源电路420中,因除了当开关191、192导通时从与电流线190连接的参考电流源(未图示)供给的电流流过电容元件189这一点之外,其他均和图27所示的电流源电路420的动作相同,故在此省略其说明。

再有,在图29中,在电流源电路的设定动作时,为了防止电流泄漏,使晶体管182截止。或者,也可以与晶体管182串联配置开关203,使开关203在设定动作时截止,而在除此之外的时间导通。这时的电流源电路由图56示出。

再有,图8、图29、图56的电流源电路420具有的晶体管全部是n沟道型,但本发明不限于此。电流源电路420也可以使用p沟道型晶体管。当使用p沟道型晶体管时,因电流源电路420的动作除了电流流动的方向不同和电容元件与Vdd而不与Vss连接之外其余均和上述动作相同,故在此省略其说明。

此外,当使用p沟道型晶体管构成电流源电路且不交换Vss和Vdd时,即在电流流动的方向不变的情况下,若将图23和图24对照使用,则用起来很容易。此外,亦能够容易实现多相化和进行点顺序驱动。

此外,在本实施形态中,说明了进行3位数字灰度显示时的信号线驱动电路的结构及其动作。但是,本发明不限于3位,可以进行任意位数的显示。此外,在本实施形态中,可以和实施形态1~4任意组合。

再有,在图27中,如图1所示,对1根信号线各配置1个与各个位对应的电流源电路。但是,也可以如图2所示,对1根信号线驱动电路配置多个与各个位对应的电流源电路。这时的图由图57示出。再有,图7的构成相当于在图27的结构中使用图57所示结构的情况。同样,在图54中,多个电流源电路共享设定信息。这时的图由图58示出。

其次,图59、图60、图61、图62示出图53所示的电路的详细结构。在图53所示的电路中,配置设定控制线或逻辑运算器,使用该设定控制线或逻辑运算器控制进行电流源电路的设定动作的时序。

图59示出当配置个数和位数相等的参考恒流源109、图53所示的信号线驱动电路使用图1所示的电流源电路、电流源电路使用图23(A)所示结构时的电路图。在图59所示的构成中,为了防止电流泄漏,在设定动作时使晶体管A~C截止。或者,也可以与晶体管A~C串联配置开关,并使该开关在设定动作时断开。若使图27的结构和图53的结构对应,则图59和图55对应。即,图59的构成和图53对应,图55的结构和图27对应。

图60示出当配置个数和位数相等的参考恒流源109、图53所示的信号线驱动电路使用图2所示的电流源电路、电流源电路使用图23(A)所示结构时的电路图。若使图27的结构和图53的结构对应,则图60和图7对应。即,图60的结构和图53对应,图7的结构和图27对应。

图61示出当配置个数比位数少的参考恒流源109、图53所示的信号线驱动电路象图54所示结构那样共享信息且使用图1所示的恒流电路、电流源电路使用图23(C)的构成时的电路图。若使图27的结构和图54的结构及图53的构成对应,则图61和图8对应。

图62示出当配置个数比位数少的参考恒流源109、图53所示的信号线驱动电路象图54所示的构成那样共享信息且使用图1所示的电流源电路、电流源电路使用图23(A)的构成时的电路图。若使图27的构成和图54的构成及图53的构成对应,则图62和图29对应。

再有,在图59、图60、图62中,配置了逻辑运算器,但也可以取代逻辑运算器而使用开关等。因上述逻辑运算器只对是否进行电流源电路的设定动作进行切换,故只要是能用于切换控制的电路,使用什么电路都可以。只是,在图60中,使用第4设定控制线,切换是否进行电流源电路的设定动作,使用第1~第3设定控制线控制对哪个电流源电路进行设定动作,使哪个电流源电路进行输入动作。此外,电流源电路的设定动作,可以不按顺序从第1列到最后1列进行而随机地进行。这时,作为移位寄存器411可以使用图43所示的译码电路等。此外,还可以使用图44、图45、图46所示的电路。

(实施形态6)

向电流源电路供给电流的参考恒流源109可以在衬底上和信号线驱动电路一体形成,也可以使用IC等配置在衬底的外部。当在衬底上一体形成时,可以使用图23~25、图38、图37、图40等所示的电流源电路中的任何一个形成。或者,也可以单单配置1个晶体管,根据加在栅极上的电压来控制电流值。在本实施形态中,说明参考恒流源109的结构及其动作。

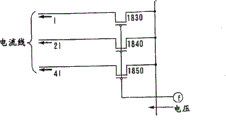

作为1个例子,图30示出最简单的情况。即,是对晶体管的栅极加电压再调节栅极电压的方式,而且示出需要3根电流线的情况。假如只需要1根电流线,只要单纯地从图30中删除晶体管1840、1850及与其对应的电流线即可。在图30中,通过调节加在晶体管1830、1840、1850的栅极电压,经端子f,从外部控制电流的大小。这时,若将晶体管1830、1840、1850的W/L值设计为1∶2∶4,则各自的导通电流变成1∶2∶4。

其次,在图31(A)中,说明从端子f供给电流的情况。如图30所示,当加栅极电压并进行调节时,有时电流值会因温度特性等原因而变动。但是,当象图31(A)那样输入电流时,可以抑制其影响。

再有,在图30、31(A)的结构的情况下,电流线持续流过电流的期间必须持续从端子f输入电压或电流。但是,当电流线不必流过电流时,则不必从端子f输入电压或电流。

此外,可以如图31(B)所示那样增加开关和电容元件。这样,即使向电流线供给电流时,也可以停止从参考IC供给(从端子f输入的电压或电流),并且功耗变小。在图30、图31所示的结构中,与配置在参考恒流源的其它电流源晶体管共享信息。即,晶体管1830、1840、1850的栅极端相互连接。

因此,图32示出各电流源电路进行设定动作的情况。在图27中,从端子f输入电流,利用从端子e供给的信号去控制时序。在图27所示的电路中,可以使用图23、24、图38、图37、图40等所示的结构。图32所示的电路是使用图23(A)的电路的例子。因此,设定动作和输入动作不能同时进行。故,在该电路中,对参考恒流源的设定动作需要按电流线不必流过电流的时序进行。

图33示出多相化的参考恒流源109的例子。即,相当于使用了图47所示的结构的参考恒流源109。在多相化的情况下,也可以使用图32、图30、图31的电路。但是,因向电流线供给的电流值相同,故如图33所示,若使用1个电流对各电流源电路进行设定动作,则可以减少从外部输入的电流数。

本实施形态可以和实施形态1~5任意组合。

(实施形态7)

在上面的实施形态中,主要说明了存在信号电流控制开关的情况。在本实施形态中,说明当没有信号电流控制开关时、即向有别于信号线其他布线供给和信号电流不成比例的电流(固定电流)的情况。这时,不必配置开关101(信号电流控制开关)。

再有,当不存在信号电流控制开关时,除了没有信号电流开关之外,其余和存在信号电流开关的情况一样。因此,进行简单的说明,省略对相同部分的说明。

将配置信号电流开关的情况和不配置的情况进行对比,图34和图1对应,图35和图2对应。图63(A)与图6(B)对应。在上面的实施形态中,利用视频信号控制信号电流控制开关,向信号线输出电流。在本实施形态中,向象素电流线输出电流。向信号线输出视频信号。

对于这时的象素结构,图63(B)示出其概略图。其次,简单说明象素的动作方法。首先,当开关晶体管导通时,通过信号线向象素输入视频信号,并保存在电容元件中。接着,根据视频信号的值,驱动用晶体管导通或截止。另一方面,电流源电路具有流过一定电流的能力。因此,当驱动用晶体管导通时,发光元件流过一定的电流而发光。当驱动用晶体管截止时,发光元件没有电流流过,不发光。这样来显示图像。只是,这时只能表现发光和不发光2种状态。因此,使用时间灰度法或面积灰度法等,以谋求多灰度化。

再有,对电流源电路部分可以使用图23、图24、图37、图38、图40等中的任何一种电路。而且,为了使电流源电路流过一定的电流,只要进行设定动作即可。当对象素的电流源电路进行设定动作时,通过象素电流线输入电流再执行。对象素的电流源电路进行的设定动作可以在任意时刻,以任意时序,执行任意次数。对象素配置的电流源电路进行的设定动作可以和用来显示图像的动作毫无关系地执行。当电流源电路内配置的电容元件保存的电荷泄漏时,可以进行设定动作。

其次,图64、图65示出图63(A)所示的恒流电路414的详细结构。图66、图67示出在图64、图65的结构中配置设定控制线和逻辑运算器并能控制进行信号线驱动电路的电流源电路的设定动作的时序的情况。这里,图64、图66示出在电流源电路部分使用图23(A)的情况下的电路。图65、67示出在电流源电路部分使用图23(E)的情况下的电路。再有,虽然图66、图67配置了逻辑运算器,但也可以用开关等代替。

此外,考虑在图63(A)所示的电流源电路部分使用图35所示结构的情况。图68示出这时的恒流源电路414的详细结构。此外,图69示出在图68的结构中配置设定控制线和逻辑运算器并能控制进行信号线驱动电路的电流源电路的设定动作的时序的情况。这里,图68、图69示出对电流源电路部分使用图23(A)的情况下的电路。在图68中,通过控制设定控制线,可以对一个电流源进行设定动作,同时,另一个电流源进行输入动作。同样,在图69中,通过控制第2设定控制线,可以对一个电流源进行设定动作,同时,另一个电流源能够进行输入动作。而且,通过控制第1设定控制线,可以控制进行信号线驱动电路的电流源电路的设定动作的时序。

这样,当不存在信号电流控制开关时,除了没有信号电流开关之外,其余和存在信号电流开关的情况一样。因此,省略详细的说明。

本实施形态可以和实施形态1~6任意组合。

(实施形态8)

使用图70说明本发明的实施形态。在图70(A)中,在象素部的上方配置信号线驱动电路,在下方配置恒流电路,在上述信号线驱动电路中配置电流源A、在恒流电路中配置电流源B。若设从电流源A、B供给的电流为IA、IB,向象素供给的信号电流为Idata,则IA=IB+Idata成立。而且,当向象素写入信号电流时,设定从电流源A、B供给电流。这时,当IA、IB变大时,可以提高信号电流对象素的写入速度。

这时,使用电流源A进行电流源B的设定动作。象素中流过由来自电流源A的电流减去电流源B的电流所得到的电流。因此,通过使用电流源A进行电流源B的设定动作,可以减小各种各样的噪声的影响。

在图70(B)中,参考恒流源(以下记作恒流源)C、E配置在象素部的上方和下方。而且,使用电流源C、E进行信号线驱动电路和恒流电路配置的电流源电路的设定动作。电流源D相当于设定电流源C、E的电流源,并从外部供给参考电流。

再有,在图70(B)中,也可以将配置在下方的恒流电路作为信号线驱动电路。由此,可以在上方和下方配置信号线驱动电路。而且,各自承担画面(整个象素部)上下半边的控制。这样,便可以同时控制2行象素。因此,可以延长对信号线驱动电路的电流源、象素和象素电流源等的设定动作(信号输入动作)的时间。故,可以更正确地进行设定。

本实施形态可以和实施形态1~7任意组合。

(实施例1)

在本实施例中,使用图14详细说明时间灰度方式。通常,在液晶显示装置或发光装置等显示装置中,帧频率是60Hz左右。即,如图14(A)所示,1秒钟进行60次左右的画面扫描。由此,可以使人的眼睛感觉不出来闪烁(画面的闪光)。这时,将进行1次画面扫描的期间称作1帧期间。

在本实施例中,作为1个例子,说明专利文献1的公报中公开的时间灰度方式。在时间灰度方式中,将1帧期间分割成多个子帧期间。这时的分割数大多和灰度的位数相等。这里,为简单起见,示出分割数和灰度位数相等的情况。即,在本实施例中,因为是3位灰度,故示出分割成3个子帧期间SF1~SF3的例子(图14(B))。

各子帧期间具有地址(写入)期间Ta和保持(发光)期间Ts。地址期间是对象素写入视频信号的期间,在各子帧期间中长度相等。保持期间是在地址期间根据象素写入的视频信号发光元件发光或不发光的期间。这时,保持期间Ts1~Ts3其长度比为Ts1∶Ts2∶Ts3=4∶2∶1。即,在表现n位灰度时,n个保持期间的长度比为2n-1∶2n-2∶......∶21∶20。而且,通过发光元件在哪个保持期间发光或不发光,决定1帧期间中各象素发光的期间的长度,由此来表现灰度。

其次,说明使用时间灰度方式的象素的具体动作,在本实施例中参照图16(B)所示的象素进行说明。图16(B)所示的象素使用电流输入方式。

首先,在地址期间Ta内进行以下动作。选择第1扫描线602和第2扫描线603,TFT606、607导通。这时,将流过信号线601的电流作为信号电流Idata。而且,当电容元件610积蓄了规定的电荷时,第1扫描线602和第2扫描线603的选择结束,TFT606、607截止。

其次,在保持期间Ts内进行以下动作。选择第3扫描线604,TFT609导通。因电容元件610保持刚才已写入的规定的电荷,故TFT608导通,从信号线605流过和信号电流Idata相等的电流。由此,发光元件611发光。

通过在各子帧期间进行以上动作来构成1帧期间。按照该方法,当想要增加显示灰度数时,可以增加子帧期间的分割数。此外,子帧期间的顺序如图14(B)(C)所示,不必按从高位到低位的顺序,在1帧期间可以随机排列。进而在各帧期间可以改变其顺序。

此外,图14(D)示出第m行扫描线的子帧期间SF2。如图14(D)所示,在象素中,地址期间Ta2一结束,便立即开始期间Ts2。

其次,说明在信号线驱动电路的电流源电路中进行设定动作的时序。

再有,在上述实施形态中对上述电流源电路能同时进行设定动作和输入动作的方式和不能同时进行的方式进行了说明。

在前者的设定动作和输入动作能同时进行的电流源电路中,对进行各动作的时序没有特别限定。这一点,对如图2或图54等那样1列配置多个电流源电路的情况也一样。但是,在后者的设定动作和输入动作不能同时进行的电流源电路中,有必要在进行设定动作的时序上下功夫。当采用时间灰度方式时,必须在不进行输出动作时进行设定动作。例如,在具有图1的驱动部的结构和图16(B)所示结构的象素的情况下,必须在象素部的哪一根扫描线都在非地址期间Ta的期间内进行设定动作。此外,在具有图34的驱动部的结构和图63(B)所示结构的象素的情况下,必须在象素配置的电流源电路不进行设定动作的期间进行驱动部配置的电流源电路的设定动作。

再有,这时,有时能低速设定控制电流源电路的移位寄存器的频率。由此,可以费点时间来正确进行电流源电路的设定动作。

或者,也可以使用图43等电路作为控制电流源电路的电路(移位寄存器)来随机地进行电流源电路的设定动作。此外,也可以使用图44、图45、图46等电路。这样,即使能进行设定动作的期间在1帧中是分散的,也能有效地利用这一期间进行设定动作。此外,所有的电流源电路的设定动作也可以不在1帧期间内而在好几帧期间内执行。这样,可以费点时间来正确进行电流源电路的设定动作。

再有,在具有图1的驱动部的结构和图16(B)所示结构的象素的情况下,输入动作可以在象素的扫描线被选择的期间(地址期间Ta)进行。此外,在具有图1的驱动部的结构和图63(B)所示结构的象素的情况下,可以在不对象素配置的电流源电路进行设定动作的期间进行驱动部配置的电流源电路的设定动作。

本实施例可以和实施形态1~8任意组合。

(实施例2)

在本实施例中,使用图13、图71说明设置在象素部的象素电路的构成例。

再有,若是具有包含输入电流的部分那样结构的象素,则对什么样的象素都可以适用。

图13(A)的象素具有信号线1101、第1和第2扫描线1102、1103、电流线(电源线)1104、开关用TFT1105、保持用TFT1106、驱动用TFT1107、变换驱动用TFT1108、电容元件1109和发光元件1110。信号线1101与电流源电路1111连接。

再有,电流源电路1111相当于配置在信号线驱动电路403中的电流源电路420。

图13(A)的象素,其开关用TFT1105的栅极与第1扫描线1102连接,第1电极与信号线1101连接,第2电极与驱动用TFT1107的第1电极和变换驱动用TFT1108的第1电极连接。保持用TFT1106的栅极与第2扫描线1103连接,第1电极与信号线1102连接,第2电极与驱动用TFT1107的栅极和变换驱动用TFT1108的栅极连接。驱动用TFT1107的第2电极与电流线(电源线)1104连接,变换驱动用TFT1108的第2电极与发光元件1110的一个电极连接。电容元件1109连接在变换驱动用TFT1108的栅极和第2电极之间,保持变换驱动用TFT1108的栅源极间的电压。电流线(电源线)1104和发光元件1110的另一个电极分别被输入规定的电位,并且相互具有电位差。

再有,图13(A)的象素相当于象素使用图38(B)的电路的情况。只是,因电流流动的方向不同,故晶体管的极性相反。图13(A)的驱动用TFT1107相当于图38(B)的TFT126,图13(A)的变换驱动用TFT1108相当于图38(B)的TFT122,图13(A)的保持用TFT1106相当于图38(B)的TFT124。

图13(B)的象素具有信号线1151、第1和第2扫描线1142、1143、电流线(电源线)1144、开关用TFT1145、保持用TFT1146、变换驱动用TFT1147、驱动用TFT1148、电容元件1149和发光元件1140。信号线1151与电流源电路1141连接。

再有,电流源电路1141相当于配置在信号线驱动电路403中的电流源电路420。

图13(B)的象素,其开关用TFT1145的栅极与第1扫描线1142连接,第1电极与信号线1151连接,第2电极与驱动用TFT1148的第1电极和变换驱动用TFT1147的第1电极连接。保持用TFT1146的栅极与第2扫描线1143连接,第1电极与驱动用TFT1148的第1电极连接,第2电极与驱动用TFT1148的栅极和变换驱动用TFT1147的栅极连接。变换驱动用TFT1147的第2电极与电流线(电源线)1144连接,变换驱动用TFT1147的第2电极与发光元件1140的一个电极连接。电容元件1149连接在变换驱动用TFT1147的栅极和第2电极之间,保持变换驱动用TFT1147的栅源极间的电压。电流线(电源线)1144和发光元件1140的另一个电极被分别输入规定的电位,并且相互具有电位差。

再有,图13(B)的象素相当于象素使用图6(B)的电路的情况。只是,因电流流动的方向不同,故晶体管的极性相反。图13(B)的变换驱动用TFT1147相当于图6(B)的TFT122,图13(B)的驱动用TFT1148相当于图6(B)的TFT126,图13(B)的保持用TFT1146相当于图6(B)的TFT124。

图13(C)的象素具有信号线1121、第1扫描线1122、第2扫描线1123、第3扫描线1135、电流线(电源线)1124、开关用TFT1125、象素用电流线1138、擦除用TFT1126、驱动用TFT1127、电容元件1128、电流源TFT1129、镜TFT1130、电容元件1131、电流输入TFT1132、保持TFT1133和发光元件1136。象素用电流线1138与电流源电路1137连接。

图13(C)的象素,其开关用TFT1125的栅极与第1扫描线1122连接,开关用TFT1125的第1电极与信号线1121连接,开关用TFT1125的第2电极与驱动用TFT1127的栅极和擦除用TFT1126的第1电极连接。擦除用TFT1126的栅极与第2扫描线1123连接,擦除用TFT1126的第2电极与电流线(电源线)1124连接。驱动用TFT1127的第1电极与发光元件1136的一个电极连接,驱动用TFT1127的第2电极与电流源TFT1129的第1电极连接。电流源TFT1129的第2电极与电流线1124连接。电容元件1131的一个电极与电流源TFT1129的栅极及镜TFT1130的栅极连接,另一个电极与电流线(电源线)1124连接。镜TFT1130的第1电极与电流线1124连接,镜TFT1130的第2电极与电流输TFT1132的第1电极连接。电流输入TFT1132的第2电极与电流线(电源线)1124连接。电流输入TFT1132的栅极与第3扫描线1135连接。电流保持TFT1133的栅极与第3扫描线1135连接,电流保持TFT1133的第1电极与象素用电流线1138连接,电流保持TFT1133的第2电极与电流源TFT1129的栅极及镜TFT1130的栅极连接。电流线(电源线)1124和发光元件1136的另一个电极被分别输入规定的电位,并且相互具有电位差。

这里,电流源电路1137相当于信号线驱动电路403(电源线)配置的电流源电路420。

再有,图13(C)的象素相当于图63(B)的象素使用图23(E)的电路的情况。因只是电流流动的方向不同,故晶体管的极性相反。再有,图13(C)的象素追加了擦除用TFT1126。利用擦除用TFT1126,可以自由控制亮灯期间的长度。

开关用TFT1125起控制视频信号对象素的供给的作用。擦除用TFT1126使电容元件1131保持的电荷放电,驱动用TFT1127根据保持在电容元件1131中的电荷控制导通或不导通。电流源TFT1129和镜TFT1130形成电流镜电路。电流线1124和发光元件1136的另一个电极被分别输入规定的电位,并且相互具有电位差。

即,当开关用TFT1125导通时,视频信号通过信号线1121输入象素,并保存在电容元件1128中。而且,驱动用TFT1127根据视频信号的值导通或截止。由此,当驱动用TFT1127导通时,发光元件流过一定的电流并发光。当驱动用TFT1127截止时,发光元件不流过电流,不发光。这样来显示图像。

再有,图13(C)的电流源电路由电流源TFT1129、镜TFT1130、电容元件1131、电流输入TFT1132和保持TFT1133构成。电流源电路具有流过一定电流的能力。该电流源电路通过象素用电流线1138流入电流,并进行设定动作。因此,即使构成电流源电路的晶体管的特性离散,从电流源电路向发光元件供给的电流的大小也不会产生离散。对象素的电流源电路的设定动作可以与开关用TFT1125或驱动用TFT1127的动作无关系地进行。

图71(A)的象素相当于图63(B)的象素使用图23(A)的电路的情况。只是,因电流流动的方向不同,故晶体管的极性相反。图71(A)的象素具有电流源TFT1129、电容元件1131、保持用TFT1133和象素用电流线1138(Ci)等。象素用电流线1138(Ci)与电流源电路1137连接。再有,电流源电路1137相当于信号线驱动电路403配置的电流源电路420。

图71(B)的象素相当于图63(B)的象素使用图24(A)的电路的情况。只是,因电流流动的方向不同,故晶体管的极性相反。图71(B)的象素具有电流源TFT1129、电容元件1131、保持用TFT1133和象素用电流线1138(Ci)等。象素用电流线1138(Ci)与电流源电路1137连接。再有,电流源电路1137相当于信号线驱动电路403配置的电流源电路420。

在图71(A)的象素和图71(B)的象素中,电流源TFT1129的极性不同。而且,因极性不同故电容元件1131和保持TFT1133的连接也不同。

这样,存在各种各样结构的象素。到此为止叙述的象素可以大致分成2种类型。第1类是向信号线输入与视频信号对应的电流的类型。图13(A)、图13(B)等与此相当。这时,信号线驱动电路如图1或图2所示,具有信号电流控制开关。

而且,另一个类型是向信号线输入视频信号、向象素用电流线输入和视频信号无关的固定电流的类型,即如图63(B)那样的象素的情况。这和图13(C)、图71(A)、图71(B)等相当。这时,信号线驱动电路如图34或图35所示那样,没有信号电流控制开关。

其次,说明与各象素的类型对应的时序图。首先,说明数字灰度和时间灰度组合的情况。只是,上述时序图取决于象素的类型或信号线驱动电路的构成。即,如已经说明的那样,对于信号线驱动电路的电流源电路的设定动作和输入动作能同时进行的情况和设定动作与输入动作不能同时进行的情况,时序有时不同。

首先,说明象素的类型是信号线输入与视频信号对应的电流的类型的情况。假定象素是图13(A)或图13(B),信号线驱动电路是图6(B)的结构。

接着,作为信号线驱动电路的电流源电路的设定动作和输入动作能同时进行的情况,说明图6(B)的恒流电路414使用图1所示的电路、电流源电路部分使用图23(C)的电路、即图5的情况。再有,作为设定动作和输入动作能同时进行的情况,图3、图4的电路也一样。

图72示出这时的时序图。为简单起见,假定表现4位灰度,子帧数是4个。首先,从最初的子帧期间SF1开始。一行一行地选择扫描线(图13(A)的第1扫描线1102或图13(B)的第1扫描线1132),从信号线(图13(A)的1101或图13(B)的1131)输入电流。该电流变成与视频信号对应的值。接着,若亮灯期间Ts1结束,便开始下一个子帧期间SF2,和SF1一样扫描。然后,开始下一个子帧期间SF3,同样进行扫描。只是,因亮灯期间的长度Ts3比地址期间的长度Ta3短,故强制地使其不发光。即,消去已输入的视频信号。或者,使电流不流过发光元件。为了进行消去,一行一行地选择第2扫描线(图13(A)的第2扫描线1103或图13(B)的第2扫描线1133)。这样,可以消去视频信号,使其处于不发光状态。然后,开始下一个子帧SF4。这里,和SF3一样进行扫描,并同样使其处于不发光状态。

以上是与图像显示动作、即与象素的动作有关的时序图。其次,说明信号线驱动电路配置的电流源电路的设定动作的时序。

这里,假定电流源电路是能同时进行设定动作和输入动作的电路。当象素的类型是向信号线输入与视频信号对应的电流的类型时,信号线驱动电路的电流源电路的输入动作(向象素输出电流)在各子帧期间中的地址期间(Ta1、Ta2等)进行。而且,信号线驱动电路的电流源电路的设定动作由从移位寄存器411来的采样脉冲控制。

而且,从移位寄存器输出的采样脉冲在某行扫描线(栅极线)被选中的期间向所有的列输出。从而,如图72所示,与从移位寄存器输出的采样脉冲同步,进行信号线驱动电路的电流源电路的设定动作。

其次,如图42所示,说明在信号线驱动电路上配置设定控制线和逻辑运算器的情况。而且,作为能对信号线驱动电路的电流源电路同时进行设定动作和输入动作的情况,说明图42中的恒流电路414使用图1所示的电路且电流源电路部分使用图23(C)时的情况、和图49的情况。

这时的时序图示于图73、图74和图75。

首先,关于图像显示动作、即与象素的开关晶体管和驱动用晶体管等有关的动作,因与上述图72的情况几乎一样,故省略其说明。

其次,说明信号线驱动电路配置的电流源电路的设定动作的时序。在图72的情况下,在各地址期间的各行扫描线(栅极线)的选择期间,进行信号线驱动电路的电流源电路的设定动作。

在图73中,可以利用设定控制线控制是否进行电流源电路的设定动作。因此,只在某地址期间的某行扫描线(栅极线)被选中时,才能设置设定动作期间Tb并在该设定动作期间Tb进行设定动作。

这样,可以减少信号线驱动电路配置的电流源电路进行设定动作的次数。因此,可以降低功耗。

再有,在电流源电路420中,配置连接在某晶体管的栅极和源极之间的电容元件。利用电流源电路的设定动作使该电容元件积蓄电荷。在理想的情况下,电流源电路的设定动作只在电源输入时进行1次即可。这是因为电容元件积蓄的电荷量不随动作状态和时间等变化也不必使其变化。因此,信号线驱动电路的电流源电路的设定动作可以按任意时序进行任意次数。

但是,实际上,电容元件会输入各种各样的噪声,与电容元件连接的晶体管也会产生漏电流。结果,电容元件积蓄的电荷量有时会随时间变化。若电荷量变化,则从电流源电路输出的电流、即输入到象素的电流发生变化。结果,象素的辉度也发生变化。因此,为了不使电容元件积蓄的电荷变动,有必要以某个周期进行电流源电路的设定动作,使电荷刷新。

使电容元件积蓄的电荷刷新的动作可以在1帧期间进行好几次。或者,也可以在几帧期间进行1次。

再有,在图73中,电流源电路的设定动作在地址期间Ta1和Ta2各进行1次。到底以什么样的频度进行设定动作,可以根据电流源电路具有的电容元件的电荷保存状况适当决定。

其次,图74示出信号线驱动电路配置的电流源电路的设定动作的时序和图73不同的情况。

在图74中,地址期间(进行信号线驱动电路的电流源电路的输入动作的期间)和信号线驱动电路的电流源电路的设定动作期间分离开。即,利用设定控制线使电流源电路的设定动作不在地址期间、即电流源电路的输入动作中进行。进而,在地址期间和地址期间的间隙期间,即在不进行电流源电路的输入动作时进行电流源电路的设定动作。

这样,通过分别进行信号线驱动电路的电流源电路的设定动作和输入动作,可以改变各动作的动作速度。即,可以改变从移位寄存器411输出的采样脉冲的频率。从而,可以只在进行信号线驱动电路的电流源电路的设定动作时使移位寄存器411的动作延迟。结果,可以在足够长的时间内进行电流源电路的设定动作,并更正确地进行设定动作。

因此,在图74的情况下,可以使用对信号线驱动电路的电流源电路不能同时进行设定动作和输入动作的构成。

再有,为了进行电流源电路的设定动作,即使移位寄存器411工作,若没有选择象素中的扫描线(栅极线),则对整个象素也不会有影响。即,在地址期间,因没有选择扫描线(栅极线),故对整个象素没有影响。

此外,当移位寄存器411如图43、图44、图45和图46等那样,是能随机选择多根布线的电路时,不必在1次地址期间和地址期间之间的间隙期间、即电流源电路不进行输入动作的期间的1个区间内完成所有电流源电路的设定动作。即,能够花费几帧期间结束所有电流源电路的设定动作。或者,当在1帧期间内有多个地址期间和地址期间之间的间隙期间时,也可以使用从这些期间选出的几个期间来进行电流源电路的设定动作。这时的时序图示于图75。